Чем отличаются ПЛИС от CPLD. Какие особенности имеют архитектуры CPLD от Xilinx и Altera. Как выбрать подходящую CPLD для проекта. Какие преимущества и недостатки есть у разных семейств CPLD.

Что такое CPLD и в чем их отличие от ПЛИС

CPLD (Complex Programmable Logic Device) — сложные программируемые логические устройства, которые занимают промежуточное положение между простыми ПЛМ и ПЛИС. Основные отличия CPLD от ПЛИС:

- Меньшая логическая емкость (до нескольких тысяч логических элементов)

- Более простая архитектура соединений между логическими блоками

- Энергонезависимая память конфигурации на основе EEPROM или Flash

- Меньшее энергопотребление

- Более высокое быстродействие для простых проектов

CPLD хорошо подходят для реализации относительно небольших проектов, где требуется высокая скорость работы и низкое энергопотребление. Они часто используются в качестве интерфейсных контроллеров, дешифраторов адреса, генераторов тактовых сигналов и т.п.

Архитектура CPLD компании Altera

Компания Altera (ныне часть Intel) была одним из пионеров в разработке CPLD. Их наиболее известные семейства CPLD:

- MAX 3000 — первое поколение CPLD Altera на основе EEPROM

- MAX 7000 — популярная серия CPLD на EEPROM с улучшенным быстродействием

- MAX II — современное семейство CPLD на Flash-памяти

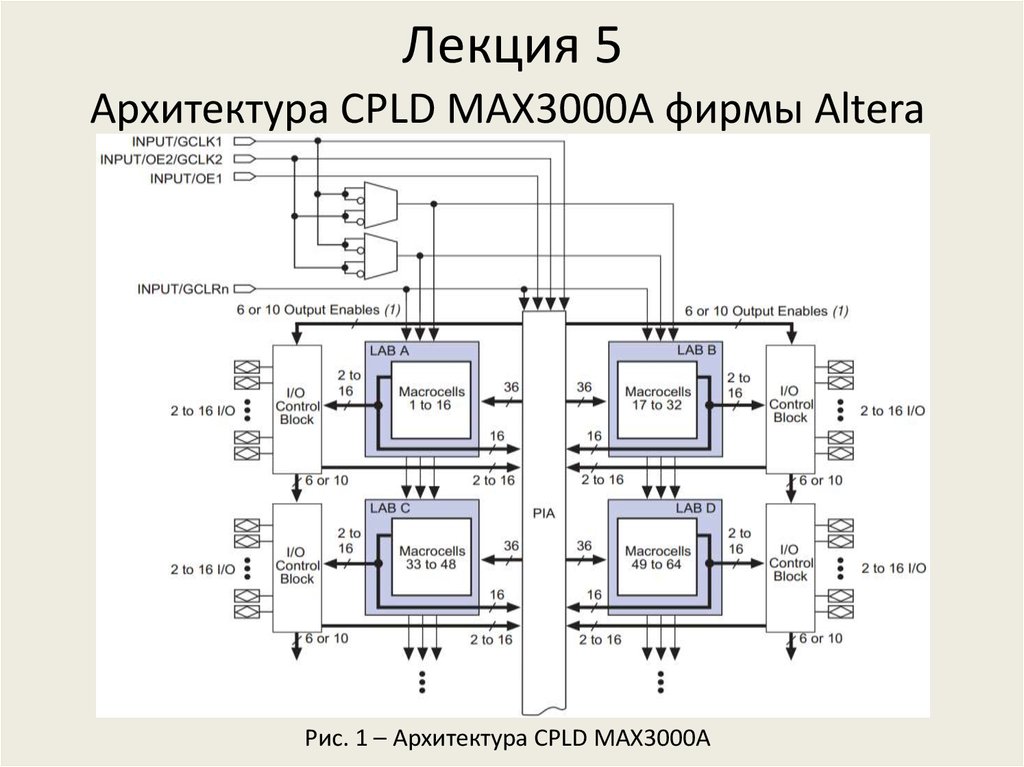

Рассмотрим архитектуру CPLD Altera на примере серии MAX 7000:

Основные компоненты архитектуры:

- Логические массивы (LAB) — блоки, содержащие макроячейки

- Матрица программируемых соединений (PIA) — обеспечивает связи между LAB

- Блоки ввода-вывода — обеспечивают связь с внешними выводами микросхемы

Такая архитектура позволяет эффективно реализовывать как комбинационную, так и последовательностную логику. PIA обеспечивает высокую гибкость соединений между логическими блоками.

Архитектура CPLD компании Xilinx

Компания Xilinx, известная в первую очередь своими ПЛИС, также предлагает линейку CPLD. Наиболее популярные семейства:

- XC9500 — классическое семейство CPLD Xilinx

- CoolRunner-II — современное низкопотребляющее семейство

Рассмотрим архитектуру на примере XC9500:

Ключевые элементы архитектуры:

- Функциональные блоки (FB) — основные логические блоки

- Матрица соединений FastCONNECT — обеспечивает связи между FB

- Блоки ввода-вывода (IOB) — интерфейс с внешними выводами

Архитектура Xilinx отличается более простой структурой по сравнению с Altera. Это обеспечивает несколько меньшую гибкость, но потенциально более высокое быстродействие.

Сравнение CPLD Altera и Xilinx

Для сравнения возьмем примерно эквивалентные по логической емкости устройства: Altera EPM7256E и Xilinx XC95288.

| Altera EPM7256E | Xilinx XC95288 | |

|---|---|---|

| Логическая емкость | 256 макроячеек | 288 макроячеек |

| Макс. частота, МГц | 125 | 100 |

| Задержка распространения, нс | 7.5 | 5 |

| Количество выводов | До 192 | До 192 |

Как видим, устройства имеют схожие характеристики. Altera обеспечивает несколько более высокую тактовую частоту, а Xilinx — меньшую задержку распространения сигнала.

Как выбрать CPLD для проекта

При выборе CPLD для конкретного проекта следует учитывать следующие факторы:

- Требуемая логическая емкость

- Необходимое быстродействие

- Энергопотребление

- Количество требуемых выводов ввода-вывода

- Поддерживаемые напряжения питания и ввода-вывода

- Доступные корпуса микросхем

- Наличие специальных функций (встроенная память, PLL и т.п.)

Также важно учитывать доступность средств разработки и их удобство. Многие разработчики предпочитают использовать CPLD того же производителя, что и применяемые ими ПЛИС, чтобы использовать единый набор инструментов.

Применения CPLD в современной электронике

Несмотря на широкое распространение ПЛИС, CPLD по-прежнему находят применение во многих областях:

- Управление периферийными устройствами

- Реализация протоколов обмена данными

- Генерация и обработка тактовых сигналов

- Дешифрация адресов в системах памяти

- Реализация конечных автоматов

- Замена устаревшей дискретной логики

CPLD особенно востребованы в приложениях, где критичны скорость работы, низкое энергопотребление и малые габариты. Они часто используются в портативных устройствах, автомобильной электронике, промышленных системах управления.

Перспективы развития технологии CPLD

Хотя ПЛИС во многом вытеснили CPLD в сложных проектах, у CPLD остаются свои ниши применения. Основные направления развития технологии CPLD:

- Дальнейшее снижение энергопотребления

- Увеличение быстродействия

- Интеграция дополнительных функций (АЦП, ЦАП, встроенные микроконтроллеры)

- Уменьшение размеров корпусов

- Снижение стоимости

Эти усовершенствования позволят CPLD и дальше успешно конкурировать с ПЛИС в определенных сегментах рынка, особенно в массовых малогабаритных устройствах.

Заключение

CPLD остаются востребованным классом программируемой логики, занимая нишу между простыми ПЛМ и сложными ПЛИС. Ведущие производители Xilinx и Altera (Intel) предлагают широкий выбор CPLD с различными характеристиками. При выборе конкретного устройства важно тщательно проанализировать требования проекта и сравнить доступные варианты. Правильно подобранная CPLD позволит оптимально реализовать требуемую функциональность при минимальных затратах.

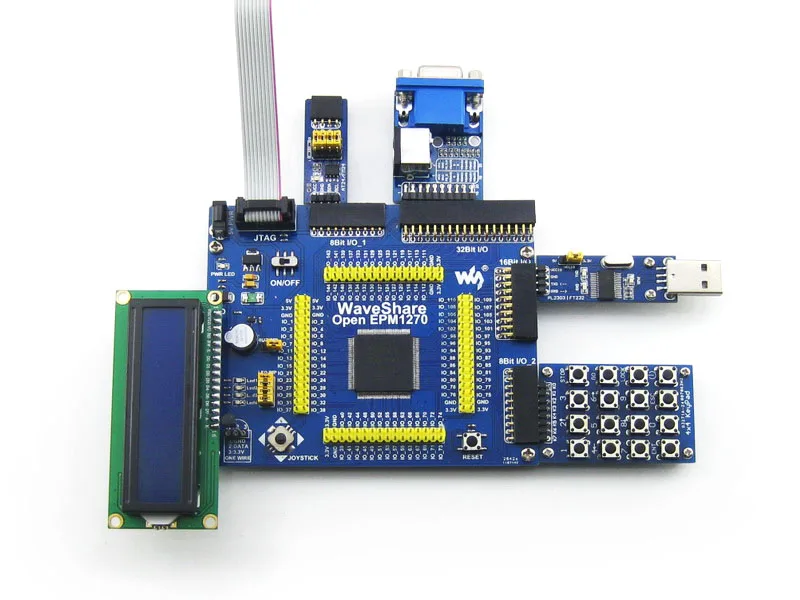

ПЛИС Altera. Часть 4 плата CTRL-CPLD-EPM570

Это четвертая часть цикла посвященная программируемой логике и среде разработки Quartus II компании Intel (Altera).

Ссылки на предыдущие части:

ПЛИС Altera. Часть 1: установка и настройка среды разработки.

ПЛИС Altera. Часть 2: проектирование цифровой схемы.

ПЛИС Altera. Часть 3: первая компиляция проекта

В первой части рассказывалось о загрузке и установке Quartus II Web Edition 13.1, создании пустого проекта с помощью мастера.

Во второй части рассматривалось проектирование цифровой схемы, определялась последовательность шагов для создания конфигурации ПЛИС.

В третьей части описывался процесс компиляции проекта и работа с окном сообщений, выводимых при компиляции. Там же выполнялась настройка главного модуля проекта.

Четвертая часть целиком посвящена электрической части проекта: плате CTRL-CPLD-EPM570 и пробной схеме с кнопками и светодиодами.

После успешной компиляции проекта можно было бы перейти к настройке выводов ПЛИС. Привязке входов и выходов спроектированной схемы к конкретным ножкам микросхемы ПЛИС. Но прежде чем приступить к настройке выводов, необходимо определиться с тем какие выводы и как будут использоваться. Спланировать электрические соединения с микросхемой. Для этого потребуется детально проработать принципиальную схему своего устройства.

Привязке входов и выходов спроектированной схемы к конкретным ножкам микросхемы ПЛИС. Но прежде чем приступить к настройке выводов, необходимо определиться с тем какие выводы и как будут использоваться. Спланировать электрические соединения с микросхемой. Для этого потребуется детально проработать принципиальную схему своего устройства.

Но и проработав принципиальную схему будет не правильным сразу садиться и собирать устройство, в основе которого лежит неизвестная плата. Только после изучения платы и знакомства с перечнем имеющихся на ней устройств можно будет переходить к осмысленному выбору контактов микросхемы ПЛИС для использования в своей схеме.

Доработка принципиальной схемы устройства

Как Вы возможно помните, целью этой серии статей является создание простого устройства состоящего из трех логических примитивов: «И», «ИЛИ» и «НЕ». Вся логика реализуется средствами ПЛИС. А для управления этой логикой, и для отслеживания состояния схемы предполагается использование набора из пяти кнопок и трех светодиодов. Перед проектированием в Quartus логической части схемы был создан набросок будущего устройства. Этот набросок приводится ниже.

Перед проектированием в Quartus логической части схемы был создан набросок будущего устройства. Этот набросок приводится ниже.

В чем недостатки этой схемы?

Во первых, не рекомендуется подключать светодиоды напрямую к источнику питания. Светодиод это полупроводниковый прибор. А сопротивление полупроводника сильно зависит от температуры окружающей среды.

Светодиод, как и другие электроприборы, выделяет тепло при своей работе. Это тепло нагревает его и сопротивление светодиода падает. Но чем меньше сопротивление диода тем больше тока через него может пройти. В свою очередь, чем больше значение тока текущего через диод, тем больше тепла на нем выделяется. Получается замкнутый круг, который приводит к более или менее быстрому перегоранию светодиода. Чтобы избежать столь печального развития событий необходимо использовать резистор. Этот резистор включается последовательно со светодиодом и ограничивает текущий через него ток. Резистор так и называется — токоограничительный. Следовательно, на схему необходимо добавить резисторы, включая их в разрыв между выходом ПЛИС и выводом соответствующего светодиода.

Следовательно, на схему необходимо добавить резисторы, включая их в разрыв между выходом ПЛИС и выводом соответствующего светодиода.

В схеме будут использованы светодиоды красного свечения, которые начинают проводить ток при напряжении около 2 В. Вывод ПЛИС может выдавать напряжение до 3,3 В, с силой тока до 16 мА. Ток в 16 мА является вполне безопасным для светодиода, а вот напряжение в 3,3 В слишком велико. Нужен резистор, который при токе в 16 мА будет пропускать только 2 В. То есть на нем должны будут оставаться лишние 1,3 В. Используя закон Ома для напряжения 1,3 В и тока 0,016 А определяем, что необходим резистор с сопротивлением не менее 82 Ом. Можно использовать резистор и большего сопротивления, но при увеличении сопротивления, например, в 8 раз, ток через него (а значит и яркость свечения диода) уменьшится так же в 8 раз. Поэтому использовать резистор с сопротивлением более 656 Ом не стоит.

Во вторых, внимательно посмотрите на левую часть схемы. Слева ко входам логических элементов подключены кнопки. Эти кнопки, с другой своей стороны, присоединены к питанию схемы – VCC. Из схемы хорошо видно, что при замыкании любой из кнопок на соответствующий вход ПЛИС будет подано напряжение VCC. Насколько большим может быть это напряжение? Из документации на микросхемы серии Max II следует, что максимальное напряжение на входе не должно превышать 4 В. А так как напряжение питания Max II, в свою очередь, не может быть больше 3,3 В, то можно использовать его же и для управления входами схемы. VCC = 3,3 В.

Эти кнопки, с другой своей стороны, присоединены к питанию схемы – VCC. Из схемы хорошо видно, что при замыкании любой из кнопок на соответствующий вход ПЛИС будет подано напряжение VCC. Насколько большим может быть это напряжение? Из документации на микросхемы серии Max II следует, что максимальное напряжение на входе не должно превышать 4 В. А так как напряжение питания Max II, в свою очередь, не может быть больше 3,3 В, то можно использовать его же и для управления входами схемы. VCC = 3,3 В.

Но каким будет напряжение на входе ПЛИС когда кнопка не нажата? Ответ — любым! Входы микросхем обладают очень большим сопротивлением, порядка миллиона Ом. И Max II не исключение. Поэтому даже самые маленькие токи, возникающие от наводок на металл ее выводов, будут создавать на этих выводах напряжения близкие или многократно превышающие 3,3 В. 50 Гц переменного тока в розетке. Атмосферное электричество. Статический заряд на Ваших пальцах. Все это может вызывать ложные срабатывания схемы, или даже вывести ее из строя. Поэтому вход микросхемы всегда должен быть соединен или с плюсом или с минусом ее питания. Но если входы соединить с плюсом питания, то тогда Вы не сможете ими управлять. Ведь кнопки как раз соединяют входы с плюсом питания. А если входы схемы соединить с минусом питания, то при нажатии на кнопку получится короткое замыкание! Нужны еще резисторы.

Поэтому вход микросхемы всегда должен быть соединен или с плюсом или с минусом ее питания. Но если входы соединить с плюсом питания, то тогда Вы не сможете ими управлять. Ведь кнопки как раз соединяют входы с плюсом питания. А если входы схемы соединить с минусом питания, то при нажатии на кнопку получится короткое замыкание! Нужны еще резисторы.

Каждый вход необходимо соединить с минусом питания через резистор. Номинал резистора не должен быть слишком маленьким, чтобы при нажатии на кнопку весь ток не ушел через него на минус питания. Но и не слишком большим, чтобы токи наводок могли свободно уходить через него на минус питания. Общей рекомендацией является применение резисторов номиналом от 10 до 47 кОм.

Таким образом, законченная схема обретает следующий вид. Смотрите рисунок ниже.

Работа над принципиальной схемой завершена. Теперь пришло время ознакомиться с ее центральным элементом: платой CTRL-CPLD-EPM570.

Плата CTRL-CPLD-EPM570

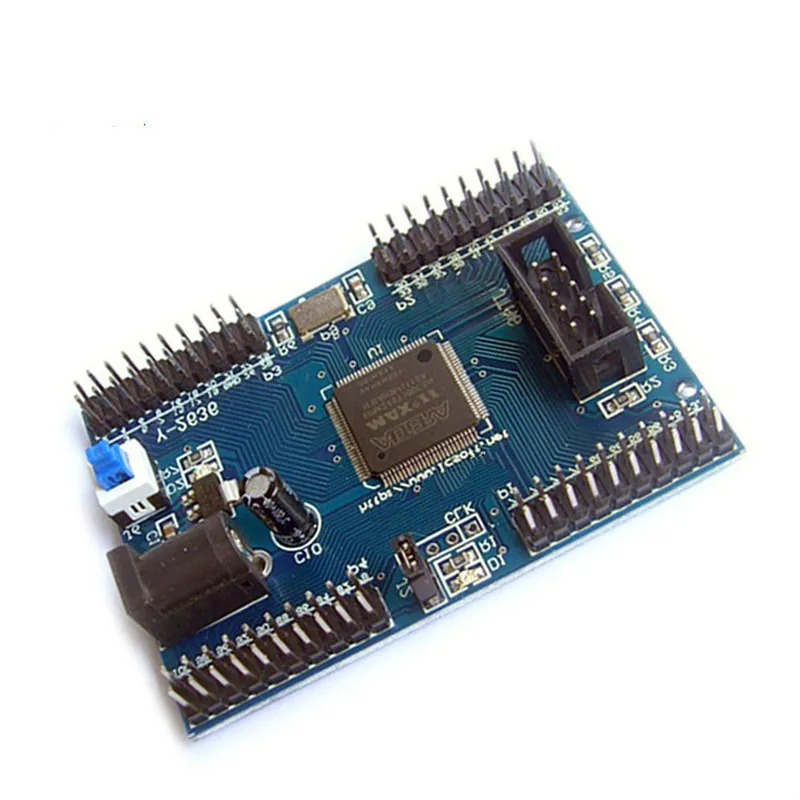

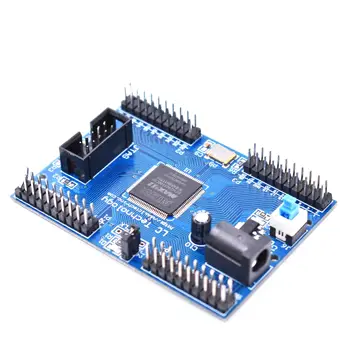

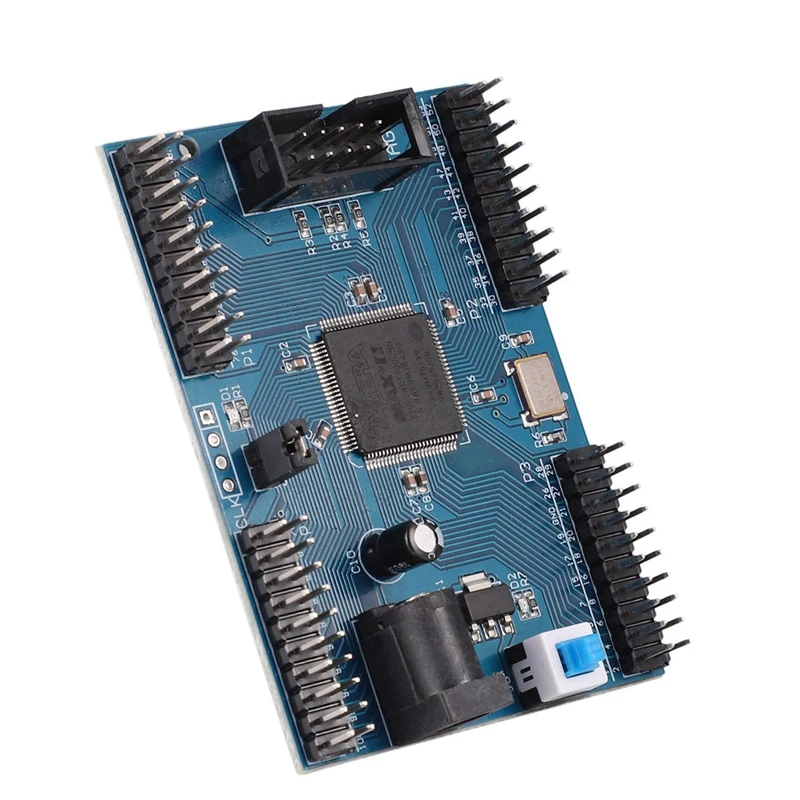

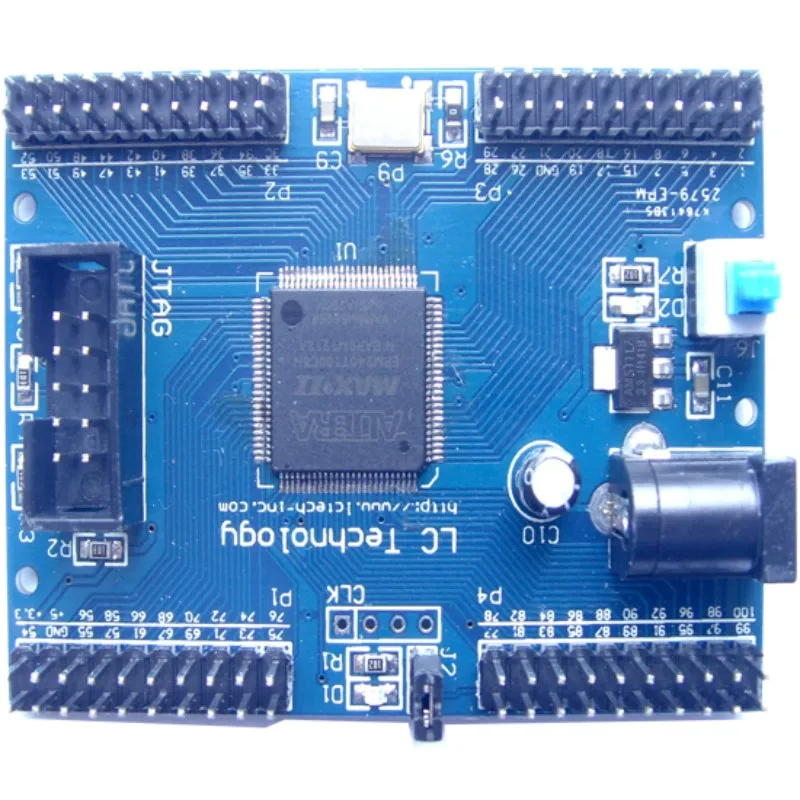

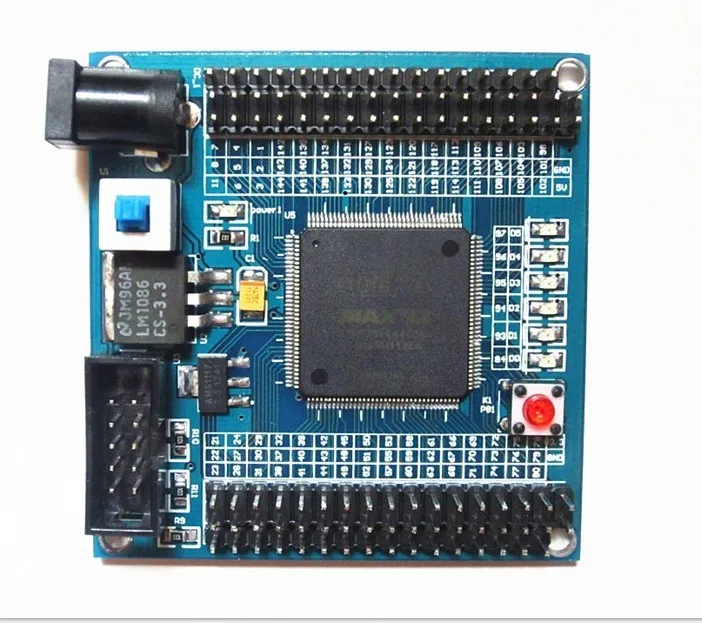

Плата CTRL‑CPLD‑EPM570 имеет почти квадратную форму, с размерами 71х72 мм. Ее внешний вид представлен на следующей фотографии.

Ее внешний вид представлен на следующей фотографии.

Плата питается напряжением 5 В от разъема в ее левом верхнем углу. Разъем обозначен цифрой 1 на фотографии. Полярность на разъеме следующая: – –(о– + То есть плюсовой контакт находится в центре разъема.

Входное напряжение 5 В поступает на микросхему стабилизатора U2, который преобразует их в 3,3 В. Стабилизатор обозначен на фотографии цифрой 2. Микросхема стабилизатора относится к 1117 серии. Максимальный ток, который она может отдать, не превышает 800 мА. Напряжение 3,3 В используется для питания ПЛИС.

Напряжение 3,3 В так же выведено на блок контактов P4, который расположен непосредственно под стабилизатором. Этот блок обозначен на фотографии цифрой 3. Его можно использовать для питания схем подключаемых к ПЛИС. Входное напряжение 5 В, как и общий минус питания, выведены на P4. Все контакты блока подписаны, что позволяет легко определить их назначение.

Справа от разъема питания располагается кнопка с фиксацией. Она обозначена цифрой 4. Эта кнопка управляет питанием платы. В отжатом положении она отключает питание. Рядом с кнопкой находится светодиод D1 (цифра 5 на фотографии), который используется как индикатор питания.

Она обозначена цифрой 4. Эта кнопка управляет питанием платы. В отжатом положении она отключает питание. Рядом с кнопкой находится светодиод D1 (цифра 5 на фотографии), который используется как индикатор питания.

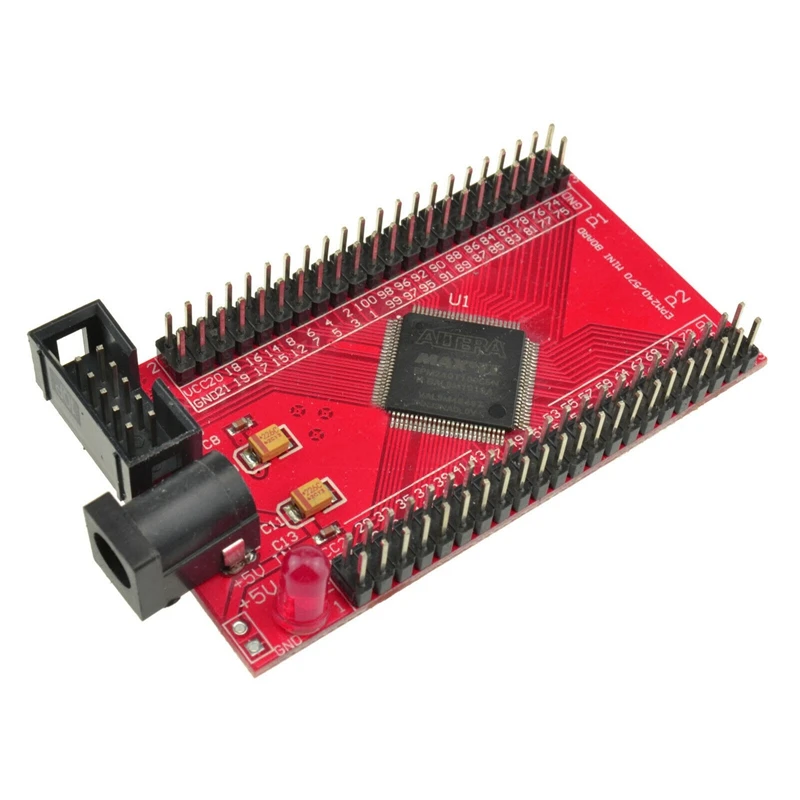

В центре платы располагается сама микросхема ПЛИС: чип Altera Max II модели epm570t100c5n.

Большая часть ножек ПЛИС выведена на контактные группы P1 и P2. P1 и P2 располагаются по левому и правому краям платы соответственно. Именно к ним необходимо подключать схему, которой должна управлять ПЛИС. Все контакты на P1 и P2 подписаны номерами соответствующих ножек ПЛИС. Но не все из них доступны для пользователя. Контакты по краям P1 и P2: 88, 90, 37 и 39 заняты установленными на них перемычками. Перемычки обозначены на фотографии цифрой 6. С их помощью на соответствующие выводы ПЛИС подается необходимое для работы питание – 3,3 В. По утверждению производителя их ни в коем случае нельзя их удалять. Но фактически, в этой версии платы перемычки продублированы дорожками на плате.

Еще пять контактов P1 и P2 подключены параллельно с установленными на плате устройствами.

Вывод 44 на P2 включен параллельно с кнопкой RESET и RC‑цепочкой R11-C13. Кнопка расположена у нижнего края платы, она обозначена цифрой 7. Непосредственно под кнопкой располагается RC‑цепочка.

Выводы 43, 42, 41, 40 соединены со светодиодами красного свечения 1, 2, 3 и 4 соответственно. Группа светодиодов располагается справа от кнопки RESET и обозначена цифрой 8 на фотографии. Их токоограничительные резисторы R7‑R10 расположены непосредственно под светодиодами.

Часть контактов ПЛИС вообще не выведена на P1 и P2. Это контакты для подключения тактовых генераторов и программатора.

12 контакт ПЛИС соединен с установленным на плате генератором тактовой частоты X1 на 50 МГц. Тактовый генератор расположен в верхней части платы, под кнопкой включения питания. На фотографии он обозначен цифрой 9.

14 контакт выведен к посадочному месту для второго тактового генератора X2. Это посадочное место расположено с нижней стороны платы. Сам генератор не установлен.

Это посадочное место расположено с нижней стороны платы. Сам генератор не установлен.

Контакты 62 и 64 выведены на отдельную контактную группу P3. P3 расположена справа от микросхемы ПЛИС, она обозначена цифрой 10 на фотографии. Контакт P3 CLK2 – это вывод 62, а P3 CLK3 – вывод 64. Группу P3 предполагается использовать для подключения внешних генераторов тактовой частоты.

Для подключения программатора предназначен разъем JTAG в левой нижней части платы. На фотографии на обозначен цифрой 11. На этот разъем выведено четыре ножки микросхемы ПЛИС: 22, 23, 24 и 25.

Таким образом, часть выводов, занятых устройствами платы, недоступны для использования каким‑либо способом кроме определенного разработчиками платы CTRL‑CPLD‑EPM570. Это вывод 12 соединенный с тактовым генератором X1. И выводы 22, 23, 24 и 25 – разъем JTAG. А вывод 14 не получится использовать без пайки. Что не так уж и много, учитывая общее число выводов микросхемы.

Так как на плате установлено четыре светодиода, возникает вопрос: возможно ли применить их в нашей схеме? Для того чтобы ответить на него необходимо рассмотреть схему включения этих светодиодов.

На схеме видно, что диоды подключены к плюсу питания. И это меняет логику управления ими, так как светодиод будет загораться при подаче логического нуля на соответствующий выход ПЛИС. И наоборот — логическая единица будет выключать диод. Такая логика управления, когда высокий логический уровень является запрещающим, а низкий — разрешающим, называется инверсной. Ранее спроектированная схема ориентирована на работу с прямой логикой. Получается, что для работы со светодиодами на плате потребуется изменить созданную в Quartus схему. Усложнить ее, добавив инверсию. Поэтому от использования предустановленных светодиодов придется отказаться. Использовать контакты включенные параллельно со светодиодами тоже не получится, так как они постоянно соединены с плюсом питания через диоды. Поэтому контакты 40, 41, 42 и 43 исключаются из списка подходящих для реализации Вашей схемы.

От использование контакта, к которому подключена кнопка RESET, тоже придется отказаться. Так как он соединяется с RC‑цепочкой R11-C13, где R11 присоединен к питанию платы. Опять инверсная логика.

Опять инверсная логика.

После знакомства с платой можно прийти к выводу, что ни одно из установленных на ней дополнительных устройств не годится для использования в спроектированной схеме. Поэтому, выводы 90, 88, 64, 62, 43, 42, 41, 40, 39, 37, 25, 24, 23, 22, 14, 12, задействованные для подключения кнопки RESET, блока светодиодов, тактовых генераторов, питания ПЛИС и программатора, не будут использоваться в проекте.

Важно знать, что платы CTRL‑CPLD‑EPM570 идут с предварительно загруженной демонстрационной конфигурацией — четырехбитный счетчик. Эта схема тактируется генератором X1 и использует четыре предустановленных светодиода LED1-LED4. Помните об этом когда будете подключать свои схемы.

После изучения возможностей платы CTRL‑CPLD‑EPM570 и детальной проработки принципиальной схемы задуманного устройства можно переходить к настройке выводов ПЛИС в Quartus. Для настройки выводов используется инструмент «Pin Planner». Работа с этим инструментом будет описана в следующей части цикла статей. А четвертая часть на этом завершается.

А четвертая часть на этом завершается.

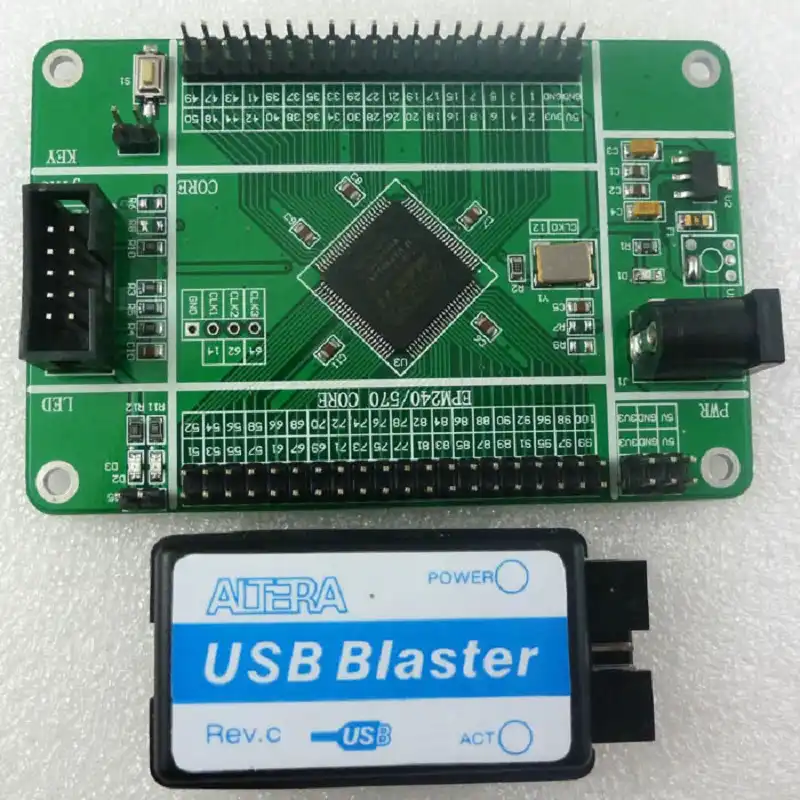

USB BLASTER CABLE (ALTERA CPLD / FPGA download cable) From 175.5 UAH

Product id: 33018Manufacturer:

Описание: Соединительный кабель для передачи/загрузки данных в ряд программируемых пользователем устройств производства FPGAs, CPLDs серий фирмы ALTERA

Тип средств разработки: Программатор

on stock: 8 pcs

7 pcs — stock Kyiv

1 pcs — RADIOMAG-Lviv

| 1+ | 195 UAH |

| 10+ | 175.5 UAH |

Technical description USB BLASTER CABLE (ALTERA CPLD / FPGA download cable)

With this product buy

| 5,1 Ohm 5W 5% (SQP50JB-5R1) Product id: 11174 |

Manufacturer: Hitano

Resistors (Through Hole) > Wire-Wound Cement Resistors 2…25W

Номинал: 5,1 Ohm

Мощность: 5 W

Точность: ±5%

U раб. макс.

макс.

Размеры, мм: 22,0×10,0x9,5; dвыв.=0,8

Тип: выводные, цементные, проволочные

500 pcs — waiting

|

| Analogue |

|

5,1 Ohm 5W 5% (KLS6-SQP-5W-5R1-J) Product id: 150332 |

| WH-7 (NS25-W7P) Product id: 59129 |

Manufacturer: Ninigi

Connectors, Interconnect > Low-voltage Power Connectors

Описание: Вилка на плату с защелкой, 7 контактов, шаг 2,54мм, 3А, 250VAC

Вилка или гнездо: Вилка (штекер)

Кол-во контактов: 7

Шаг контактов: 2,54 mm

Серия разьема

Монтаж: На плату

96 pcs — RADIOMAG-Kyiv

48 pcs — RADIOMAG-Lviv

136 pcs — RADIOMAG-Odesa

145 pcs — RADIOMAG-Dnipro

|

| BH-10 вилка на плату (KLS1-202-10-S-B KLS) Product id: 72272 |

Manufacturer: KLS

Connectors, Interconnect > Interface (D-Sub, D-Shaped)

Функциональное описание: Вилка на плату, прямая шаг 2,54мм 10 контактов (2х5), 1А, 250VAC

Вилка или розетка: Вилка

Кол-во контактов: 10

Серия: BH

Механический монтаж: На плату

20000 pcs — waiting 30.04.2023

|

| Possible replacement |

|

BH-10 (ZL231-10PG) (вилка на плату) Product id: 12373 |

| Related products |

|

IDM-10 (вилка на шлейф) Product id: 123996 |

| BH-10R вилка на плату (KLS1-202-10-R-B KLS) Product id: 72273 |

Manufacturer: KLS

Connectors, Interconnect > Interface (D-Sub, D-Shaped)

Функциональное описание: Вилка на плату, угловая шаг 2,54мм 10 контактов (2х5), 1А, 250VAC

Кол-во контактов: 10

Серия: BH

Механический монтаж: На плату

Ориентация в пространстве: Угловой

29 pcs — RADIOMAG-Odesa

60 pcs — RADIOMAG-Dnipro

2000 pcs — waiting 30. 05.2023

05.2023

|

| Related products |

|

IDM-10 (вилка на шлейф) Product id: 123996 |

| Флюс RF800 100мл средне активный канифольный (ART.AGT-109) Product id: 79905 |

Manufacturer: AG Termopasty

Soldering Equipment, Solders > Soldering fluxes

Категория: Флюс

Описание: Средне активный канифольный флюс, который идеально увлажняет поверхности как Cu, так и PbSn. Дополнительно не требует смывания.

Вес/объём/Кол-во

Вес/объём/Кол-во

: 100 ml

24 pcs — stock Kyiv

2 pcs — RADIOMAG-Kyiv

3 pcs — RADIOMAG-Lviv

4 pcs — RADIOMAG-Odesa

2 pcs — RADIOMAG-Dnipro

|

Сравнение Xilinx и Altera CPLD

04. 08.2021, hardwarebee

08.2021, hardwarebee

В этой статье обсуждается разница между архитектурой Xilinx (AMD) и Altera (Intel) CPLD и их сравнение. Кроме того, в этой статье обсуждаются архитектура CLB, генерация тактовых импульсов, память и операции DSP как для Xilinx, так и для Altera.

Что такое CPLD?

За последние 10 лет процесс проектирования сложных систем претерпел значительные изменения. Удобство использования программируемых устройств значительно возросло. Инженеры-электронщики начинают реализовывать свои логические схемы на простой программируемой логической матрице (PLA), программируемой логической матрице (PAL), затем переходят к простой программируемой логической матрице (SPLA), а затем переходят к сложному программируемому логическому устройству (CPLD).

Чип CPLD включает в себя несколько блоков логики и матрицу соединений для соединения одного блока с другим, чтобы облегчить разработчику реализацию на чипе большего количества входов и выходов, необходимых для приложения.

Существует два основных варианта CPLD, основанных на стратегии проектирования производителя: некоторые фиксируют массив И и оставляют программируемые логические элементы ИЛИ, а некоторые используют противоречивый подход с программируемыми логическими элементами И и фиксированными логическими элементами ИЛИ. Чтобы внедрить логику в CPLD, разработчик должен уметь работать с языками RTL, Verilog или VHDL, и должен иметь набор инструментов, предоставленный поставщиком, для применения правильной стратегии размещения и маршрутизации для окончательной реализации проекта.

Применения CPLD

Применения CPLD включают следующее:

- Сложные программируемые логические устройства идеально подходят для высокопроизводительных приложений, где не требуются большие задержки.

- CPLD может использоваться в цифровых конструкциях для выполнения функций загрузчика.

- CPLD также может использоваться для загрузки данных конфигурации FPGA.

- Как правило, они используются в небольших дизайнерских приложениях, таких как кодирование и декодирование адресов.

- CPLD часто используются во многих приложениях, например, в экономичных приложениях.

- CPLD выгодно использовать в приложениях небольшого размера и с низким энергопотреблением.

Рассмотрение выбора CPLD

При рассмотрении выбора CPLD для использования в проекте следует учитывать некоторые ключевые критерии.

Технология программирования

Какие возможности программирования предлагает вам CPLD на основе EPROM? CPLD на основе FLASH или EEPROM. SRAM, технологии Antifuse также доступны для CPLD.

Возможности функциональных блоков

Каковы возможности функциональных блоков и возможности программирования CPLD?

Возможности ввода-вывода

Возможности ввода-вывода, количество операций ввода-вывода, которые может обрабатывать CPLD. Уровень напряжения также входит в критерии выбора.

Уровень напряжения также входит в критерии выбора.

Плотность

Вы можете определить требуемый размер CPLD (логическая плотность) для своего проекта, отправив свой проект в программное обеспечение поставщика.

Производительность

CPLD бывают разных классов скорости, так что вы платите только за необходимую производительность. Используйте программное обеспечение CPLD поставщика, чтобы определить класс скорости, необходимый для удовлетворения требований синхронизации вашей системы.

Напряжение и мощность

Различные семейства CPLD имеют различные предложения по напряжению (питание и ввод-вывод) и мощности (в режиме ожидания и динамическом режиме).

Упаковка

CPLD поставляются в различных типах корпусов: от недорогих корпусов QFP до сверхмалых страниц размером с микросхему и корпусов BGA с большим количеством операций ввода-вывода. выберите CPLD, который лучше всего соответствует требованиям проекта. Далее в этой статье мы обсудим архитектуру Xilinx и Altera CPLD и их преимущества.

выберите CPLD, который лучше всего соответствует требованиям проекта. Далее в этой статье мы обсудим архитектуру Xilinx и Altera CPLD и их преимущества.

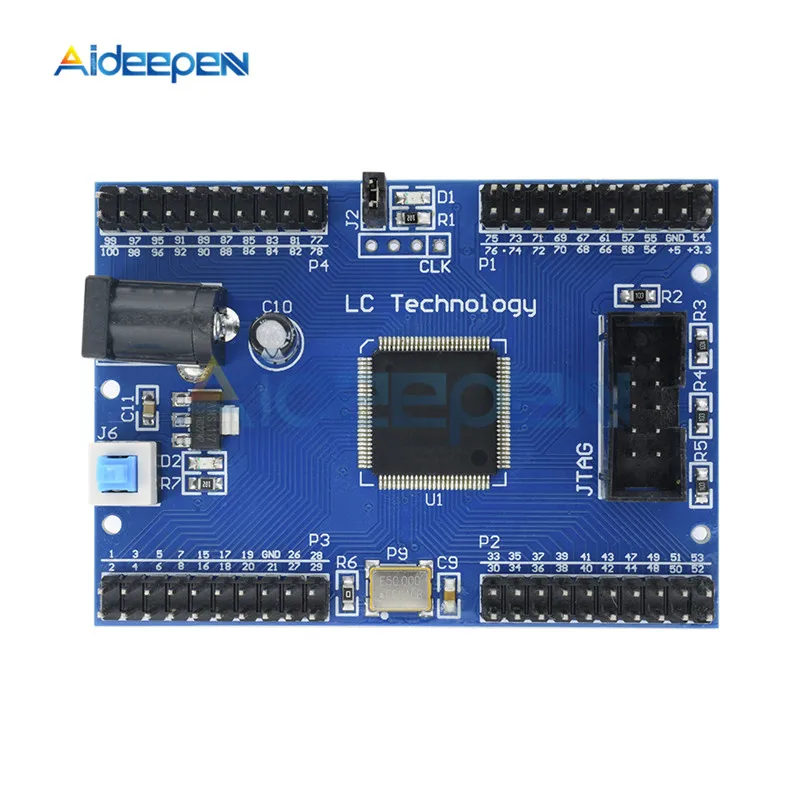

CPLD компании Altera

Компания Altera произвела первые CPLD. Сначала в их семействе микросхем под названием Classic EPLD, а затем в трех разных сериях, названных MAX 5000, MAX 7000 и MAX 9.000. Из-за быстрорастущего рынка программируемых устройств другие разработчики разработали устройства в категории CPLD, и теперь доступно много вариантов, например, Microsemi, Xilinx. Здесь обсуждение будет сосредоточено на серии MAX 9000 для Altera, поскольку она широко используется и предлагает современную логическую емкость и быстродействие. MAX 9000 представляет собой более старую технологию, предлагающую экономичное решение.

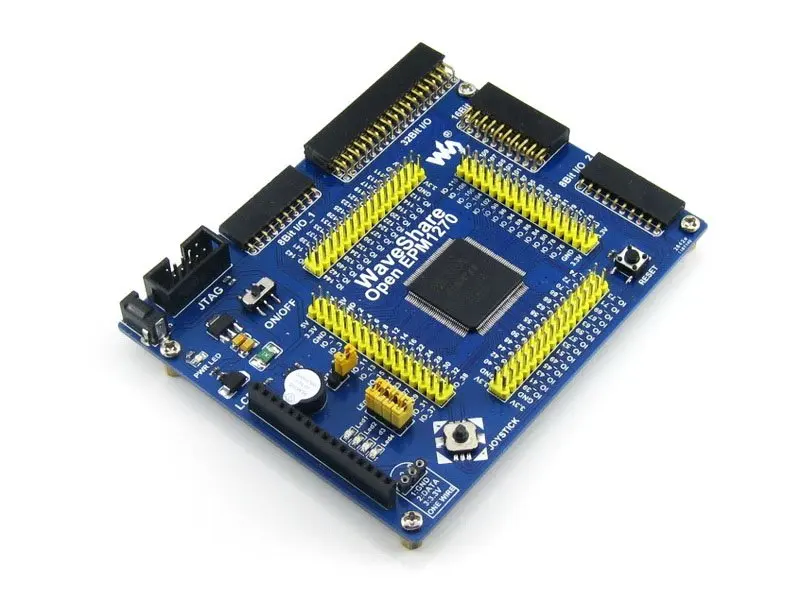

Общая архитектура серии Altera MAX 7000 показана на рисунке 1. Она содержит массив блоков, называемых блоками логического массива (LAB), которые используются в Altera, и соединительные провода, называемые массивом программных межсоединений (PIA). PIA может подключать любой вход или выход LAB к любой другой LAB для реализации сложных функций. Вот как работает маршрутизация между различными логическими блоками. IO чипа подключаются напрямую к PIA и LAB. LAB можно рассматривать как сложную структуру, подобную CPLD, поэтому весь чип можно рассматривать как массив CPLD. Устройства MAX 7000 доступны как на базе технологии EPROM, так и на основе технологии EEPROM.

PIA может подключать любой вход или выход LAB к любой другой LAB для реализации сложных функций. Вот как работает маршрутизация между различными логическими блоками. IO чипа подключаются напрямую к PIA и LAB. LAB можно рассматривать как сложную структуру, подобную CPLD, поэтому весь чип можно рассматривать как массив CPLD. Устройства MAX 7000 доступны как на базе технологии EPROM, так и на основе технологии EEPROM.

Рисунок 1 : Altera Max 7000 Series

CPLD XILINX

XILINX — в основном производитель FPGA; но они также предлагают выбор CPLD. Их самый известный CPLD называется XC9500. Каждое устройство XC9500 состоит из нескольких функциональных блоков (FB) и блоков ввода/вывода (IOB), полностью связанных между собой матрицей переключателей Fast CONNECT. IOB обеспечивает буферизацию входных и выходных данных устройства. Каждый FB обеспечивает возможность программирования логики с 36 входами и 18 выходами. Матрица переключателей Fast CONNECT соединяет все выходы FB и входные сигналы со входами FB. Для каждого функционального блока от 12 до 18 выходов (в зависимости от количества выводов корпуса) и связанные с ними выходные сигналы позволяют передавать сигналы непосредственно на IOB. На рис. 2 показан XC9.500 Xilinx CPLD архитектура.

Матрица переключателей Fast CONNECT соединяет все выходы FB и входные сигналы со входами FB. Для каждого функционального блока от 12 до 18 выходов (в зависимости от количества выводов корпуса) и связанные с ними выходные сигналы позволяют передавать сигналы непосредственно на IOB. На рис. 2 показан XC9.500 Xilinx CPLD архитектура.

Figure 2 : Xilinx XC9500 CPLD Architecture (courtesy Xilinx)

Altera vs Xilinx CPLDs

In this section, a comparison between Altera vs Xilinx CPLD предоставляется. Для сравнения выбрано устройство семейства XC9500 (XC95288) и устройство семейства Altera MAX7000 (EPM7256E). Оба устройства имеют большой потенциал и возможности, чтобы превзойти друг друга. Например, Altera CPLD имеет меньше ресурсов, но может работать на более высокой частоте. Устройства Xilinx работают на более низкой частоте, но обеспечивают меньшую выходную мощность и задержку от контакта к выводу.

5 UAH

5 UAH