Что такое арифметико-логическое устройство. Какие функции выполняет АЛУ в составе процессора. Как устроено АЛУ и из каких компонентов состоит. Какие операции выполняет арифметико-логическое устройство. Как происходит обработка данных в АЛУ.

Что такое арифметико-логическое устройство и его роль в процессоре

Арифметико-логическое устройство (АЛУ) — это ключевой компонент центрального процессора компьютера, отвечающий за выполнение арифметических и логических операций над данными. АЛУ является «вычислительным ядром» процессора и обеспечивает обработку числовой и логической информации.

Основные функции АЛУ включают:

- Выполнение арифметических операций (сложение, вычитание, умножение, деление)

- Выполнение логических операций (И, ИЛИ, НЕ, исключающее ИЛИ)

- Побитовые операции над данными

- Сравнение чисел

- Сдвиги и циклические сдвиги

АЛУ работает под управлением устройства управления процессора, которое подает на него управляющие сигналы и операнды. Результаты вычислений АЛУ передает обратно в регистры процессора или память.

Структура и компоненты арифметико-логического устройства

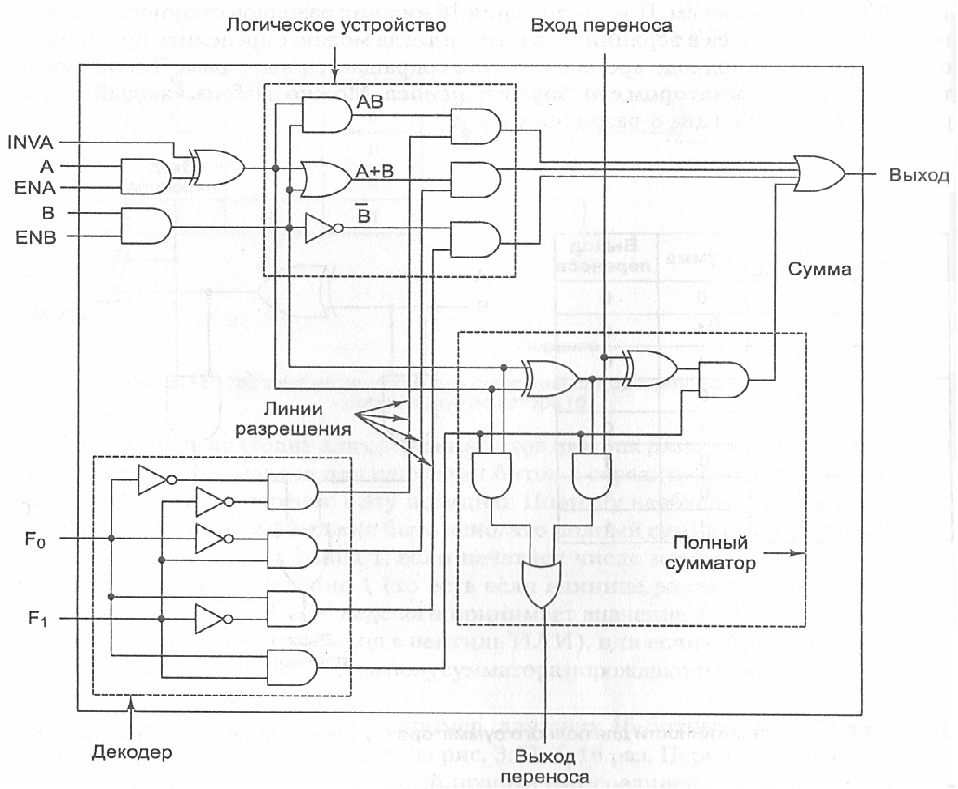

В состав типичного АЛУ входят следующие основные компоненты:

- Комбинационные схемы для выполнения арифметических и логических операций

- Регистры для хранения операндов и результатов

- Схемы управления и синхронизации

- Схемы формирования признаков результата (флагов)

Ключевым элементом АЛУ является сумматор — устройство для сложения двоичных чисел. На его основе реализуются и другие арифметические операции. Логические операции выполняются с помощью схем на логических элементах.

Принцип работы АЛУ при выполнении операций

Рассмотрим последовательность работы АЛУ на примере операции сложения двух чисел:

- Операнды загружаются в регистры АЛУ из памяти или других регистров процессора

- Устройство управления подает на АЛУ код операции сложения

- Комбинационная схема сумматора выполняет сложение операндов

- Результат записывается в регистр результата

- Устанавливаются флаги (переполнение, знак и т.д.)

- Результат передается для дальнейшего использования

Аналогичным образом выполняются и другие операции, только задействуются различные функциональные блоки АЛУ.

Виды операций, выполняемых в АЛУ

Современные АЛУ способны выполнять широкий спектр операций над данными:

- Арифметические операции над целыми числами и числами с плавающей точкой

- Логические операции (И, ИЛИ, НЕ, исключающее ИЛИ)

- Побитовые операции (сдвиги, циклические сдвиги, маскирование)

- Операции сравнения чисел

- Преобразование форматов данных

- Вычисление контрольных сумм

Набор операций зависит от архитектуры конкретного процессора. Более сложные АЛУ могут выполнять и специальные математические функции.

Особенности реализации АЛУ в современных процессорах

В современных процессорах применяются различные подходы к реализации АЛУ для повышения производительности:

- Использование нескольких параллельных АЛУ для одновременного выполнения операций

- Конвейерная обработка данных в АЛУ

- Применение SIMD-расширений для векторных операций

- Специализированные АЛУ для работы с числами с плавающей точкой

- Оптимизация схемотехники для уменьшения задержек

Это позволяет существенно увеличить скорость обработки данных в процессоре. Однако базовые принципы работы АЛУ остаются неизменными.

Взаимодействие АЛУ с другими устройствами процессора

АЛУ тесно взаимодействует с другими компонентами процессора в ходе выполнения вычислений:

- Получает операнды из регистров общего назначения

- Выполняет операции под управлением устройства управления

- Записывает результаты обратно в регистры

- Устанавливает флаги состояния в регистре флагов

- Взаимодействует с кэш-памятью при обращении к данным

Эффективная организация этого взаимодействия — важная задача при проектировании процессоров для обеспечения высокой производительности.

Эволюция архитектуры АЛУ

Архитектура АЛУ прошла долгий путь развития с момента создания первых ЭВМ:

- Первые АЛУ выполняли только простейшие операции сложения и вычитания

- Постепенно добавлялись новые арифметические и логические операции

- Появились специализированные АЛУ для чисел с плавающей точкой

- Внедрены параллельные и конвейерные архитектуры

- Реализована поддержка векторных SIMD-инструкций

- Созданы специализированные АЛУ для криптографии, обработки сигналов и др.

Развитие АЛУ продолжается и сегодня в направлении повышения энергоэффективности и производительности.

Арифметико-логическое устройство — Энциклопедия по машиностроению XXL

До недавнего времени цифровые вычислительные устройства могли оперировать лишь с числовыми значениями, т. е. заниматься только арифметикой, сводя к четырем действиям арифметики даже самые сложные вычислительные и логические задачи. По выведенным уже кем-то и как-то формулам машина могла вычислить результат для любого частного случая, но вывести эти же самые формулы (даже достаточно простые) сама не могла. Цифровая символика по силам ЦВМ, а буквенная (т. е. алгебраическая) до недавних пор — нет. [c.253]Моделирование цифровой РЭА возможно с различной степенью детализации. На логическом (вентильном) подуровне функционально-логического проектирования в качестве элементов аппаратуры рассматривают простые схемы типа вентилей, на регистровом подуровне элементами могут быть как отдельные вентили, так и любые более сложные сочетания простых схем, например регистры, счетчики, дешифраторы, сумматоры, арифметико-логические устройства и т.

Другой вариант мультимикропроцессорной реализации адаптивного управления УИМ-28 основывается на использовании микропроцессорного набора серии К-589. В состав этого набора входят блок управления памятью, один-два модуля ПЗУ. 2-раз-рядные наращиваемые модули арифметико-логического устройства (АЛУ), четыре-пять регистров. Быстродействие АЛУ в конвейерном режиме составляет 0,1 мкс на микрокоманду, сложение модулей 32-разрядных чисел в ПЗУ выполняется за О, мкс, умножение — за 2 мкс. Как показывают расчеты [47 1, для вычисления одного такта цифрового адаптивного управления КИР за время, не превышающее 256 мкс, требуется восемь микропроцессоров типа К-589. Такое быстродействие мультимикропроцессорной системы адаптивного управления позволяет не только полностью автоматизировать процесс наведения ИГ, но и гарантировать высокое качество переходных процессоров в условиях значительной неопределенности и непредсказуемого дрейфа параметров КИР и измеряемой детали.

Процессор ЦВМ состоит из арифметико-логического устройства (АЛУ), устройства управления (УУ), внутренних регистров (Р) и интерфейсных средств (И), обеспечивающих связь этих устройств между собой и с внешними по отношению к ним устройствами (рис. 5.1). [c.135]

АЛУ — арифметико-логическое устройство У У — устройство управления Р — юк регистров И — интерфейс [c.136]

Арифметико-логическое устройство (АЛУ) включает один или несколько сумматоров и регистры для хранения промежуточных данных и результатов. Принцип работы сумматоров — поразрядное сложение с последующими переносами в старшие разряды. Умножение и деление осуществляются многократным сложением или вычитанием с поразрядным сдвигом. Сдвиг содержимого регистра на один разряд влево-вправо эквивалентен умножению-делению содержимого числа на 2. [c.484]

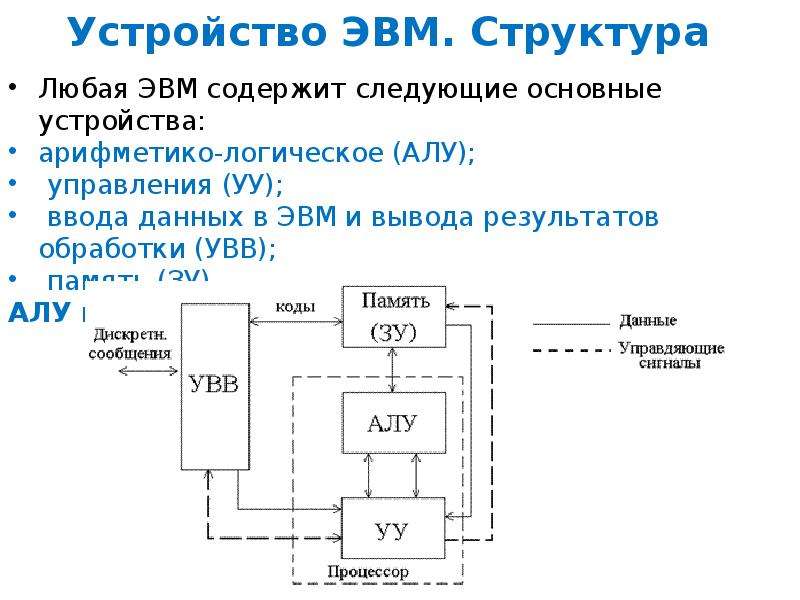

Электронная вычислительная машина (компьютер) — предназначенный для автоматизации процесса обработки информации комплекс технических средств, построенный на электронных элементах. Обобщенная структурная схема ЭВМ включает пять основных функциональных блоков устройство ввода (УВв), запоминающее устройство (ЗУ), арифметико-логическое устройство (АЛУ), устройство управления (УУ) и устройство вывода информации (УВыв) (рис. 2.1).

[c.40]

Обобщенная структурная схема ЭВМ включает пять основных функциональных блоков устройство ввода (УВв), запоминающее устройство (ЗУ), арифметико-логическое устройство (АЛУ), устройство управления (УУ) и устройство вывода информации (УВыв) (рис. 2.1).

[c.40]

Преобразование информации происходит в арифметико-логическом устройстве. АЛУ выполняет арифметические операции (например, сложение или умножение) и логические операции (обработка кодов чисел с помощью булевой алгебры И , ИЛИ ).

Совокупность устройств ЭВМ, включающая устройство управления, арифметико-логическое устройство, внутреннюю регистровую память, принято называть центрапьным процессором. В компьютере его функции выполняет микропроцессор. [c.43]

На 1 уровне системы располагаются центральные процессоры (ЦП), в состав которых входят арифметико-логические устройства, центральные устройства управления и внутренняя память процессоров (иногда сверхоперативная память — СОП). Процессоров может быть несколько. Они могут быть универсальными и специализированными и отличаться своими функциональными возможностями. На этом же уровне находятся модули оперативных запоминающих устройств.

[c.44]

Процессоров может быть несколько. Они могут быть универсальными и специализированными и отличаться своими функциональными возможностями. На этом же уровне находятся модули оперативных запоминающих устройств.

[c.44]

В арифметико-логическом устройстве ЭВМ арифметические операции выполняются над операндами, представленными с фиксированной или плавающей точкой, в двоичной либо в десятичной системах счисления. [c.58]

Арифметико-логическое устройство. АЛУ выполняет арифметические и логические операции над операндами в принятой системе счисления и вырабатывает признаки результата, необходимые для управления ходом вычислительного процесса. В некоторых моделях машин АЛУ называется операционным блоком. [c.65]

| Рис. 2.7. Структурная схема арифметико-логического устройства |

333]

333]Арифметико-логическое устройство (АЛУ) процессора выполняет операции в соответствии с правилами двоичной арифметики независимо от типа данных. Наряду с самим результатом АЛУ формирует также признаки нулевого (ALU Z) и отрицательного (ALUN) результата, переполнения (ALUV) и переноса (ALUС). Отметим, что эти признаки еще не являются кодами условий, а только используются процессором для их установки в зависимости от типа операции. Можно выделить четыре основных типа операций и соответственно четыре типа установки кодов условий [c.93]

Основным элементом блока обработки является арифметико-логическое устройство (АЛУ), способное выполнять 16 арифметических и 16 логических операций. Состав операций АЛУ определяется возможностями микросхемы К155ИПЗ. АЛУ управляется двумя полями микрокоманды ФНК —функция и МДФ —модификация функции. Основная операция задается полем ФНК и может быть модифицирована в зависимости от содержимого РК. Такой способ управления АЛУ позволяет минимизировать объем памяти микрокоманд. Например, для реализации всех арифметических и логических команд базового набора используется единая микропрограмма, а микрооперации, выполняемые в АЛУ, задаются фактически кодом машинной команды в РК.

[c.111]

Например, для реализации всех арифметических и логических команд базового набора используется единая микропрограмма, а микрооперации, выполняемые в АЛУ, задаются фактически кодом машинной команды в РК.

[c.111]

Основным узлом операционной части служит арифметико-логическое устройство, построенное на двух микросхемах КР1802ВС1. АЛУ выполняет до шестнадцати логических и арифметических операций и четыре их модификации. Входные операнды для АЛУ задаются по шинам А и В результат операции АЛУ выдается и используется также через шину А. Отметим, что шины А и В являются двунаправленными с тремя состояниями. Фазы приема и выдачи информации разделяются сигналами микропрограммного управления. [c.112]

Процессор СМ-1420 имеет структуру, показанную на рис. 2.5. Ядром центрального процессора является 16-разрядный арифметико-логический модуль AM, построенный на базе четырехразрядных обрабатывающих секций КР1804 [8]. Кроме арифметико-логического устройства и вспомогательных регистров, AM содерл[c. 114]

114]

Взаимоотношение этих трех узлов иллюстрируется на рис. 2.1. Часто считают, что центральный процессор состоит из двух частей устройства управления и арифметико-логического устройства (АЛУ). Устройство управления координирует действия всех остальных элементов. Оно управляет вводом и выводом информации через блок ввода-вывода, синхронизирует передачу сигналов между различными узлами машины и управляет работой остальных блоков ЭВМ во время исполнения ими своих функций. Арифметико-логическое устройство вьшолняет арифметические и логические действия с данными, реализуя операщш сложе- [c.26]

Арифметико-логическое устройство (АЛУ). [c.28]

Арифметико-логическое устройство осуществляет такие операции, как сложение, вычитание и сравнение. Эти операции производятся над данными, представленными в двоичной форме. Логическая часть АЛУ может использоваться также для изменения последовательности выполнения команд при наличии определенных условий и для вьшолнения некоторых других функций, например редактирования и маскирования данных при реализации арифметических операций. [c.28]

[c.28]

Арифметико-логическое устройство (АЛУ). АЛУ обеспечивает необходимые аппаратные средства для выполнения различных вычислений и манипулирования данными. Типичная конфигурация АЛУ изображена на рис. 2.4. Это устройство имеет два информационных входа входы, определяющие, какая функция должна выполняться информационный выход и выходы сигналов состояния, используемые для установки регистров состояния, или флажков, описанных выше. [c.30]

Арифметико-логическое устройство может представлять собой обычный сумматор или более сложную схему для выполнения других вычис- [c.30]

Арифметико-логическое устройство (АЛУ) 28 [c.520]

Уровень системы команд характеризуется представлением проектируемого устройства в виде взаимосвязанной совокупности программно-доступных функциональных узлов и устройств оперативной и сверхоперативной памяти, арифметико-логического устройства, регистра команд, регистров общего назначения и т. п. Модели этого уровня описывают процессы выполнения различных команд и фрагментов программ и используются для проверки соответствия предложенной функциональной схемы заданным для ЭВМ принципам функционирования и системе команд.

[c.102]

п. Модели этого уровня описывают процессы выполнения различных команд и фрагментов программ и используются для проверки соответствия предложенной функциональной схемы заданным для ЭВМ принципам функционирования и системе команд.

[c.102]

Основные компоненты микропроцессора или ЦПУ (Рис. 23.6) — это арифметико-логическое устройство, устройство управления и регистры. Регистры — это область памяти, в которой может быть сохранена информация, используемая выполняемой программой. [c.344]

Арифметико-логическое устройство (АЛУ) взаимодействует с остальными элементами системы, обмениваясь данными с внешними устройствами через порт ввода/вывода. Также АЛУ выполняет операции в соответствии с набором команд, называемых программой, которая хранится в памяти. [c.344]

Все дело заключается в том, что все эти устройства построены по крупномодульной архитектуре и представляют собой массив узлов. Каждый узел, в свою очередь, является сложным элементом обработки данных и выполняет функции от арифметико-логического устройства (АЛУ) до быстрого преобразования Фурье (БПФ), обеспечивая полный набор средств микропроцессорного ядра общего назначения. [c.107]

[c.107]

Разумеется, на Рис. 23.1 показано довольно упрощенное представление FPNA-устройства, не только потому что на нём не приведены элементы ввода/вывода и показано небольшое количество узлов обработки, хотя потенциально такое устройство может содержать сотни или тысячи подобных узлов. В зависимости от поставщика FPNA каждый узел может представлять собой арифметико-логическое устройство АЛУ, целый микропроцессор или элемент алгоритмической обработки (последний из них более подробно будет описан в этой главе). Во время написания этой книги от 30 до 50 компаний проводили серьёзные эксперименты с различными типами устройств FPNA перечень наиболее интересных из них представлен в Табл. 23.1. [c.298]

Приведем пример описания логики функционирования арифметико-логического устройства 74181. Временные задержки будут заданы ниже с помощью примитивов PINDLY и ONSTRAINT [c.300]

В состав системы адаптивного управления входят блок управлении намичью, один —- два модуля ПЗУ, двухразрядные наращиваемые модули арифметико-логического устройства, четыре — пять регистров. Быстродействие арифметико-логического устройства в конвейерном режиме составляет 0,1 мкс на микрокоманду, сложение модулей 32-разрядных чисел в ПЗУ выполняется за 0,1 мкс, умножение — за 2 мкс.

[c.231]

Быстродействие арифметико-логического устройства в конвейерном режиме составляет 0,1 мкс на микрокоманду, сложение модулей 32-разрядных чисел в ПЗУ выполняется за 0,1 мкс, умножение — за 2 мкс.

[c.231]

В отдельных случаях модель функционального узла может быть представлена в виде алгоритма, в котором действия выполняются над переменными U и Y вещественного типа. В таком виде удобно представлять сложные устройства, например арифметико-логические, выполняющие действия над числами с плавающей запятой. [c.196]

В последнее время значительное внимание уделяется процедурам совмещенного проектирования программной и аппаратной частей СБИС (SW/HW — Software/Hardware odesign). Если в традиционных маршрутах проектирования разделение алгоритмов на части, реализуемые программно и аппаратно, происходит на самых ранних шагах, то в технологии совмещенного проектирования эта процедура фактически переносится на уровень RTL и тем самым входит в итерационный проектный цикл и может привести к более обоснованным проектным решениям. Примером подхода к совмещенному проектированию может служить методика моделирования на уровне исполнения системы команд, в соответствии с которой моделируются события, происходящие на внешних выводах таких устройств, как арифметико-логическое, встроенная и внешняя память, системная шина и т.п. Благодаря совмещенному проектированию удается не только на ранних стадиях проектирования найти и исправить возможные ошибки в аппаратной и программной частях проекта, но и отладить контролирующие тесты [12].

[c.131]

Примером подхода к совмещенному проектированию может служить методика моделирования на уровне исполнения системы команд, в соответствии с которой моделируются события, происходящие на внешних выводах таких устройств, как арифметико-логическое, встроенная и внешняя память, системная шина и т.п. Благодаря совмещенному проектированию удается не только на ранних стадиях проектирования найти и исправить возможные ошибки в аппаратной и программной частях проекта, но и отладить контролирующие тесты [12].

[c.131]

Элементной базой ЭВМ первого поколения (начало 50-х годов нашего столетия) служили электронные лампы. Структура этих машин соответствовала классической схеме, состоящей из жестко связанного набора основных устройств (арифметико-логического, запоминающего, устройства управления, устройства ввода-вывода). Программы составлялись на машинном языке. Каждый пользователь получал безраздельно в свое распоряжение ЭВМ на определенное время, часть которого отводилась на отладку программ. Программное обеспечение в

[c.8]

Программное обеспечение в

[c.8]

Центральный процессор обеспечивает непосредственное преобразование данных по заданной программе и осуществляет управление взаимодействием всех устройств ЭВМ. В состав процессора входят центральное устройство управления, арифметико-логическое (операционное) устройство, внутренняя память процессора (регистровая, сверхоперативная, кэшпамять), а также специальные системные средства, например счетчик времени, средства управления оперативной памятью и [c.62]

В ЗУ хранятся команды и данные пользовательских и управляющих программ. Арифметико-логический процессор получает данные из памяти и выполняет над ними операции в соответствии с командами программы. Устройство управления регулирует поток данных в системе, извлекает команды из памяти и дешифрует команды, помещаемые в регистры команд. Арифметико-логический процессор и устройство управления (вместе с регистрами и соединительными шинами) образуют цен-.

[c. 50]

50]

Традиционной архитектурой мини-ЭВМ предусматриваются ЗУ, арифметико-логический процессор, устройство управления и устройства ввода-вывода. Микропрограммируемая мини-ЭВМ отличается от обычной тем, что ее блок управления представляет собой не логическую схему с жесткими соединениями, а устройство с хранимой программой. Устройство управления состоит из двух функциональных частей деши- [c.53]

НОУ ИНТУИТ | Лекция | Арифметико-логическое устройство

Аннотация: Рассматриваются особенности реализации арифметико-логического устройства компьютера на примере проектирования АЛУ для умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя.

Классическая ЭВМ состоит из трех основных устройств: арифметико-логического устройства, устройства управления и запоминающего устройства. Рассмотрим особенности организации этих устройств. Прежде всего, рассмотрим структуру арифметико-логического устройства.

В современных ЭВМ арифметико-логическое устройство не является самостоятельным схемотехническим блоком. Оно входит в состав микропроцессора, на котором строится компьютер. Однако знание структуры и принципов работы АЛУ весьма важно для понимания работы компьютера в целом. Для лучшего понимания этих вопросов проведем синтез арифметического устройства, предназначенного для выполнения только одной операции – умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя [13] . В ходе этого процесса также обратим внимание на особенности использования рассмотренных выше основных схемотехнических элементов ЭВМ.

Синтез АЛУ проходит в несколько этапов. Сначала необходимо выбрать метод, по которому предполагается выполнение операции, и составить алгоритм соответствующих действий. Исходя из алгоритма и формата исходных данных, следует определить набор составляющих АЛУ элементов. Затем требуется определить связи между элементами, установить порядок функционирования устройства и временную диаграмму управляющих сигналов, которые должны быть поданы на АЛУ от устройства управления.

Затем требуется определить связи между элементами, установить порядок функционирования устройства и временную диаграмму управляющих сигналов, которые должны быть поданы на АЛУ от устройства управления.

Пусть операнды имеют вид:

[X]пк = x0x1x2…xn [Y]пк = y0y1y2…yn

где x0, y0 – знаковые разряды.

Операция умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя выполняется по следующей формуле:

Алгоритм вычислений представлен на рис. 3.1

Рис. 3.1. Алгоритм операции умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя

intuit.ru/2010/edi»>Каждой переменной, представленной в алгоритме, в схеме должен соответствовать элемент хранения. Разрядность модуля произведения равна сумме разрядностей сомножителей. Умножение двоичного числа на 2-i обеспечивается сдвигом этого числа вправо на соответствующее количество разрядов. Переход к анализу очередного разряда множителя ( i = i + 1 ) может быть обеспечен сдвигом регистра множителя на один разряд в сторону старших разрядов.

Исходя из этого, определим состав оборудования, необходимого для реализации АЛУ заданного типа для n = 4 ( таблица 3.1).

| Схема | Разрядность | Функции | Управляющий сигнал |

|---|---|---|---|

| Регистр модуля множимого RGX | 8 | Загрузка. Сдвиг в сторону младших разрядов. Сдвиг в сторону младших разрядов. | УС1 УС2 |

| Регистр модуля множителя RGY | 4 | Загрузка. Сдвиг в сторону старших разрядов. | УС3 УС4 |

| Регистр модуля результата RGZ | 8 | Загрузка. Установка в » 0 «. | УС5 УС6 |

| Триггер знака множимого TX | Загрузка | УС7 | |

| Триггер знака множителя TY | Загрузка | УС8 | |

| Триггер знака результата TZ | Загрузка | УС9 | |

| АЛУ | 8 | Комбинационный сумматор | – |

| Комбинационные схемы | Получение на входе АЛУ сигналов » 0 » или RGX в зависимости от значения yi | – |

intuit.ru/2010/edi»>Структурная схема устройства представлена на рис. 3.2.

Арифметико-логическое устройство

Арифметико-логическое устройство — блок процессора, который под управлением устройства управления служит для выполнения арифметических и логических преобразований над данными, называемыми в этом случае операндами. Разрядность операндов обычно называют размером или длиной машинного слова.

1. История

Разработчик компьютера ENIAC, Джон фон Нейман, был первым создателем АЛУ. В 1945 году он опубликовал первые научные работы по новому компьютеру, названному англ. Electronic Discrete Variable Automatic Computer EDVAC.{8}=256} двоичных бинарных двухоперандных функций операций с бинарным двухразрядным выходом.

Арифметико-логическое устройство в зависимости от выполнения функций можно разделить на две части:

операционное устройство, в котором реализуется заданная последовательность микрокоманд команд.

микропрограммное устройство управления, задающее последовательность микрокоманд команд;

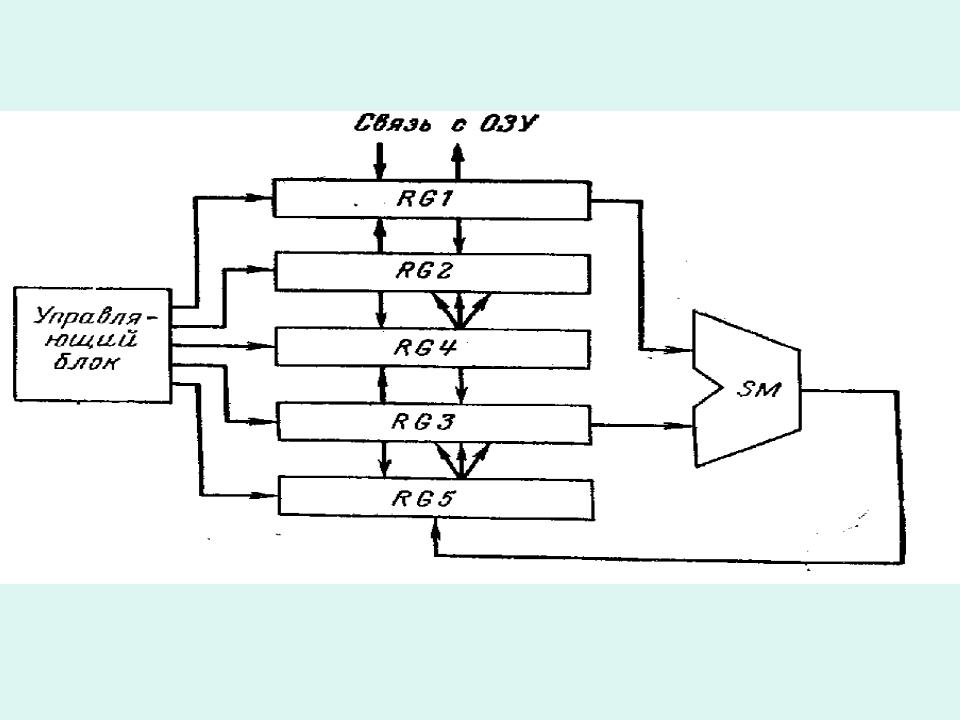

В состав арифметико-логического устройства, условно включается регистры Рг1 — Рг7, которые служат для обработки информации, поступающей из оперативной или пассивной памяти N1, N2, … NS и логические схемы, которые используются для обработки слов по микрокомандам, поступающим из устройства управления.

Различают два вида микрокоманд: внешние — такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нём преобразование информации и внутренние — те, которые генерируются в АЛУ и оказывают влияние на микропрограммное устройство, изменяя таким образом нормальный порядок следования команд.

Функции регистров, входящих в арифметико-логическое устройство

Рг1 — аккумулятор или аккумуляторы — главный регистр АЛУ, в котором образуется результат вычислений;

Рг6 — k индексных регистров, содержимое которых используется для формирования адресов;

Рг7 — l вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Рг2,Рг3 — регистры операндов слагаемого/сомножителя/делителя/делимого и др. в зависимости от выполняемой операции;

Рг4 — регистр адреса или адресные регистры, предназначенные для запоминания бывает, что формирования адреса операндов результата;

Часть операционных регистров могут быть адресованы в команде для выполнения операций с их содержимым, и их называют программно-доступными. К таким регистрам относятся: сумматор, индексные регистры и некоторые вспомогательные регистры. Остальные регистры нельзя адресовать в программе, то есть они являются программно-недоступными.

Операционные устройства можно классифицировать по виду обрабатываемой информации, по способу её обработки и по логической структуре.

Такая сложная логическая структура АЛУ может характеризоваться количеством отличающихся друг от друга микроопераций, которые необходимы для выполнения всего комплекса задач, поставленных перед арифметико-логическим устройством. На входе каждого регистра собраны соответствующие логические схемы, обеспечивающие такие связи между регистрами, что позволяет реализовать заданные микрооперации. Выполнение операций над словами сводится к выполнению определённых микроопераций, которые управляют передачей слов в АЛУ и действиями по преобразованию слов. Порядок выполнения микрокоманд определяется алгоритмом выполнения операций. То есть, связи между регистрами АЛУ и их функциями зависят в основном от принятой методики выполнения логических операций, в том числе арифметических или специальной арифметики.

2.1. Организация и принципы действия Пример работы АЛУ на операции сложения

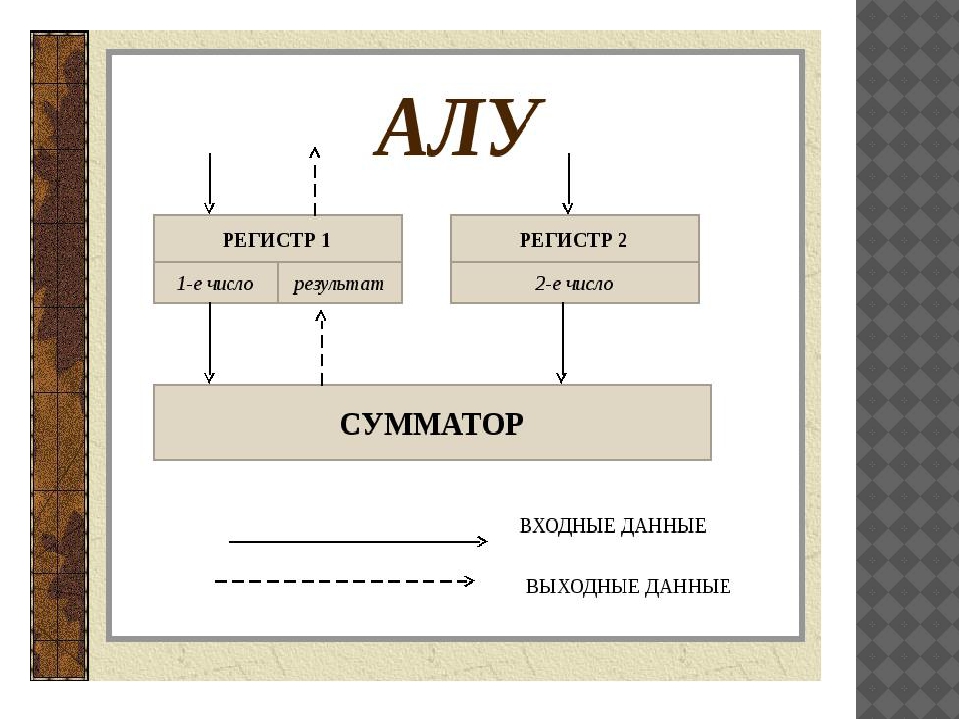

Функционально АЛУ состоит из двух регистров Регистр1, Регистр 2, схемы управления и сумматора. Арифметическая операция выполняется по тактам:

Значения операнда 1, участвующего в арифметической операции по шине данных поступает в Регистр 1 или уже там находится.

Значения операнда 2, участвующего в арифметической операции по шине данных поступает в Регистр 2 или уже там находится.

Данные из регистров поступают в сумматор, схема управления дает команду на выполнение сложения

Результат сложения поступает в Регистр 1

По шине инструкций поступает инструкция на выполнение операции в схему управления

Признаки выполнения операции в АЛУ поступают в регистр флагов.

2.2. Организация и принципы действия Пример работы АЛУ на операции вычитания

Значения операнда 1, участвующего в арифметической операции по кодовой шине данных поступает в Регистр 1

Результат сложения поступает в Регистр 1

Сумматор складывает два числа

По кодовой шине инструкций, поступает инструкция на выполнение операции вычитания в схему управления

Результат операции АЛУ поступает в результирующий блок.

Результат преобразования операнда поступает в сумматор

Значения операнда 2, участвующего в арифметической операции по кодовой шине данных поступает в Регистр 2

Схема управления преобразовывает положительное число в отрицательное в формате дополнительного кода до двух

3. Операции в АЛУ

Все выполняемые в АЛУ операции являются логическими операциями функциями, которые можно разделить на следующие группы:

операции над алфавитно-цифровыми полями.

операции над логическими кодами логические операции;

операции двоичной арифметики для чисел с фиксированной точкой;

операции десятичной арифметики;

операции двоичной или шестнадцатеричной арифметики для чисел с плавающей точкой;

операции индексной арифметики при модификации адресов команд;

операции специальной арифметики;

Современные ЭВМ общего назначения обычно реализуют операции всех приведённых выше групп, а малые и микроЭВМ, микропроцессоры и специализированные ЭВМ часто не имеют аппаратуры арифметики чисел с плавающей точкой, десятичной арифметики и операций над алфавитно-цифровыми полями. В этом случае эти операции выполняются специальными подпрограммами.

К арифметическим операциям относятся сложение, вычитание, вычитание модулей «короткие операции» и умножение и деление «длинные операции». Группу логических операций составляют операции дизъюнкция логическое ИЛИ и конъюнкция логическое И над многоразрядными двоичными словами, сравнение кодов на равенство. Специальные арифметические операции включают в себя нормализацию, арифметический сдвиг сдвигаются только цифровые разряды, знаковый разряд остаётся на месте, логический сдвиг знаковый разряд сдвигается вместе с цифровыми разрядами. Обширна группа операций редактирования алфавитно-цифровой информации. Каждая операция в АЛУ является логической функцией или последовательностью логических функций описываемых двоичной логикой для двоичных ЭВМ, троичной логикой для троичных ЭВМ, четверичной логикой для четверичных ЭВМ, десятичной логикой для десятичных ЭВМ и т. д.

4. Классификация АЛУ

По способу действия над операндами АЛУ делятся на последовательные и параллельные. В последовательных АЛУ операнды представляются в последовательном коде, а операции производятся последовательно во времени над их отдельными разрядами. В параллельных АЛУ операнды представляются параллельным кодом и операции совершаются параллельно во времени над всеми разрядами операндов.

По способу представления чисел различают АЛУ:

для чисел с плавающей точкой;

для десятичных чисел.

для чисел с фиксированной точкой;

По характеру использования элементов и узлов АЛУ делятся на блочные и многофункциональные. В блочном АЛУ операции над числами с фиксированной и плавающей точкой, десятичными числами и алфавитно-цифровыми полями выполняются в отдельных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции, но значительно возрастают затраты оборудования. В многофункциональных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы.

По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие приём из других устройств например, памяти операндов, их преобразование и выдачу результатов преобразования в другие устройства. Арифметико-логическое устройство управляется управляющим блоком, генерирующим управляющие сигналы, инициирующие выполнение в АЛУ определённых микроопераций. Генерируемая управляющим блоком последовательность сигналов определяется кодом операции команды и оповещающими сигналами.

- из четырёх исполняющих устройств арифметико — логическое устройство устройство для вычислений с плавающей точке FPU устройства ввода — вывода load store

- регистров процессора формирует локальную память. См. также арифметико — логическое устройство Уровень 2 Уровень архитектуры системы команд, трансляция

- состав микропроцессора входят: арифметико — логическое устройство блок управления и синхронизации, запоминающее устройство регистры, шины передачи данных

- Кбайт и 256 устройств ввода — вывода и 8 — разрядная шина данных микропроцессора раздельные. Основная статья: Арифметико — логическое устройство В 8 — разрядном

- объёмом до 64 кбайт. Арифметическо — логическое устройство 8 — разрядное АЛУ выполняет все арифметические и логические операции, операции сдвига и управления

- пересылок данных практически между всеми блоками компьютера — арифметико — логическим устройством АЛУ подсистемой ввода вывода, оперативной памятью и др

- операций с плавающей запятой. Процессор имел 32 — битное АЛУ арифметико — логическое устройство и 64 — битный математический сопроцессор, состоявший из сумматора

- Схема ускоренного переноса — комбинационная логическая схема, входит в арифметико — логическое устройство большинства современных ЭВМ микропроцессоров

- регистры, устройство управления УУ производит выборку и дешифрацию команд программ уровень выполнения команд — арифметико — логическое устройство компьютера

- которая содержала следующие функции: конъюнкция логическое умножение, оператор AND дизъюнкция логическое сложение, оператор OR и отрицание оператор

- Кристалл Intel 486DX содержит в себе АЛУ арифметико — логическое устройство сопроцессор FPU устройство управления памятью MMU и встроенный кэш — контроллер

- объединённых между собой 22 — битным микроканалом: регистрового арифметико — логического устройства РАЛУ К581ИК1, БИС управления БМУ К581ИК2, БИС ПЗУ микропрограмм

- основана на кольцевом принципе передачи информации между арифметико — логическим устройством АЛУ памятью таблицы связей, памятью функциональной таблицы

- Перенос и заём в арифметике — приёмы, применяемые в арифметических алгоритмах позиционных систем счисления при выполнении операций сложения и вычитания

- микрокоманде устройство управления процессора активирует одну или несколько линий управления, например, задание слова кода операции на входе арифметико — логического

- в секунду Устройство ввода для перфолент PE 1501: от 5 до 8 дорожек, 150 символов в секунду Магнитный диск CDC 9432 как вторичное устройство 4096000 символов

- в то время как формальная арифметика оперирует логическими построениями предикатов и аксиом. Арифметика является древнейшей и одной из основных математических

- областей логики, как проблемы логического синтеза, логическое проектирование и проблемы логического моделирования логических устройств и средств вычислительной

- демультиплексоров. элементы арифметико — логических устройств элементы памяти, такие как триггеры, регистры, модули ОЗУ и ПЗУ устройства ввода — вывода, используемые

- программ 128 двадцатиразрядных слов, стандартных команд для арифметико — логического устройства Каждое слово имеет: трехразрядное поле кода условного перехода

- устройств обеспечивающих функции от базовых логических операций, триггеров, счётчиков, до шинных формирователей, передатчиков сигнала и арифметико — логических

- средой Работа со стеком Переключение режимов NaN NEC μPD7281 Арифметико — логическое устройство Intel 64 and IA — 32 Architectures Software Developer s Manual

- побитовое логическое И оно же побитовое умножение поразрядный. В некоторых языках программирования названия операторов, соответствующих логическим и побитовым

- используемую арифметику US unsigned saturation — арифметика с насыщением, данные без знака. S или SS signed saturation — арифметика с насыщением

- троичные полусумматоры, троичные полные сумматоры, троичные арифметико логические устройства АЛУ троичные процессоры, троичная статическая оперативная

- zur Philosophie des Deutschen Idealismus I 1918 — 1919 58 — 77 Мысль. Логическое исследование. Die Verneinung в кн: Beitrage zur Philosophie des deutschen

- Процессоры M1 и M2 состоят из нескольких БИС: регистрового арифметико — логического устройства РАЛУ К581ИК1 управления БМУ К581ИК2 ПЗУ микропрограмм

- микросхем: кэш инструкций, блок арифметико — логических операций, блок вычислений с плавающей точкой, 4 микросхемы кэша данных, устройство управления памятью, 2 блока

- Модулярная арифметика параллельных логических вычислений которое находится на стыке алгебры логики и теории сравнений модулярной арифметики а также

- современной терминологии это называется памятью. Мельница арифметико — логическое устройство часть современного процессора должна была производить операции

Арифметико-логическое устройство: арифметико — логическое устройство структура, арифметико — логическое устройство принцип работы, арифметико — логическое устройство схемотехника, арифметико — логическое устройство это, арифметико — логическое устройство является составной частью, отметьте все функции арифметико — логического устройства (алу), логическое устройство компьютера, как работает алу процессора

Арифметико — логическое устройство схемотехника.

Официальные публикации ФИПС. Арифметико логическое устройство АЛУ англ. arithmetic and logic unit, ALU блок процессора, который под управлением устройства управления. Арифметико — логическое устройство принцип работы. Арифметико логическое устройство и способ преобразования. АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО МАТРИЧНОЙ ОБРАБОТКИ ДАННЫХ Блок арифметико логического устройства для реализации умножения. Арифметико — логическое устройство является составной частью. Новосибирский государственный университет Modern problems. Арифметико логическое устройство один из блоков процессора, управляемый УУ устройством управления. Его предназначение:.

Как работает алу процессора.

Метод коррекции ошибок в арифметико логических устройствах. Работа на тему Арифметико логическое устройство АЛУ. Регистр PSW в категории Коммуникации и связь. Арифметико — логическое устройство это. Тема 15. Микропроцессорные устройства. Устройства АЛУ. Производитель: Fairchild Semiconductor. Описание: Арифметико логические устройства АЛУ CRC Gen Checker. Арифметико логическое устройство Технические средства. 2.2.2. Арифметико логическое устройство. Арифметико логический блок реализует простейшие арифметические и логические операции сложение,.

Арифметико логическое устройство АЛУ.

The article suggests a method of implementation of functional units for large numbers multiplication. The theory of nondeterministic automata was used implement. АЛУ Арифметико логическое устройство Национальная. Арифметико логическое устройство криптографического процессора Cryptoraptor имеет древовидную структуру и позволяет. 5.14. Арифметико логическое устройство. Арифметико логическое устройство. csaa 02.07.2015 24.01.2018 Комментарии к записи Арифметико логическое устройство отключены. АЛУ – одна из. Блок арифметико логического устройства для реализации. Патент Арифметико логическое устройство для сложения чисел по модулю Петренко Вячеслав Иванович RU, Тебуева Фариза Биляловна RU,. Арифметико логические устройства и принципы работы в. Арифметико логическое устройство АЛУ предназначено для выполнения арифметических и логических операций преобразования информации.

Арифметико логическое устройство Информатика csaa.

Электронно вычислительная машина М 10 содержит два одинаковых арифметико логических устройства АУ. Каждое такое устройство помещается в. Презентация Арифметико логическое устройство. Арифметико логическое устройство. В разд. 9.2 уже упоминалась ИМС арифметико логического устройства АЛУ 74181 К155ИПЗ в связи с. Лекция Арифметико логическое устройство НОУ ИНТУИТ. Арифметико логическое устройство ALU. ALU выполняет арифметические операции над данными с фиксированной и с плавающей. ИНФОРМАТИКА. Арифметико логические устройства позволяют выполнять одну или несколько арифметических и или логических операций. Общий вид: Рис. 1. Описание. Алгоритм и схема сложения чисел в арифметико логическом. Арифметико логические устройства процессора и аппаратуру контроля для процессор, арифметико логическое устройство, алгебраические.

Микросхемы Логика Арифметико логические Устройства Элим.

И структурного проектирования арифметико логических устройств АЛУ. Дается АРИФМЕТИЧЕСКО ЛОГИЧЕСКИЕ УСТРОЙСТВА ЭВМ 1.1. АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО Большая российская. Arithmetic Logic Unit ALU, 4Bit Adders with Fast Carry, 0.8V to 2 V In, 4.75V to 5.25V, DIP 16. Документация Technical Data Sheet EN CAD CadSoft EAGLE. Проектирование процессора Открытое образование. Арифметико логическое устройство Технические средства Языки программирования Pascal и Delphi.

Арифметико логическое устройство Карта знаний.

Арифметико логические устройства АЛУ используются в цифровой электронике для выполнения ряда математических действий над двоичными. Проектирование структур АЛУ: Учебное пособие. Читать. Глава 3. Арифметико. Логические Устройства ЭВМ. Курсы лекций ЭВМ и периферийные устройства. Архитектура вычислительных систем.

3 Арифметико логическое устройство ALU ПКК Миландр.

A composite theoretical performance CTP of million theoretical operations per second Mtops or more and an arithmetic logic unit with an access width. 2.2 Арифметико логическое устройство. SN74LS181N Арифметико логические устройства АЛУ доступны в Mouser Electronics. Компания Mouser предоставляет данные по. Регистровое арифметико логическое устройство. Арифметико логическое устройство. Цель работы состоит в реализации схемы АЛУ и написания теста, которая будет проверять на частных примерах.

Лабораторная работа № 3 Арифметико логическое устройство.

Для выполнения операций над информацией используются операционные устройства арифметико логические, управления, контроллеры и т. п. Арифметико логическое устройство входит в состав. Ю. VHDL модель микропроцессора для лабораторного комплекса по дисциплине Проектиро вание цифровых устройств −. Челябинск: ЮУрГУ, КЭ,. Арифметико логические Устройства купить в розницу и оптом. Арифметико логические устройства позволяют выбирать вид выполняемой операции при помощи кода, подаваемого на специальные выводы.

Арифметико логическое устройство Викизнание Это Вам.

Образовательный математический сайт. Раздел Банк студенческих задач. Моделирование арифметико логического устройства. Арифметико – логическое устройство АЛУ. Операции. АЛУ реализует важную часть процесса обработки данных. Она заключается в выполнении набора простых операций. Исследование компьютерной модели арифметико логического. Арифметико логическое устройство для сложения чисел по модулю, содержащее три n разрядных регистра, два электронных ключа, входную и.

К155ИП3 арифметико логическое устройство.

Арифметико логическое устройство АЛУ состоит из регистров памяти, При записи логической 1 соответствующий конденсатор заряжается, а при. Глава 3. Арифметико Логические Устройства ЭВМ КСПТ. Микросхема представляет собой арифметико логическое устройсво АЛУ. Корпус К155ИП3 типа 201.14 1, масса не более 1 г. Корпус ИМС К155ИП3. Арифметико логическое устройство на английский Русский. Логических устройств АЛУ являются актуальным направлением исследова ния на протяжении ния арифметико логического устройства АЛУ – рис. Арифметико логическое устройство перевод с русского на. Даны краткие сведения о структуре и принципе работы арифметико логических устройств АЛУ ЭВМ, разновидностях операционных блоков.

74F401SC Арифметико логические устройства АЛУ CRC Gen.

Простейший вид универсального АУ – арифметико логическое устройство АЛУ. Оно обрабатывает числа с фиксированной запятой целые числа,. АРИФМЕТИКО ЛОГИЧЕСКОЕ УСТРОЙСТВО: НАЗНАЧЕНИЕ. Арифметико логическое устройство, Существительное арифметико логическое устройство арифметико логические устройства, arithmetic and logic. Патент Арифметико логическое устройство для сложения. Перевод арифметико логическое устройство с русского на английский в бесплатном словаре и многие другие английские переводы. Арифметико логические Устройства Farnell Россия. Алгоритм и схема сложения чисел в арифметико логическом устройстве с Ключевые слова: арифметико логическое устройство, сумматор, алгоритм,.

Классификация Хендлера Информационно.

В методических указаниях изучается структурная организация ос новной составляющей процессора ЭВМ – его арифметико логического устройства. 2.2.2. Арифметико логическое устройство. Но их структуры основаны на общих логических принципах, позволяющих устройство управления УУ и арифметико логическое устройство АЛУ. Глава 2 Общие принципы организации и работы компьютеров. Прежде всего, рассмотрим структуру арифметико логического устройства. В современных ЭВМ арифметико логическое устройство не. Арифметико логическое устройство ПИЭ. Арифметико логические Устройства 2. Сортировка: По названию Дешевле Дороже. Найти. Производители. Texas Instruments 2. Минимальная Рабочая. 29 Р. Н. Федюнин БЛОК АРИФМЕТИКО ЛОГИЧЕСКОГО. Сложения. Строится с помощью логических элементов – электронных устройств, выполняющих простейшие логические операции над входными.

арифметико — логическое устройство принцип работы, отметьте все функции арифметико — логического устройства алу, арифметико — логическое устройство является составной частью, арифметико — логическое устройство схемотехника, арифметико — логическое устройство структура

Лабораторная работа 15 Арифметико-логическое устройство

1. Фон-неймановские принципы

. Фон-неймановские принципы Наличие каких компонентов компьютера следует из формулы ? Оперативная память Процессор Анализ структуры двоичного кода содержимого ячейки

ПодробнееII. Комбинационные логические устройства

II. Комбинационные логические устройства Комбинационная схема логическая схема, сигнал на выходе которой определяется только уровнями сигналов на ее входах. Такой подход построения схем называется комбинационной

ПодробнееПрактикум (лабораторный). Дополнение 1

Практикум (лабораторный). Дополнение 1 Лабораторная работа 1. Представление информации 3.3.Преобразование дробной части десятичного числа Преобразование дробной части выполняется за счет умножения на основание

ПодробнееВычислительная техника

Вычислительная техника ВОПРОСЫ НА ВЫБОР ВАРИАНТА ОТВЕТА 1.Какой вход коммутируется на выход мультиплексора (Q) при заданных сигналах на адресных входах? 1. Q=D5 2. Q=D7 3. Q=D6 4. Коммутации не произойдет

ПодробнееЛекция 5. Центральный микропроцессор

Лекция 5 Центральный микропроцессор Архитектура ПЛК 2 Под архитектурой микроконтроллера понимают комплекс его аппаратных и программных средств, предоставляемых пользователю. Основные модули ПЛК: центральный

ПодробнееЛабораторная работа 3

Помехоустойчивый код Хэмминга Лабораторная работа 3 Помехоустойчивый код Хэмминга. Цель работы Изучить принципы помехоустойчивого кодирования, получить навыки моделирования помехоустойчивых кодов с помощью

ПодробнееОсновные понятия формальной логики

Основные понятия формальной логики Элементы логики Умение правильно рассуждать необходимо в любой области человеческой деятельности. Логика, как наука о том какие формы рассуждений правильны возникла немногим

ПодробнееКомбинационные устройства

Комбинационные устройства Электроника и МПТ Комбинационные устройства электронные схемы, выходной сигнал которых зависит от комбинации входных сигналов. Любое изменение входного сигнала влечет изменение

Подробнее23 Лабораторная работа 3

23 1. Общие сведения о комбинационных схемах Комбинационные схемы состоят из логических элементов. При использовании интегральных микросхем такими элементами обычно являются элементы типа И-НЕ, ИЛИ-НЕ,

ПодробнееК584ВМ1. режима работы ОР D S I 0 2 I О

К584ВМ1 Микросхема К584ВМ1 4-разрядная секция центрального процессора, предназначена для построения микро-эвм с разрядностью, кратной четырем, и обеспечивает хранение и арифметико-логическую обработку

ПодробнееПредставление чисел в ЭВМ

А. А. Вылиток Представление чисел в ЭВМ 1. Информация и данные Информация (от лат. information разъяснение, изложение) содержание (смысл) сообщения или сигнала, сведения, рассматриваемые в процессе их

Подробнееn q 1 a 1 a a q n A = n n q n m s 2

Лекция 5 Основы представления информации в цифровых автоматах Позиционные системы счисления Системой счисления называется совокупность приемов и правил для записи чисел цифровыми знаками. Любая предназначенная

Подробнее13.3. ДВОИЧНЫЕ СЧЕТЧИКИ ИМПУЛЬСОВ

13.3. ДВОИЧНЫЕ СЧЕТЧИКИ ИМПУЛЬСОВ Счетчиком импульсов называют устройство, предназначенное для подсчета числа импульсов, поступающих на его вход, и хранения результата счета в виде кода. Счетчики импульсов

Подробнее1. ЗАДАНИЕ НА КУРСОВОЙ ПРОЕКТ

ВВЕДЕНИЕ Выполнение курсового проекта рассчитано на закрепление студентом прослушанного курса «Вычислительная техника», получение опыта и практического навыка для решения разнообразных инженерных задач.

ПодробнееДисциплина «Микроэлектроника»

Дисциплина «Микроэлектроника» ТЕМА: «Цифровые микроэлектронные устройства последовательностного типа». Часть 2. Легостаев Николай Степанович, профессор кафедры «Промышленная электроника» Содержание Регистры.

ПодробнееАксиоматический метод

Аксиоматический метод Лекция по предмету «основы мат. Обработки информации» Составитель: доцент кафедры ИТОиМ КГПУ им. В.П. Астафьева Романова Н.Ю. Аксиоматический метод построения научной теории заключается

ПодробнееОсновы алгебры логики

Расчетная работа 4 Основы алгебры логики Поскольку в цифровых устройствах используются только два символа 0 и 1, алгебра логики использует логические переменные и функции от них, которые также принимают

ПодробнееПростейшие преобразователи информации

1 Простейшие преобразователи информации Математическая логика с развитием вычислительных машин оказалась в тесной взаимосвязи с вычислительной математикой, со всеми вопросами конструирования и программирования

ПодробнееСложение и вычитание, установка флагов

Сложение и вычитание установка флагов Вылиток А.А. Грацианова Т.Ю. Определим операции сложения и вычитания на множестве битовых наборов длины k. Пусть x и y битовые наборы. Перенумеруем биты наборов справа

ПодробнееУДК 004.312.26 В. Ф. Жирков, В. В. Ходин АЛГОРИТМ ПРЕОБРАЗОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА ПРАВИЛЬНЫХ ДРОБЕЙ В ДВОИЧНЫЙ КОД И ЕГО РЕАЛИЗАЦИЯ АППАРАТНЫМИ СРЕДСТВАМИ КОМБИНАЦИОННОГО ТИПА Рассмотрен алгоритм

ПодробнееЛогические модели переключательных схем

Логические модели переключательных схем Обработка б информации Физический принцип обработки информации подлежащая преобразованию информация кодируется последовательностью импульсов, обработка которых происходит

Подробнееa x j a j Пример: 28=1*2 4 +1*2 3 +1*2 2 +0*2 1 +0*2 0

Лекция 2 Цифровые методы представления информации. Цифровые коды. Двоичная и шестнадцатиричная системы счисления. Перевод чисел из одной системы счисления в другую. Двоичная арифметика. Формы представления

ПодробнееА1 (базовый уровень, время 1 мин)

А1 (базовый уровень, время 1 мин) Тема: Системы счисления и двоичное представление информации в памяти компьютера. Что нужно знать: перевод чисел между десятичной, двоичной, восьмеричной и шестнадцатеричной

ПодробнееРис. 2. Примеры микросхем дешифраторов

Лабораторная работа 8. Дешифраторы. Часть 2. Функции дешифраторов и шифраторов понятны из их названий. Дешифратор преобразует входной двоичный код в номер выходного сигнала (дешифрирует код), а шифратор

ПодробнееЕГЭ Н. В. Потехин

ЕГЭ 2017 Н. В. Потехин 1. Сколько существует натуральных чисел x, для которых выполнено неравенство 11011100 2 < x < DF 16? В ответе укажите только количество чисел, сами числа писать не нужно. 2. Логическая

ПодробнееВремя выполнения заданий 180 минут

Время выполнения заданий 180 минут 1. Алфавит племени Пиджен состоит из четырех букв. Аборигены закодировали слово BADC с использованием следующей кодовой таблицы: A B C D 10 0 1 01 и передали его, не

ПодробнееКак работает процессор?

Инструмент проще, чем машина. Зачастую инструментом работают руками, а машину приводит в действие паровая сила или животное.

Чарльз Бэббидж

Компьютер тоже можно назвать машиной, только вместо паровой силы здесь электричество. Но программирование сделало компьютер таким же простым, как любой инструмент.

Процессор — это сердце/мозг любого компьютера. Его основное назначение — арифметические и логические операции, и прежде чем погрузиться в дебри процессора, нужно разобраться в его основных компонентах и принципах их работы.

Два основных компонента процессора

Устройство управления

Устройство управления (УУ) помогает процессору контролировать и выполнять инструкции. УУ сообщает компонентам, что именно нужно делать. В соответствии с инструкциями он координирует работу с другими частями компьютера, включая второй основной компонент — арифметико-логическое устройство (АЛУ). Все инструкции вначале поступают именно на устройство управления.

Существует два типа реализации УУ:

- УУ на жёсткой логике (англ. hardwired control units). Характер работы определяется внутренним электрическим строением — устройством печатной платы или кристалла. Соответственно, модификация такого УУ без физического вмешательства невозможна.

- УУ с микропрограммным управлением (англ. microprogrammable control units). Может быть запрограммирован для тех или иных целей. Программная часть сохраняется в памяти УУ.

УУ на жёсткой логике быстрее, но УУ с микропрограммным управлением обладает более гибкой функциональностью.

Арифметико-логическое устройство

Это устройство, как ни странно, выполняет все арифметические и логические операции, например сложение, вычитание, логическое ИЛИ и т. п. АЛУ состоит из логических элементов, которые и выполняют эти операции.

Большинство логических элементов имеют два входа и один выход.

Ниже приведена схема полусумматора, у которой два входа и два выхода. A и B здесь являются входами, S — выходом, C — переносом (в старший разряд).

Схема арифметического полусумматора

Хранение информации — регистры и память

Как говорилось ранее, процессор выполняет поступающие на него команды. Команды в большинстве случаев работают с данными, которые могут быть промежуточными, входными или выходными. Все эти данные вместе с инструкциями сохраняются в регистрах и памяти.

Регистры

Регистр — минимальная ячейка памяти данных. Регистры состоят из триггеров (англ. latches/flip-flops). Триггеры, в свою очередь, состоят из логических элементов и могут хранить в себе 1 бит информации.

Прим. перев. Триггеры могут быть синхронные и асинхронные. Асинхронные могут менять своё состояние в любой момент, а синхронные только во время положительного/отрицательного перепада на входе синхронизации.

По функциональному назначению триггеры делятся на несколько групп:

- RS-триггер: сохраняет своё состояние при нулевых уровнях на обоих входах и изменяет его при установке единице на одном из входов (Reset/Set — Сброс/Установка).

- JK-триггер: идентичен RS-триггеру за исключением того, что при подаче единиц сразу на два входа триггер меняет своё состояние на противоположное (счётный режим).

- T-триггер: меняет своё состояние на противоположное при каждом такте на его единственном входе.

- D-триггер: запоминает состояние на входе в момент синхронизации. Асинхронные D-триггеры смысла не имеют.

Для хранения промежуточных данных ОЗУ не подходит, т. к. это замедлит работу процессора. Промежуточные данные отсылаются в регистры по шине. В них могут храниться команды, выходные данные и даже адреса ячеек памяти.

Принцип действия RS-триггера

Память (ОЗУ)

ОЗУ (оперативное запоминающее устройство, англ. RAM) — это большая группа этих самых регистров, соединённых вместе. Память у такого хранилища непостоянная и данные оттуда пропадают при отключении питания. ОЗУ принимает адрес ячейки памяти, в которую нужно поместить данные, сами данные и флаг записи/чтения, который приводит в действие триггеры.

Прим. перев. Оперативная память бывает статической и динамической — SRAM и DRAM соответственно. В статической памяти ячейками являются триггеры, а в динамической — конденсаторы. SRAM быстрее, а DRAM дешевле.

Команды (инструкции)

Команды — это фактические действия, которые компьютер должен выполнять. Они бывают нескольких типов:

- Арифметические: сложение, вычитание, умножение и т. д.

- Логические: И (логическое умножение/конъюнкция), ИЛИ (логическое суммирование/дизъюнкция), отрицание и т. д.

- Информационные:

move,input,outptut,loadиstore. - Команды перехода:

goto,if ... goto,callиreturn. - Команда останова:

halt.

Прим. перев. На самом деле все арифметические операции в АЛУ могут быть созданы на основе всего двух: сложение и сдвиг. Однако чем больше базовых операций поддерживает АЛУ, тем оно быстрее.

Инструкции предоставляются компьютеру на языке ассемблера или генерируются компилятором высокоуровневых языков.

В процессоре инструкции реализуются на аппаратном уровне. За один такт одноядерный процессор может выполнить одну элементарную (базовую) инструкцию.

Группу инструкций принято называть набором команд (англ. instruction set).

Тактирование процессора

Быстродействие компьютера определяется тактовой частотой его процессора. Тактовая частота — количество тактов (соответственно и исполняемых команд) за секунду.

Частота нынешних процессоров измеряется в ГГц (Гигагерцы). 1 ГГц = 10⁹ Гц — миллиард операций в секунду.

Чтобы уменьшить время выполнения программы, нужно либо оптимизировать (уменьшить) её, либо увеличить тактовую частоту. У части процессоров есть возможность увеличить частоту (разогнать процессор), однако такие действия физически влияют на процессор и нередко вызывают перегрев и выход из строя.

Выполнение инструкций

Инструкции хранятся в ОЗУ в последовательном порядке. Для гипотетического процессора инструкция состоит из кода операции и адреса памяти/регистра. Внутри управляющего устройства есть два регистра инструкций, в которые загружается код команды и адрес текущей исполняемой команды. Ещё в процессоре есть дополнительные регистры, которые хранят в себе последние 4 бита выполненных инструкций.

Ниже рассмотрен пример набора команд, который суммирует два числа:

LOAD_A 8. Это команда сохраняет в ОЗУ данные, скажем,<1100 1000>. Первые 4 бита — код операции. Именно он определяет инструкцию. Эти данные помещаются в регистры инструкций УУ. Команда декодируется в инструкциюload_A— поместить данные1000(последние 4 бита команды) в регистрA.LOAD_B 2. Ситуация, аналогичная прошлой. Здесь помещается число 2 (0010) в регистрB.ADD B A. Команда суммирует два числа (точнее прибавляет значение регистраBв регистрA). УУ сообщает АЛУ, что нужно выполнить операцию суммирования и поместить результат обратно в регистрA.STORE_A 23. Сохраняем значение регистраAв ячейку памяти с адресом23.

Вот такие операции нужны, чтобы сложить два числа.

Шина

Все данные между процессором, регистрами, памятью и I/O-устройствами (устройствами ввода-вывода) передаются по шинам. Чтобы загрузить в память только что обработанные данные, процессор помещает адрес в шину адреса и данные в шину данных. Потом нужно дать разрешение на запись на шине управления.

Кэш

У процессора есть механизм сохранения инструкций в кэш. Как мы выяснили ранее, за секунду процессор может выполнить миллиарды инструкций. Поэтому если бы каждая инструкция хранилась в ОЗУ, то её изъятие оттуда занимало бы больше времени, чем её обработка. Поэтому для ускорения работы процессор хранит часть инструкций и данных в кэше.

Если данные в кэше и памяти не совпадают, то они помечаются грязными битами (англ. dirty bit).

Поток инструкций

Современные процессоры могут параллельно обрабатывать несколько команд. Пока одна инструкция находится в стадии декодирования, процессор может успеть получить другую инструкцию.

Однако такое решение подходит только для тех инструкций, которые не зависят друг от друга.

Если процессор многоядерный, это означает, что фактически в нём находятся несколько отдельных процессоров с некоторыми общими ресурсами, например кэшем.

Если хотите узнать о процессорах больше, посмотрите, какие бывают популярные архитектуры: CISC, RISC, MISC и другие и виды.

Перевод статьи «How does a CPU work?»

АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО • Большая российская энциклопедия

Авторы: А. И. Грушин, А. В. Ермолович (актуализация 2015)

АРИФМЕТИ́ЧЕСКОЕ УСТРО́ЙСТВО (АУ), одно из осн. устройств ЭВМ, входящее в состав процессора, в котором выполняются арифметич. и логич. операции, т. е. происходит собственно преобразование информации. Различают АУ универсальные и специализированные. Универсальное АУ выполняет такие операции, как сложение, вычитание, сравнение, преобразование, умножение, деление, вычисление квадратного корня, сдвиг и др., предусмотренные системой команд ЭВМ. Простейший вид универсального АУ – арифметико-логическое устройство (АЛУ). Оно обрабатывает числа с фиксированной запятой (целые числа), выполняет операции сложения, вычитания, сдвига и логич. операции. Специализир. АУ выполняет группу близких по алгоритму операций. Так, устройство сложения реализует операции сложения, вычитания, сравнения и преобразования типов и форматов данных; устройство деления – деление и вычисление квадратного корня. Универсальное АУ имеет меньший объём оборудования, чем неск. специализированных, совместно выполняющих такие же функции. Преимуществом специализир. АУ является меньшее время выполнения операции. В состав АУ входят регистры, сумматоры, коммутаторы, сдвигатели, кодировщики приоритетов, дешифраторы и др. узлы. Регистры предназначены для врем. хранения информации, а сумматоры, сдвигатели и др. – для преобразования информации. Скорость работы этих узлов, особенно сумматора, в значит. степени определяет быстродействие АУ. Для работы АУ необходимо получить код операции и операнды (числа, над которыми выполняется операция). В вычислит. машинах существуют две формы представления чисел: с фиксированной запятой (преим. для целых чисел) и с плавающей запятой. Для представления целых чисел в ЭВМ обычно применяют 8-, 16-, 32- и 64-разрядные форматы, а для вещественных – 32-, 64-, 80- и 128-разрядные.

Осн. характеристики АУ: тип обрабатываемых операндов и их формат, время выполнения операций, пропускная способность. Время выполнения операций сложения, вычитания и сравнения целых чисел, логич. операций и операций сдвига обычно соответствует 1 такту (в самых быстрых совр. ЭВМ составляет 2∙10–9–2∙10–10 с). Для чисел с плавающей запятой 64-разрядного формата сложение занимает 2–4 такта, умножение 2–5 тактов, а деление от 9 до 60 тактов. Пропускная способность определяется тем, через сколько тактов после начала операции устройство может начать выполнение следующей операции. АУ, которое организовано по принципу конвейера (см. Процессор), способно каждый такт запускать новую операцию, что обеспечивает большую производительность ЭВМ. Для повышения скорости работы АУ используют более быстродействующую элементную базу, разрабатывают новые алгоритмы работы устройства, расширяют систему команд. Использование в ЭВМ неск. специализир. АУ позволяет выполнять одновременно неск. арифметич. операций, что существенно увеличивает производительность ЭВМ.

Начиная с 1990-х гг. получило распространение АУ, совмещающее умножение чисел с плавающей запятой со сложением (А·В+С). В таких АУ время выполнения сложной операции меньше суммы времён умножения и сложения. При этом экономится оборудование и уменьшается ошибка округления, т. к. округление производится только один раз. Эти устройства позволяют делить и извлекать квадратный корень по методу Ньютона – Рафсона и вычислять некоторые трансцендентные функции в ЭВМ, в которой отсутствует устройство деления. В это же время получили широкое распространение векторные и мультимедийные АУ (доступные посредством расширений систем команд Intel MMX, AMD 3DNow! , ARM Neon, Motorola AltiVec, и др.), позволяющие выполнять одну и ту же операцию одновременно над неск. парами операндов (напр., независимое сложение 16 пар чисел с плавающей запятой одинарной точности, доступное в расширении системы команд Intel AVX-512). Помимо работы с графической и аудиоинформацией, где приходится обрабатывать большие объёмы данных небольшой разрядности, они также активно применяются при ручном программировании критических по производительности участков кода (напр., подсчёт контрольных сумм в программной реализации некоторых уровней RAID (англ. Redundant Array of Independent Disks, избыточный массив независимых дисков) либо автоматической векторизации циклов современными оптимизирующими трансляторами. Особые требования к АУ предъявляются в специализир. ЭВМ, предназначенных для цифровой обработки сигналов (ЦОС), напр. радиолокационных. Они, как правило, обрабатывают числа с фиксированной запятой 16- и 32-разрядных форматов в режиме реального времени и очень часто используют АУ, выполняющие умножение с накоплением за один такт (перемножаются два целых операнда и прибавляется результат, полученный в предыдущей команде), т. к. эта операция часто используется в алгоритмах ЦОС. Прогресс в электронных технологиях позволяет разработчикам реализовывать в АУ всё более сложные и быстрые алгоритмы.

Арифметико-логическое устройство с магистральной связью.

⇐ ПредыдущаяСтр 5 из 6Следующая ⇒

· Указать назначение АЛУ.

· Описать принцип работы АЛУ с магистральной связью.

Ответ

Разнообразные арифметические и логические операции выполняются в устройствах, которые называются арифметико-логическими устройствами.

В последнее время широко используются АЛУ с магистральной связью.В состав АЛУ входят регистры Рг1-Рг2, коммутатор К, сумматор СМ и устройство управления УУ. В таком АЛУ регистры обычно служат только для хранения операндов и результатов вычислений, а их входные цепи содержат только схемы, обеспечивающие прием информации. Любой из регистров может быть подключен коммутатором К к выходной магистрали. Прием информации в регистры из оперативной памяти ОП производится только через входную магистраль, а выдача результатов в ОП — с выходной магистрали. Операнды поступают на сумматор СМ с выходной магистрали. Это позволяет производить операции над числами, расположенными в любых регистрах, что является существенным достоинством данной схемы. Результат операции через входную магистраль отсылается с сумматора СМ в один из регистров.

Потенциометрический датчик.

· Указать назначение потенциометрических датчиков.

· Описать принцип работы потенциометрического датчика по предложенной схеме.

· Указать материал, используемый при изготовлении датчиков, указать достоинства и недостатки датчиков.

Схема потенциометрического датчика

Ответ

Потенциометрические датчики предназначены для измерения линейных и угловых перемещений.

Потенциометрический датчик состоит из потенциометров П1 и П2, которые подключены параллельно к общему источнику питания UП. Подвижные контакты потенциометров К1 и К2 соединены механически с задающим (ЗРО) и исполнительным (ИРО) рабочими органами. Напряжение, снимаемое с подвижных контактов потенциометров, является напряжением сигнала UС. При согласованном положении рабочих органов (подвижные контакты находятся в одинаковом положении), когда α = β, напряжение сигнала равно 0. При рассогласованном положении, когда α ≠ β, сигнал на выходе датчика неравен 0. Причем сигнал будет пропорционален углу рассогласования, т.е. UС = α-β, а знак сигнала определяет направление рассогласования.

Для изготовления датчиков применяется константановая, манганиновая, нихромовая проволока. Также применяется проволока из сплавов серебра, платины и золота.

Достоинства: конструктивная простота, малая масса, небольшие габариты, возможность питания постоянным и переменным током, простота регулировки, высокая стабильность.

Недостатки: наличие подвижного контакта, снижающего надежность работы и срок службы, невысокая чувствительность, нелинейность характеристики при низкоомной нагрузке и наличие ошибки от ступенчатости характеристики.

Тензодатчики.

· Указать назначение тензодатчиков.

· Изобразить схему тензодатчики.

· Описать принцип работы.

· Указать виды тензодатчиков, их достоинства и недостатки.

Ответ

Тензометрические датчики предназначены для определения упругих деформаций (растяжения, сжатия, изгибающих и крутящих моментов) деталей машин и конструкций в линейном и плосконапряженном состоянии при воздействии на них статических и динамических нагрузок.

Схема тензометрического датчика.

Основой конструкции датчиков (рисунок8) служит константановая проволока (1) диаметром 0,01 – 0,05 мм, сложенная зигзагообразной решеткой между склеенными полосками бумаги или пленки (2).

Для измерения деформации датчик приклеивается к поверхности измеряемой детали.

При воздействии на испытуемую деталь или конструкцию каких-либо деформаций, например растяжения, будет растягиваться проволока датчика. При этом за счет увеличения длинны l проволоки тензодатчика и уменьшением её сечения S сопротивление проволоки R=ρl/S увеличивается. Это сопротивление является выходной величиной датчика. Такая деформация показана на рисунке8 сплошной стрелкой. Если деформацию направить так, как показано пунктирной стрелкой, проволока тензодатчика в местах её изгиба еще больше изогнется. Длинна и толщина проволоки при этом практически не меняются, не меняется и сопротивление датчика. Отсюда видно, что деформацию такого вида датчик не измеряет. Основными характеристиками тензодатчиков являются: номинальное сопротивление R. Длина решетки (база) l, коэффициент тензочувтвительности

где -абсолютное изменение длины проволоки, -относительное изменение длины проволоки;

-относительное изменение сопротивления тензодатчика.

Значение коэффициента тензочувтвительности 1,8-2,5 и зависит от технического изготовления датчика и материала его проволоки.

Достоинства: малые габариты и масса, почти полное отсутствие их влияния на деформацию детали, линейность характеристики.

Кроме проволочных существуют еще тензодатчики, у которых проводящий элемент делается из фольги толщиной 4-12 мм. По сравнению м проволочными у этих датчиков сила рабочего тока значительно выше, следовательно, повышена чувствительность датчика.

Полупроводниковые тензодатчики изготавливаются из германия, кремния. Коэффициент тензочувствительности в 60 раз выше, чем у проволочных и фольговых. Конструктивно представляет собой пластину из полупроводника, наклеенную на бумагу. Пластина снабжена металлическими выводами, с помощью которых датчик подключается в схему. Температурный диапазон этих датчиков от .

Емкостные датчики.

· Указать назначение емкостных датчиков. Их виды.

· Изобразить схемы емкостных датчиков.

· Описать принцип работы.

Ответ

Различают несколько видов емкостных датчиков:

Емкостные датчики

Емкостные датчики предназначены для измерения линейных и угловых перемещений.

Емкостной датчик с переменным расстоянием между пластинами (рисунок а) содержит две неподвижные пластины 1, 2 и подвижную пластину 3, которая механически связана с измеряемым объектом. Если d1 = d2, то С1 = С2, при перемещении подвижной пластины 3 в какую либо сторону происходит изменение расстояния между пластинами изменяется емкость условных конденсаторов. Так при увеличении параметра d1 увеличивается емкость конденсатора увеличивается емкость конденсатора С2, и наоборот. По изменению емкостей С1 и С2 можно измерить линейное перемещение объекта (до 0,1мм).

Емкостной датчик с поворотными пластинами (рисунок б) представляет собой воздушный конденсатор, у которого одна группа пластин неподвижна 1, а другая может поворачиваться на угол α 2. При α = 0 площадь перекрытия пластин S, а следовательно и емкость, наибольшая. При повороте подвижных пластин на угол α площадь перекрытия и емкость уменьшаются. Такие датчики применяются для измерения углов поворота от 00 до 1800.

Емкостной датчик с переменной диэлектрической проницаемостью (рисунок в) представляет собой конденсатор, с переменным диэлектриком. При различных величинах E1 воздуха, и Е2 перемещаемого диэлектрика, образуются два параллельно соединенных конденсатора. При перемещении диэлектрика, т.е. изменении уровня жидкости, изменяется перемещение h и емкость С. По изменению емкости судят о изменении уровня жидкости.

Рекомендуемые страницы:

Арифметико-логический блок (ALU): определение, конструкция и функции — видео и стенограмма урока

Как работает ALU

ALU выполняет основные арифметические и логические операции. Примерами арифметических операций являются сложение, вычитание, умножение и деление. Примерами логических операций являются сравнения таких значений, как НЕ, И и ИЛИ.

Вся информация в компьютере хранится и обрабатывается в виде двоичных чисел , то есть 0 и 1. Транзисторные переключатели используются для управления двоичными числами, поскольку существует только два возможных состояния переключателя: разомкнутый или замкнутый. Открытый транзистор, через который нет тока, представляет собой 0. Закрытый транзистор, через который есть ток, представляет собой 1.

Операции могут выполняться путем соединения нескольких транзисторов. Один транзистор может использоваться для управления вторым — по сути, включение или выключение транзистора в зависимости от состояния второго транзистора.Он упоминается как вентиль , потому что устройство может использоваться для разрешения или остановки тока.

Самый простой тип операции — вентиль НЕ. Здесь используется только один транзистор. Он использует один вход и производит один выход, который всегда противоположен входу. На этом рисунке показана логика шлюза НЕ:

Другие вентили состоят из нескольких транзисторов и используют два входа.Логический элемент ИЛИ дает 1, если первый или второй вход равен 1. Логический элемент ИЛИ дает 0, только если оба входа равны 0. На этом рисунке показана логика логического элемента ИЛИ:

Логический элемент И дает 1 только в том случае, если и первый, и второй вход равны 1. На этом рисунке показана логика логического элемента И:

Логический элемент XOR, также произносится как вентиль X-OR, приводит к 0, если оба входа равны 0 или оба равны 1.В противном случае результатом будет 1. На этом рисунке показана логика логического элемента XOR:

Различные ворота звучат немного абстрактно, но помните, что компьютер обрабатывает только двоичные данные. Следуя двоичной логике этих операций, вы начинаете думать как компьютер.

Различные комбинации логических вентилей позволяют выполнять арифметические операции.Например, в двоичном коде число 2 представлено как один-ноль, а число 3 представлено как один-один. Так как же компьютер складывает 2 и 3? Вычисление осуществляется с помощью серии логических элементов ИЛИ, И и ИСКЛЮЧАЮЩЕЕ ИЛИ. Результатом шагов логической обработки является один-ноль-один, что является двоичным кодом для 5.

Шлюзы позволяют компьютеру разбить любую сложную операцию на очень большое количество двоичных шагов. Поначалу это может показаться довольно громоздкой системой для выполнения простого добавления; однако компьютер может выполнять эти операции со скоростью своего центрального процессора, которая измеряется в гигагерцах или триллионах вычислений в секунду.Кроме того, типичный ЦП содержит сотни миллионов транзисторов, которые позволяют создавать очень сложные ALU. Компьютер также одновременно обрабатывает гораздо большие двоичные последовательности. В результате сложные операции можно выполнять за доли секунды.

Итоги урока

Давайте рассмотрим. Центральный процессор компьютера содержит арифметико-логический блок (АЛУ) для выполнения операций. Транзисторы используются для создания логических вентилей, включая НЕ, ИЛИ, И и XOR.Комбинации логических вентилей позволяют выполнять арифметические операции.

Результаты обучения

Урок дает возможность:

- Определить арифметико-логический блок (АЛУ)

- Идентифицировать логические элементы НЕ, ИЛИ, И и ИСКЛЮЧАЮЩЕЕ

- Объясните, как ALU выполняет арифметические операции

Что такое арифметико-логическая единица (АЛУ)?

Что означает арифметико-логическая единица (ALU)?

Арифметико-логический блок (АЛУ) является основным компонентом центрального процессора компьютерной системы.Он выполняет все процессы, связанные с арифметическими и логическими операциями, которые должны выполняться над командными словами. В некоторых архитектурах микропроцессоров ALU разделен на арифметический блок (AU) и логический блок (LU).

Инженеры могут спроектировать АЛУ для расчета любой операции. По мере усложнения операций ALU также становится более дорогим, занимает больше места в ЦП и рассеивает больше тепла. Вот почему инженеры делают ALU достаточно мощным, чтобы гарантировать, что ЦП также будет мощным и быстрым, но не настолько сложным, чтобы стать непомерно дорогим с точки зрения стоимости и другими недостатками.

Арифметико-логический блок также известен как целочисленный блок (IU).

Techopedia объясняет арифметико-логическое устройство (ALU)

Арифметико-логический блок — это часть ЦП, которая обрабатывает все вычисления, которые могут потребоваться ЦП. Большинство этих операций имеют логический характер. В зависимости от того, как спроектирован ALU, он может сделать процессор более мощным, но он также потребляет больше энергии и выделяет больше тепла. Следовательно, должен быть баланс между тем, насколько мощным и сложным является ALU, и насколько дорогим становится все устройство.Вот почему более быстрые процессоры дороже, потребляют больше энергии и рассеивают больше тепла.

Основными функциями ALU являются выполнение арифметических и логических операций, включая операции сдвига битов. Это важные процессы, которые необходимо выполнять практически с любыми данными, обрабатываемыми ЦП.

ALU обычно выполняют следующие операции: