Что представляет собой архитектура ARM Cortex-A57. Какие преимущества она имеет по сравнению с предыдущими поколениями процессоров ARM. Где планируется применять процессоры на базе Cortex-A57. Какие перспективы открывает эта архитектура для развития мобильных и серверных устройств.

Ключевые особенности архитектуры ARM Cortex-A57

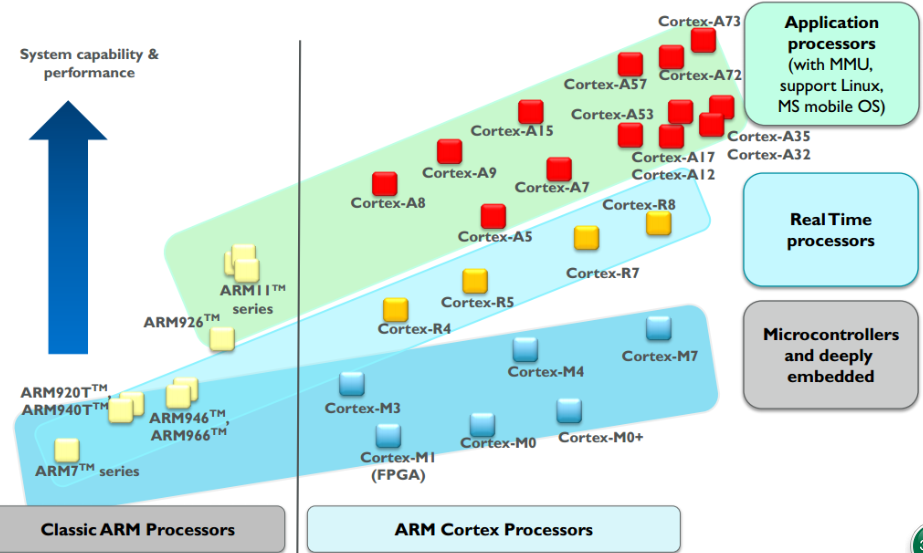

ARM Cortex-A57 — это высокопроизводительное 64-битное процессорное ядро, разработанное компанией ARM Holdings. Оно было представлено в 2012 году как один из первых процессоров ARM с поддержкой 64-битных вычислений.

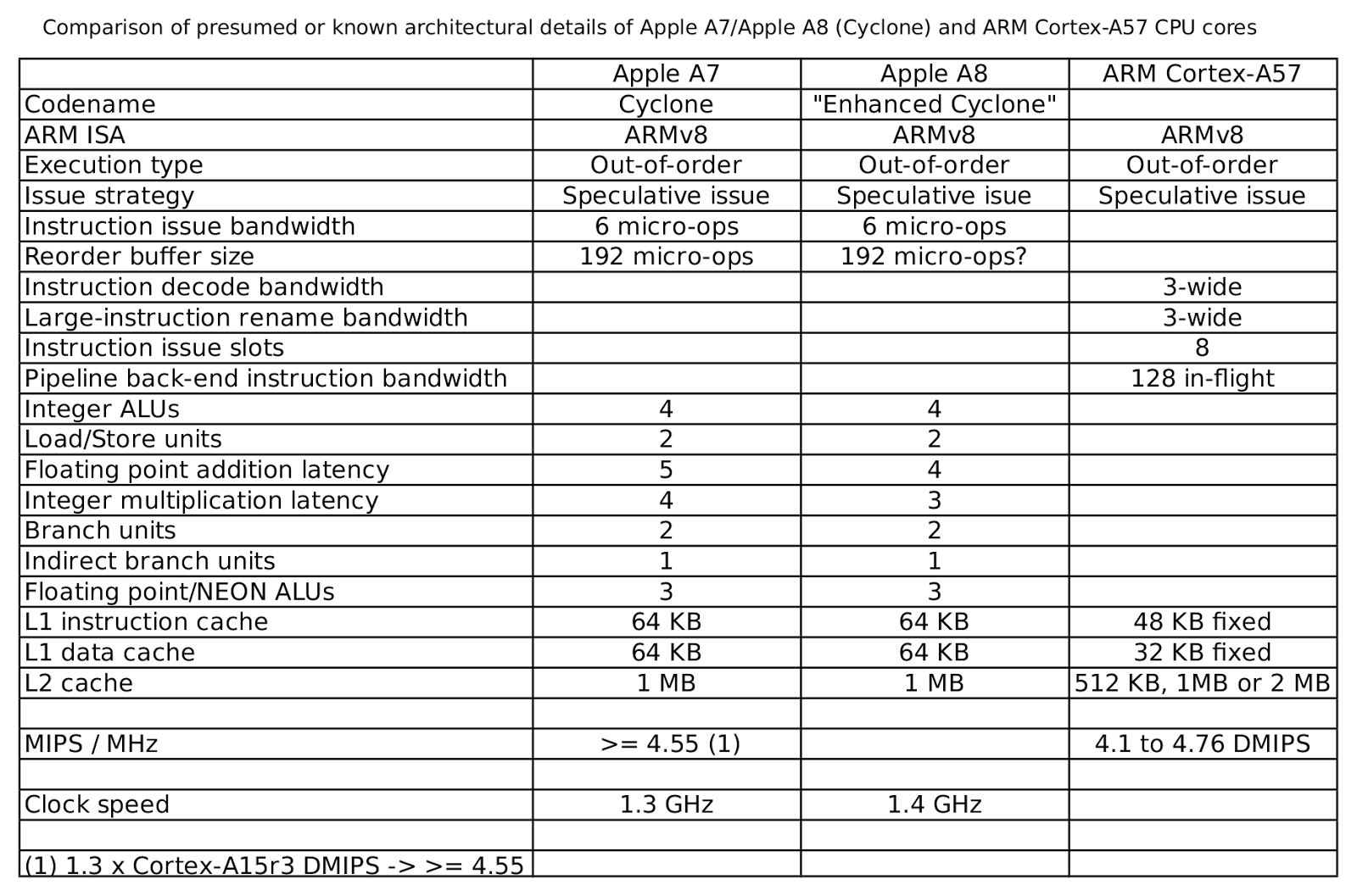

Основные характеристики Cortex-A57:

- 64-битная архитектура ARMv8-A

- Суперскалярный процессор с внеочередным исполнением инструкций

- До 3 инструкций за такт

- Кэш первого уровня: 48 КБ для инструкций и 32 КБ для данных

- Кэш второго уровня: до 2 МБ

- Поддержка виртуализации и TrustZone

- Возможность объединения до 4 ядер в кластер

Сравнение Cortex-A57 с предыдущими поколениями процессоров ARM

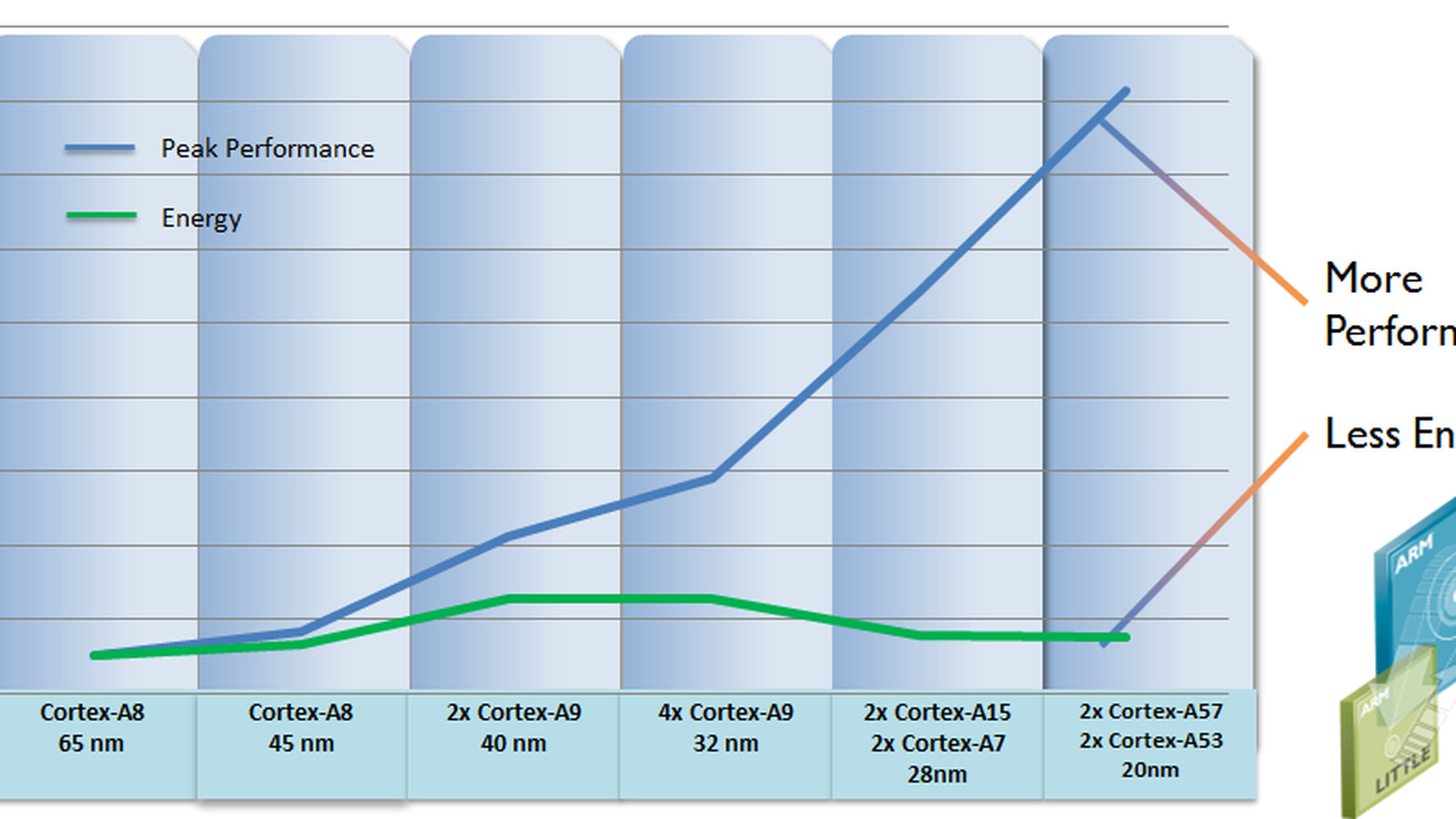

По сравнению с предшественниками, Cortex-A57 обеспечивает значительный прирост производительности:

- На 25-50% выше производительность на такт по сравнению с Cortex-A15

- На 20-30% выше энергоэффективность в сравнении с Cortex-A15 при той же производительности

- Поддержка 64-битных вычислений и адресации до 1 ТБ памяти

- Улучшенный блок предсказания ветвлений

- Расширенный набор SIMD-инструкций NEON

Таким образом, Cortex-A57 обеспечивает существенное повышение производительности и энергоэффективности по сравнению с 32-битными процессорами предыдущих поколений.

Области применения процессоров на базе Cortex-A57

Благодаря высокой производительности и энергоэффективности, процессоры на базе Cortex-A57 нашли применение в различных устройствах:

- Мощные смартфоны и планшеты премиум-класса

- Ноутбуки и хромбуки на ARM-процессорах

- Серверы и микросерверы

- Сетевое оборудование

- Автомобильные информационно-развлекательные системы

- Системы машинного обучения и искусственного интеллекта

Cortex-A57 стал одним из первых процессоров ARM, который начал применяться не только в мобильных устройствах, но и в серверном сегменте.

Преимущества Cortex-A57 для мобильных устройств

В мобильных устройствах применение Cortex-A57 позволило добиться следующих преимуществ:

- Повышение производительности без увеличения энергопотребления

- Поддержка более качественной графики и видео высокого разрешения

- Улучшение многозадачности благодаря 64-битной архитектуре

- Возможность использования более 4 ГБ оперативной памяти

- Ускорение шифрования и повышение безопасности

Все это позволило создавать более производительные смартфоны и планшеты с увеличенным временем автономной работы.

Перспективы применения Cortex-A57 в серверном сегменте

Применение Cortex-A57 в серверах открыло новые возможности:

- Создание энергоэффективных микросерверов

- Снижение стоимости серверного оборудования

- Повышение плотности размещения серверов в дата-центрах

- Оптимизация под специфические задачи облачных вычислений

- Улучшение производительности в расчете на ватт потребляемой энергии

Это сделало ARM-серверы привлекательной альтернативой традиционным x86-серверам для некоторых типов нагрузок.

Технологии, реализованные в Cortex-A57

В Cortex-A57 реализован ряд передовых технологий:

- Технология big.LITTLE для оптимизации энергопотребления

- Расширенная поддержка виртуализации

- Криптографические расширения для ускорения шифрования

- Поддержка когерентности кэш-памяти в многопроцессорных системах

- Улучшенная предвыборка данных из памяти

Эти технологии позволили повысить производительность и энергоэффективность процессора в различных сценариях использования.

Сравнение Cortex-A57 с конкурирующими архитектурами

По сравнению с конкурирующими архитектурами, Cortex-A57 имеет следующие преимущества:

- Более высокая энергоэффективность по сравнению с x86-процессорами

- Лучшая производительность на ватт в сравнении с MIPS-архитектурой

- Более широкая экосистема ПО по сравнению с RISC-V

- Меньшая стоимость лицензирования в сравнении с x86

При этом Cortex-A57 уступает высокопроизводительным x86-процессорам в пиковой производительности, что ограничивает его применение в высокопроизводительных системах.

Развитие архитектуры Cortex-A57 в последующих поколениях процессоров ARM

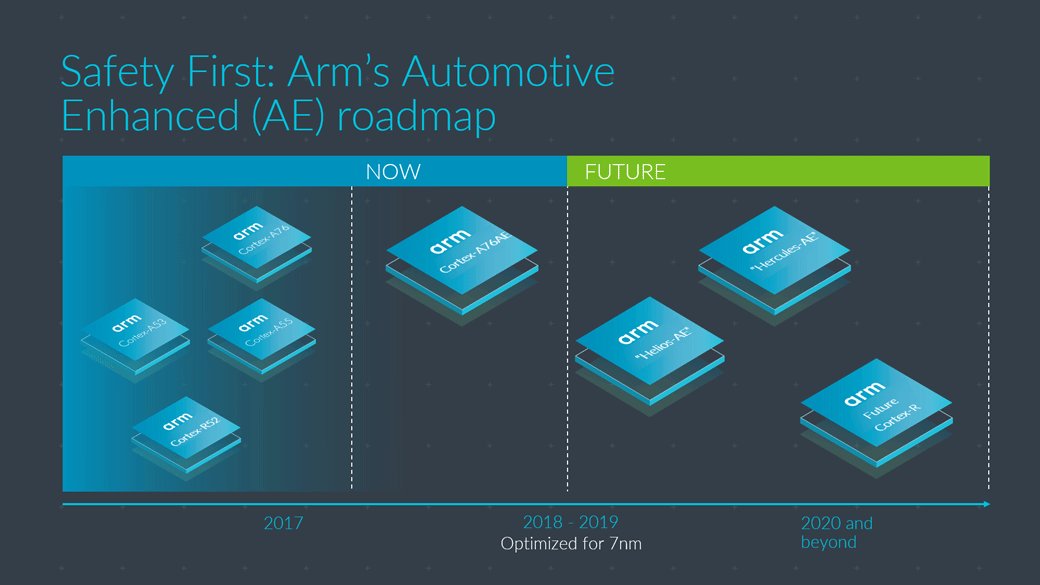

Архитектура Cortex-A57 получила дальнейшее развитие в последующих поколениях процессоров ARM:

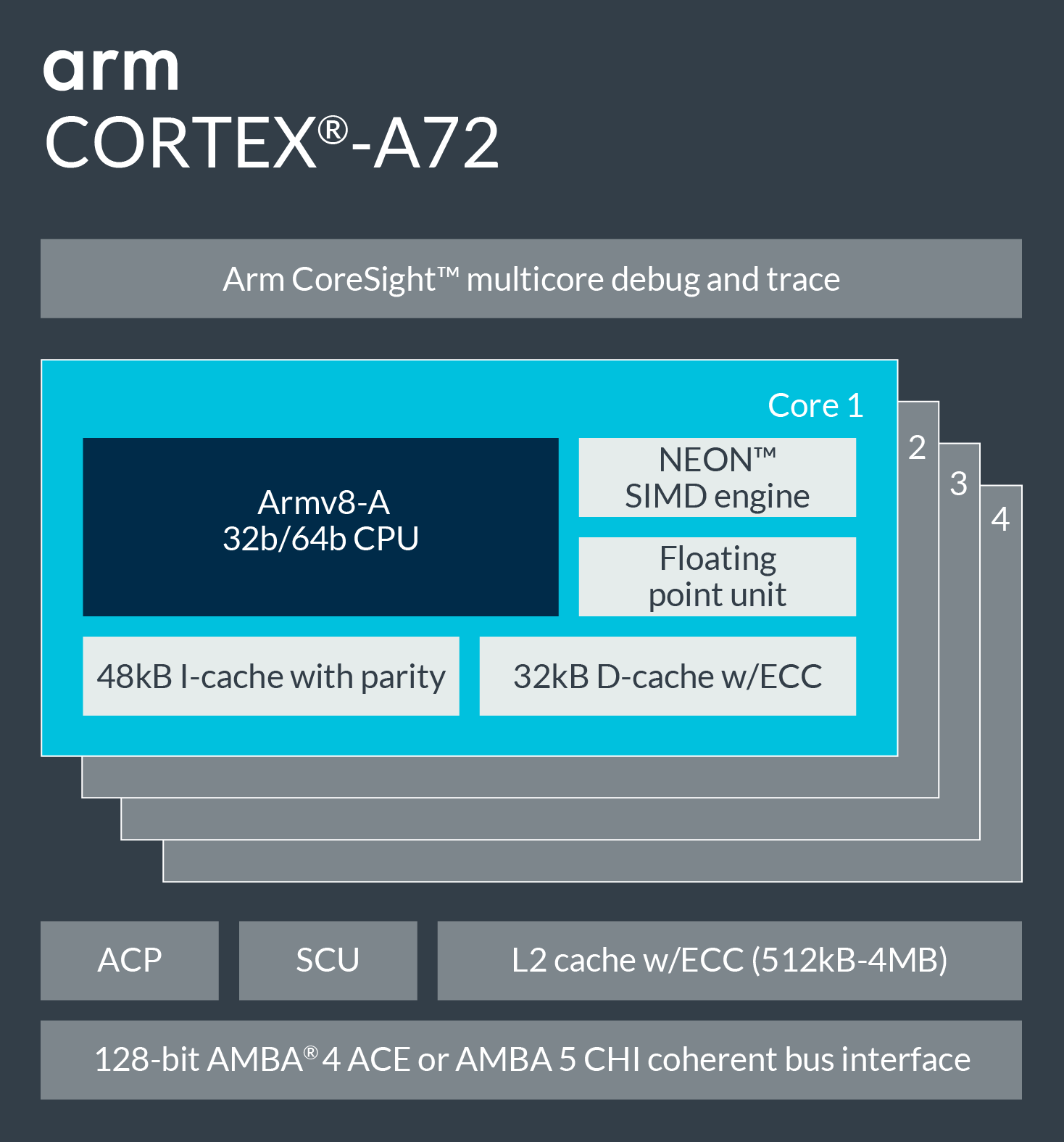

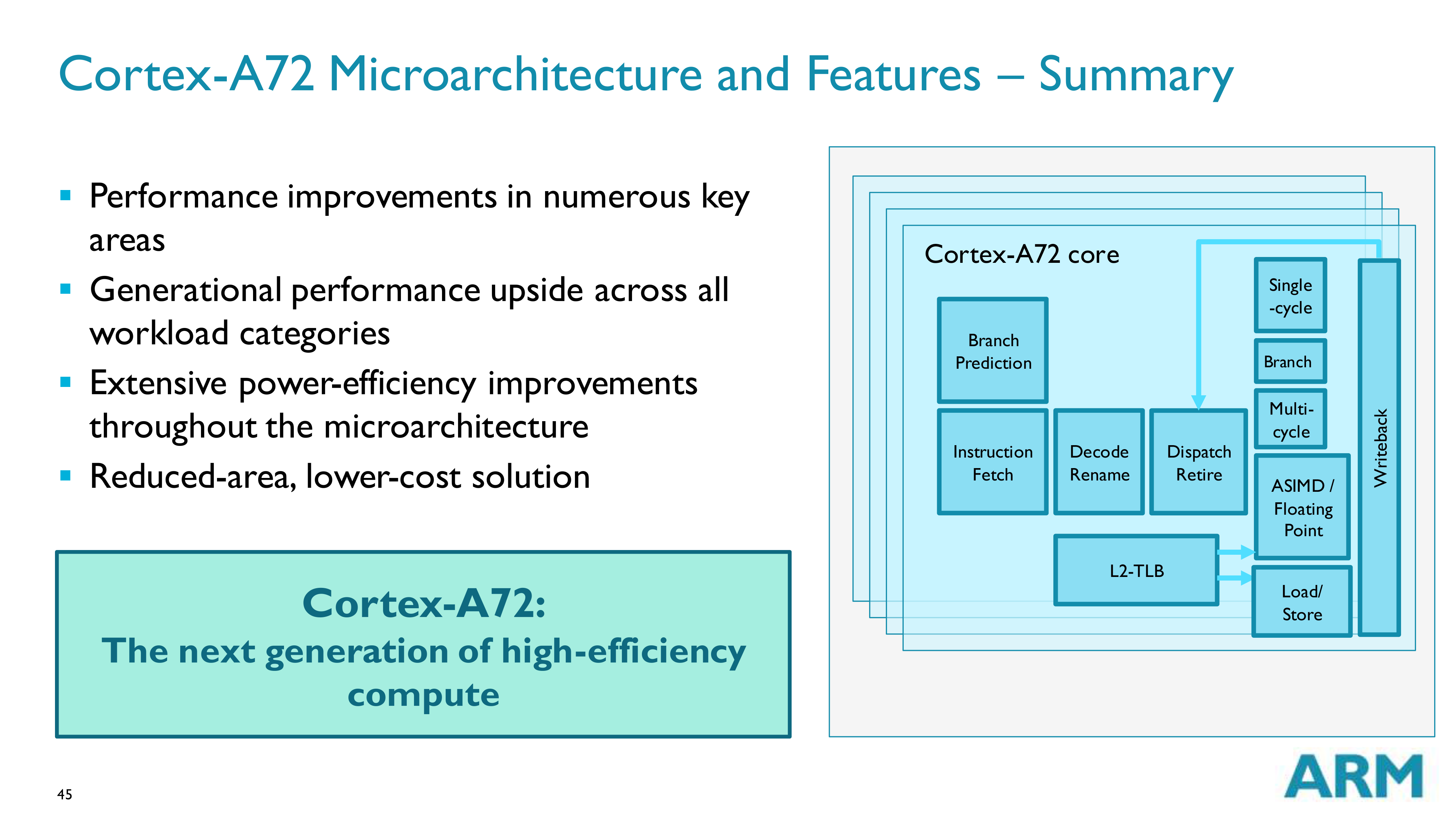

- Cortex-A72 — улучшенная версия с повышенной производительностью и энергоэффективностью

- Cortex-A73 — оптимизирован для мобильных устройств

- Cortex-A75 — поддержка технологии DynamIQ для гибкой конфигурации ядер

- Cortex-A76 — существенное повышение производительности для конкуренции с x86

Таким образом, Cortex-A57 заложил основу для дальнейшего развития высокопроизводительных ARM-процессоров как для мобильных устройств, так и для серверов.

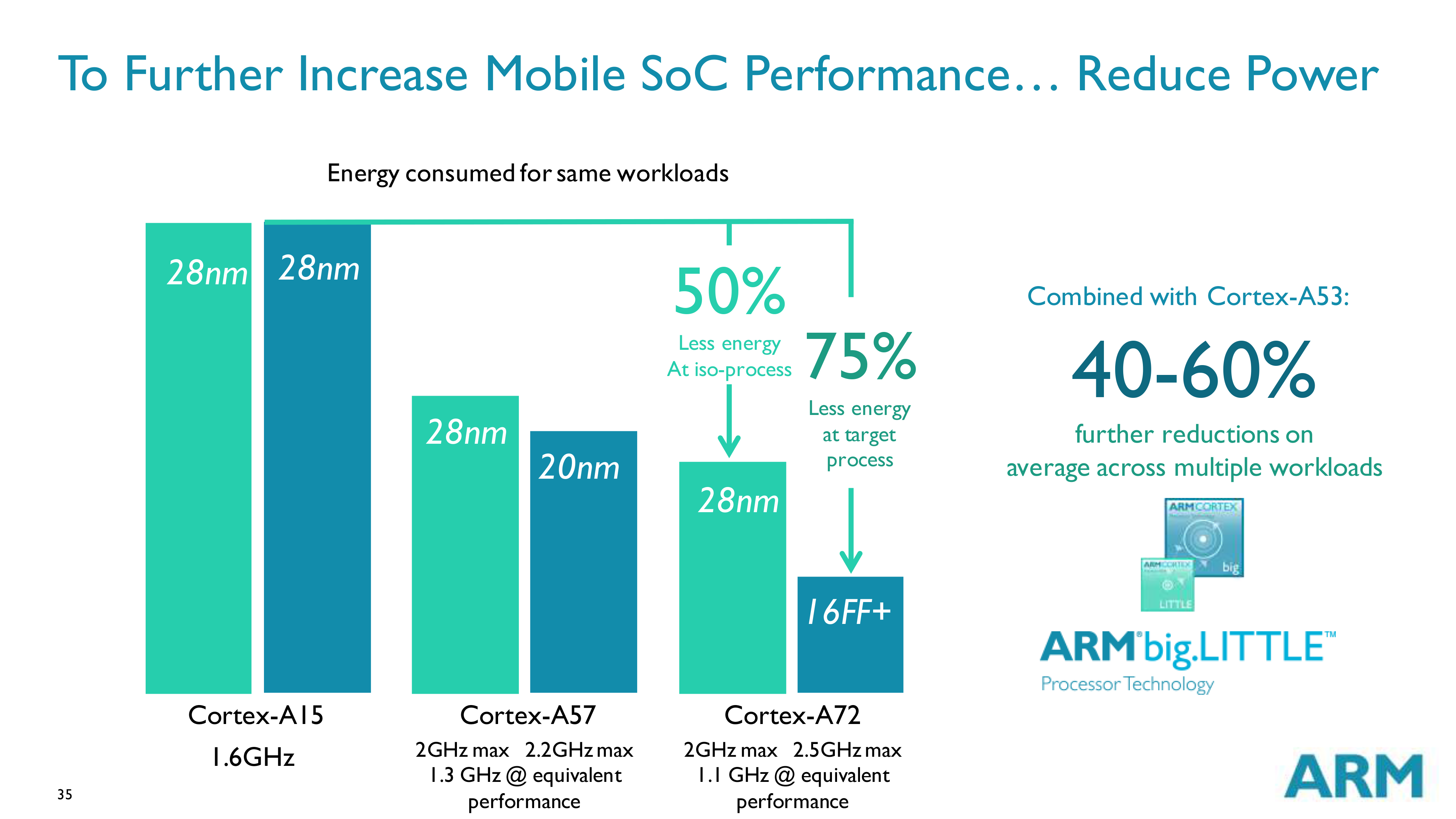

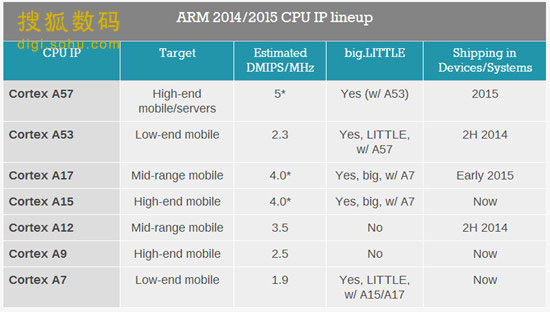

ARM сравнила процессорные ядра Cortex-A72 с существующими решениями, включая мобильные CPU Intel

Процессорное ядро Cortex-A72 было представлено в начале февраля. Некоторые компании уже анонсировали однокристальные платформы с такими ядрами, но до их появления ещё относительно далеко.

А пока ARM решила раскрыть больше подробностей о своей разработке, сравнив её с актуальными решениями собственного лагеря, а также представителями мобильной платформы.

Итак, если сравнивать новое ядро с Cortex-A57, то стоит отметить несколько фактов. Во-первых, новое ядро может похвастаться улучшенным блоком предсказания ветвлений, который превосходит таковой у существующих ядер на 20%. Также компания переработала трёхполосную кэш-память первого уровня и его диспетчер управления.

В функциональных блоках улучшений ещё больше. Они затронули блоки MUL, FADD, FMAC и CVT. Общая кэш-память второго уровня была «настроена на высокую пропускную способность». По сравнению с Cortex-A57 у новых ядер на 20%-60% выросло количество выполняемых за такт инструкций. Новые ядра, функционируя на частоте 2,7 ГГц будут потреблять примерно на 10% меньше энергии, нежели Cortex-A57 на частоте 2,5 ГГц. Естественно, это при условии одинакового техпроцесса, хотя Cortex-A72 будут производиться уже по нормам 16 и 14 нм. В целом, с точки зрения энергетической эффективности, новые решения на 18%-30% лучше, нежели существующие.

По сравнению с Cortex-A57 у новых ядер на 20%-60% выросло количество выполняемых за такт инструкций. Новые ядра, функционируя на частоте 2,7 ГГц будут потреблять примерно на 10% меньше энергии, нежели Cortex-A57 на частоте 2,5 ГГц. Естественно, это при условии одинакового техпроцесса, хотя Cortex-A72 будут производиться уже по нормам 16 и 14 нм. В целом, с точки зрения энергетической эффективности, новые решения на 18%-30% лучше, нежели существующие.

Не преминула ARM сравнить свои разработки и с настольными собратьями. Конечно, говорить о прямом противостоянии по производительности не приходится, хотя с наиболее медленными настольными CPU топовые платформы в некоторых задачах уже вполне способны потягаться.

По мнению компании, если сравнить новые ядра с процессорами Intel Broadwell, то получится, что при равной производительности (в теории), энергопотребление решений ARM будет на 75% ниже.

На последнем графике ARM напрямую сравнивает процессор Core-M 5Y10C (0,8-2 ГГц при 4 Вт) с какой-то платформой, основанной на четырёх ядрах Cortex-A72 (

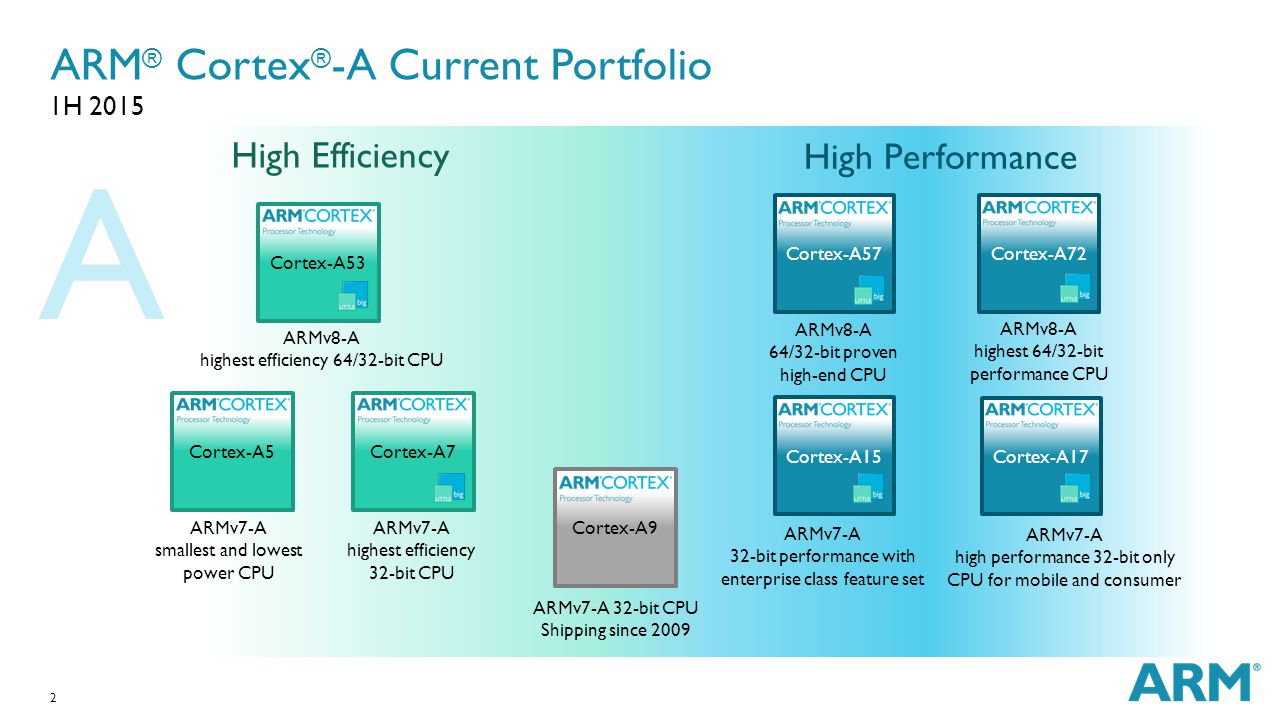

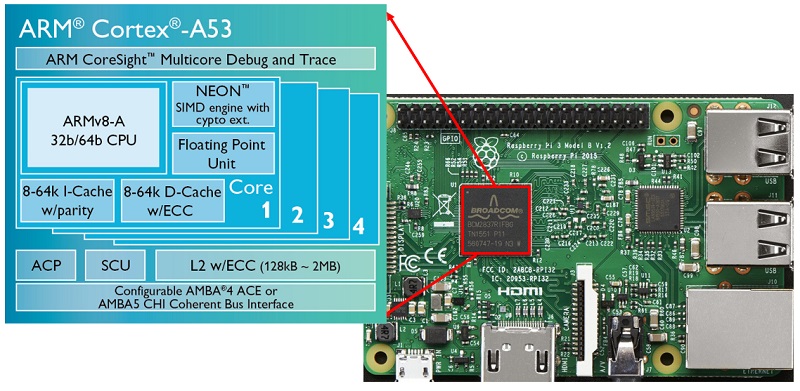

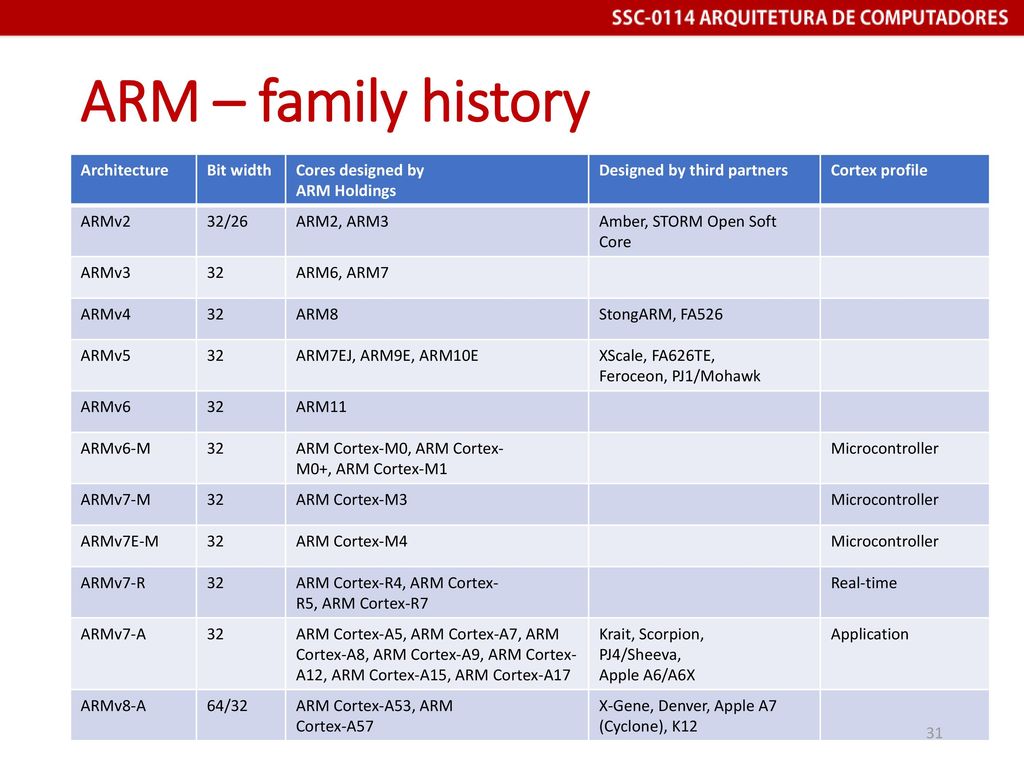

Первые ядра CPU ARMv8 с 64-битной поддержкой — Cortex-A57 и Cortex-A53

Вчера мы опубликовали новость о новой стратегии AMD — компания планирует выпускать процессоры Opteron с 64-битной поддержкой ARM. Они будут ориентированы на рынок микро-серверов. Но пока не понятно, какие ядра ARM будут использоваться в процессорах AMD Opteron. Нынешние ядра ARMv7 являются по-прежнему 32-битными. И как раз два недавно объявленных ядра ARM кажутся прекрасными кандидатами на новую роль для AMD — мы имеем в виду ядра CPU ARMv8 Cortex-A57 и Cortex-A53.

Они будут ориентированы на рынок микро-серверов. Но пока не понятно, какие ядра ARM будут использоваться в процессорах AMD Opteron. Нынешние ядра ARMv7 являются по-прежнему 32-битными. И как раз два недавно объявленных ядра ARM кажутся прекрасными кандидатами на новую роль для AMD — мы имеем в виду ядра CPU ARMv8 Cortex-A57 и Cortex-A53.

Оба ядра имеют 64-битную поддержку. Ядро Cortex-A57 также известно под кодовым названием Atlas, а A53 — кодовым названием Apollo. Они, соответственно, замещают Cortex-A15 и Cortex-A7. По структуре тоже присутствуют сходства.

Cortex-A57 можно назвать оптимизированным A15. В дополнение к 64-битной поддержек (но 32-битный режим тоже присутствует) была увеличена ширина исполнительных блоков, а также добавлены некоторые менее значимые оптимизации. Производительность 32-битного режима по сравнению с A15 была увеличена примерно на 20-30 процентов. В 64-битном режиме преимущество по производительности ещё чуть выше. Для серверного использования можно комбинировать до 16 ядер Cortex-A57.

Ядро Cortex-A53 тоже является дальнейшим совершенствованием Cortex-A7, но его структура проще по сравнению с A57. По производительности мы должны получить примерно уровень Cortex-A9, но кристаллу требуется всего около 60 процентов площади.

ARM также привела некоторые сравнительные описания производительности моделей Cortex-A50. Младший процессор Cortex-A53 будет производительнее современных high-end смартфонов, но при этом ещё и в четыре раза более эффективным. Cortex-A57 будет работать примерно с уровнем энергопотребления современных high-end смартфонов, но зато по производительности будет примерно в три раза быстрее.

Процессоры с ядрами Cortex-A57 и Cortex-A53 будут производиться, начиная с середины 2013 года партнёрами ARM. Сюда входят, среди других компаний, ARM и Samsung. Соответствующие потребительские продукты появятся наверняка не раньше 2014 года. Изначально для производства будет использоваться 28-нм и 20-нм техпроцесс. Позднее планируется переход на 14-нм техпроцесс.

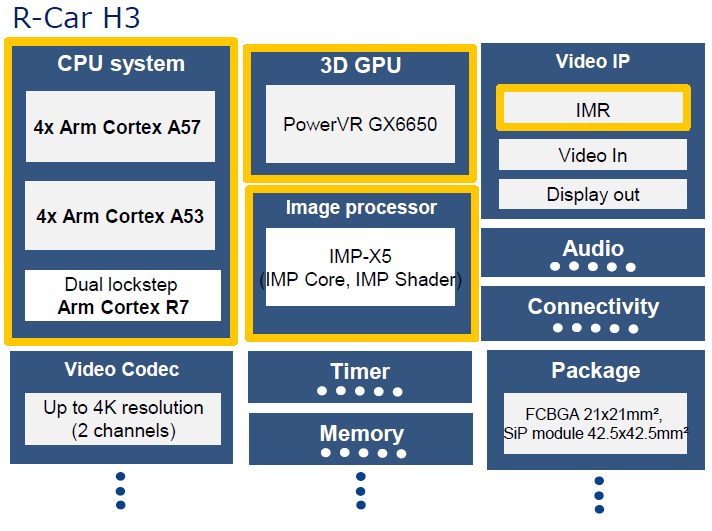

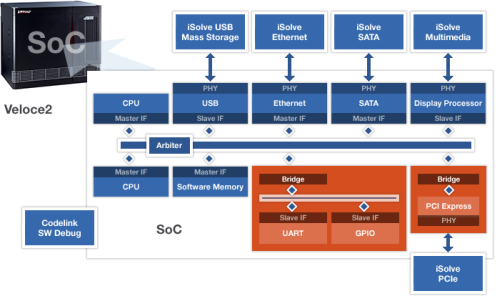

Байкал-М, процессор BE-M1000, микропроцессор Baikal-M, CPU Байкал-М

Отечественная система на кристалле на базе архитектуры ARM v8

Сферы применения

Офисные рабочие места

Промышленная автоматизация и управление зданиями

Рабочие станции

Структурная схема

Современный высокопроизводительный процессор Байкал М, предназначен для широкого

диапазона целевых устройств потребительского и B2B сегментов.

Современный высокопроизводительный процессор Байкал М, предназначен для широкого

диапазона целевых устройств потребительского и B2B сегментов.

Технические характеристики

- CPU: 8 ядер Arm® Cortex™-A57 с частотой до 1.5 ГГц (архитектура Armv8-A)

- GPU: 8 ядер Arm Mali™-T628 с частотой до 750 МГц

- Кэш L2: 1 МБ на кластер

- Кэш L3: 8 МБ

- Два канала памяти 64-bit DRAM DDR4-2400/DDR3-1600 с поддержкой коррекции ошибок (ECC)

- Технологический процесс TSMC 28 нм

- Энергопотребление до 35 W

- Тип – FCBGA

- 40 × 40 мм

- 2.

8/3.05/3.3 мм – высота (мин/ном/макс)

8/3.05/3.3 мм – высота (мин/ном/макс) - 1521 вывод

- 1 мм шаг

- 0.6 мм диаметр вывода

Корпус:

Документация

Краткое описание

Тесты производительности

Другие материалы

Документация для программистов

Комплект документов Baikal-M (BE-M1000) Programming Guide предназначен для программистов, разрабатывающих системное программное обеспечение или bare-metal приложения.

Документация включает 39 томов (общий объём — более 3600 страниц на английском языке) и описывает как структуру микропроцессора в целом (карта памяти, карта прерываний и т.п.), так и отдельные функциональные подсистемы (DDR, USB, PCIe, HDMI и др.).

Для каждой функциональной подсистемы приводится:

• детальное описание структуры;

• назначение основных блоков и интерфейсов, особенности их функционирования;

• описание программируемых регистров и их полей;

• рекомендации по программному управлению подсистемой.

Среда разработки

В состав SDK (Software Development Kit) входит следующий набор системных программных модулей: • Toolchain на основе кросс-компилятора gcc

• ARM Trusted Firmware-A (TF-A) – в исходных кодах

• TianoCore UEFI (EDK II) — в исходных кодах

• Linux kernel — в исходных кодах

• Rootfs на основе busybox

UEFI tianocore (поддержка загрузки ядра Linux через интерфейсы:• SATA

• USB

• 1Gb Ethernet

• SPI

• PCIe

ARM Cortex-A57 vs ARM Cortex-A9: в чем разница?

Производительность

Скорость центрального процессора показывает сколько циклов обработки в секунду может выполнять процессор, учитывая все его ядра (процессоры). Она рассчитывается путем сложения тактовых частот каждого ядра или, в случае многоядерных процессоров, каждой группы ядер.

Она рассчитывается путем сложения тактовых частот каждого ядра или, в случае многоядерных процессоров, каждой группы ядер.

Большее число потоков приводит к более высокой производительности и лучшему одновременному выполнению нескольких задач.

Используя технологию big.LITTLE, чип может переключаться между двумя наборами процессоров, чтобы обеспечить максимальную производительность и срок службы батареи. Например, во время игр более мощный процессор будет использоваться для повышения производительности, в то время как проверка электронной почты будет использовать менее мощный процессор для продления срока службы аккумулятора.

HMP — это более продвинутая версия технологии big.LITTLE. В этой конфигурации, процессор может использовать все ядра одновременно, или только одно ядро для задач низкой интенсивности. Это может обеспечить высокую производительность и увеличение срока службы батареи соответственно.

Когда процессор работает ниже своих ограничений, он может перейти на более высокую тактовую частоту, чтобы увеличить производительность.

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A57)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Больше сверхоперативной памяти L2 приводит к быстрым результатам в центральном процессорном устройстве и настройках производительности системы.

7.L1 кэшНеизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A57)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Больше сверхоперативной памяти L1 приводит к быстрым результатам в центральном процессорном устройстве и настройках производительности системы.

8.часовой множительНеизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A57)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Часовой множитель контролирует скорость процессора.

9.L3 кэшНеизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A57)

Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A9)

Больше сверхоперативной памяти L3 приводит к быстрым результатам в центральном процессорном устройстве и настройках производительности системы.

+ Показать больше +

ARM Cortex-A57 vs MediaTek MT6750: в чем разница?

Производительность

Скорость центрального процессора показывает сколько циклов обработки в секунду может выполнять процессор, учитывая все его ядра (процессоры). Она рассчитывается путем сложения тактовых частот каждого ядра или, в случае многоядерных процессоров, каждой группы ядер.

Большее число потоков приводит к более высокой производительности и лучшему одновременному выполнению нескольких задач.

Используя технологию big.LITTLE, чип может переключаться между двумя наборами процессоров, чтобы обеспечить максимальную производительность и срок службы батареи. Например, во время игр более мощный процессор будет использоваться для повышения производительности, в то время как проверка электронной почты будет использовать менее мощный процессор для продления срока службы аккумулятора.

HMP — это более продвинутая версия технологии big.LITTLE. В этой конфигурации, процессор может использовать все ядра одновременно, или только одно ядро для задач низкой интенсивности. Это может обеспечить высокую производительность и увеличение срока службы батареи соответственно.

Это может обеспечить высокую производительность и увеличение срока службы батареи соответственно.

Когда процессор работает ниже своих ограничений, он может перейти на более высокую тактовую частоту, чтобы увеличить производительность.

6.Кэш L2Неизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A57)

Больше сверхоперативной памяти L2 приводит к быстрым результатам в центральном процессорном устройстве и настройках производительности системы.

7.L1 кэшНеизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A57)

Больше сверхоперативной памяти L1 приводит к быстрым результатам в центральном процессорном устройстве и настройках производительности системы.

8.часовой множительНеизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A57)

Неизвестно. Помогите нам, предложите стоимость. (MediaTek MT6750)

Часовой множитель контролирует скорость процессора.

9.L3 кэшНеизвестно. Помогите нам, предложите стоимость. (ARM Cortex-A57)

Неизвестно. Помогите нам, предложите стоимость. (MediaTek MT6750)

Помогите нам, предложите стоимость. (MediaTek MT6750)

Больше сверхоперативной памяти L3 приводит к быстрым результатам в центральном процессорном устройстве и настройках производительности системы.

+ Показать больше +

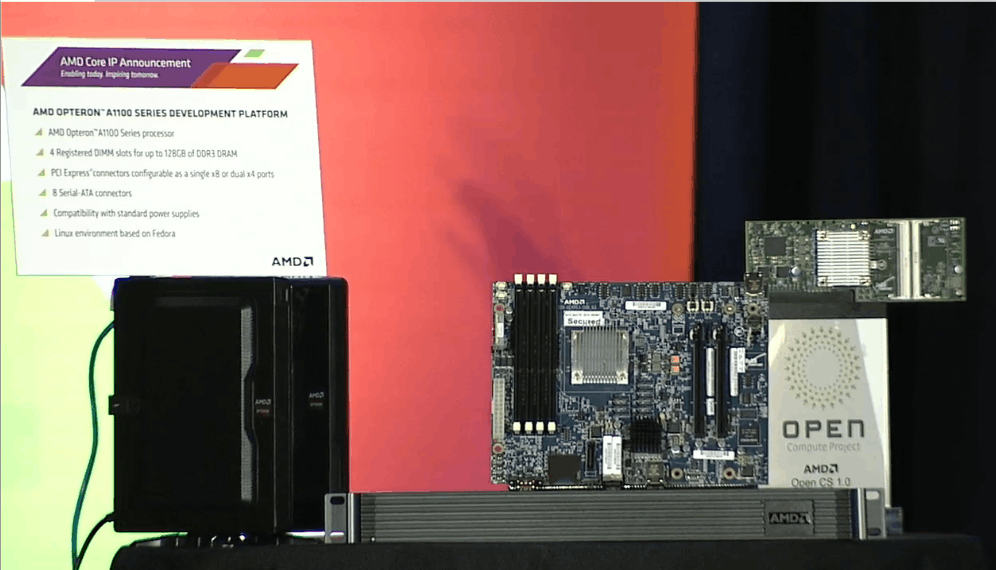

Работа Hadoop на базе ARM Cortex-A57 и платформе AMD Opteron A-серии

Компания AMD провела первую демонстрацию фреймворка Apache™ Hadoop® на процессоре AMD Opteron™ A-серии с архитектурой ARM® Cortex®-A57. В рамках технической сессии на конференции JavaOne™ менеджер компании AMD Леендерт ван Доорн (Leendert van Doorn) представил развивающуюся серверную программную экосистему AMD Opteron A-серии, которая теперь включает в себя фреймворк Hadoop, ПО на базе Java для хранения и обработки больших массивов данных. В ходе сессии к г-ну Леендерту присоединился Хенрик Сталь (Henrik Stahl), вице-президент по продуктам Java и направления «Интернет вещей» в Oracle, который рассказал о поддержке серверной 64-битной ARM архитектуры AMD.

Hadoop, технология распределённых вычислений, используемая в первую очередь для анализа больших данных, активно развивается, и ожидается, что к 2020 году достигнет более 50 млрд. долларов США в объёме рынка. Сочетание 64-битных ARM-серверов и Hadoop позволит ускорить темпы меняющейся экономической ситуации на рынке крупномасштабных вычислений за счёт использования распределённой обработки данных на кластерах ARM-серверов. Демонстрация системы, под управлением недавно анонсированной платформы AMD Opteron™ A1100, представляла собой Apache Hadoop, исполняемый на базе Oracle JDK. Г-н Ван Доорн также показал работу многоузлового кластера под управлением сред Linux, на базе технологии Fedora – комьюнити-проекта, который спонсируется компанией Red Hat, при поддержке сообщества OpenSUSE Project.

«Эта демонстрация подтверждает лидирующие позиции AMD в области разработки устойчивых экосистем на основе отраслевых стандартов для серверов с ARM-архитектурой, – считает г-н Ван Доорн. – Серверы, оснащённые процессорами AMD Opteron A-серии, идеально подходят для работы с Hadoop и предлагают эффективную горизонтально масштабируемую вычислительную платформу, которая одновременно может использоваться как экономичное решение для надёжного хранения данных».

AMD продолжает разрабатывать новаторские решения для серверных экосистем, предлагая возможности для лёгкой интеграции инструментов и программного обеспечения в архитектурные среды ARM и x86. Благодаря сотрудничеству с такими компаниями, как ARM, Linaro, Oracle, Red Hat и SUSE, AMD открывает доступ к полноценной среде для разработки приложений на базе ARM архитектуры и кросс-платформенной поддержки.

Более подробную информацию о сессии AMD можно получить на странице страницу JavaOne.

Дополнительная информация:

AMD.com

ARM выпустила процессоры нового поколения, которые ускорят искусственный интеллект в 50 раз

Интеграция Техника | Поделиться ARM представила два первых процессорных ядра Cortex-A75 и Cortex-A55 с новой архитектурой DynamIQ, а также новую графику ARM Mali-G72. Компания обещает 50-кратный рост производительности в области ИИ и универсальность использования – от смартфонов до серверов.

Компания обещает 50-кратный рост производительности в области ИИ и универсальность использования – от смартфонов до серверов.

Первые процессоры нового поколения

Компания ARM, ведущий мировой разработчик процессоров для мобильных устройств, представила два первых процессорных ядра Cortex-A75 и Cortex-A55 на базе новой мультиядерной процессорной микроархитектуры DynamIQ, которая на ближайшие годы станет основой всех новых процессоров семейства Cortex-A.

Новая микроархитектура DynamIQ, впервые представленная компанией в марте 2017 г., пришла на смену предыдущей технологии big.LITTLE, впервые представленной ARM в 2011 году и успешно зарекомендовавшей себя за пять с лишним лет. В ARM отмечают, что DynamIQ является дальнейшим эволюционным развитием идей и технологий big.LITTLE.

По словам представителей ARM, новые процессорные ядра Cortex-A75 и Cortex-A55 с технологией DynamIQ обеспечат оптимизацию для 50-кратного повышения производительности вычислений в области искусственного интеллекта в течение следующих трех-пяти лет, и 10-кратное увеличение производительности с применением интегрированных аппаратных акселераторов.![]()

Новые процессорные ядра ARM Cortex-A75 и Cortex-A55

В ARM подчеркивают, что в отличие от прежнего позиционирования своих вычислительных ядер для определенных узких рынков – например, для мобильных устройств, с выпуском микроархитектуры DynamIQ компания начинает переход к гибкой универсальной платформе с огромными возможностями масштабирования, поддерживающей интеллектуальные решения для практически любых применений, от облаков и сетей до гаджетов.

Нандан Найямпали (Nandan Nayampally), глава ARM Compute Products Group, отметил: «По мере усложнения вычислительных систем, нам необходимо переосмысление мультипроцессорной обработки данных. Это означает не только гибкую обработку данных в CPU, но также совершенствование и интеграцию гетерогенных вычислений в виде, более близком к разнообразным, дифференцированным решениям. С новой архитектурой вы можете настраивать производительность как на уровне кластеров, так и отдельных процессорных ядер, устанавливая для каждого подходящий уровень производительности и характеристик потребления энергии».

DynamIQ выводит возможности big.LITTLE на новый уровень

Вместе с первыми процессорными ядрами Cortex-A на платформе DynamIQ компания также представила новое графическое ядро ARM Mali-G72. Список улучшений новой графики включает расширенную поддержку игровых и VR-технологий, а также специфические возможности в области машинного обучения.

Новая графика ARM Mali-G72

Графика ARM Mali-G72 ориентирована на использование в мобильных устройствах премиального сегмента и обещает увеличение производительности на 40% по сравнению с предыдущим поколением.

Обновленное семейство процессорных ядер Cortex-A: что нового

Процессорная технология DynamIQ унаследовала от архитектуры предыдущего поколения ARM big.LITTLE проверенную временем организацию вычислительных мощностей – когда экономичные процессорные ядра сочетаются в одном кристалле с несколькими высокоэффективными ядрами. Это позволяет сконструировать мобильный процессор, способный при необходимости значительно наращивать производительность, и экономить заряд батареи мобильного устройства в остальное время.

Особенности архитектуры новых процессорных ядер Cortex-A

Развивая идею «правильный процессор для правильной задачи», архитектура DynamIQ поддерживает до 8 процессорных ядер на один вычислительный кластер, при этом кластеров в финальном чипе может быть практически бесконечно много.

Каждый вычислительный кластер, в свою очередь, обеспечивает определенный уровень производительности. В отличие от традиций big.LITTLE, где использовалось только попарное ускорение мощных и экономичных ядер (2+2, 2+4, 4+4 и т.п.), архитектура DynamIQ может работать с любыми сочетаниями экономичных и мощных ядер – от 1+3 или 1+7 до любых других.

Более гибкая работа вычислительных кластеров нового типа

Благодаря микроархитектуре DynamIQ, каждое ядро кластера может иметь различные показатели производительности и энергопотребления. Новая архитектура DynamIQ также поддерживает ряд новых инструкций, оптимизированных для ускорения процесса машинного обучения и для работы с приложениями искусственного интеллекта.

Специфика микроархитектуры DynamIQ

Дополнительную гибкость новой вычислительной архитектуре придает переделанная подсистема памяти, которая обеспечивает более быстрый доступ к данным при одновременном снижении энергопотребления.

Архитектура DynamIQ способна обеспечить низкое энергопотребление благодаря быстрому переключению между различными уровнями состояния и точному управлению уровнями производительности.

Особенности ARM Cortex-A75

Производительное процессорное ядро ARM Cortex-A75 обеспечивает значительный прирост производительности и энергоэффективности по сравнению со своими предшественниками Cortex-A72 и Cortex-A73. Чип обладает улучшенной примерно на 20% производительностью при работе с целыми числами, значительными улучшениями при работе с числами с плавающей запятой и задачами с большой нагрузкой на подсистему памяти.

Почему цифровые двойники становятся мэйнстримом в энергетике

Новое в СХДДля процессора Cortex-A75 характерна пиковая производительность при однопоточных нагрузках благодаря наличию симметричного трехстороннего суперскалярного конвейера варьируемой длины с полностью произвольной (out-of-order) выборкой команд.

Ядра Cortex-A75 обладают распределенным кластером кэша L3, поддержкой асинхронных частот и практически независимых напряжений питания для различных ядер внутри многоядерного процессора или кластера. Ядра Cortex-A75 также оснащены отдельной кэш-памятью L2 на каждое ядро с уменьшенной вдвое латентностью по сравнению со своими предшественниками.

В сочетании с распределенным модулем DynamIQ (DynamIQ Shared Unit, DSU), процессор Cortex-A75 позволяет обеспечить необходимый уровень производительности для широкого спектра системы и рынков – от смартфонов и умных домов до серверов и автомобильной электроники.

Благодаря базовому исполнению на уровне микроархитектуры ARMv8-A, вычислительные ядра Cortex-A75 обладают полной обратной совместимостью со всей экосистемой операционных систем, инструментов и приложений, разработанных для этой платформы, обеспечивая в то же время новые возможности для разработчиков систем с искусственным интеллектом.

Особенности ARM Cortex-A55

Экономичное процессорное ядро ARM Cortex-A55, по данным компании, обеспечивает лучшее в серии сочетание энергоэффективности и производительности в своем классе. Чип также базируется на технологиях DynamIQ и архитектуре ARMv8-A с поддержкой самых последних ее расширений в области машинного обучения.

Чип также базируется на технологиях DynamIQ и архитектуре ARMv8-A с поддержкой самых последних ее расширений в области машинного обучения.

Ядро Cortex-A55 обеспечивает на 18% лучшую производительность при работе с целыми числами, на 20% с числами с плавающей запятой, на 40% при расчетах NEON SIMD, на 15% при работе с JavaScript и на 200% при расчетах с большой нагрузкой на память при уменьшенном на 15% потреблении энергии по сравнению со своим предшественником Cortex-A53.

Ядро Cortex-A55 также обладает интегрированным конфигурируемым кэшем L2 на каждое ядро с более чем на 50% сниженной латентностью при обращении к подсистеме памяти. Ядра Cortex-A55 поддерживают кэш-память L3, распределяемой на кластер из 8 ядер.

На горизонте – новый мобильный флагман Qualcomm Snapdragon 845

В Сети уже появилась информация о том, что в Qualcomm работают над созданием следующего за Snapdragon 835 нового флагманского 8-ядерного процессора Snapdragon 845, выполненного на представленных сегодня ядрах Cortex-A75 и Cortex-A55. По аналогии с чипом Snapdragon 835, новый Snapdragon 845 также будет производиться с нормами 10-нм техпроцесса.

По аналогии с чипом Snapdragon 835, новый Snapdragon 845 также будет производиться с нормами 10-нм техпроцесса.

Для Snapdragon 845 ожидается рост производительности примерно на 30% при однопоточных вычислениях и ориентировочно на 70% при мультипоточных вычислениях.

Сроки официального анонса чипа Snapdragon 845 пока не известны, но аналитики прогнозируют это событие на конец 2017 г.

Первые смартфоны на DynamIQ: уже в 2018

По данным ARM, компания в последние четыре года поставила своим партнерам порядка 50 млрд 64-битных чипов, и в следующие пять лет планирует как минимум удвоить это число. Ожидается, что большинство из этих 100 млрд чипов, которые компания планирует поставить до 2021 года, будут ARM-ядрами на основе Dynamiq или из экономичных семейств Cortex-R и Cortext-M.

Планы ARM и партнеров по выпуску нового поколения смартфонов

Согласно заявлению ARM, компания работает с «многочисленными партнерами» над практическим внедрением технологий DynamIQ. По мнению представителей руководства ARM, микроархитектура Dynamiq может появиться во множестве различных смартфонов в ближайшие два года.

По мнению представителей руководства ARM, микроархитектура Dynamiq может появиться во множестве различных смартфонов в ближайшие два года.

Владимир Бахур

Cortex A57 — Архитектура — ARM A53 / A57 / T760 исследовано

Cortex A57 — Архитектура

Если взглянуть на высокопроизводительные ядра процессора Exynos 5433, у нас есть Cortex-A57, преемник более ранней ARMv7 Cortex-A15 от ARM.

Как первое высокопроизводительное ядро ARMv8 ARM, A57 выходит на интересный рынок. Первый год A57, вероятно, будет даже более успешным, чем A15, и все же это будет самая конкурентная среда в экосистеме ARM благодаря большему количеству лицензиатов архитектуры ARM, чем когда-либо прежде.Многие из этих лицензиатов работают в сфере серверов — такие компании, как AppliedMicro, которые пробиваются на рынке серверов — в то время как другие, такие как Apple и NVIDIA, использовали свои разработки на потребительском рынке, даже опередив A57 почти на год в этом случае. компании Apple. Тем не менее, в более узких рамках области Android A57 в настоящее время является процессором, который должен превзойти в 2015 году, и все, от Samsung до Qualcomm, лицензируют дизайн для своих высокопроизводительных процессоров.

компании Apple. Тем не менее, в более узких рамках области Android A57 в настоящее время является процессором, который должен превзойти в 2015 году, и все, от Samsung до Qualcomm, лицензируют дизайн для своих высокопроизводительных процессоров.

Если погрузиться в сам A57, то A57 во многих отношениях является прямым развитием и продолжением дизайна A15.Предназначенный для 28-нм и более новых узлов, A57, по сути, продолжает работу с того места, где остановился A15, представляя поддержку ARMv8 и одновременно повышая IPC ARM, общую однопоточную производительность и даже энергоэффективность. Под капотом ARM внесен ряд изменений для повышения эффективности, сохранив при этом другие элементы A15, которые все еще имеют смысл. Конечным результатом является что-то вроде «тактика» Intel, что означает, что мы рассматриваем что-то, что не является капитальным ремонтом архитектуры (например, Cyclone или Denver), но вводит ряд новых функций и оптимизаций.

A57 по своей сути представляет собой полностью вышедший из строя дизайн, что очень интересно контрастирует с NVIDIA Denver, которую мы рассмотрели на прошлой неделе. Это в основном норма для неортодоксальности NVIDIA, A57 представляет собой гораздо более традиционный процессор, который следует историческим тенденциям дизайна ARM и аналогичным образом предназначен для примерно того же дизайна, что и A15.

Это в основном норма для неортодоксальности NVIDIA, A57 представляет собой гораздо более традиционный процессор, который следует историческим тенденциям дизайна ARM и аналогичным образом предназначен для примерно того же дизайна, что и A15.

С точки зрения высокого уровня ARM делает довольно простой компромисс с точки зрения производительности и энергопотребления.A57 разработан, чтобы быть больше и производительнее, чем A15, но, в свою очередь, он также может потреблять больше энергии. Согласно внутренним прогнозам ARM для A57, он может улучшить IPC на 25-50% при увеличении энергопотребления на 20%, если будет построен на 28-нм узле. С точки зрения общей энергоэффективности это должно оставить A57 с приличным преимуществом над A15 благодаря увеличению производительности, опережающему увеличение энергопотребления.

Фактором подстановки во всем этом будет производственный узел, особенно темпераментные 20-нанометровые процессы.В то время как A57 может производиться на 28 нм, в соответствии с темпами технологии производства и необходимостью компенсировать его больший размер, первые потребительские конструкции A57, такие как Exynos 5433, производятся на 20 нм, в отличие от 28 нм для большинства конструкций A15. . Меньший процесс помогает сохранить размер A57 относительно небольшим — достаточно, чтобы легко разместить четыре ядра на SoC — и это означает, что мы получаем выигрыш в энергоэффективности, который достигается за счет меньшего технологического узла, добавляя к выигрышам в архитектуре A57.Однако это также означает, что прирост производительности при отгрузке SoC A57 будет зависеть от производственных факторов, таких как утечка и жизнеспособность более высоких тактовых частот, поэтому реальный прирост производительности по сравнению с A15 будет немного более изменчивым. В целом ARM настаивает на разработке более высокого уровня IPC, отчасти чтобы лучше контролировать эти факторы, поскольку более высокий уровень IPC позволит партнерам немного снизить тактовую частоту, а, следовательно, и энергопотребление.

. Меньший процесс помогает сохранить размер A57 относительно небольшим — достаточно, чтобы легко разместить четыре ядра на SoC — и это означает, что мы получаем выигрыш в энергоэффективности, который достигается за счет меньшего технологического узла, добавляя к выигрышам в архитектуре A57.Однако это также означает, что прирост производительности при отгрузке SoC A57 будет зависеть от производственных факторов, таких как утечка и жизнеспособность более высоких тактовых частот, поэтому реальный прирост производительности по сравнению с A15 будет немного более изменчивым. В целом ARM настаивает на разработке более высокого уровня IPC, отчасти чтобы лучше контролировать эти факторы, поскольку более высокий уровень IPC позволит партнерам немного снизить тактовую частоту, а, следовательно, и энергопотребление.

В любом случае поговорим о дизайне А57.Создавая A57, ARM сообщает нам, что их целью было спроектировать ЦП с учетом тех вычислительных нагрузок, которые они ожидают увидеть в ближайшие несколько лет, чтобы добиться максимальной реальной производительности от их конструкции. С этой целью ARM сообщает, что при планировании A57 они обнаружили, что мобильные рабочие нагрузки не так чувствительны к конвейеру инструкций, как когда-то, и в результате самые большие узкие места находятся не в самом конвейере, а скорее в его подпитке. Следовательно, конструкция A57 внесла меньше изменений в конвейер A15 и больше сфокусировалась на улучшении оборудования, поддерживающего конвейер, такого как функции выборки, декодирования и выполнения вне очереди.

С этой целью ARM сообщает, что при планировании A57 они обнаружили, что мобильные рабочие нагрузки не так чувствительны к конвейеру инструкций, как когда-то, и в результате самые большие узкие места находятся не в самом конвейере, а скорее в его подпитке. Следовательно, конструкция A57 внесла меньше изменений в конвейер A15 и больше сфокусировалась на улучшении оборудования, поддерживающего конвейер, такого как функции выборки, декодирования и выполнения вне очереди.

Изображение предоставлено Хиросигэ Гото

Итак, начиная с передней части, на этапе выборки ARM внесла множество мелких изменений. Кэш L1 был расширен с 32 КБ в A15 до 48 КБ в A57, и аналогичным образом его ассоциативность изменилась с двухсторонней на трехстороннюю. Общее увеличение кеша помогает повысить производительность, хотя, что, возможно, более важно, больший размер кеша инструкций помогает компенсировать больший размер 64-битных инструкций ARM. Между тем размер буфера Branch Target Buffer, который используется для хранения прошлых ветвей и лучшего прогнозирования будущих ветвей, увеличился вдвое, теперь он составляет 2K-4K. Между тем, на стороне данных кэш данных L1 остается неизменным — 32 КБ.

Между тем, на стороне данных кэш данных L1 остается неизменным — 32 КБ.

Кэш L2

, с другой стороны, настраивается для каждой SoC. A57 поддерживает размер кэша L2 от 512 КБ до 2 МБ, при этом кэш является ассоциативным по 16 параметрам. Каждое ядро A57 получает свой собственный интерфейс с кешем L2, поэтому на уровне интерфейса нет разделения полосы пропускания. Здесь также стоит упомянуть, что с A57 ARM теперь поддерживает несколько размеров страниц памяти сверх стандартного размера страницы памяти 4K, хотя большие страницы в основном предназначены для использования на сервере.

Для декодирования инструкций A57 сохраняет знакомую внешнюю часть декодера с 3 шириной. ARM всегда сталкивается с тонкой балансировкой размера декодера — более широкие декодеры физически больше — и, как и в случае с A57, это соответствует цели ARM — сосредоточиться на питании конвейера, а не на самом конвейере, поскольку ARM считает, что они еще не достигли предел 3-х ширины дорожки. Хотя этот декодер не стал шире, в него были внесены и другие изменения, направленные на повышение производительности и энергоэффективности. Особо следует отметить, что различные плоскости декодирования для каждого набора инструкций — Thumb, NEON, AArch64 и ARMv7 — теперь могут управляться по мощности, так что только необходимая плоскость декодирования включается, что помогает компенсировать затраты на поддержку четырех разных инструкций. форматы.Переименование регистров также было изменено на этапе декодирования, в частности, чтобы воспользоваться преимуществом того факта, что ARMv8 позволяет использовать карту плоских регистров, в отличие от ранее использовавшейся карты регистров с банковским разделением.

Хотя этот декодер не стал шире, в него были внесены и другие изменения, направленные на повышение производительности и энергоэффективности. Особо следует отметить, что различные плоскости декодирования для каждого набора инструкций — Thumb, NEON, AArch64 и ARMv7 — теперь могут управляться по мощности, так что только необходимая плоскость декодирования включается, что помогает компенсировать затраты на поддержку четырех разных инструкций. форматы.Переименование регистров также было изменено на этапе декодирования, в частности, чтобы воспользоваться преимуществом того факта, что ARMv8 позволяет использовать карту плоских регистров, в отличие от ранее использовавшейся карты регистров с банковским разделением.

Тем временем ARM также внесла несколько важных изменений на этапах отправки и выполнения инструкций. Следует отметить, что окно инструкций для OoOE снова увеличено в размере; ARM до сих пор не комментирует точный размер, но, как утверждается, может содержать более 128 инструкций для дальнейшего повышения производительности OoOE. В другом месте регистровый файл получил собственные улучшения, в первую очередь для совместимости с AArch64. Каждый сегмент размером 4 КБ файла регистров теперь можно настроить как 128 32-разрядных регистров или 64 64-разрядных регистров, что позволяет переключать относительно небольшие части файла в 64-разрядный режим и не тратить место на значения, которые не используются. t требуется регистр большего формата.

В другом месте регистровый файл получил собственные улучшения, в первую очередь для совместимости с AArch64. Каждый сегмент размером 4 КБ файла регистров теперь можно настроить как 128 32-разрядных регистров или 64 64-разрядных регистров, что позволяет переключать относительно небольшие части файла в 64-разрядный режим и не тратить место на значения, которые не используются. t требуется регистр большего формата.

| Сравнение ядер процессора ARM | ||||||

| Cortex-A15 | Cortex-A57 | |||||

| ARM ISA | ARMv7 (32-разрядная версия) | ARMv8 (32/64-бит) | ||||

| Ширина декодера | 3 микрооператора | 3 микрооператора | ||||

| Длина трубопровода | 18 ступеней | 18 ступеней | ||||

| Штраф за неправильное прогнозирование филиала | 15 циклов | 15 циклов? | ||||

| Целое Сложить | 2 | 2 | ||||

| Целое число Mul | 1 | 1 | ||||

| Единицы загрузки / хранения | 1 + 1 (выделенный аккредитив) | 1 + 1 (выделенный аккредитив) | ||||

| Филиалы | 1 | 1 | ||||

| ФП / НЕОН АЛУ | 2×64-бит | 2×128 бит | ||||

| Кэш L1 | 32 КБ I $ + 32 КБ D $ | 48 КБ I $ + 32 КБ D $ | ||||

| Кэш L2 | 512 КБ — 4 МБ | 512 КБ — 2 МБ | ||||

Что касается самого конвейера, как для целочисленных, так и для вычислений с плавающей запятой были внесены некоторые улучшения из соображений производительности и 64-битной совместимости. Хотя ARM не очень подробно описывает, как это устроено, у них есть целочисленные пути данных как для 32-битного, так и для 64-битного исполнения, что позволяет им запускать 64-битный путь только тогда, когда он им нужен. Дополнительные пути создают некоторую сложность, но отдача от одного 64-битного пути заключается в том, что дополнительные транзисторы не запускаются, а дополнительная мощность сжигается только для выполнения 32-битного кода.

Хотя ARM не очень подробно описывает, как это устроено, у них есть целочисленные пути данных как для 32-битного, так и для 64-битного исполнения, что позволяет им запускать 64-битный путь только тогда, когда он им нужен. Дополнительные пути создают некоторую сложность, но отдача от одного 64-битного пути заключается в том, что дополнительные транзисторы не запускаются, а дополнительная мощность сжигается только для выполнения 32-битного кода.

С другой стороны, блоки с плавающей запятой / NEON намного шире, увеличиваясь вдвое с 64 до 128 бит и, в свою очередь, потенциально удваивая производительность NEON (когда блоки FP могут быть полностью запитаны).В отличие от целочисленного конвейера, здесь нет отдельных путей для разных размеров данных, но ARM сообщает нам, что они работали над некоторыми дополнительными оптимизациями энергопотребления, чтобы снизить энергопотребление. Эти устройства теперь также соответствуют IEEE-754-2008 при выполнении кода ARMv8. Для потребительского рынка это не оказывает большого влияния, но является важным отличием для рынка серверов, который является еще одной областью, в которой ARM надеется внедрить A57 теперь, когда у них есть возможности 64-битной адресации. Наконец, A57 поддерживает дополнительный блок ускорителя криптографии на этом этапе для повышения производительности AES и SHA1 / SHA2-256.

Наконец, A57 поддерживает дополнительный блок ускорителя криптографии на этом этапе для повышения производительности AES и SHA1 / SHA2-256.

И последнее, но не менее важное: блоки загрузки / сохранения также научились нескольким новым приемам. Загрузки теперь могут обходить однозначные магазины, что дает прирост производительности еще примерно на 5%. В то же время на этом этапе теперь существует предсказатель зависимости, в первую очередь, чтобы помочь улучшить производительность OoOE за счет предотвращения чрезмерных спекуляций A57 и иного ущерба производительности во время спекулятивных операций с памятью.

Между тем, быстрый взгляд на задержку памяти и пропускную способность ядер A57 в Exynos 5433 обнаруживает неожиданное соединение.Задержка практически не изменилась по сравнению с A15 через кеш L2, но как только она попадает в основную память, задержка увеличивается почти на 40 нс. С другой стороны, пропускная способность памяти у A57 стабильно лучше, даже в кеш-памяти. Что касается задержки, это может быть связано с дизайнерским решением Samsung в самой SoC. Между тем улучшенная полоса пропускания, вероятно, является следствием различных усовершенствований A57, направленных на повышение пропускной способности ядер ЦП.

Что касается задержки, это может быть связано с дизайнерским решением Samsung в самой SoC. Между тем улучшенная полоса пропускания, вероятно, является следствием различных усовершенствований A57, направленных на повышение пропускной способности ядер ЦП.

ARM принесли им плохую репутацию, когда дело доходит до производительности памяти, но то, что мы видим здесь, может быть грубым искажением реальной производительности.Чтобы понять, как получаются эти цифры, нам нужно посмотреть, как процессор подключен к межсоединениям SoC и контроллерам памяти. ARM, в отличие от разработок Apple или NVIDIA, использует отдельные порты данных для чтения и записи в своей структуре. На уровне кластера это двойной 128-битный интерфейс (один для чтения, один для записи), который подключается к соответствующим портам контроллеров памяти SoC через архитектуру кроссбара CCI (Cache Coherent Interconnect). На Exynos 5430 и 5433 CCI работает на половине частоты DRAM, что означает 412. 5 МГц для вышеупомянутых SoC. Это приводит к максимальной физической пропускной способности 6,6 ГБ / с в каждом направлении.

5 МГц для вышеупомянутых SoC. Это приводит к максимальной физической пропускной способности 6,6 ГБ / с в каждом направлении.

Большинство сегодняшних синтетических тестов демонстрируют только полосу пропускания, измеренную в любом направлении, что дает ARM явный недостаток. Общая достижимая пропускная способность может достигать этих показателей вдвое. Фактически, когда мы выполняем одновременные тесты чтения и записи (многопоточные на двух процессорах), мы измеряем показатели пропускной способности, достигая теоретических пиков контроллеров памяти на уровне 13.2 ГБ / с. Интересно, что похоже, что ARM использует ту же настройку для кэша L2, поскольку пропускная способность там также удваивается до 25 ГБ / с для 5430 A15 и 27,5 ГБ / с для 5433 кластеров A57.

Хороший вопрос, почему ARM предпочитает такую конфигурацию. Мы подозреваем, что конструкция может иметь преимущества по мощности или задержке, но мы не можем быть в этом уверены. В целом, это должно иметь меньшее влияние в реальных сценариях, как показывают тесты. Сценарии использования, когда вычисления являются либо чтением, либо записью, должны появляться только в таких сценариях, как кодирование видео или распаковка текстур, таких как загрузка ресурсов видеоигр, причем первое не является реальной проблемой в мобильном пространстве из-за оборудования с фиксированной функцией, предназначенного для задание.

Сценарии использования, когда вычисления являются либо чтением, либо записью, должны появляться только в таких сценариях, как кодирование видео или распаковка текстур, таких как загрузка ресурсов видеоигр, причем первое не является реальной проблемой в мобильном пространстве из-за оборудования с фиксированной функцией, предназначенного для задание.

В целом, собранный A57 является естественным шагом вперед по сравнению с A15, как с точки зрения основного дизайна, так и с точки зрения общей архитектуры. Здесь нет единого значительного изменения для повышения производительности — и на самом деле конвейер команд не сильно отличается по выполнению — но, сосредоточившись на создании для выполнения AArch64 и улучшениях, чтобы лучше питать эти конвейеры, ARM ожидает, что они могут получить значительный Повышение IPC по сравнению с A15. В сочетании с 20-нм и более поздними 16-нм / 14-нм процессами ARM и их партнеры надеются далеко продвинуть A57, хотя, учитывая тот факт, что A15 и так потреблял немного энергии в телефонах, будет интересно посмотреть, сколько из этих преимуществ процесса тратится на производительность (тактовые частоты) и сколько уходит на снижение энергопотребления.

Между тем, в долгосрочных планах ARM по поводу A57 также содержится призыв к тому, чтобы он работал вдвойне как серверный ЦП. Благодаря 64-битному пространству памяти приложения, работающие на A57, могут, наконец, адресовать всю необходимую им память (а затем и некоторые), поэтому в сочетании с увеличением IPC ARM надеется взломать рынок серверов так, как никогда не удавалось ранним усилиям A15. . Среди первых компаний, поставляющих серверные ЦП, будет AMD и их A1100, поэтому будет интересно посмотреть, как A57 будет играть на рынке серверов в следующем году.

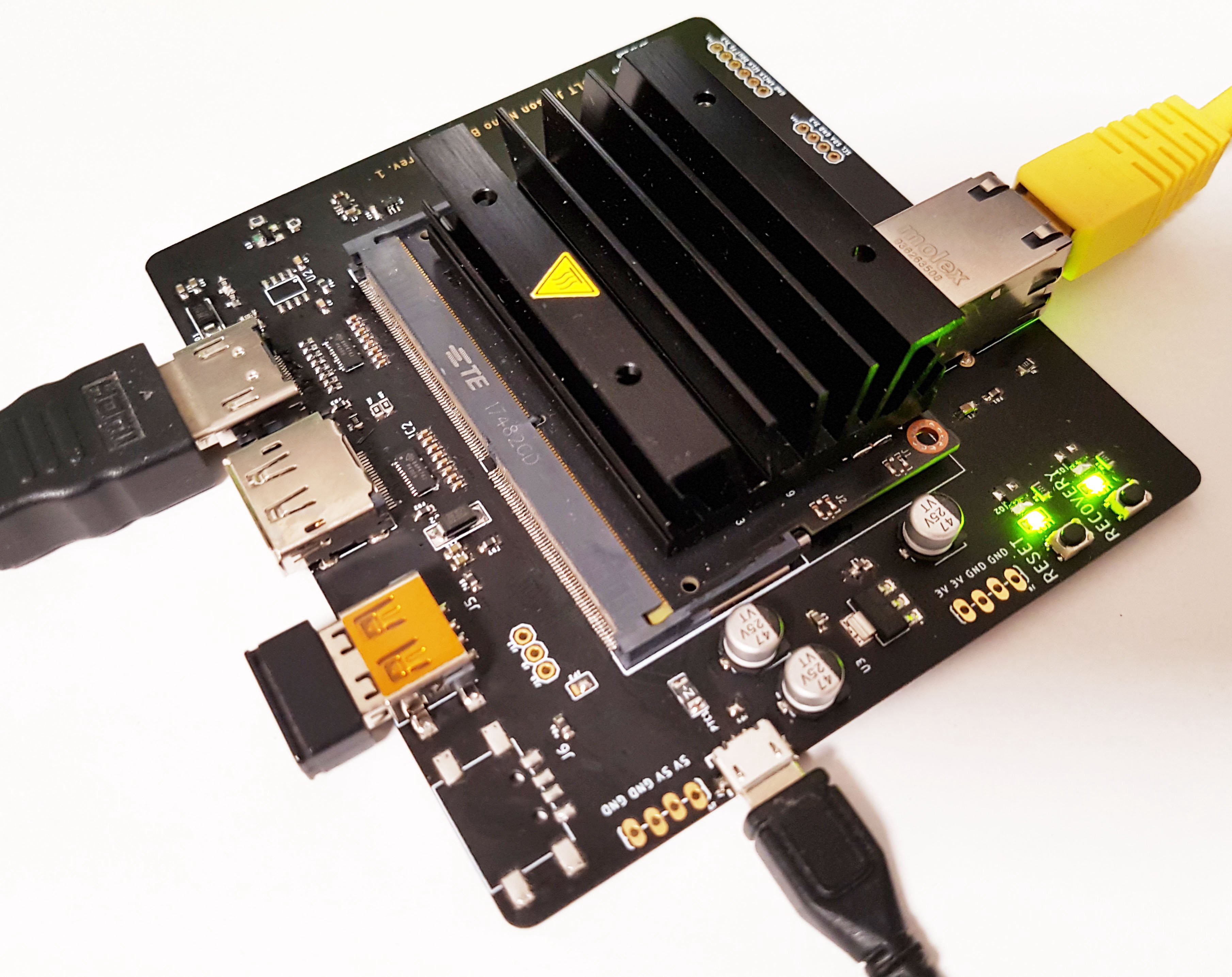

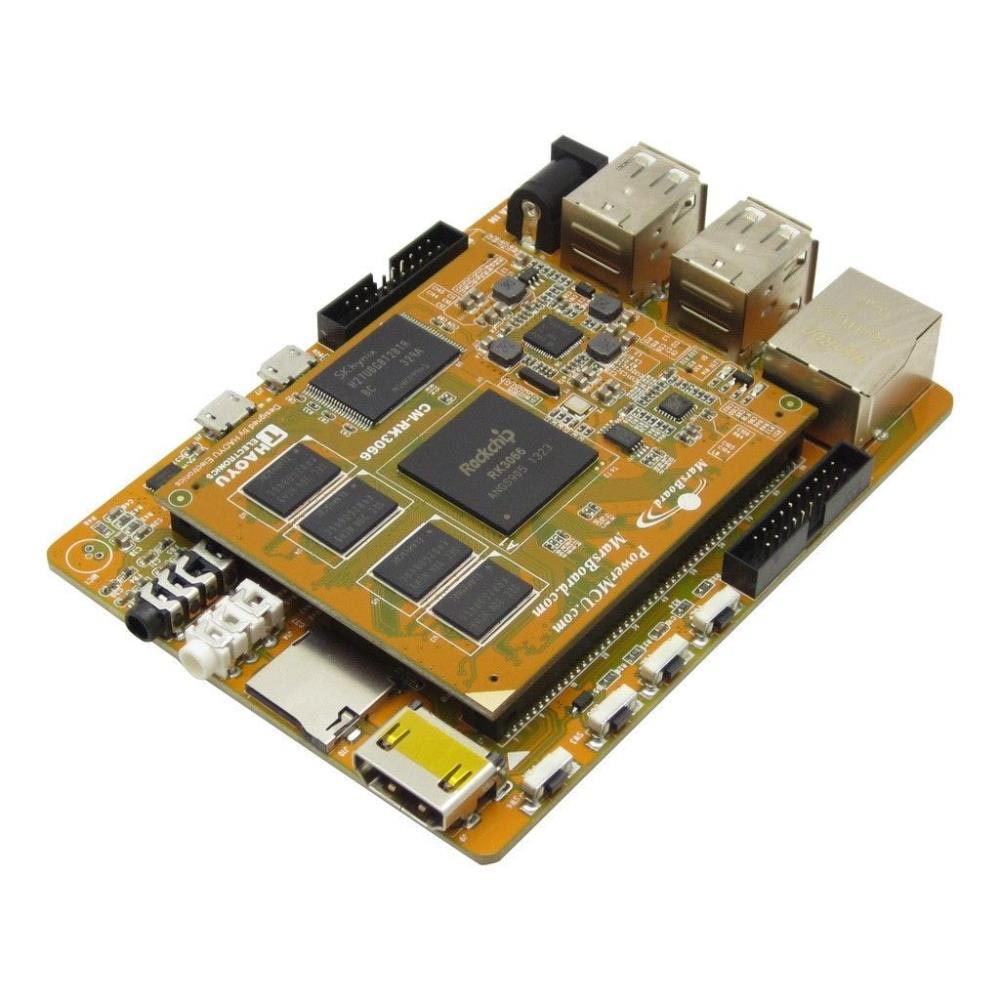

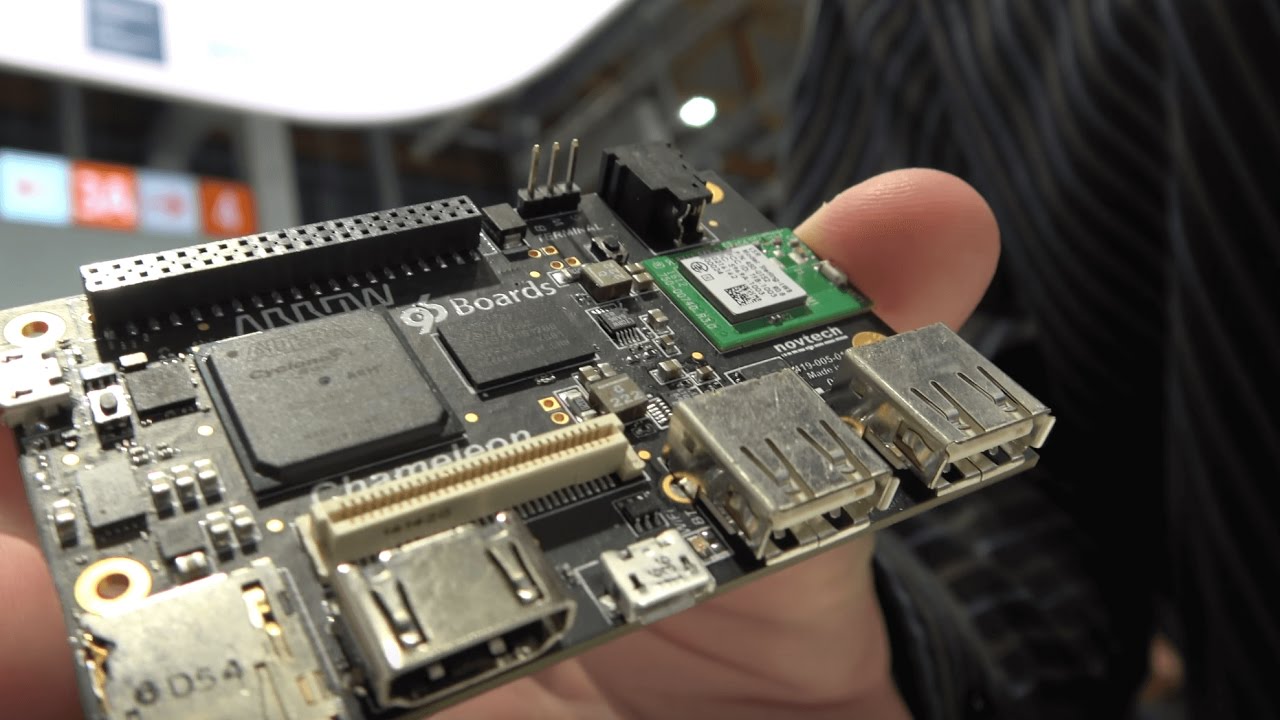

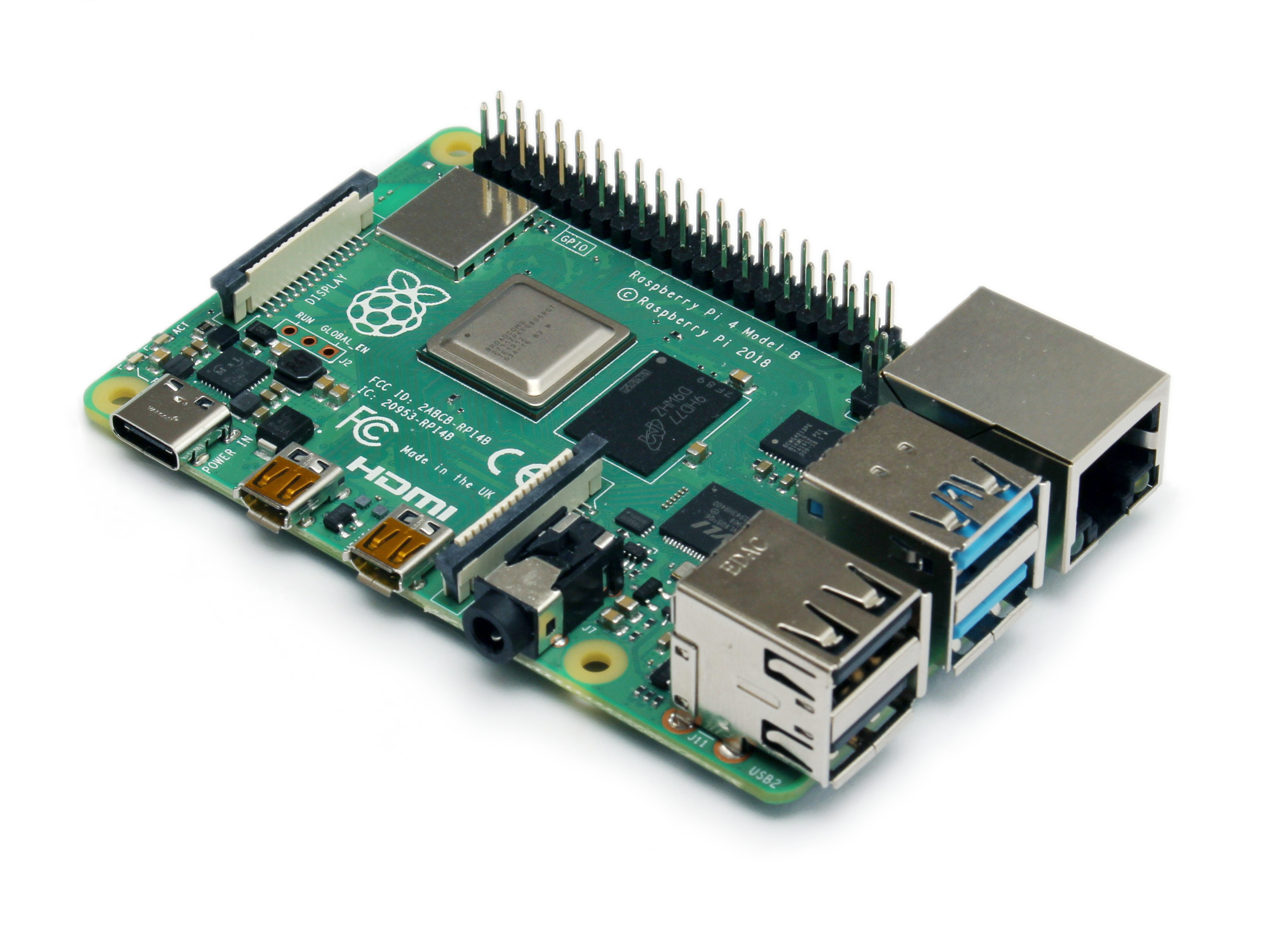

NVIDIA Jetson Nano — Модуль с процессором ARM Cortex A57 1,43 ГГц, 4 ГБ ОЗУ, Nvidia Maxwell

Подробнее

Описание

Модуль NVIDIA с процессором ARM Cortex A57 , работающим на частоте 1,43 ГГц и графической системой Maxwell состоящий из 128 ядер, поддерживающих технологию CUDA. Система поддерживает 4 ГБ оперативной памяти DDR4, Ethernet, HDMI и интерфейс MIPI-CSI. Пакет разработан специально для графического дизайна и обработки очень больших объемов данных.Он позволяет вам ознакомиться с техникой программирования графических процессоров.

Пакет разработан специально для графического дизайна и обработки очень больших объемов данных.Он позволяет вам ознакомиться с техникой программирования графических процессоров.

Модуль Jetson Nano — самое маленькое устройство на платформе Jetson. Он обеспечивает производительность для с современными AI-нагрузками в небольшом энергосберегающем формате. Обеспечивает 472 GFLOP вычислительной мощности для быстрой работы с современными алгоритмами SI. Он может запускать несколько нейронных сетей параллельно и одновременно обрабатывать данные с нескольких датчиков высокого разрешения, что делает его идеальным решением для базовых сетевых видеорегистраторов (NVR), домашних роботов и интеллектуальных шлюзов с полными аналитическими возможностями.

Nvidia предоставляет на вашем сайте (https://courses.nvidia.com/courses/course-v1:DLI+C-RX-02+V1/about) бесплатный курс искусственного интеллекта на базе NVIDIA Jetson Nano.

Модуль также доступен в версии с базовой платой в виде набора для разработки.

Видео-презентация

Характеристики

- Графический процессор NVIDIA Maxwell ™ со 128 ядрами NVIDIA CUDA®

- ЦП Четырехъядерный процессор ARM® Cortex®-A57 MPCore

- 4 ГБ 64-битной памяти LPDDR4

- Запоминающее устройство 16 ГБ Flash eMMC 5.1 память

- 1x 4K @ 30 кодирование видео (HEVC)

- 1x 4K @ 60 видео декодирование (HEVC)

- Камера 12 полос (3×4 или 4×2) MIPI CSI-2 DPHY 1.1 (1,5 Гбит / с)

- Подключение Gigabit Ethernet и соединительные разъемы

- Дисплей HDMI 2.0 или DP1.2 | eDP 1.4 DSI (1×2) 2 одновременно

- UPHY 1 x1 / 2/4 PCIE, 1x USB 3.0, 3x USB 2.0

- Порты ввода / вывода 3x UART, 2x SPI, 2x I2S, 4x I2C, GPIO

- 260-контактный краевой соединитель

- Размеры: 69.6 x 45 мм

Производители микросхем пропускают Cortex-A57, каковы последствия?

Следует помнить об одном. Cortex-A57 ни в коем случае не является новым дизайном. Фактически, об этом было объявлено в октябре 2012 года, а доступность намечена на 2014 год. Как мы все знаем, развертывание было не очень гладким, и единственной потребительской частью Cortex-A57, готовой к отправке в 2014 году, был Exynos 7410 из знаменитого Galaxy Note 4 . За ним последовали Snapdragon 810 и Exynos 7420, которые вряд ли нуждаются в представлении.

Cortex-A57 идет почти по графику, так что в этом такого?

Хотя это правда, что Cortex-A57 был почти вовремя, нас беспокоит не график развертывания, а отсутствие дизайна. Для продукта, анонсированного 30 месяцев назад, у него относительно мало побед в дизайне, и это не изменится. Фактически, на данный момент более или менее очевидно, что ряд крупных производителей SoC вообще откажутся от него.

MediaTek недавно анонсировала свою первую часть планшета Cortex-A72, и к концу года компания планирует внедрить Cortex-A72 в SoC для смартфонов.

Другой относительно крупный игрок, Huawei HiSilicon, похоже, также пропускает A57. Грядущие компоненты Kirin 940 и Kirin 950 должны получить вместо этого ядра Cortex-A72. Это еще не все, потому что у некоторых устройств, таких как Nvidia, есть собственные ядра. Ожидается, что Qualcomm также будет использовать специальное ядро в Snapdragon 820, в то время как слухи о пользовательском ядре Samsung ARMv8 ходят уже много лет.

Грядущие компоненты Kirin 940 и Kirin 950 должны получить вместо этого ядра Cortex-A72. Это еще не все, потому что у некоторых устройств, таких как Nvidia, есть собственные ядра. Ожидается, что Qualcomm также будет использовать специальное ядро в Snapdragon 820, в то время как слухи о пользовательском ядре Samsung ARMv8 ходят уже много лет.

Тепловой барьер и экономическая остановка ARM SoC evolution

Есть несколько возможных объяснений отсутствия преимуществ дизайна Cortex-A57, и они связаны с физикой и экономикой.

С технической точки зрения, A57 требует слишком много усилий и не дает большого прироста производительности. Используемый в восьмиядерном процессоре big.LITTLE, Cortex-A57 требует использования четырех дополнительных ядер Cortex-A53, большого графического процессора, соответствующего его потенциалу, и обычного 4G-модема, который можно найти на высокопроизводительных устройствах. Все это приводит к относительно большому кристаллу с большим количеством транзисторов, особенно на планарных узлах.

Компоновка Snapdragon 810 — обратите внимание на размер графического процессора, модема и других модулей.Процессор не выглядит слишком большим, но, в отличие от других модулей, он всегда в той или иной степени загружен. Под нагрузкой ЦП и графический процессор ограничены тепловой оболочкой, чего нельзя сказать о остальной части чипа.

Проблемы с термической эффективностью и энергоэффективностью — еще одна проблема, поскольку такой чип просто не сможет полностью раскрыть свой потенциал на планарных узлах, если потребители внезапно не заинтересуются покупкой больших и толстых телефонов с большими радиаторами и батареями.

Cortex-A57 действительно не вариант на 28 нм.Однако его можно успешно развернуть на узлах FinFET 20 и 14/16 нм. Это делает его непривлекательным для всех устройств, кроме самых дорогих, поскольку это тщательно продуманный дизайн, требующий использования дорогостоящего передового узла. К тому времени, когда FinFET созреет и затраты на литейное производство снизятся, ARM уже будет иметь другой дизайн, который займет его место — Cortex-A72.

Cortex-A57 в сравнении с Cortex-A72

Cortex-A72 был анонсирован в феврале 2015 года, и ARM ожидает увидеть его в коммерчески доступных устройствах к началу 2016 года.Некоторые производители микросхем хотели бы получить его еще раньше, даже используя его на 28-нм узлах, а не на узлах FinFET, для которых он изначально был разработан.

В некоторых отношениях Cortex-A57 разделил судьбу своего предшественника, Cortex-A15. Последний дебютировал на 32-нм компонентах Samsung, но из-за проблем с температурой ядро не использовалось широко, пока 28-нм узлы не стали доступными (и дешевыми). Однако все это было вопросом удачного момента — A15 прибыл как раз вовремя для 28 нм, в то время как A57 как бы упустил свое окно возможностей.

Хуже того, в прошлом году в Android 5.0 появилась поддержка 64-битных систем, что побудило Google использовать Nvidia для своего планшета Nexus 9, поскольку его ядро Denver было практически единственным 64-битным «большим ядром» ARM, которое Google мог использовать. Потребители могли получить доступные устройства Cortex-A53 с поддержкой 64-разрядной версии, но не могли получить флагманские 64-разрядные устройства. Возможно, это несущественное различие для среднего читателя Fudzilla, поскольку технические энтузиасты знают, что поддержка 64-битной версии просто не была актуальной в 2014 году (и до сих пор не актуальна). Однако было намного проще продавать 64-битные компоненты на основе небольших ядер, чем большие 32-битные ядра.

Потребители могли получить доступные устройства Cortex-A53 с поддержкой 64-разрядной версии, но не могли получить флагманские 64-разрядные устройства. Возможно, это несущественное различие для среднего читателя Fudzilla, поскольку технические энтузиасты знают, что поддержка 64-битной версии просто не была актуальной в 2014 году (и до сих пор не актуальна). Однако было намного проще продавать 64-битные компоненты на основе небольших ядер, чем большие 32-битные ядра.

Итак, получит ли Cortex-A72 больше дизайнерских побед, чем A57? Неужели он намного лучше А57?

Лично я склонен сказать, что Cortex-A72 будет намного более успешным, не в силу его дизайна, а благодаря лучшему таймингу и ограниченной привлекательности Cortex-A57. ARM не раскрыла много информации об A72, кроме как заявить, что новое ядро будет значительно более эффективным, чем A15 и A57, но его числа основывались на разных узлах (28 нм для A15, 20 нм для A57, 16 нм для A72 ).

Мы просто еще мало что знаем о Cortex-A72, и пока рано делать выводы.

Что это означает для 2015 года?

В дальнейшем отсутствие жизнеспособного 64-битного ядра ARM для среднего уровня и даже некоторых высокопроизводительных устройств на 28-нм техпроцессе неизбежно будет иметь ряд последствий для рынка SoC для смартфонов и дизайна смартфонов в целом.

Cortex-A57 просто не будет использоваться во многих устройствах, так как он имеет смысл только на узлах FinFET 20 и 14/16 нм, поэтому у производителей микросхем будет только один выбор — выпускать больше деталей Cortex-A53 на более высоких тактовых частотах, с более быстрыми графическими процессорами и лучшей поддержкой LTE.В отличие от прошлого года, у них нет возможности использовать четыре ядра (A15, A17, A9 и A7), поскольку они могут использовать только ядра A57 и A53, но A57 просто не работает для большинства сегментов рынка. Cortex-A17 выглядит очень заманчивой альтернативой, и MediaTek уже использовал его для некоторых частей, но это 32-битное ядро, расположенное ниже Cortex-A15 и Cortex-A57. В то время как A17 является хорошим исполнителем с хорошим соотношением цена / производительность, потребителям требуются простые и простые 64-битные чипы.

В то время как A17 является хорошим исполнителем с хорошим соотношением цена / производительность, потребителям требуются простые и простые 64-битные чипы.

Это, очевидно, приведет к стиранию границы между устройствами низкого и среднего уровня, поскольку многие из них должны будут использовать аналогичные кремниевые компоненты — потребители получат ядра A53, независимо от того, покупают ли они телефон за 100 долларов или телефон за 300 долларов.

Такие компании, как Huawei и MediaTek, уже намекнули или раскрыли чипы, предназначенные для решения этой проблемы, путем включения четырех ядер A53 на более высоких тактовых частотах (Huawei называет их A53e или улучшенными ядрами). Эти ядра будут поддерживаться четырьмя более медленными ядрами A53, и Qualcomm уже использует такую компоновку в Snapdragon 615.

Когда ARM анонсировала Cortex-A17 в феврале прошлого года, компания дала понять, что 28 нм обеспечат «наибольшее количество транзисторов на доллар» — это все еще так.

Маловероятно, что какой-либо из этих чипов будет производиться с использованием дорогих 20-нм узлов или узлов FinFET, по крайней мере, в обозримом будущем (по крайней мере, четыре квартала, возможно, пять из-за высокого спроса на флагманские чипы в первом квартале 2016 года). Емкость ограничена, стоимость будет оставаться непомерно высокой в течение нескольких месяцев, а 28-нм техпроцесс отлично подходит для деталей Cortex-A53. В результате разработчики SoC уже удваивают пропускную способность 28 нм, поскольку очевидно, что узел должен будет выйти на рынок в 2016 году.

Итак, вот прогнозы Fudzilla для SoC и смартфонов 2015 года:

- Жестокая конкуренция в области 28-нм SoC низкого и среднего уровня, каждая копейка на счету.

- Использование восьмиъядерных процессоров Cortex-A53 в некоторых флагманских и квази-флагманских устройствах, особенно в Китае.

- Ограниченный спрос на продукты Cortex-A57.

- Отсутствие проектов Cortex-A17 (необходима 64-битная альтернатива).

- Повышается в четвертом квартале 2015 года и в последующий период, поскольку в продажу поступают Cortex-A72 и пользовательские ядра.

- Еще больше 28-нм конструкций Cortex-A53 с улучшенными ядрами, обновленной графикой и модемами.

- Производители смартфонов должны будут разработать новые способы дифференциации не-флагманских продуктов.

- Скорее всего, упадут цены на устройства среднего класса.

- Нет деталей Cortex-A53 на узлах 20 нм или 14/16 нм. Узел

- , 28 нм, будет продолжать доминировать в мобильной индустрии как минимум 4 квартала и начнет сокращаться во второй половине 2016 года.

- Мягкий спрос на узлы FinFET ограниченной емкости в течение следующих 2-3 кварталов из-за отсутствия конструкций Cortex-A57.

- Intel могла бы извлечь выгоду из застопорившейся разработки ARM.

Есть несколько предостережений. Некоторые микросхемы с малым ядром могут появиться на новом узле в конце этого года, но мы говорим о нишевых продуктах (возможно, о некоторых носимых SoC или собственных разработках для определенных смартфонов с малым объемом). Если спрос на детали FinFET окажется намного ниже, чем ожидалось, возможно, что литейным предприятиям придется снизить цены по мере того, как появится больше мощностей, но это зависит от целого ряда факторов, и мы сомневаемся, что кто-то сможет сделать хороший прогноз по крайней мере в следующем квартале или около того.

Если спрос на детали FinFET окажется намного ниже, чем ожидалось, возможно, что литейным предприятиям придется снизить цены по мере того, как появится больше мощностей, но это зависит от целого ряда факторов, и мы сомневаемся, что кто-то сможет сделать хороший прогноз по крайней мере в следующем квартале или около того.

2015 год не будет очень насыщенным для рынка ARM SoC, но он может оказаться гонкой на дно.

Cortex-A57 переводит ARM на 64-разрядную версию, войдет в серверную комнату в 2014 году

Этот сайт может получать партнерские комиссии за ссылки на этой странице. Условия эксплуатации. Ранее на этой неделе ARM раскрыла подробности о своих процессорах SoC A57 и A53 следующего поколения.Преемники Cortex-A15 текущего поколения, серия Cortex-A50 привносит архитектуру ARM в 64-битный процессор, который может использоваться в гораздо более широком диапазоне устройств — от смартфонов до рабочих лошадок центров обработки данных. В частности, Cortex-A57 является флагманом этой серии и станет серьезным выходом на рынок серверов.

В частности, Cortex-A57 является флагманом этой серии и станет серьезным выходом на рынок серверов.

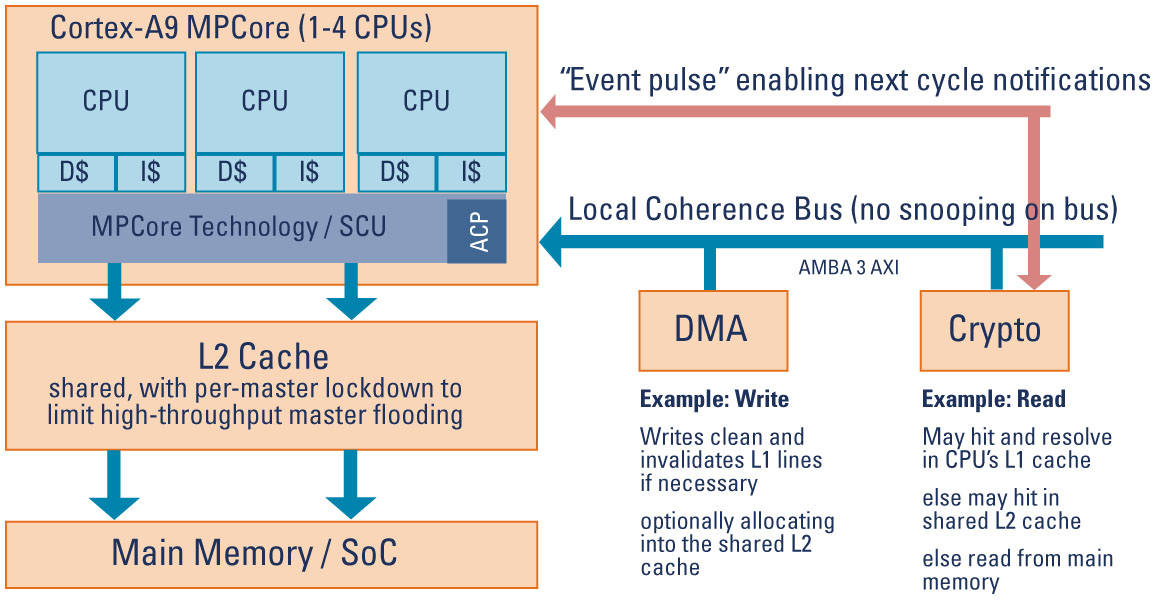

Cortex-A57 — это, по сути, Cortex-A15 с 64-битными регистрами, 64-битной адресацией памяти и различными низкоуровневыми настройками. Наряду с исправлением ошибок и аппаратной поддержкой TrustZone, улучшения хорошо подходят для использования на серверах.Процессор поддерживает ARMv7A и ARMv8 ISA (что означает, что он может запускать как 32-битный, так и 64-битный код), виртуальную 44-битную физическую адресацию и поддержку аппаратной виртуализации.

Кроме того, это трехрядный дизайн, состоящий из 8 выпусков и более 15 этапов конвейера инструкций. В архитектуре ARM следующего поколения также присутствует более широкий механизм NEON SIMD и модуль с плавающей запятой двойной точности IEEE-754. A57 имеет кэш данных 48 КБ, кэш инструкций 32 КБ и кэш L2 (512–2 МБ), совместно используемый четырьмя ядрами ЦП.Если принять во внимание когерентную сеть кэш-памяти CCN-504, до 16 ядер ЦП могут получить доступ от 8 до 16 МБ к общей кэш-памяти третьего уровня (в зависимости от реализации).

Межсоединение также связывает ядра с контроллером памяти, сетевым интерфейсом и виртуальным вводом-выводом, например USB, SATA, DSP (процессоры цифровых сигналов) и PCIe. ARM предоставила поддержку своей конфигурации big.LITTLE, которая позволяет объединять несколько процессоров Cortex-A57 и Cortex-A53, подключенных к когерентной сети кеш-памяти CCN-400.Это позволяет устройству динамически использовать либо A57 с более высокой производительностью, либо A53 с низким энергопотреблением (производительность аналогична 32-разрядному Cortex-A9 с последовательным 8-ступенчатым конвейером) в зависимости от текущей рабочей нагрузки.

Что касается производительности, то Cortex-A57 будет примерно в три раза быстрее, чем смартфоны текущего поколения (на базе Cortex-A9), с таким же энергопотреблением, что и более старые чипы (при прочих равных). ARM ожидает, что чипы будут работать с более высокими частотами, чем когда-либо прежде, и дополнительный графический процессор Mali T67x может быть соединен с ядрами процессора. Будут поддерживаться технологические узлы от 28 до 14 нм, и в 2014 году вы должны увидеть чипы, использующие технологические узлы от 28 до 20 нм.

Будут поддерживаться технологические узлы от 28 до 14 нм, и в 2014 году вы должны увидеть чипы, использующие технологические узлы от 28 до 20 нм.

По сравнению с SoC Cortex-A15, который только начинает появляться в планшетах и Chromebook, A57 предлагает прирост производительности примерно на 20%. Дальнейшее улучшение скорости будет реализовано при работе с 64-битным программным обеспечением, а также при доступе к большему объему оперативной памяти. Изменения в архитектуре вместе с меньшим производственным процессом (и сопутствующим более высокими тактовыми частотами) несут ответственность за повышение производительности.

Прямо сейчас Cortex-A15 зарекомендовал себя достойным конкурентом Atom, особенно старым чипам. По мере того как Intel переходит к внеплановому исполнению (OoOE) со своими будущими процессорами Atom, а также использует преимущества своего производственного узла для развертывания все меньших процессоров с большим количеством ядер, будет интересно посмотреть, где находится Cortex-A57.

Помимо чистой производительности, Cortex-A57 представляет собой интересный вариант серверного чипа от ARM. Это расширит возможности серверов на базе ARM, позволяя им брать на себя более серьезные рабочие нагрузки и «большие данные» в центрах обработки данных, не отказываясь от своей директивы о низком энергопотреблении.

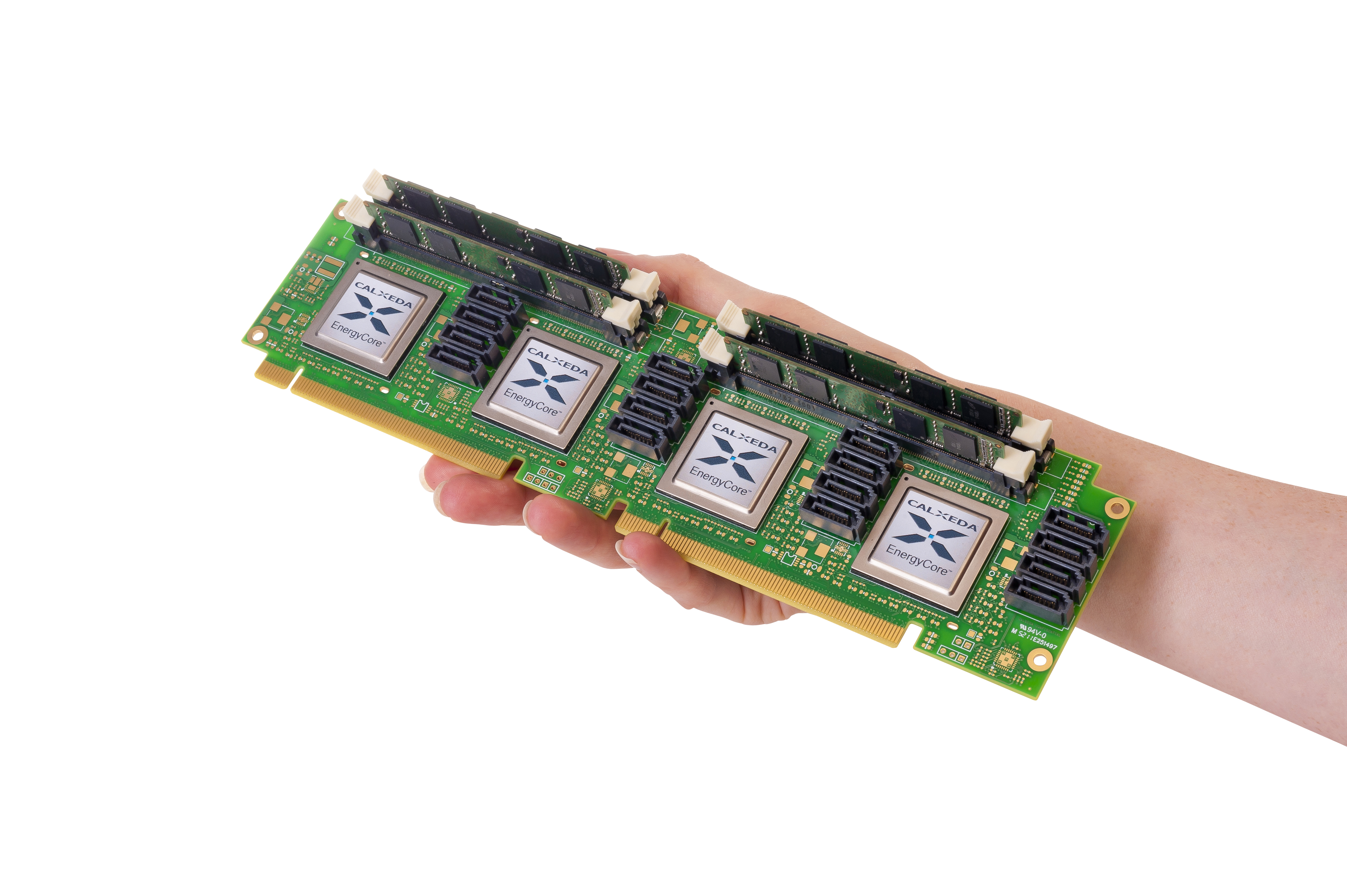

Немало компаний заявили о намерении производить серверное оборудование на базе нового процессора Cortex-A57. AMD и Calxeda говорили об использовании SoC следующего поколения ARM для питания серверов с высокой плотностью размещения, предназначенных для размещения общедоступных и частных облачных сервисов (таких как веб-хостинг, облачные сервисы, анализ больших данных и внутренние корпоративные приложения) с относительно небольшими затратами. мощность.

Серверная карта с несколькими SoC от Calxeda. В планах компании — обеспечить будущие кластеры серверов ARM процессорами серии Cortex-A50.

Broadcom, Samsung и STMicroelectronics также планируют выпуск оборудования на базе A57 и A53. Что касается программного обеспечения, то популярные разработчики дистрибутивов Linux Red Hat и Canonical являются основными компаниями, обеспечивающими поддержку 64-битного программного обеспечения ARM, что должно гарантировать, что серверы на базе Linux будут готовы к работе на процессорах следующего поколения.

Что касается программного обеспечения, то популярные разработчики дистрибутивов Linux Red Hat и Canonical являются основными компаниями, обеспечивающими поддержку 64-битного программного обеспечения ARM, что должно гарантировать, что серверы на базе Linux будут готовы к работе на процессорах следующего поколения.

имеют конкурентные шансы на уровне центров обработки данных, где стойки с серверами, потребляющими энергию, могут привести к огромным счетам за электроэнергию, а эффективность производительности на ватт имеет важное значение для компаний, предлагающих облачные услуги, зарабатывающих деньги.2014 год, безусловно, будет интересным годом для серверов с низким энергопотреблением, поскольку это первый крупный набег архитектуры ARM на рынок серверов.

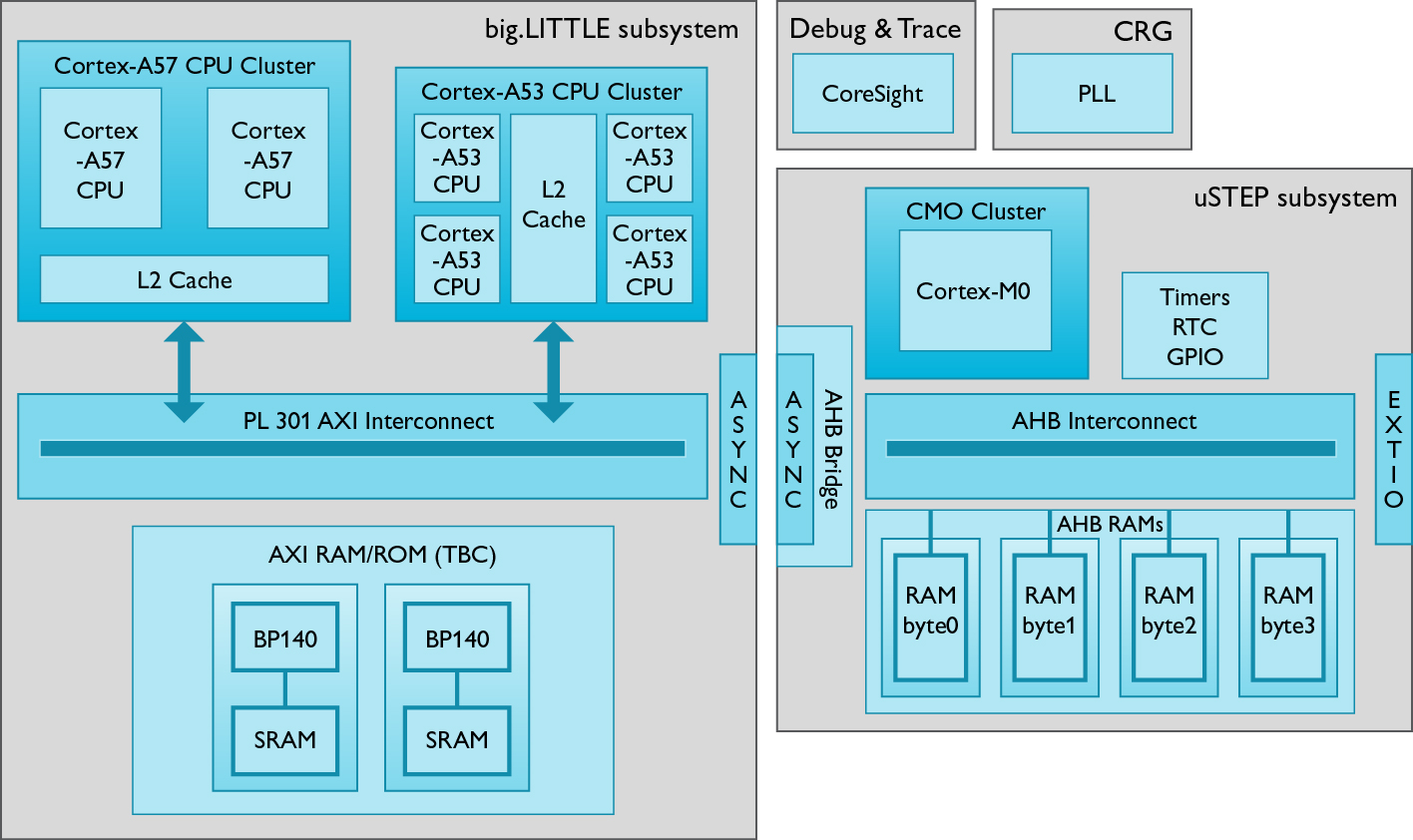

Подробное описание архитектуры ARM Cortex-A72 — Tom’s Hardware

Введение

ARM анонсировала Cortex-A72, высококлассный преемник Cortex-A57, в начале 2015 года. Уже более года поставщики SoC работают над интеграцией нового ядра ЦП в свои продукты. Теперь, когда появление мобильных устройств, использующих A72, неизбежно, самое время обсудить, что заставляет флагманский процессор ARM работать.

Теперь, когда появление мобильных устройств, использующих A72, неизбежно, самое время обсудить, что заставляет флагманский процессор ARM работать.

Выпустив A57, ARM стремилась расширить рынок своих процессоров за пределы мобильных устройств и выйти на рынок серверов с низким энергопотреблением. Использование единой архитектуры ЦП как для смартфонов, так и для серверов звучит неразумно, но, по словам Майка Филиппо из ARM, ведущего архитектора A72, высокопроизводительные мобильные рабочие нагрузки оказывают сильное давление на кеши, прогнозирование ветвлений и резервный буфер трансляции (TLB). , которые также важны для серверных нагрузок. В то время как A57, казалось, был склонен к серверным приложениям из-за его энергопотребления, A72 использует более сбалансированный подход и выглядит более подходящим для мобильных устройств.

Cortex-A72 является развитием Cortex-A57; базовая архитектура очень похожа. Однако ARM изменила весь конвейер для повышения мощности и производительности. Возможно, самой большой слабостью A57 было его относительно высокое энергопотребление, особенно на узле 20 нм, что серьезно ограничивало стабильную производительность мобильных устройств, сводя его к коротким, скачкообразным рабочим нагрузкам и вынуждая SoC использовать менее производительные ядра Cortex-A53 для расширенного использования. .

Возможно, самой большой слабостью A57 было его относительно высокое энергопотребление, особенно на узле 20 нм, что серьезно ограничивало стабильную производительность мобильных устройств, сводя его к коротким, скачкообразным рабочим нагрузкам и вынуждая SoC использовать менее производительные ядра Cortex-A53 для расширенного использования. .

ARM пытается исправить эту проблему с помощью A72, вернувшись назад и оптимизируя почти каждый из логических блоков A57 для снижения энергопотребления.Например, ARM смогла реализовать снижение динамической мощности на 35-40% для каскада декодера, и, используя ранний поиск тегов IC, трехпозиционные инструкции L1 и двухсторонние кэши данных L1 в A72 также потребляют меньше энергии, аналогично тому, как использовались бы кеши с прямым отображением. Согласно ARM, все изменения, внесенные в A72, приводят к снижению энергопотребления примерно на 15% по сравнению с A57, когда оба ядра выполняют одинаковую рабочую нагрузку с одинаковой частотой и используют один и тот же 28-нм техпроцесс. A72 видит еще более значительное сокращение при использовании современного процесса FinFET, такого как 16-нм FinFET + от TSMC, где ядро A72 остается в пределах диапазона мощности 750 мВт на уровне 2.5 ГГц, согласно ARM.

A72 видит еще более значительное сокращение при использовании современного процесса FinFET, такого как 16-нм FinFET + от TSMC, где ядро A72 остается в пределах диапазона мощности 750 мВт на уровне 2.5 ГГц, согласно ARM.

[Источник изображения: часы Hiroshige Goto для ПК]

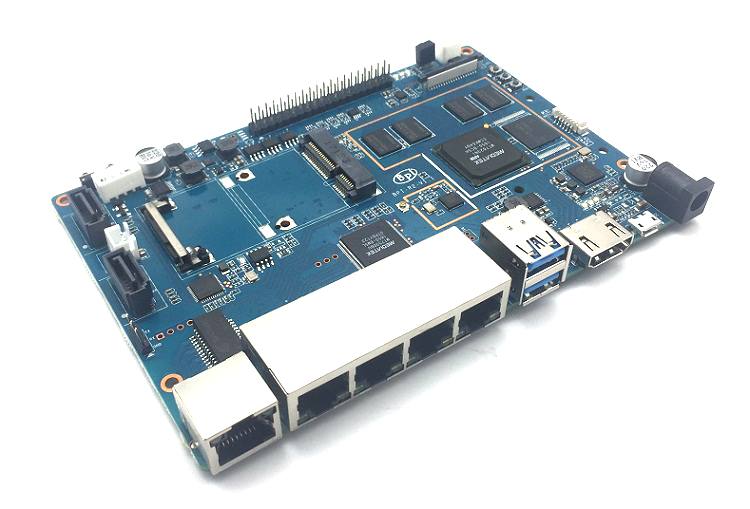

Последняя серия решений QorIQ LS2 system-on-chip (SoC) от Freescale основана на архитектуре Arm-8 Cortex-A50 ARM-8 (см. « Поставка 64-битных платформ Arm» в электронном дизайне.com) и архитектура SoC Layerscape от Freescale. QorIQ LS2085A (Рис. 1) построен на базе 8-ядерного процессора Cortex-A57 с 4 Мбайт кеш-памяти второго уровня. Каждая пара из двух ядер имеет кэш-память второго уровня объемом 1 Мбайт. Система также использует один кэш L3 объемом 1 Мбайт. Два 64-битных контроллера памяти DDR4 поддерживают ECC и имеют чередующуюся полосу пропускания 2,1 Гбайт / с. Коммутатор LS2 Ethernet имеет пропускную способность 88 Мбайт / с, а встроенный ускоритель обработки пакетов имеет пропускную способность 20 Мпакетов / с.Криптографический движок может работать со скоростью 20 Гбит / с, а механизм сопоставления с образцом работает со скоростью 10 Гбит / с. Сжатие данных может осуществляться со скоростью до 20 Гбит / с. В системе есть дополнительный 32-разрядный контроллер памяти DDR4 только для поддержки ускорения сети. Сетевые интерфейсы включают восемь портов Ethernet 1/10 Гбит плюс еще восемь портов Ethernet 1 Гбит.Он поддерживает коммутацию L2 на портах. Поддержка IEEE MAC security (MACsec) может быть применена к четырем из портов Ethernet 1/10 Гбит. Поддержка PCI Express Gen 3 может обрабатывать SR-IOV (виртуализацию ввода-вывода с одним корневым элементом). Конфигурации включают 1×8, 4×4, 4×1 и 4×1. Также есть пара портов SATA 3.0 и два порта USB 3.0 со встроенными физическими уровнями. LS2045A вдвое сокращает количество ядер в LS2085A. Это сокращает объем кеш-памяти L2, но включает в себя такое же периферийное устройство. Freescale также анонсировала добавление SoC Power Architecture QorIQ, которые также основаны на Layerscape. Эти SoC включают в себя меньшее периферийное оборудование, включая один порт Ethernet 10 Гбит. Они также поддерживают доверительную архитектуру Freescale QorIQ с безопасной загрузкой, безопасной отладкой и обнаружением несанкционированного доступа.Чипы также имеют энергозависимое хранилище ключей. Они SoC Layerscape работают под управлением Linux. Freescale предоставляет драйверы с открытым исходным кодом для аппаратных ускорителей и других периферийных устройств на кристалле.

Это список всех типов событий счетчика производительности ARM V8 Cortex-A57.

См. Cortex-A57 MPCore Техническое справочное руководство Cortex A57 DDI

(ARM DDI 0488D, редакция r1p1).

ПОДРОБНЕЕ: Лучшие смартфоны.

Cortex-A57 SoC для приложений SDN / NFV

Эта комбинация обеспечивает быструю и глубокую поддержку проверки пакетов, что делает платформы идеальными для программно-конфигурируемых сетей (SDN) и виртуализации сетевых функций (NFV). Это включает поддержку таких стандартов, как OpenFlow.

Эта комбинация обеспечивает быструю и глубокую поддержку проверки пакетов, что делает платформы идеальными для программно-конфигурируемых сетей (SDN) и виртуализации сетевых функций (NFV). Это включает поддержку таких стандартов, как OpenFlow.  К ним относится T4080 с восемью 64-битными ядрами с архитектурой питания e5500. T1023 и T1024 используют от одного до четырех ядер. T4080 включает поддержку векторных изображений AltiVec. Он совместим по выводам с T4160 и T4240.

К ним относится T4080 с восемью 64-битными ядрами с архитектурой питания e5500. T1023 и T1024 используют от одного до четырех ядер. T4080 включает поддержку векторных изображений AltiVec. Он совместим по выводам с T4160 и T4240.

События процессора ARM V8 Cortex-A57

Имя Описание Счетчики, пригодные для использования Опции маски единиц SW_INCR Выполнение инструкции архитектурно, проверка кода состояния, приращение программного обеспечения все

L1I_CACHE_REFILL Пополнение кэша инструкций уровня 1 все

L1I_TLB_REFILL Инструкция уровня 1 Пополнение TLB все

L1D_CACHE_REFILL Пополнение кэша данных уровня 1 все

L1D_CACHE Доступ к кэшу данных уровня 1 все

L1D_TLB_REFILL Заполнение TLB данных уровня 1 все

LD_RETIRED Инструкция архитектурно выполнена, проверка кода состояния пройдена, загрузка все

ST_RETIRED Архитектурно выполненная инструкция, проверка кода состояния, сохранение все

INST_RETIRED Инструкция архитектурно оформленная все

EXC_TAKEN Исключение принято все

EXC_RETURN Инструкция архитектурно выполняется, проверка кода условия, возврат исключения все

CID_WRITE_RETIRED Инструкция архитектурно выполнена, проверка кода состояния пройдена, запись в CONTEXTIDR все

PC_WRITE_RETIRED Инструкция архитектурно выполнена, проверка кода состояния пройдена, смена программного обеспечения ПК все

BR_IMMED_RETIRED Инструкция архитектурно оформленная, непосредственное отделение все

BR_RETURN_RETIRED Инструкция архитектурно выполнена, проверка кода условия пройдена, возврат процедуры все

UNALIGNED_LDST_RETIRED Инструкция архитектурно выполнена, проверка кода условия пройдена, невыровненная загрузка или сохранение все

BR_MIS_PRED Неправильно предсказанная или непредсказуемая ветвь спекулятивно выполнена все

CPU_CYCLES Цикл все

BR_PRED Предсказуемая ветвь, спекулятивно исполненная все

MEM_ACCESS Доступ к памяти данных все

L1I_CACHE Доступ к кэшу инструкций уровня 1 все

L1D_CACHE_WB Обратная запись кэша данных уровня 1 все

L2D_CACHE Доступ к кэшу данных уровня 2 все

L2D_CACHE_REFILL Пополнение кэша данных уровня 2 все

L2D_CACHE_WB Кэш данных уровня 2 с обратной записью все

BUS_ACCESS Доступ к автобусу все

MEMORY_ERROR Ошибка локальной памяти все

INST_SPEC Операция предположительно выполнена все

TTBR_WRITE_RETIRED Инструкция архитектурно выполнена, проверка кода состояния пройдена, запись в TTBR все

BUS_CYCLES Автобусный цикл все

L1D_CACHE_ALLOCATE Выделение кэша данных уровня 1 без пополнения все

L2D_CACHE_ALLOCATE Выделение кэша данных уровня 2 без пополнения все

L1D_CACHE_LD Доступ к кэшу данных уровня 1 — чтение все

L1D_CACHE_ST Доступ к кэшу данных уровня 1 — запись все

L1D_CACHE_REFILL_LD Пополнение кэша данных уровня 1 — чтение все

L1D_CACHE_REFILL_ST Пополнение кэша данных уровня 1 — Запись все

L1D_CACHE_WB_VICTIM Кэш данных уровня 1 Обратная запись — жертва все

L1D_CACHE_WB_CLEAN Кэш данных уровня 1 Обратная запись — событие очистки: и согласованность все

L1D_CACHE_INVAL Кэш данных уровня 1 недействителен все

L1D_TLB_REFILL_LD Пополнение TLB данных уровня 1 — чтение все

L1D_TLB_REFILL_ST Заполнение TLB данных уровня 1 — Записать все

L2D_CACHE_LD Доступ к кэшу данных уровня 2 — чтение все

L2D_CACHE_ST Доступ к кэшу данных уровня 2 — запись все

L2D_CACHE_REFILL_LD Пополнение кэша данных уровня 2 — чтение все

L2D_CACHE_REFILL_ST Пополнение кэша данных уровня 2 — Запись все

L2D_CACHE_WB_VICTIM Кэш данных уровня 2 Обратная запись — жертва все

L2D_CACHE_WB_CLEAN Кэш данных уровня 2 Обратная запись — очистка и согласованность все

L2D_CACHE_INVAL Кэш данных уровня 2 недействителен все

BUS_ACCESS_LD Доступ к шине — чтение все

BUS_ACCESS_ST Доступ к шине — запись все

BUS_ACCESS_SHARED Доступ к шине — нормальный все

BUS_ACCESS_NOT_SHARED Доступ к шине — ненормально все

BUS_ACCESS_NORMAL Доступ к шине — нормальный все

BUS_ACCESS_PERIPH Доступ к шине — периферийные устройства все

MEM_ACCESS_LD Доступ к памяти данных — чтение все

MEM_ACCESS_ST Доступ к памяти данных — запись все

UNALIGNED_LD_SPEC Невыровненный доступ — чтение все

UNALIGNED_ST_SPEC Невыровненный доступ — запись все

UNALIGNED_LDST_SPEC Невыровненный доступ все

LDREX_SPEC Эксклюзивная операция, предположительно выполненная — LDREX все