Что представляет собой микроконтроллер 1986ВЕ91Т от компании Миландр. Какие ключевые особенности и характеристики у этого микроконтроллера на базе ядра ARM Cortex-M3. Как выглядит внутренняя структура кристалла микросхемы 1986ВЕ91Т. Какие функциональные блоки можно выделить в архитектуре данного микроконтроллера.

Обзор микроконтроллера 1986ВЕ91Т

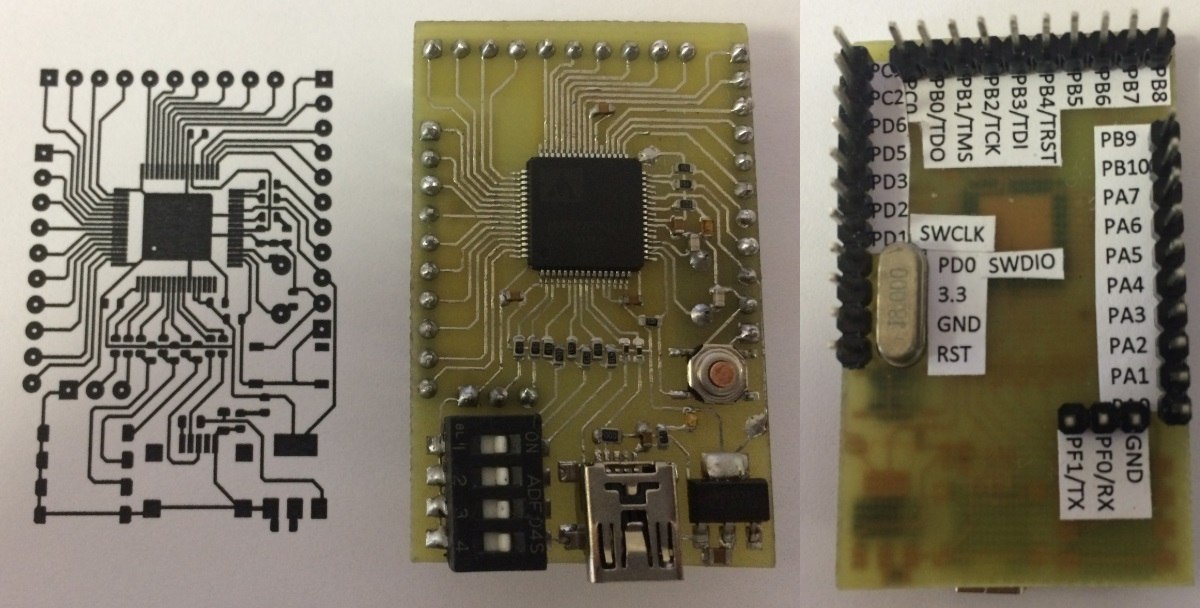

Микроконтроллер 1986ВЕ91Т производства российской компании Миландр представляет собой 32-разрядный микроконтроллер на базе ядра ARM Cortex-M3. Данная микросхема обладает следующими ключевыми характеристиками:

- Ядро ARM Cortex-M3 с тактовой частотой до 80 МГц

- 128 КБ флеш-памяти программ

- 32 КБ оперативной памяти SRAM

- Встроенный контроллер USB

- Технологический процесс 180 нм

- Металлокерамический корпус

1986ВЕ91Т — это высокопроизводительный микроконтроллер общего назначения, который может применяться в различных встраиваемых системах управления, измерительных приборах, промышленной автоматике и других областях.

Архитектура и внутренняя структура кристалла

Размер кристалла микросхемы 1986ВЕ91Т составляет 6.54 x 5.9 мм. На фотографиях кристалла, полученных после удаления слоев металлизации, можно выделить следующие ключевые функциональные блоки:

- Ячейки ввода-вывода (IO Cells) и контактные площадки

- 4 блока флеш-памяти по 32 КБ

- Блок статического ОЗУ 32 КБ

- Загрузочное ПЗУ 256 x 32 байта

- Физический интерфейс USB

- Внутренний линейный регулятор напряжения на 1.8В

- Схема домена батарейного питания

- RC-генераторы

- Системная ФАПЧ и ФАПЧ для USB

- 2 ЦАП и 2 АЦП

- Блоки SRAM для CAN-контроллеров

- Область синтезированной логики на стандартных ячейках

Особенности реализации памяти

Интересной особенностью является организация флеш-памяти в виде 4 блоков по 32 КБ. Почему было выбрано такое решение вместо одного большого блока? Ответ кроется в ограничениях используемого компилятора флеш-памяти:

- Компилятор мог генерировать память с шириной шины не более 32 бит

- Для обеспечения высокой производительности требовалась 128-битная шина

- Поэтому было реализовано 4 параллельных 32-битных блока

Такой подход позволил достичь требуемой производительности при имеющихся ограничениях инструментов проектирования.

Внутренний линейный регулятор напряжения

В составе микросхемы реализован внутренний линейный регулятор напряжения, понижающий напряжение питания с 3.3В до 1.8В. Зачем это нужно? Использование пониженного напряжения питания для внутренней логики позволяет существенно снизить энергопотребление:

- Транзисторы на 1.8В потребляют значительно меньше энергии, чем на 3.3В

- Снижается тепловыделение кристалла

- Повышается энергоэффективность микроконтроллера в целом

Таким образом, внутренний регулятор напряжения является важным элементом для обеспечения низкого энергопотребления микросхемы.

Домен батарейного питания

В составе микроконтроллера выделена отдельная область схемы, работающая от батарейного питания. Какие функции она выполняет?

- Обеспечивает работу часов реального времени (RTC)

- Содержит небольшой объем энергонезависимой памяти

- Включает генератор на внешнем кварце 32 кГц

- Оптимизирована для сверхнизкого энергопотребления

Это позволяет сохранять текущее время и критически важные данные даже при отключении основного питания микроконтроллера. Батарейный домен потребляет минимум энергии и может работать от миниатюрной батарейки в течение длительного времени.

Синтезированная логика на стандартных ячейках

Центральную часть кристалла занимает область синтезированной цифровой логики. Что она содержит и как реализована?

- Включает ядро процессора ARM Cortex-M3

- Содержит контроллеры периферийных устройств

- Синтезирована автоматически из Verilog-описания

- Построена на основе библиотеки стандартных ячеек

Использование синтеза на стандартных ячейках позволяет автоматизировать процесс создания сложных цифровых схем. Разработчики описывают логику на языке Verilog, а специальные инструменты преобразуют это описание в готовую схему на транзисторном уровне.

Особенности реализации аналоговых блоков

В составе микроконтроллера 1986ВЕ91Т реализован ряд аналоговых блоков. Какие это блоки и в чем их особенности?

- 2 цифро-аналоговых преобразователя (ЦАП)

- 2 аналого-цифровых преобразователя (АЦП)

- RC-генераторы низкой и высокой частоты

- Системная ФАПЧ и ФАПЧ для USB

Наличие встроенных АЦП и ЦАП позволяет микроконтроллеру работать с аналоговыми сигналами без использования внешних микросхем. RC-генераторы обеспечивают возможность работы без внешнего кварцевого резонатора. А схемы ФАПЧ позволяют умножать частоту для получения высокочастотного тактового сигнала.

Физический интерфейс USB

Микроконтроллер 1986ВЕ91Т оснащен встроенным контроллером USB. Как он реализован на уровне кристалла?

- Физический интерфейс (PHY) выделен в отдельный блок

- Содержит аналоговые приемники и передатчики сигнала

- Цифровая часть контроллера находится в области синтезированной логики

Такое разделение позволяет оптимизировать аналоговую часть USB отдельно от цифровой логики. Физический интерфейс требует специальных схемотехнических решений, в то время как протокольная часть может быть реализована на стандартных цифровых ячейках.

Происхождение функциональных блоков микроконтроллера

При разработке сложных микросхем часто используются готовые блоки интеллектуальной собственности (IP-блоки). Что в микроконтроллере 1986ВЕ91Т разработано самостоятельно, а что лицензировано у сторонних компаний?

Собственные разработки Миландр:

- Цифровые периферийные блоки (таймеры, CAN, USB и др.)

- Контроллеры памяти

- Аналоговые блоки (АЦП, ЦАП, генераторы, ФАПЧ)

- Встроенный линейный регулятор напряжения

- Ячейки ввода-вывода

Лицензированные IP-блоки:

- Ядро процессора ARM Cortex-M3

- Контроллер DMA

- Интерфейсы UART и SPI

Такой подход позволяет сократить время разработки за счет использования проверенных IP-блоков, сохраняя при этом ключевые ноу-хау компании.

“Электронные устройства в мехатронике”

Московский государственный технический университет им. Н.Э.Баумана

Г. А. Орлов

Исследование интегральных логических элементов транзи- сторно-транзисторной логики

Методические указания к лабораторной работе по дисциплинам

Москва |

2009 г |

Данные методические указания издаются в соответствии с учебным планом. Рассмотрены и одобрены кафедрой ………………01 г., методической комиссией факультета ………………01г., и учебно-мето- дическим управлением …………….01 г.

© Кафедра СМ-7 МГТУ им. Н.Э. Баумана

Оглавление |

|

I. Цель работы……………………………………………………………………… |

1 |

II. Принцип действия элементов ТТЛ …………………………………………… |

1 |

III. Основные параметры и характеристики элементов ТТЛ …………………… |

4 |

IV. |

7 |

V. Исследование функционирования элементов ²И-НЕ² ТТЛ …………………. |

8 |

VI. Исследование статических параметров элементов ТТЛ серии К155 ……… |

9 |

VII. Исследование динамических свойств элементов ТТЛ серии К155 ……….. 11 Литература ………………………………………………………………………….. 13

2

Интегральные логические элементы транзисторно-транзисторной логики (ТТЛ).

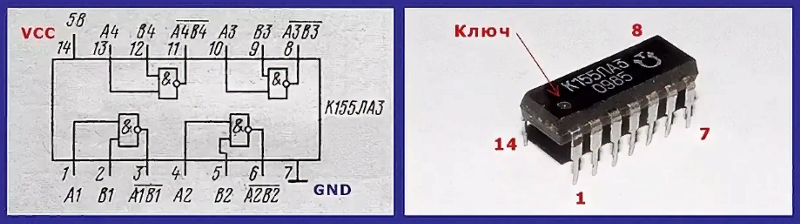

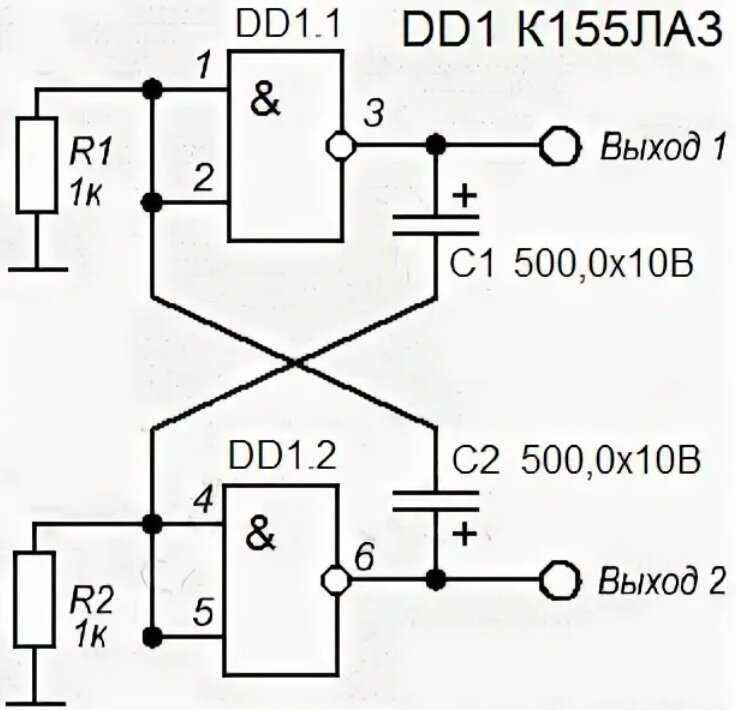

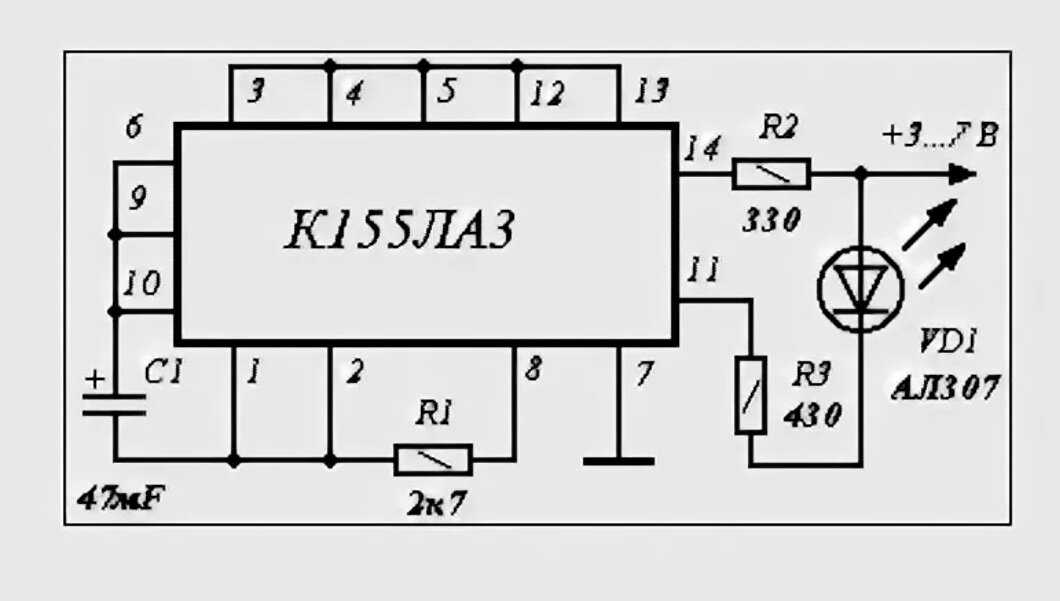

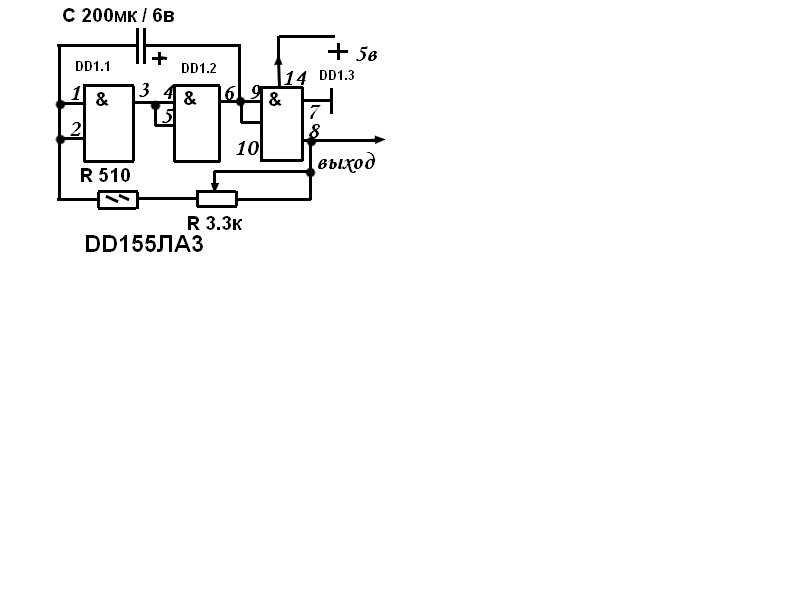

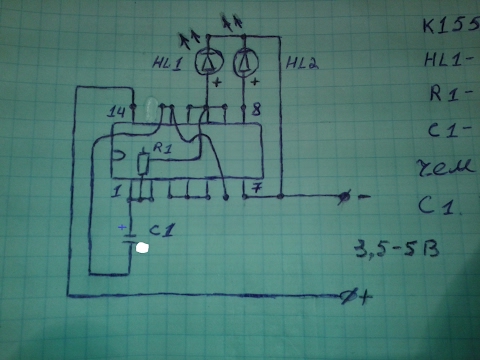

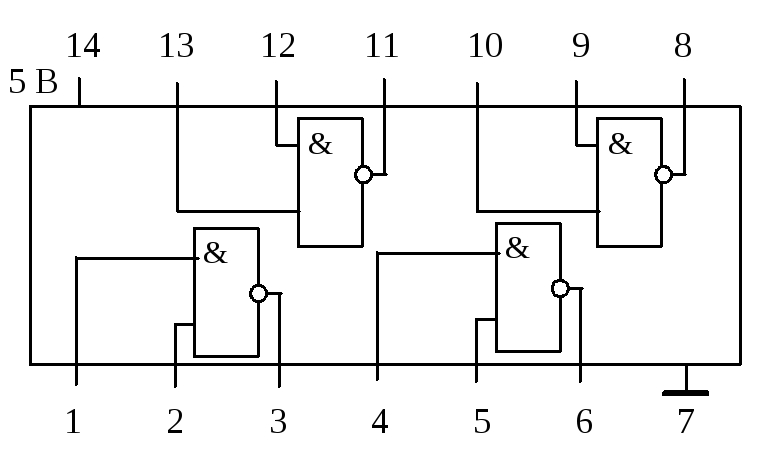

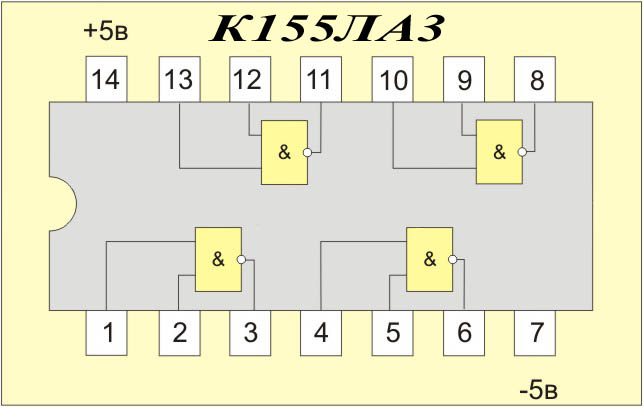

I. Цель работы. Целью работы является исследование основных характеристик и параметров интегральных элементов ТТЛ серии К155 на примере микросхемы К155ЛА3.

II. Принцип действия элементов ТТЛ.

Основная схема элемента ТТЛ микросхемы К155ЛА3 имеет структуру, соответ-

ствующую логической операции «И-НЕ». |

|

|

||||||||

Применительно к функции от двух |

аргументов операция “И-НЕ” записывается анали- |

|||||||||

тически как F = |

|

|

и в виде таблицы истинности табл. |

|

|

|||||

x1 × x2 |

|

|

||||||||

|

|

|

|

|

Табл 1. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x1 |

|

x 2 |

|

F |

|

|

|

DA1 |

|

|

0 |

|

0 |

|

1 |

X1 |

|

|

|

|

|

|

|

|

|

& |

F |

|||||

|

|

|

||||||||

1 |

|

0 |

|

1 |

X2 |

|

|

|||

|

|

|

|

Рис. |

||||||

0 |

|

1 |

|

1 |

|

|

|

|

||

|

|

|

|

|

|

|

||||

1 |

|

1 |

|

0 |

|

|

|

|

|

|

Условное графическое обозначение элемента, реализующего операцию “И-НЕ” для двух аргументов приведено на рис.1.

При подаче на входы элемента сигналов вида Х1 и Х2, изображенного на рис.2, выходной сигнал будет иметь вид F на том же рис.

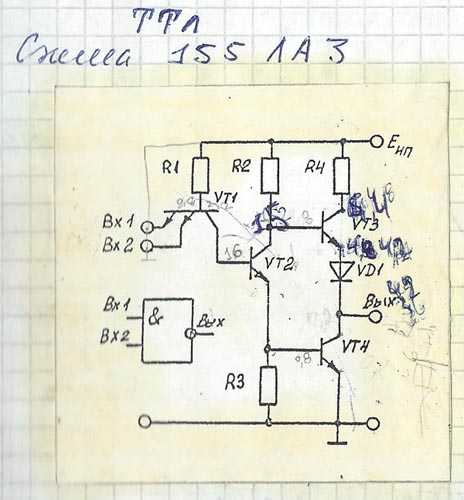

В простейшем случае элемент И-НЕ представляет собой соединение схемы «И», состоящей из многоэмиттерного транзистора и инвертора на обычном транзисторе

3

(рис. 3a).

3a).

Многоэмиттерный транзистор эквивалентен нескольким n-p-n транзисторам, у которых объединены базы и коллекторы ( рис.3 б).

Если на эмиттер одного из транзисторов подать напряжение логического нуля, например, соединить его с общей шиной, то этот транзистор будет насыщен от UИП. Напряжение на базе VT2 при этом близко к нулю и VT2 закрыт. На выходе схемы появляется высокий потенциал U1ВЫХ, близкий к UИП. Для того, чтобы на выходе системы был низкий потенциал U0ВЫХ , необходимо одновременно на все эмиттеры подать напряжение, близкое к UИП. Транзисторы VT1.1, VT1.2 , при этом переходят в инверсный режим работы, при котором коллектор и эмиттер меняются местами по выполняемым функциям. Переходы база-коллектор транзисторов открываются напряжением UИП и через них насыщается транзистор VT2. В результате напряжение на выходе элемента падает до уровня, определяемого остаточным падением напряжения на транзисторе VT2. Это напряжение является напряжением логического нуля схемы. Таким образом, элемент ТТЛ относится к схемам положительной логики, для которой высокий потенциал U1ВЫХ ≤ UИП соответствует уровню логической единицы, а низкий потенциал U0ВЫХ — уровню логического нуля.

4

Полная схема элемента ТТЛ «И-НЕ» содержит усложненный инвертор (рис.4), в состав которого входят фазоинвертор на транзисторе VT2 и двухтактный усилитель мощности на транзисторах VT4, VT5.

Если под воздействием Х1 = Х2 = «1» транзистор VT2 насыщен, то через него и резистор R1 насыщен от UИП и транзистор VT5. Напряжения UКЭН и UКБН малы. Так как UБЭ4 = UБЭН5 + UКЭН2 — UКЭН5 – UДПР3, то VT4 будет закрыт, поскольку UКЭН5 UКЭН2, UБЭ5 < UДПР3 и UБЭ4 < 0. Остаточное падение напряжения на насыщенном VT5 не превышает значения 0.3…0.4 В. Это значение определяет уровень логического нуля микросхем ТТЛ. В. U0ВЫХ = 0,3…,4 В.

Транзистор VT3 вместе с задающим его режим резистором R3 и резистором R4 образуют нелинейное сопротивление, с помощью которого улучшается помехозащищённость элемента и повышается его быстродействие. Благодаря этому нелинейному сопротивлению ток коллектора VT2 не может протекать до тех пор, пока не откроются транзисторы VT3 и VT5. Поэтому напряжение на выходе элемента сохраняется на уровне U1ВЫХ вплоть до большего значения входного напряжения логического нуля, изменяющегося под воздействием напряжения помехи. Уменьшение сопротивления в цепи базы VT5 по сравнению со случаем отсутствия VT3 уменьшает время рассасывания для VT5, то есть способствует быстрому выключению элемента.

Уменьшение сопротивления в цепи базы VT5 по сравнению со случаем отсутствия VT3 уменьшает время рассасывания для VT5, то есть способствует быстрому выключению элемента.

Если входной сигнал на любом из входов равен нулю, то VT1 работает в нормальном усилительном режиме и насыщен от UИП через R1. Транзистор VT2 закрыт, поскольку его база через открытый VT1 соединена с общим проводом. Следовательно, к эмиттерному переходу VT2 приложено в запирающем направлении падение напряжения на R4 и VT3, создаваемое токами утечки VT2 и VT5. Транзистор VT4, наоборот, насыщен от UИП через R3 . При отсутствии сопротивления нагрузки выходное напряжение элемента определяется значением UИП = 5В, падениями напряжения на R5, на переходе «эмиттер-коллектор» VT4 и диоде VD4 от токов утечки. При наличии нагрузки падения напряжения на R5, VT4 и VD4 возрастают и выходное напряжение уменьшается. При нормальной температуре напряжение на выходе не превышает +(3,8…4,2)В для ненагруженной схемы и +(3,2…3,8)В для нагруженной схемы. При минусовой температуре t°С = −60°С U1ВЫХ снижается еще на (0,4…0,6)В. Минимальным значением логической единицы принято считать +2,4В. При переключениях схемы из одного состояния в другое из-за инерционности транзисторов VT4 и VT5 они оба на время длительности переходных процессов могут оказаться в открытом состоянии. Например, VT5 еще не вышел из состояния насыщения, а VT4 уже открылся. Возникает импульс так называемого сквозного тока через VT4 и VT5, который минует нагрузку. Резистор R5 позволяет ограничить значение этого импульса на допустимом уровне.

При минусовой температуре t°С = −60°С U1ВЫХ снижается еще на (0,4…0,6)В. Минимальным значением логической единицы принято считать +2,4В. При переключениях схемы из одного состояния в другое из-за инерционности транзисторов VT4 и VT5 они оба на время длительности переходных процессов могут оказаться в открытом состоянии. Например, VT5 еще не вышел из состояния насыщения, а VT4 уже открылся. Возникает импульс так называемого сквозного тока через VT4 и VT5, который минует нагрузку. Резистор R5 позволяет ограничить значение этого импульса на допустимом уровне.

Применение сложного выходного каскада позволяет существенно сократить время перезаряда паразитных емкостей схемы и монтажа и тем самым резко увеличить бы-

5

стродействие элемента. При включении схемы, когда UВЫХ изменяется от U1ВЫХ до U0ВЫХ, открытый транзистор VT5 обеспечивает быстрый разряд присоединенных к выходу паразитных емкостей и емкостей нагрузки. Благодаря этому фронт спада выходного импульса получается крутым. При выключении схемы VT5 закрыт, VT4 — открыт. Эмиттерный ток VT4 обеспечивает быстрый заряд емкостей на выходе схемы, а следовательно, малую длительность переднего фронта (фронта нарастания) импульса выходного напряжения. В реальных условиях из-за сложного характера паразитных реактивностей кривые переходных процессов микросхемы (передний и задний фронты импульса) носят колебательный характер.

При выключении схемы VT5 закрыт, VT4 — открыт. Эмиттерный ток VT4 обеспечивает быстрый заряд емкостей на выходе схемы, а следовательно, малую длительность переднего фронта (фронта нарастания) импульса выходного напряжения. В реальных условиях из-за сложного характера паразитных реактивностей кривые переходных процессов микросхемы (передний и задний фронты импульса) носят колебательный характер.

Для большинства серий ТТЛ предельно допустимая величина отрицательного напряжения на входе микросхемы составляет 0,8 В. В реальных схемах аппаратуры сигнал, поступающий на вход интегральной схемы, не имеет строгой прямоугольной или трапецеидальной формы. В момент окончания сигнала в монтажных цепях возникают затухающие колебания, которые могут вызвать ложное срабатывание микросхемы. Для исключения таких ложных срабатываний к каждому из входов микросхемы добавлены демпфирующие диоды VD1, VD2.

III. Основные параметры и характеристики элементов ТТЛ.

Основной статической характеристикой микросхем ТТЛ является так называемая передаточная характеристика, определяемая зависимостью UВЫХ =f(UВХ) (рис. 5). На ней можно выделить три области: область I нахождения микросхемы в состоянии логической единицы, область III нахождения микросхемы в состоянии логического нуля и активную, или переходную область II.

5). На ней можно выделить три области: область I нахождения микросхемы в состоянии логической единицы, область III нахождения микросхемы в состоянии логического нуля и активную, или переходную область II.

Передаточной характеристике соответствуют следующие статические параметры элементов ТТЛ;

U0ВЫХ — выходное напряжение логического нуля, U1ВЫХ — выходное напряжение логической единицы,

U1ПОР — наименьшее (пороговое) значение высокого уровня на входе, при котором

6

микросхема переходит из состояния «III» в активную область.

U0ПОР — наибольшее (пороговое) значение низкого уровня напряжения на входе, при котором микросхема переходит из состояния «I» в активную область,

(U1ПОР — U0ПОР) — ширина активной области,

U0 MAX |

— |

наибольшее значение допустимого напряжения логического нуля, |

U1 MIN |

— |

наименьшее значение допустимого напряжения логической единицы, |

U+П. |

— наибольшее значение допустимого напряжения помехи положительной по- |

|

лярности, которое вызывает переход микросхемы из состояния логической единицы в активную область, U+П.СТ = U0ПОР − U0 MAX ,

U−П.СТ — наибольшее значение допустимого напряжения помехи отрицательной полярности, которое вызывает переход микросхемы из состояния логического нуля в ак-

тивную область, |

U−П.СТ = U1 MIN − U1ПОР, |

|

UП.СТ — |

помехоустойчивость статическая — наибольшее значение допустимого |

|

напряжения статической помехи по высокому и низкому уровням входного напряжения, при котором еще не происходит изменение уровней выходного напряжения цифровой интегральной микросхемы. Для микросхем серии 155 UП.СТ имеет величину не более 0.4В.

Передаточная характеристика измеряется при различных значениях напряжения питания, температуры и сопротивления нагрузки.

Помимо передаточной к статическим характеристикам микросхем также относятся входная и выходная характеристики. Входная характеристика определяется зависимостью IВХ = f(UВХ) (рис.6). Участок от оси ординат характеристики до точки А соответствует сигналу логического нуля на входе, при котором ток из микросхемы протекает в источник управляющего сигнала. Для элементов ТТЛ серии 155 ток I0 ВХ = — 1,6 мА .

Участок АВ соответствует постепенному закрыванию входного эмиттерного перехода. В точке В входной переход запирается. Теперь ток I1 ВХ, соответствующий напряжению логической единицы на входе схемы, протекает от источника через входной эмиттерный переход , работающий в инверсном режиме, то есть в режиме коллекторного перехода. Для элементов серии 155 ток I1 ВХ = +40 мкА.

Выходная характеристика элементов ТТЛ определяется зависимостями:

U1ВЫХ = f(I1 ВЫХ) при U0ВХ и U0ВЫХ = f(I0 ВЫХ) при U1ВХ

Они позволяют оценить выходное сопротивление микросхемы в двух ее состояниях. Важными статическими параметрами, определяющими возможность использо-

Важными статическими параметрами, определяющими возможность использо-

вания микросхем, являются коэффициенты объединения по входу КОБ и разветвления по выходу КРАЗ. Коэффициент объединения по входу КОБ показывает, какое наибольшее количество входов может иметь логический элемент. Обычно КОБ является заданным самой конструкцией микросхем.

7

I вх |

B |

I1вх

Uвх

Iвх0 |

A |

Рис. 6 |

|

|

Коэффициент разветвления по выходу КРАЗ или нагрузочная способность интегральной схемы показывает количество схем этой же серии, входы которых могут быть присоединены к выходу данной схемы без нарушения ее работоспособности. Критерием достижения максимально допустимой нагрузки является уменьшение выходного напряжения логической единицы до предельного значения.

Динамические свойства микросхем оцениваются следующими основными параметрами (рис.7):

fВХ — частота следования входных импульсов,

t1,0ЗД -время задержки включения — интервал времени между входным и выходным импульсами при переходе напряжения на выходе микросхемы от напряжения логической единицы к напряжению логического нуля, измеренный на уровне 0,1UВХ и 0,9UВЫХ

t0,1ЗД — время задержки выключения — интервал времени между входным и выход-

UВХ |

|

|

t1,0 |

|

|

|

t0,1 |

ЗДР |

|

|

|

|

|

|

|||||

|

|

|

|

||||||

|

|

|

ЗДР |

|

|

|

|

|

|

U1 |

|

|

|

|

|

|

|

|

|

ВХ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0,9×UВХ |

|

|||

U0 |

|

|

0,1×UВХ |

0,5×U |

|

ВХ |

|

||

|

|

||||||||

|

|

|

|

|

|

|

|||

ВХ |

|

|

|

|

|

|

|

||

UВЫХ |

t1,0 |

|

|

|

|

|

|||

|

|

|

ЗД |

|

|

|

|

|

|

U1 |

|

|

|

|

|

|

|

||

ВЫХХ |

0,9×UВЫХ |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||

0,5×UВЫХ |

|

0,1×UВХ |

|

|

|

|

|

||

U0 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||

ВЫХ |

|

|

|

|

|

|

|

||

Рис. |

|

|

|

|

|

t0,1 |

ЗД |

||

ным импульсами при переходе напряжения на выходе микросхемы от напряжения логического нуля к напряжению логической единицы, измеренный на уровнях 0,9UВХ и 0,1UВЫХ ,

8

Что же внутри российского Арма? / Хабр

После предыдущих статей с внутренностями микросхем (1, 2) многие писали, что фотографии — это конечно интересно, но хотелось бы знать что есть что.

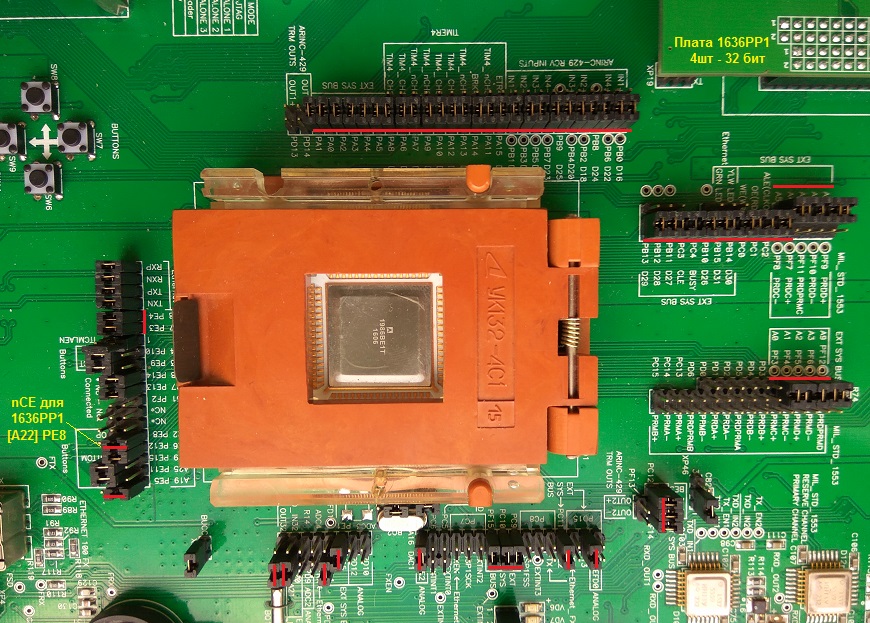

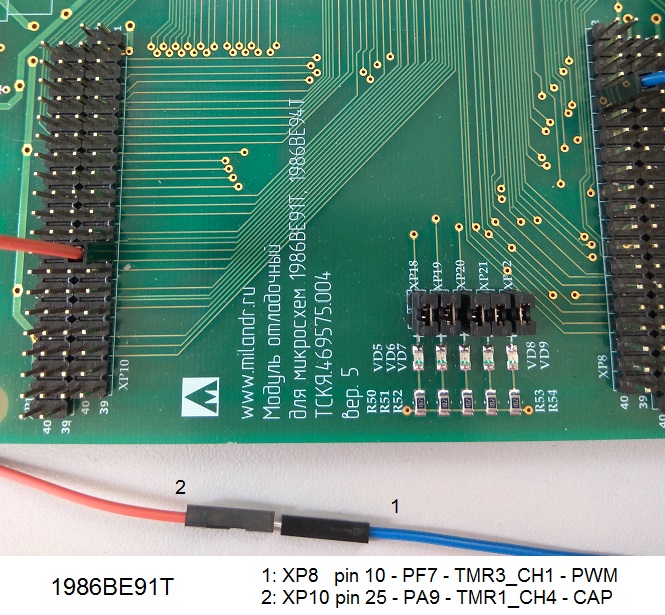

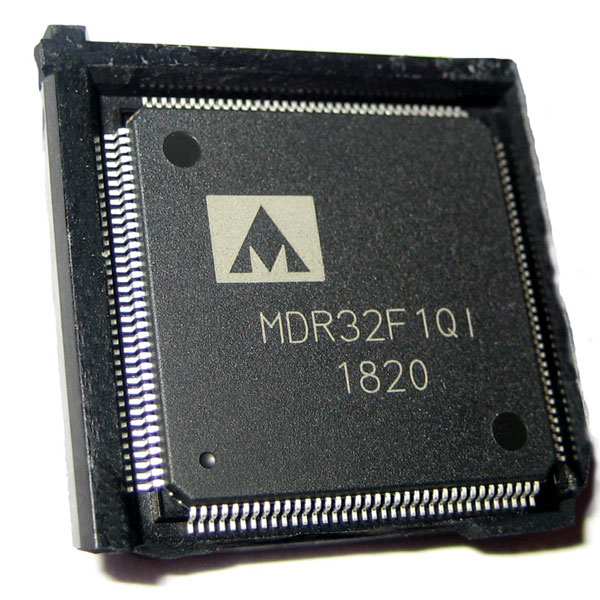

Сегодня возможность удовлетворить этот закономерный интерес наконец появилась. Ковырять будем 1986ВЕ91Т — это микроконтроллер Миландра, основанный на ядре ARM Cortex-M3 (официально лицензированного). Внутри — 128 КиБ флеш-памяти, 32 КиБ статической памяти, аппаратный USB и 80Мгц ядро, изготовлено по технологии 180нм.

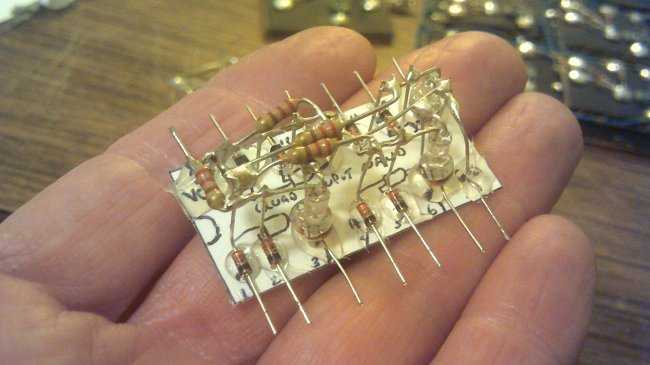

Проволока, соединяющая выводы и контактные площадки на микросхеме осталась: корпус металлокерамический, и травить его не пришлось. Весь фарш скрыт от нашего взора несколькими слоями алюминиевых соединений. Размер кристалла — 6.54×5.9мм.

Весь фарш скрыт от нашего взора несколькими слоями алюминиевых соединений. Размер кристалла — 6.54×5.9мм.

Травим металлизацию… Почти достали до самого дна:

А вот и самый нижний слой с транзисторами и слоем поликремния (первый уровень соединений и затворы транзисторов):

IO Cells & bonding pads — стандартные кусочки схемы, которые управляют каждой ногой микросхемы, содержат элементы защиты от статического электричества, могут переключатся в режим входа и выхода. Непосредственно под контактными площадками транзисторов нет — т.к. при приваривании проволоки они могут быть повреждены.

4x32KiB flash — 4 стандартных блока флеш-памяти. Почему не один большой? Компилятор флеш-памяти не мог генерировать память с шиной шире 32 бит, а из соображений производительности нужно было 128.

32KiB SRAM — быстрая статическая память, состояние которой не сохраняется при выключении питания.

256x32B ROM — загрузочная память. Запрограммирована на заводе «перемычками» — и не может быть изменена.

USB PHY — физический интерфейс протокола USB. Тут только приемники/передатчики сигнала, а цифровая часть USB контроллера — в синтезированной «каше» в центре кристалла.

Internal linear regulator (1.8V) — внутренняя схема понижения напряжения питания до 1.8В. Это нужно потому что 1.8В транзисторы при работе потребляют существенно меньше энергии, чем 3.3В.

Battery domain — работающая от часовой батарейки схема, заточенная под сверхнизкое потребление энергии. Тут таймер реального времени, несколько байт памяти, генератор на внешнем 32кГц кварце.

RC Oscillators — внутренние RC генераторы (низкой и высокой частоты), позволяющие использовать микроконтроллер без кварца.

System/USB PLL — схемы умножения частоты для системы и USB. Позволяют например из 10Мгц кварца получить 80Мгц системную частоту, и 48Мгц для USB.

2xDAC — цифро-аналоговые преобразователи.

2xADC — аналогово-цифровые преобразователи. Пустые места — это вероятно были конденсаторы.

2xCAN SRAM — маленькие блоки статической памяти. Вероятно это буфферы для 2-х CAN контроллеров и проч.

Большинство из вышеперечисленных блоков — не обязательно разрабатывать с нуля, а можно лицензировать на фабрике, или приобрести у компаний, разрабатывающих и продающих IP. Но в данном случае — все цифровые блоки (Timer, CAN, USB, контроллеры ОЗУ/ПЗУ внешнюю шину, итп), аналоговые блоки АЦП, ЦАП, генераторы, PLL, встроенный LDO, и даже площадки ввода-вывода собственной разработки, а куплены только ядро, DMA, UART, SPI.

Cell based synthesized logic — автоматически синтезированная схема из Verilog-описания. Тут как само ядро процессора, так и контроллеры периферии. Синтезируются схема не напрямую из транзисторов, а из стандартных ячеек фиксированной высоты — реализующих различные функции вроде И, ИЛИ, триггеров и проч.

Boot ROM

При желании содержимое можно «прочитать». Но конечно, в данном случае это не требуется, т.

Описание лабораторной установки УМ-16 …………………………………..

Описание лабораторной установки УМ-16 …………………………………..

1

1 СТ

СТ 7

7