Что такое делитель частоты на 10. Как работает схема делителя частоты на 10. Для чего применяются делители частоты в радиотехнике. Какие микросхемы используются для построения делителей частоты.

Принцип работы делителя частоты на 10

Делитель частоты на 10 — это электронная схема, которая уменьшает частоту входного сигнала в 10 раз. Принцип работы такого делителя основан на использовании счетчиков или триггеров, настроенных на деление входной частоты на определенный коэффициент.

Базовая схема делителя частоты на 10 обычно содержит:

- Входной формирователь для преобразования входного сигнала в импульсы прямоугольной формы

- Счетчик на 10 или каскад из нескольких триггеров, дающих суммарный коэффициент деления 10

- Выходной формирователь для получения выходного сигнала требуемой формы

При подаче на вход 10 импульсов, на выходе формируется 1 импульс. Таким образом, частота выходного сигнала оказывается в 10 раз ниже входной.

Схемы делителей частоты на 10

На микросхеме К155ИЕ2

Простая схема делителя на 10 может быть реализована на микросхеме К155ИЕ2, которая представляет собой двоично-десятичный счетчик:

- Вход счетчика подключается к источнику входного сигнала

- С выхода «1» снимается выходной сигнал с частотой в 10 раз ниже входной

- Вход сброса подключается к общему проводу через резистор 1-10 кОм

На микросхемах К155ТМ2

Более сложный вариант делителя на 10 можно собрать на двух микросхемах К155ТМ2, каждая из которых содержит по два D-триггера:

- Первые три триггера включаются как делители на 2

- Четвертый триггер замыкается в кольцо для получения деления на 5/4

- Выход последнего триггера дает частоту в 10 раз ниже входной

Применение делителей частоты на 10 в радиотехнике

Делители частоты на 10 широко используются в различных радиотехнических устройствах:

Частотомеры

В цифровых частотомерах делители на 10 применяются для расширения диапазона измеряемых частот в сторону высоких значений. Входной высокочастотный сигнал последовательно делится на 10 несколько раз, после чего его частота становится доступной для измерения счетчиком частотомера.

Синтезаторы частот

В схемах синтезаторов частот делители на 10 входят в состав делителей с переменным коэффициентом деления, что позволяет формировать сигналы с дискретностью 10 Гц, 100 Гц, 1 кГц и т.д.

Преобразователи частоты

Делители на 10 используются в схемах гетеродинов супергетеродинных приемников для получения частот гетеродина из опорной частоты кварцевого генератора.

Микросхемы для построения делителей частоты

Для реализации делителей частоты на 10 и других коэффициентов деления применяются следующие распространенные микросхемы:

- К155ИЕ2, К155ИЕ5 — десятичные счетчики

- К155ТМ2 — D-триггеры для построения делителей с произвольным коэффициентом

- К155ИЕ7 — программируемый делитель с коэффициентом деления до 16

- К176ИЕ12 — делитель на 10 в одном корпусе (КМОП)

- К561ИЕ8 — делитель на 10 с предустановкой (КМОП)

Выбор конкретной микросхемы зависит от требуемого быстродействия, напряжения питания, потребляемой мощности и других параметров разрабатываемого устройства.

Расчет делителя частоты на 10

При проектировании делителя частоты на 10 необходимо учитывать следующие моменты:

- Определить максимальную входную частоту и выбрать подходящую микросхему

- Рассчитать цепи формирования входного сигнала (при необходимости)

- Подобрать номиналы времязадающих элементов для обеспечения требуемого коэффициента деления

- Предусмотреть цепи сброса и начальной установки

- Согласовать выходные уровни с последующими каскадами

Важно также обеспечить качественную развязку по питанию и экранирование высокочастотных цепей для устойчивой работы делителя.

Проверка работы делителя частоты на 10

Для проверки правильности работы собранного делителя частоты на 10 можно использовать следующие методы:

- Подача на вход сигнала известной частоты и измерение выходной частоты

- Наблюдение входного и выходного сигналов на двухканальном осциллографе

- Подсчет количества входных импульсов, приходящихся на один выходной

При этом необходимо проверить работу делителя во всем заявленном диапазоне входных частот и амплитуд сигналов.

Применение делителей частоты в любительской радиоаппаратуре

Радиолюбители часто используют делители частоты на 10 и с другими коэффициентами в своих конструкциях:

- Приставки к осциллографам для расширения полосы пропускания

- Калибраторы для настройки радиоприемников

- Генераторы сигналов с цифровой шкалой

- Синтезаторы частот для трансиверов

Делители частоты позволяют существенно расширить функциональные возможности любительской аппаратуры при относительно небольших затратах.

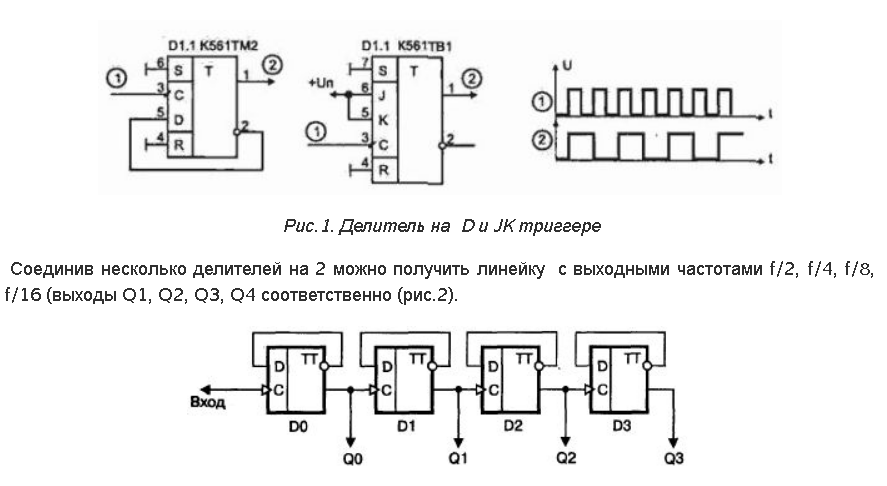

Делитель частоты на микросхемах

Генераторы

В радиолюбительской практике часто бывают необходмы делители частоты с большим коэффициентом деления (1000… 10000 и выше). Обычно для этого используют или 4-5 счетчиков-делителеи на 10, или микросхему К561ИЕ15.

Я предлагаю делитель с программируемым коэффициентом деления (от 10 до 15000), выполненный на широко распространенных микросхемах К561ИЕ16 (К561ИЕ20), представляющих собой двоичные счетчики с коэффициентом деления 2 14 и 212 соответственно. При несколько необычном включении на их основе можно собрать делитель с изменяемым коэффициентом деления (К561ИЕ16 — от 200 до 15000, К561ИЕ20 — от 10 до 4000).

Рис.1 Делитель частоты с программируемым коэффициентом деления

Для примера на рисунке показан делитель с коэффициентом деления 10000, предназначенный для электронных часов на основе ИМС LM8560 и аналогичных, использующих в качестве образцовой частоту сети (50 Гц). Как видно из рисунка, микросхема будет считать импульсы генератора до тех пор, пока на ее выходах не установится код 10011100010000, что в десятичном счислении равно 10000.

Как видно из рисунка, микросхема будет считать импульсы генератора до тех пор, пока на ее выходах не установится код 10011100010000, что в десятичном счислении равно 10000.

Как только она «досчитает» до этого числа, все диоды VD1… VD5 закроются, и на входе R (вывод 11) DD2 сформируется короткий положительный импульс, который “обнулит” все триггеры счетчика. В итоге на выводах 8, 9 DD1.3 будут короткие положительные импульсы с частотой 500000:10000 = 50 (Гц). Элемент DD1.4 вместе с R3, VD6, С1 используется для расширения импульсов. При неустойчивой работе микросхемы часов на выходе DD1.4 следует включить конденсатор С2 емкостью порядка сотен пикофарад.

По этому же принципу, с помощью подключаемых диодов между выходами и входом сброса R микросхемы DD2, можно получить любой коэффициент деления. Например, если подключить диоды к выводам 6, 7, 13, то получится коэффициент деления 200. Однако для получения некоторых коэффициентов деления, например, 100, у К561ИЕ16 не хватает «пропущенных» выходов 2 и 4. В этих случаях следует применять ИМС К561ИЕ20. Цоколевка этих двух микросхем одинаковая. Чтобы узнать, к каким выходам следует подключить диоды, нужно складывать коэффициенты деления на соответствующих выходах микросхемы DD2, пока не получится требуемый коэффициент деления. Какие цифры при этом пришлось сложить, к тем выходам и следует подключать диоды При увеличении выходной частоты в несколько раз следует во столько же раз уменьшить соотношение R3, С1.

А. Колдунов

СВЧ делители частоты. Схемы. Описание. — Цифровая техника — СХЕМЫ — Статьи

Большинство частотомеров, собранных на микросхемах дискретной логики или микроконтроллерах, не позволяют измерять частоты выше 40…50 мГц. Для измерения частот выше этого значения необходимо использовать предварительный СВЧ делитель. Существует большое количество микросхем, на которых можно собрать такой предварительный делитель частоты, но, к сожалению, в магазинах их выбор довольно ограничен.

Это объясняется тем, что в новых серийных разработках частотомеров и другой измерительной техники используются микросхемы все большей и большей степени интеграции — однокристальные синтезаторы, частотомеры и др. Отдельно микросхемы делителей частоты используются относительно редко, поэтому их стоимость высока и они довольно дефицитны. Но, к счастью для радиолюбителей, выбор пока еще есть.Предлагается несколько вариантов схем делителей для СВЧ измерений. Определяющий критерий при выборе элементной базы — простота схемы и доступность комплектующих. Конструктивно СВЧ делители частоты выполняются в виде выносного пробника, в качестве корпуса хорошо подходят металлические корпуса от внешних делителей напряжения, которые широко использовались в старых отечественных осциллографах.

Все схемы делителей частоты можно использовать совместно с частотомерами, описания которых есть на этом сайте. Сигнал с выхода делителя подается по кабелю длиной до 1 м на входной формирователь частотомера. Коэффициент деления учитывается в программе частотомера, поэтому на индикатор будет выводиться истинная частота измеряемого сигнала.

На этой страничке описано, как сделать СВЧ делитель частоты на микросхемах К193ИЕ2, К193ИЕ3, LB3500, SAB6456, TD6359, TD6380, TD6381, TD6382, TD7614.

Серия 193 была освоена отечественной промышленностью в девяностые годы прошлого века на основе разработок фирмы «Plessey Semiconductors». Для предварительных делителей частоты можно использовать К193ИЕ2 и К193ИЕ3. Но эти отечественные микросхемы не полные аналоги импортных. Отличия в данном случае в расположении выводов и особенностях подачи напряжения питания.

Микросхема К193ИЕ2 является аналогом SP8685A, имеет диапазон рабочих частот от 40 до 500 мГц, коэффициент деления 10. Двойная амплитуда выходного напряжения около 0,8 В, чувствительность 100…200 мВ. Потребляемый ток около 50 мА. Схема делителя показана на рисунке.

К193ЕИ3 функциональный аналог SP8690. Схема ее включения имеет незначительные отличия от К193ИЕ2. Диапазон рабочих частот этого делителя несколько уже — от 30 до 200 мГц, но у него есть выход с TTL уровнями, сигнал с которого можно непосредственно, без входного формирователя, подать на логику частотомера. И потребляемый ток меньше — около 20 мА. Коэффициент деления равен10, чувствительность 100…200 мВ.

Хороший выбор для ВЧ делителя — микросхема LB3500 фирмы «Sanyo». Согласно datasheet, диапазон рабочих частот 30…150 мГц, но имеющийся у меня экземпляр устойчиво работает до 350 мГц. Коэффициент деления 8, чувствительность 100 мВ, двойная амплитуда выходного сигнала 0,9 В. Потребляемый ток около 20 мА. Простое и дешевое решение!

Особо следует отметить SAB6456 фирмы «Philips Semiconductors». Это делитель с диапазоном рабочих частот от 70 до 1000 мГц. Потребляемый ток около 20 мА, а заявленная чувствительность 10мВ! Двойная амплитуда выходного сигнала 1 В. Коэффициент деления равен 64 или 256.

Как уже упоминалось, микросхемы делителей частоты малой степени интеграции постепенно снимаются с производства. Иногда проще и дешевле приобрести микросхему синтезатора частоты, чем микросхему делителя. К счастью для радиолюбителей, в некоторых типах синтезаторов разработчики предусмотрели тестовый режим, при котором на один из выводов микросхемы подается входной сигнал после делителя с фиксированным коэффициентом деления. Тестовый режим включается определенной комбинацией уровней напряжения на управляющих входах синтезатора.

Один из таких синтезаторов TD6359 фирмы «Toshiba». Микросхема выпускается в корпусе DIP20. Схема делителя с ее использованием в тестовом режиме показана рисунке. Диапазон рабочих частот 80…1000 мГц. Коэффициент деления 256, выход с открытым коллектором. Чувствительность около 100…200 мВ, но потребляемый ток довольно значительный — 60…80 мА.

Аналогичную схему включения и параметры имеют синтезаторы TD6380, TD6381 и TD6382, которые также можно использовать в схеме СВЧ делителей. Цоколевка для DIP корпусов TD6380P и TD6380N совпадает с TD6359.

Еще один синтезатор, который может работать в тестовом режиме как СВЧ делитель — это TD7614F «Toshiba». Он выпускается в корпусе SOP20. Частотный диапазон 80…1300 мГц, чувствительность 100…200 мВ, потребляемый ток до 75 мА, двойная амплитуда выходного сигнала около 0,8 В. Коэффициент деления 128.

СВЧ делители частоты. Схемы. Описание.

Делитель частоты до 1ГГц

Делитель частоты до 1ГГц

http://vrtp.ru/index.php?act=categories&CODE=article&article=2298

Применение микросхемы U664BS высокочастотного цифрового делителя частоты способствовало упрощению конструкции устройства, которое автор использовал для расширения диапазона измерений относительно низкочастотного частотомера. Делитель можно конструктивно оформить как переходник между входным гнездом и кабелем к источнику сигнала либо встроить в имеющийся любительский частотомер с дополнительным высокочастотным входом. В радиолюбительской литературе уже были опубликованы схемы делителей частоты (например [1, 2]), предназначенных для использования с низкочастотным частотомером. Делитель, описанный в [1], при относительной простоте позволяет увеличить верхнюю частотную границу прибора всего лишь в 10 раз. Делитель частоты из [2] имеет коэффициент деления 100, но, на мой взгляд, его устройство неоправданно усложнено как по номенклатуре примененных деталей, так и по технической реализации. Между тем, используя современную элементную базу, можно значительно упростить схему делителя частоты без необходимости программирования в случае применения микроконтроллера [3]. Описываемый делитель имеет коэффициент деления, равный 100, и диапазон устойчивой работы 25 МГц… 1 ГГц {верхняя граница соответствует паспортному значению частоты входного делители). Чувствительность делителя составляет 20 мВ при входном сопротивлении 50 Ом. Схема делителя приведена на рис. 1. Микросхема U664BS (TELEFUNKEN) представляет собой монолитный цифровой делитель частоты в отношении 1:64. Эта микросхема выполнена по технологии ЭСЛ (змиттерно-связанной логики), ее транзисторы имеют граничную частоту frp = 4,5 ГГц. Диоды с барьером Шотки (VD1, VD2) служат для защиты входа микросхемы DD1 от сигналов большой амплитуды. Как известно, логические уровни ЭСЛ в стандартном включении находятся в области напряжения отрицательной полярности и поэтому они непосредственно не совместимы с логическими уровнями микросхем ТТЛ и КМОП. Для преобразования уровней ЭСЛ в уровни ТТЛ при питании микросхемы ЭСЛ от напряжения плюсовой полярности служит согласующий каскад на транзисторе VT1. Входной сигнал с частотой, поделенной на 64, поступает на следующие два делителя, выполненных на микросхемах DD2 (К555ИЕ20) и DD3 (К155ТЛЗ). Микросхема К555ИЕ20 содержит два четырехразрядных двоично-десятичных счетчика каждый из них имеет триггер со входом С1, выходом 1 и делитель частоты на 5 со входом С2 и выходами 2, 4, 8. В этом устройстве счетчики DD2 работают в режиме делителя частоты на пять со входом С2 и выходом 8. Кстати, исходя из моей практики, верхняя рабочая частота всего устройства определяется максимальной частотой для счетчика DD2.1 (К555ИЕ20), которая по входам С2 обычно не менее 20 МГц, т. е. фактически не менее 1,28 ГГц. Каждый из делителей на DD2.1, DD3.1, DD3.2 и DD2 2, DD3.3. DD3.4 имеет дробный коэффициент деления Кя= 1,25 (или 5/4). Суть использованного способа дробного деления частоты состоит в следующем. Пусть имеется последовательность импульсов, следующих с частотой F (рис. 2) Если из каждой пачки, образованной m импульсами, исключить n импульсов, то средняя частота следовании импульсов в новой последовательности Fo=(m-n)/m*F Коэффициент деления имеет вид отношения двух чисел КД = m/(m-n),: т. е. в общем случае представляет неправильную дробь. В общем виде структурная схема дробного делителя частоты показана на рис. 3. Его основу составляет делитель А1 на целое число т. Формирователь А2 создает импульс длительностью, равной n периодов входной последовательности импульсов.: Устройство совпадения A3 выделяет импульсы числом (m-п) из каждой последовательности в гп импульсов. В нашем случае m = 5 и n = 1. Триггеры Шмитта логических элементов микросхемы D03 позволяют использовать схему совпадения для четкого выделения только четыре> импульсов из каждых пяти входных импульсов, поступающих на счетчики микросхемы DD2. На рис. 4 показаны временные диаграммы поясняющие работу каждого из двух каскадно включенных дробных делителей. Таким образом, если на вход описываемою делителя частоты поступает сигнал частотой, например, F = 1000 МГц, то после первого делителя DD1 частота F2 = F1/64 = 15,625 МГц. После второго делителя (с DD2.1) частота станет равной F2 = F1/1,25 = 12,5 МГц и после третьего — F2/1,25 = 10 МГц Все элементы делителя размещены на плате из фольгированного стеклотекстолита. Чертеж печатной платы представлен на рис. 5. Плату следует поместить в металлический экран. Вход и выход делителя соединяют с частотомером ВЧ кабелем Если частотомер выполнен в виде законченной малогабаритной конструкции, делитель можно конструктивно оформить как переходник между входным гнездом и кабелем к источнику сигнала. Для этого плату нужно поместить в прямоугольный экран, в торцах которого смонтировать разъемы СР-50-75: с одной стороны — штыревую часть разъема, с другой — гнездовую. Делитель частоты был испытан совместно с частотомером, описанным в [4], и показал отличные результаты. 1 Бирюков С. А. Предварительный делитель. — Радио, 1980, № 10, с- 61. 2 Жук В. Предварительный делитель частоты на диапазон 50 .1500 МГц. — Радио, 1992, № 10. с. 46, 47 3 Нечаев И. Делитель частоты диапазона 0.1. .3.5 ГГц. — Радио. 2005. № 9, с. 24—26. 4 Бирюков С. Цифровой частотомер — Радио, 1981, № 10, с. 44 47.

kvarz

Применение бросовых кварцев для получения сигнала

с частотой 100 кГц.При конструировании частотомеров, цифровых шкал, калибраторов, часов возникает необходимость в получении сигнала с эталонной частотой, часто в качестве, которой применяется частота 100 кГц. Для этого, как правило, используют генератор, где частотозадающим элементом обычно является кварц на, так называемую, «точную» частоту (10МГц, 1МГц с применением делителей на 10, либо 100кГц). Однако с этой целью можно применить кварцы частоты, которых содержат не только единицу и нули. Это, так называемые, «бросовые» кварцы. «Бросовые» — потому, что их в свое время надолго бросили в «долгий» ящик.

Рис.1. КГ 70…2300кГц. Рис.2. КГ 2…18,5МГц.

Для кварцев с низкими частотами от 70 до 2300кГц следует применять генератор, показанный на рисунке 1. Он выполнен на трех элементах 2И-НЕ микросхемы К155ЛА3. Подбором величины емкости конденсатора С2 можно в небольших пределах изменять генерируемую частоту.

Для высокочастотных кварцев с частотами 2…18,5МГц следует применять генератор, показанный на рисунке 2. Подстройкой конденсатора С1 генерируемая частота изменяется максимум на 5кГц на самых высоких частотах.

Далее непосредственно к выходу генератора подключают делитель с коэффициентом деления в зависимости от частоты примененного кварца. В делителях применены микросхемы К155ТМ2 если частоту необходимо разделить на 2, 4, 8, 10, К155ИЕ4 при делении на 2, на 6 или 12, и К155ИЕ5 при делении на 2, на 8 или 16. При коэффициенте деления 10 применяются все выше указанные микросхемы, а также К155ИЕ2. Применение этих микросхем обусловлено необходимостью получения на выходе сигнала в форме симметричного меандра, каковой обычно присутствует на выходе вышеуказанных генераторов.

Ниже приводится таблица №1, в которой указаны частоты кварцев, где для получения частоты 100кГц при делении используются микросхемы К155ТМ2 и К155ИЕ4.

Таблица №1.

|

Частота кварца кГц |

Кделения К155ТМ2 |

К деления К155ИЕ4 |

|

12000 |

:10 |

:2 :6 |

|

9600 |

:2 :2 :2 :2 |

:6 |

|

9600 |

:2 :2 :2 |

:2 :6 |

|

6000 |

:10 |

:6 |

|

4800 |

:2 :2 |

:2 :6 |

|

2400 |

:2 |

:2 :6 |

|

2400 |

:2 :2 |

:6 |

|

1200 |

:2 :6 | |

|

600 |

:6 |

В таблице №2 указаны частоты кварцев, используемые для получения частоты 100кГц, когда в делителях применяются микросхемы К155ТМ2 и К155ИЕ5.

Таблица №2.

|

Частота кварца кГц |

К деления К155ТМ2 |

К деления К155ИЕ5 |

|

12800 |

:2 :2 :2 :2 |

:8 |

|

12800 |

:2 :2 :2 |

:2 :8 |

|

8000 |

:2 :2 :2 |

:10 |

|

8000 |

:10 :2 :2 :2 |

|

|

6400 |

:2 :2 |

:2 :8 |

|

3200 |

:2 :2 |

:8 |

|

3200 |

:2 |

:2 :8 |

|

1600 |

:2 :8 | |

|

800 |

:8 |

В таблице №3 указаны частоты кварцев, используемые для получения частоты 100кГц, когда в делителях применяются микросхемы К155ИЕ4 и К155ИЕ5.

Таблица №3.

|

Частота кварца кГц |

К деления К155ИЕ4 |

К деления К155ИЕ5 |

|

12800 |

:8 :16 | |

|

12000 |

:12 |

:10 |

|

9600 |

:12 |

:8 |

|

8000 |

:10 |

:8 |

|

7200 |

:12 :6 |

|

|

6400 |

:8 :8 | |

|

6000 |

:6 |

:10 |

|

4800 |

:6 |

:8 |

|

3600 |

:6 :6 |

Микросхема К155ТМ2 содержит 2 независимых D – триггера объединенных общей цепью питания. Эти триггеры показаны на рисунках 3 и 4.

Рис.3. Делитель на 2. Рис.4. Делитель на 2. Рис.5. Делитель на 2 и на 6.

Для превращения его в счетный триггер необходимо инверсный выход триггера соединить с входом D (6 с 2 и 8 с 12). Входной сигнал подается на вход С. Таким образом из одой микросхемы получается 2 делителя с коэффициентом деления 2. Если выход первого делителя соединить с входом второго, то получится делитель на 4. Использовав аналогичным образом еще один корпус такой же микросхемы получим делители на 8 и 16.

На рисунке 5 показана микросхема К155ИЕ4, в состав которой входят 2 делителя: на 2 и на 6. Если на вход С1 (14) подать сигнал с частотой 200кГц, то на выводе 12 будет присутствовать частота 100кГц (форма – симметричный меандр). Если на вход С2 подать сигнал 600кГц, то на выводе 8 получим сигнал 100кГц. Если вывод 1 микросхемы соединить с выводом 12, как показано на рисунке 6, то получим делитель на 12.

Рис.6. Делитель на 12. Рис.7.Делитель на 2 и на 8. Рис.8. Делитель на 16.

На рисунке 7 показана микросхема К155ИЕ5. Ее можно использовать как делитель на 2, если подать сигнал на вывод 14, а снимать с вывода 12, и как делитель на 8, если подать сигнал на вывод 1, а снимать с вывода 11. Если вывод 12 этой микросхемы соединить с выводом 1, а сигнал подавать на вывод 14, то на выводе 11 получим сигнал с частотой деленной на 16. Такой делитель показан на рисунке №8.

Рис. 9. Делитель на 32.На рисунке №9 показан делитель на 32. Он выполнен на одном элементе микросхемы К155ТМ2 и на микросхеме К155ИЕ5 включенной как делитель на 16.

Рис. 10. Делитель на 32.В отличие от предыдущей схемы делитель на 32 показанный на рисунке 10 выполнен на двух элементах К155ТМ2, а К155ИЕ5 включена как делитель на 8.

В некоторых случаях возникает необходимость установки делителей в нулевое состояние. Реализовать систему сброса делителей в нулевое состояние можно по схеме показанной на рисунке №11. Для этого использован элемент 2И-НЕ микросхемы К155ЛА3 оставшийся свободным при реализации генераторов по рисункам №1 и №2. Кстати, во всех схемах делителей приведенных в этой статье и выполненных на микросхемах К155ТМ2 и К155ИЕ4, а также К155ТМ2 и К115ИЕ5 в случае возникновения необходимости введения системы сброса следует использовать данную схему.

Рис. 11. Делитель на 32 с установкой в нулевое состояние.Все микросхемы К155ИЕ4 и К155ИЕ5 последующих делителей следует подключать к выходу элемента DD1.4 (11). Так как нагрузочная способность микросхемы К155ЛА3 для микросхем однотипной серии составляет 10, то можно подключить 5 корпусов микросхем (ибо у каждой микросхемы подключается по 2 входа). Если исключить из схемы резистор R1, то схема останется работоспособной, так как на входах 12, 13 DD1.4 останется «грязная» единица, однако схема будет работать надежнее, если через R1 подана «чистая» логическая единица. Вместо SA1 можно подключить выход логического элемента участвующего в цепях установки в ноль других делителей.

Рис. 12. Делитель на 48.На рисунке №12 показан делитель на 48. Он выполнен на двух триггерах микросхемы К155ТМ2 и микросхеме К155ИЕ4, включенной как делитель на двенадцать.

Рис. 13. Делитель на 64. Рис. 14. Делитель на 24.

На рисунке 13 показан делитель на 64. Он выполнен на двух триггерах микросхемы К155ТМ2 и микросхеме К155ИЕ5 включенной как делитель на 16. На рисунке 14 показан делитель на 24. Он состоит из делителя на 2 (один элемент К155ТМ2) и делителя на 12 (К155ИЕ4).

Рис. 15. Делитель на 10. Рис. 16. Делитель на 10.

Рис.17.Делитель на 10. Рис.18.Делитель на 10. Рис.19.Делитель на 10.

В том случае, когда согласно таблицам №1, №2, №3 возникает необходимость использовать делитель, в состав которого входит делитель на 10, то следует использовать делители, показанные на рисунках №15 … №19. Следует помнить, что только у одного из этих делителей показанного на рисунке №17, на выходе присутствует сигнал в виде симметричного меандра. Это происходит потому, что он включен в режим счета «двумя пятерками». В результате триггер, делящий частоту на 2 (в состав микросхемы К155ИЕ2 входят делители на 2 и на 5) оказывается включенным последним, что и приводит к указанному выше эффекту. Чтобы и в остальных делителях, в состав которых входят оставшиеся делители на 10, на выходе получился правильный меандр, необходимо последним на выходе устанавливать либо делитель на 2 (К155ТМ2), либо делители, выполненные на микросхемах К155ИЕ4 и К155ИЕ5 приведенные в этой статье, с коэффициентом деления отличным от 10. Так в делителе с коэффициентом 120 первым следует поставить делитель на 10 (например, рис.15), а последним делитель на 12 (рис.6). Делитель, показанный на рисунке 16, считает в весовом коде 1-2-4-8 (двоично-десятичный код).

Рис. 20. Делитель на 128.На рисунке 20 показан делитель на 128, выполненный на четырех триггерах микросхем К155ТМ2 (2 корпуса) и микросхеме К155ИЕ5 включенной как делитель на 8. Делитель с аналогичным коэффициентом деления можно выполнить и по схеме показанной на рисунке №21 использовав 3 триггера К155ТМ2, а делитель на К155ИЕ5 включив как делитель на 16 (согласно рисунку №8).

Рис. 21. Делитель на 96.На самом же рисунке 21 показан делитель на 96.

Рис. 22. Делитель на 96. Рис. 23. Делитель на 64.

Делитель с коэффициентом деления 96 можно выполнить и так, как показано на рисунке 22. Здесь использованы 2 микросхемы. К155ИЕ4 включена как делитель на 12, а К155ИЕ5 как делитель на 8. На рисунке 23 показан делитель на 64. Обе микросхемы К155ИЕ5 включены как делители на 8.

Рис. 24. Делитель на 128. Рис. 25. Делитель на 120.

На рисунке 24 показан делитель на 128 выполненный на микросхемах К155ИЕ5. Первая включена как делитель на 8, вторая – на 16. Делитель на 120, показанный на рисунке 25 выполнен на К155ИЕ5 (делитель на 10) и на К155ИЕ4 (делитель на 12).

Рис. 26. Делитель на 80. Рис. 27. Делитель на 72.На рисунке 26 показан делитель на 80. К155ИЕ4 включена как делитель на 10, а К155ИЕ5 – на 8. На рисунке 27 – делитель на 72. Первая К155ИЕ4 включена как делитель на 12, вторая – на 6.

Рис. 28. Делитель на 60. Рис. 29. Делитель на 48.На рисунке 28 показан делитель на 60. К155ИЕ5 включена как делитель на 10, К155ИЕ4 – на 6. На рисунке 29 – делитель на 48. К155ИЕ4 включена как делитель на 6, К155ИЕ5 – на 8.

Рис. 30. Делитель на 36. Рис.31. Делитель на 80 с установкой в ноль.На рисунке 30 показан делитель на 36. Обе микросхемы К155ИЕ4 включены как делители на 6. На рисунке 31 показан делитель на 80 с системой установки в ноль. Система сброса реализована на микросхеме К155ЛА3. Все особенности схемы показанной на рисунке 11 в равной мере относятся и к этой схеме. Аналогично система сброса организуется и в других схемах представленных в данной статье, которые выполнены на двух микросхемах — К155ИЕ4 и К155ИЕ5, причем первая должна стоять К155ИЕ4 и на ней должен быть реализован делитель на 10. Если первой стоит микросхема К155ИЕ5, включенная как делитель на 10, то систему установки в ноль следует реализовать, как показано на рисунке 32 (делитель на 60). Входы установки в ноль всех последующих делителей выполненных на микросхемах К155ИЕ4 и К155ИЕ5 следует подключать к выводу 8 элемента DD3.3 (не более 5 штук).

Рис.32. Делитель на 60 Рис.33. Делитель на 48 с установкой в ноль. с установкой в ноль.

Если в делителях собранных на К155ИЕ4 и К155ИЕ5 микросхемы включены с коэффициентом деления отличным от десяти, то систему установки в ноль следует организовать, как показано на рисунке №33 (делитель на 48).

Все микросхемы указанные в данной статье питаются напряжением 5 вольт. Напряжение +5 вольт на К155ЛА3 и К155ТМ2 подается на вывод 14, а -5 вольт (корпус) – на вывод 7. На микросхемы К155ИЕ2, К155ИЕ4, К155ИЕ5 напряжение +5 вольт подается на вывод 5, а -5 вольт (корпус) – на вывод 10.

Рубцов В.П. UN7BV Казахстан, Астана

[email protected] 73!73!

Выносной щуп — делитель частоты на 10 для частотомера FC250

Эксплуатация частотомера FC250 с выносным щупом (ВЩ), передающим сигнал на той же частоте, выявила нестабильность его показаний и перегрев микросхемы DD2 на плате частотомера FC250 [1] на частотах более 150 МГц. Эта частота является предельной для большинства микросхем, применённых в предварительных усилителях-формирователях (ПУ) и на входе FC250. Поэтому был изготовлен новый ВЩ, схема которого с ПУ приведена на рис. 1. ПУ собран по схеме рис. 1 из [1], изменены номиналы некоторых элементов. ВЩ собран на двух микросхемах: DA1 (ADCMP604KSZ-R2) — КМОП-компараторе, имеющем время задержки 1,6 нс, входное дифференциальное сопротивление до 70 кОм, и делителе частоты на 10 — DD1 (КС193ИЕ3) [2], имеющем рабочий диапазон частот от 100 кГц до 270 МГц.

Рис. 1. Схема выносного щупа с ПУ

Способ подачи напряжения смещения на входы компаратора DA1 с помощью резисторов R3-R7 позволяет подстроечным резистором R3 изменять напряжение гистерезиса и регулировать чувствительность ВЩ. Высоким входным сопротивлением компаратора ADCMP604, достигающим 70 кОм, объясняется большое сопротивление резисторов R4 и R5, выбранное так, чтобы наименее шунтировать входы компаратора. Выходы компаратора DA1 подключены к входам делителя DD1 без разделительных конденсаторов через согласующие резисторы R8-R10, которые нужны для того, чтобы исключить подачу на входы делителя противофазного напряжения более 2 В в статическом режиме.

В отличие от своего прототипа SP8690A, КС193ИЕ3 не является в полной мере микросхемой стандарта ЭСЛ, напряжение смещения на её входах (выводы 11 и 12) соответствует стандарту PECL, что даёт возможность соединять их напрямую с выходами компаратора ADCMP604 стандарта LVDS. При этом противофазный сигнал прямоугольной формы с ADCMP604 подаётся сразу на оба дифференциальных входа делителя, что позволяет работать ВЩ практически во всём диапазоне рабочих частот КС193ИЕ3.

В статическом режиме разность напряжений на входах микросхемы КС193ИЕ3 0,5 В предотвращает её самовозбуждение, а подача противофазного сигнала уровня LVDS (0,35 В) позволила с новым ВЩ получить диапазон измеряемых FC250 частот от 400 кГц до 270 МГц при малой входной ёмкости, большом входном сопротивлении и дискретности измерения в 100 Гц. На участке от 1 до 200 МГц чувствительность частотомера FC250 с ВЩ не хуже 0,35 В, в режиме «мягкого» управляемого самовозбуждения компаратора DA1 не хуже 0,2 В, а по краям диапазона измерений не хуже 0,65 В.

Не было цели добиваться нижней границы рабочей частоты делителя КС193ИЕ3 в 100 кГц. Но при увеличении ёмкости конденсаторов С1 и С2 до 43 пФ нижняя рабочая частота ВЩ становилась менее 300 кГц.

Напряжение питания +5 В подаётся на ВЩ от стабилизатора напряжения частотомера FC250, потребляемый ток — приблизительно 35 мА. Вывод 6 делителя КС193ИЕ3, выход ТТЛ с открытым коллектором, не задействован и оставлен неподключённым. С его выводов 2 и 4 противофазный сигнал стандарта ЭСЛ по шлейфу длиной 0,3-1 м подаётся на входы ПУ, который размещён на плате FC250 и формирует сигналы уровня ТТЛ, необходимые для работы частотомера [1, 3].

Резистор R12 установлен на конце шлейфа, в месте его соединения с ПУ. Оба дифференциальных входа ВЩ равноценны, они не соединены ни с общим проводом, ни с линией питания частотомера.

При работе оба контакта ВЩ подключают к измеряемому объекту. Для удобства один из контактов ВЩ можно подключать к общему проводу измеряемого устройства отрезком провода длиной до 10 см с зажимом «крокодил» на конце. Применение ВЩ позволяет измерять частоту сигналов уровней ТТЛ и ЭСЛ, частоту гетеродинов различных типов радиоприёмников в диапазонах от ДВ до УКВ-2 при небольшом влиянии ёмкости ВЩ на их частоту. На диапазонах с большим перекрытием по частоте, в частности УКВ-2, из-за снижения напряжения гетеродина на низкочастотном участке частоту удаётся измерить только в режиме управляемого самовозбуждения ВЩ, тогда как подключение других щупов, с меньшим входным сопротивлением, приводило к срыву генерации. В случае недостаточного уровня измеряемого сигнала, при уста-новке малого уровня чувствительности ВЩ и в случае плохого контакта щупа с измеряемым устройством происходит занижение или срыв показаний частотомера. При подаче на ВЩ сигнала частотой 100-200 МГц и напряжением более 0,5 В, имеющего неправильную форму, компаратор DA1 может удваивать частоту. В этом случае для уменьшения напряжения сигнала ВЩ подключают к источнику сигнала через аттенюатор, детали которого можно припаять прямо к контактам ВЩ. Частотомер FC250 по-прежнему может измерять сигналы частотой от 50 Гц до 100 МГц с дискретностью 10 Гц. Для этого вместо шлейфа с ВЩ к конденсаторам С6 и С7 на входе ПУ [1] подключают провода длиной до 20 см с ограничительными резисторами сопротивлением до 1 кОм.

ВЩ собран на плате из фольгированого с двух сторон стеклотекстолита толщиной 1,5 мм. Плата изготовлена методом прорезания фольги после высверливания на ней отверстий. Чертёж платы показан на рис. 2. ПУ можно собрать на плате по рис. 2 в [1].

Рис. 2. Чертёж платы выносного щупа

В устройстве применены конденсаторы и резисторы, за исключением R3 и R12, для поверхностного монтажа типоразмера 1206 или 0805. Переменный резистор R3 — 3310Y или любой другой, подходящий по размерам и расположению выводов. Резистор R12 — выводной, мощностью 0,125 Вт, расположен на конце шлейфа, соединённом с ПУ Компаратор DA1 — для поверхностного монтажа в корпусе SOT 323-6, делитель КС193ИЕ3 (в корпусе DIP-16) установлен в панель, из которой вынуты незадействованные контакты. При установке микросхемы КС193ИЕ3 непосредственно на плату у её неподключённых выводов удаляют концы, вставляемые в отверстия.

Расположение деталей показано на рис. 3. Перемычки на контактных площадках для проводов шлейфа, предотвращающие отслоение фольги при их распайке, и контакты ВЩ изготовлены из лужёного провода диаметром 0,75 мм. Остальные перемычки и «прошивка» краёв платы выполнены лужёным проводом диаметром 0,5 мм. Фотография нижней стороны печатной платы приведена на рис. 4. Правильно собранный ВЩ налаживания не требует. Если самовозбуждение ВЩ не устраняется резистором R3, то основная причина этого — обрыв (плохая пайка) одного из выходов компаратора DA1. Щуп помещён в пластмассовый корпус. Крепёжные отверстия сверлят «по месту» на облу-женных краях платы ВЩ. Можно просто обмотать щуп липкой лентой, оставив снаружи контакты и шлиц подстроечного резистора R3.

Рис. 3. Расположение деталей на плате ВЩ

Рис. 4. Фотография нижней стороны печатной платы

На рис. 5 приведён пример измерения максимальной частоты 300 МГц.

Рис. 5. Пример измерения максимальной частоты 300 МГц

Литература

1. Паньшин А. Предварительный усилитель-формирователь для частотомера FC250. — Радио, 2015, № 2, с. 18-20.

2. Хлюпин Н. СВЧ-делители частоты. — URL: http://ra4nal.qrz.ru/prescaler.shtml (19.02.15).

3. Нечаев И. Щуп-компаратор для частотомера. — Радио, 2014, № 7, с. 20.

Автор: А. Паньшин, г. Москва

Приставка — делитель частоты 1:100

Представленный делитель является приставкой к цифровому измерителю частоты. Благодаря его использованию возможно измерение частоты до 1,2 ГГц измерителем частоты с максимальным диапазоном измерений 10 МГц. Во входном каскаде делителя работает монолитный цифровой делитель ECL, который входную частоту делит в соотношении 1 : 64.

Вход микросхемы предохранен от повреждения сигналами со слишком большой амплитудой диодами Шотки. Устройство хорошо работает при частотах от 30 МГц до 1,2 ГГц. Чувствительность делителя равна ~20 мВ при входном сопротивлении 50 Ом.

Входная частота, деленная на 64, поступает на следующие делители с соотношением 5/4. Транзистор Т1 доводит уровень ECL к стандарту TTL. Роль делителей 5/4 выполняет микросхема 74LS390, имеющая в своей структуре 2 бинарных десятичных счетчика.

Каждый из них имеет делитель на 2 и на 5. Разделение 5/4 состоит в том, что из каждых пяти входных импульсов пропускаются только 4. Если на вход делителя поступает 1600 импульсов, то после деления на 64 их будет 25. После прохождения через первый делитель их будет 20, а после прохождения через второй — 16. Таким образом реализуется деление на 100.

Следует помнить об умножении показаний измерителя частоты, работающего с делителем на 100.

Устройство можно встроить в имеющийся измеритель частоты или использовать в качестве щупа. Выводы элементов, использованных для делителя, должны быть как можно короче. Интегральные микросхемы следует впаять непосредственно в плату. После монтажа всю приставку следует заэкранировать.

Делитель требует напряжения питания 5 В. Прототипная схема потребляла ~70 мА.

| US1 | U664 |

| US2 | 74LS390 |

| US3 | 74LS132 |

| D1, D2 | ВАТ86 |

| Т1 | BF414 |

| С5 | 47 нФ |

| С7 | 100 нФ |

| R1 | 1,2 кОм |

| R2 | 47 Ом |

| R3 | 150 Ом |

| 01,02,03 | 1 нФ |

| С4 | 10 нФ |

| С6 | 47 мкФ (тантал.) |

Внимание! После монтажа схемы следует соединить между собой выводы интегральной микросхемы US3 (74LS132).

ВРЛ — 100 лучших радиоэлектронных схем, 2004.

Счетчики Микросхемы последовательностного типа Справочник по микросхемам ТТЛ и КМОП Любительская Радиоэлектроника

Счетчики

В состав рассматриваемых серий ТТЛ-микросхем входит большое число счетчиков и делителей частоты, различающихся по своим свойствам и назначению.

Микросхема К155ИЕ1 (рис. 24) — делитель частоты на 10. Установка триггеров микросхемы в 0 осуществляется подачей лог. 1 одновременно на два объединенных по схеме И входа R. Рабочая полярность входных счетных импульсов, подаваемых на входы С, отрицательная. Импульсы можно подавать или отдельно на каждый из входов (на второй вход должна при этом подаваться лог. 1), или одновременно на оба входа. Одновременно с каждым десятым входным импульсом на выходе формируется равный ему по длительности выходной импульс отрицательной полярности. Многокаскадные делители частоты можно строить, соединяя входы С последующих каскадов с выходами предыдущих.

Микросхемы ИЕ2, К155ИЕ4 и ИЕ5 (рис. 25) содержат по четыре счетных триггера. В каждой микросхеме один из триггеров имеет отдельный вход С1 и прямой выход, три оставшихся триггера соединены между собой так, что образуют делитель на 8 в микросхеме ИЕ5, на 6 в К155ИЕ4 и на 5 в ИЕ2.

При соединении выхода первого триггера с входом С2 цепочки из трех триггеров образуются соответственно делители на 16, 12 и 10. Делители на 10 и 16 работают в коде 1-2-4-8, делитель на 12 — в коде 1-2-4-6. Микросхемы имеют по два входа R установки в 0, объединенные по схеме И. Сброс (установка в 0) триггеров производится при подаче лог. 1 на оба входа R. Микросхема ИЕ2 имеет, кроме того, входы R9 для установки в состояние 9, при котором первый и последний триггеры декады находятся в единичном состоянии, остальные — в нулевом.

Наличие входов установки, объединенных по схеме И, позволяет строить делители частоты с различными коэффициентами деления в пределах 2-6 без использования дополнительных логических элементов. На рис. 26 приведены схема декады на микросхеме К155ИЕ4 и ее временная диаграмма. До прихода десятого импульса декада работает как делитель частоты на 12. Десятый импульс переводит триггеры микросхемы в состояние 10, при котором на выходах 4 и 6 микросхемы формируются уровни лог. 1.

Эти уровни, поступая на входы R микросхемы, переводят ее в 0, в результате чего коэффициент пересчета К становится равным 10.

Для установки рассмотренной декады в 0 внешним сигналом необходимо введение в нее логических элементов И-НЕ (рис 27).

В табл. 4 приведены номера выводов микросхем, которые нужно соединить между собой для получения различных К Все делители, полученные соединением выводов по табл. 4, работают по одному принципу — при достижении состояния, соответствующего необходимому коэффициенту пересчета, происходит установка счетчика в 0. Исключение составляет делитель на 7 на микросхеме ИЕ2. В этом делителе после подсчета шести импульсов на входах R9 формируются уровни лог. 1, поэтому из состояния 5 делитель сразу переходит в состояние 9, минуя 6,7 и 8. Код работы этого делителя — невесовой.

Делители на микросхемах ИЕ5 и ИЕ2 работают в весовом коде 1-2-4-8, на микросхеме К155ИЕ4 — в коде 1-2-4-6 при использовании входа 14 и в коде 1-2-3 — при использовании входа 1.

Микросхемы ИЕ6 и ИЕ7 — реверсивные счетчики. Первый из них — двоично-десятичный, второй — двоичный Оба работают в коде 1-2-4-8 Цоколевка обеих микросхем одинакова (рис 28), различие в том, что первый считает до 10, второй до 16.

Таблица 4

| К |

К155ИЕ2 |

К155ИЕ4 | К155ИЕ5 | ||||||

| Вход | Вых. | Соединить выводы | Вход | Вых. | Соединить выводы | Вход | Вых. | Соединить выводы | |

| 2 | 14 | 12 | 14 | 12 | — | 14 | 12 | — | |

| 3 | 1 | 8 | 9-2,8-3 | 1 | 9 | — | 1 | 8 | 9-2,8-3 |

| 4 | 1 | 8 |

11-2-3 |

1 | 8 | 11-6,8-7 | 1 | 8 | — |

| 5 | 1 | 11 | — | 1 | 8 | 9-6,8-7 | 1 | 11 | 9-2,11-3 |

| 6 | 14 | 8 | 12-1,9-2,8-3 | 1 | 8 | — | 1 | 11 | 8-2,11-3 |

| 7 | 14 | 11 | 12-1,9-6,8-7 | 14 | 8 | 12-1-6,8-7 | — | — | — |

| 8 | 14 | 8 | 12-1,11-2-3 | 14 | 8 | 12-1,11-6,8-7 | 1 | 11 | — |

| 9 | 14 | 11 | 12-1-2,11-3 | — | — | — | 14 | 11 | 12-1-2,11-3 |

| 10 | 14 | 11 | 12-1 | 14 | 8 | 12-1,9-6,8-7 | 14 | 11 | 12-1,9-2,11-3 |

| 12 | — | 14 | 8 | 12-1 | 14 | 11 | 12-1,8-2,11-3 | ||

| 16 | — | — | — | — | — | — | 14 | 11 | 12-1 |

Рассмотрим для примера работу микросхемы ИЕ6 В отличие от рассмотренных ранее счетчиков, эта микросхема имеет большее число выходов и входов Входы +1 и -1 служат для подачи тактовых импульсов, +1 — при прямом счете, -1 — при обратном. Вход R служит для установки счетчика в 0, вход L — для предварительной записи в счетчик информации, поступающей по входам D1 — D8.

Установка триггеров счетчика в 0 происходит при подаче лог 1 на вход R, при этом на входе L должна быть лог. 1. Для предварительной записи в счетчик любого числа от 0 до 9 его код следует подать на входы D1 — D8 (D1 — младший разряд, D8 — старший), при этом на входе R должен быть лог 0, и на вход L подать импульс отрицательной полярности

Режим предварительной записи можно использовать для построения делителей частоты с перестраиваемым коэффициентом деления для учета фиксированной частоты (например, 465 кГц) в цифровой шкале радиоприемника Если этот режим не используется, на выходе L должен постоянно поддерживаться уровень лог 1

Прямой счет осуществляется при подаче импульсов отрицательной полярности на вход +1, при этом на входах -1 и L должна быть лог 1, на входе R — лог 0 Переключение триггеров счетчика происходит по спадам входных импульсов, одновременно с каждым десятым входным импульсом на выходе >=9 формируется отрицательный выходной импульс переполнения, который может подаваться на вход +1 следующей микросхемы многоразрядного счетчика Уровни на выходах 1-2-4-8 счетчика соответствуют состоянию счетчика в данный момент (в двоичном коде) При обратном счете входные импульсы подаются на вход -1, выходные импульсы снимаются с выхода <=0 Пример временной диаграммы работы счетчика приведен на рис. 29.

Первый импульс установки в 0 устанавливает все триггеры счетчика в 0. Три следующих импульса, поступающих на вход +1, переводят счетчик в состояние 3, которому соответствуют лог. 1 на выходах 1 и 2 и лог 0 — на 4 и 8. Если на входах D1 — D4 лог. 0, на входе D8 лог. 1, импульс на входе L устанавливает счетчик в состояние 8.

Следующие шесть импульсов, поступающие на вход +1, переводят счетчик последовательно в состояния 9,0,1,2,3,4 Одновременно с импульсом, переводящим счетчик в 0, на выходе S9 появляется выходной импульс прямого счета Следующие импульсы, поступающие на вход -1, изменяют состояние счетчика в обратном порядке 3, 2, 1,0,9,8 и т д.

Одновременно с импульсом обратного счета, переводящим счетчик в состояние 9, на выходе <=0 появляется выходной импульс.

В микросхеме ИЕ7 импульс на выходе =>15 появляется одновременно с импульсом на входе +1 при переходе счетчика из состояния 15 в состояние 0, а на выходе <=0 — при переходе счетчика из 0 в 15 одновременно с импульсом на входе -1.

Предельная частота функционирования микросхем К155ИЕ6, К155ИЕ7 — 15 МГц, К555ИЕ6 и К555ИЕ7 — 25 МГц, КР1533ИЕ6 и КР1533ИЕ7 — 30 МГц.

Микросхему К155ИЕ8 обычно называют делителем частоты с переменным коэффициентом деления, однако это не совсем точно. Эта микросхема содержит шестиразрядный двоичный счетчик, элементы совпадения, позволяющие выделять не совпадающие между собой импульсы — каждый второй, каждый четвертый, каждый восьмой и т. д. и управляемый элемент И-ИЛИ, который позволяет подавать на выход часть или все выделенные импульсы, в результате чего средняя частота выходных импульсов может изменяться от 1/64 до 63/64 частоты входных импульсов.

Графическое обозначение микросхемы приведено на рис. 30, пример временной диаграммы ее работы — на рис. 31. Для наглядности на рис. 30 вынесен логический элемент И-НЕ, входящий в микросхему.

Микросхема имеет следующие входы: инверсный вход ЕС — разрешения счета, при подаче на который лог. 1 счетчик не считает, вход R — установки 0, установка триггеров счетчика в 0 происходит при подаче на него лог. 1; вход С — вход тактовых импульсов отрицательной полярности, переключение триггеров счетчика происходит по спадам входных импульсов; входы XI — Х32 позволяют управлять выдачей отрицательных выходных импульсов, совпадающих по времени с входными, на выход Z. На рис. 31 в качестве примера показано, какие импульсы выделяются на выходе Z при подаче лог. 1 на входы:

Х32 (диаграмма Х32), Х16 (диаграмма Х16) и Х8 (диаграмма Х8). В этих случаях на выходе Z выделяется соответственно 32, 16 или 8 равномерно расположенных импульсов. Если же одновременно подать лог. 1 на несколько входов, например, на Х32 и Х8, то, как показано на диаграмме Z, на выходе Z выделится 40 импульсов, но расположенных неравномерно. В общем случае число импульсов N на выходе Z за период счета составит

N = 32 х Х32 + 16 х Х16 + 8 х Х8 + 4 х Х4 + 2 х Х2 + X1, где X1-Х32 принимают значения соответственно 1 или 0 в зависимости от того, подана или нет лог.2 импульсов. Число импульсов на выходе подсчитывается по формуле, аналогичной приведенной выше, в которой коэффициенты имеют значения от 2048 до 1. Если требуется соединить большее число делителей, их соединение производится аналогично рис. 32.

Однако выходной элемент И-НЕ, выполняющий функцию ИЛИ-НЕ для отрицательных импульсов, поступающих с выходов Z делителей, необходимо использовать из отдельной микросхемы И-НЕ или И.

Микросхема ИЕ9 (рис. 33) — синхронный десятичный счетчик с возможностью параллельной записи информации по фронту тактового импульса, имеет девять входов. Подача лог. 0 на вход R независимо от состояния других входов приводит к установке триггеров микросхемы в состояние 0. Для обеспечения режима счета на входе R необходимо подать лог. 1, тот же сигнал должен быть подан на входы разрешения параллельной записи EL, разрешения ЕС, разрешения выдачи сигнала переноса ER Изменение состояния триггеров счетчика при счете происходит по спаду импульсов отрицательной полярности, подаваемых на вход С.

При подаче лог. 0 на вход EL микросхема переходит в режим параллельной записи информации со входов D1 — D8. Запись происходит по спадам импульсов отрицательной полярности на входе С, что позволяет использовать микросхему в режиме сдвигающего регистра. При записи на входе R должна быть лог. 1, сигналы на входах ЕС и ЕР произвольны.

На выходе переноса Р лог. 1 появляется в том случае, когда счетчик находится в состоянии 9, а на входе ЕР — лог. 1, в остальных случаях на выходе Р лог. 0. Подача лог. 0 на вход ЕР запрещает выдачу лог. 1 на выходе Р и счет импульсов. Подача лог. 0 на вход ЕС запрещает счет, но не запрещает выдачу сигнала переноса. Сигнал запрета счета (лог. 0 на входах ЕС и ЕР) действует лишь в том случае, если он полностью перекрывает по длительности импульс отрицательной полярности на входе С, в том числе он может совпадать с ним по времени.

Для обеспечения параллельной записи лог. 0 на вход EL информация на входы D1 — D8 может быть подана как при лог. 1, так и при лог. 0 на входе С и удерживаться до момента перехода лог. 0 на входе С в лог. 1, когда и произойдет запись.

Для обеспечения счета с числа, введенного в микросхему при параллельной записи, лог 0 на входе EL должен быть изменен на лог. 1 или одновременно с переходом лог. 0 в лог. 1 на входе С, или при лог. 1 на входе С.

На рис. 34 (а) приведена схема соединения микросхем ИЕ9 в многоразрядный синхронный счетчик, которая снижает быстродействие счетчика, так как для его нормальной работы необходимо, чтобы сигнал переноса от младшего разряда прошел через все микросхемы до старшего разряда до подачи очередного тактового импульса. Для получения максимального быстродействия многоразрядного счетчика, равного быстродействию отдельной микросхемы, микросхемы можно соединить по схеме рис. 34 (б). В этом случае сигнал переноса с выхода Р микросхемы DD1 разрешает работу остальных микросхем, соединенных в счетчик по схеме рис. 34 (а), лишь в те моменты, когда микросхема DD1 находится в состоянии 9, поэтому от счетчика DD2 — DD9 требуется быстродействие в 10 раз меньшее быстродействия микросхемы DD1, что обеспечивается при любой практически встречающейся длине счетчика.

Как уже указывалось выше, микросхемы ИЕ9 могут работать в режиме сдвигающего регистра. Для обеспечения такого режима необходимо входы D1 — D8 соединить с выходами 1-2-4-8 в нужном порядке. Для сдвига информации на один двоичный разряд по каждому тактовому импульсу в сторону старших разрядов соединение необходимо произвести в соответствии с рис. 35 (а). Для обеспечения динамической индикации удобно сдвигать информацию сразу на один десятичный разряд, а сдвигающий регистр замыкать в кольцо. Такая возможность проиллюстрирована на рис. 36.

На рис. 36 не показаны цепи подачи импульсов и управляющих сигналов, которые могут быть выполнены в соответствии с рис. 34 (а) или 34 (б). Роль входа разрешения сдвига выполняет вход Запись. Естественно, что при соединении микросхем в соответствии с рис. 35,36 параллельная запись информации в микросхемы невозможна.

Микросхемы ИЕ9 удобно использовать в делителе с переключаемым коэффициентом пересчета.м (длительность импульсов отрицательной полярности равна периоду входных импульсов).

Если делитель собран по схеме рис. 34 (б), инвертор DD3 необходимо заменить на двухвходовый элемент И-НЕ, второй вход которого подключить к выходу переноса Р первой микросхемы делителя.

Микросхема ИЕ10 (рис. 38) по своему функционированию аналогична микросхеме ИЕ9 и отличается от нее тем, что считает в двоичном коде, и ее коэффициент пересчета равен 16. В остальном ее работа и правила включения те же.

Микросхема ИЕ11 — десятичный синхронный счетчик (рис. 38). Логика его работы соответствует логике работы счетчиков ИЕ9. Отличие лишь в том, что для сброса в состояние 0 счетчика ИЕ9 необходима подача на вход R лог. 0, а для сброса в состояние 0 счетчика ИЕ11 кроме подачи на вход ER (разрешение уст. 0) лог. 0

необходима подача тактового импульса отрицательной полярности на вход С, по спаду которого и происходит сброс счетчика. Таким образом, все изменения выходных сигналов этой микросхемы происходят по спаду импульсов отрицательной полярности на входе С.

Микросхема КР1533ИЕ12 (рис. 39) обеспечивает параллельную запись и режим счета. Входы Dl, D2, D4, D8 служат для подачи сигналов кода при параллельной записи информации. Запись в триггеры счетчика происходит асинхронно при поступлении на вход L лог. 0 независимо от состояния других входов. При лог. 1 на входе L и лог. 0 на входе разрешения работы Е счетчик изменяет состояние по спадам импульсов отрицательной полярности на входе С. Направление счета определяется сигналом на входе D/U: при лог. 0 происходит счет вверх, при лог. 1 — вниз.

Для построения многоразрядных счетчиков у микросхемы есть два специальных выхода: последнего состояния 0/9 и переноса Р. На выходе 0/9 лог. 1 появляется при достижении состояния 9 при прямом счете и состояния 0 при обратном. В остальных случаях на выходе 0/9 — лог. 0. При наличии лог. 1 на выходе 0/9 и лог. 0 на входе Е одновременно с импульсом на входе С на выходе переноса Р появляется импульс отрицательной полярности и той же длительности.

Счетчик КР1533ИЕ12 не имеет входа установки в 0. Для этой цели на входы Dl, D2, D4, D8 подают лог. 0, а на вход L — импульс отрицательной полярности. Смена сигналов на входах D/U и Е должна происходить в момент переключения сигнала на входе С из лог. 0 в лог. 1 или в паузе между импульсами на входе С (то есть при лог. 1 на этом входе).

Пример временной диаграммы работы счетчика представлен на рис. 40. По импульсу отрицательной полярности на входе L записываются сигналы кода числа 7 в триггеры счетчика (сигналы кода 0111 на входах D8, D4, D2, Dl не показаны). Первые пять импульсов на входе С переводят его последовательно в состояния 8, 9, 0, 1, 2. На выходе 0/9 лог. 1 появляется при переходе счетчика в состояние 9. Импульс на его выходе Р формируется одновременно с третьим импульсом на входе С, по спаду которого счетчик переключается в состояние 0.

В момент окончания пятого импульса происходит смена направления счета изменением сигнала на входе D/U и следующие пять импульсов на входе С переводят счетчик последовательно в состояния 1, 0, 9, 8,7 и т. д. При переходе счетчика в состояние 0 на выходе 0/9 появляется лог. 1, а одновременно с восьмым импульсом на входе С, переключающим счетчик в состояние 9, на выходе Р формируется импульс отрицательной полярности.

Схема соединения микросхем КР1533ИЕ12 в многоразрядный счетчик показана на рис. 41 (а). Из-за последовательного переключения быстродействие такого счетчика в реверсивном режиме снижается относительно быстродействия одной микросхемы.

Если необходим реверсивный счетчик с максимально возможным быстродействием, его собирают по схеме рис. 41 (б). В этом счетчике все триггеры микросхем переключаются одновременно и его быстродействие не зависит от числа разрядов. Однако для каждого десятичного разряда, кроме первого, требуется элемент И-НЕ с числом входов, возрастающим по мере роста номера разряда.

В зависимости от необходимого быстродействия возможно построение различных вариантов последовательно-параллельного счетчика. Можно, например, не использовать выход 0/9 микросхемы DD4 (рис. 41, б), а ее выход Р соединить с входом тактовых импульсов второго такого счетчика.

Микросхема КР1533ИЕ13 (рис. 39) аналогична КР1533ИЕ12, но ее коэффициент пересчета равен 16. Все правила ее использования и схемы включения соответствуют микросхеме КР1533ИЕ12.

Микросхема ИЕ14 (рис. 42) во многом напоминает микросхему ИЕ2. Она также содержит счетный триггер с входом С2. При соединении выхода 1 счетного триггера (вывод 5) с входом С2 образуется двоично-десятичный счетчик, работающий в коде 1-2-4-8. Срабатывание триггера и делителя на 5 происходит по спадам импульсов положительной полярности. Различие с микросхемой ИЕ2 заключается в полярности импульсов сброса — триггеры микросхемы ИЕ14 устанавливаются в 0 при подаче на вход R лог. 0. Кроме того, в микросхеме ИЕ14 есть возможность предварительной установки триггеров счетчика. Для установки триггеров необходимый код следует подать на входы D1 — D8, а на вход L — импульс отрицательной полярности. При лог. 0 на входе L сигналы на выходах 1-8 повторяют сигналы на входах D1 — D8, при лог. 1 происходит запоминание и возможен счетный режим работы микросхемы.

Микросхему можно использовать в счетчиках с предварительной установкой, например, в цифровых шкалах радиоприемников и трансиверов с учетом промежуточной частоты.

Микросхема ИЕ15 (рис. 42) по своей структуре и функционированию аналогична микросхеме ИЕ14, но делитель с входом С2 делит частоту на 8,

Микросхемы КР531ИЕ16 и КР531ИЕ17 — реверсивные синхронные четырехразрядные счетчики — двоично-десятичный и двоичный соответственно. Разводка их выходов совпадает (рис. 43), более того, она совпадает с разводкой микросхем ИЕ9 и ИЕ10, за исключением вывода 1, для описываемых микросхем это вход изменения направления счета U/D, вход сброса отсутствует.

При лог. 1 на входе U/D счетчик считает вверх, при лог. 0 — вниз. Синхронная параллельная запись информации в микросхемы КР531ИЕ16 и КР531ИЕ17 происходит со входов D1 — D8 по спаду тактового импульса отрицательной полярности на входе С и подаче лог. 0 на вход разрешения загрузки EL. При счете на входе EL должна быть лог. 1.

Отличием описываемых микросхем от ИЕ9 и ИЕ10 является также полярность сигналов разрешения переноса ЕР и разрешения счета ЕС (для разрешения работы на эти входы необходимо подать лог. 1). Соответственно выходным разрешающим сигналом на выходе переноса Р является лог. 0, он появляется в случае, когда микросхема КР531ИЕ16 досчитала до состояния 9 (КР531ИЕ17 — до состояния 15) при прямом счете или до 0 при обратном, а на входе разрешения переноса ЕР — лог. 0.

Примеры соединения микросхем КР531ИЕ16 и КР531ИЕ17 в многоразрядный счетчик приведены на рис. 44 и 45. При соединении микросхем по схеме рис. 44 максимальная частота счета снижается по отношению к максимально возможной для одной микросхемы, при соединении по схеме рис. 45 — не снижается. Следует помнить, что переключение направления счета на входе U/D и смену информации на входах ЕР и ЕС следует производить в паузе между тактовыми импульсами, то есть при лог. 1 на входах С микросхем или в момент изменения сигнала на этих входах с лог. 0 на лог. 1. Входной ток микросхем по входу ЕР в состоянии лог. 0-4 мА. Микросхема ИЕ18 (рис. 46) аналогична по функционированию микросхеме ИЕ11, но ее коэффициент пересчета равен 16.

Рассмотренные выше микросхемы счетчиков серии КР531 имеют входные токи по управляющим входам, как правило, больше стандартных. При подаче на входы лог. 0 токи составляют для микросхем КР531ИЕ9 и КР531ИЕ10 по выводу 2 — 5 мА, выводу 10-3 мА, выводу 9-4 мА. Для микросхем КР531ИЕ11 и КР531ИЕ18 ток по выводу 10 составляет 4 мА, а для КР531ИЕ14 и КР531ИЕ15 ток по выводу 8-8 мА, по выводу 6-10 мА, по выводам 1, 3, 4, 10, 11, 13 — 0,75 мА.

Микросхема К555ИЕ19 — два четырехразрядных двоичных счетчика (рис. 47), каждый из которых имеет два входа: R — для установки триггеров счетчика в 0 при подаче на вход R лог. 1 и С — для подачи счетных импульсов. Срабатывание триггеров счетчика происходит по спадам импульсов положительной полярности, подаваемых на вход С, выходной код счетчиков — стандартный, 1-2-4-8. Для соединения счетчиков в многоразрядный выходы 8 предыдущих разрядов необходимо соединить со входами С последующих.

Микросхема К555ИЕ20 (рис. 47) -два четырехразрядных двоично-десятичных счетчика, каждый из которых аналогичен счетчику микросхем ИЕ2, за исключением входов установки в 0 R.

Каждый счетчик имеет триггер со входом С1, выходом 1 и делитель частоты на 5 со входом С2 и выходами 2,4,8. Триггер и счетчик срабатывают по спадам положительных импульсов, подаваемых на входы С1 и С2, на входе R при счете должен быть лог. 0. Для получения десятичного счетчика выход 1 надо соединить со входом С2, при этом код счетчика будет 1-2-4-8. Если же выход 8 соединить со входом С1, входные импульсы подать на вход С2, выходной код будет 1-2-4-5, а на выходе 1 сигнал будет иметь форму меандра с частотой, в 10 раз меньше входной. Впрочем, так же можно соединять счетчики микросхем ИЕ2 и ИЕ14. Предельная частота работы триггера — 25 МГц, делителя на 5 — 20 МГц.

picDIV — Одночиповый делитель частоты

picDIV — Одночиповый делитель частоты LeapSecond.compicDIV — Одночиповый делитель частоты

20 октября 2011 г.

Есть много способов разделить частоту. Если частота равна 10 МГц, а желаемая частота — 1 Гц, нужно разделить на 10 миллионов. Это легко сделать с помощью серии дискретных декадных счетчиков.Но крошечный микроконтроллер может выполнять ту же функцию.picDIV ™ — цифровой делитель частоты на основе PIC. который функционирует как серия из синхронных счетчиков декад. Как видно здесь, «PIC» — это широко распространенный крошечный недорогой 8-битный микроконтроллер. Простая программа «раскручивает» и каждые 5 миллионов тактовые циклы ЦП переключает выходной контакт. Таким образом, входной тактовый сигнал 10 МГц становится выходным прямоугольным сигналом с частотой 1 Гц.

Точность вывода равна точности ввода.

Джиттер чрезвычайно низок, поскольку PIC является синхронным устройством.

Недавние измерения показывают, что оно меньше 2 пс.

Чип picDIV не может быть проще в использовании. Кроме питания +5 В постоянного тока ( контакт 1 ) и земли ( контакт 8 ) всего два контакта!

контакт 2 — Тактовая частота 10 МГц управляет PIC (он выполняет изохронный код).КМОП-совместимая прямоугольная волна идеальна но вход PIC clock довольно щадящий. Например, если уровень и амплитуда подходящие, подойдет даже синусоида 10 МГц.

контакт 7 — Выходной прямоугольный сигнал частотой 1 Гц.

Степени десяти делителей

- PD3 делится на тысячу (10 3 ), например, 10 МГц → 10 кГц

- PD4 делится на десять тысяч (10 4 ), например, 10 МГц → 1 кГц

- PD5 делится на сто тысяч (10 5 ), например, 10 МГц → 100 Гц

- PD6 делится на один миллион (10 6 ), например, 10 МГц → 10 Гц или 1 МГц → 1 Гц

- PD7 делится на десять миллионов (10 7 ), е.г., 10 МГц → 1 Гц

- PD8 делится на пять миллионов, например, 5 МГц → 1 Гц

Примечание: нет необходимости всегда управлять этими делителями с частотой 10 МГц. PD3 будет делиться на 1000 независимо от входной частоты; выходная частота всегда в 1000 раз меньше входной. Часы PIC работают от постоянного тока до 20 МГц.

Узкие импульсные выходы

Следующие ниже делители picDIV выводят узкие импульсы вместо прямоугольной волны 50%.- PD9 генерирует 1PPS от 10 МГц. На выходе получается очень узкий импульс 20 мкс, чего более чем достаточно для запуска счетчиков и достаточно мал, чтобы иметь близкую к нулю среднюю мощность.

- PD10 генерирует 1PPS от 10 МГц. Выходной сигнал — импульс длительностью 10 мс, которого достаточно для того, чтобы светодиоды сердцебиения были видны.

Схема подключения для PD7 (и PD3, PD4, PD5, PD6, PD8, PD9, PD10)

---__---

5V (Vdd) +++++ | 1 8 | ===== Земля (Vss)

входные часы ----> | 2 pD 7 | ----> выходные часы

* | 3 07 6 | *

о | 4 5 | о

--------

Примечание. Для PD3 — PD10 контакты 3 и 6 являются выходами вместе с контактом 7.Это может быть полезно, если требуется несколько выходов или более высокий ток (параллельный привод). На этих микросхемах контакты 4 и 5 не используются и могут быть оставлены открытыми или связаны с Vdd или Vss.

Делители синхронизированные

Следующие делители 1PPS имеют разную ширину вывода и возможность синхронизации 1PPS.- PD11 принимает тактовую частоту 10 МГц и генерирует три разных выхода 1 Гц: узкий импульс 100 мкс выводится с вывода 7, импульс длительностью 10 мс выводится с контакта 3, и прямоугольный сигнал частотой 1 Гц выводится с контакта 6.

- PD12 принимает тактовую частоту 5 МГц и генерирует три разных выхода 1 Гц: узкий импульс 100 мкс выводится с вывода 7, импульс длительностью 10 мс выводится с контакта 3, и прямоугольный сигнал частотой 1 Гц выводится с контакта 6.

Узкий импульс хорош для запуска счетчиков временного интервала или частотомера, и достаточно долго для использования с последовательными портами ПК. Импульс 10 мс удобен для мигания светодиода.

Эти делители также обеспечивают синхронизацию 1PPS.Если на выводе 4 (Arm) в течение секунды удерживается низкий уровень, делитель останавливается и ждет. Делитель синхронизируется с нарастающим фронтом вывода 5 (Sync). Слабое подтягивание на штифте синхронизации. Если вы никогда не планируете останавливать или синхронизировать делитель, подключите контакт Arm к Vdd, или просто подключите контакт Arm к контакту Sync.

Схема подключения PD11:

---__---

5V (Vdd) +++++ | 1 8 | ===== Земля (Vss)

Тактовая частота 10 МГц на входе ----> | 2 pD 7 | ----> 1 PPS на выходе (100 мкс)

1PPS (10 мс) на выходе 1 Гц на выходе (50%)

Arm o ---> | 4 5 |

Схема подключения PD12:

---__---

5V (Vdd) +++++ | 1 8 | ===== Земля (Vss)

Тактовая частота 5 МГц на входе ----> | 2 pD 7 | ----> 1 PPS на выходе (100 мкс)

1PPS (10 мс) выход 1 Гц (50%)

Arm o ---> | 4 5 |

Обратите внимание: если все, что вам нужно, это выход 100 мкс, это 4-контактная ИС.Если вам нужны все три выхода, это «6-контактная ИС».

Если вам нужна синхронизация, то это полноценная «8-контактная» ИС.

Несколько выходных частот

Несколько делителей были разработаны с несколькими выходами прямоугольной частоты, от 1 Гц до 10 кГц.- PD13 (входная частота 10 МГц) генерирует три выхода: 1 Гц, 10 Гц, 100 Гц, с дополнительной функцией Arm / Sync.

- PD14 (входная частота 5 МГц) генерирует три выхода: 1 Гц, 10 Гц, 100 Гц, с дополнительной функцией Arm / Sync.

- PD15 (входная частота 10 МГц) генерирует три выхода: 1 Гц, 1000 Гц, 10000 Гц, с дополнительной функцией Arm / Sync.

Схема подключения PD13:

---__---

5V (Vdd) +++++ | 1 8 | ===== Земля (Vss)

Тактовая частота 10 МГц на входе ----> | 2 пД 7 | ----> 100 Гц на выходе

1 Гц на выходе 10 Гц на выходе

Arm o ---> | 4 5 |

Схема подключения PD14:

---__---

5V (Vdd) +++++ | 1 8 | ===== Земля (Vss)

Тактовая частота 5 МГц на входе ----> | 2 пД 7 | ----> 100 Гц на выходе

1 Гц на выходе 10 Гц на выходе

Arm o ---> | 4 5 |

Схема подключения PD15:

---__---

5V (Vdd) +++++ | 1 8 | ===== Земля (Vss)

Тактовая частота 10 МГц на входе ----> | 2 пД 7 | ----> 10 кГц на выходе

1 Гц на выходе 1 кГц на выходе

Arm o ---> | 4 5 |

Несколько входных частот

Большинство эталонных частот сегодня составляют 10 МГц, но не редко можно найти 1.0 МГц, 2,5 МГц или 5,0 МГц. Для этого набора частот было разработано несколько микросхем делителя.- PD16 (входная частота 5 или 10 МГц) генерирует четыре выхода: 1 Гц, 10 Гц, 100 Гц, 1000 Гц.

- PD17 (1, 2,5, 5 или 10 МГц) тактовая частота на входе генерирует один выходной сигнал 1PPS (Рабочий цикл 10%), с дополнительной функцией Arm / Sync.

- PD18 (1, 2,5, 5 или 10 МГц) тактовая частота на входе генерирует один выходной сигнал 1PPS (Рабочий цикл 1%), с дополнительной функцией Arm / Sync.

Схема подключения PD16:

---__---

5V (Vdd) +++++ | 1 8 | ===== Земля (Vss)

Тактовая частота 5/10 МГц на входе ----> | 2 пД 7 | ----> 1000 Гц на выходе

1 Гц на выходе 100 Гц на выходе

Выберите o ---> | 4 5 | ----> 10 Гц

--------

Схема подключения PD17:

---__---

5V (Vdd) +++++ | 1 8 | ===== Земля (Vss)

Частота N МГц в ----> | 2 пД 7 || 4 5 |

Схема подключения PD18:

---__---

5V (Vdd) +++++ | 1 8 | ===== Земля (Vss)

Частота N МГц в ----> | 2 пД 7 || 4 5 |

Примечания к интерфейсу

- байпасный конденсатор (например,g., 0,1 мкФ) рекомендуется между контактами 1 и 8.

- Выходной вывод PIC будет управлять током 20 мА.

- Входы обычно имеют уровни сигнала, совместимые с CMOS / TTL.

- Для некоторых приложений может потребоваться настроить входной сигнал. или буферизировать выходной сигнал. Очевидно, это добавляет к решению дополнительные активные и пассивные компоненты. С другой стороны, для многих приложений не требуются дополнительные детали. и микросхема picDIV действительно представляет собой однокомпонентное решение.

- Выходной джиттер менее 2 пс.

- Эти PIC будут работать от 2,0 до 5,5 В.

Дети относительности немного подросли с тех пор, как вы в последний раз видели их в 2005 году. Пора им узнать, что такое работа. Я поручил им прием заказов, запись прошивки, изготовление этикеток, тестирование, упаковка и отгрузка. Стоимость минимальная:

- один picDIV стоит 3 доллара (десять за 25 долларов, любая комбинация)

- один picPET стоит 5 долларов (десять за 40 долларов)

- Первоклассные почтовые расходы и обработка — 4 доллара (США) или 8 долларов (международный)

- свяжитесь со мной (tvb @ LeapSecond.6 делителей частоты (от 5 МГц до 1 Гц)

- pd09.asm / pd09.hex / PD09 — «4-контактный» делитель частоты от 10 МГц до 1PPS (импульс 20 мкс)

- pd10.asm / pd10.hex / PD10 — «4-контактный» делитель частоты от 10 МГц до 1PPS (импульс 10 мс)

- pd11.asm / pd11.hex / PD11 — делитель частоты от 10 МГц до 1PPS (3 ширины импульса), с синхронизацией

- pd12.asm / pd12.hex / PD12 — делитель частоты от 5 МГц до 1PPS (3 ширины импульса), с синхронизацией

- pd13.asm / pd13.hex / PD13 — делитель от 10 МГц на три частоты (1-10-100 Гц), с синхронизацией

- pd14.asm / pd14.hex / PD14 — делитель 5 МГц на три частоты (1-10-100 Гц), с синхронизацией

- pd15.asm / pd15.hex / PD15 — делитель от 10 МГц на три частоты (1-1000-10000 Гц), с синхронизацией

- pd16.asm / pd16.hex / PD16 — от 5/10 МГц до четырехчастотного делителя (1-10-100-1000 Гц)

- pd17.asm / pd17.hex / ПД17 — 1/2.Делитель частоты от 5/5/10 МГц до 1PPS (100 мс), с синхронизацией

- pd18.asm / pd18.hex / PD18 — делитель частоты от 1 / 2,5 / 5/10 МГц до 1PPS (10 мс), с синхронизацией

- pd26.asm / pd26.hex / PD26 — делитель от 10 МГц до 1PPS, с синхронизацией и микрошагом

- pd27.asm / pd27.hex / PD27 — делитель от 10 МГц до 1PPS, с синхронизацией и миллишагом

- pd28.asm / pd28.hex / PD28 — от 10 МГц до звездного делителя 1PPS, с синхронизацией и миллишагом

Если у вас есть запросы на специальные функции, дайте мне знать.

См. Страницу проекта PIC LeapSecond.com.

Вернитесь на домашнюю страницу LeapSecond.com.

Комментарии / вопросы к tvb.

Деление частоты с использованием триггеров деления на 2

В обучающих материалах по последовательной логике мы увидели, как работают триггеры D-типа и как их можно соединить вместе, чтобы сформировать защелку данных.

Еще одна полезная функция триггера D-типа — это двоичный делитель для частотного делителя или счетчик «деления на 2».Здесь перевернутая выходная клемма Q (НЕ-Q) подключена напрямую к клемме ввода данных D, обеспечивая устройству «обратную связь», как показано ниже.

Счетчик деления на 2

Из представленных выше частотных сигналов можно увидеть, что, «возвращая» выходной сигнал Q на вход D, выходные импульсы на Q имеют частоту, которая ровно половину (÷ 2) частоты входных синхроимпульсов. частота. Другими словами, схема выдает с частотным разделением , поскольку теперь она делит входную частоту на коэффициент два (октаву).

Это затем создает тип счетчика, называемый «счетчиком пульсаций», а в счетчиках пульсаций тактовый импульс запускает первый триггер, выход которого запускает второй триггер, который, в свою очередь, запускает третий триггер и т. Д. цепь, создающая эффект пульсации (отсюда и их название) синхронизирующего сигнала, когда он проходит через цепь.

Переключатель Flip-Flop

Другой тип цифровых устройств, которые можно использовать для деления частоты, — это триггеры T-типа или Toggle.С небольшой модификацией стандартного триггера JK мы можем построить новый тип триггера, который называется Toggle flip-flop .

Перекидные триггеры могут быть изготовлены из триггеров D-типа, как показано выше, или из стандартных триггеров JK, таких как 74LS73. В результате получается устройство только с двумя входами, входом «Toggle» и отрицательным управляющим входом «Clock», как показано.

74LS73 Тумблер

«Переключатель триггера» получил свое название от того факта, что триггер имеет возможность переключаться или переключаться между двумя разными состояниями, «состоянием переключения» и «состоянием памяти».Поскольку имеется только два состояния, триггер T-типа идеально подходит для использования в схемах с частотным разделением и двоичных счетчиков.

Двоичные счетчики пульсаций могут быть построены с использованием «тумблеров» или «триггеров T-типа», подключив выход одного к тактовому входу следующего. Перекидные триггеры идеально подходят для создания счетчиков пульсаций, поскольку они переключаются из одного состояния в другое (от высокого до низкого или от низкого до высокого) в каждом тактовом цикле, поэтому простые схемы делителя частоты и счетчика пульсаций могут быть легко построены с использованием стандартного Т-типа. триггерные схемы.

Если мы соединим последовательно два Т-образных триггера, начальная входная частота будет «делиться на два» первым триггером (÷ 2), а затем снова «делиться на два» на второй триггер (÷ 2) ÷ 2, дает выходную частоту, которая эффективно делится четыре раза, тогда его выходная частота становится одной четвертой (25%) первоначальной тактовой частоты (÷ 4).

Каждый раз, когда мы добавляем еще один переключатель или триггер «T-типа» в цепочку, выходная тактовая частота уменьшается вдвое или снова делится на 2 и так далее, давая выходную частоту 2 n , где «n» — количество триггеров, используемых в последовательности.

Тогда тумблер или триггер T-типа представляет собой устройство деления на 2, запускаемое по фронту, основанное на стандартном триггере JK-типа и которое запускается по нарастающему фронту тактового сигнала. В результате каждый бит перемещается вправо на один триггер. Все триггеры могут быть сброшены асинхронно и могут быть запущены для включения либо переднего, либо заднего фронта входного тактового сигнала, что делает его идеальным для частотного деления .

Этот тип схемы счетчика, используемый для частотного деления, обычно известен как Асинхронный 3-битный двоичный счетчик , поскольку выход на QA-QC шириной 3 бита представляет собой двоичный счет от 0 до 7 для каждого тактового импульса.

В асинхронном счетчике тактовые импульсы применяются только к первому каскаду, при этом выход одного каскада триггера обеспечивает синхронизирующий сигнал для следующего каскада триггера, а последующие каскады получают тактовый сигнал из предыдущего каскада с тактовым импульсом. уменьшается вдвое на каждом этапе.

Эта схема обычно известна как Асинхронный , поскольку каждое событие синхронизации происходит независимо, поскольку не все биты в счетчике изменяются одновременно. Поскольку счетчик ведет счет последовательно в направлении вверх от 0 до 7.Этот тип счетчика также известен как «прямой» или «прямой» счетчик ( CTU ) или «3-битный асинхронный повышающий счетчик» . Показанный трехразрядный асинхронный счетчик является типичным и использует триггеры в режиме переключения. Также доступны асинхронные счетчики «вниз» ( CTD ).

Таблица истинности для 3-битного асинхронного повышающего счетчика

| Цикл часов | Выходной битовый шаблон | ||

| КК | QB | QA | |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 2 | 0 | 1 | 0 |

| 3 | 0 | 1 | 1 |

| 4 | 1 | 0 | 0 |

| 5 | 1 | 0 | 1 |

| 6 | 1 | 1 | 0 |

| 7 | 1 | 1 | 1 |

Таким образом, мы можем видеть, что выходной сигнал триггера D-типа составляет половину частоты входного сигнала, другими словами, он считается двойным.Посредством каскадного соединения большего количества триггеров D-типа или тумблеров мы можем создать схему деления на 2, деления на 4, деления на 8 и т. Д., Которая будет делить входную тактовую частоту на 2, 4 или 8 раз, фактически любое значение до степени двойки, мы хотим сделать схему двоичного счетчика.

Двоичные счетчики

Таким образом, мы можем видеть, что счетчик — это не что иное, как специализированный регистр или генератор шаблонов, который производит заданный выходной шаблон или последовательность двоичных значений (или состояний) после подачи входного импульсного сигнала, называемого «Clock».

Часы фактически используются для передачи данных в этих приложениях. Обычно счетчики представляют собой логические схемы, которые могут увеличивать или уменьшать счетчик на единицу, но при использовании в качестве асинхронных счетчиков деления на n они могут делить эти входные импульсы, создавая сигнал деления тактовой частоты.

Счетчикиформируются путем соединения триггеров вместе, и любое количество триггеров может быть соединено или «каскадно» вместе, чтобы сформировать двоичный счетчик «деление на n», где «n» — это количество используемых каскадов счетчика, которые называется модулем Modulus .Модуль или просто «MOD» счетчика — это количество выходных состояний, которые счетчик проходит, прежде чем вернуться к нулю, то есть за один полный цикл.

Тогда счетчик с тремя триггерами, как в схеме выше, будет считать от 0 до 7, то есть 2 n -1. Он имеет восемь различных состояний выхода, представляющих десятичные числа от 0 до 7, и называется счетчиком Modulo-8 или MOD-8 . Счетчик с четырьмя триггерами будет считать от 0 до 15 и поэтому называется счетчиком Modulo-16 и так далее.

Пример этого дан как.

- 3-битный двоичный счетчик = 2 3 = 8 (по модулю 8 или MOD-8)

- 4-битный двоичный счетчик = 2 4 = 16 (по модулю 16 или MOD-16)

- 8-битный двоичный счетчик = 2 8 = 256 (по модулю 256 или MOD-256)

- и т. Д.

Число по модулю можно увеличить, добавив больше триггеров к счетчику, а каскадирование — это метод достижения счетчиков с более высоким модулем. Тогда номер по модулю или MOD может быть просто записан как: Номер MOD = 2 n

4-битный счетчик по модулю 16

Многобитовые асинхронные счетчики, подключенные таким образом, также называются «счетчиками пульсаций» или делителями пульсаций, потому что изменение состояния на каждом этапе, по-видимому, «пульсирует» через счетчик от выхода LSB к его выходному соединению MSB.Счетчики пульсаций доступны в стандартной форме ИС, от двойного 4-разрядного счетчика 74LS393 до 74HC4060, который представляет собой 14-разрядный счетчик пульсаций с собственным встроенным тактовым генератором и обеспечивает отличное частотное деление основной частоты.

Сводка по частотному разделению