Что представляют собой ПЛИС Altera. Какие семейства ПЛИС выпускает компания. Чем ПЛИС Altera отличаются от конкурентов. Каковы преимущества использования ПЛИС Altera в разработке электронных устройств.

Обзор компании Altera и ее продукции

Компания Altera является одним из ведущих мировых производителей программируемой логики. Основанная в 1983 году, Altera специализируется на разработке и производстве программируемых логических интегральных схем (ПЛИС), также известных как FPGA (Field-Programmable Gate Array).

Основные семейства ПЛИС, выпускаемые компанией Altera:

- Stratix — высокопроизводительные ПЛИС для самых требовательных применений

- Arria — ПЛИС среднего уровня с оптимальным соотношением цена/производительность

- Cyclone — недорогие ПЛИС для массовых приложений

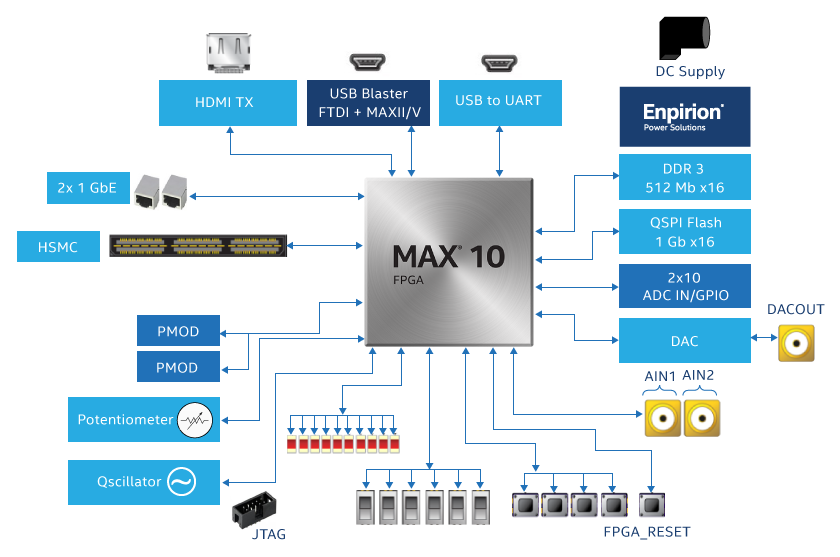

- MAX — CPLD (Complex Programmable Logic Device) для простых схем

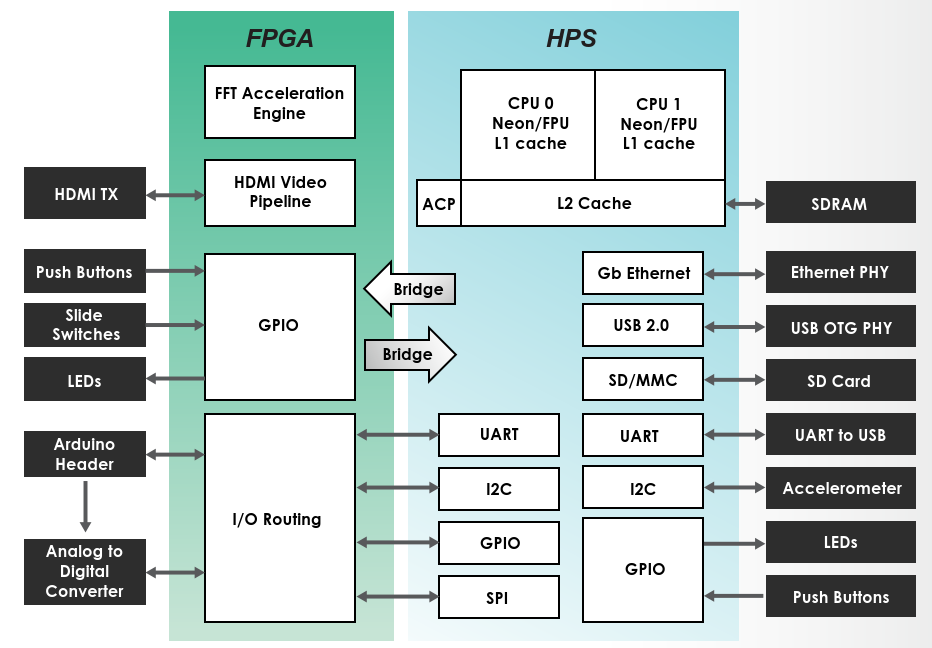

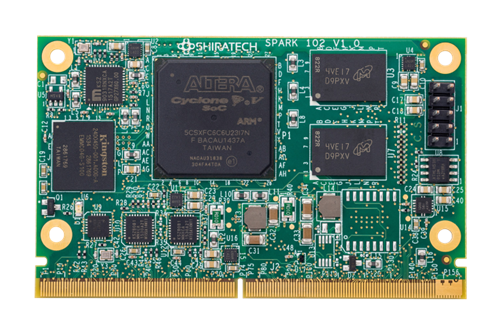

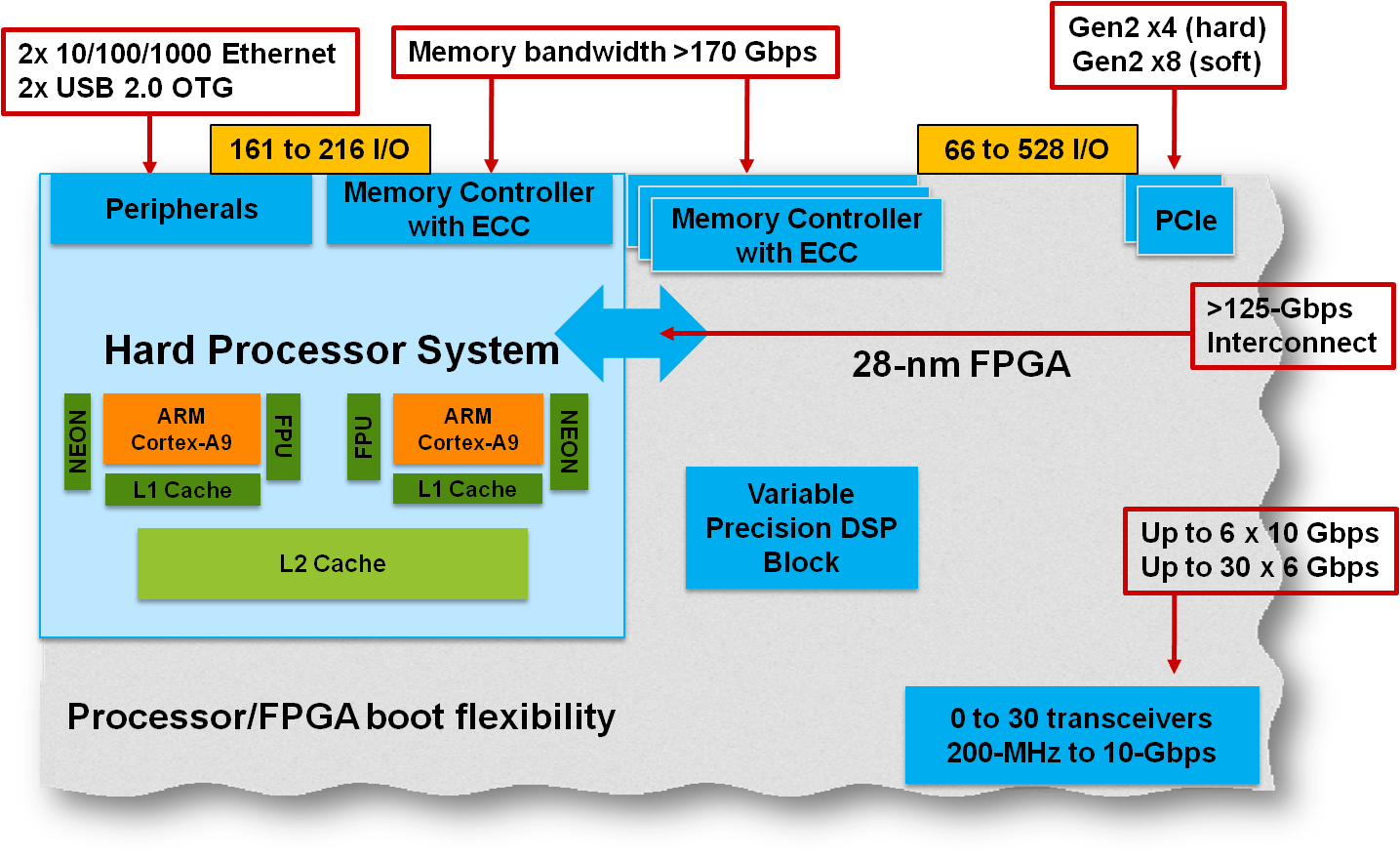

Кроме того, Altera предлагает системы на кристалле (SoC FPGA), сочетающие ПЛИС и процессорные ядра ARM на одном чипе.

Преимущества ПЛИС Altera

Чем же ПЛИС производства Altera выделяются на фоне конкурентов? Рассмотрим основные преимущества использования микросхем Altera:

- Передовые технологические процессы — Altera одной из первых осваивает новые техпроцессы, что позволяет создавать более быстрые и экономичные ПЛИС

- Высокая производительность — ПЛИС Altera демонстрируют лидирующие показатели быстродействия в своих классах

- Низкое энергопотребление — применение современных технологий позволяет снизить потребляемую мощность

- Широкий выбор IP-ядер — Altera предлагает обширную библиотеку готовых функциональных блоков

- Развитые средства проектирования — САПР Quartus Prime обеспечивает удобную разработку проектов на ПЛИС

Применение ПЛИС Altera

ПЛИС Altera находят применение в самых разных областях электроники и вычислительной техники. Основные сферы использования:

- Телекоммуникационное оборудование

- Системы обработки видео и изображений

- Высокопроизводительные вычислительные системы

- Промышленная автоматика

- Автомобильная электроника

- Бытовая техника

- Аэрокосмические и военные системы

Благодаря гибкости и универсальности ПЛИС, разработчики могут создавать специализированные высокопроизводительные устройства, оптимизированные под конкретные задачи.

Сравнение ПЛИС Altera с конкурентами

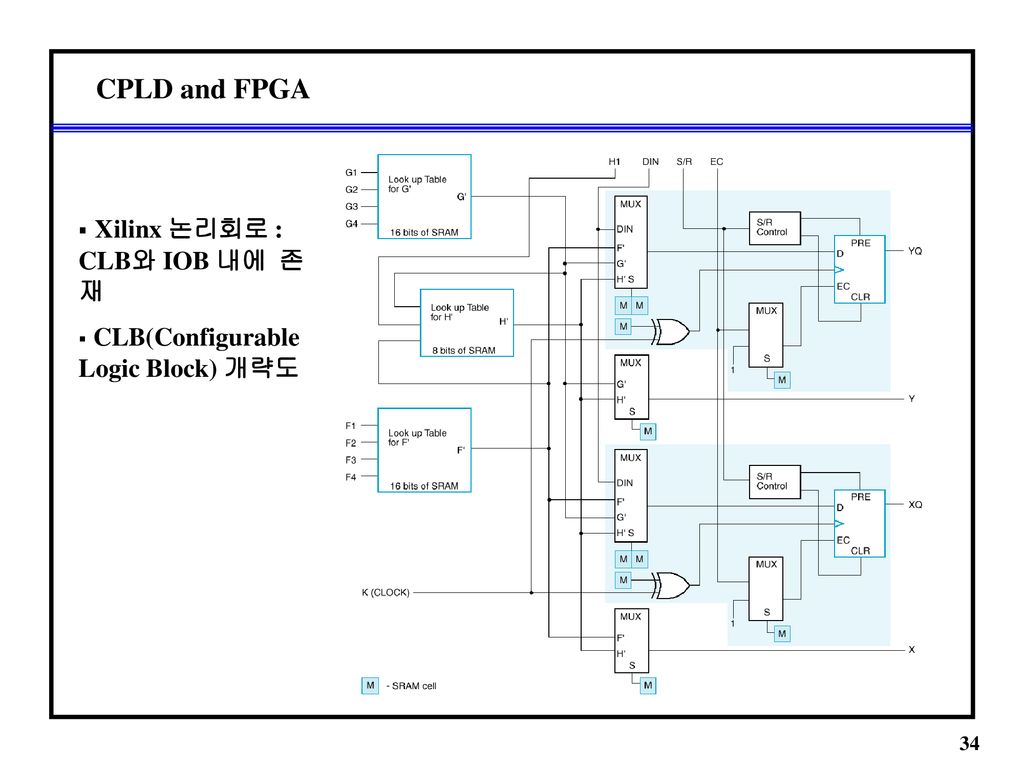

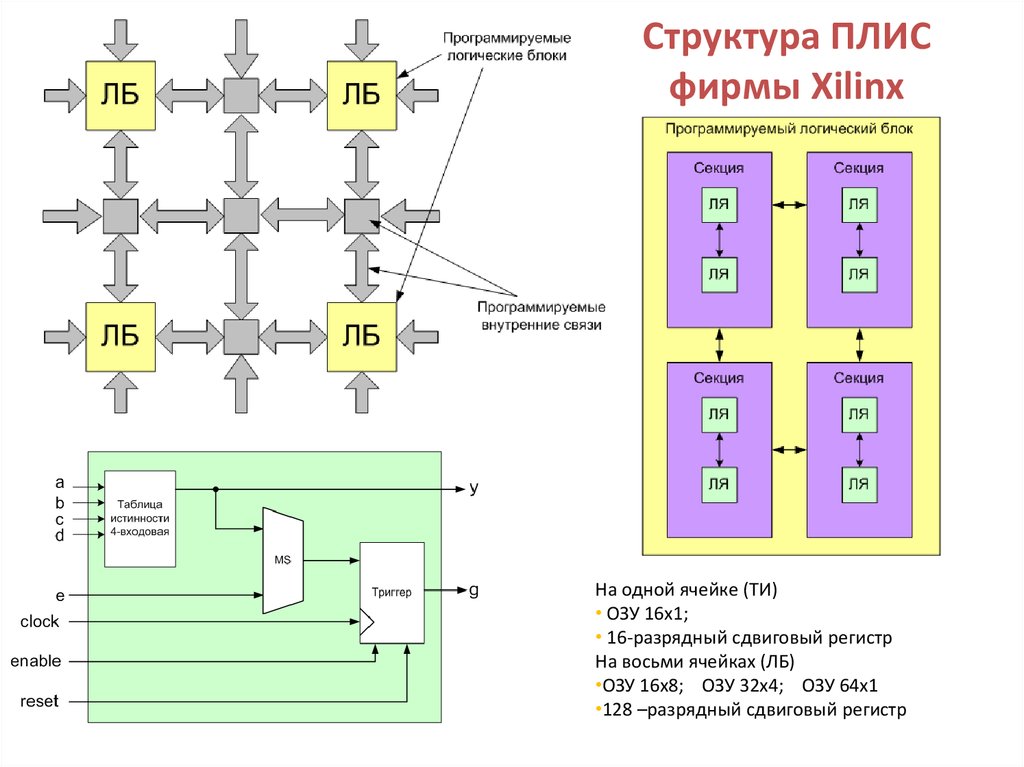

Основным конкурентом Altera на рынке ПЛИС является компания Xilinx. Как же соотносятся ПЛИС этих производителей?

- По технологическому уровню Altera и Xilinx идут примерно вровень, попеременно лидируя в освоении новых техпроцессов

- По производительности ПЛИС обеих компаний сопоставимы в своих классах

- Altera традиционно лидирует по энергоэффективности ПЛИС

- Xilinx имеет несколько большую долю рынка ПЛИС

- Средства разработки Altera считаются более удобными и интуитивно понятными

В целом, обе компании предлагают высококачественные решения, выбор между которыми часто определяется предпочтениями конкретных разработчиков.

Особенности архитектуры ПЛИС Altera

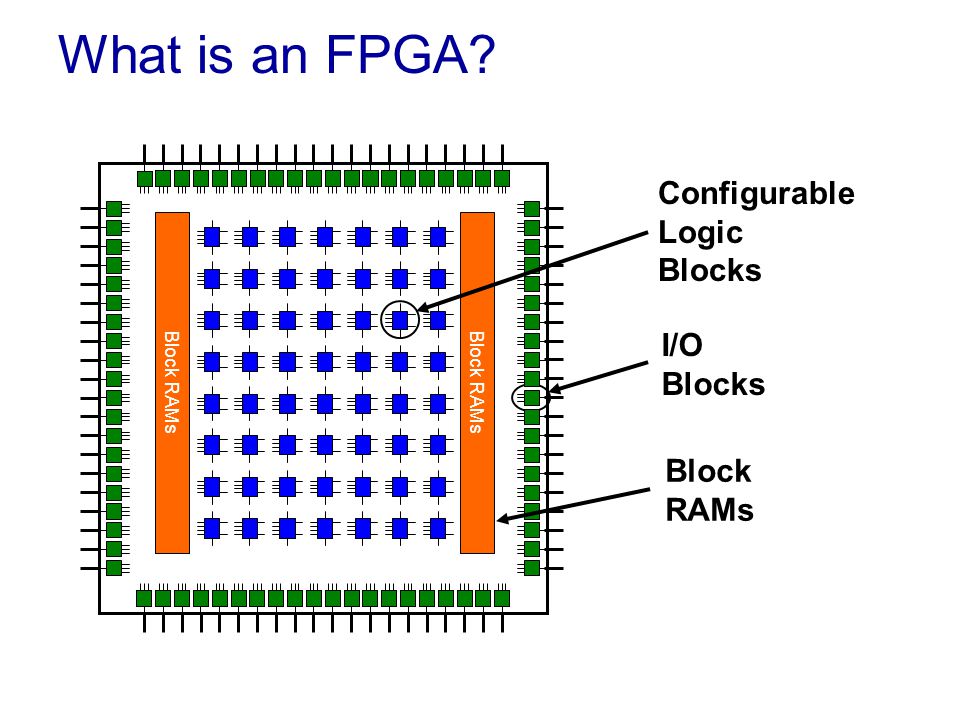

Рассмотрим ключевые архитектурные особенности, характерные для ПЛИС Altera:

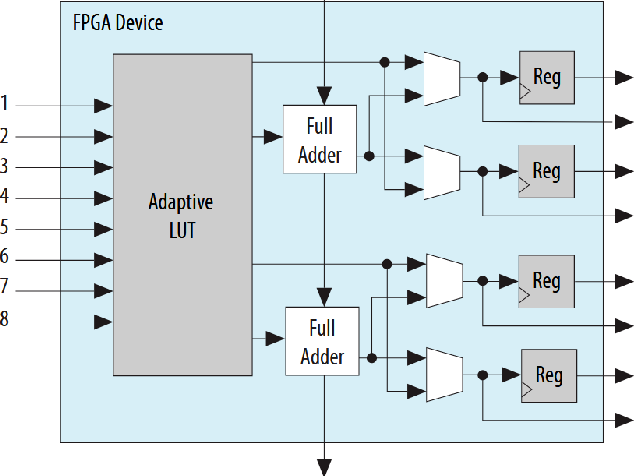

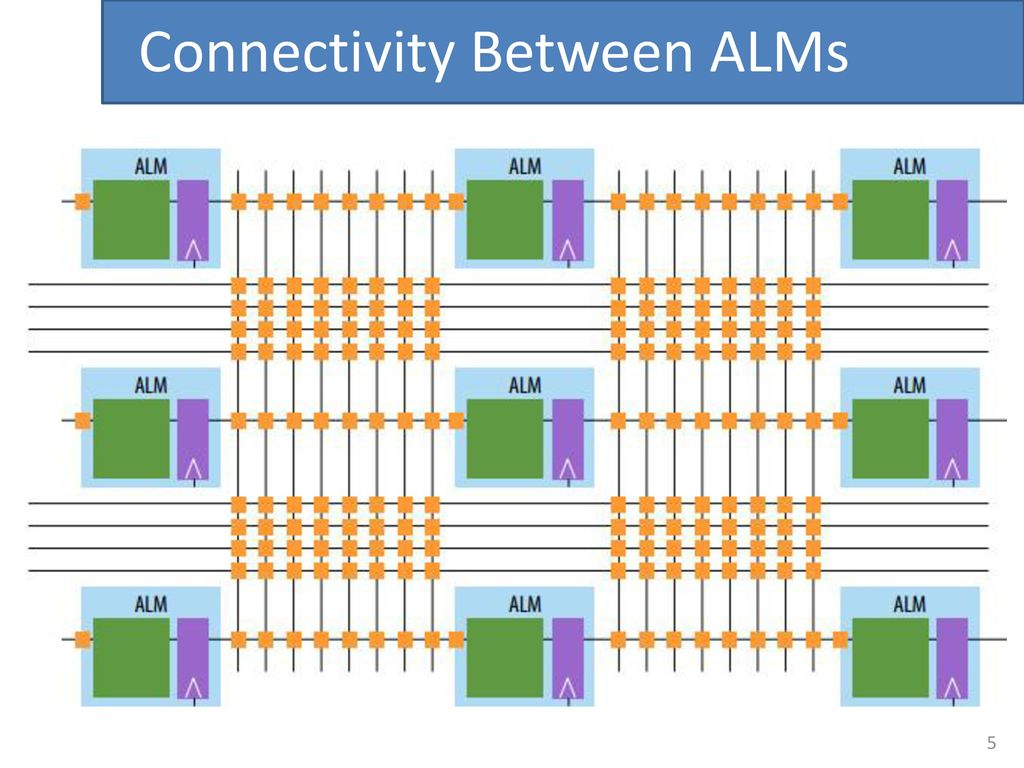

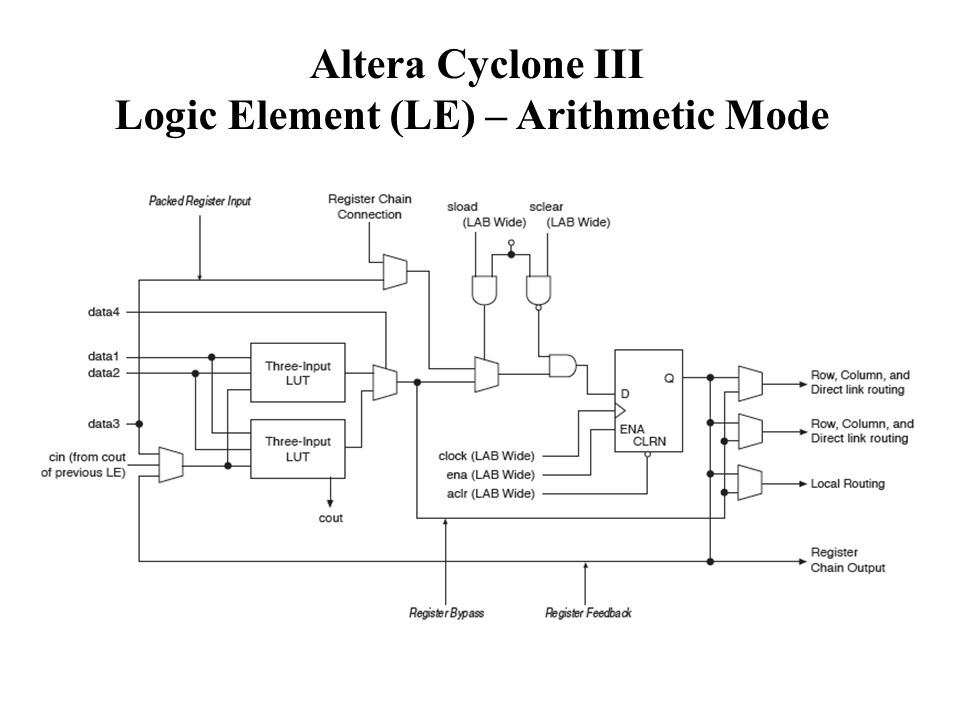

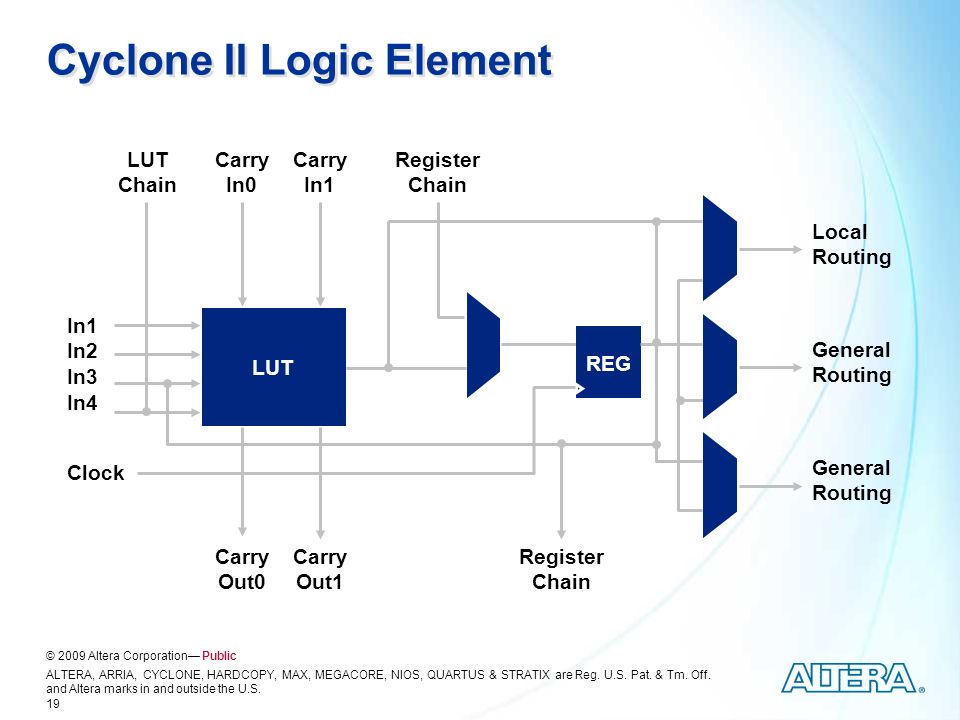

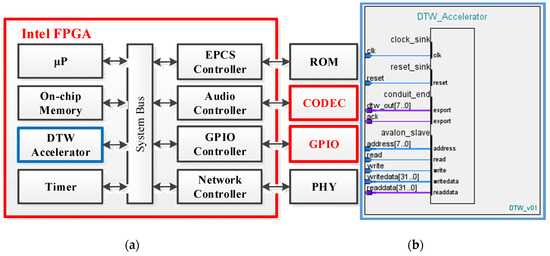

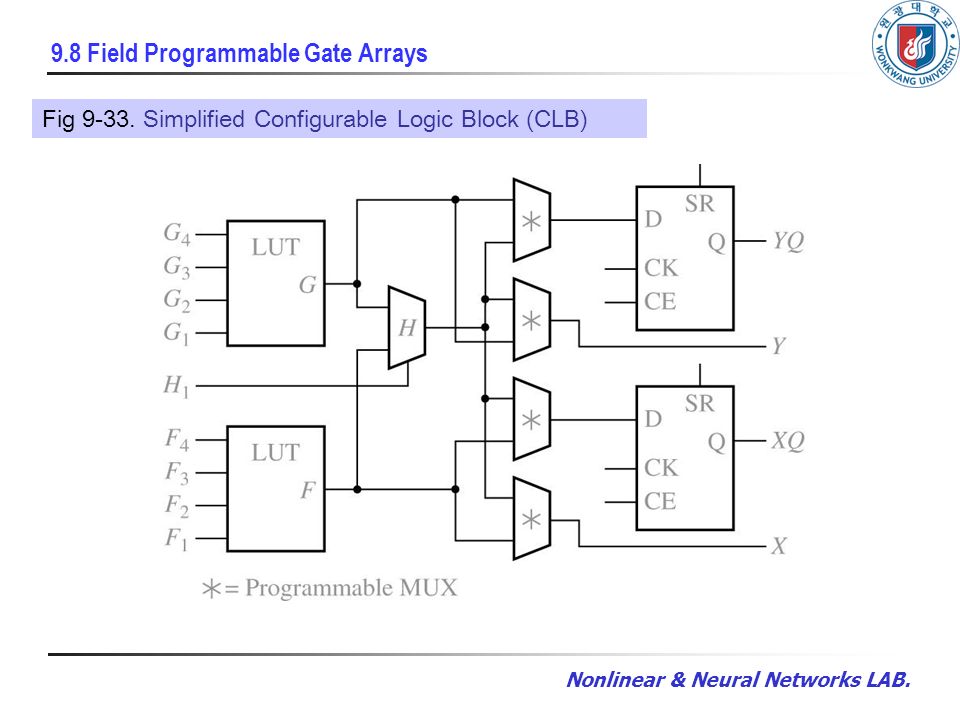

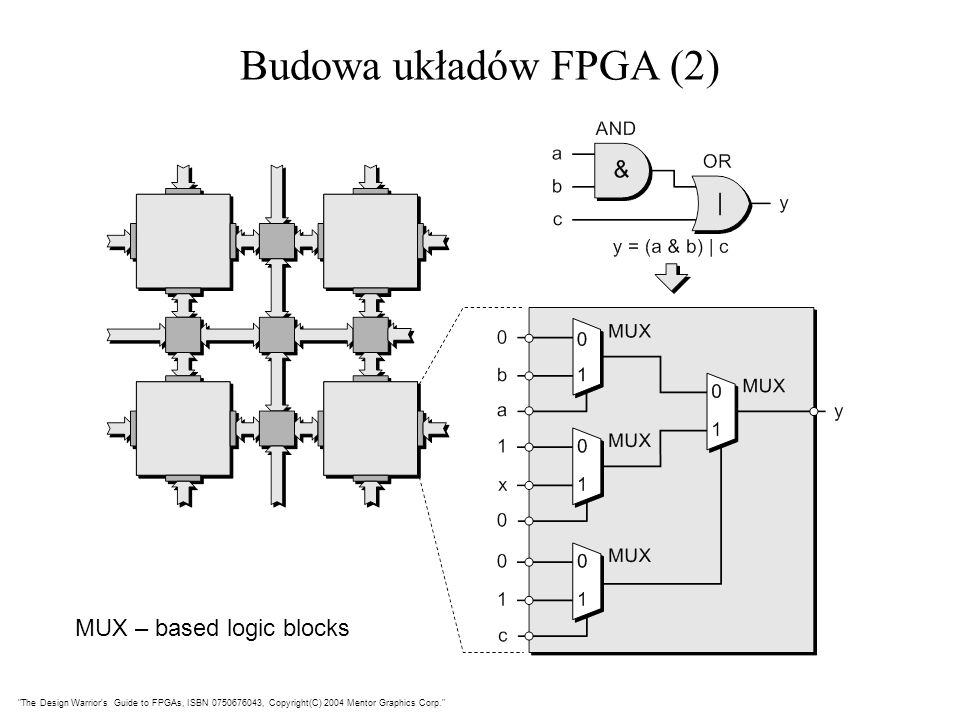

- Адаптивные логические модули (ALM) — базовые блоки, сочетающие LUT и триггеры

- Встроенные блоки памяти различного объема

- DSP-блоки для быстрых вычислений

- Высокоскоростные приемопередатчики

- Конфигурируемые блоки ввода-вывода

- Программируемые линии межсоединений

Такая архитектура обеспечивает высокую гибкость и эффективность реализации различных цифровых схем на ПЛИС Altera.

Средства разработки для ПЛИС Altera

Для проектирования устройств на базе ПЛИС Altera предлагает комплексный набор программных инструментов:

- Quartus Prime — основная САПР для разработки проектов

- ModelSim-Altera — средство моделирования цифровых схем

- DSP Builder — инструмент для разработки систем цифровой обработки сигналов

- Nios II EDS — среда разработки для встраиваемых процессоров Nios II

- SoC EDS — инструменты для разработки систем на кристалле

Данные средства позволяют эффективно создавать, отлаживать и оптимизировать проекты на ПЛИС Altera.

Перспективы развития ПЛИС Altera

Каковы основные тенденции в развитии ПЛИС Altera на ближайшие годы? Можно выделить следующие направления:

- Освоение все более тонких технологических норм (7 нм, 5 нм и далее)

- Увеличение степени интеграции и логической емкости ПЛИС

- Снижение энергопотребления

- Развитие гетерогенных систем на кристалле

- Повышение производительности специализированных блоков (DSP, память и т.д.)

- Совершенствование средств проектирования

Это позволит ПЛИС Altera оставаться конкурентоспособным решением для создания высокопроизводительных специализированных вычислительных систем.

Altera ПЛИС, Intel программируемая логика,FPGA, CPLD SPLD, системы на кристале

- Главная

- Производители

- Intel PSG (бывш. Altera)

www.intel.com

После слияния корпораций Intel и Altera, в рамках Intel было сформировано подразделение Intel PSG, в котором сконцентрировались все компетенции Altera.

На сегодняшний день Intel PSG (бывш. Altera) является одним из мировых лидеров на рынке микросхем программируемой логики, средств разработки для них и готовых решений, позволяющих значительно сократить время разработки цифрового оборудования.Intel PSG (бывш. Altera) предлагает разработчикам широкий спектр микросхем программируемой логики — от самых малых (логической емкостью 40 логических элементов) до самых больших (логической емкостью более 5,5 млн. эквивалентных логических элементов). Требованиям современных комплексных систем удовлетворяют микросхемы новых семейств Intel PSG (бывш. Altera):

эквивалентных логических элементов). Требованиям современных комплексных систем удовлетворяют микросхемы новых семейств Intel PSG (бывш. Altera):

- микросхемы с высокой логической емкостью серии Stratix;

- микросхемы среднего диапазона серии Arria;

- недорогие микросхемы серии Cyclone и MAX.

В состав семейств Arria 10, Arria V и Cyclone V входят устройства класса система-на-кристалле со встроенными аппаратными процессорными ядрами ARM Cortex A9.

В состав семейства Stratix 10 входят устройства класса система-на-кристалле со встроенными аппаратными процессорными 64-разрядными ядрами ARM Cortex A53.

Самое широкое признание в радиоэлектронной промышленности получили ПЛИС Intel PSG (бывш. Altera) со встроенными высокоскоростными приемопередатчиками.

Современные микросхемы фирмы Intel PSG (бывш. Altera) выпускаются по самым передовым проектным нормам на мощностях Intel (14 нм) и тайваньской фирмы TSMC (20 нм и более).

Более подробную информацию о продукции Intel PSG можно получить на нашем специализированном сайте www.altera.ru .

Наличие на складе

Продукция

Новости

03 Декабря 2021 altera.ru

С 6 по 9 декабря 2021 года Intel® FPGA проводит бесплатный вебинар для разработчиков, посвященный новой продукции

05 Апреля 2021 altera.ru

Компания Intel PSG® (ранее ALTERA) выпустила новую версию САПР Quartus Prime Pro Edition 21.1

28 Января 2021

altera. ru

ru

Компания Terasic представила универсальный компактный ускоритель FLIK

20 Октября 2020 altera.ru

Мультипротокольный промышленный шлюз Интернета вещей (IIOT), разработанный на базе С-н-К Intel Cyclone V SoC, для перехода к «Индустрии 4.0»

22 Июля 2020 altera.ru

Выпущена новая версия САПР Quartus Prime Pro Edition 20.2

15 Июня 2020 altera.ru

Компания Intel предлагает бесплатный доступ к средствам разработки, предназначенным для работы с ПЛИС Intel на своем облачном сервере Intel DevCloud.

21 Мая 2020 altera.ru

Представлена система на модуле на базе новейшего семейства ПЛИС Intel® AGILEX

20 Мая 2020 altera.ru

Представлены новые компоненты для построения многофазных понижающих DC-DC конверторов

22 Апреля 2020 altera.ru

Возрождение Бортового Управляющего Компьютера космического корабля АПОЛЛОН (Apollo Guidance Computer), сделанного 50 лет назад, с помощью платы TERASIC DE0-Nano

15 Апреля 2020

altera. ru

ru

Компания Terasic выпустила новый отладочный комплект Apollo Developer Kit.

Статьи

Июль 2009

Перспективные линейные стабилизаторы напряжения для питания микросхем программируемой логики фирмы Altera

69,33 KB

Каталоги, брошюры, CD-диски

Контакты

| Отдел программируемой логики | Роман Николаевич Золотухо | plis@efo. ru ru |

Ваш заказ

Наверх

Первый проект на FPGA Altera и подключение USB-Blaster в Linux / Хабр

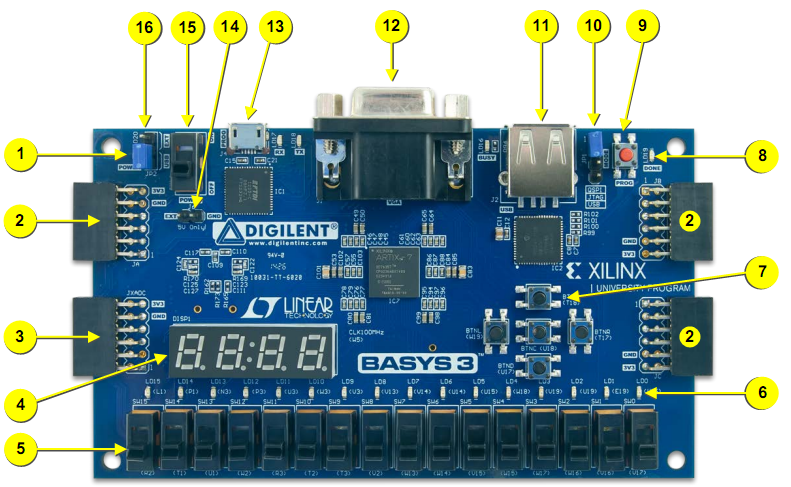

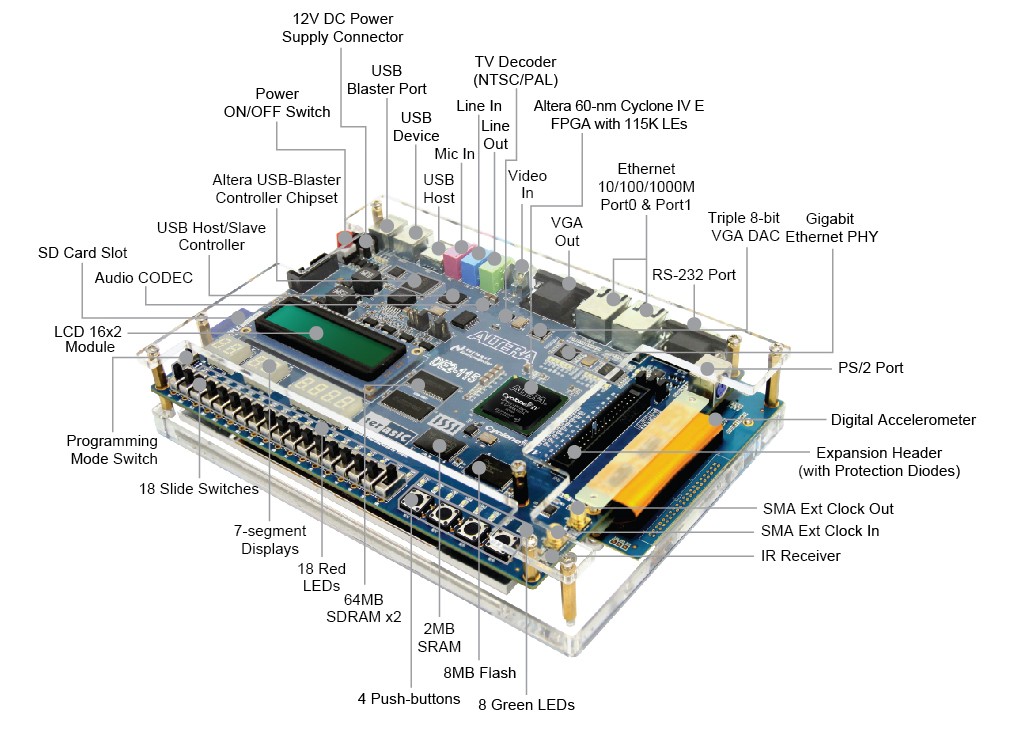

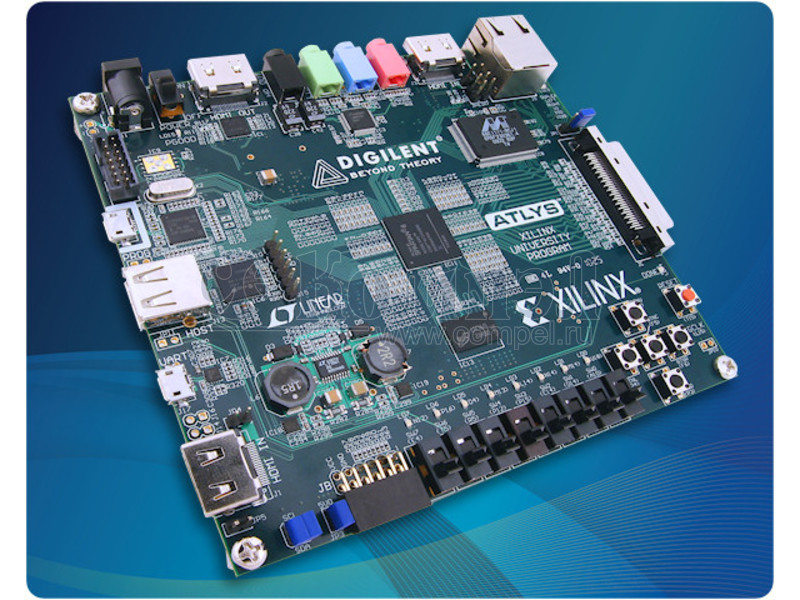

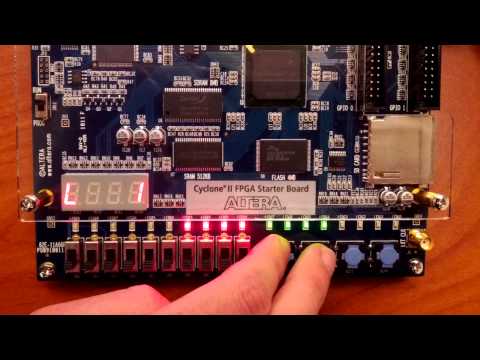

Продолжаем осваивать FPGA Altera. В первой части я описал процесс установки программного обеспечения Altera Quartus под CentOS7. Теперь уже наконец попробуем что-то сделать «железное», например светодиодики позажигаем. Но прежде небольшое вступление.

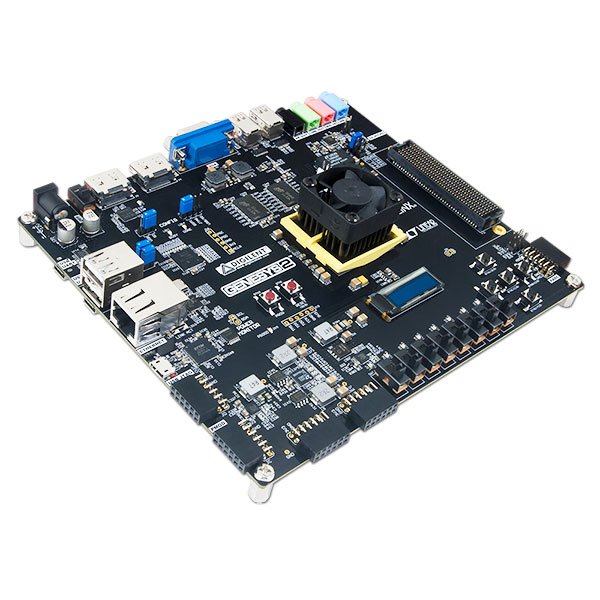

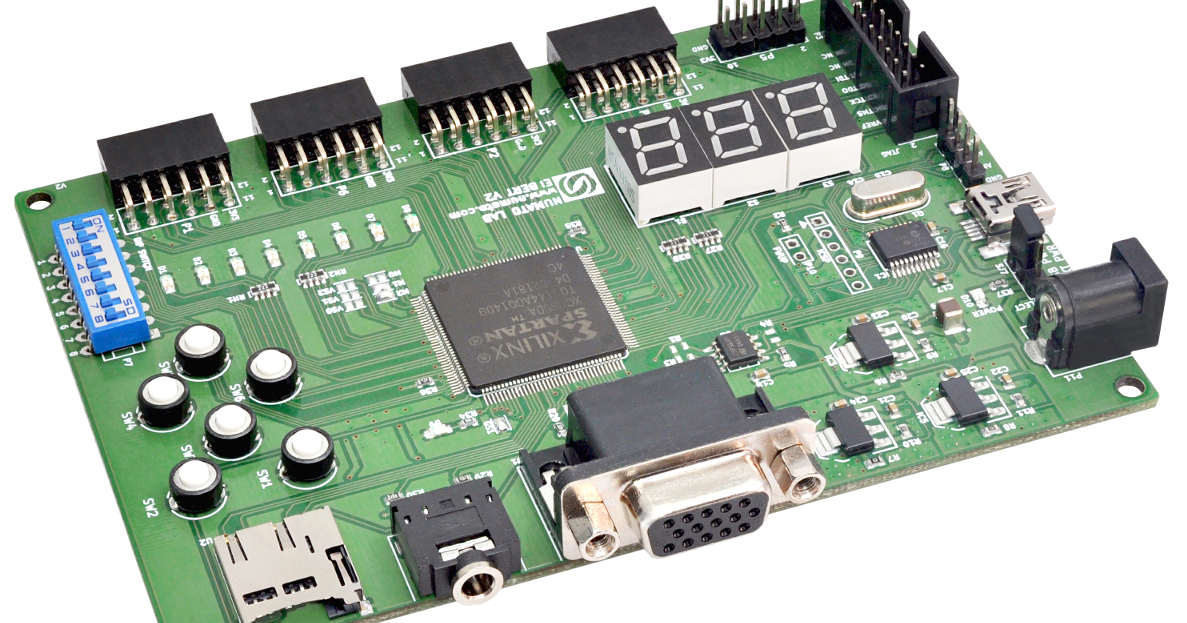

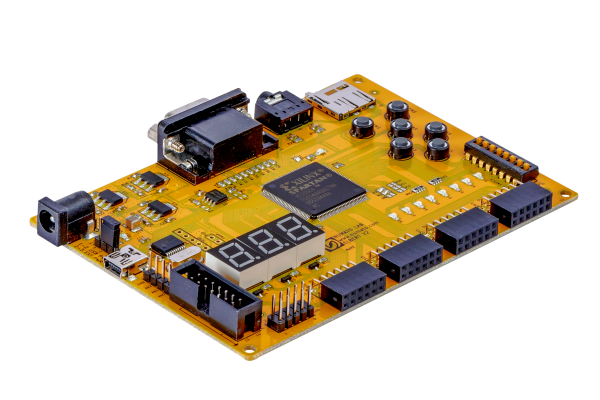

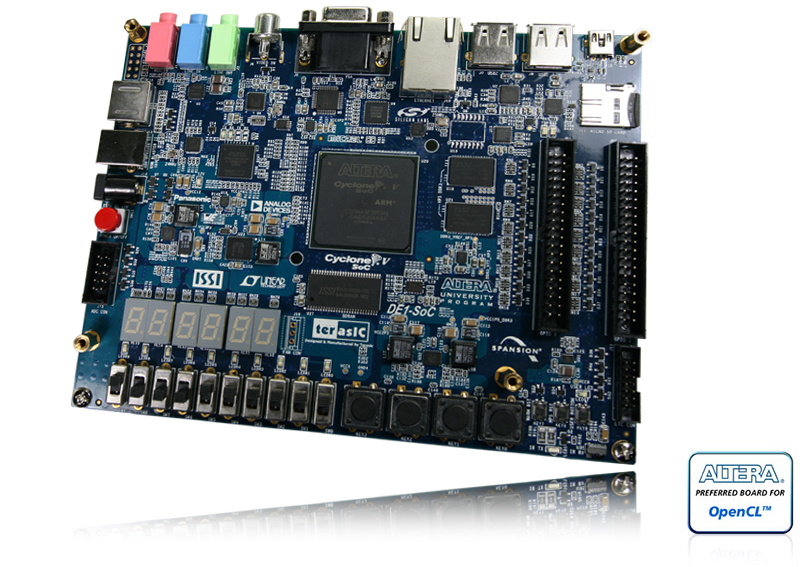

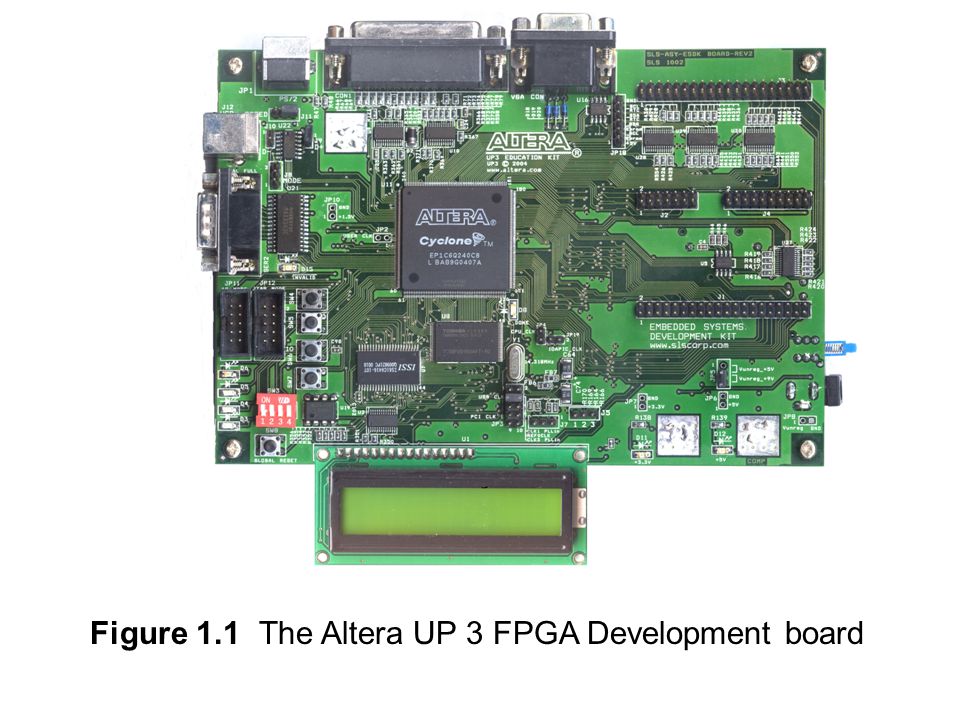

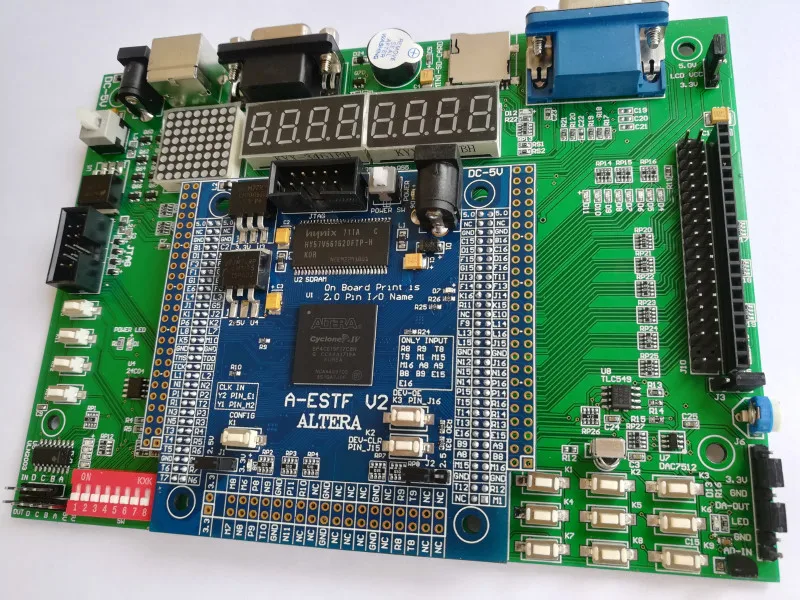

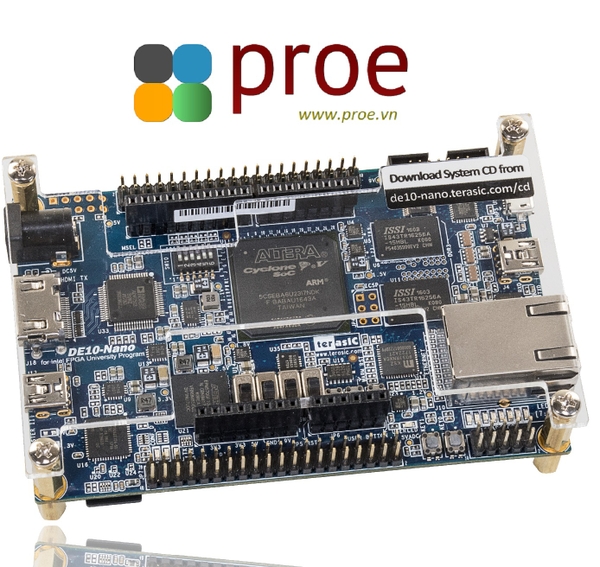

Одним из направлений моей деятельности является преподавание в кружке робототехники в небольшом городке Беларуси. Окунувшись во всю эту кухню и поучаствовав в разных конкурсах не только как тренер команды, но и как судья, я пришел к выводу, что ардуино в частности и микроконтроллеры в целом не самая лучшая база для конкурсных роботов (про лего вообще молчу). Многие задачи эффективней решать на уровне голой электроники. Кроме того 90% процентов кружков и «школ» робототехники не дают даже базовых знаний именно электроники, сосредоточившись чисто на «обучении» программированию готовых конструкций. Но чисто электронные роботы (например незаслуженно забытые BEAM) заточены под конкретную задачу и изменение условий конкурса приведет к необходимости существенной перестройки робота, что не всегда возможно. Вот тут я и вспомнил про программируемую логику. В результате поиска информации о применении ПЛИС в обучении я наткнулся на блог Юрия Панчула YuriPanchul. Пользуясь случаем я хочу публично выразить ему свою благодарность. Благодаря ему наш кружок совершенно бесплатно получил плату TerasIC DE0-CV c Altera Cyclone V на борту.

Но чисто электронные роботы (например незаслуженно забытые BEAM) заточены под конкретную задачу и изменение условий конкурса приведет к необходимости существенной перестройки робота, что не всегда возможно. Вот тут я и вспомнил про программируемую логику. В результате поиска информации о применении ПЛИС в обучении я наткнулся на блог Юрия Панчула YuriPanchul. Пользуясь случаем я хочу публично выразить ему свою благодарность. Благодаря ему наш кружок совершенно бесплатно получил плату TerasIC DE0-CV c Altera Cyclone V на борту.

Собственно эта и последующие публикации будут представлять собой реальный учебный материал, который мы реализовываем на кружке. И я буду благодарен за конструктивную критику и замечания, так как применение ПЛИС на кружках для школьников — нехоженая пока область.

Итак, начинаем. В этой публикации будут описаны первые шаги в Quartus, описание элементарной цифровой логики на языке Verilog и загрузка конфигурации в FPGA Altera Cyclone V. Работать мы будем с платой TerasIC DE0-CV, которая имеет на борту встроенный USB-Blaster. Так же затронем и вопрос «запуска» USB-Blaster под Linux.

Так же затронем и вопрос «запуска» USB-Blaster под Linux.

Запускаем Quartus:

Выбираем «Create a New Project». Запускается диалог мастера создания проекта. Тут просто нажимаем Next.

А теперь нам надо выбрать рабочую директорию для проекта (не забываем про права доступа!). Придумываем название проекта:

На следующем шаге нам предлагают добавить в проект дополнительные файлы. На данном этапе нам это не нужно, но в будущем для облегчения работы стоит добавлять как минимум файл назначения выводов.

Теперь настало время важных настроек. На этом шаге нам надо выбрать кристалл, под который пишется проект. В принципе если вы ошибетесь или захотите перекомпиллировать проект под другое устройство — это можно будет исправить позже.

Здесь нам предлагают выбрать дополнительные инструменты. Мы пока оставляем все как есть и жмем Next.

Ну вот, мы выполнили первоначальные настройки и создали проект. Жмем Finish.

Теперь нам нужно создать файл, описывающий логику проекта. Заходим в меню File/New, появляется диалог в котором требуется выбрать тип файла. В принципе логику можно нарисовать в специальном графическом редакторе, но сейчас мы выбираем Verilog HDL File:

Заходим в меню File/New, появляется диалог в котором требуется выбрать тип файла. В принципе логику можно нарисовать в специальном графическом редакторе, но сейчас мы выбираем Verilog HDL File:

Файл создан, пишем текст нашей программы, описывающей элементы NO, AND, OR, XOR. В качестве входов используем, имеющиеся на плате переключатели (key*), а состояние выхода индицируем светодиодами (led*). Небольшая ремарка: производитель платы предлагает создать конфигурационный файл для входов-выходов в специальной программе, работающей только под Windows. Если пойти этим путем, то надо следить чтобы имена «проводов» и «регистров» в программе совпадали с таковыми в конфигурационном файле. Но мы сейчас будем делать все вручную, поэтому вольны выбрать любые имена.

Теперь сохраняем файл. Важный момент — для корректной работы необходимо, чтобы имя файла совпадало с именем модуля, описываемого в программе (В нашем примере basic_logic).

Теперь необходимо сделать ряд настроек для успешной компиляции проекта. Во-первых укажем, какой модуль у нас главный явным образом. Конкретно в этом проекте это не актуально, но для сложных проектов с множеством модулей этот шаг обязателен. Заходим в меню Project/Set As Top Level Entity. Готово. Далее надо сделать ряд настроек для конкретного кристалла. Выберем пункт меню Assignments/Device. Открывается диалог, в котором мы имеем возможность изменить тип кристалла (или проверить, что ранее мы его указали верно):

Во-первых укажем, какой модуль у нас главный явным образом. Конкретно в этом проекте это не актуально, но для сложных проектов с множеством модулей этот шаг обязателен. Заходим в меню Project/Set As Top Level Entity. Готово. Далее надо сделать ряд настроек для конкретного кристалла. Выберем пункт меню Assignments/Device. Открывается диалог, в котором мы имеем возможность изменить тип кристалла (или проверить, что ранее мы его указали верно):

Теперь жмем кнопку Device and Pin Option и в открывшемся диалоге в первую очередь зададим состояние для неиспользуемых выводов. По умолчанию все неиспользуемые контакты микросхемы подключаются к нулю по питанию. Но мы не знаем, как эти выводы разведены физически на плате и такая конфигурация может привести к короткому замыканию и выходу из строя чипа. Поэтому безопасней неиспользуемые выводы сделать входами с высоким сопротивлением — As input tri-stated

Следующий необходимый шаг — указать, какие физические ножки микросхемы соответствуют входам и выходам описанного нами модуля. Для этого идем в меню Assignments/Assignment Editor. В открывшемся окне делаем нужные нам назначения согласно схеме нашей платы. В колонке To вписываем имя входа или выхода. В колонке Assignment Name выбираем из списка нужную нам настройку Location. В колонке Value вписываем название контакта микросхемы:

Для этого идем в меню Assignments/Assignment Editor. В открывшемся окне делаем нужные нам назначения согласно схеме нашей платы. В колонке To вписываем имя входа или выхода. В колонке Assignment Name выбираем из списка нужную нам настройку Location. В колонке Value вписываем название контакта микросхемы:

Закономерный вопрос: откуда берется название контактов? Обычно в даташите на плату или конкретную микросхему есть табличка PIN OUT. Так же, как я ранее писал, с платой может идти специальная программа, создающая конфигурационный файл. А сейчас вы можете воспользоваться этими данными:

Наконец-то можно нажать кнопочку Start Compilation!

Получаем 16 warnings. Ничего серьезного.

Можно посмотреть репорт:

Теперь подключаем плату и запускаем программу программатора: Tools/Programmer. Линукс автоматически подхватывает USB-Blaster, но прошивка не работает… Что же, открываем любимую консоль, вооружаемся бубном и погружаемся в документацию к Quartus…

Для начала убеждаемся, что система видит программатор:

dmesg | tail

Переходим в папку /etc/profile. d/ , где создаем файл custom.sh

d/ , где создаем файл custom.sh

А затем в папке /etc/udev/rules.d/ файл с названием 51-usbblaster.rules И наполняем его

смыслом:

Теперь все работает и прошивка прекрасно вгружается в чип:

Любуемся результатом, играемся переключателями, мигая светодиодиками:

ГАММА — Семейство ПЛИС FPGA компании Altera

Cyclone

Компания Altera представляет семейство Cyclone — самые недорогие FPGA. Имея вдвое меньшую стоимость по сравнению с конкурирующими недорогими FPGA, семейство Cyclone — это оптимальное решение для массовых, критичных к стоимости применений.

Устройства Cyclone построено на основе оптимизированной полностью медной технологии 1,5 В SRAM, и предлагает полную функциональность за половину цены конкурирующих устройств FPGA. С логической емкостью до 20’060 логических элементов (LE) и ОЗУ 288 Кбит, устройства Cyclone могут объединять в себе множество сложных функций. Устройства Cyclone содержат несколько полнофункциональных систем ФАПЧ (PLL), предназначенных для управления сетью тактовых сигналов и выделенных интерфейсов ввода/вывода, для работы с внешней памятью. Процессор для встроенных применений Nios и полный набор интеллектуальных продуктов (IP) Altera будут доступны для проектирования с устройствами Cyclone. Поддержка семейства Cyclone будет включена в ПО Quartus II Web Edition — бесплатное ПО доступное на сайте компании Altera.

С логической емкостью до 20’060 логических элементов (LE) и ОЗУ 288 Кбит, устройства Cyclone могут объединять в себе множество сложных функций. Устройства Cyclone содержат несколько полнофункциональных систем ФАПЧ (PLL), предназначенных для управления сетью тактовых сигналов и выделенных интерфейсов ввода/вывода, для работы с внешней памятью. Процессор для встроенных применений Nios и полный набор интеллектуальных продуктов (IP) Altera будут доступны для проектирования с устройствами Cyclone. Поддержка семейства Cyclone будет включена в ПО Quartus II Web Edition — бесплатное ПО доступное на сайте компании Altera.

Больше емкости за меньшую стоимость

Семейство устройств Cyclone — несомненный лидер по стоимости на рынке FPGA. При 4-х кратном увеличении логической емкости по сравнению с другими недорогими семействами и относительной ценой за 1’000 логических элементов менее 3$, устройства Cyclone устанавливают новый ценовой стандарт для программируемой логики. Комбинация недорогой структуры с богатыми ресурсами в устройствах Cyclone позволяет создавать законченные системы на кристалле (SOPC), идеальные для массовых применений.

Комбинация недорогой структуры с богатыми ресурсами в устройствах Cyclone позволяет создавать законченные системы на кристалле (SOPC), идеальные для массовых применений.

Недорогая альтернатива разработчикам полузаказных схем

Устройства Cyclone предлагают недорогую альтернативу следующему поколению применений, которые в настоящий момент используют полузаказные схемы (ASIC) низкой и средней емкости. Сегодня системные разработчики все чаще сталкиваются с различными трудностями, основными из которых являются увеличение ценового давления и сложности проектирования, появляющиеся новые стандарты и сокращающиеся циклы разработки. При разработке на полузаказных схемах привлекается множество технических ресурсов, проводятся сложные процессы моделирования и проверки разработки, и обычно требуется несколько циклов доводки. При использовании устройств Cyclone с возможностями интеграции системного уровня, устраняются дорогие единовременные затраты на проектирование, требования минимального заказа, и риск задержки продукции, который бывает при разработке с использованием полузаказных схем. Системные разработчики теперь получат некоторый ценовой паритет программируемой логики и полузаказных схем для своих массовых проектов.

Системные разработчики теперь получат некоторый ценовой паритет программируемой логики и полузаказных схем для своих массовых проектов.

Обзор семейства Altera Cyclone

Семейство Cyclon на сегодняшний день это самое недорогое семейство FPGA. Устройства Cyclone содержат оптимальный набор свойств для массовых применений, чувствительных к цене, таких как потребительские товары, автоэлектроника и коммуникационные устройства.

Выполненные по передовой технологии с медными слоями, устройства Cyclone имеют логическую емкость от 2’910 до 20’060 логических элементов (LE) и встроенную память, емкостью почти 300 Кбит (таблица 1). Устройства Cyclone поддерживают разные стандарты ввода/вывода, такие как LVTTL, LVCMOS, PCI, SSTL-2/3 и LVDS с поддержкой до 129 каналов, каждый из которых может работать со скоростями 311 Мбит/с. Устройства Cyclone содержат в своем составе выделенную цепь для подключения внешней памяти DDR SDRAM и FCRAM. Устройства Cyclone содержат до двух цепей ФАПЧ на кристалле и иерархическую структуру тактовых сигналов, предлагая богатые возможности управления тактовыми сигналами на уровне кристалла или платы. Комбинация этих свойств и эффективной архитектуры, делают это семейство FPGA наиболее гибкой и недорогой альтернативой полузаказным схемам ASIC. В таблице 2 представлены корпуса ПЛИС Cyclone.

Устройства Cyclone содержат в своем составе выделенную цепь для подключения внешней памяти DDR SDRAM и FCRAM. Устройства Cyclone содержат до двух цепей ФАПЧ на кристалле и иерархическую структуру тактовых сигналов, предлагая богатые возможности управления тактовыми сигналами на уровне кристалла или платы. Комбинация этих свойств и эффективной архитектуры, делают это семейство FPGA наиболее гибкой и недорогой альтернативой полузаказным схемам ASIC. В таблице 2 представлены корпуса ПЛИС Cyclone.

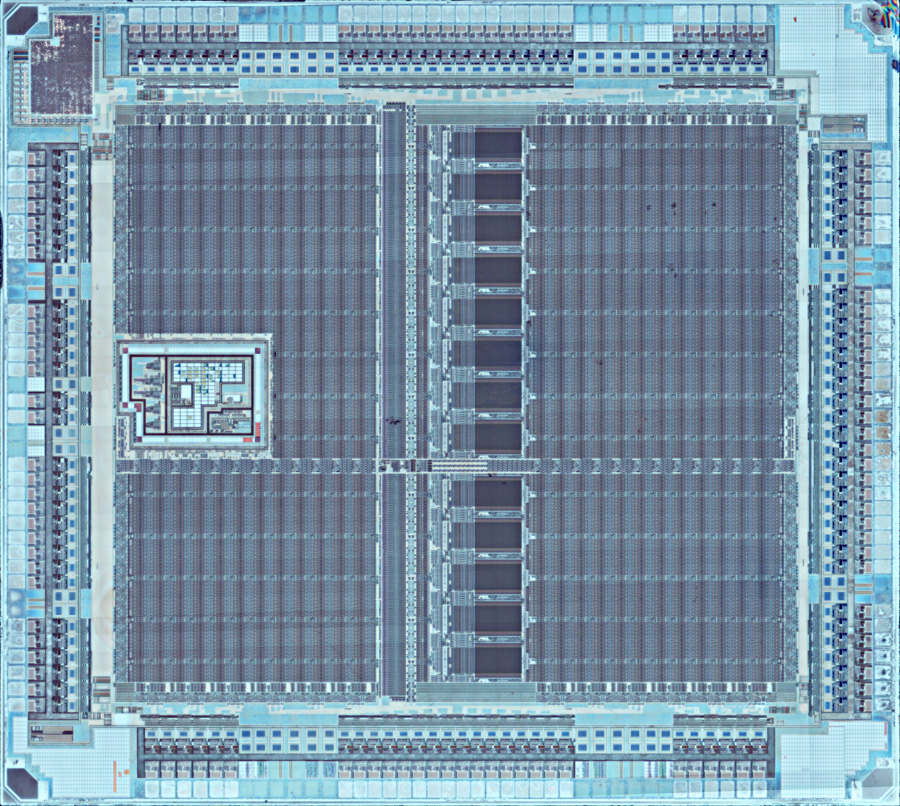

Архитектура устройств Cyclone

Зачастую, снижение цены предполагает снижение емкости или уменьшение функций. Но только не в случае с устройствами Cyclone. Устройства Cyclone содержат богатые ресурсы логики и памяти, цепь управления тактовыми сигналами и расширенные возможности ввода/вывода.

Хотя устройства Cyclone используют те же самые основные блоки, что и семейство Stratix, они не являются «переупакованной» версией полуфункциональных кристаллов Stratix. Устройства Cyclone разрабатывались «с нуля» используя те же новшества, повышающие производительность и снижающие занимаемую площадь, которые присутствуют в устройствах Stratix.

Устройства Cyclone разрабатывались «с нуля» используя те же новшества, повышающие производительность и снижающие занимаемую площадь, которые присутствуют в устройствах Stratix.

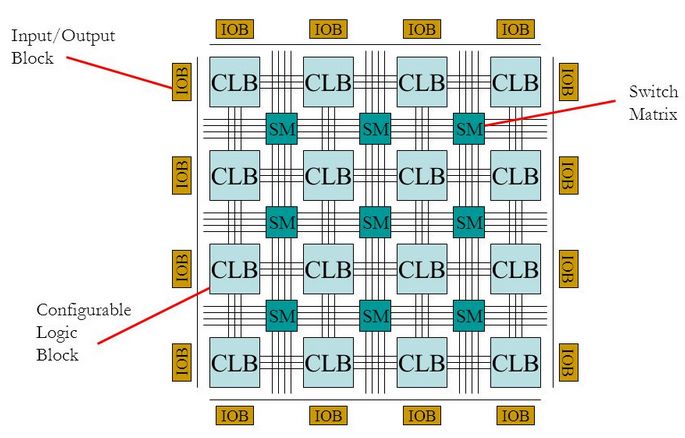

Архитектура Cyclone содержит вертикально упорядоченные логические элементы (LE), блоки встроенной памяти, и цепи ФАПЧ, которые окружены элементами ввода/вывода (рис.1). Высокоэффективная система межсоединений и структура тактовых сигналов с малым фазовым сдвигом обеспечивают связь между этими элементами для передачи тактовых сигналов и данных.

Рис.1 Архитектура устройств Cyclone.

Элементы ввода/вывода группируются в банки ввода/вывода, которые располагаются вокруг устройства, обеспечивая высокую производительность при минимальном занимаемом на кристалле месте. Элементы ввода/вывода поддерживают большой диапазон несимметричных и дифференциальных стандартов ввода/вывода, таких, как стандарт LVDS со скоростями передачи до 311 Мбит/с. Каждый элемент ввода/вывода содержит три регистра для реализации применений с двойной скоростью передачи данных (DDR) и связанную цепь для реализации таких свойств ввода/вывода, как программируемая интенсивность сигнала, удержание шины и программируемая скорость нарастания сигнала.

Каждый элемент ввода/вывода содержит три регистра для реализации применений с двойной скоростью передачи данных (DDR) и связанную цепь для реализации таких свойств ввода/вывода, как программируемая интенсивность сигнала, удержание шины и программируемая скорость нарастания сигнала.

Некоторые банки ввода/вывода содержат выделенную цепь для подключения внешней памяти. Эта цепь облегчает передачу данных внешним устройствам памяти, включая устройства DDR SDRAM и FCRAM. Максимальная скорость передачи данных достигает 266 Мбит/с (при тактовой частотой 133 МГц).

Устройства Cyclone совместимы со стандартом PCI 32-bit/66 МГц, и поддерживают спецификацию 2.1. Каждый элемент ввода/вывода обеспечивает несколько путей от вывода до ядра, что позволяет удовлетворить заданные требования по времени установки и задержкам.

Распределение тактовых сигналов

Все устройства Cyclone используют глобальную структуру тактовых сигналов, содержащей до 8 отдельных линий. Эти линии тактовых сигналов доступны со всех участков устройства и могут соединяться с входами, выходами цепей ФАПЧ, входами DDR/PCI или внутренней логикой (рис. 2).

Эти линии тактовых сигналов доступны со всех участков устройства и могут соединяться с входами, выходами цепей ФАПЧ, входами DDR/PCI или внутренней логикой (рис. 2).

Рис.2 Распределение тактовых сигналов.

Интерфейс внешней памяти в устройствах Cyclone

Устройства Cyclone способны работать с различными видами внешней памяти. Это новые стандарты памяти DDR SDRAM, FCRAM, и уже традиционные SDR SDRAM. Обмен данными осуществляется через выделенный интерфейс, который гарантирует быструю, надежную передачу данных со скоростями до 266 Мбит/с (таблица 3.) При использовании имеющихся, оптимизированных функций контроллеров, разработчики могут реализовать интерфейсы DDR SDRAM и FCRAM в считанные минуты.

Устройства DDR SDRAM и FCRAM

Недавно, устройства DDR SDRAM стали популярны благодаря низкому потреблению энергии, относительно небольшой стоимости и способности быстрой передачи данных. Передача данных происходит по обоим фронтам тактового сигнала, максимально увеличивая скорость передачи данных и удваивая эффективность по сравнению с более медленной архитектурой SDR. Устройства DDR SDRAM проникли на рынок через компьютерную область и теперь широко используются в широком диапазоне применений, от сетевых и коммуникационных приложений до домашних развлекательных приложений.

Передача данных происходит по обоим фронтам тактового сигнала, максимально увеличивая скорость передачи данных и удваивая эффективность по сравнению с более медленной архитектурой SDR. Устройства DDR SDRAM проникли на рынок через компьютерную область и теперь широко используются в широком диапазоне применений, от сетевых и коммуникационных приложений до домашних развлекательных приложений.

Устройства FCRAM похожие на SRAM устройства с малой задержкой, основанные на той же архитектуре, что и SRAM. Подобно SDRAM, устройства FCRAM поддерживают передачу данных по обоим фронтам системного тактового сигнала. Большая производительность этих устройств напрямую связана с собственными конвейерными и предзарядными операциями, которые существенно снижают время доступа по сравнению с архитектурой SDRAM.

Всё семейство Cyclone поддерживается бесплатным ПО Quartus II Web Edition.

На нашем сайте доступен для заказа диск Altera Complete Design Suite.

Назад

Основные производители современных ПЛИС-компьютеров и комплектующих к ним | PARALLEL.RU

Достаточно много компаний в мире занято производством цифровых устройств на основе ПЛИС и использованием их в своих системах. В данном разделе перечисляются и кратко описываются основные производители современных вычислительных систем на основе ПЛИС и комплектующих к ним.

Xilinx, Altera, Lattice Semiconductor, Actel, Atmel, Nallatech, Mitrionics, Alpha Data, QuickLogic, Achronix Semiconductor, MathStar, Rapid Prototypes, National Instruments, Sun Microsystems, SGI, Cray, MNB Technologies, CPU Tech, Exegy, Celoxica, XtremeData, Plurality.

Представительство российских компаний в данной области пока освещено

не слишком широко, русскоязычная информация достаточно скудна.

В данном разделе собрана информация о российских организациях, работающих

в области ПЛИС-компьютеров.

НИИ МВС, ФГУП «НИИ КВАНТ», Инлайн Груп, Эфо, ИТМИВТ, Высокотехнологичные системы, НПП «Цифровые решения», DeverSYS,

|

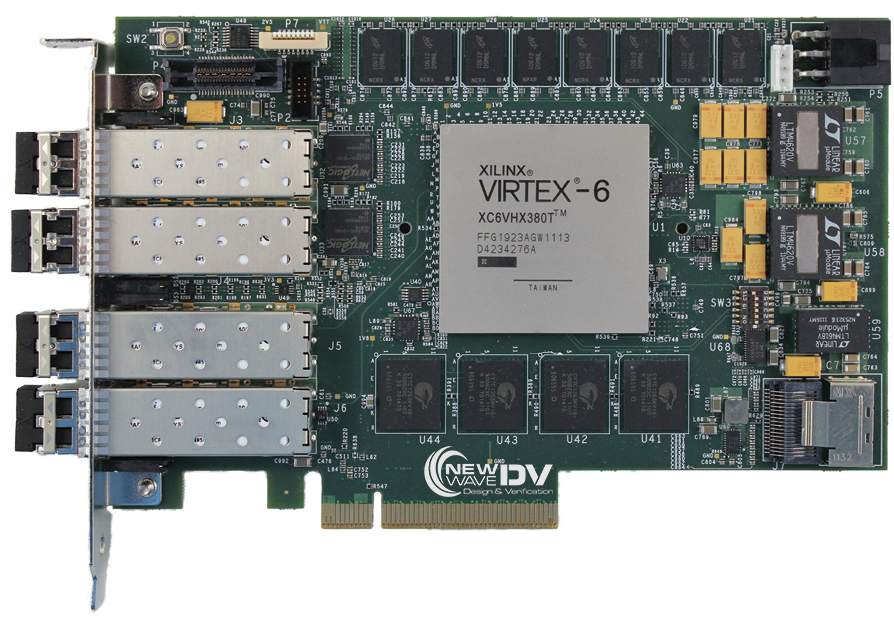

Xilinx |

Основанная в 1984 году американская компания Xilinx является одним из лидеров в области производства ПЛИС-микросхем. На данный момент у этой компании существует несколько серий выпускаемой аппаратуры для разного рода вычислений:

Микросхемы данных серий применяются довольно широко: последнее семейство Virtex-5 из серии Virtex используется, например, в суперкомпьютерах Cray XT5h и NEC SX-9. Также ПЛИС FPGA являются альтернативой процессоров цифровой обработки сигналов, для чего в каждом семействе присутствуют модели со встроенными блоками для этой обработки. Для работы с представленными микросхемами компания Xilinx предоставляет различные программные средства для реализации цифровых схем, для разработки встраиваемых программируемых процессорных систем, а также для отладки и повышения производительности. Помимо собственно разработки микросхем, компания Xilinx уделяет большое внимание цифровой обработке сигналов, разработке различных IP-ядер для использования в микросхемах, созданию встроенных процессоров и др. |

|

Altera |

Компания Altera является основным конкурентом компании Xilinx, причем

по всем основным направлениям. Начиная с серии Stratix III, в ПЛИС используется технология

Programmable Power Technology, которая позволяет варьировать режим работы

и, соответственно, потребляемую мощность логических ячеек в зависимости от

необходимости быстрого выполнения поставленной задачи. Микросхемы компании Altera активно применяются во многих областях, например, на рынке беспроводных и проводных коммуникаций, в военных технологиях, в области телевещания, а также в различных мобильных устройствах. Компания Altera занимается разработкой разнообразного ПО для работы с их микросхемами, среди которых основным программным продуктом является пакет программ Quartus II, который предоставляет различные средства для проектирования и анализа структуры микросхем, а также для оптимизации затрат по потребляемой мощности. |

|

Lattice Semiconductor |

Lattice Semiconductor только в 2002 году начала производство FPGA-микросхем, и на этом рынке она занимает всего порядка нескольких процентов. Однако Lattice Semiconductor является одним из лидеров в области производства CPLD и SPLD (simple PLD — более простые по сравнению с CPLD программируемые устройства) микросхем. На этом рынке компания предоставляет целый спектр ПЛИС различной направленности:

Хотя компания Lattice Semiconductor появилась на рынке ПЛИС FPGA относительно недавно, она выпускает довольно большой ассортимент микросхем данного типа. Среди них стоит выделить микросхемы Field Programmable System Chip (FPSC) — первой серии ПЛИС со встроенными ASIC ядрами, которые предназначены для реализации стандартных IP ядер — шинного интерфейса, высокоскоростного интерфейса или высокоскоростного трансивера; а также серию Lattice XP2 и предназначенный для его программирования прикладной пакет ispLEVER, которым в 2008 году была присуждена премия DesignVision Award в области «Средства программирования микросхем типа ASIC, FPGA и PLD». |

|

Actel |

Компания Actel делает ставку на производство небольших и недорогих

микросхем типа FPGA, ориентируясь на надежность таких ПЛИС.

Оба типа микросхем обеспечивают высокий уровень защищенности информации как от несанкционированного доступа, так и от альфа- и нейтронного излучения. Также большим преимуществом таких микросхем является тот факт, что они являются не изменяющимися — не требуют загрузки конфигурации архитектуры ПЛИС каждый раз при включении питания. Это означает, что они готовы к работе сразу же после запуска оборудования. Поскольку компания Actel занимается производством компактных и

недорогих ПЛИС (в феврале этого года Actel стала выпускать микросхемы

серии ProASIC3 по рекордно низкой цене в 99 центов), основными ее

покупателями являются компании, занимающиеся различными портативными

устройствами и автомобильной промышленностью. Также благодаря

описанным свойствам высокой надежности и моментальной готовности к

работе микросхемы компании Actel используются в военной и

аэрокосмической областях. Также стоит отметить разработанную компанией Actel технологию Fusion, которая позволяет объединить логические блоки FPGA, flash-память и аналоговые устройства на одной микросхеме. |

|

Atmel |

Компания Atmel занимается многими отраслями рынка полупроводников:

производством микроконтроллеров, устройств Flash-памяти, ASIC-устройств,

а также ПЛИС. Направление программируемых микросхем, производством

которых она занялась в 1999 году, не является приоритетным, и набор

предоставляемой продукции не очень велик. На рынке ПЛИС типа FPGA

основной является серия AT40KAL — небольшие микросхемы с числом

ячеек порядка нескольких тысяч, используемых в основном для цифровой

обработки сигналов. На базе этих микросхем построено семейство чипов

Field Programmable System Level Integrated Circuits (FPSLIC),

объединяющих на одном кристалле микропроцессорное ядро, оперативную

память и программируемую логику. Помимо производства собственно микросхем, компания Amtel занимается производством оперативной EEPROM памяти (в том числе Flash-памяти), предназначенной для использования в собственных микросхемах серии FPSLIC и FPGA-устройствах основных производителей. Также Amtel предоставляет услугу Ultimate Logic Conversion (ULC), в рамках которой разработанный для ПЛИС проект переносится на создаваемые этой компанией более дешевые ULC-кристаллы. Процесс конвертирования компания практически полностью берет на себя. В течение 20 лет предоставления этой услуги было преобразовано около 2000 проектов. |

|

Nallatech |

Шотландская компания Nallatech является одним из лидеров в

области создания готовых вычислительных решений на основе ПЛИС. Существует 4 различные серии плат в соответствии с поддерживаемым ими интерфейсом: PCI, cPCI, PIC-104 или VME. Большинство из них работают на ПЛИС Virtex II Pro или Virtex 4, однако в конце 2007 года вышла PCI-X плата со встроенной микросхемой Virtex-5. Все платы поддерживают некоторое количество подключаемых модулей. Эти модули могут отличаться встроенными ПЛИС (Virtex II Pro либо Virtex 4; также бывают модули с двумя встроенными микросхемами), объемом и типом оперативной памяти, а также наличием аналогового или цифрового ввода/вывода. Данные модули подключаются к платам с помощью созданного этой компанией интерфейса Dime. Для того чтобы облегчить использование предоставляемых решений,

компания Nallatech предоставляет среду проектирования DimeTalk, а

также пакет FUSE — набор API для языков С/С++ и пакета MatLab. Помимо оборудования для настольных ПК Nallatech также предоставляет вычислительные решения для HPC производительностью до 50 GFlop/s, представленные в формате IBM BladeCenter или в качестве PCI-X платы. В частности, платы Nallatech h201 используются в суперкомпьютере Maxwell. |

|

Mitrionics |

Эта компания из Швеции занимается довольно узким направлением — созданием программного обеспечения для упрощения использования ПЛИС в HPC-технологиях. Основная разработка Mitrionics — выпущенный в 2005 году продукт Mitrion Platform, который состоит из Mitrion Virtual Processor (MVP) и Mitrion SDK. MVP — это построенный на программном ядре настраиваемый процессор

с массовым параллелизмом. По своей сути, MVP является абстракцией,

прослойкой между пользовательской программой и аппаратурой. Сначала

программа преобразуется в конфигурацию для MVP, после чего

сконфигурированный нужным образом процессор запускается на ПЛИС и

реализует подходящую архитектуру этой микросхемы. Преобразованием пользовательской программы в конфигурацию для MVP занимается Mitrion SDK. В состав этого пакета входят компилятор, отладчик, а также симулятор для тестирования приложений при отсутствии доступа к ПЛИС-аппаратуре. Программа должна быть написана на Mitrion-C — языке программирования с неявным параллелизмом, по синтаксису сильно напоминающем С. Поскольку MVP берет целиком на себя задачу проектирования ПЛИС-устройств, которые отличаются довольно сильно от производителя к производителю, он не может быть универсальным. Обеспечивается поддержка следующих платформ:

Продукция компании Mitrionics применяется для решения различных

ресурсоемких задач, требующих HPC-вычислений, таких как изучение

последовательностей генов, распознавание образов, а также в

биоинформатике. |

|

Alpha Data |

Данная компания занимается производством оборудования на основе ПЛИС-микросхем. Среди выпускаемой продукции можно выделить две группы:

Выпускаемые компанией Alpha Data платы применяются в военной и космической промышленностях, в телекоммуникациях, а также в цифровой обработке сигналов. Для облегчения работы с ними компания предлагает программные пакеты, встраиваемые в программы Matlab и Simulink. ПЛИС-платы компании Alpha Data используются в суперкомпьютере Maxwell, а также в таких компаниях, как Boeing, Nokia и Motorola. |

|

QuickLogic |

Организованная в 1988 году компания QuickLogic полностью

ориентирована на рынок портативных устройств. CSSP устройства компании QuickLogic обладают следующими свойствами:

В связи с изменением политики компании, серия ПЛИС PolarPro была переориентирована в соответствующие CSSP устройства, а также было выпущено новое семейство CSSP микросхем ArcticLink. Сферы применения микросхем компании QuickLogic:

|

|

Achronix Semiconductor |

В отличие от многих производителей ПЛИС, компания Achronix Semiconductor при производстве ПЛИС FPGA делает ставку не на низкую стоимость и энергопотребление, а на высокую производительность и надежность. Выпускается две серии микросхем:

Причиной появления столь высокой тактовой частоты является использование

асинхронной технологии — элементы микросхемы не синхронизированы между

собой. При этом частота в 2.2 ГГц означает, что такая микросхема работает

с той же производительностью, что и имеющая аналогичную архитектуру

синхронизированная микросхема

(

CEO Interview: John Lofton Holt of Achronix). Как становится понятным из вышеперечисленных свойств выпускаемых данной компанией микросхем, основными целевыми отраслями являются сферы, требующие большой вычислительной мощности и/или работы в экстремальных условиях. Это аэрокосмическая и военная промышленности, высокопроизводительные вычисления, а также сфера коммуникаций и цифровая обработка сигналов. |

|

MathStar |

Компания MathStar занимается производством устройств с программируемой

логикой, однако она выпускает не совсем обычные микросхемы —

Field Programmable Object Arrays (FPOA). Отличием последних является то,

что в них логические вентили объединены в объекты, каждый из которых

обладает некоторой законченной функциональностью. Объекты бывают двух

типов: основные и периферийные. Основные объекты — арифметико-логическое

устройство, умножитель и регистровый файл, — работают на частоте в 1 ГГц

и предназначены собственно для вычислений, тогда как периферийные объекты

предоставляют дополнительную память и доступ к вводу/выводу. Преимуществом такого подхода является абстрагирование от самого низкого уровня архитектуры при ее проектировании: пользователю приходится работать не с уровнем вентилей, а с уровнем объектов. Это существенно упрощает процесс проектирования, однако уменьшает гибкость системы. Основной и практически единственной областью применения данных устройств является обработка видео и изображений, о чем свидетельствует набор предоставляемых IP-ядер, нацеленных целиком на использование в данной сфере. |

|

Rapid Prototypes |

|

National Instruments |

Основной сферой компании National Instruments является разработка и

создание различных программно-аппаратных средств автоматизации

моделирования, диагностики, тестирования и т. Среди готовых решений представлены программируемые контроллеры, подключаемые PCI и PXI платы, предназначенные для обработки данных или организации высокоскоростного ввода/вывода, а также системы слежения, в которых FPGA-микросхемы используются для обработки изображений, модуляции сигналов и синхронизации. |

|

Sun Microsystems |

Компания Sun в 2005 году запустила проект OpenSparc, в рамках которого

она предоставляет открытые коды процессора UltraSparc T1 и предлагает

разработчикам участвовать в процессе его усовершенствования. А для того,

чтобы процесс разработки был более доступным, Sun предлагает реализацию

на ПЛИС некоторых элементов OpenSparc — собственно ядра процессора Sparc,

математического сопроцессора и коммутатора между центральным процессором

и кэш-памятью. |

|

SGI |

Компания SGI является одним из лидеров в области высокопроизводительных вычислений. Среди ее разработок семейство Altix масштабируемых блейд-серверов, система высокоскоростного межсетевого взаимодействия NUMALink, а также различные решения в области хранения данных. Для увеличения производительности компания SGI выпустила в 2006 году блейд-модуль с использованием FGPA ускорителей — SGI RASC RC100. В его состав входят две ПЛИС микросхемы Xilinx Virtex 4, 80 МБ QDR SRAM, а также 4 порта NUMALink. Модуль рассчитан на использование в блейд-серверах семейства Altix. Компания SGI предлагает использовать данное решение в задачах исследования жидкостей и газа, биоинформатики, а также в военной сфере. Для возможности использования и программирования ПЛИС-микросхем предлагается следующее:

Проект RASC (Reconfigurable Application Specific Computing). |

|

Cray |

Компьютерный гигант компания Cray поддерживает программу Adaptive Supercomputing, идея которой состоит в создании гибридных суперкомпьютеров, объединяющих различные архитектуры. Необходимость таких компьютеров они объясняют тем, что суперкомпьютеры с обычной архитектурой зачастую не предоставляют нужной производительности, а главное — гибкости. В 2004 году Cray построила гибридный суперкомпьютер Cray XD1, в котором для большего ускорения совместно с основными процессорами AMD Opteron используются FPGA-микросхемы компании Xilinx. А в 2007 году был построен суперкомпьютер Cray XT5h, объединяющий в себе скалярные и векторные процессоры, а также процессоры на основе ПЛИС. |

|

MNB Technologies |

Образованная бывшими сотрудниками компании Mentor Graphics компания

MNB Technologies занимается разработкой и производством устройств на

основе ПЛИС, обладающих повышенной надежностью и предназначенных для

использования в «полевых» условиях, то есть в мобильных и персональных

компьютерах.

Также компания MNB Technologies предлагает различные сервисы по разработке необходимой архитектуры для плат, ПЛИС-микросхем и проектированию. |

|

CPU Tech |

Основное направление компании CPU Tech — разработка и создание

систем на кристалле (SoC) — схем, выполняющих функцию целого устройства. Основным решением компании в области «железа» является SoC-семейство Acalis. CPU Tech называет эти устройства Программируемые логические многоядерные схемы (Field Programmable Multicore Chip, FPMC). Если обычные ПЛИС микросхемы — это набор вентилей, то FPMC — это набор ядер, которые в этих устройствах являются элементарными единицами. Каждое ядро (микропроцессор) — это либо блок вычислений, ввода/вывода или RAM памяти, либо контроллер памяти, либо элемент коммуникаций. Для работы с данными устройствами не требуется специальное ПО: те программные средства, которые используются при работе со стандартными микропроцессорами, могут быть применены и на FPMC-устройствах. |

|

Celoxica |

|

XtremeData |

|

Plurality |

|

НИИ МВС ЮФУ |

Многопроцессорные системы с программируемой архитектурой, построенные

на основе принципа модульного наращивания.

|

|

ФГУП «НИИ КВАНТ» | Кластеры из реконфигурируемых вычислительных модулей на базе специализированных плат с программируемыми логическими интегральными схемами. |

|

Инлайн Груп |

|

ИТМИВТ |

|

Высокотехнологичные системы |

|

НПП «Цифровые решения» |

|

DeverSYS |

© Лаборатория Параллельных информационных технологий НИВЦ МГУ

Рынок Altera и Xilinx в России. FPGA.

Давно хотел написать статью о рынке программируемой логики (FPGA), а если быть точнее, о брендах Altera и Xilinx. Мой интерес обусловлен тем, что лет 18 назад я начал развивать направление по продажам Altera в России. Мы не были дистрибьюторами, но нашли выход на дистрибьюторов в Китае. Всё сложилось так хорошо, что когда спустя много лет к нам приехал представитель Altera для обсуждения условий дистрибуции, компания, не будучи дистрибьютором, оказалась на втором месте по продажам в России. Последняя новость о том, что AMD покупает Xilinx, напомнила мне об этом желании.

Мы не были дистрибьюторами, но нашли выход на дистрибьюторов в Китае. Всё сложилось так хорошо, что когда спустя много лет к нам приехал представитель Altera для обсуждения условий дистрибуции, компания, не будучи дистрибьютором, оказалась на втором месте по продажам в России. Последняя новость о том, что AMD покупает Xilinx, напомнила мне об этом желании.

Согласно прогнозам аналитиков объем продаж FPGA достигнет в 2026 году $9,1 млрд., что значительно превышает сумму $6,2 млрд в 2021 году (данные MarketsandMarkets). В среднем за год рост объема продаж составляет 7,8%. Основные факторы прироста: развертывание центров обработки данных (ЦОД) и высокопроизводительных вычислений, внедрение искусственного интеллекта (ИИ) и интернета вещей (IoT).

В мире две компании делят большую часть рынка.

Altera — американская компания, существовавшая в 1983-2015 годах, бесфабричный производитель ПЛИС. В июне 2015 года была поглощена корпорацией Intel за $16,7 млрд. После слияния Intel и Altera, в рамках Intel было сформировано подразделение Intel PSG, в котором сконцентрировались все компетенции Altera. После поглощения Altera перестала развиваться, как независимая компания, о чем свидетельствует тот факт, что ее сайт и домен больше не функционируют. Подразделение PSG занимает в общих продажах Intel 2,6%.

После поглощения Altera перестала развиваться, как независимая компания, о чем свидетельствует тот факт, что ее сайт и домен больше не функционируют. Подразделение PSG занимает в общих продажах Intel 2,6%.

Xilinx — американский разработчик и производитель интегральных микросхем программируемой логики (ПЛИС, FPGA). 27 октября 2020 года было заключено соглашение о слиянии компаний AMD и Xilinx. По собственному заявлению компании, она занимает 51% мирового рынка FPGA. На втором месте, с долей 34%, располагается Altera, и на третьем, с большим отставанием от лидеров – Lattice Semiconductor.

Данные по продажам, указанные в Таблице 1 (в млрд долларов), взяты мной из открытых источников.

Таблица 1. Данные по продажам лидеров по ПЛИС или FPGA в мире.

| 2018 | 2019 | 2020 | |

| Xilinx | 2,4 | 3 | 3,1 |

| Intel | 2,1 | 2 | 1,9 |

| Lattice Semiconductor | 0,28 | 0,4 | 0,4 |

Любопытно, что двоих непримиримых конкурентов купили два других непримиримых конкурента. С рыночной точки зрения все логично: для обеих компаний рынок решений для серверов и ЦОД является стратегическим. Потеря конкурентных преимуществ на нем недопустима.

С рыночной точки зрения все логично: для обеих компаний рынок решений для серверов и ЦОД является стратегическим. Потеря конкурентных преимуществ на нем недопустима.

Три компании из Таблицы 1 контролируют весь рынок, их мы и будем анализировать. Остальные игроки в 2020 году владели незначительными долями на мировом рынке и нулевыми на российском. Перечислим эти компании: Microchip Technology Microsemi, QuickLogic (US), TSMC (Taiwan), United Microelectronics (Taiwan), GLOBALFOUNDRIES (US), Achronix (US), S2C Inc (US), Efinix Inc. (US), Flex Logix Technologies (US), GOWIN Semiconductor Corporation (US).

Итак, в 2020 году реальное положение рынка в России распределялось в соответствии с Таблицей 2.

Таблица 2. Рынок в России лидеров по ПЛИС или FPGA в мире.

| Изготовитель | Итог |

| INTEL | 2170464 |

| INTEL/ALTERA | 12451674 |

| XILINX | 75406377 |

| LATTICE | 155437 |

| Общий итог | 90183952 |

Две компании удерживают лидирующие позиции и составляют основную долю рынка. Другие фирмы, включая LATTICE, в данной обзорной статье рассматриваться не будут.

Другие фирмы, включая LATTICE, в данной обзорной статье рассматриваться не будут.

С XILINX все просто – это независимая компания, ее импорт не сложно увидеть и рассчитать. Компания ALTERA перестала существовать, но многие импортеры все еще используют этот бренд при импорте. Во второй строке, где указан изготовитель INTEL/ALTERA, итоговая цифра складывается из данных об импорте, при котором был использован конкретно бренд ALTERA, слова FPGA, ПЛИС или подразделение PSG. Для получения корректных данных мне пришлось использовать различные комбинации названий и словосочетаний.

Цифра импорта в первой строке INTEL получена более сложным путем. После обработки информации и расчетов импорта производителя INTEL/ALTERA у меня осталось более $100 млн под брендом INTEL. Я удалил строки с такими ключевыми словами, как процессоры, микропроцессоры, преобразователи, удалил всех IT-дистрибьюторов, а также всех, кого не было в списке расшифрованных импортеров, работающих на компонентном рынке. В результате осталась цифра, которую вы видите в первой строке. Она содержит поставки именно бренда INTEL, без указания ключевых слов (ALTERA, FPGA, ПЛИС и т.д), тех импортеров, включая бывших дистрибьюторов, которые работают на компонентном рынке и были засвечены в моих более ранних статьях.

В результате осталась цифра, которую вы видите в первой строке. Она содержит поставки именно бренда INTEL, без указания ключевых слов (ALTERA, FPGA, ПЛИС и т.д), тех импортеров, включая бывших дистрибьюторов, которые работают на компонентном рынке и были засвечены в моих более ранних статьях.

После вышеописанных действий, у меня остался список компаний, которые не являются 100% игроками на компонентном рынке. Они импортировали бренд INTEL под тремя ключевыми кодами ТНВД, именно по этим кодам на 95% импортируется и XILINX, всего на $6,5 млн. Это та сумма, которую нельзя однозначно отнести к процессорам INTEL, но и однозначного признака, например слов FPGA, кроме таможенного кода, они не содержат. Приведу только 4 компании из этого списка для примера, в случайном порядке: ООО «НЕОТЕХНИКА», ООО «ЭЛКО РУС», ООО «МАРСАЛА», ООО «НОВЫЙ АЙ ТИ ПРОЕКТ».

Как видите, это все IT-дистрибьюторы. Я не отношу этот импорт к FPGA, но обязан привести эту цифру, что бы вы понимали, почему мои результаты могут не сходиться с цифрами, которыми вы, возможно, владеете. Повторюсь, я не уверен, что эти компании импортировали именно ПЛИС, поэтому приводя данную цифру, анализировать и заносить ее в Таблицу 2 не считаю нужным. Итого, в сумме, бренд INTEL/ALTERA импортировал в Россию $14,5 млн. Не могу утверждать, что эта цифра достоверная, это минимальная сумма, а реальная, скорее всего, на 1-2 млн больше.

Повторюсь, я не уверен, что эти компании импортировали именно ПЛИС, поэтому приводя данную цифру, анализировать и заносить ее в Таблицу 2 не считаю нужным. Итого, в сумме, бренд INTEL/ALTERA импортировал в Россию $14,5 млн. Не могу утверждать, что эта цифра достоверная, это минимальная сумма, а реальная, скорее всего, на 1-2 млн больше.

Необходимо отметить, что еще в 2017 году ситуация была кардинально другой. Почему 2017 год? Сделка по поглощению была анонсирована в середине 2015 года, 2016 год – время подготовки, а 2017 год стал переломным.

Поставки все еще осуществлялись по старым условиям, если компания INTEL и успела их пересмотреть, то новые только начинали оказывать свое воздействие на российский рынок. В 2017 году примерно $50 млн импорта приходилось на ALTERA и $40 млн на XILINX.

Такая диспропорция, в 2017 и 2020, меня сильно озадачила. Сначала подумал, что мои обобщенные данные по ALTERA и INTEL неверны, и решил проверить алгоритм по двум официальным дистрибьюторам ALTERA (от 2016 года).

Обобщенные данные представлены в Таблице 3.

Таблица 3. Продажи официальных дистрибуторов ALTERA по данным этого статуса от 2016, тыс. usd.

| дистрибьютор 1 | дистрибьютор 2 | |||

| 2017 | 2020 | 2017 | 2020 | |

| ALTERA | 4999 | 707 | 1742 | 307 |

| XILINX | 58 | 112 | 52 | 50 |

| INTEL | 0 | 832 | 21 | 144 |

| итого | 5057 | 1651 | 1815 | 501 |

Я зашел на сайт INTEL, эти компании, еще в 2016 году точно дистрибьюторы ALTERA, на странице дистрибьюторов INTEL не указаны. Это важно, обе компании не указаны на сайте INTEL, как прямые дистрибьюторы. Скорее всего, у них есть статус субдистрибьютора или аналогичный, и, несомненно, остались все компетенции. Отмечу, что это весь импорт бывших дистрибьюторов, включая процессоры, словом – все, что поставляет в Россию INTEL.

По Таблице 3 видно огромное падение продаж. Я не знаю, чем это вызвано, повышением цен, разрушением каналов поставок или массовым снятием с производства популярных в России семейств продукции. Важно то, что это разрушило устоявшуюся и конкурентную модель бизнеса, что привело к повальному переходу клиентов на XILINX и потере конкурентоспособности ALTERA в целом.

Просто посмотрите на цифры 2017 года по ALTERA. Подразделение PSG, бывшая ALTERA, занимала в общих продажах Intel 2,6%, а доля России в продажах ALTERA (PSG) составляла 2,5%, половину из которых занимали непрямые поставки, не через официальных дистрибьюторов.

Руководство INTEL ничего не стало регулировать. Каков результат? Рынок остался примерно на одном уровне, доли поменялись кардинально. Мое личное мнение, что компания AMD после покупки XILINX предпримет то же самое, они не будут вникать в тонкости нашего рынка и порежут текущие каналы поставок на свое усмотрение.

Итак, в 2020 году рынок импорта Altera и Xilinx в России составлял $90млн. Далее я разделю каждый бренд на 2 группы, брокеры и производители. В обоих случаях данные достоверны, рассматриваются исключительно расшифрованные мной поставщики-брокеры и производители с сайтами (если они есть). Обе группы работают на компонентном рынке. Контрактные производители, транспортные компании и брокеры в таблицах не представлены. Под брокерами я подразумеваю всех посредников, включая дистрибьюторов.

Далее я разделю каждый бренд на 2 группы, брокеры и производители. В обоих случаях данные достоверны, рассматриваются исключительно расшифрованные мной поставщики-брокеры и производители с сайтами (если они есть). Обе группы работают на компонентном рынке. Контрактные производители, транспортные компании и брокеры в таблицах не представлены. Под брокерами я подразумеваю всех посредников, включая дистрибьюторов.

Под остальными – всех расшифрованных мною импортеров, не попавших в ТОП-15.

Таблица 4. ТОП-15 импортеров ALTERA в России в 2020 году.

| Брокеры | Итог | Производители | Итог |

| 1 | 1700525 | 1 | 1059046 |

| 2 | 830045 | 2 | 439286 |

| 3 | 649323 | 3 | 302094 |

| 4 | 414023 | 4 | 230022 |

| 5 | 276611 | 5 | 196193 |

| 6 | 268738 | 6 | 151363 |

| 7 | 266752 | 7 | 99521 |

| 8 | 253943 | 8 | 78969 |

| 9 | 251459 | 9 | 70384 |

| 10 | 243872 | 10 | 66054 |

| 11 | 234953 | 11 | 64360 |

| 12 | 213069 | 12 | 47672 |

| 13 | 206811 | 13 | 46821 |

| 14 | 203337 | 14 | 46139 |

| 15 | 187482 | 15 | 31042 |

| Всего ТОП-15 | 6200943 | Всего ТОП-15 | 2928965 |

| Остальные | 3648875 | Остальные | 160763 |

| Сумма 12939545 | |||

Таблица 5. ТОП-15 импортеров-производителей XILINX в России в 2020 году.

ТОП-15 импортеров-производителей XILINX в России в 2020 году.

| Брокеры | Итог | Производители | Итог |

| 1 | 27524353 | 1 | 2787090 |

| 2 | 7731328 | 2 | 2093427 |

| 3 | 6738701 | 3 | 1172752 |

| 4 | 2618715 | 4 | 757500 |

| 5 | 2259930 | 5 | 534660 |

| 6 | 1532318 | 6 | 432457 |

| 7 | 1159071 | 7 | 428450 |

| 8 | 1035360 | 8 | 427514 |

| 9 | 924860 | 9 | 256644 |

| 10 | 823213 | 10 | 244533 |

| 11 | 614301 | 11 | 216017 |

| 12 | 446855 | 12 | 204370 |

| 13 | 355105 | 13 | 195985 |

| 14 | 319946 | 14 | 109003 |

| 15 | 289242 | 15 | 81897 |

| Всего ТОП-15 | 54373296 | Всего ТОП-15 | 9942297 |

| Остальные | 3640918 | Остальные | 393521 |

| Сумма 68350032 | |||

Взглянув на эти таблицы, можно с уверенностью сказать, что 80% импортных поставок осуществляют брокеры, а если прибавить глобальных дистрибьюторов, то процент будет стремиться к 100%.

Если статья вам понравилась, подписывайтесь, чтобы ознакомиться с остальными и видеть новые. Скоро выйдет интересная статья о керамических конденсаторах, планируется статья об одном полностью русском сайте.

Что такое ПЛИС и с чего начать изучение FPGA Altera?

Что такое ПЛИС и с чего начать изучение FPGA Altera?

30 января 2020

897

0

С чего начинается изучение ПЛИС Альтера: подробный алгоритм действий – как сделать все самому и что для этого нужно.

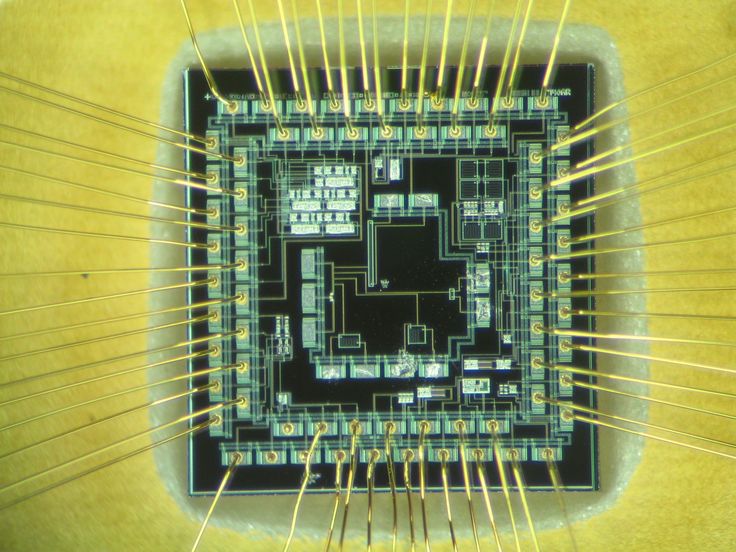

Современные ПЛИС – программируемые логические микросхемы, выполняемые по технологии от 10 нм и содержащие большое количество логических элементов. Элементы могут выполнять простые логические операции «И», «ИЛИ» и др. или реализовывать функции умножителей, сумматоров, мультиплексоров и более сложных устройств.

FPGA – это микросхемы, в которых производителем не определены связи между логическими элементами. Разработчику необходимо самому определять взаимосвязи, назначение выводов и пути прохождения сигналов. В этом заключается большой плюс ПЛИС, так как следствием такого подхода становятся исключительно гибкая архитектура и быстродействие полученной электронной схемы. Но за это приходится платить увеличенным временем разработки устройства.

Разработчику необходимо самому определять взаимосвязи, назначение выводов и пути прохождения сигналов. В этом заключается большой плюс ПЛИС, так как следствием такого подхода становятся исключительно гибкая архитектура и быстродействие полученной электронной схемы. Но за это приходится платить увеличенным временем разработки устройства.

С чего начать обучение? Читайте в нашей статье

Автор

Сухомлинов Максим Валерьевич

Электроника-РА

Другие полезные материалы

-

Жизненный цикл импортных электронных компонентов

2510

-

Прогноз развития рынка электронных компонентов на 2018 год

3352

-

Методика оценки поставщиков импортных активных электронных компонентов

5091

-

4 западных метода борьбы с контрафактными импортными электронными компонентами

3089

-

Как повысить качество закупаемой электронной компонентной базы?

1625

-

Как выбрать надежного поставщика электронных компонентов?

1929

-

Маркировка микросхем Atmel

1233

-

Объективны ли традиционные критерии выбора поставщика?

3485

-

Кейс.

Комплектование авиапредприятия микросхемами Altera с проверкой качетства

Комплектование авиапредприятия микросхемами Altera с проверкой качетства

910

-

Кейс. Импортные реле для производства систем навигации для судостроения

993

-

Как определить сроки хранения и службы импортных микросхем?

4218

-

3 способа скачать datasheet микросхем импортного производства

1968

-

Как найти аналоги зарубежных микросхем за 3 минуты?

725

-

Кейс.

Поставка украинских устройств контактных для пр-ва испытательной оснастки

Поставка украинских устройств контактных для пр-ва испытательной оснастки

742

-

Поставка комплектующих производства Ближнего зарубежья на авиаремонтный завод

563

-

Что такое RoHS и REACH: Влияние на крупные рынки

654

-

Как проверить снята ли импортная микросхема с производства или еще выпускается?

1068

Программная автономная плата разработки Altera FPGA от Simulink — MATLAB & Simulink

Основное содержание

В этом примере показано, как настроить макетную плату Altera ® FPGA для синтеза с использованием FPGA Turnkey

рабочий процесс.

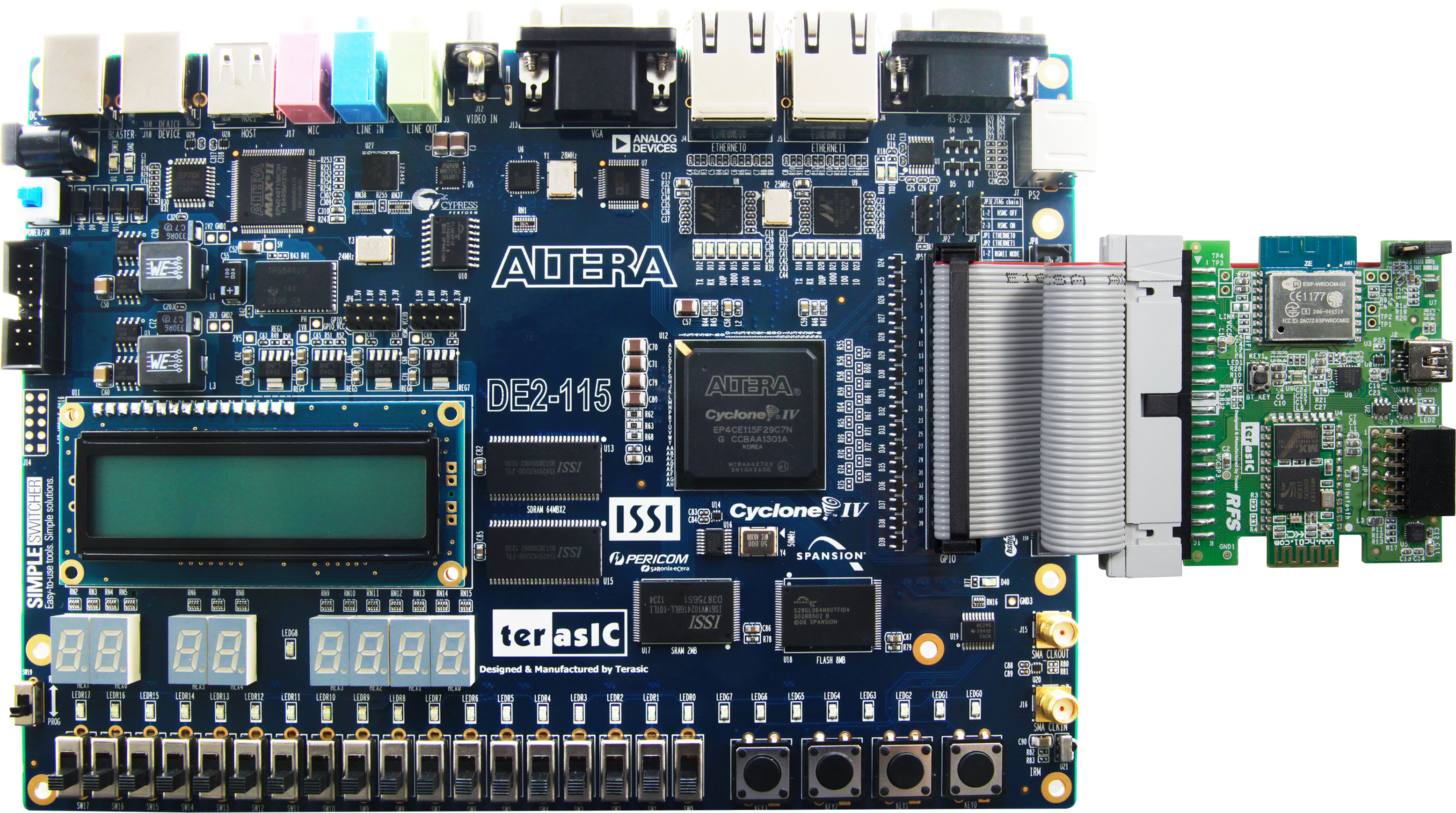

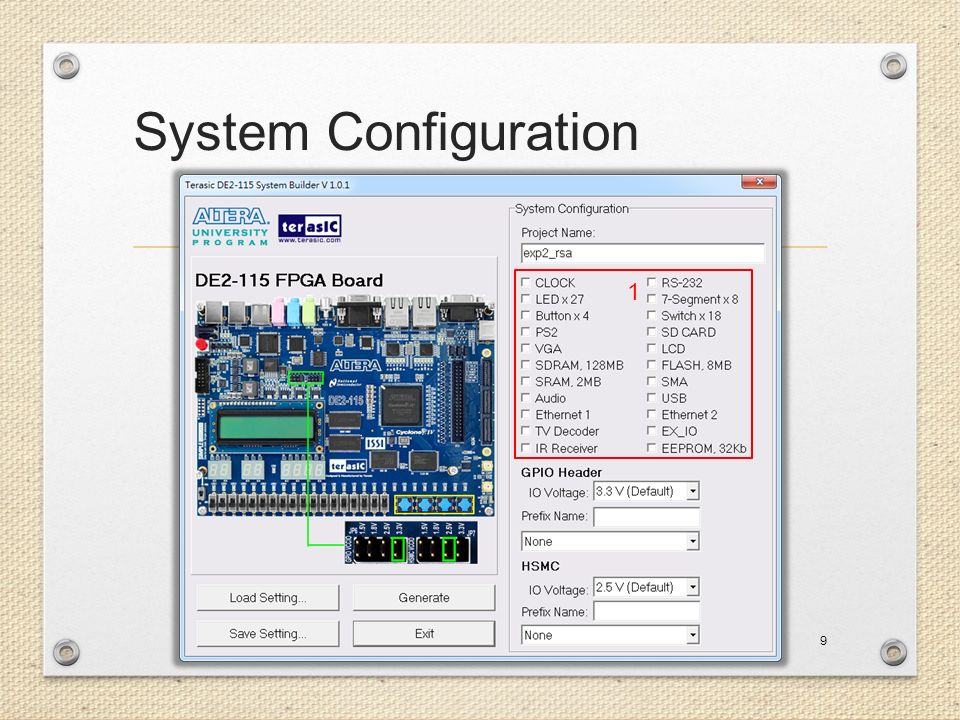

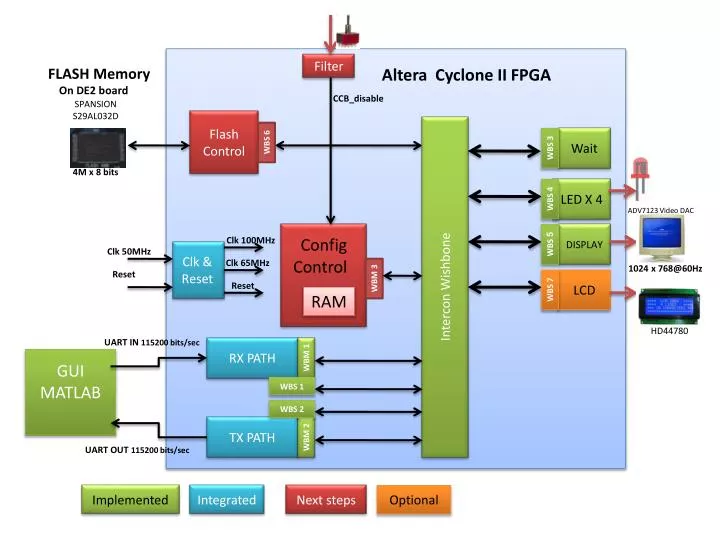

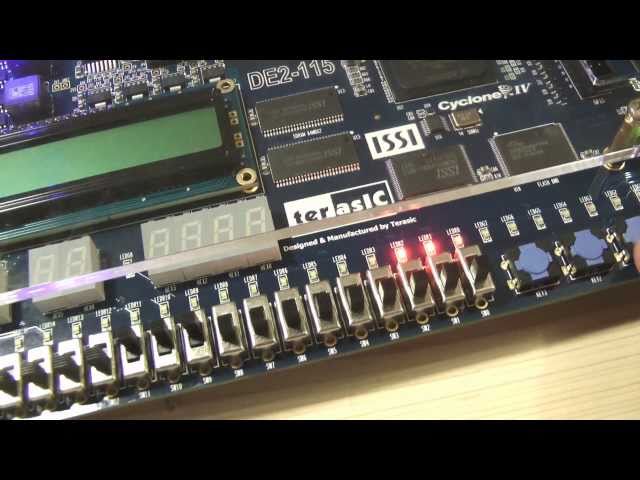

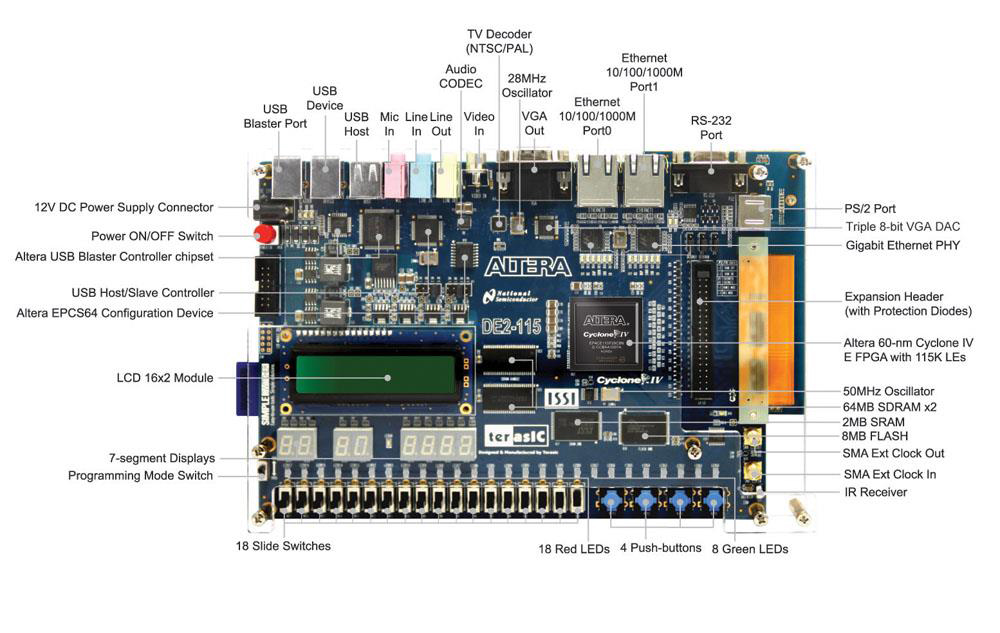

Модель hdlcoderUARTServoControllerExampleAltera предназначена для

работа с платой разработки и обучения Altera DE2-115.

Подсистема UART_Servo_on_FPGA получает команды через UART

порты. Подсистема генерирует сигнал широтно-импульсной модуляции (ШИМ) для управления

серводвигатель.

Прежде чем начать

Для запуска этого примера необходимо настроить инструмент синтеза. Чтобы научиться устанавливать ваш инструмент синтеза, см. Настройка пути к инструменту синтеза.

В этом примере используется плата разработки и обучения Altera DE2-115. Вы можете попробовать этот пример с другой плате и укажите целевой интерфейс в соответствии с определение интерфейса. Чтобы просмотреть список плат Altera, поддерживаемых для рабочего процесса FPGA «под ключ», см. Поддерживаемые инструменты и оборудование EDA.

Если вы хотите загрузить файл программирования, вы должны сначала подключить цель

устройство. Однако, если целевое устройство не подключено, вы все равно можете сгенерировать

программный файл.

Однако, если целевое устройство не подключено, вы все равно можете сгенерировать

программный файл.

Откройте модель

-

Добавьте каталог примеров к вашему пути MATLAB ® .

addpath(fullfile(docroot,'toolbox','hdlcoder','examples'))

-

Откройте модель.

hdlcoderUARTServoControllerExampleAltera

Выберите целевое устройство

-

Щелкните правой кнопкой мыши подсистему

UART_Servo_on_FPGAи выберите > . -

В HDL Workflow Advisor выберите Set Target > Установить задачу целевого устройства и инструмента синтеза .

-

Для Целевой рабочий процесс выберите FPGA Под ключ .

-

Для целевой платформы , выберите Altera DE2-115 совет по развитию и образованию .

Если плата не появляется в списке автоматически, выберите Получите дополнительные платы , чтобы загрузить пакет поддержки плат Altera FPGA.

HDL Workflow Advisor автоматически устанавливает инструмент синтеза на основе ваш выбор доски.

-

Щелкните .

Установка целевого интерфейса и целевой частоты

-

На левой панели HDL Workflow Advisor выберите набор . Задача целевого интерфейса .

-

Для каждого порта выберите параметр из целевой платформы . Меню интерфейсов , как показано на следующем рисунке, и щелкните Применить .

Каждому порту назначается указанная битовая позиция

[или диапазон битовые позицииb][.младший бит:старший бит] Ширина спецификации в битах должна равняться ширине порта на

ДУТ. Когда вы выбираете параметры, HDL Workflow Advisor автоматически

выделяет битовый диапазон. Вы можете дважды щелкнуть в диапазоне бит /

Столбец Address / FPGA Pin для редактирования значения.

Ширина спецификации в битах должна равняться ширине порта на

ДУТ. Когда вы выбираете параметры, HDL Workflow Advisor автоматически

выделяет битовый диапазон. Вы можете дважды щелкнуть в диапазоне бит /

Столбец Address / FPGA Pin для редактирования значения. Для получения подробной информации о каждой целевой платформе . Интерфейсы , обратитесь к документации вашей платы.

-

Щелкните .

-

В задаче Set Target Frequency установите FPGA системная тактовая частота до 100 МГц, затем нажмите Run Это Задача .

В этом примере целевая частота должна быть 100 МГц из-за фиксированного Скорость передачи UART.

Создание кода, синтез и программирование целевого устройства

После выбора целевого устройства и настройки его интерфейса порта HDL

Workflow Advisor может выполнять следующую последовательность задач автоматически. Эти задачи

включают:

Эти задачи

включают:

-

: Проверка модель совместимости генерации HDL-кода.

-

: Настройка, связанная с HDL параметры диалогового окна Model Configuration Parameters и создание HDL код.

-

: Выполнение синтез и временной анализ в Altera Quartus II. Обратное аннотирование модели критическим путем информация, полученная в ходе синтеза.

-

имеет две подзадачи:

Для автоматического запуска этой последовательности задач:

-

Откройте группу задач.

-

Щелкните правой кнопкой мыши и выберите .

Последовательность задач завершается программированием целевой платы с помощью сгенерированный программный файл. Затем вы можете прочитать генерацию кода и файлы журналов синтеза.

Вы щелкнули ссылку, соответствующую этой команде MATLAB:

Запустите команду, введя ее в командном окне MATLAB. Веб-браузеры не поддерживают команды MATLAB.

Выберите веб-сайт, чтобы получить переведенный контент, где он доступен, и ознакомиться с местными событиями и предложениями. В зависимости от вашего местоположения мы рекомендуем вам выбрать: .

Вы также можете выбрать веб-сайт из следующего списка:

Европа

Обратитесь в местный офис

В чем разница между Xilinx FPGA и Altera FPGA? — Производство печатных плат и сборка печатных плат

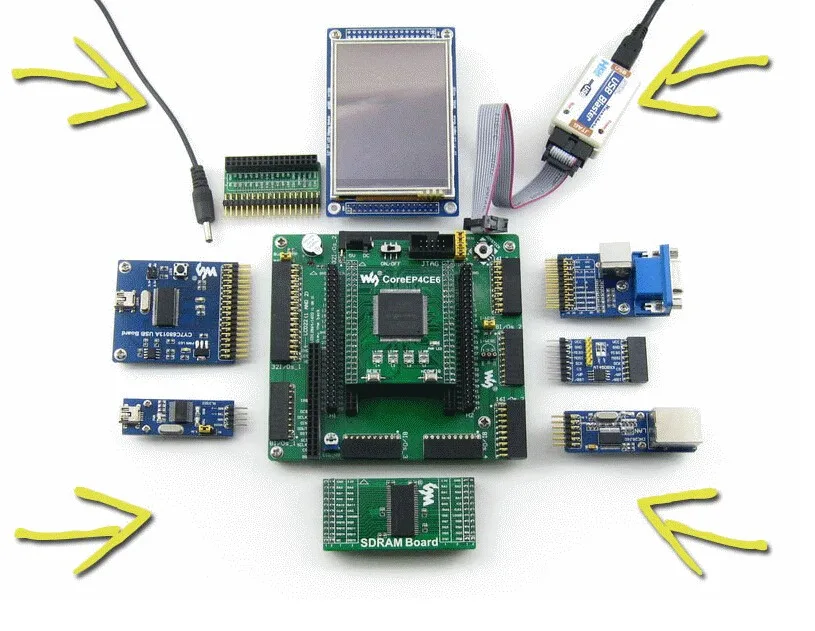

Думаете о покупке платы FPGA от Altera? Вот список некоторых из лучших доступных плат FPGA с различными функциями и целями. Наряду с описанием, эта статья включает спецификации и идеи о том, как легко их получить.

Ученые, инженеры и любители используют ПЛИС для самых разных проектов. Кроме того, некоторые люди используют ПЛИС в своей повседневной жизни, даже не подозревая об этом. Примеры включают следующее:

Кроме того, некоторые люди используют ПЛИС в своей повседневной жизни, даже не подозревая об этом. Примеры включают следующее:

FPGA обычно используются в областях, связанных с компьютерами, включая обработку изображений, цифровую обработку сигналов, сжатие/распаковку видео, компьютерное зрение, сжатие/распаковку данных, компьютерные сети и телекоммуникационные устройства, разработанные такими производителями, как RayMing PCB и Assembly .

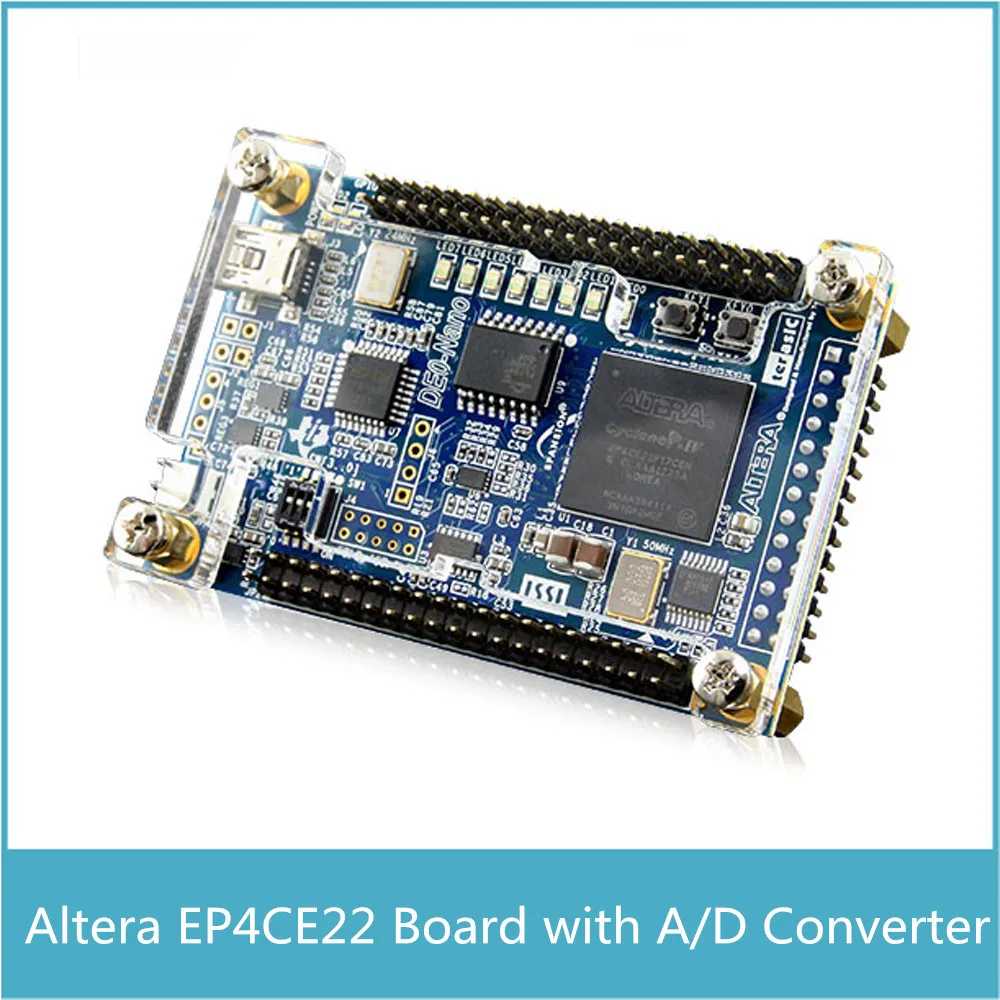

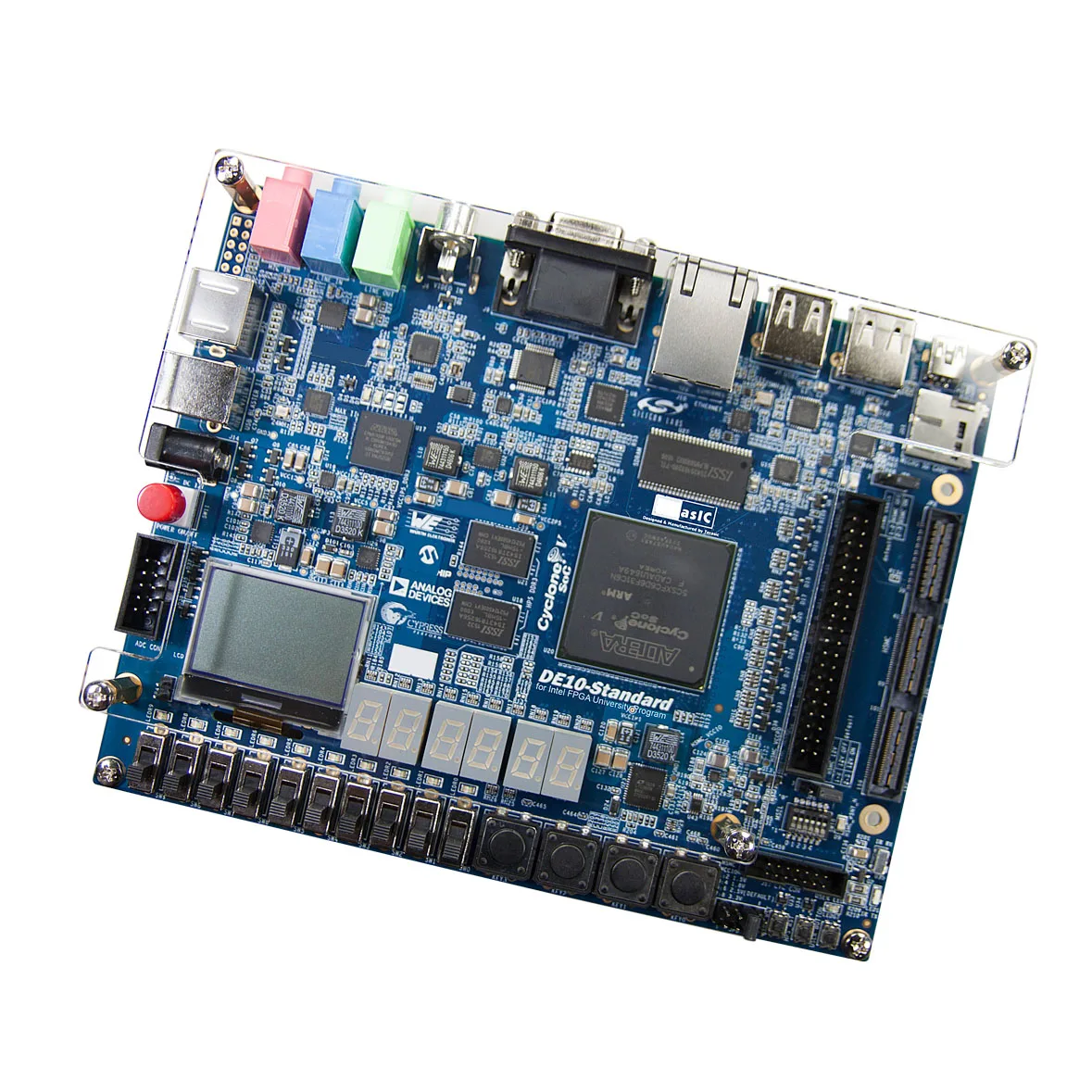

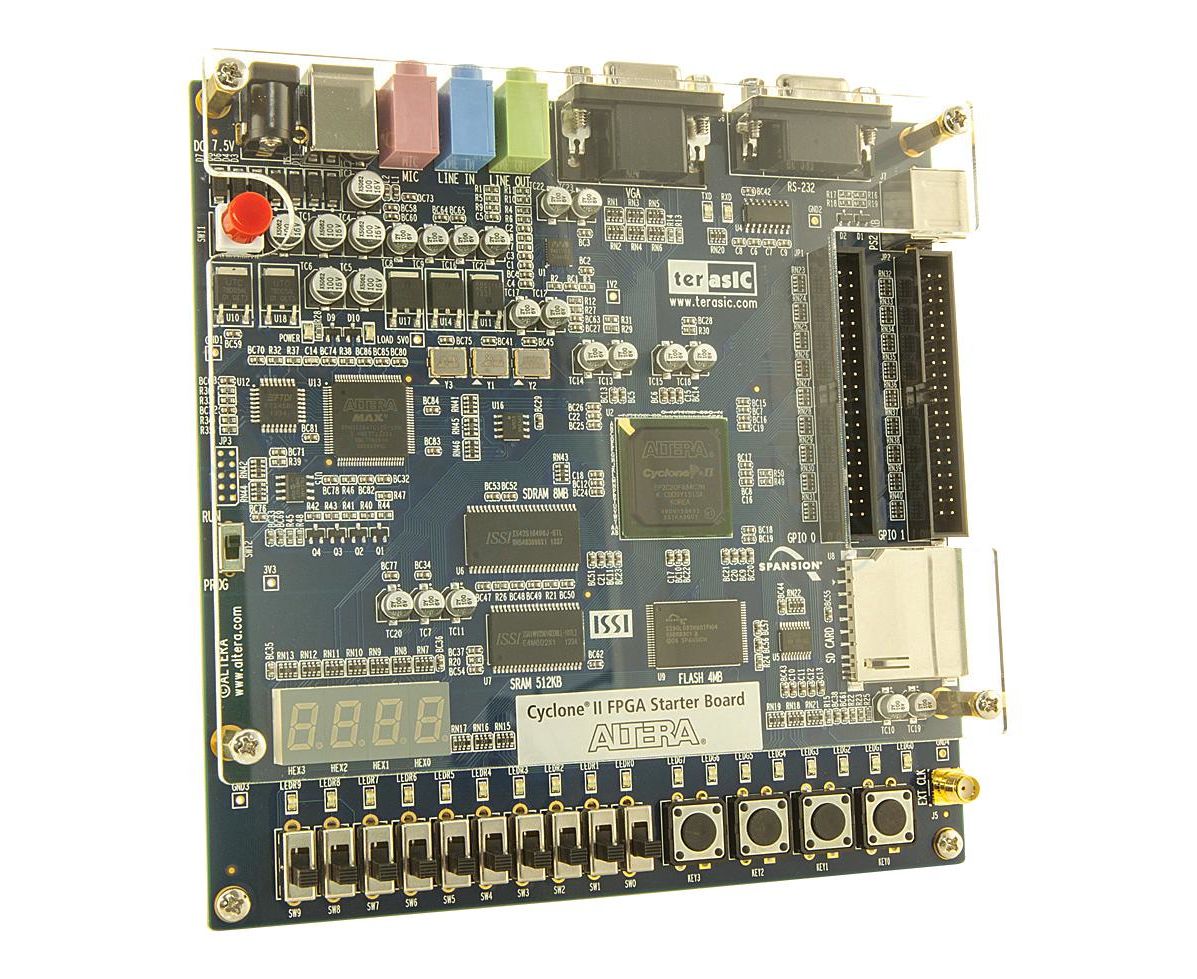

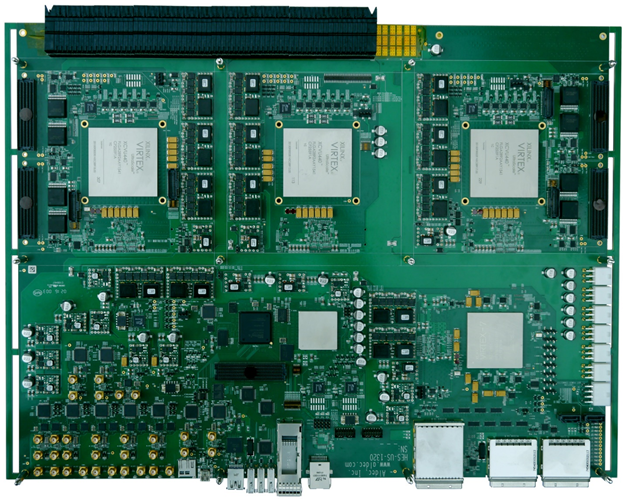

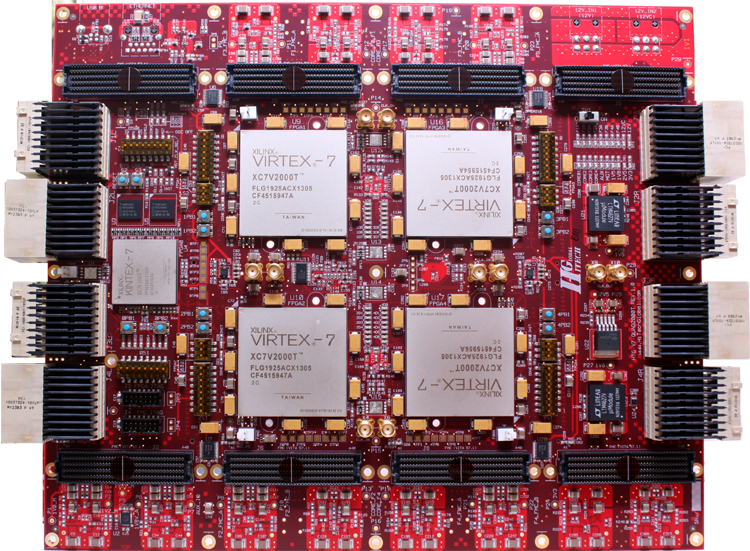

Платы FPGA серии Altera представляют собой многопользовательскую многопоточную конструкцию, подходящую для многих областей применения, таких как автоматизация предприятий, цифровая обработка сигналов и кибербезопасность. Эти серии включают устройства FPGA с широким диапазоном расширения ввода-вывода для приложений с интенсивным использованием процессора. Среди них:

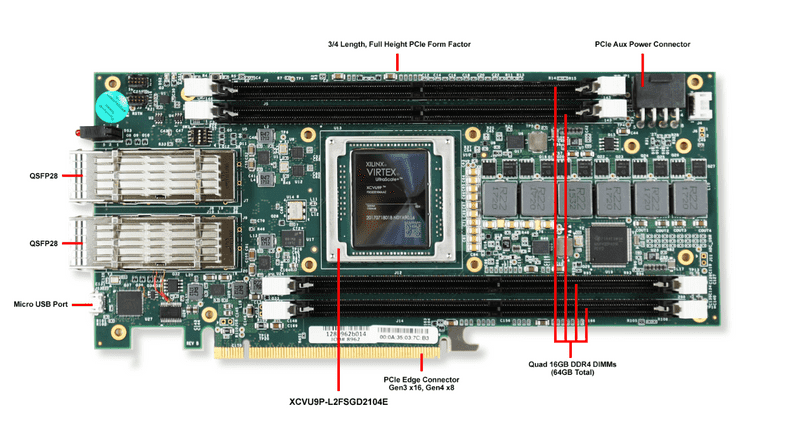

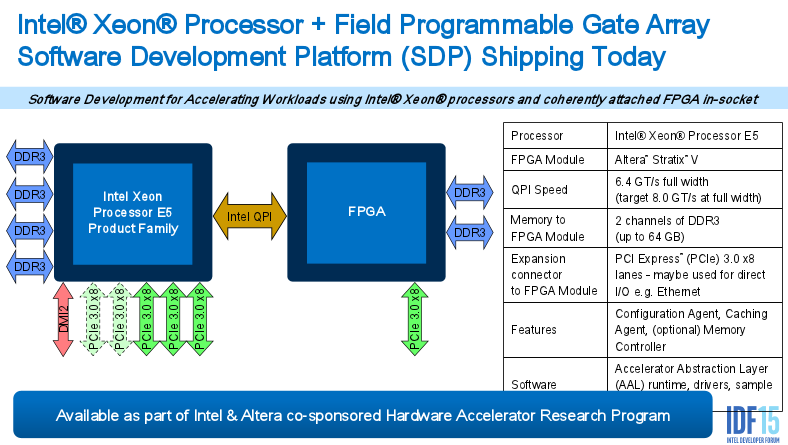

Плата Intel Stratix 10 FPGA:

Если вам нужна компактная, мощная FPGA для различных инженерных приложений в различных отраслях промышленности, это ваша плата. Платы FPGA полезны во многих различных приложениях, включая разработку встроенных систем и обработку видео.

Платы FPGA полезны во многих различных приложениях, включая разработку встроенных систем и обработку видео.

Плата Intel Stratix Ge FPGA:

Эта плата специально разработана для аэрокосмической промышленности, тогда как плата Stratix 10 FPGA является более универсальной FPGA. Плата Ge FPGA имеет немного большую вычислительную производительность и пропускную способность, чем плата Stratix 10 FPGA. Эта плата может работать с широким спектром приложений. Доска также подходит для профессиональных дизайнерских проектов.

Плата Stratix 10 GX FPGA:

Плата Ge FPGA полностью совместима с платой Stratix 10 FPGA, обладает дополнительными функциями и более высокой вычислительной производительностью. Эти доски необходимы в проектах коммерческого дизайна, особенно тех, которые связаны с промышленным дизайном или потребительскими товарами.

Запросить предложение Intel Altera FPGA

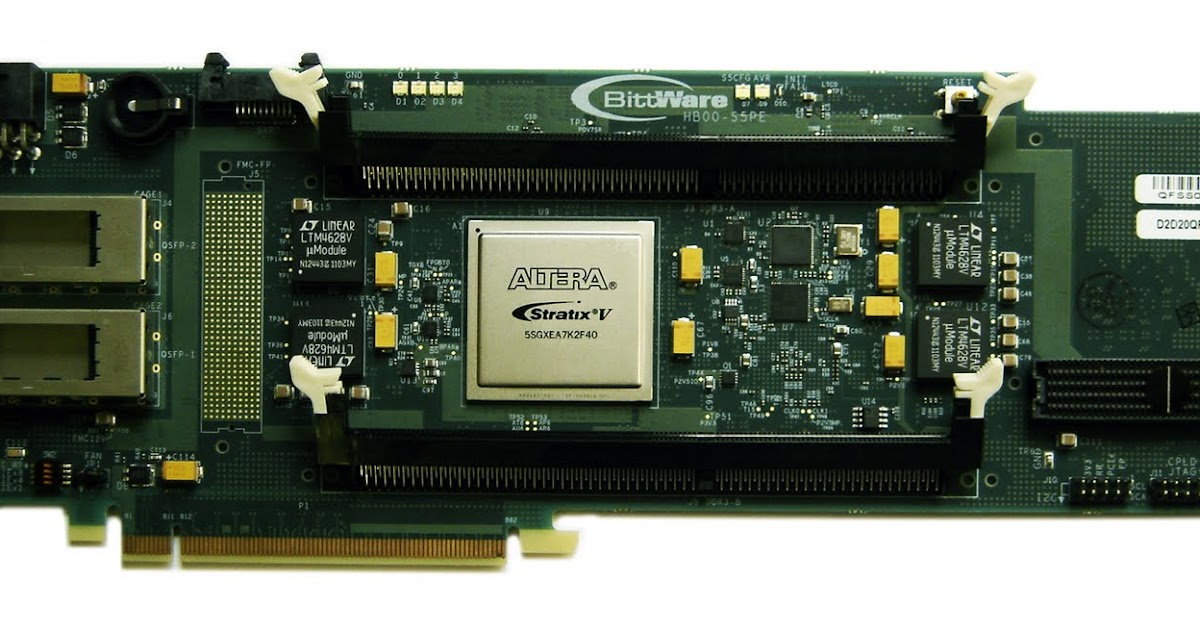

Платы Stratix V FPGA:

Это линейка плат FPGA на основе серии Stratix. Плата предлагает высокопроизводительные и расширенные функции, такие как высокоскоростные приемопередатчики и расширенные возможности подключения. Он также имеет более низкое энергопотребление, чем предыдущие 9Платы 0003

Плата предлагает высокопроизводительные и расширенные функции, такие как высокоскоростные приемопередатчики и расширенные возможности подключения. Он также имеет более низкое энергопотребление, чем предыдущие 9Платы 0003

FPGA, которые были доступны от Altera. Это может быть полезно в определенных приложениях, таких как устройства с батарейным питанием. Тем не менее, его дизайн также важен для промышленного дизайна и инженерных приложений.

Плата Stratix 7 FPGA:

Это плата FPGA последнего поколения, основанная на серии Stratix. Плата Stratix 7 FPGA совместима с предыдущими моделями (6, 6 E, 6 GX) и обладает эксклюзивными функциями. Как и его предшественники, он предлагает высокую производительность и быстрые вычислительные возможности. Как и другие платы Altera, она поставляется с отличной программной поддержкой. В результате мы можем использовать плату как в промышленных проектах, так и в проектах встроенного дизайна.

Плата Arria 10 FPGA:

Если вы ищете многофункциональную высокопроизводительную плату FPGA и вас не волнует цена, обратите внимание на эту плату FPGA. Таким образом, он предлагает отличные характеристики по конкурентоспособной цене. Плата Arria 10 FPGA подходит для использования в проектах промышленного и коммерческого дизайна.

Таким образом, он предлагает отличные характеристики по конкурентоспособной цене. Плата Arria 10 FPGA подходит для использования в проектах промышленного и коммерческого дизайна.

Платы Cyclone III FPGA:

Эти платы в первую очередь предназначены для клиентов, которым нужна высокопроизводительная FPGA с высокой тактовой частотой и большим количеством контактов ввода/вывода. Мы можем использовать доски как в коммерческих, так и в промышленных дизайнерских проектах. Дизайн серии Cyclone III поможет удовлетворить потребности опытных пользователей.

Платы Max V CPLD:

Серия Altera Max V представляет собой линейку программируемых логических устройств, используемых в различных аппаратных решениях. Обычно они используются в качестве встроенных микроконтроллеров или для аппаратного ускорения. Платы Cyclone V серии

FPGA также имеют широкий спектр применений, особенно в секторах промышленного дизайна и встраиваемых систем.

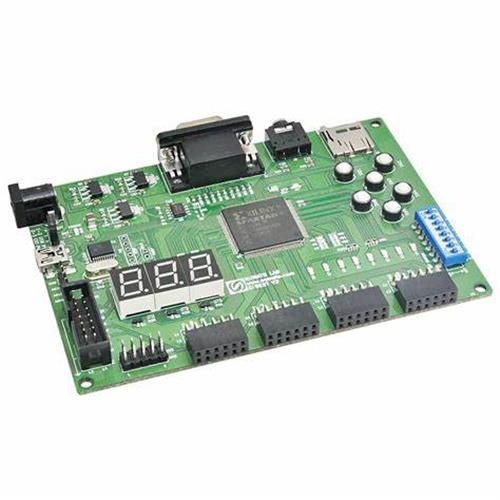

Отладочные платы FPGA:

Дизайн этих плат помогает продвигать и поддерживать разработку приложений на FPGA. Они включают программное обеспечение Cypress FX2 и Altera Quartus II для оборудования Xilinx и Altera. Это позволяет вам взаимодействовать с FPGA на вашем компьютере и очень быстро проектировать и создавать сложные системы.

Stratix 10 SBC:

Это мощный и компактный одноплатный компьютер для проектирования FPGA. Мы можем использовать его как удобную платформу разработки для отладки оборудования и создания прототипов. Он также поддерживает программное обеспечение Altera Quartus II, которое очень полезно для разработки программного обеспечения на ПЛИС.

В чем разница между Xilinx и Altera?

Основное отличие заключается в том, что конструкция плат FPGA серии Xilinx предназначена в основном для разработки приложений. Платы FPGA серии Altera необходимы для промышленного дизайна и встроенных приложений. Поскольку серия Xilinx более популярна, многие замечательные инструменты поддерживают устройства Xilinx. Однако между двумя брендами FPGA есть различия.

Поскольку серия Xilinx более популярна, многие замечательные инструменты поддерживают устройства Xilinx. Однако между двумя брендами FPGA есть различия.

Традиционным способом передачи блока IP между устройствами является собственный протокол связи Altera, известный как межсоединение на уровне протокола (PLI). PLI Altera предлагает прямой и эффективный метод связи между IP-блоками. Платы FPGA серии Xilinx используют интерфейс IEEE 1394, открытый стандартный протокол, поддерживаемый всеми устройствами FPGA.

Еще одно существенное отличие состоит в том, что платы FPGA серии Xilinx имеют бесплатный комплект для разработки программного обеспечения (SDK). Кроме того, это инструменты проектирования программируемой логики, такие как Altium Designer и Quartus II. Платы FPGA серии Altera не поставляются с этими дополнительными программами.

Общие характеристики плат FPGA серии Intel (Altera)

Корпорация Intel, производитель оригинального дизайна (ODM), производит платы Intel FPGA. Корпорация Intel разрабатывает, производит и продает компьютерное оборудование и программные компоненты.

Корпорация Intel разрабатывает, производит и продает компьютерное оборудование и программные компоненты.

1. Триггеры

Это небольшие блоки логики, которые мы используем для изменения состояния сигнала. Триггеры полезны в цифровых схемах для хранения битов данных. Конструкция триггера очень распространена для плат FPGA. На каждом фронте тактового сигнала система копирует входное значение в выходное значение. Мы синхронизируем входное значение с триггером на отрицательном фронте часов. Есть два типа триггеров, а именно:

а. D-триггер: D-триггер копирует данные, присутствующие на его входах D, на его выходы Q при каждом положительном фронте тактового сигнала.

г = с

б. Т-триггер: Т-триггер копирует данные, присутствующие на положительных фронтах тактового сигнала, на свои выходы Q. Это означает, что система обновляет вывод только при каждом положительном фронте тактового сигнала. В результате триггеры T-типа работают медленнее, чем триггеры D-типа.

в. B-триггер: B-триггер копирует данные, присутствующие на его выходах Q, на входы D при каждом отрицательном фронте тактового сигнала.

d = c

2. Задержка

Термин задержка означает время, которое требуется сигналу для достижения своего конечного значения. Задержка отражает скорость платы FPGA. Если задержка слишком велика, вы столкнетесь с низкой производительностью вашего приложения. Мы определяем задержку по размеру блока FPGA, тактовой частоте FPGA и количеству триггеров, необходимых для каждого входного или выходного сигнала. Система делит вход CLK на несколько субтактов с разными частотами. Один из самых длинных делителей тактовой частоты определяет задержку. Самые быстрые платы FPGA имеют более высокую задержку. Задержка является важным параметром платы FPGA для обеспечения высокой скорости передачи сигнала.

Серия Altera имеет много улучшений по сравнению с серией Xilinx. Таким образом, серия Altera лучше, чем серия Xilinx, для приложений, требующих высокой производительности и гибкости. Кроме того, интерфейс от одного блока к другому осуществляется через его передовые проприетарные протоколы, известные как межсоединение на уровне протокола (PLI).

Кроме того, интерфейс от одного блока к другому осуществляется через его передовые проприетарные протоколы, известные как межсоединение на уровне протокола (PLI).

3. Умножители и слайсы DSP

Умножители и слайсы DSP представлены в виде предварительно запрограммированных аппаратных блоков. Мы можем выполнить операцию multi-1 над входным блоком. Он выполняет последовательность логических операций, а затем копирует результат обратно на выход. В результате он синхронизирует выход с соседним триггером. Это приводит к фиксированной задержке между подачей данных в блок и его тактированием. Задержки между блоками вызывают задержку в вашем приложении.

4. Память

Память поставляется в виде флэш-памяти, SRAM и EEPROM. Флэш-память является энергозависимой памятью. Мы можем использовать его для сохранения ваших настроек конфигурации во время загрузки. SRAM — энергонезависимая память. В SRAM содержимое данных сохраняется даже при отключении питания от платы FPGA. EEPROM содержит постоянную память, которая может хранить информацию в энергонезависимом режиме при включении питания.

EEPROM содержит постоянную память, которая может хранить информацию в энергонезависимом режиме при включении питания.

5. Часы

Генератор тактовых сигналов генерирует все сигналы, необходимые для управления ПЛИС. Плата FPGA имеет до 72 тактовых сигналов. T=Можно распределить эти 72 тактовых сигнала по плате, используя 4-битную шину. Разные платы FPGA имеют разное количество тактовых сигналов. Количество тактовых сигналов прямо пропорционально размеру блока FPGA, присутствующего на плате. Это связано с тем, что более крупные блоки FPGA требуют большей вычислительной мощности и, следовательно, используют больше каналов тактового сигнала.

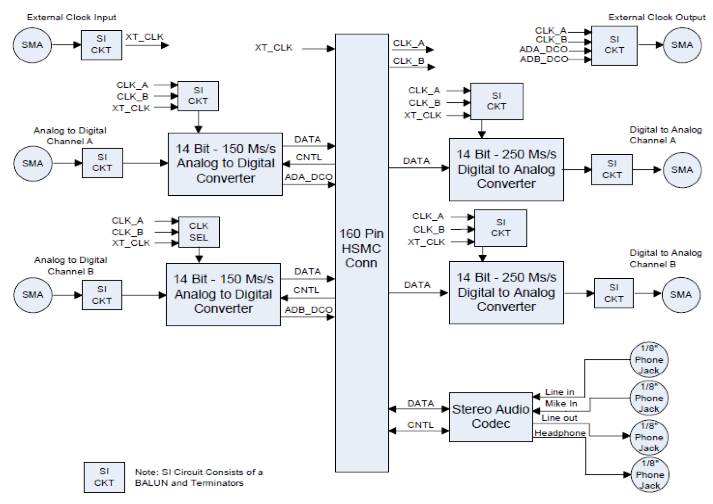

6. АЦП и ЦАП

АЦП (аналогово-цифровой преобразователь) — это устройство, которое может преобразовывать уровни напряжения в цифровые данные. ЦАП (цифро-аналоговый преобразователь) работает в обратном направлении. Таким образом, он преобразует цифровые данные в аналоговые сигналы и выполняет преобразование напряжения. Например, если на плате FPGA используется АЦП, вы можете подключить его к датчику давления и контролировать его.

Например, если на плате FPGA используется АЦП, вы можете подключить его к датчику давления и контролировать его.

7. DMA

Плата FPGA имеет встроенную память, которая называется DMA (прямой доступ к памяти). Возможности этой встроенной памяти позволяют плате передавать блоки данных непосредственно между внутренними регистрами и некоторыми внутренними контактами ввода/вывода. Это полезно, когда вы хотите управлять платой FPGA, записывая шаблоны байтов в ее встроенную память вместо записи целых чисел битов в ее регистр.

8. Флэш-память

Платы ПЛИС содержат флэш-память. Флэш-память является энергонезависимой, как EEPROM (электрически стираемая программируемая постоянная память). Однако процесс считывания выполняется быстрее, чем в EEPROM. Мы используем его для хранения файла конфигурации FPGA. Этот файл содержит всю информацию, необходимую ПЛИС для выполнения вашего проекта. Количество интерфейсов SPI (последовательный периферийный интерфейс) варьируется в зависимости от платы FPGA.

Запрос Intel Altera FPGA Цитата

Проектирование FPGA в систему Плата разработки altera fpga

1. Определите системные требования

Первым шагом является определение требований вашего приложения. Вам нужно будет перечислить функции вашего приложения, требуемые возможности платы FPGA и любые ограничения, которые могут возникнуть в отношении хранения или доступности питания. Напишите список функциональных блоков для каждого проектного требования. Но убедитесь, что вы включили любые дополнительные требования, которые могут возникнуть позже в процессе проектирования.

2. Архитектура системы

Разработайте архитектуру вашей системы на основе функциональных блоков, перечисленных в вашем документе требований к приложению (ARD). Используйте языки описания оборудования для создания блок-схемы. Таким образом, эта блок-схема по сути является основой всей работы по проектированию ПЛИС. Затем мы будем использовать его для программирования платы FPGA, которую вы выберете для своей системы.