Учебный курс AVR. Использования TWI модуля. Основы I2C. Ч1

В составе некоторых микроконтроллеров AVR есть модуль двухпроводного последовательного интерфейса (Two -wire Serial Interface или TWI). Модуль предназначен для организации обмена данными между микросхемами, подключенными к двухпроводной шине. Основное преимущество этого интерфейса перед SPI и UART`ом — это возможность организации сети из нескольких устройств.

Двухпроводный интерфейс является аналогом I2C интерфейса фирмы Philips, только в случае AVR, не поддерживает высокие скорости передачи данных (свыше 400 kbit/s). Соображения, по которым Atmel использует другое названия, видимо связано с нежеланием платить Philips за лицензию.

В этом материале мы разберемся с основами двухпроводного последовательного интерфейса, а в следующих перейдем к работе с TWI модулем AVR.

Далее я буду опираться на даташит atmega16 и спецификацию I2C.

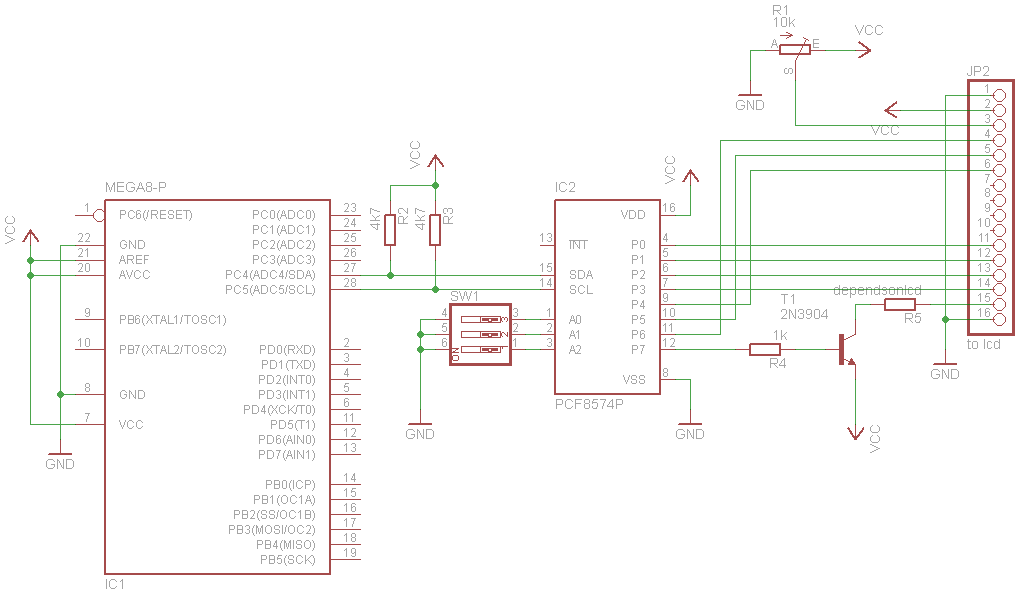

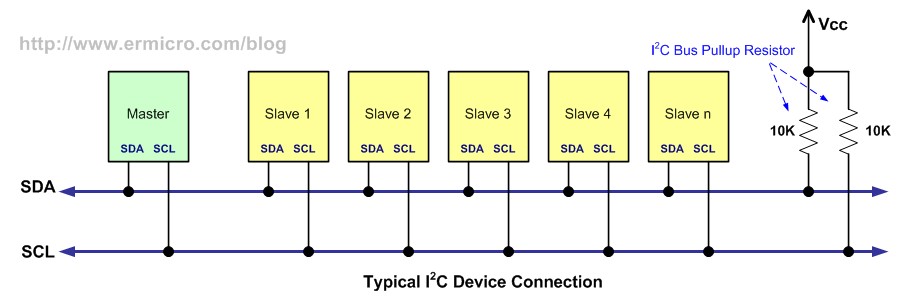

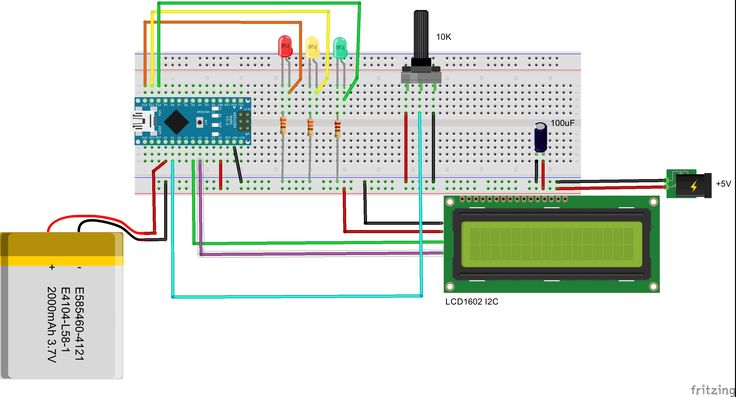

I2C шина представляет собой две двунаправленные линии связи — SDA (Serial Data Line) и SCL (Serial Clock Line). По SDA передаются данные, по SCL тактовый сигнал. Обе линии подтянуты через резисторы к плюсу питания.

По SDA передаются данные, по SCL тактовый сигнал. Обе линии подтянуты через резисторы к плюсу питания.

Устройства на шине подразделяются на ведущих (master) и ведомых (slave). Ведущие запускают и завершают передачу данных, ведомые — отвечают на запросы. Одни — начальники, другие — подчиненные. Микроконтроллеры могут совмещать в себе обе эти функции.

Выходные каскады устройств, поддерживающих I2C, выполнены как структуры с открытым коллектором/стоком. При подключении к шине, они образуют схему монтажного «И». Это значит, что любое устройство, установившее низкий логический уровень на линии шины, «проваливает» высокий уровень остальных устройств.

На шине может быть несколько ведущих устройств, но в любой момент времени, обмен данными может производить только один из них. Остальные ведущие в это время молчат в тряпочку и слушают шину.

Существует механизм распределения приоритетов между ведущими, если они начинают передачу данных одновременно. Он заключается в том, что ведущие устанавливают на шине данные и проверяют результат. Если он отличается от ожидаемого, устройство теряет приоритет и останавливает передачу данных.

Он заключается в том, что ведущие устанавливают на шине данные и проверяют результат. Если он отличается от ожидаемого, устройство теряет приоритет и останавливает передачу данных.

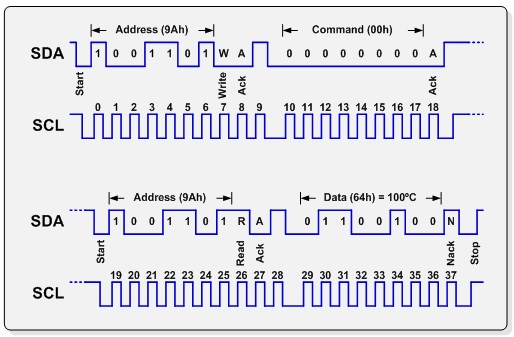

Данные передаются поразрядно (спасибо кэп!), старшим разрядом вперед. Каждый разряд сопровождается тактовым сигналом.

Начало и окончание передачи данных сопровождается специальными состояниями шины — СТАРТ и СТОП. Эти состояния формирует ведущее устройство. Также ведущий может сформировать состояние повторного старта до формирования состояния СТОП.

Данные передаются по I2C шине со служебной информацией. Все вместе это называется пакетом. Существуют адресные пакеты и пакеты данных. Адресные пакеты состоят из 7-и разрядного адреса, управляющего бита R/W и бита квитирования (весь пакет — 9 бит). Адресный пакет нужен, чтобы обратиться к конкретному устройству.

R/W — определяет последующее направление передачи данных. Бит квитирования — это ответ ведомого устройства на принятый адрес. Если адрес распознан, ведомый выдает на линию SDA низкий уровень. В противном случае на линии удерживается высокий уровень.

Если адрес распознан, ведомый выдает на линию SDA низкий уровень. В противном случае на линии удерживается высокий уровень.

Под адрес отведено 7 разрядов, что как бы намекает на возможность адресации 128 устройств, но это не совсем так. Во-первых существует ряд служебных адресов, например, 0000000 — это адрес общего вызова (обращение ко всем ведомым устройствам). Во-вторых есть режим 10-и разрядной адресации, когда адрес передается двумя пакетами. Не буду углубляться в эту тему, только скажу, что адреса из диапазона 1111000…1111111 не рекомендуется использовать в TWI модуле AVR (курим даташит).

Пакеты данных состоят из байта данных и бита квитирования, то есть тоже имеют длину 9 бит. После приема каждого байта данных, принимающее устройство (приемник) отвечает передающему устройству (передатчику), устанавливая на линии SDА низкий уровень (это и есть бит квитирования). Если принимающее устройство получило последний байт или больше не может продолжать прием данных, оно должно «оставить» на линии SDA высокий уровень.

В общем случае, полный цикл обмена по I2C состоит из следующих шагов:

— формирование состояния СТАРТ,

— передача адресного пакета,

— передача пакетов данных,

— прием пакетов данных,

— формирование состояния СТОП.

На этом все. Продолжение следует..

17. Микроконтроллеры avr. Интерфейс twi.

Интерфейс последовательной связи I2C (I2C, TWSI)

МК AVR m163.

Характеристики:

1) двухпроводной

2) работа с адресуемыми устройствами (до 128)

3) 8-ми битовый обмен в любом направлении

4) имеет средства контроля передачи адреса и данных в виде подтверждения сигнала

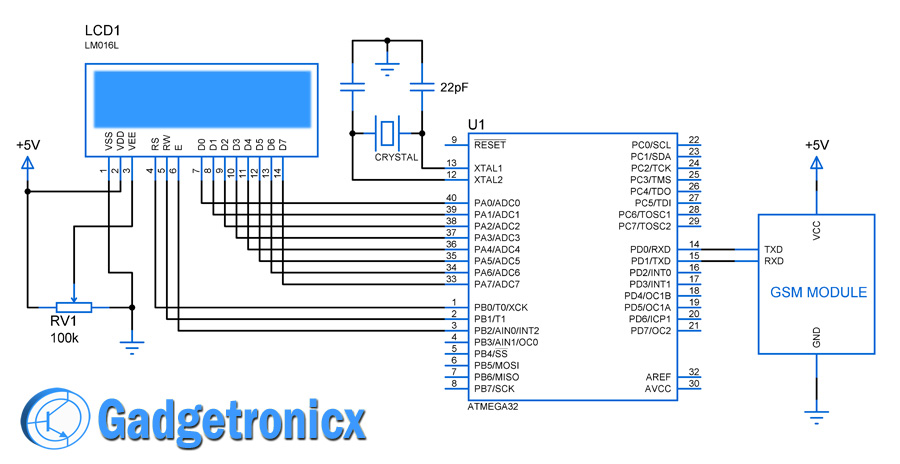

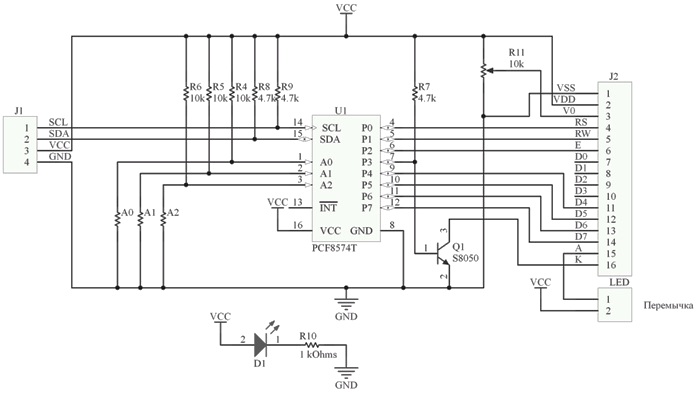

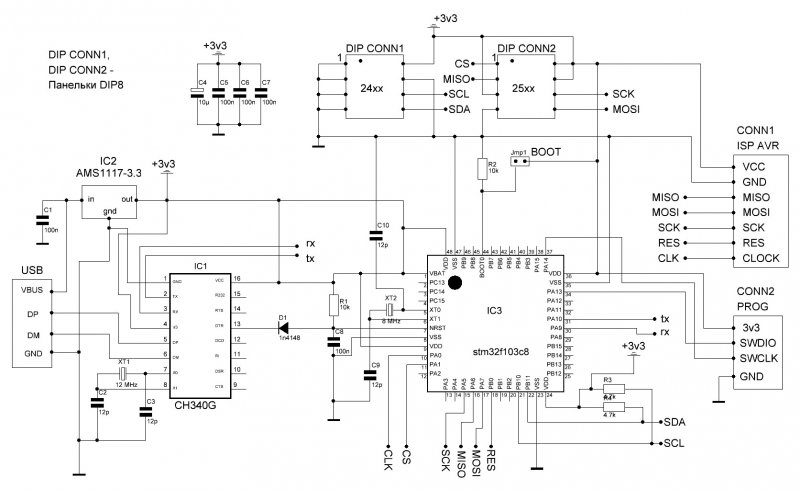

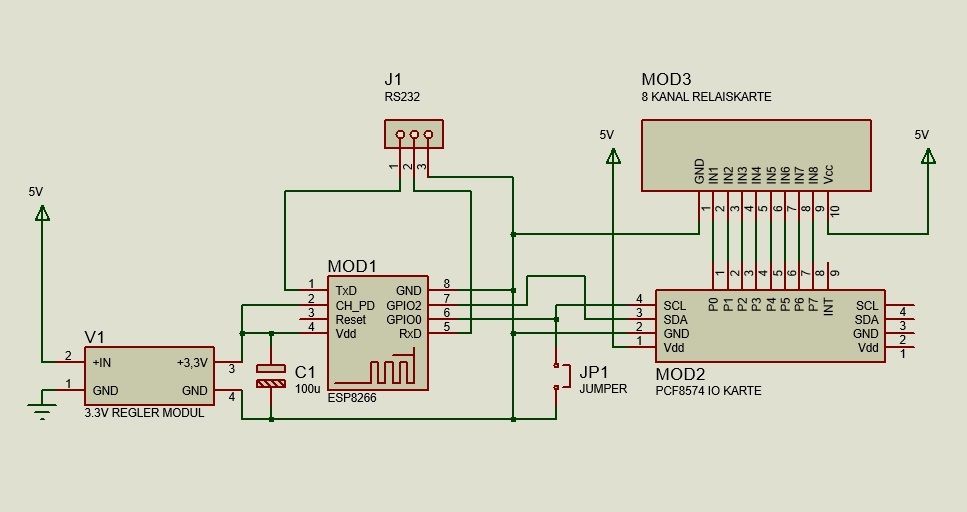

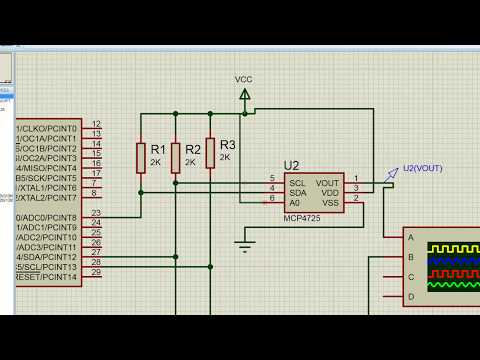

Схемотехника I2C:

Протокол обмена по I2C:

— от ведущего выводится стартовая посылка ST (начало обмена)

— от ведущего выводится стартовый байт (7 бит.)

— от ведущего выводится бит направления обмена (1 бит) (запись от ведущего к ведомому и чтение от ведомого к ведущему)

— от ведомого поступает бит подтверждения

— от ведущего поступает байт (байты) данных

— от ведомого поступает бит подтверждения после каждого байта

— ведущий формирует стоповую посылку (завершение обмена)

Временные диаграммы работы I2C:

АСК – сигнал подтверждения

* — варианты возможного продолжения работы:

1) Передача данных в том же направлении

2) Выбор

другого ведомого или изменение

направления передачи данных, либо

делается и то и другое. Для этого

формируется ST (стартовая посылка) еще

раз.

Для этого

формируется ST (стартовая посылка) еще

раз.

3) Окончание обмена (SP стоповая посылка), освобождающая шину.

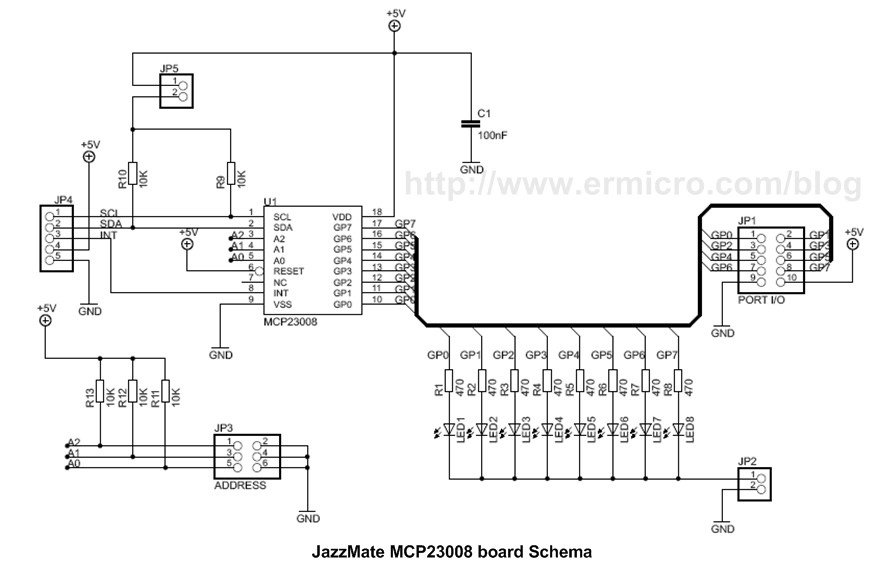

Технические средства I2C в составе МК (на примере AVR):

TWDR – регистр данных, TWAR – регистр адреса, TWBR – регистр скорости, TWCR – регистр управления, TWSR – регистр статуса

Средняя скорость (бит/с) . Для AVR m163 = 8МГц, = (200-600) нс.

Состояния TWSR:

— ведущий с передачей данных — ведущий с приемом данных — ведомый с приемом данных — ведомый с передачей данных + условие перехода к следующим словам данных в виде битов TWSR.

Аналоговый компаратор (на примере ATmega128)

Аналоговый компаратор сравнивает

уровни напряжений на неинвертирующем

входе AIN0 и инвертирующем входе AIN1. Если

напряжение на неинвертирующем входе

AIN0 превышает напряжение на инвертирующем

входе AIN1, то выход аналогового компаратора

ACO принимает единичное состояние. Выход

компаратора может быть настроен для

использования в качестве источника

входного сигнала для схемы захвата

фронтов таймера-счетчика 1.

Включение АК осуществляется установкой

бита ADEN регистра ADCSRA. Кроме того, если

бит ACME регистра SFIOR установлен (и ADEN=0),

то к инвертирующему входу аналогового

компаратора подключается выход

аналогового мультиплексора АЦП. Сброс

данного бита приведет к подключению

инвертирующего входа аналогового

компаратора к выводу микроконтроллера

AIN1. Для управления АК используется

регистр ACSR (регистр состояния и управления

аналогового компаратора). Его разряды:

7 – ACD: Отключение АК; 6 – ACBG: Подключение

источника опорного напряжения к

аналоговому компаратору; 5 – ACO: Выход

аналогового компаратора; 4 – ACI: Флаг

прерывания аналогового компаратора;

3 – ACIE: Разрешение прерывания аналогового

компаратора; 2 – ACIC: Подключение

аналогового компаратора к схеме захвата

фронтов; 1, 0 – ACIS1, ACIS0: Выбор события

прерывания аналогового компаратора.

Имеется возможность использовать выводы ADC7..0 в качестве неинвертирующих входов аналогового компаратора. Для организации такого ввода используется мультиплексор АЦП и, следовательно, в этом случае АЦП должен быть отключен. Если установлен бит разрешения подключения мультиплексора к аналоговому компаратору (бит ACME в SFIOR) и выключен АЦП (ADEN=0 в регистре ADCSRA), то состояние разрядов MUX2..0 регистра ADMUX определяют какой вывод микроконтроллера подключен к неинвертирующему входу аналогового компаратора. Если ACME сброшен или установлен ADEN, то в качестве неинвертирующего входа аналогового компаратора используется вывод микроконтроллера AIN1.

Аналого-цифровой преобразователь (на примере ATmega128)

ATmega128

содержит 10-разр. АЦП последовательного

приближения. АЦП связан с 8-канальным

аналоговым мультиплексором, 8 однополярных

входов которого связаны с линиями порта

F. Общий входных сигналов должен иметь

потенциал 0В (т. е. связан с GND). АЦП также

поддерживает ввод 16 дифференциальных

напряжений. Два дифференциальных входа

(ADC1, ADC0 и ADC3, ADC2) содержат каскад со

ступенчатым программируемым усилением:

0 дБ (1x), 20 дБ (10x), или 46 дБ (200x). Семь

дифференциальных аналоговых каналов

используют общий инвертирующий вход

(ADC1), а все остальные входы АЦП выполняют

функцию неинвертирующих входов. Если

выбрано усиление 1x или 10x, то можно

ожидать 8-разр. разрешение, а если 200x,

то 7-разрядное. АЦП содержит УВХ

(устройство выборки-хранения), которое

поддерживает на постоянном уровне

напряжение на входе АЦП во время

преобразования. АЦП имеет отдельный

вывод питания AVCC (аналоговое питание).

AVCC не должен отличаться более чем на ±

0.3В от VCC.

е. связан с GND). АЦП также

поддерживает ввод 16 дифференциальных

напряжений. Два дифференциальных входа

(ADC1, ADC0 и ADC3, ADC2) содержат каскад со

ступенчатым программируемым усилением:

0 дБ (1x), 20 дБ (10x), или 46 дБ (200x). Семь

дифференциальных аналоговых каналов

используют общий инвертирующий вход

(ADC1), а все остальные входы АЦП выполняют

функцию неинвертирующих входов. Если

выбрано усиление 1x или 10x, то можно

ожидать 8-разр. разрешение, а если 200x,

то 7-разрядное. АЦП содержит УВХ

(устройство выборки-хранения), которое

поддерживает на постоянном уровне

напряжение на входе АЦП во время

преобразования. АЦП имеет отдельный

вывод питания AVCC (аналоговое питание).

AVCC не должен отличаться более чем на ±

0.3В от VCC.

В

качестве внутреннего опорного напряжения

может выступать напряжение от внутреннего

ИОНа на 2.56В или напряжение AVCC. Если

требуется использование внешнего ИОН,

то он должен быть подключен к выводу

AREF с подключением к этому выводу

блокировочного конденсатора для

улучшения шумовых характеристик.

АЦП преобразовывает входное аналоговое напряжение в 10-разр. код методом последовательных приближений. Минимальное значение соответствует уровню GND, а максимальное уровню AREF минус 1 мл. разр.

Канал аналогового ввода и каскад дифференциального усиления выбираются путем записи бит MUX в регистр ADMUX. В качестве однополярного аналогового входа АЦП может быть выбран один из входов ADC0…ADC7, а также GND и выход фиксированного источника опорного напряжения 1,22 В. В режиме дифференциального ввода предусмотрена возможность выбора инвертирующих и неинвертирующих входов к дифференциальному усилителю.

Если выбран дифференциальный режим аналогового ввода, то дифференциальный усилитель будет усиливать разность напряжений между выбранной парой входов на заданный коэффициент усиления. Усиленное таким образом значение поступает на аналоговый вход АЦП. Если выбирается однополярный режим аналогового ввода, то каскад усиления пропускается

Работа

АЦП разрешается путем установки бита

ADEN в ADCSRA. Выбор опорного источника и

канала преобразования не возможно

выполнить до установки ADEN. Если ADEN = 0,

то АЦП не потребляет ток, поэтому, при

переводе в экономичные режимы сна

рекомендуется предварительно отключить

АЦП.

Выбор опорного источника и

канала преобразования не возможно

выполнить до установки ADEN. Если ADEN = 0,

то АЦП не потребляет ток, поэтому, при

переводе в экономичные режимы сна

рекомендуется предварительно отключить

АЦП.

АЦП генерирует 10-разрядный результат, который помещается в пару регистров данных АЦП ADCH и ADCL.

АЦП генерирует собственный запрос на прерывание по завершении преобразования. Если между чтением регистров ADCH и ADCL запрещен доступ к данным для АЦП, то прерывание возникнет, даже если результат преобразования будет потерян.

Одиночное

преобразование запускается путем

записи лог. 1 в бит запуска преобразования

АЦП ADSC. Данный бит остается в высоком

состоянии в процессе преобразования

и сбрасывается по завершении

преобразования. Если в процессе

преобразования переключается канал

аналогового ввода, то АЦП автоматически

завершит текущее преобразование прежде,

чем переключит канал.

В режиме автоматического перезапуска АЦП непрерывно оцифровывает аналоговый сигнал и обновляет регистр данных АЦП. Данный режим задается путем записи лог. 1 в бит ADFR регистра ADCSRA. Первое преобразование инициируется путем записи лог. 1 в бит ADSC регистра ADCSRA. В данном режиме АЦП выполняет последовательные преобразования, независимо от того сбрасывается флаг прерывания АЦП ADIF или нет.

Регистр SFIOR

ADTS2 |

ADTS1 |

ADTS0 |

— |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

0 |

0 | 0 |

ADTS2:ADTS0=000 — режим непрерывного преобразования

Регистр ADMUX

REFS1 |

REFS0 |

ADLAR |

MUX4 |

MUX3 |

MUX2 |

MUX1 |

MUX0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

REFS1:REFS0=01 — источник опорного напряжения — напряжение питания AVсс

ADLAR=1 — выравнивание по левой границе 16-битного слова

MUX4:MUX0=00100 — входной канал — несимметричный вход ADC4

Регистр ADCSRA

ADEN |

ADSC |

ADATE |

ADIF |

ADIE |

ADPS2 |

ADPS1 |

ADPS0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

ADEN=1 — разрешение АЦП

ADSC=1 — запуск преобразования

ADATE=1 — режим непрерывного преобразования

ADIF=0 — флаг прерывания от компаратора

ADIE=1 – прерывание от компаратора разрешено

ADPS2:ADPS0=110 — коэффициент деления предделителя 64 (частота выборок 131072 Гц)

При завершении каждого цикла преобразования

АЦП инициируется прерывание, обработчик

которого читает значения регистров

результата ADCH и ADCL и записывает их в

соответствующие регистры общего

назначения (radch и radcl). Поскольку сдвиг

10-битного результата осуществляется

влево, и в рамках данной лабораторной

работы достаточно 8-битной точности,

то вывод на дисплей осуществляется

только из регистра radch. Причём старшие

4 бита этого регистра выводятся в

основном цикле работы программы на

первый слева индикатор (в PORTB передаём

00000001), а младшие 4 бита — на второй слева

(в PORTB — 00000010).

Поскольку сдвиг

10-битного результата осуществляется

влево, и в рамках данной лабораторной

работы достаточно 8-битной точности,

то вывод на дисплей осуществляется

только из регистра radch. Причём старшие

4 бита этого регистра выводятся в

основном цикле работы программы на

первый слева индикатор (в PORTB передаём

00000001), а младшие 4 бита — на второй слева

(в PORTB — 00000010).

Помимо прочего в программе организуется задержка (цикл TIME), необходимая для возможности корректного восприятия данных с индикатора.

Инструменты I2C, SPI, USB для разработчиков AVR

Total Phase предлагает гибкие, мощные и доступные инструменты I2C, SPI и USB, которые идеально подходят для разработчиков AVR. Используя эти инструменты и бесплатный API, предлагаемый Total Phase, разработчики AVR могут свободно создавать собственные утилиты, графические пользовательские интерфейсы и многое другое. Кроссплатформенная поддержка обеспечивает гибкость разработки на платформах Windows, Linux или Mac OS X. Независимо от того, разрабатываете ли вы творческие проекты в свободное время или создаете мощные устройства на работе, разработчики AVR могут положиться на инструменты отладки Total Phase, которые обеспечивают идеальное сочетание гибкости, низкой стоимости и мощности.

Независимо от того, разрабатываете ли вы творческие проекты в свободное время или создаете мощные устройства на работе, разработчики AVR могут положиться на инструменты отладки Total Phase, которые обеспечивают идеальное сочетание гибкости, низкой стоимости и мощности.

- Последовательные шины на AVR и AVR32

- USB на AVR и AVR32

- Дополнительные функции и преимущества

Последовательные шины на AVR и AVR32

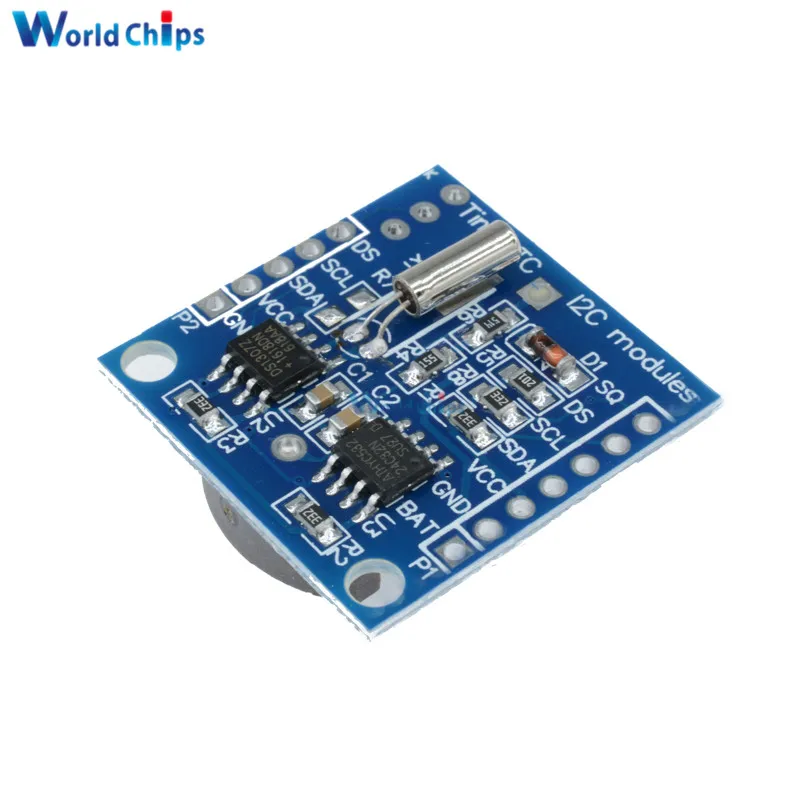

Все микроконтроллеры AVR и AVR32 имеют несколько шин I2C (TWI) и SPI для взаимодействия с периферийными устройствами, такими как EEPROM, микросхемы флэш-памяти, датчики, АЦП/ЦАП и т. д. Total Phase предлагает широкий спектр инструментов I2C и SPI, которые могут быстро имитировать, программировать, тестировать и пассивно контролировать эти последовательные шины.

Инструменты для I2C (TWI) и SPI

Хост-адаптер Aardvark I2C/SPI

Хост-адаптер Aardvark I2C/SPI — это недорогой USB-интерфейс, который позволяет разработчикам отправлять и получать данные в качестве главного или ведомое устройство с ПК под управлением Windows, Linux или Mac OS X. Этот универсальный инструмент незаменим для отладки встроенных систем. Адаптер Aardvark можно использовать для эмуляции ведущих или ведомых устройств, внутрисистемного программирования, настройки периферийных устройств I2C или SPI, автоматических тестовых приспособлений и многого другого.

Этот универсальный инструмент незаменим для отладки встроенных систем. Адаптер Aardvark можно использовать для эмуляции ведущих или ведомых устройств, внутрисистемного программирования, настройки периферийных устройств I2C или SPI, автоматических тестовых приспособлений и многого другого.

Анализатор протокола Beagle I2C/SPI

Анализатор протокола Beagle I2C/SPI — это недорогой, ненавязчивый USB-монитор шины для I2C и SPI. Этот анализатор может отображать трафик шины I2C с частотой до 4 МГц и трафик шины SPI с частотой до 24 МГц в режиме реального времени с временным разрешением на уровне битов 20 нс. Анализатор полностью поддерживает Windows, Linux и Mac OS X и является отличным дополнением к хост-адаптерам Aardvark и Cheetah.

Хост-адаптер Cheetah SPI

Хост-адаптер Cheetah SPI — это эффективный высокоскоростной адаптер SPI через USB. Достигая скорости до 40+ МГц без пропусков, адаптер Cheetah является отличным инструментом для внутрисистемного программирования последовательной флэш-памяти, приложений потоковой передачи данных и многого другого.

USB на AVR и AVR32

AVR32 AP7

Микроконтроллер AVR32 AP7 имеет встроенный USB PHY со скоростью 480 Мбит/с, который позволяет разработчикам разрабатывать высокоскоростные встроенные хосты или устройства на базе USB.

AVR32 UC3

Микроконтроллер AVR32 UC3 обеспечивает полноскоростной порт USB (12 Мбит/с) и возможность работы в режиме On-The-Go для создания следующего поколения устройств plug-and-play.

Инструменты для USB

Анализаторы USB-протокола Beagle

USB-анализаторы Beagle обеспечивают непревзойденную видимость USB-трафика в режиме реального времени. Анализатор протокола Beagle USB 480 — это высоко-/полно-/низкоскоростной USB-анализатор с поддержкой OTG. Он может отслеживать и отображать USB-трафик со скоростью до 480 Мбит/с в режиме реального времени, включая низкоуровневые события шины, такие как OTG HNP и SRP, звуковые сигналы K и J и многое другое.

Анализатор протокола USB 12 Beagle — недорогой анализатор USB с полной/низкой скоростью, который также может отслеживать и отображать трафик USB со скоростью до 12 Мбит/с в режиме реального времени. Это один из самых доступных аппаратных USB-анализаторов на рынке.

Это один из самых доступных аппаратных USB-анализаторов на рынке.

Дополнительные функции и преимущества

- Гибкость — Простой интерфейс API дает пользователям гибкость для интеграции оборудования Total Phase в специализированные программные решения.

- Совместимость — полностью совместим с Windows, Linux и Mac OS X.

- Комплекты разработчика — Заинтересованы как в хост-адаптере, так и в анализаторе протоколов? Купите комплект разработчика I2C, комплект разработчика SPI или комплект программирования, который включает в себя несколько устройств, дополнительные кабели и тестовые платы.

- Без дополнительных затрат — Бесплатное программное обеспечение, бесплатный API, бесплатные обновления прошивки/программного обеспечения и бесплатная техническая поддержка.

Названия и логотипы Atmel, AVR, AVR32 являются товарными знаками корпорации Atmel.

Любой порт, любой контакт: Мастер TWI для Attiny, Atmega

TWI, I2C, SMBus, 2-Wire . . . это бесценный способ добраться до датчиков в проектах микроконтроллеров. Хотя существует множество примеров использования I2C и других двухпроводных протоколов на назначенных контактах чипа Atmel, как разработать мастер I2C на нестандартных контактах?

Питер Флери написал здесь замечательную мастер-библиотеку I2C. Библиотеку можно скачать здесь и адаптировать как для чипов Attiny, так и для Atmega.

Нам пришлось адаптировать эту библиотеку для использования в проекте, где мы хотели использовать Attiny и Atmega. Ниже мы шаг за шагом расскажем вам, что мы сделали, чтобы эта библиотека работала для Attiny и Atmega.

Чтобы адаптировать это к вашему проекту, выполните два шага: измените определения контактов и портов и установите тактовую частоту задержки.

Изменение контактов:

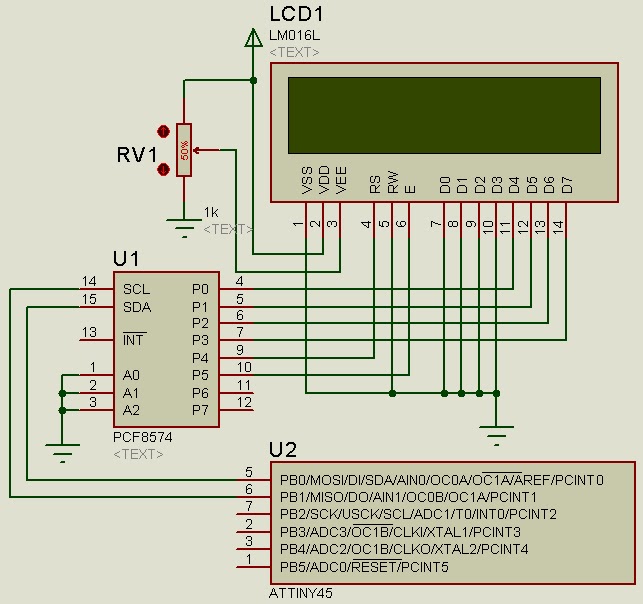

В качестве примера мы будем использовать Attiny88. Распиновка для нормального использования показана на картинке справа. SDA и SCL обычно определяются стандартными библиотеками TWI как PB2 и PB0. Для нашего проекта мы хотели переместить линии SCL и SDA на контакты PB3 и PB4.

Распиновка для нормального использования показана на картинке справа. SDA и SCL обычно определяются стандартными библиотеками TWI как PB2 и PB0. Для нашего проекта мы хотели переместить линии SCL и SDA на контакты PB3 и PB4.

Выводы выбираются в файле i2Cmaster.S, полученном из исходного кода. Откройте этот файл в текстовом редакторе или AVR Studio, и вы найдете следующее:

#Define SDA 4 // SDA Port D, PIN 4 #Define SCL 5 // SCL Port D, PIN 5 #Define SDA_PORT PORTD //SDA Port D #define SCL_PORT PORTD // SCL Port DТеперь просто переопределите выводы так, как они вам нужны. Опять же, в нашем примере мы перемещаем мастер I2C на PB3 и PB4.

#define sda 4 // #define scl 3 // #define sda_port portb // #define scl_port portb // Как вы можете увидеть булавки.

Изменение процедуры задержки:

Второй шаг — изменение процедуры задержки. Поскольку I2C является двухпроводным протоколом, ему не нужны точные часы (точные, но не точные). Однако для некоторых датчиков требуется как точность, так и точность (например, для многих датчиков SMBus требуется тактовая частота меньше или равная 100 кГц).

Файлы Fleury написаны на AVR Assembler, который не является невероятно удобным или простым в использовании языком. Мы покопались и нашли здесь некоторую информацию о задержках в AVR, по крайней мере, достаточную, чтобы помочь нам изменить задержку.

Давайте начнем с исходного кода ниже. Он предполагает кварц 4 МГц. :

;****************************************************** *************************** ;половина периода задержки ;для I2C в нормальном режиме (100 кГц) используйте T/2 > 5us ; Для I2C в быстром режиме (400 кГц) используйте T/2 > 1,3 мкс ;************************************ ********************************************* . удары «»,100 ,0,0,i2c_delay_T2 .stabs «i2cmaster.S»,100,0,0,i2c_delay_T2 .func i2c_delay_T2 ; задержка 5,0 мкс с кристаллом 4 МГц i2c_delay_T2: ; 4 цикла rjmp 1f ;2 » 1: rjmp 2f ; 2 » 2: rjmp 3f ; 2 » 3: rjmp 4f ; 2 » 4: rjmp 5f ; 2 » 5: rjmp 6f ; 2 » 6: нет ; 1 ” рет ; 3 » .endfunc ; Всего 20 циклов = 5,0 мкс с кварцем 4 МГц. В нашем примере мы используем внешние часы с частотой 16 МГц, что в 4 раза быстрее, чем исходная программа. На странице ассемблера мы видим, что функция «nop» задерживает 1 отсчет или цикл. Чтобы получить 100 кГц, Флери изначально записал 20 тактов, чтобы получить задержку в 5,0 микросекунд. В нашем примере мы просто добавим 80 отсчетов, чтобы увеличить задержку в 4 раза.

удары «»,100 ,0,0,i2c_delay_T2 .stabs «i2cmaster.S»,100,0,0,i2c_delay_T2 .func i2c_delay_T2 ; задержка 5,0 мкс с кристаллом 4 МГц i2c_delay_T2: ; 4 цикла rjmp 1f ;2 » 1: rjmp 2f ; 2 » 2: rjmp 3f ; 2 » 3: rjmp 4f ; 2 » 4: rjmp 5f ; 2 » 5: rjmp 6f ; 2 » 6: нет ; 1 ” рет ; 3 » .endfunc ; Всего 20 циклов = 5,0 мкс с кварцем 4 МГц. В нашем примере мы используем внешние часы с частотой 16 МГц, что в 4 раза быстрее, чем исходная программа. На странице ассемблера мы видим, что функция «nop» задерживает 1 отсчет или цикл. Чтобы получить 100 кГц, Флери изначально записал 20 тактов, чтобы получить задержку в 5,0 микросекунд. В нашем примере мы просто добавим 80 отсчетов, чтобы увеличить задержку в 4 раза. Мы можем сделать это с помощью «nop», и мы вставим это ниже.

Мы можем сделать это с помощью «nop», и мы вставим это ниже. ;****************************************************** ****************************

;половина периода задержки ;Для I2C в обычном режиме (100 кГц) используйте T/2 > 5 мкс ; Для I2C в быстром режиме (400 кГц) используйте T/2 > 1,3 мкс . ;****************************************************** ************************* .stabs «»,100,0,0,i2c_delay_T2 .stabs «i2cmaster.S», 100,0,0,i2c_delay_T2 .func i2c_delay_T2 ; задержка 5,0 мкс с кварцем 4 МГц i2c_delay_T2: ; 4 цикла ; nop задерживает 1 счет. ; вы должны выровнять это до тактовой частоты процессора. ; Чтобы получить 5,0 микросекунд с кристаллом 16 МГц, вам нужно ; иметь 80 задержек счета. Без этого не получится. нет ; задержки 1 счет нет; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет (5) нет; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (10) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (15) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет нет ; задержки 1 количество (20) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (25) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (30) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет нет ; задержки 1 счет nop ; задержки 1 количество (35) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (40) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (45) nop ; задержки 1 счет nop ; задержки 1 счет нет ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (50) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (55) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (60) nop ; задержки 1 счет нет ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (65) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (70) nop ; 1 нет ; 1 » нет ; 1 ” рет ; 3 » .

нет ; задержки 1 счет нет; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет (5) нет; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (10) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (15) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет нет ; задержки 1 количество (20) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (25) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (30) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет нет ; задержки 1 счет nop ; задержки 1 количество (35) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (40) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (45) nop ; задержки 1 счет nop ; задержки 1 счет нет ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (50) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (55) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (60) nop ; задержки 1 счет нет ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (65) nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 счет nop ; задержки 1 количество (70) nop ; 1 нет ; 1 » нет ; 1 ” рет ; 3 » .