Что такое интерфейс SWD. Как использовать SWD для отладки микроконтроллеров STM32. Какие адаптеры подходят для работы с SWD. Как настроить и подключить SWD-адаптер к микроконтроллеру.

Что такое интерфейс SWD и чем он отличается от JTAG

SWD (Serial Wire Debug) — это современный последовательный интерфейс для отладки микроконтроллеров, который пришел на смену классическому JTAG. Основные отличия SWD от JTAG:

- SWD использует всего 2 сигнальные линии вместо 4-5 у JTAG

- SWD обеспечивает более высокую скорость обмена данными

- SWD проще в реализации на уровне микроконтроллера

- SWD поддерживается большинством современных ARM Cortex-M микроконтроллеров

При этом функциональность SWD аналогична JTAG — он позволяет производить отладку, программирование памяти, управление выводами микроконтроллера и т.д.

Возможности отладки по SWD для микроконтроллеров STM32

Интерфейс SWD поддерживается практически всеми современными микроконтроллерами семейства STM32. С его помощью можно выполнять следующие операции:

- Пошаговое выполнение программы

- Установка точек останова

- Чтение/запись регистров и памяти микроконтроллера

- Программирование Flash-памяти

- Управление выводами микроконтроллера

- Анализ производительности работающего кода

Для работы с SWD требуется специальный программатор-отладчик, который подключается к ПК по USB и к отлаживаемой плате по интерфейсу SWD.

Популярные адаптеры SWD для работы с STM32

Существует несколько распространенных вариантов SWD-адаптеров для микроконтроллеров STM32:

ST-Link V2

Официальный программатор-отладчик от STMicroelectronics. Поддерживает интерфейсы JTAG, SWD и SWIM. Отличается высокой надежностью и совместимостью со всеми микроконтроллерами STM32.

Клоны ST-Link V2

Более дешевые аналоги официального ST-Link V2. Обычно поддерживают только SWD, без JTAG. Могут иметь ограничения по функциональности, но в целом работоспособны с большинством STM32.

Black Magic Probe

Продвинутый SWD-адаптер с открытым исходным кодом. Имеет встроенный GDB-сервер, что упрощает процесс отладки. Поддерживает широкий спектр ARM-микроконтроллеров.

J-Link

Профессиональный программатор-отладчик от SEGGER. Обеспечивает высокую скорость работы и поддерживает огромное количество микроконтроллеров. Относительно дорогой.

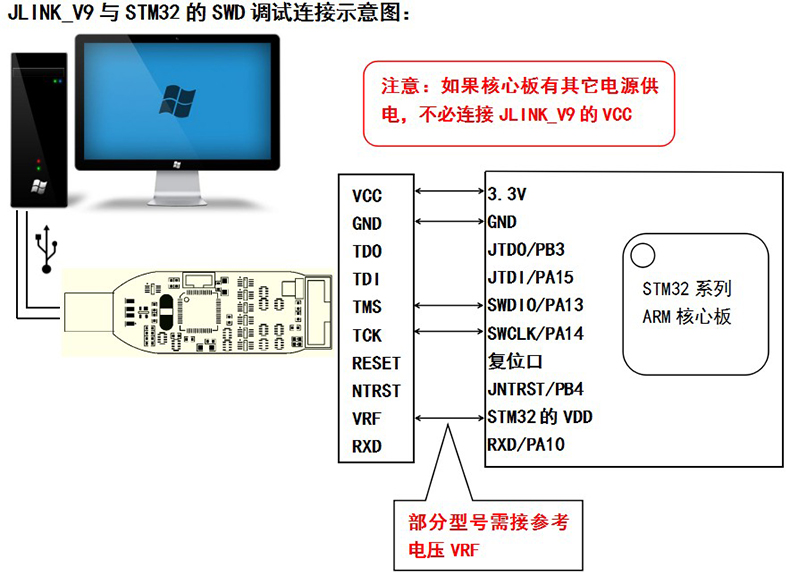

Как подключить SWD-адаптер к микроконтроллеру STM32

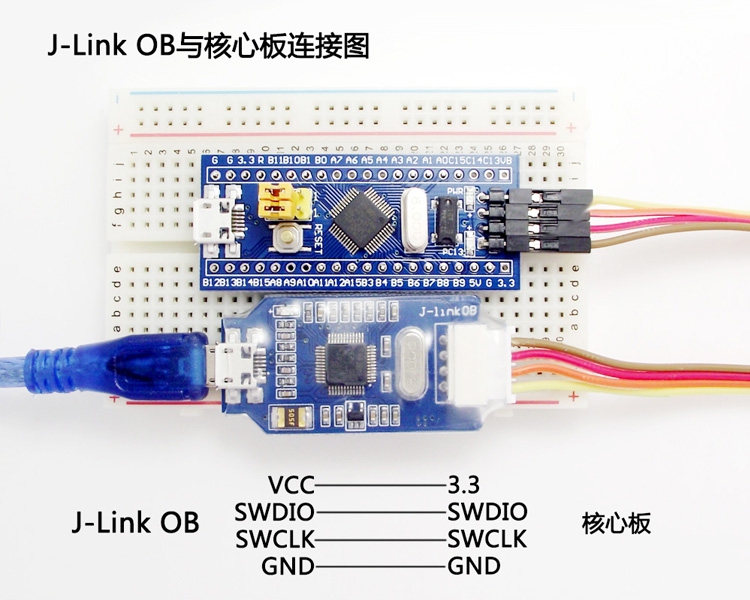

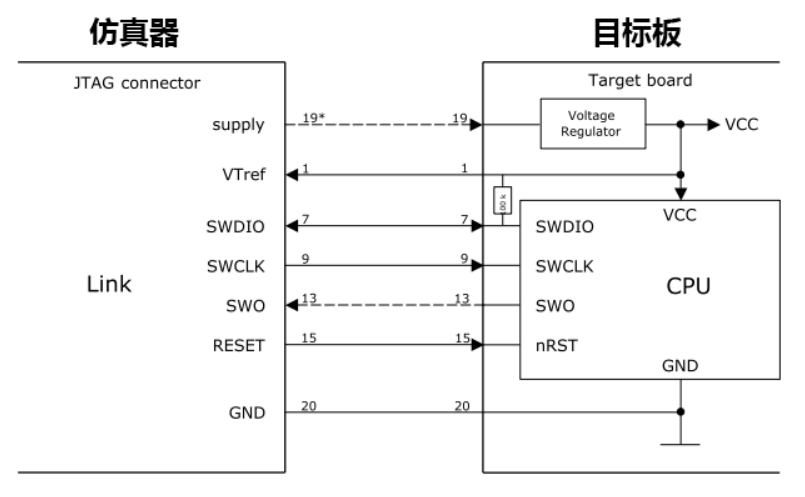

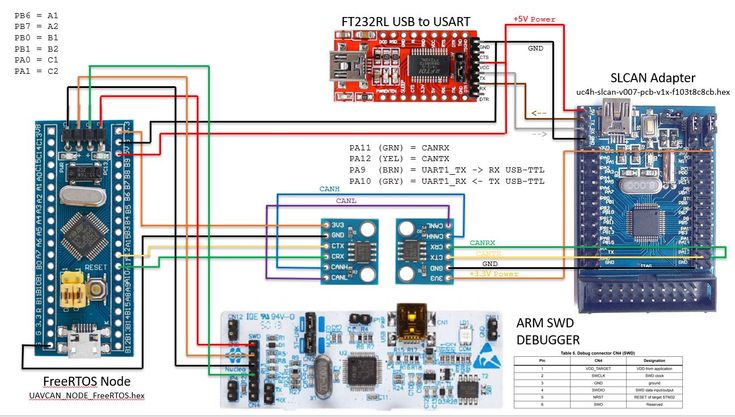

Для подключения SWD-адаптера к микроконтроллеру STM32 требуется всего 4 линии:

- SWDIO — двунаправленная линия данных

- SWCLK — тактовый сигнал

- GND — общий провод

- VCC — питание (обычно 3.3В)

Дополнительно может использоваться линия RESET для сброса микроконтроллера. Конкретное расположение выводов зависит от используемого адаптера и отлаживаемой платы.

Настройка среды разработки для отладки по SWD

Для отладки микроконтроллеров STM32 по интерфейсу SWD обычно используются следующие инструменты:

- IDE (например, STM32CubeIDE или Eclipse)

- GCC-компилятор для ARM

- OpenOCD — программа для работы с отладчиком

- GDB — отладчик

Настройка среды разработки включает следующие шаги:

- Установка и настройка IDE

- Установка ARM GCC компилятора

- Установка и настройка OpenOCD

- Настройка проекта в IDE для работы с SWD

- Подключение SWD-адаптера к микроконтроллеру

После этого можно запускать отладку, устанавливать точки останова и пошагово выполнять код на микроконтроллере.

Основные команды для отладки по SWD

При отладке микроконтроллера STM32 по интерфейсу SWD часто используются следующие команды GDB:

load— загрузка программы в память микроконтроллераcontinue— запуск или продолжение выполнения программыbreak— установка точки остановаstep— пошаговое выполнениеprint— вывод значения переменнойx— просмотр содержимого памяти

Эти команды позволяют эффективно отлаживать программу, выполняющуюся на микроконтроллере STM32.

Преимущества использования SWD для отладки STM32

Интерфейс SWD имеет ряд преимуществ при отладке микроконтроллеров STM32:

- Минимальное количество выводов микроконтроллера (всего 2)

- Высокая скорость обмена данными

- Возможность отладки в режиме реального времени

- Доступ ко всей памяти и периферии микроконтроллера

- Поддержка всеми современными средами разработки

Это делает SWD оптимальным выбором для отладки большинства проектов на базе STM32.

Типичные проблемы при отладке по SWD и их решение

При использовании интерфейса SWD для отладки STM32 могут возникать следующие проблемы:

- Отсутствие связи с микроконтроллером

- Невозможность загрузить программу

- Сбои при выполнении программы

- Некорректная работа точек останова

Для решения этих проблем рекомендуется:

- Проверить правильность подключения SWD-адаптера

- Убедиться в исправности кабелей и разъемов

- Проверить настройки в IDE и OpenOCD

- Обновить прошивку SWD-адаптера

- Попробовать использовать другой SWD-адаптер

Большинство проблем решается правильной настройкой оборудования и программного обеспечения.

Руководство по программированию и отладке MCU — Azure Sphere

- Статья

- Чтение занимает 9 мин

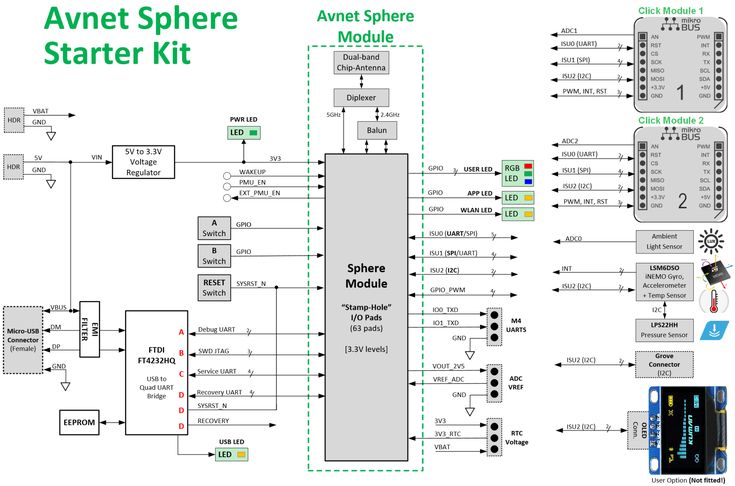

MT3620 предоставляет два выделенных UAR и два сигнала управления (сброс и восстановление) для использования во время подготовки и восстановления устройства. Кроме того, интерфейс SWD доступен для отладки RTApps, а дополнительный UART зарезервирован для диагностики Майкрософт.

Программным средствам для ПК Azure Sphere требуется использовать микросхему интерфейса USB-to-UART, которая предоставляет эти интерфейсы компьютеру таким образом, который позволяет средствам распознавать их и взаимодействовать с ними. Средства Azure Sphere включают поддержку загрузки приложения через USB с помощью UART службы и восстановления ОС Azure Sphere с помощью UART восстановления. Для предоставления интерфейсов средствам ПК требуется использовать микросхему интерфейса UART-to-USB (FTDI) FT4232HQ UART to-USB. В настоящее время средства не поддерживают другие микросхемы FTDI или микросхемы интерфейса от разных производителей.

Средства Azure Sphere включают поддержку загрузки приложения через USB с помощью UART службы и восстановления ОС Azure Sphere с помощью UART восстановления. Для предоставления интерфейсов средствам ПК требуется использовать микросхему интерфейса UART-to-USB (FTDI) FT4232HQ UART to-USB. В настоящее время средства не поддерживают другие микросхемы FTDI или микросхемы интерфейса от разных производителей.

Для до плат разработки эта микросхема интерфейса обычно находится на том же БПО, что и MT3620. Этот подход описан в макете эталонной платы разработки MT3620 (RDB). Для пользовательской платы или модуля, использующего MT3620, может быть целесообразно использовать микросхему интерфейса на отдельном БПО, так как это оборудование требуется только во время производства или обслуживания, что позволяет сократить затраты на единицу. Этот подход задокументирован в проектировании автономного программирования и отладки на доске интерфейса.

Общие сведения о портах

MT3620 предоставляет три UART и интерфейс SWD, которые используются для программирования, диагностики Майкрософт и подготовки микросхемы. Четыре интерфейса имеют следующие функции:

Четыре интерфейса имеют следующие функции:

Отладка UART — UART отладки позволяет корпорации Майкрософт выполнять диагностику. Обратите внимание, что этот UART недоступен для отладки или диагностики приложений.

Под направлением Майкрософт этот интерфейс предоставляет средства сбора дополнительных диагностических сведений, которые могут быть полезны при отладке определенных проблем. Поэтому рекомендуется включить этот интерфейс для устройств, которые используются для разработки программного обеспечения или оборудования, но его можно считать необязательным для устройств, которые достигли производственного этапа.

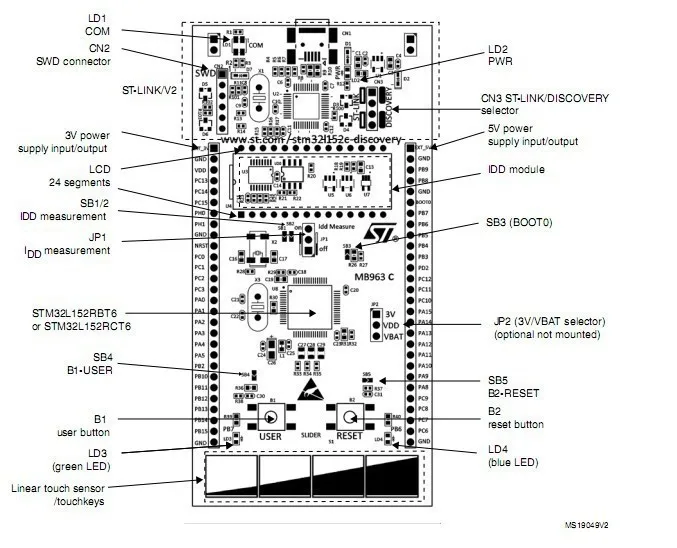

Интерфейс SWD — интерфейс SWD используется при отладке приложений, поддерживающих режим реального времени (RTApps), которые выполняются на ядрах M4F; этот интерфейс является общим для двух ядер M4F.

Если требуется возможность отладки приложений RTApp (например, во время разработки устройства), устройство должно поддерживать этот интерфейс.

UART службы — UART службы предоставляет основной интерфейс программирования и отладки между MT3620 и главным компьютером.

Этот интерфейс включает все операции Azure Sphere CLI, для которых требуется подключенное устройство, за исключением восстановления (как описано в следующем абзаце). Так как UART службы является основным интерфейсом между MT3620 и главным компьютером, этот интерфейс должен быть доступен для устройств, поддерживающих разработку программного обеспечения, а также во время производства розничных устройств. Если этот интерфейс доступен для устройства в поле, его также могут использовать инженеры служб, например для загрузки новых версий программного обеспечения приложения, если устройство не получает облачные обновления, так как оно не подключено к Интернету.

UART восстановления — порт восстановления предоставляет средства восстановления устройства до последней версии операционной системы.

Этот интерфейс должен поддерживаться во время производства, так как восстановление устройства до последней версии операционной системы является распространенной задачей во время производства устройства. Однако после того как устройство было продано клиенту (и оно подключено к Интернету), облачные обновления гарантируют, что устройство будет поддерживаться в актуальном состоянии с последней версией операционной системы.

Общие сведения о компонентах

На следующей схеме представлен обзор основных компонентов интерфейса FTDI с 4 портами и их подключений к MT3620:

Вы можете использовать микросхему и схему FTDI как часть той же платы, что и MT3620 (например, если вы создаете плату разработки) или на отдельной плате интерфейса, которая находится между устройством MT3620 и компьютером.

Чтобы обеспечить совместимость со средствами ПК, важно убедиться, что все предоставляемые UART и интерфейс SWD, которые будут использоваться в вашей разработке, подключены к ftDI-портам, как описано в следующей таблице.

| Закрепление восстановления UART, сброса и восстановления | Порт D | DDBUS0 (48) | RECOVERY_RXD (134) | |

| DDBUS1 (52) | RECOVERY_TXD (135) | |||

| DDBUS2 (53) | RECOVERY_CTS (137) | |||

| DDBUS3 (54) | RECOVERY_RTS (136) | |||

| DDBUS5 (57) | DEBUG_RTS (96)* | |||

| DDBUS6 (58) | SYSRST_N (125) (и при необходимости WAKEUP (70) через канал, описанный ниже) | |||

| UART службы | Порт C | CDBUS0 (38) | SERVICE_RXD (129) | |

| CDBUS1 (39) | SERVICE_TXD (127) | |||

| CDBUS2 (40) | SERVICE_CTS (130) | |||

| CDBUS3 (41) | SERVICE_RTS (128) | |||

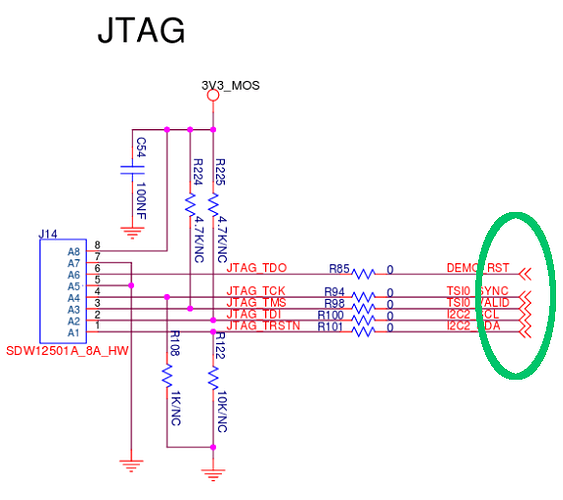

SWD и сброс |

Порт B | BDBUS0 (26) | SWCLK | Дополнительные сведения о каналах SWD см. в интерфейсе SWD в интерфейсе SWD |

| BDBUS1 (27) | SWDIO out | |||

| BDBUS2 (28) | SWDIO в | |||

| BDBUS4 (30) | Направление SWDIO | |||

| BDBUS5 (32) | Включение SWD | |||

| BDBUS6 (33) | SYSRST_N (125) (и при необходимости WAKEUP (70) через канал, описанный ниже) | |||

Отладка UART |

Порт A | ADBUS0 (16) | DEBUG_RXD (94) | |

| ADBUS1 (17) | DEBUG_TXD (95) | |||

| ADBUS2 (18) | DEBUG_CTS (97) | |||

| ADBUS3 (19) | DEBUG_RTS (96)* | |||

*DEBUG_RTS является одним из «закреплений» MT3620, который при извлечении высокой нагрузки во время сброса микросхемы приводит к переходу микросхемы в режим восстановления. Во всех остальных случаях этот пин-код является пин-кодом RTS отладочной UART.

Схемы

На следующих схемах показаны основные компоненты, необходимые для поддержки микросхемы FT4232HQ. Эталонная доска MT3620 предоставляет эталонную схему, включаемую в эту схему.

Эталонная доска MT3620 предоставляет эталонную схему, включаемую в эту схему.

Схема 1:

Примечания— схема 1:

- Резисторы 1K в ряде со строкой сброса включаются, чтобы избежать короткого замыкание в случае, если пользователь нажимает кнопку сброса (если включен в проект) одновременно с программным управлением строкой сброса во время восстановления.

- При развертывание PCB убедитесь, что разностная пара USB_P и USB_N перенаправяются параллельно друг другу, чтобы обеспечить разностную степень разностности характеристик 90.0.

- Резисторы 33. Ряды со строками SWD (необязательно) предназначены для сокращения временных значений и должны размещаться рядом с FT4232HQ.

Схема 2.

Примечания— схема 2:

- SYSRST_N извлекается высоко с помощью резистора объемом 100 тыс. (R8). Это означает, что сброс микросхемы не утверждается по умолчанию.

Следующие два элемента являются необязательными. При наличии они позволяют физической кнопке RESET и интерфейсу FTDI на компьютере автоматически пробудить MT3620, когда сброс был бы включен. Это рекомендуется для любой конструкции, использующей режим Power Down, где кнопка сброса или интерфейс ПК должны продолжать работать в режиме power Down.

При наличии они позволяют физической кнопке RESET и интерфейсу FTDI на компьютере автоматически пробудить MT3620, когда сброс был бы включен. Это рекомендуется для любой конструкции, использующей режим Power Down, где кнопка сброса или интерфейс ПК должны продолжать работать в режиме power Down.

- Пара диодов Schottky соединена последовательность между SYSRST_N и WAKEUP, а общее подключение к котодам подключается к кнопке сброса и сигналам сброса FTDI. Это предотвращает низкое SYSRST_N при низком переключатель пробуждения.

- WakeUP извлекается высоко с резистором 100 000, подключенным к 3V3_RTC питания. Устойчивость 100 000 гарантирует, что wakeUP переключается низко, SYSRST_N переключается низко; подключение к 3V3_RTC гарантирует, что активация пробуждения будет по-прежнему высокой, если источник питания MT3620 отключается для режима отключения питания.

FTDI EEPROM

Микросхема интерфейса FTDI предоставляет набор контактов, которые должны быть подключены к небольшому EEPROM, который используется для хранения сведений о производителе и серийного номера. После сборки доски эти сведения запрограммированы в EEPROM по USB с помощью программного средства, предоставляемого FTDI, как описано далее в средстве программирования FTDI FT_PROG.

После сборки доски эти сведения запрограммированы в EEPROM по USB с помощью программного средства, предоставляемого FTDI, как описано далее в средстве программирования FTDI FT_PROG.

Следующие части EEPROM совместимы с микросхемой FTDI:

- 93LC46BT-I/OT

- 93LC56BT-I/OT

- 93LC66BT-I/OT

Обратите внимание на использование варианта LC, совместимого с предложением 3.3V. В целях внутренней разработки корпорация Майкрософт всегда использовала часть 93LC56BT-I/OT.

Подключите EEPROM к микросхеме FTDI следующим образом:

| Канал EEPROM | Подключение к микросхеме FTDI |

|---|---|

Интерфейсы UART

Для подключений UART восстановления, службы и отладки между MT3620 и FTDI не требуются специальные каналы. Однако обратите внимание на перекрестное использование TXD и RXD, а также CTS и RTS. В документации FTDI описано закрепление 0 каждого порта в виде TXD и закрепление 1 как RXD. Эти определения являются относительным для микросхемы FTDI; То есть пин-код 0 является выходным, а пин-код 1 — входными данными. Следовательно, необходимо пересекать подключения RXD и TXD к MT3620 (и аналогично для CTS и RTS). На следующей схеме показано, как это сделать для UART службы. используйте ту же схему для UART восстановления и отладки:

Эти определения являются относительным для микросхемы FTDI; То есть пин-код 0 является выходным, а пин-код 1 — входными данными. Следовательно, необходимо пересекать подключения RXD и TXD к MT3620 (и аналогично для CTS и RTS). На следующей схеме показано, как это сделать для UART службы. используйте ту же схему для UART восстановления и отладки:

Интерфейс SWD

Хотя микросхемы FTDI обычно используются для обеспечения моста между UART и USB, интерфейс программирования и отладки Azure Sphere использует дополнительные цепи на основе буфера четырехмерных значений, чтобы позволить части FTDI работать в качестве высокоскоростного интерфейса SWD.

Ниже показан необходимый канал и подключение к микросхеме FTDI. Обратите внимание, что сигнал SWDIO подключается к контакту MT3620 pin 98, а SWCLK подключается к контакту 99.

| Размещение буфера с три состояниями | Подключения FTDI Port-B |

|---|---|

USB-индикатор активности (необязательно)

Светодиодный индикатор действия USB может быть полезен для передачи данных через USB-подключение во время обычной работы. Светодиодный индикатор действия USB можно реализовать несколькими способами. Следующий канал является просто примером.

Светодиодный индикатор действия USB можно реализовать несколькими способами. Следующий канал является просто примером.

Канал AND объединяет часы и линии данных, которые подключают FT4232HQ к EEPROM. Хотя это и не очевидно, эти две строки переключаются при отправке и получении данных по USB и, следовательно, могут использоваться для определения активности USB. Однако во время выходных данных от шлюза AND слишком мало для освещения индикатора; Таким образом, этот сигнал используется для управления моно стабильным каналом, который, в свою очередь, определяет светодиодный индикатор.

Во время моно стабильного канала установлено значение 100 мс, поэтому даже короткие пики USB-трафика приведут к освещению индикатора.

Средство программирования FT_PROG FTDI

Чтобы помочь в программировании EEPROM, FTDI предоставляет бесплатное программное обеспечение с именем FT_PROG. Средство доступно как в качестве приложения графического пользовательского интерфейса Windows, так и в качестве программы командной строки. оба параметра устанавливаются одновременно из одного пакета. Скачайте средство с веб-сайта FTDI и установите его в расположении по умолчанию.

оба параметра устанавливаются одновременно из одного пакета. Скачайте средство с веб-сайта FTDI и установите его в расположении по умолчанию.

FT_PROG командной строки

Версия командной строки FT_PROG является предпочтительным методом программирования EEPROM, так как она принимает имя файла конфигурации в качестве параметра, а затем программирует несколько устройств с помощью одной команды.

Репозиторий «Конструкторы оборудования Azure Sphere» на сайте GitHub содержит файл конфигурации EEPROM для использования со средством командной строки. Настоятельно рекомендуется использовать этот файл и средство командной строки в производственных сценариях. Файл конфигурации программирует EEPROM со следующими параметрами:

- Включает прямой режим D2XX и отключает виртуальный COM-порт

- Автоматически создает серийный номер, начиная с «AS».

- Задает для описания продукта значение «MSFT MT3620 Std Interface» (MsFT MT3620 Std Interface).

Для программирования EEPROM необходимо использовать этот файл без изменений, так как средства ПК Azure Sphere искать строку описания продукта и завершались сбоем при изменении этого значения.

Пошаговые инструкции по программированию EEPROM

Чтобы использовать версию командной строки FT_PROG для программирования EEPROM для микросхемы FTDI с четырьмя портами:

Установите средства FTDI в расположении по умолчанию:

C:\Program Files(x86)\FTDI\FT_ProgПодключите одну или несколько плат MT3620 к компьютеру.

Откройте командную строку (например, cmd.exe) и перейдите в папку, в которой сохранен файл конфигурации.

Введите следующую команду, чтобы вывести список всех подключенных устройств:

"c:\Program Files (x86)\FTDI\FT_Prog\FT_Prog-CmdLine.exe" scanЕсли подключено четыре устройства, выходные данные будут выглядеть примерно так:

Device 0: FT4232H, MSFT MT3620 Std Interface, 984A8DD25A36 Device 1: FT4232H, MSFT MT3620 Std Interface, 984A8DD25A36 Device 2: FT4232H, MSFT MT3620 Std Interface, 984A8DD25A36 Device 3: FT4232H, MSFT MT3620 Std Interface, 984A8DD25A36

Введите следующую команду, чтобы за программирование всех подключенных устройств.

Укажите индексы подключенных устройств (0, 1, 2 и т. д.) после

Укажите индексы подключенных устройств (0, 1, 2 и т. д.) после progcyclпараметров:"c:\Program Files (x86)\FTDI\FT_Prog\FT_Prog-CmdLine.exe" scan prog 0,1,2,3 MT3620_Standard_Interface.xml cycl 0,1,2,3Средство должно отображать следующее:

Scanning for devices... Device 0: FT4232H, MSFT MT3620 Std Interface, 984A8DD25A36 Device 1: FT4232H, MSFT MT3620 Std Interface, 984A8DD25A36 Device 2: FT4232H, MSFT MT3620 Std Interface, 984A8DD25A36 Device 3: FT4232H, MSFT MT3620 Std Interface, 984A8DD25A36 Device 0 programmed successfully! Device 1 programmed successfully! Device 2 programmed successfully! Device 3 programmed successfully! Finished Re-enumerating Device 0.... Re-enumerating Device 1.... Re-enumerating Device 2.... Re-enumerating Device 3....

Чтобы убедиться, что программирование прошло успешно, проверьте еще раз:

"c:\Program Files (x86)\FTDI\FT_Prog\FT_Prog-CmdLine.exe" scanОбратите внимание, что серийные номера имеют изменения в выходных данных и теперь начинаются с AS:

Scanning for devices.

..

Device 0: FT4232H, MSFT MT3620 Std Interface, AS5AW7FD

Device 1: FT4232H, MSFT MT3620 Std Interface, AS5AHG3C

Device 2: FT4232H, MSFT MT3620 Std Interface, AS5DWM2I

Device 3: FT4232H, MSFT MT3620 Std Interface, AS5JQ0LJ

..

Device 0: FT4232H, MSFT MT3620 Std Interface, AS5AW7FD

Device 1: FT4232H, MSFT MT3620 Std Interface, AS5AHG3C

Device 2: FT4232H, MSFT MT3620 Std Interface, AS5DWM2I

Device 3: FT4232H, MSFT MT3620 Std Interface, AS5JQ0LJ

FT_PROG графического пользовательского интерфейса

Версия графического пользовательского интерфейса Windows приложения полезна для чтения и проверки состояния сведений EEPROM. Его также можно использовать для изменения информации. однако мы рекомендуем использовать версию программы из командной строки для программирования устройства.

После запуска приложения нажмите кнопку Scan (со значком лупы), чтобы прочитать и отобразить текущее содержимое EEPROM.

Если появится диалоговое окно «Неизвестное устройство», как показано в следующем примере, нажмите кнопку «ОК», пока в окне приложения не отобразится информация.

В следующем примере показано правильное отображение:

Дополнительные сведения об использовании программного обеспечения см. в FT_PROG документации.

в FT_PROG документации.

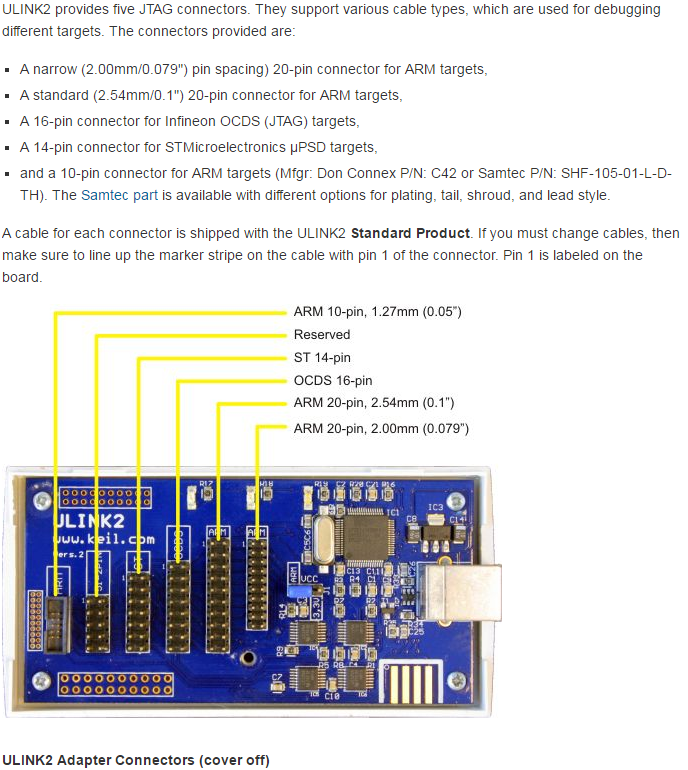

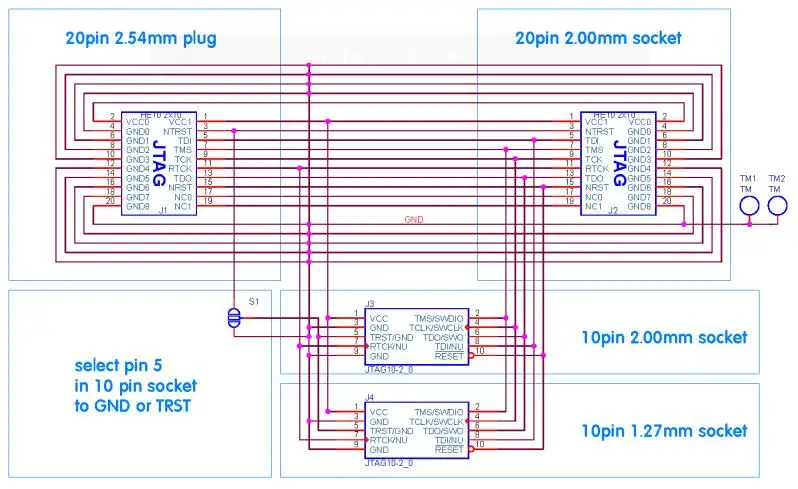

Адаптеры JTAG с поддержкой SWD | arm

Технология JTAG широко применяется для тестирования электронных устройств, чаще всего основанные на микроконтроллерах, CPU, CPLD и/или FPGA. JTAG также позволяет аппаратную отладку, чтение/запись памяти, управление ножками I/O, анализ на производительность работающего кода (здесь приведен перевод статьи [1]).

Технология SWD (расшифровывается как Serial Wire Debug) это более современная версия JTAG, требующая для работы только 2 сигнальных выводов вместо как минимум 4 у стандартного JTAG (иногда добавляется еще один сигнал, что доводит количество сигнальных проводников до 5). SWJ это комбинация SWD и традиционного JTAG. Однако на высшем уровне оба этих интерфейса предоставляют аналогичные функции с разными вариациями, зависящими от управляющего ПО и от аппаратного обеспечения.

С одной стороны эта функциональность должна поддерживаться в целевом устройстве (target device). Порт отладки (Debug Port) часто называют JTAG-DP для JTAG и SW-DP для SWD. Устройство с поддержкой SWJ часто комбинирует в себе оба этих стандарта, при этом SWD-сигналы SWDIO и SWCLK повторно используются как JTAG-сигналы JTMS и JTCK (таким образом, SWJ обеспечивает обратную совместимость с традиционным JTAG). Большинство 32-битых микроконтроллеров и чипов SoC имеют на борту один из таких интерфейсов (или оба).

Порт отладки (Debug Port) часто называют JTAG-DP для JTAG и SW-DP для SWD. Устройство с поддержкой SWJ часто комбинирует в себе оба этих стандарта, при этом SWD-сигналы SWDIO и SWCLK повторно используются как JTAG-сигналы JTMS и JTCK (таким образом, SWJ обеспечивает обратную совместимость с традиционным JTAG). Большинство 32-битых микроконтроллеров и чипов SoC имеют на борту один из таких интерфейсов (или оба).

С другой стороны Вам нужен SWJ-адаптер, который может обмениваться данными с устройством по протоколу JTAG и/или SWD. SWJ могут стоить недорого (< 5$) и очень дорого (> 1000$), в зависимости от качества аппаратуры и ПО (и от бренда производителя). Ниже перечислены несколько описаний SWJ-адаптеров.

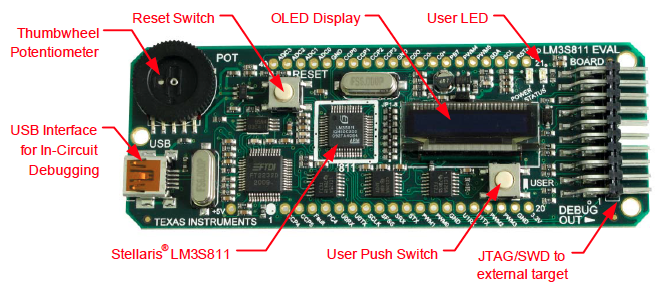

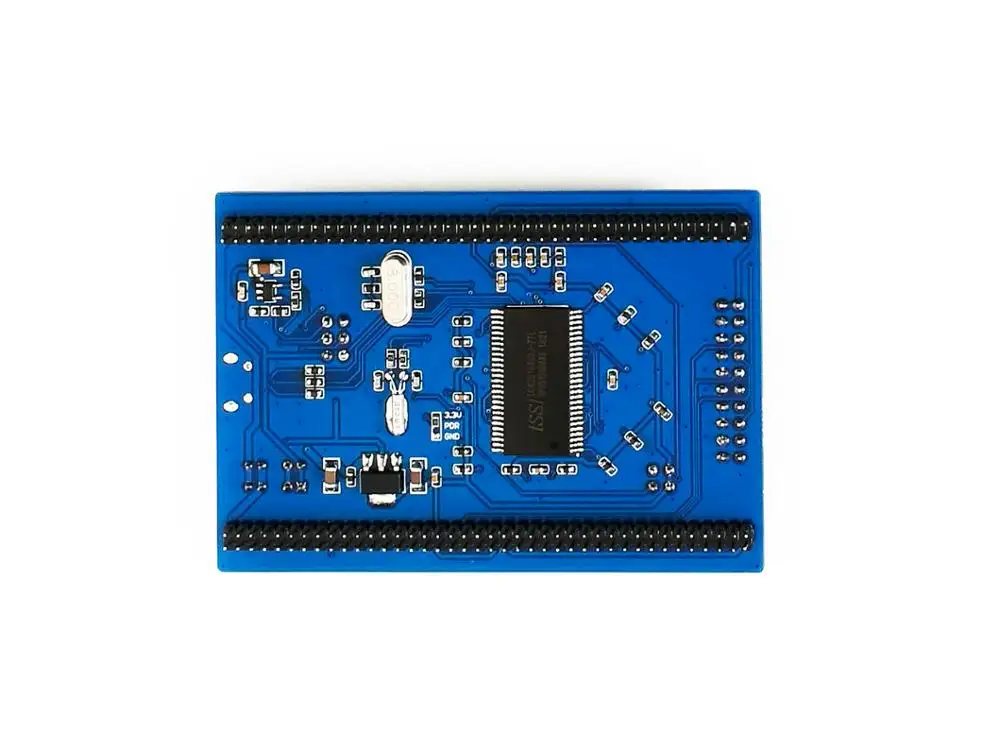

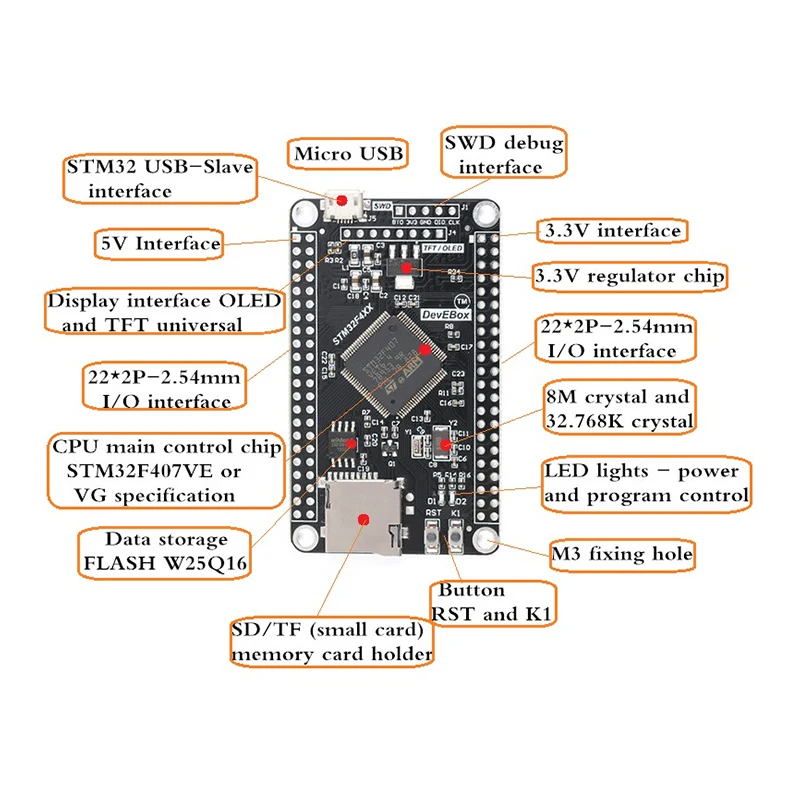

[ST-Link v2]

ST-LINK/V2 это адаптер от STMicroelectronics, очень удобный для прошивки микроконтроллеров STM8 и STM32 этой компании, таких как серия STM32 F1. Адаптер поддерживает интерфейсы JTAG, SWD и SWIM (последний применяется для STM8).

Эти SWJ-адаптеры основаны на микроконтроллерах STM32F1xx ARM Cortex M3. Любопытно, что адаптер на основе микроконтроллера STM32F1xx применяется для программирования и отладки таких же микроконтроллеров STM32F1xx.

Использование ST-LINK/V2 на Linux. Для нормального использования сначала добавьте правила для обычного пользователя, чтобы можно было получить доступ к этому устройству (правило udev, основанное на идентификаторах VID и PID адаптера, показываемых lsusb). Это делается только один раз перед тем, как адаптер подключается для непосредственного использования:

echo -n 'ST-Link V2 SWJ adapter' | sudo tee -a /etc/udev/rules.d/60-st-linkv2.rules

echo -n 'ATTR{idVendor}=="0483", ATTR{idProduct}=="3748", MODE="0666"' | sudo tee

-a /etc/udev/rules.d/60-st-linkv2.rules

sudo udevadm control --reload-rules

Для подключения к микроконтроллерам STM32F1xx ARM Cortex M3 используется OpenOCD [9]:

openocd --file interface/stlink-v2.cfg --file target/stm32f1x.cfg Open On-Chip Debugger 0.10.0-dev-00189-g554313b (2016-01-12-10:52) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html Info : auto-selecting first available session transport "hla_swd". To override use 'transport select < transport >'. Info : The selected transport took over low-level target control. The results might differ compared to plain JTAG/SWD adapter speed: 1000 kHz adapter_nsrst_delay: 100 none separate Info : Unable to match requested speed 1000 kHz, using 950 kHz Info : Unable to match requested speed 1000 kHz, using 950 kHz Info : clock speed 950 kHz Info : STLINK v2 JTAG v17 API v2 SWIM v4 VID 0x0483 PID 0x3748 Info : using stlink api v2 Info : Target voltage: 3.534945 Info : stm32f1x.cpu: hardware has 6 breakpoints, 4 watchpoints

[Клон ST-LINK/V2]

Это полностью содранный с оригинала ST-LINK/V2. Он поставляется в таком же корпусе, с такими же кабелями, выглядит так же, сохранено даже название печатной платы (MB936). Но сама плата не такая же, список деталей (BOM) не совпадает с оригинальным.

Он поставляется в таком же корпусе, с такими же кабелями, выглядит так же, сохранено даже название печатной платы (MB936). Но сама плата не такая же, список деталей (BOM) не совпадает с оригинальным.

Оригинальный адаптер снабжен дополнительной защитой от статического электричества, защитными резисторами и трансивером, позволяющим работать с уровнями сигнала от 1.65V до 5.5V. В клоне это полностью отсутствует, поскольку сигналы интерфейса напрямую подключены к микроконтроллеру. Таким образом, поддерживаются только уровни сигналов 3.3V на отлаживаемой/программируемой системе, и иногда 5V, потому что выводы микроконтроллера допускают по входу уровни 5V (5V tolerant).

Этот адаптер стоит $9, что довольно много. Если не нужен JTAG, то есть более дешевый адаптер, описанный ниже.

[ST-LINK V2 aluminium]

Эти адаптеры поставляются в маленьком алюминиевом корпусе, стоит порядка $2.5. Они поддерживают SWD и SWIM (для STM8), но не поддерживают JTAG. Это вероятно самый дешевый клон, который можно найти. Вероятно, такая низкая цена обусловлена тем, что в адаптере используются STM32F101. В сравнении с STM32F103 возможности у STM32F101 меньше, но все-таки это адаптер USB! Вероятно, что у STM32F101 тот же самый кристалл, что и STM32F103, и тот же самый корпус, просто STM32F101 получают в результате отбраковки STM32F103. Подобным образом декларируется, что у STM32F103C8 только 64 килобайта памяти flash, потому что полный тест они не прошли, в сравнении с 128 килобайтами STM32F103CB, но на борту STM32F103C8 часто есть больше памяти (Вы можете проверить эту память на ошибки путем чтения/записи).

Это вероятно самый дешевый клон, который можно найти. Вероятно, такая низкая цена обусловлена тем, что в адаптере используются STM32F101. В сравнении с STM32F103 возможности у STM32F101 меньше, но все-таки это адаптер USB! Вероятно, что у STM32F101 тот же самый кристалл, что и STM32F103, и тот же самый корпус, просто STM32F101 получают в результате отбраковки STM32F103. Подобным образом декларируется, что у STM32F103C8 только 64 килобайта памяти flash, потому что полный тест они не прошли, в сравнении с 128 килобайтами STM32F103CB, но на борту STM32F103C8 часто есть больше памяти (Вы можете проверить эту память на ошибки путем чтения/записи).

Существует несколько версий плат этого варианта адаптера, и может также отличаться цоколевка.

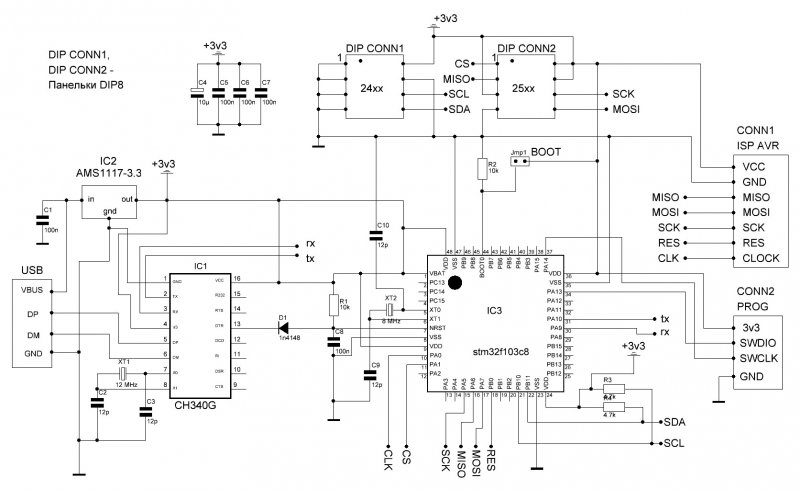

2014-06-22 ST-LINK V2. Ниже показана схема и внешний вид этих адаптеров.

В адаптере используется интересный трюк для подключения двух светодиодов (LED) на одной ножке порта (PA9):

• Когда ножка выхода порта установлена в лог. 1, зажигается один светодиод

1, зажигается один светодиод

• Когда эта же ножка переводится в лог. 0, зажигается другой светодиод

• Когда ножка переводится в состояние висящего входа, оба светодиода выключается

• Когда выход работает в режиме ШИМ (PWM), Вы можете смешивать эти 2 цвета светодиодов (красный и синий). Это происходит потому, что глаз не замечает быстрых мерцаний, светодиоды находятся рядом и светят в маленькую дырку по центру.

Тот же самый адаптер, но с другой цоколевкой. Выглядит очень похоже на вышеописанный адаптер, но цоколевка сигналов разъема сильно отличается (кроме питания), и используется только один светодиод. На плате нет никакой маркировки сигналов.

2016-01-18 MX-LINK V2. У этого адаптера логотип «M» вместо логотипа ST, что возможно соответствует маркировке «MX-LINK V2» на плате.

[Baite]

Это аналог ST-Link V2 с поддержкой JTAG, SWD и SWIM (для STM8) [2].

Автор статьи [1] сделал для этого адаптера стикер с цоколевкой сигналов.

Автор также перерисовал по плате схему. Все выводы коннектора защищены резисторами 220 ом.

Baite-V2A. Более новая версия промаркирована «V2A» (под кварцем), но схема почти такая же, со следующими изменениями:

• Присутствуют все ножки микроконтроллера (есть даже маска пайки между ними).

• Добавлен порт SWD.

• STM32F103C8 заменен на STM32F101CB, но используется как STM32F103 (так же, как в других дешевых адаптерах).

• Используются пассивные элементы меньшего размера.

• Некачественная разводка платы.

[Black Magic Probe]

Адаптер Black Magic Probe [3] (известный как BMP) очень интересный SWJ-адаптер, потому что в него встроен сервер GDB. Таким образом, не нужно запускать сервер OpenOCD, чтобы управлять адаптером SWJ. Вы можете напрямую подключить GDB к этому адаптеру (через драйвер USB CDC ACM).

Вы можете напрямую подключить GDB к этому адаптеру (через драйвер USB CDC ACM).

В этом адаптере также есть порт UART (через второй канал USB CDC ACM). Это очень полезно для отладки в реальном времени, без точек останова (для обмена сообщениями printf).

Поставляемая аппаратура имеет следующие недостатки:

• Используется не очень удобный коннектор ARM Cortex SWJ с маленьким шагом.

• Отдельный UART используется не всегда (UART также доступен на коннекторе SWJ).

• Дорогой (> $50), но эта цена относительно разумная, поскольку есть поддержка проекта.

Из-за того, что firmware этого адаптера открыто (open source), его можно портировать на другую аппаратуру, и народ реально этим пользуется [4]. Проект был портирован [5] на blue pill [6]. Также он был портирован и на клон ST-Link V2 [7], но на нем больше нет дополнительного UART. Автор решил сделать порт на baite [2]. На коннекторе используется меньше выводов питания, но зато получается достаточно функциональных выводов для добавления UART (и SRST).

Сборка firmware (ожидается интегрирование патча):

git clone https://github.com/tsaitgaist/blackmagic.git cd blackmagic git submodule init git submodule update git checkout baite-platform # if you are usgin GCC >= 7 git cherry-pick 2ebcffa2a4911090b43c36594dae6b58d4bb2f27 make cd src make clean make PROBE_HOST=baite

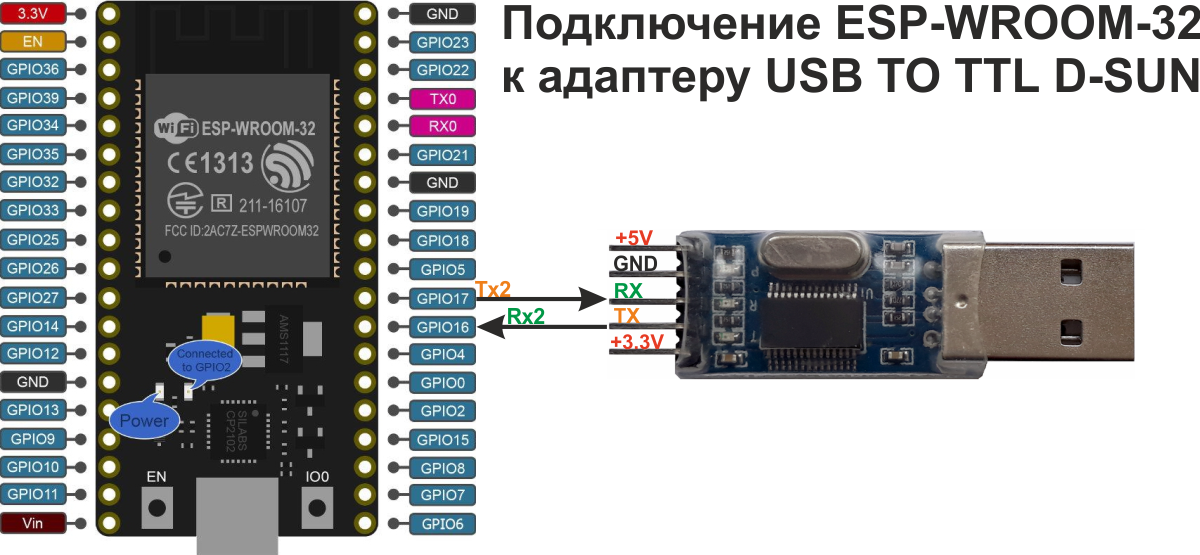

После получения двоичного кода нужно перепрошить им адаптер Baite. Как Вы можете видеть по схеме, выводы JTAG и SWD микроконтроллера не подключены (на плате нет контактных площадок, куда эти выводы припаяны). Но на обратной стороне платы можно найти контрольные точки, чтобы запрограммировать микроконтроллер через serial bootloader:

| Вывод | Сигнал |

| 1 (квадратный) | RX |

| 2 | TX |

| 3 | BOOT0 |

| 4 | +5V |

| 5 | GND |

Для подключения используйте любой конвертер USB — TTL UART, и подключите соответствующие выводы к этому порту. Не подавайте питание на адаптер Baite через USB, потому что это может привести к его загрузке в нормальном режиме (не в режиме serial bootloader). Вместо этого подайте питание через конвертер USB — UART. Для запуска serial bootloader в момент подачи питания на адаптер нужно перевести сигнал BOOT0 в лог. 1 путем подключения его к +3.3V или к DTR (или к любому другому сигналу, который находится в лог. 1 на конвертере USB — UART).

Не подавайте питание на адаптер Baite через USB, потому что это может привести к его загрузке в нормальном режиме (не в режиме serial bootloader). Вместо этого подайте питание через конвертер USB — UART. Для запуска serial bootloader в момент подачи питания на адаптер нужно перевести сигнал BOOT0 в лог. 1 путем подключения его к +3.3V или к DTR (или к любому другому сигналу, который находится в лог. 1 на конвертере USB — UART).

Чтобы прошить Black Magic firmware автор использовал stm32flash. Поскольку flash защищена от чтения/записи, сначала нужно очистить эти биты опций.

# disable flash read protection stm32flash -k /dev/ttyUSB0 # disable flash write protection stm32flash -u /dev/ttyUSB0 # erase flash stm32flash -o /dev/ttyUSB0 # flash the DFU bootloader stm32flash -w src/blackmagic_dfu.bin -v /dev/ttyUSB0 # flash the main firmware stm32flash -w src/blackmagic.bin -v -S 0x08002000 /dev/ttyUSB0

Поскольку этот адаптер основан на микроконтроллере STM32F103C8 с 64 килобайтами flash, DFU bootloader дает возможность использовать только 56 килобайт памяти flash для основного приложения. Blackmagic firmware превышает этот размер, поэтому его нельзя прошить, если программное обеспечение DFU не игнорирует это ограничение. У микроконтроллера STM32F103C8 часто есть 128 килобайт flash, так что все еще можно прошить blackmagic firmware, используя serial bootloader (по адресу 0x08002000). Проверка во время прошивки (verification) гарантирует, что весь код firmware был успешно записан.

Blackmagic firmware превышает этот размер, поэтому его нельзя прошить, если программное обеспечение DFU не игнорирует это ограничение. У микроконтроллера STM32F103C8 часто есть 128 килобайт flash, так что все еще можно прошить blackmagic firmware, используя serial bootloader (по адресу 0x08002000). Проверка во время прошивки (verification) гарантирует, что весь код firmware был успешно записан.

Отключите Baite, и снова подключите его через USB. В нем должно запуститься основное программное обеспечение, и операционная система хоста должна обнаружить два порта USB CDC ACM.

Вы можете перепрошить устройство из основного приложения, используя dfu-util (если Вы сможете перевести dfu-util в состояние игнорирования ограничения по размеру памяти):

dfu-util -d 1d50:6018 -s 0x08002000:leave -D blackmagic.bin

Цоколевка нового «BMP Baite»:

| Сигнал | Вывод | Вывод | Сигнал |

| SRTST | 1 | 2 | +3. 3V 3V |

| +5V | 3 | 4 | JTCK/SWCLK |

| RX | 5 (ключ) | 6 | JTMS/SWDIO |

| GND | 7 | 8 | JTDO/TRACESWO |

| TX | 9 | 10 | JTDI |

Примечание: вывод RX подтягивается к лог. 1 с помощью резистора 620 ом. Таким образом TX, подключенный к BMP Baite, должен иметь достаточную нагрузочную способность, чтобы подтянуть сигнал к лог. 0 (скорее всего, USB — UART адаптер наподобие Ch440 это сделать не сможет).

Если Вы подключите SRST к сигналу NRST целевой отлаживаемой системы, то можно будет подавать на неё сброс без нажатия кнопки сброса на плате отлаживаемой системы (если конечно такая кнопка есть). Сигнал сброса генерируется следующей командой:

gdb --eval-command="target extended-remote /dev/ttyACM0" --eval-command="monitor hard_srst" --eval-command="quit"

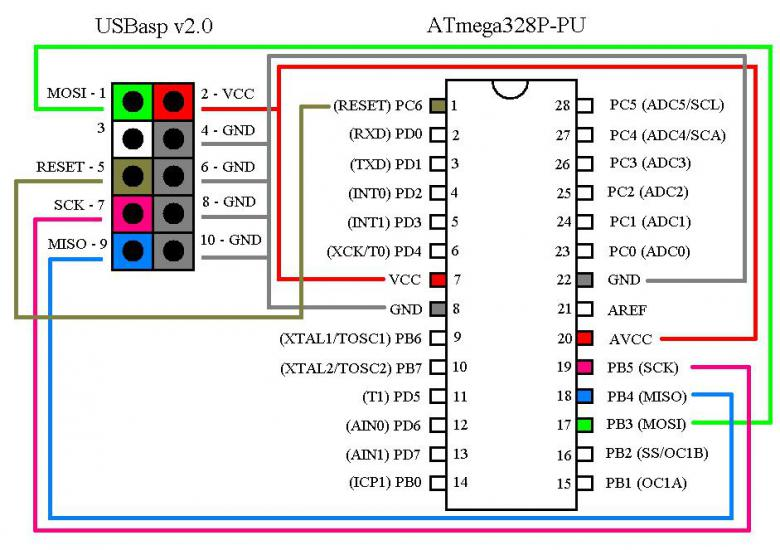

[Altera USB-Blaster]

USB-Blaster это адаптер от компании Altera. Он часто используется для прошивки FPGA, но по сути это обычный адаптер JTAG.

Он часто используется для прошивки FPGA, но по сути это обычный адаптер JTAG.

Внимание: вывод VCC{TARGET} подключается к опорному напряжению, используемому для обмена JTAG, обычно предоставляемому печатной платой целевого отлаживаемого устройства (часто это напряжение 3.3V или 1.8V). Иначе сигналы не смогут определиться адаптером JTAG.

Сначала добавьте правила для обычного пользователя, чтобы он мог получить доступ к устройству (правило udev на основе идентификаторов VID и PID, показываемых lsusb). Это делается только один раз, перед тем как устройство подключается для непосредственного использования:

echo -n 'Altera USB-Blaster JTAG adatper' | sudo tee

-a /etc/udev/rules.d/60-altera-usb-blaster.rules

echo -n 'ATTR{idVendor}=="09fb", ATTR{idProduct}=="6001", MODE="666"'

| sudo tee -a /etc/udev/rules.d/60-altera-usb-blaster.rules

sudo udevadm control --reload-rules

Чтобы можно было использовать этот адаптер, нужно перекомпилировать OpenOCD для USB-Blaster, чтобы использовалась библиотека libftdi (наверное потому что это клон).

git clone http://git.code.sf.net/p/openocd/code openocd-code cd openocd-code ./bootstrap ./configure --enable-usb_blaster_libftdi make sudo make install cd ..

Иначе OpenOCD зависает, загружая на 100% CPU, и его нужно прибить используя -KILL.

openocd --file interface/altera-usb-blaster.cfg Open On-Chip Debugger 0.10.0-dev-00189-g554313b (2016-01-12-11:26) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html Warn : Adapter driver 'usb_blaster' did not declare which transports it allows; assuming legacy JTAG-only Info : only one transport option; autoselect 'jtag' adapter speed: 1000 kHz adapter_nsrst_delay: 100 jtag_ntrst_delay: 100 none separate cortex_m reset_config sysresetreq Info : No lowlevel driver configured, will try them all Info : Altera USB-Blaster II found (Firm. rev. = 6??) Info : This adapter doesn't support configurable speed

openocd --debug 3 --file interface/altera-usb-blaster.cfg ... Debug: 385 845 tcl.c:497 handle_nand_init_command(): Initializing NAND devices... Debug: 386 845 command.c:145 script_debug(): command - ocd_command ocd_command type ocd_pld init Debug: 387 845 command.c:145 script_debug(): command - ocd_pld ocd_pld init Debug: 389 846 pld.c:207 handle_pld_init_command(): Initializing PLDs...

Теперь Вы можете использовать адаптер, пример с микроконтроллером STM32F1:

openocd --file interface/altera-usb-blaster.cfg --file target/stm32f1x.cfg Open On-Chip Debugger 0.10.0-dev-00189-g554313b (2016-01-12-16:26) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html Warn : Adapter driver 'usb_blaster' did not declare which transports it allows; assuming legacy JTAG-only Info : only one transport option; autoselect 'jtag' adapter speed: 1000 kHz adapter_nsrst_delay: 100 jtag_ntrst_delay: 100 none separate cortex_m reset_config sysresetreq Info : No lowlevel driver configured, will try them all Info : usb blaster interface using libftdi Error: unable to get latency timer Info : This adapter doesn't support configurable speed Info : JTAG tap: stm32f1x.cpu tap/device found: 0x3ba00477 (mfg: 0x23b, part: 0xba00, ver: 0x3) Info : JTAG tap: stm32f1x.bs tap/device found: 0x16410041 (mfg: 0x020, part: 0x6410, ver: 0x1) Info : stm32f1x.cpu: hardware has 6 breakpoints, 4 watchpoints

Оригинальный адаптер Altera USB-Blaster использует чипы FTDI FT245 и MAX CPLD. Имеется множество его клонов разного качества и разной поддержкой диапазонов напряжения.

[SiLabs USB-Blaster]

Здесь используется микроконтроллер C8051F321 от Silicon Labs и 4-канальный буфер 74LVC125 (для преобразования уровней сигналов в пределах от 1.65V до 3.6V).

[PIC USB-Blaster]

Этот адаптер использует микроконтроллер PIC18F14 компании Microchip, без каких-либо буферов (поддерживаются только сигналы с уровнями 5V).

[ARMJISHU USB-Blaster]

Здесь используется STM32F101 от ST (как STM32F103 с поддержкой USB) и 8-канальный буфер 74HC244 (для преобразования уровней от 2. 0V до 6.0V).

0V до 6.0V).

На схеме видно, что аппаратура может также управлять сигналами (на 3.3V) в случае, когда Vcc_target не подключен, и Вы можете добавить слот карт uSD или память SPI flash. Не известно, поддерживается ли этот функционал в программном обеспечении.

[SEGGER J-Link]

O-Link-ARM V8 [8], клон SEGGER J-Link.

Поддерживает JTAG, SWD, SWO, RTCK и опорное напряжение для регулировки уровней, что делает этот JTAG-адаптер наиболее полным.

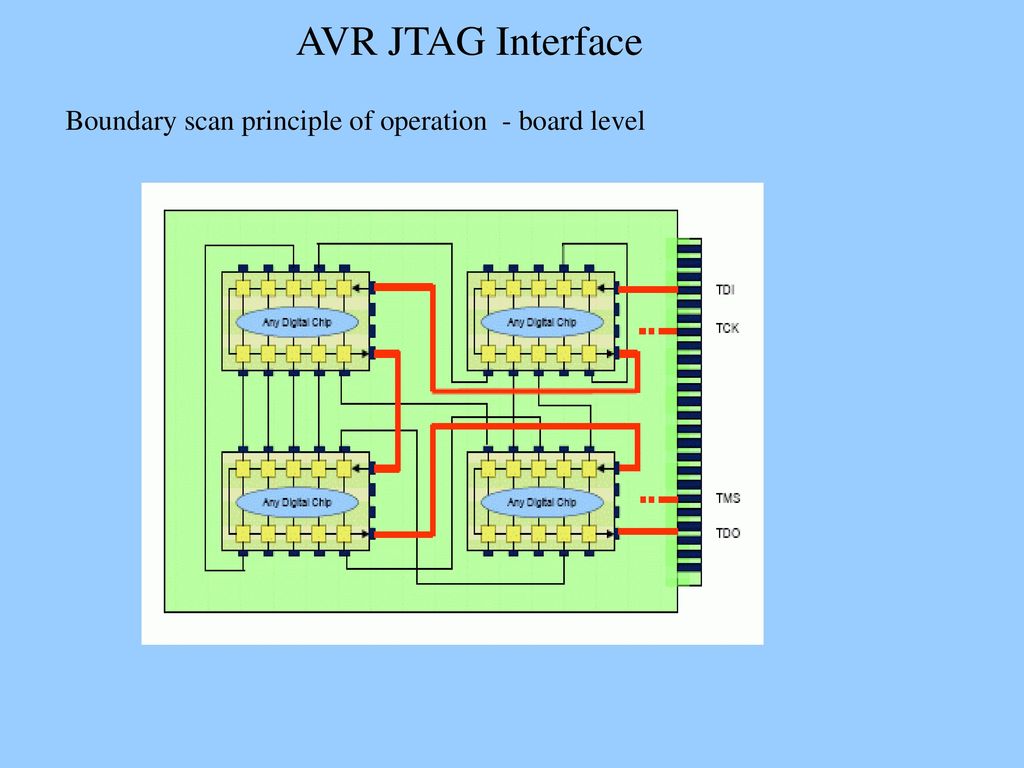

[Цепочка сканирования JTAG]

Микросхемы с поддержкой JTAG имеют точки тестирования, которые называются Test Access Points (TAP). Один микроконтроллер может иметь несколько TAP, соединяемых в цепочку (scan chain). Несколько микросхем с TAP-ми также могут быть соединены (сигналами на печатной плате) в цепочку, это позволяет опрашивать все устройства на плате через одно подключение JTAG. Каждый TAP имеет идентификатор (IDCODE) и он может быть выбран индивидуально.

Иногда полезно перечислить все доступные TAP-ы на цепочке, чтобы узнать, какие есть устройства в системе. Это можно просто осуществить с помощью ПО urJTAG [10]. Пример с USB Blaster:

jtag UrJTAG 0.10 #2007 Copyright (C) 2002, 2003 ETC s.r.o. Copyright (C) 2007, 2008, 2009 Kolja Waschk and the respective authors UrJTAG is free software, covered by the GNU General Public License, and you are welcome to change it and/or distribute copies of it under certain conditions. There is absolutely no warranty for UrJTAG. warning: UrJTAG may damage your hardware! Type "quit" to exit, "help" for help. jtag> cable UsbBlaster Connected to libftdi driver. jtag> detect IR length: 9 Chain length: 2 Device Id: 00111011101000000000010001110111 (0x3BA00477) Unknown manufacturer! (01000111011) (/usr/share/urjtag/MANUFACTURERS) Device Id: 00010110010000010000000001000001 (0x16410041) Unknown manufacturer! (00000100000) (/usr/share/urjtag/MANUFACTURERS)

OpenOCD также сканирует цепочку, если нет предоставленных target (какой используется адаптер, все-таки определить нужно):

openocd --file interface/altera-usb-blaster.cfg Open On-Chip Debugger 0.10.0-dev-00189-g554313b (2016-01-12-16:26) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html Warn : Adapter driver 'usb_blaster' did not declare which transports it allows; assuming legacy JTAG-only Info : only one transport option; autoselect 'jtag' Info : No lowlevel driver configured, will try them all Info : usb blaster interface using libftdi Error: unable to get latency timer Info : This adapter doesn't support configurable speed Warn : There are no enabled taps. AUTO PROBING MIGHT NOT WORK!! Info : JTAG tap: auto0.tap tap/device found: 0x3ba00477 (mfg: 0x23b, part: 0xba00, ver: 0x3) Info : JTAG tap: auto1.tap tap/device found: 0x16410041 (mfg: 0x020, part: 0x6410, ver: 0x1) Warn : AUTO auto0.tap - use "jtag newtap auto0 tap -irlen 4 -expected-id 0x3ba00477" Warn : AUTO auto1.tap - use "jtag newtap auto1 tap -irlen 5 -expected-id 0x16410041" Warn : gdb services need one or more targets defined

0x3ba00477 соответствует Cortex-M3 TAP, и 0x16410041 boundary scan TAP, как указано в документации на STM32F1xx.

Хотя ST-Link v2 с микроконтроллерами ST главным образом используется как адаптер SWD, он также поддерживает обычный JTAG. Оба этих протокола реализованы драйвером High Level Adapter (HLA). Но все выглядит так, как будто scan chain не поддерживается драйвером HLA.

openocd --file interface/stlink-v2.cfg -c "transport select hla_jtag" -c "adapter_khz 100" Open On-Chip Debugger 0.10.0-dev-00189-g554313b (2016-01-12-16:26) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html hla_jtag adapter speed: 100 kHz Info : clock speed 100 kHz Error: BUG: current_target out of bounds

[Ссылки]

1. SWJ adapters site:wiki.cuvoodoo.info.

2. Best Quality~ST-Link stlink V2 for STM8S STM8L STM32 Cortex-M0 Cortex-M3 SWIM JTAG SWD interface Programmer site:aliexpress.com.

3. blacksphere/blackmagic site:github. com.

com.

4. blacksphere/blackmagic Supported Hardware site:github.com.

5. Converting an STM32F103 board to a Black Magic Probe site:medium.com.

6. blue pill site:wiki.cuvoodoo.info.

7. Cheap Chinese ST-Link v.2 Programmer converted to Black Magic Probe Debugger site:blog.linuxbits.io.

8. FREE SHIPPING V8 ARM Emulator,supports ARM7,ARM9,ARM11,Cortex-M3 core,ADS,IAR,STM32 Emulator + Adapter converter site:aliexpress.com.

9. OpenOCD: руководство пользователя, начало.

10. UrJTAG: бесплатный инструментарий JTAG.

11. Цоколевка интерфейсов JTAG.

SWD — альтернатива JTAG от ARM — Kudelski Security Research

Для разработчиков встраиваемых систем и аппаратных хакеров JTAG — это стандарт де-факто для отладки и доступа к регистрам микропроцессора. Этот протокол используется уже много лет и используется до сих пор. Его главный недостаток в том, что он использует для работы очень много сигналов (минимум 4 — TCK, TMS, TDI, TDO). Это стало проблемой сейчас, когда устройства становятся все меньше и меньше, а микроконтроллеры с малым количеством контактов доступны.

Его главный недостаток в том, что он использует для работы очень много сигналов (минимум 4 — TCK, TMS, TDI, TDO). Это стало проблемой сейчас, когда устройства становятся все меньше и меньше, а микроконтроллеры с малым количеством контактов доступны.

Чтобы решить эту проблему, ARM создала альтернативный интерфейс отладки под названием SWD (Serial Wire Debug), который использует только два сигнала (SWDCLK и SWDIO). Этот интерфейс и связанный с ним протокол теперь доступны почти во всех процессорах Cortex-[A,R,M].

Интерфейс отладки ARM

Обзор архитектуры

В отличие от JTAG, который объединяет TAP в цепочку, SWD использует шину с именем DAP (порт доступа отладки). На этом DAP есть один ведущий ( DP — порт отладки) и один или несколько подчиненных ()0013 AP — порты доступа), аналогично JTAG TAP. DP связывается с точками доступа с помощью пакетов, содержащих адрес точки доступа.

Подводя итог, внешний отладчик подключается к DAP через DP, используя протокол SWD. В этом техническом документе от ARM представлен хороший обзор архитектуры SWD:

В этом техническом документе от ARM представлен хороший обзор архитектуры SWD:

Порты отладки

Порт отладки — это интерфейс между хостом и DAP. Он также обрабатывает интерфейс хоста. Для доступа к DAP доступны три различных порта отладки:

- Порт отладки JTAG (JTAG-DP) . Этот порт использует стандартный интерфейс и протокол JTAG для доступа к DAP .

- Последовательный проводной порт отладки (SW-DP) . Этот порт использует протокол SWD для доступа к DAP.

- Последовательный провод/порт отладки JTAG (SWJ-DP) . Этот порт может использовать JTAG или SWD для доступа к DAP. Это общий интерфейс, используемый во многих микроконтроллерах. Он повторно использует сигналы TMS и TCK JTAG для передачи сигналов SWDIO и SWDCLK соответственно. Для переключения с одного интерфейса на другой необходимо отправить определенную последовательность.

Порты доступа

К DAP можно добавить несколько точек доступа, в зависимости от потребностей. ARM предоставляет спецификации для двух точек доступа:

ARM предоставляет спецификации для двух точек доступа:

- Порт доступа к памяти (MEM-AP) . Эта точка доступа обеспечивает доступ к основной памяти и регистрам.

- Порт доступа JTAG (JTAG-AP) . Эта точка доступа позволяет подключить цепочку JTAG к DAP.

Протокол SWD

Сигнализация

Как было сказано ранее, SWD использует только два сигнала:

- SWDCLK . Тактовый сигнал, отправленный хостом. Поскольку нет никакой связи между тактовой частотой процессора и тактовой частотой SWD, выбор частоты зависит от интерфейса хоста. В этой статье базы знаний максимальная тактовая частота отладки составляет около 60 МГц, но на практике она меняется.

- SWDIO . Это двунаправленный сигнал, передающий данные от/к DP. Данные устанавливаются хостом во время переднего фронта и отбираются DP во время заднего фронта сигнала SWDCLK.

Обе линии должны быть натянуты на цель.

Транзакции

Каждая транзакция SWD состоит из трех фаз:

- Фаза запроса. 8 бит, отправленных с хоста.

- Фаза подтверждения. 3 бита отправлено от цели.

- Фаза данных. От/на хост отправляется до 32 битов с нечетным битом четности.

Обратите внимание, что цикл Trn должен быть отправлен, когда направление данных должно измениться.

Передача SWDЗапрос

Заголовок запроса содержит следующие поля:

| Поле | Описание |

| Старт | Стартовый бит. Должно быть 1 |

| АПнДП | Доступ к DP(0) или AP(1) |

| РНВ | Запрос на запись(0) или чтение(1) |

| А[2:3] | Биты адреса регистра AP или DP [2:3] |

| Контроль четности | Нечетность по четности (APnDP, RnW, A[2:3]) |

| Стоп | Стоповый бит. Должно быть 0 Должно быть 0 |

| Парк | Бит парковки отправлен перед изменением SWDIO на открытый сток. Должно быть 1 |

ACK

Биты ACK содержат статус ACK заголовка запроса. Обратите внимание, что сначала должны быть прочитаны три бита LSB.

| Бит | Описание |

| 2 | OK ответ. Операция прошла успешно |

| 1 | ЖДИТЕ ответа. Хост должен повторить запрос. |

| 0 | Реакция на ОШИБКУ. Произошла ошибка |

Данные

Данные отправляются либо хостом, либо целью. Он отправляется первым LSB и заканчивается нечетным битом четности.

Протокол взаимодействия

Теперь, когда мы знаем больше о низкоуровневой части протокола, пришло время взаимодействовать с реальной целью. Для этого я использовал Hydrabus, но это также можно сделать с помощью Bus Pirate или любого другого подобного инструмента. В ходе этого эксперимента я использовал отладочную плату STM32F103, получившую прозвище Blue Pill . Он легко доступен и уже имеет разъем SWD.

В ходе этого эксперимента я использовал отладочную плату STM32F103, получившую прозвище Blue Pill . Он легко доступен и уже имеет разъем SWD.

Документ спецификации архитектуры интерфейса отладки ARM содержит все детали, необходимые для взаимодействия с интерфейсом SWD, так что давайте начнем.

Инициализация SWD

Поскольку цель использует интерфейс SWJ-DP, ее необходимо переключить из режима JTAG по умолчанию в режим SWD. В главе 5.2.1 документа показана последовательность, которая должна быть отправлена для переключения с JTAG на SWD:

1. Отправьте не менее 50 циклов SWCLKTCK с SWDIOTMS HIGH. Это гарантирует, что текущий интерфейс находится в состоянии сброса. Интерфейс JTAG обнаруживает только 16-битную последовательность JTAG-to-SWD, начиная с состояния Test-Logic-Reset.

2. Отправьте 16-битную последовательность выбора JTAG-to-SWD на SWDIOTMS.

3. Отправьте не менее 50 циклов SWCLKTCK с SWDIOTMS HIGH. Это гарантирует, что, если SWJ-DP уже был в режиме SWD перед отправкой последовательности выбора, интерфейс SWD войдет в состояние сброса линии.

Последовательность 0b0111 1001 1110 0111 (0x79e7) сначала MSB, нам нужно использовать 0x7b 0x9e в формате LSB-first.

импорт pyHydrabus

г = pyHydrabus.RawWire('/dev/ttyACM0')

r._config = 0xa # Сначала установить GPIO с открытым стоком / LSB

r._configure_port()

r.write(b'\xff\xff\xff\xff\xff\xff\x7b\x9е\xff\xff\xff\xff\xff\xff)

Теперь, когда DP находится в состоянии сброса, мы можем выполнить команду чтения DPIDR , чтобы определить порт отладки. Для этого нам нужно прочитать регистр DP по адресу 0x00

| Старт | АПнДП | РНВ | А[2:3] | Паритет | Стоп | парк | |-------|-------|-----|--------|--------|------|-- ----| | 1 | 0 | 1 | 0 0 | 1 | 0 | 1 | = 0xa5

r.write(b'\x0f\x00\xa5')

статус = 0

для я в диапазоне (3):

статус += ord(r.read_bit())< Следующим шагом является включение домена отладки. Глава 2.4.5 говорит нам, что нам нужно установить CDBGRSTREQ и CDBGRSTACK (биты 28 и 29) в регистре CTRL/STAT (адрес 0x4) DP:

Глава 2.4.5 говорит нам, что нам нужно установить CDBGRSTREQ и CDBGRSTACK (биты 28 и 29) в регистре CTRL/STAT (адрес 0x4) DP:

r.write(b'\x81') # Запись запрос к адресу регистра DP 0x4

для _ в диапазоне (5):

r.read_bit() # Не обращайте внимания на ответ

# Записать 0x00000078-MSB в регистр CTRL/STAT

r.write(b'\x1e\x00\x00\x00\x00')

# Отправляем несколько тактов для синхронизации линии

r.write(b'\x00')

Использование SWD

Теперь, когда домен мощности отладки включен, DAP полностью доступен. В качестве первого процесса обнаружения мы будем запрашивать точку доступа, а затем сканировать все точки доступа в DAP.

Чтение с точки доступа

Чтение с точки доступа всегда выполняется через DP. Чтобы запросить AP, хост должен сообщить DP, чтобы он записал в AP, указанный адресом в DAP. Для чтения данных предыдущей транзакции DP использует специальный регистр RDBUFF (адрес 0xc). Это означает, что правильный метод запроса следующий:

- Запись в регистр DP SELECT , установка полей APSEL и APBANKSEL .

- Считайте регистр DP RDBUFF один раз, чтобы «зафиксировать» последнюю транзакцию.

- Снова прочтите регистр RDBUFF , чтобы считать его фактическое значение.

Регистр SELECT описан в главе 2.3.9, интересные поля отмечены здесь:

| Регистр | Позиция | Описание |

| АПСЕЛ | [31:24] | Выбор адреса точки доступа. На DAP имеется до 255 APS. |

| АПБАНКСЕЛ | [7:4] | Выбирает регистр AP для запроса. В нашем случае мы будем запрашивать регистр IDR , чтобы определить тип AP . |

Одним из интересных регистров AP для чтения является Регистр IDR (адрес 0xf), который содержит идентификационную информацию для этой точки доступа. Код ниже суммирует процедуру чтения IDR точки доступа по адресу 0x0.

ap = 0 # адрес точки доступа

r.write(b'\xb1') # Запись в регистр DR SELECT

для _ в диапазоне (5):

r.read_bit() # Не читать биты состояния

r.write(b'\xf0\x00\x00') # Заполнить APBANKSEL значением 0xf

r.write(ap.to_bytes(1, byteorder="little")) # Заполнить APSEL адресом точки доступа

# Это вычисляет бит четности, который будет отправлен после фазы данных

если (бин (ap). count ('1')% 2) == 0:

r.write(b'\x00')

еще:

r.write(b'\x01')

r.write(b'\x9f') # Чтение RDBUFF из DP

статус = 0

для я в диапазоне (3):

status += ord(r.read_bit())< write(b'\x00')

Сканирование точек доступа

С помощью точно такого же кода мы можем выполнить итерацию по всему адресному пространству и посмотреть, есть ли какие-либо другие точки доступа в DAP:

для точки доступа в диапазоне (0x100):

r.write(b'\x00')

r.write(b'\xb1')

для _ в диапазоне (5):

r.read_bit()

#r.записать(b'\xf0\x00\x00\x00\x00')

r.write(b'\xf0\x00\x00')

r.write(ap.to_bytes(1, порядок байтов="мало"))

если (бин (ap). count ('1')% 2) == 0:

r.write(b'\x00')

еще:

r.write(b'\x01')

r.write(b'\x9ж')

статус = 0

для я в диапазоне (3):

статус += ord(r.read_bit())< from_bytes(r.read(4), byteorder="little"))

если идентификатор != '0x0':

print("AP", hex(ap), idcode)

Запуск сценария показывает, что на шине имеется только одна точка доступа. Согласно документации, это MEM-AP:

> python3 /tmp/swd.py Статус: 0x1 ДПИДР 0x2ba01477 AP 0x0 0x24770011

Отсюда можно отправлять команды MEM-AP для запроса памяти процессора.

Обнаружение выводов SWD

На реальных устройствах не всегда легко определить, какие выводы или контрольные точки используются для интерфейса отладки. Это также верно и для JTAG, поэтому существуют такие инструменты, как JTAGulator. Его цель состоит в том, чтобы обнаружить интерфейсы JTAG, пробуя каждую комбинацию контактов, пока комбинация не вернет действительный IDCODE.

Теперь, когда мы лучше знаем, как инициализируется интерфейс SWD, мы можем сделать примерно то же самое, но для интерфейсов SWD. Идея заключается в следующем:

- Возьмите несколько интересных выводов на целевой доске

- Подключите их к устройству обнаружения SWD

- Выберите два контакта на устройстве обнаружения SWD как SWDCLK и SWDIO

- Отправьте последовательность инициализации SWD.

- Чтение ответа о состоянии и регистра DPIDR

- Если результаты действительны, распечатайте решение

- Если нет действительных результатов, перейдите к шагу 3 и выберите два новых контакта

Этот метод реализован для прошивки Hydrabus и пока приносит положительные результаты. Здесь показан пример сеанса:

> 2-wire Устройство: двухпроводное1 Резистор GPIO: плавающий Частота: 1000000 Гц Порядок битов: сначала MSB twowire1> брут 8 Брутфорс на 8 пинах. Устройство найдено. ИДЕНТИФИКАЦИОННЫЙ КОД: 2BA01477 ЦЛК: PB5 ИО: PB6 двухпроводной 1>

Операция занимает менее двух секунд и надежно обнаруживает интерфейсы SWD на всех протестированных платах.

Выводы

В этом посте мы показали, как устроен интерфейс отладки ARM, и как протокол SWD работает на очень низком уровне. С помощью этой информации можно отправлять запросы к MEM-AP с помощью простого микроконтроллера. Эта часть выходит далеко за рамки этой статьи и не будет здесь рассматриваться. Библиотека PySWD — полезный ресурс для начала взаимодействия с MEM-AP.

Библиотека PySWD — полезный ресурс для начала взаимодействия с MEM-AP.

Мы также показали, как реализовать инструмент обнаружения SWD, чтобы помочь найти порты SWD, аналогично существующим инструментам, используемым для обнаружения JTAG.

Нравится:

Нравится Загрузка...

| Торговая марка | Номер детали |

|---|---|

STA2051,STM32F101C4, STM32F101C6, STM32F101C8, STM32F101CB, STM32F101R4, STM32F101R6, STM32F101R8, STM32F101RB, STM32F101RC, STM32F101RD, STM32F101RE, STM32F101T4, STM32F101T6, STM32F101T8, STM32F101V8, STM32F101VB, STM32F101VC, STM32F101VD, STM32F101VE, STM32F101ZC, STM32F101ZD, STM32F101ZE, STM32F102C4, STM32F102C6 , STM32F102C8, STM32F102CB, STM32F102R4, STM32F102R6, STM32F102R8, STM32F102RB, STM32F103C4, STM32F103C6, STM32F103C8, STM32F103CB, STM32F103R4, STM32F103R6, STM32F103R8, STM32F103RB, STM32F103RC, STM32F103RD, STM32F103RE, STM32F103T4, STM32F103T6, STM32F103T8, STM32F103V8, STM32F103VB, STM32F103VC, STM32F103VD, STM32F103VE .

|