Как работает компаратор на логических элементах. Какие бывают схемы компараторов на логических элементах. Где применяются компараторы на логических элементах. Каковы преимущества и недостатки компараторов на логических элементах.

Что такое компаратор на логических элементах

Компаратор на логических элементах — это устройство для сравнения двух аналоговых сигналов, построенное на базе цифровых логических элементов. Его основная функция — определить, какой из двух входных сигналов больше, и выдать соответствующий логический уровень на выходе.

Ключевые особенности компаратора на логических элементах:

- Использует цифровые логические элементы (И, ИЛИ, НЕ и др.) вместо аналоговых схем

- Имеет два аналоговых входа для сравниваемых сигналов

- Выход — цифровой логический сигнал

- Простая схемотехника

- Совместимость с цифровыми устройствами

Принцип работы компаратора на логических элементах

Принцип работы компаратора на логических элементах основан на преобразовании аналоговых сигналов в цифровые с помощью пороговых устройств и последующем логическом сравнении. Рассмотрим основные этапы:

- Входные аналоговые сигналы подаются на пороговые устройства

- Пороговые устройства преобразуют аналоговые сигналы в цифровые уровни

- Цифровые сигналы поступают на логические элементы

- Логические элементы выполняют операцию сравнения

- На выходе формируется логический уровень, соответствующий результату сравнения

Таким образом, компаратор определяет, какой из входных сигналов больше, и выдает соответствующий логический уровень на выходе.

Основные схемы компараторов на логических элементах

Существует несколько базовых схем компараторов на логических элементах:

1. Компаратор на двух инверторах

Простейшая схема компаратора использует два логических инвертора:

- Первый инвертор преобразует входной сигнал в цифровой

- Второй инвертор формирует выходной сигнал

- Порог срабатывания определяется характеристиками инверторов

2. Компаратор с гистерезисом на элементах И-НЕ

Более сложная схема с положительной обратной связью:

- Использует элементы И-НЕ

- Обеспечивает гистерезис для повышения помехоустойчивости

- Пороги переключения можно регулировать

3. Компаратор на RS-триггере

Схема на основе RS-триггера:

- Обеспечивает четкое переключение состояний

- Имеет раздельные входы для установки и сброса

- Позволяет реализовать дополнительные функции управления

Преимущества компараторов на логических элементах

Компараторы на логических элементах имеют ряд преимуществ по сравнению с аналоговыми компараторами:

- Простота схемотехники — используются стандартные логические элементы

- Низкая стоимость — не требуются специализированные аналоговые компоненты

- Высокая скорость работы — за счет использования быстродействующих логических элементов

- Совместимость с цифровыми устройствами — выходные уровни соответствуют логическим стандартам

- Возможность реализации сложных функций сравнения

- Низкое энергопотребление — особенно при использовании КМОП-логики

Недостатки компараторов на логических элементах

Однако у компараторов на логических элементах есть и некоторые недостатки:

- Ограниченная точность сравнения — определяется порогами логических элементов

- Чувствительность к помехам — требуются дополнительные меры для повышения помехоустойчивости

- Ограниченный диапазон входных напряжений — обычно не превышает напряжение питания логики

- Сложность реализации прецизионного сравнения — требуются дополнительные схемы

- Возможны ложные срабатывания при медленно меняющихся сигналах

Применение компараторов на логических элементах

Компараторы на логических элементах находят широкое применение в различных областях электроники:

1. Измерительная техника

- Детекторы уровня сигнала

- Пороговые устройства в измерительных приборах

- Преобразователи аналоговых сигналов в цифровые

2. Системы автоматики

- Контроллеры температуры и влажности

- Датчики предельных значений

- Системы защиты от перегрузок

3. Цифровая обработка сигналов

- Аналого-цифровые преобразователи

- Устройства выборки-хранения

- Схемы синхронизации

4. Силовая электроника

- Системы управления импульсными преобразователями

- Защита от перенапряжений и перегрузок

- Драйверы силовых ключей

Как выбрать компаратор на логических элементах

При выборе компаратора на логических элементах следует учитывать несколько ключевых факторов:

- Требуемая точность сравнения

- Диапазон входных напряжений

- Быстродействие схемы

- Помехоустойчивость

- Совместимость с другими элементами схемы

- Энергопотребление

- Стоимость реализации

Выбор конкретной схемы компаратора зависит от специфики применения и требований к устройству.

Перспективы развития компараторов на логических элементах

Компараторы на логических элементах продолжают развиваться и совершенствоваться. Основные направления развития включают:

- Повышение точности сравнения

- Увеличение быстродействия

- Снижение энергопотребления

- Интеграция с цифровыми системами обработки сигналов

- Разработка новых схемотехнических решений

- Применение программируемых логических интегральных схем (ПЛИС) для реализации компараторов

Эти направления позволят расширить области применения компараторов на логических элементах и повысить их эффективность.

Сумматоры и цифровые компараторы: принцип работы, схемы

Сумматоры — это комбинационные устройства, предназначенные для сложения чисел. Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значения входных чисел А и В, значение результата суммирования S и значение переноса в старший разряд P (см. рис. 3.48).

Сумматоры — это комбинационные устройства, предназначенные для сложения чисел. Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значения входных чисел А и В, значение результата суммирования S и значение переноса в старший разряд P (см. рис. 3.48).

Цифровые сумматоры

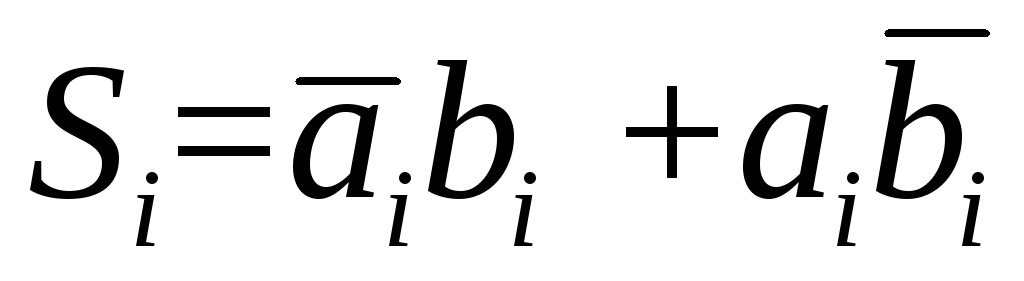

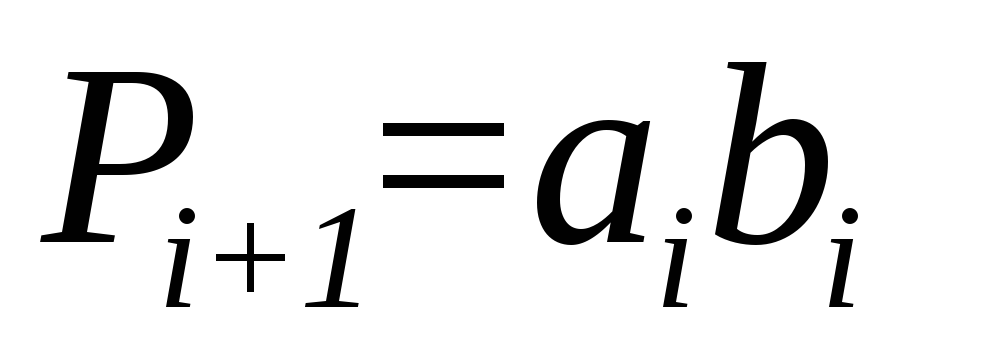

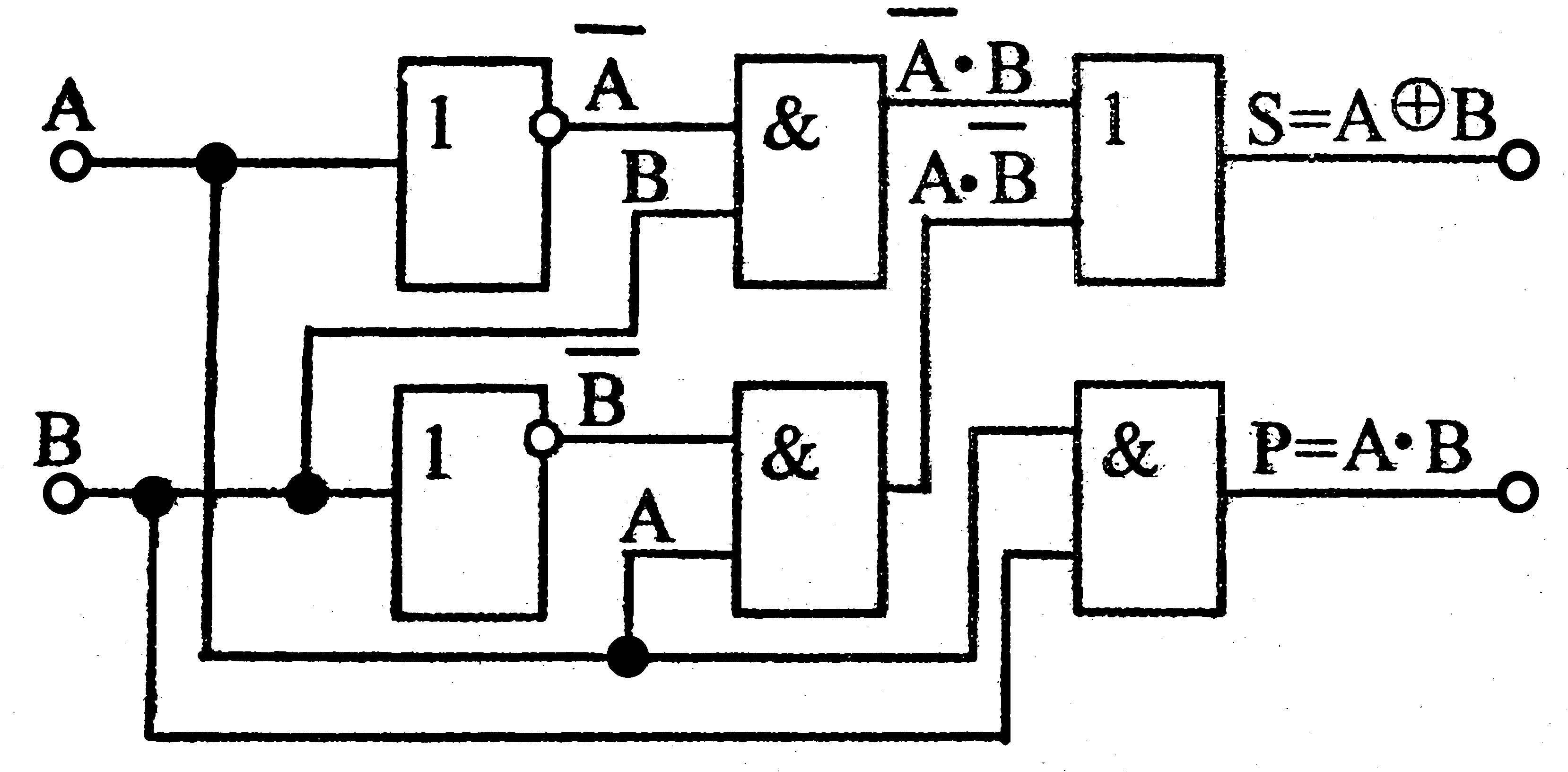

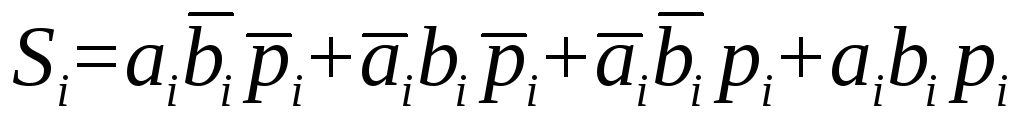

Работа устройства, реализующего таблицу истинность (рис. 3.48), описывается следующими уравнениями

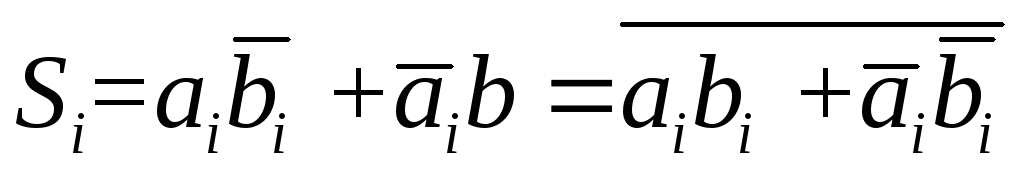

S = А·В + А·В

Р = А·В

Очевидно, что по отношении: к столбцу S реализуется логическая функция «исключающее ИЛИ», т. е. S = А + В. Устройство, реализующее таблицу (рис. 3.48), называют полусумматором, и оно имеет логическую структуру, изображенную на рис. 3.49.

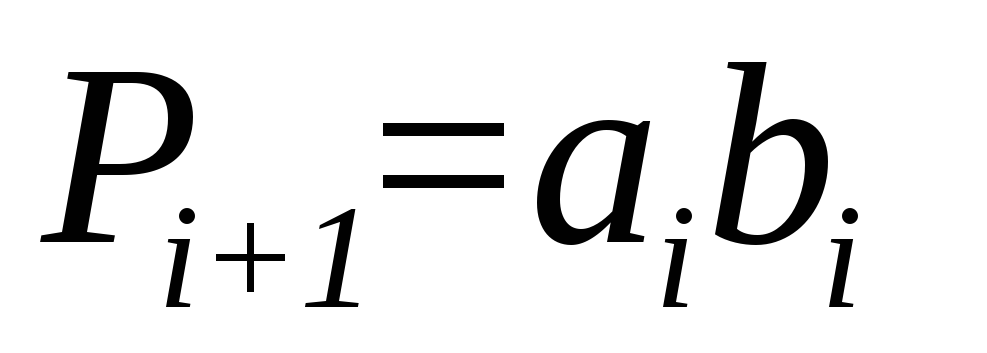

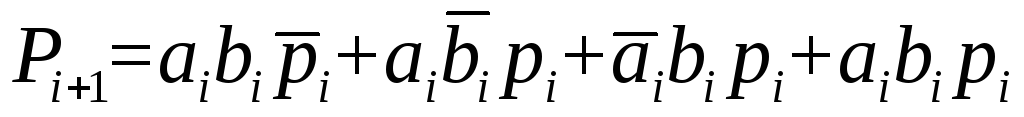

Поскольку полусумматор имеет только два входа, он может использоваться для суммирования лишь в младшем разряде.

При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса. Такое устройство (рис. 3.50) называют полным сумматором и его можно представить как объединение двух полусумматоров (Рвх — дополнительный вход переноса). Сумматор обозначают через SM.

Цифровые компараторы

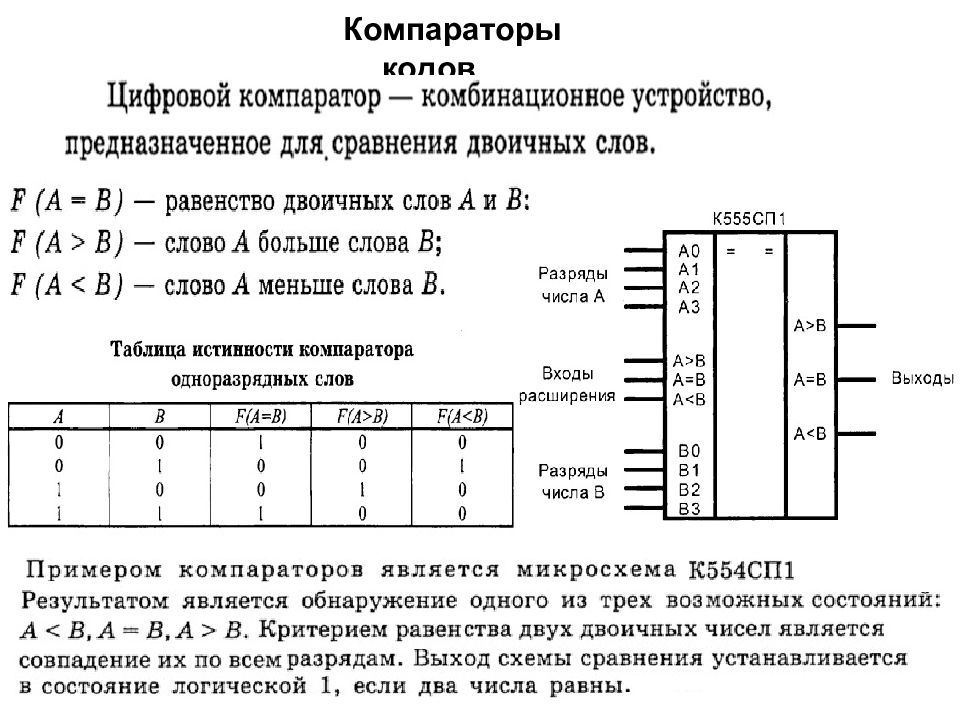

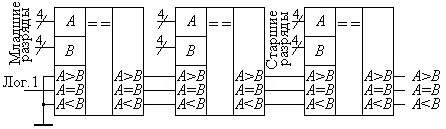

Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел A и B с одинаковым количеством разрядов либо вид неравенства A> B или A < B. Цифровые компараторы имеют три выхода.

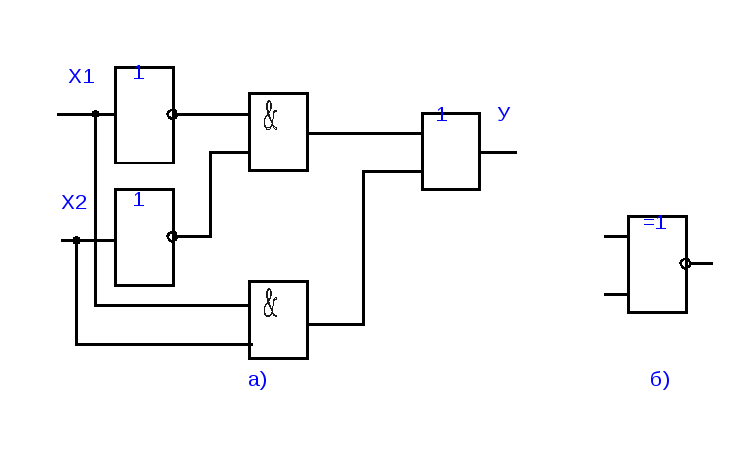

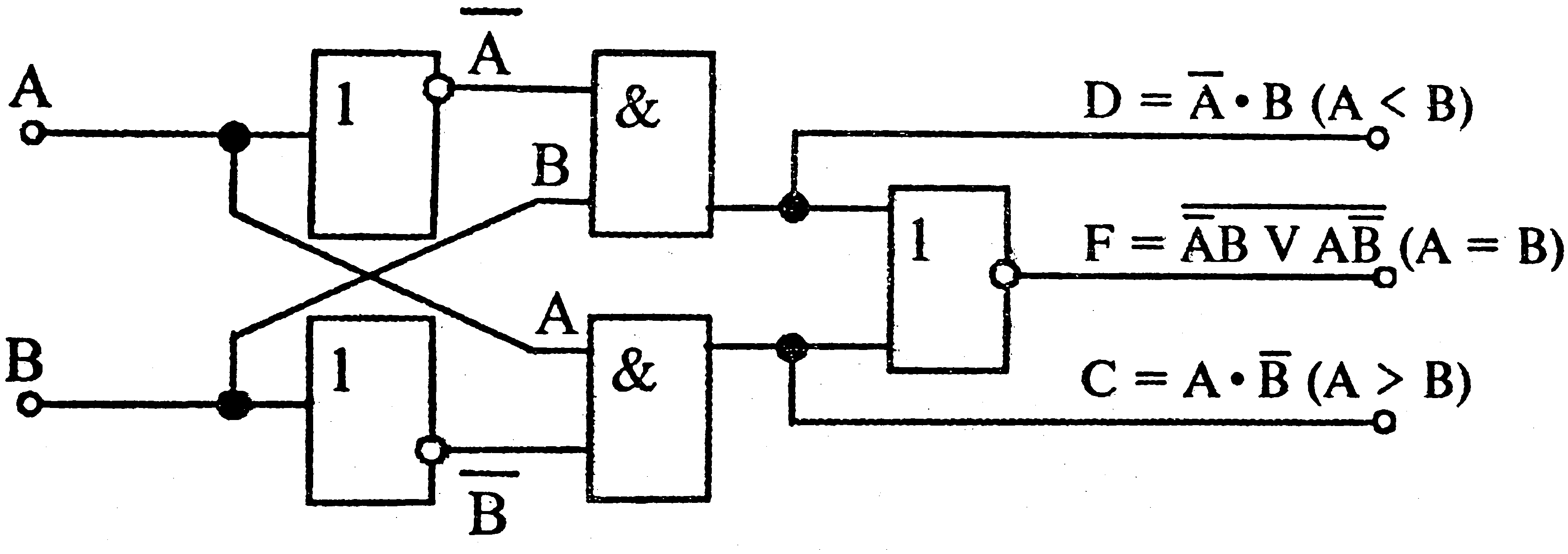

Схема одноразрядного компаратора представляет собой структуру логического элемента «исключающее ИЛИ-НЕ» (рис. 3.51).

Из анализа схемы следует, что если A= B, то F = 1, в противном случае, т. е. при А ≠ В, F = 0. Если А > В, т. е. А = 1, В = 0, то С = 1, а если А < В, т. е. А = 0, В = 1, то D = l.

Если попарно равны между собой все разряды двух n-разрядных двоичных чисел, то равны и эти два числа А и В. Применяя цифровой компаратор для каждого разряда, например, четырехзначных чисел, и определяя значения F1, F2, F3, F4 логических переменных на выходах компараторов, факт равенства А = В установим в случае, когда F = F1 · F2 · F3 · F4 = 1. Если же F = 0, то А ≠ В.

Неравенство А > В обеспечивается (для четырехразрядного числа) в четырех случаях: или А4 > В4, или А4 = В4 и А3 > В3, или А4 = В4, А3 = В3 и А2 > В2, или А4 = В4, А3 = В3, А2 = В2 и A1 > В1 (где А4 и В4 — старшие разряды чисел А и В). Очевидно, что если поменять местами А1 и B1, то будет выполняться неравенство А < В.

Цифровые компараторы выпускают, как правило, в виде самостоятельных микросхем. Так, микросхема К564ИП2 (рис. 3.52) является четырехразрядным компаратором, в котором каждый из одноразрядных компараторов аналогичен рассмотренной ранее схеме. Данная микросхема имеет расширяющие входы А < В, А = В, А > В, что позволяет наращивать разрядность обоих чисел. Для этого компараторы соединяют каскадно или параллельно (пирамидально).

Рассмотрим каскадное соединение компараторов К564ИП2 для сравнения двух восьмиразрядных чисел (рис. 3.53). При этом соединении выходы А = В и А < В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А < В, А = В, А > В микросхемы младших разрядов подают соответственно потенциалы U0 и U1 (U0 соответствует логическому 0, a U1 — «1»). В последующих микросхемах на входах А > В поддерживают потенциал логической единицы U1.

Рассмотрим каскадное соединение компараторов К564ИП2 для сравнения двух восьмиразрядных чисел (рис. 3.53). При этом соединении выходы А = В и А < В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А < В, А = В, А > В микросхемы младших разрядов подают соответственно потенциалы U0 и U1 (U0 соответствует логическому 0, a U1 — «1»). В последующих микросхемах на входах А > В поддерживают потенциал логической единицы U1.

pue8.ru

Компаратор схема на логических элементах

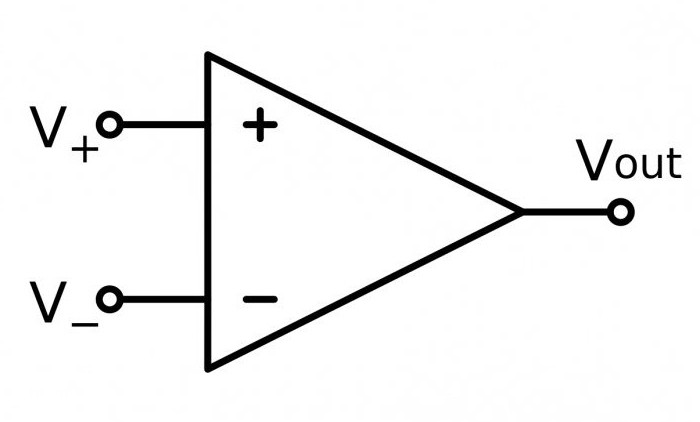

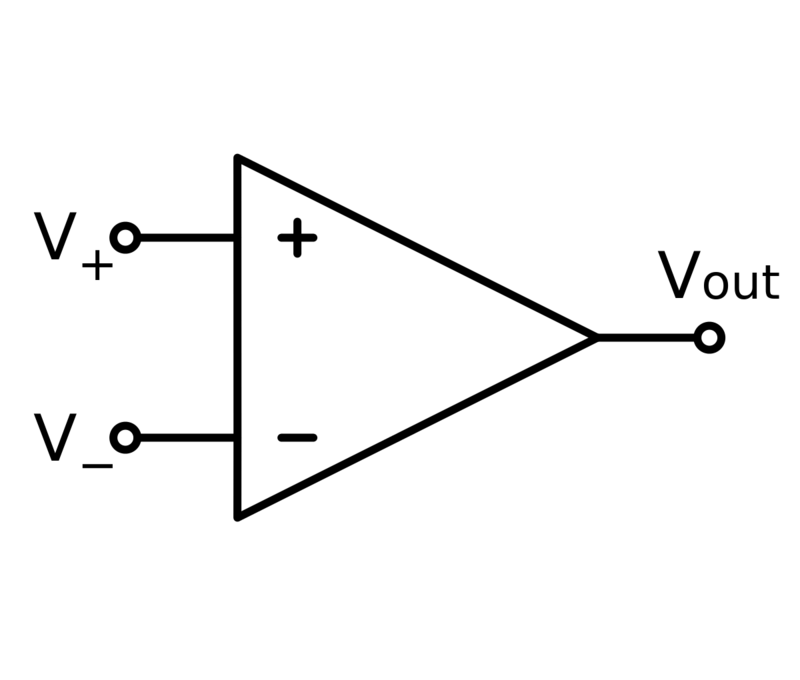

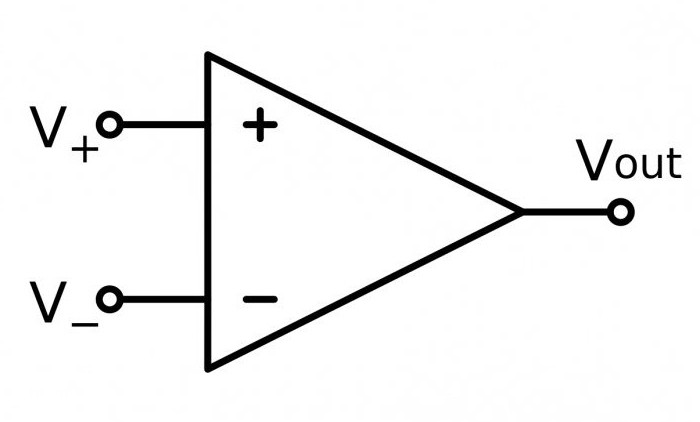

Компаратор – это устройство, предназначенное для сравнения каких-либо величин (от лат. comparare – «сравнивать»). Является операционным усилителем с большим коэффициентом умножения. Имеет входы: прямой и инверсный. При необходимости опорный сигнал может быть подключен к любому из них.

Как работает компаратор?

На один из входов подается постоянный сигнал, который называется опорным. Он используется как образец для сравнения. Ко второму поступает испытуемый сигнал. На выходе стоит транзистор, меняющий свое состояние в зависимости от условий:

- Напряжение прямого входа выше инверсного – транзистор открыт.

- Напряжение инверсного входа выше прямого – закрыт.

Соответственно, выходное напряжение меняется скачком от минимума до максимума, или наоборот.

Напряжение выходных каскадов соответствует входным уровням большинства цифровых микросхем. Это необходимо для случаев, когда компаратор – это формирователь импульса, управляющего работой логических элементов.

Применение компаратора

Используются в схемах измерения электрических сигналов и в аналогово-цифровых преобразователях. В логических цепях работают элементы «или» и «не», также являющиеся компараторами. Соответственно, использование этого компонента не ограничивается конкретными примерами, поскольку он применяется повсеместно.

Стоит отметить, что устройство сравнения можно сделать из любого операционного усилителя, но не наоборот. Коэффициент усиления компаратора достаточно высок. Соответственно, его входы очень чувствительны к разнице напряжений между ними. Расхождение в несколько милливольт значительно изменяет напряжение выхода.

Таким образом, компаратор позволяет наблюдать минимальные колебания уровней входных напряжений. Это делает его незаменимым элементом схем сравнения и измерительных приборов высокой точности:

- индикаторы уровня входящего сигнала;

- металлоискатели;

- микро- и милливольтметры;

- детекторы электромагнитных излучений;

- лабораторные датчики;

- компараторы массы;

- газоанализаторы.

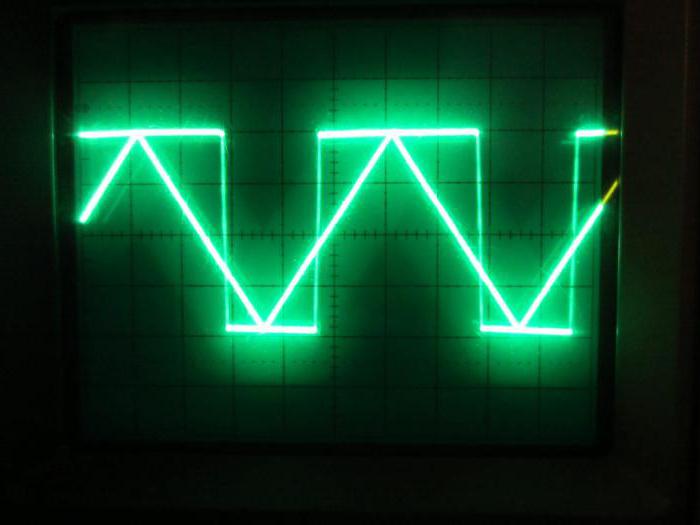

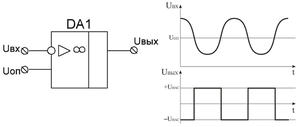

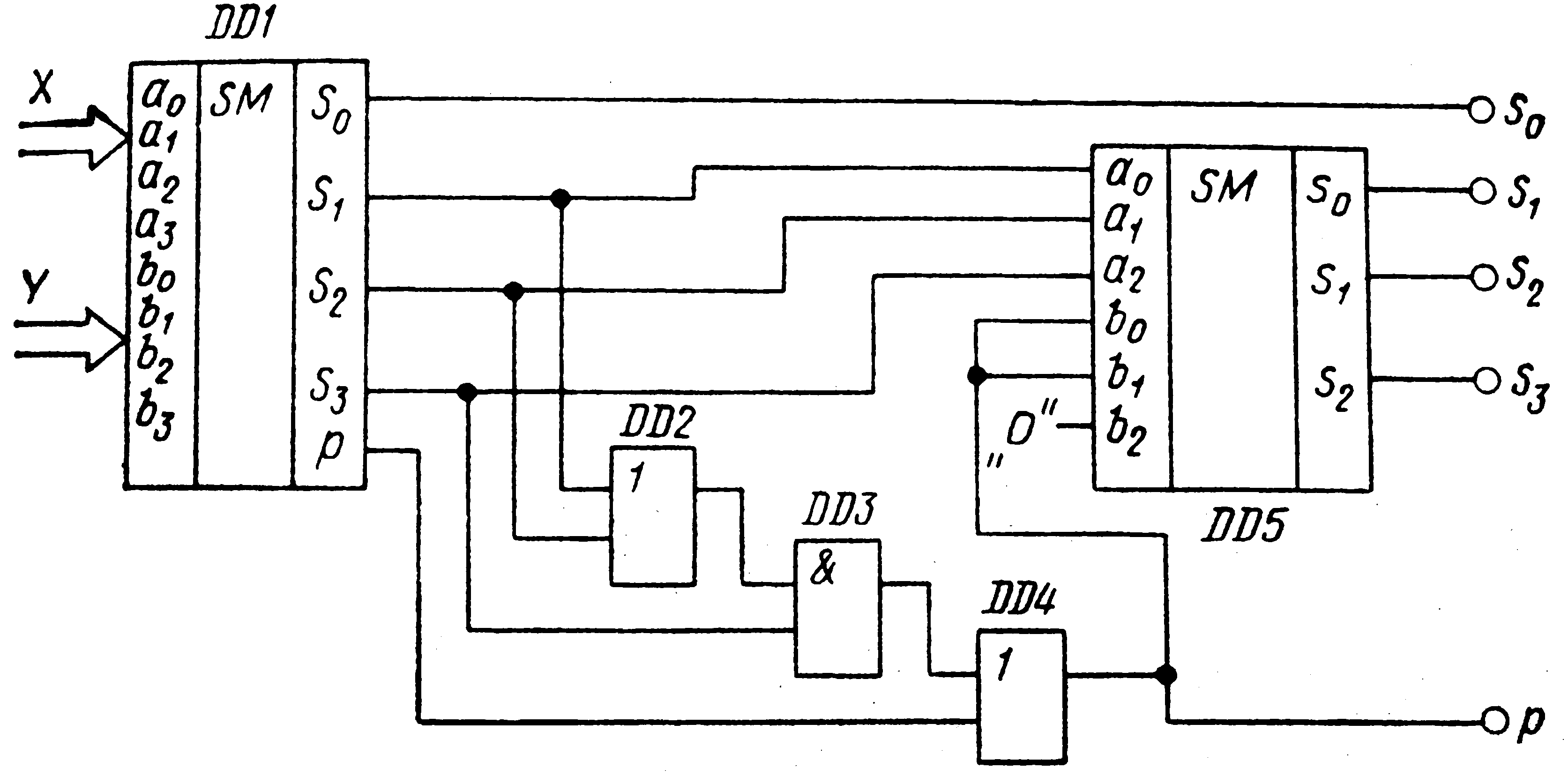

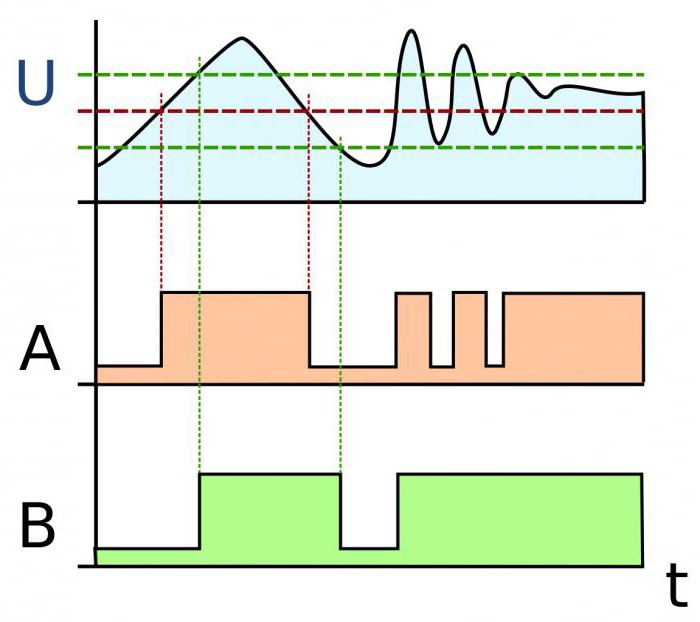

Принцип действия аналогового компаратора

Аналоговый компаратор сравнивает непрерывные сигналы – входной измеряемый и входной опорный. Как работает устройство, показано на графике ниже.

При медленном изменении входного сигнала, происходит многократное переключение компаратора за малый отрезок времени. Такое явление называют «электронным дребезгом». Его наличие значительно снижает эффективность сравнения. Поскольку часто повторяющиеся смены состояния выхода, вводят оконечный транзистор в состояние насыщения.

Для уменьшения эффекта «электронного дребезга», в схему вводят ПОС – положительную обратную связь. Она обеспечивает гистерезис – небольшую разницу между уровнем напряжения включения и отключения. Некоторые компараторы имеют встроенную ПОС, что уменьшает количество дополнительных элементов построения конструкции. Например, при незначительной потери чувствительности, добиваются стабильной работы компаратора.

Особенности цифрового компаратора

Цифровой компаратор – это однобитный аналогово-цифровой преобразователь. Напряжение выхода представляет либо логический «0», либо «1». На вход может быть подан как аналоговый, так и цифровой сигнал. Устройство используется в качестве формирователя импульсов для сопряжения схем датчиков и устройств отображения. Может применяться для анализа спектра звукового или светового сигнала. Компаратор – это также логические элементы «или» и «не», используемые в вычислительной технике.

Теоретически при незначительно малых колебаниях уровня входного сигнала, может возникать состояние неопределенности выхода. На практике равенство измеряемого и опорного напряжений не наступает. Поскольку компаратор имеет ограниченный коэффициент усиления или положительную обратную связь.

Характерным примером является триггер Шмитта (ТШ). У него не совпадают уровни включения и выключения, что определяется ПОС. Это позволяет пренебречь дискретной помехой при работе компаратора.

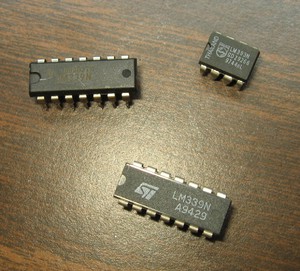

Компаратор-микросхема

Промышленность выпускает компараторы в виде интегральных схем. Их использование позволяет создавать компактные приборы, с минимумом навесных элементов. Также преимущество малогабаритных деталей в незначительной длине соединительных проводников. В условиях повышенного электромагнитного излучения они являются приемными антеннами для всевозможных электрических помех.

Компаратор на операционном усилителе

У компараторов есть немалое сходство с операционными усилителями:

- коэффициент усиления;

- входное сопротивление;

- значение входных токов;

- состояние насыщения.

Чувствительность, по-другому разрешающая способность, – это специфический параметр. Она определяет точность сравнения. Характеризуется минимальной разностью сигналов, при которой происходит срабатывание компаратора. Ее значение у интегральных микросхем имеет сотен микровольт. Это несколько хуже, чем у компараторов на операционных усилителях.

Время переключения характеризует быстродействие компараторов. Определяется минимальным временем изменения выходного сигнала: от момента сравнения до момента срабатывания. Зависит от разности сигналов на входах. Значения времени переключения составляют десятки и сотни наносекунд.

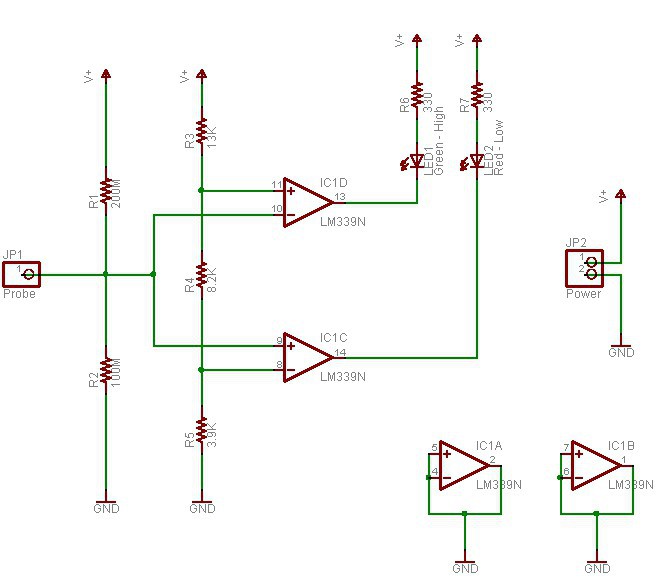

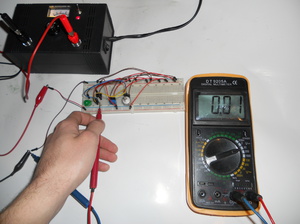

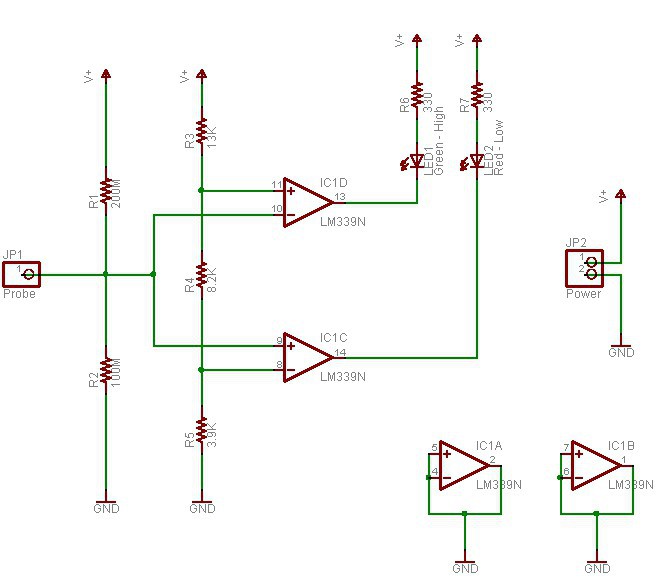

Как сделать компаратор своими руками?

Кто умеет читать принципиальные схемы и паять, без труда соберет простейшие компараторы для использования в быту. Область применения весьма обширна. На них можно построить массу конструкций с минимальными затратами. Простейший компаратор – это операционный усилитель без положительной обратной связи.

В качестве основы для компаратора используется ОУ серии LM339. Для контроля и наглядности работы схемы введены красный и зеленый индикаторы. При подключении питания на ОУ должен засветиться один из светодиодов, причем какой из них — неважно. Это определяется множеством факторов: сетевые наводки на схему, особенности партии и параметров ОУ. Даже если взять несколько одинаковых микросхем, получатся различные результаты.

Если входной сигнал близок к «0» – будет светиться зеленый, а если близкое к напряжению питания, то красный светодиод. Затем можно попробовать сменить логическое состояние компаратора, подав на один из входов напряжение равное, например, половине напряжения питания ОУ. Сигнал на выходе не зависит от абсолютного значения напряжений на прямом и инверсном входе. А только от разницы напряжений.

Данные опыты демонстрируют работу компаратора без ПОС. Такой компаратор может быть использован там, где не требуется особой точности измерений. Такими приборами являются бытовые термостаты, зарядные устройства для автомобильных аккумуляторов, устройства десульфатации (восстановления) автоаккумуляторов, фотореле.

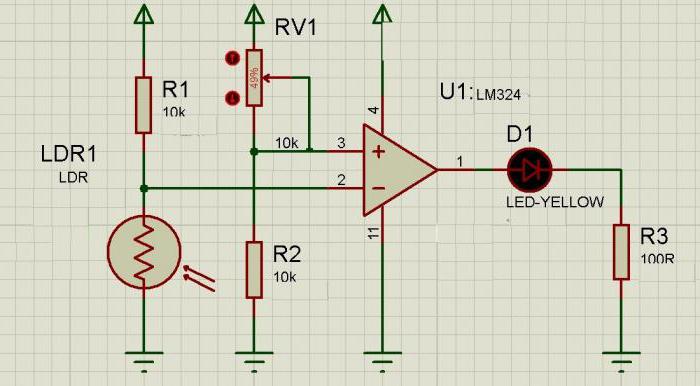

Пример практического применения компаратора

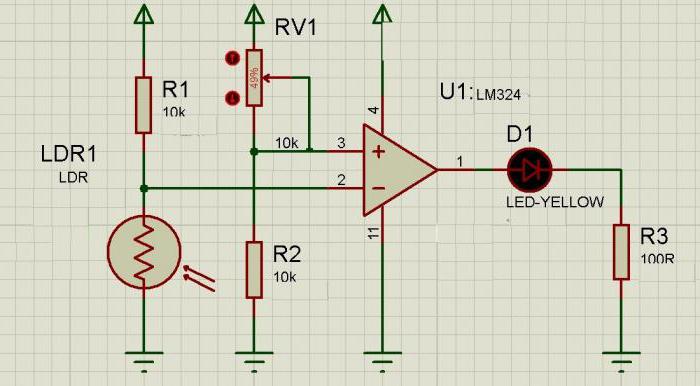

На принципиальной схеме представлен датчик освещенности.

Опорное напряжение задается резисторами RV1 и R2. При этом, RV1 служит регулятором чувствительности конструкции. Индикация реализована на светодиоде D1. Датчиком является элемент LDR1, который меняет омическое сопротивление в зависимости от освещенности. Собственно компаратор представлен операционным усилителем LM324. Это простое устройство демонстрирует то, как работает компаратор на практике.

Компараторы массы: понятие

Компаратор массы это устройство, предназначенное для уточнения разности значений массы гирь при контроле стандартов массы и веса, а также, для прецизионного взвешивания. Наиболее точные компараторы массы способны взвесить любой образец и сравнить его с иным, подобным ему. Происходит это на уровне атомов. Необходимость в таких устройствах возникает по причине несовершенства эталонных образцов мер веса и объема жидкости.

Примеры и использование устройств уточнения веса

Российским стандартом массы является платиновый цилиндр. Он был скопирован с французского образца 125 лет назад. За прошедшие годы, эталон потерял в виде окислов около 40 мкг от первоначального веса. Соответственно, его использование для нужд производств, с высокой точностью измерения массы сейчас затруднительно.

Был разработан новый стандарт массы. Ученые назначили таковым кремниевый шар с четным количеством атомов. Сейчас это наиболее точный вариант эталона килограмма. Его характеристики приняты международным сообществом для использования.

Созданный образец нуждается в многократном копировании. Так как современные направления в науке, особенно фармакология, биоинженерия, компьютерная электроника, нанотехнологические разработки требуют прецизионной точности измерений. Для таких областей науки и техники критичны сотые доли микрограмма. Эту задачу должен решить атомный компаратор массы – устройство способное определить разницу в несколько частиц.

Атомный компаратор использует для измерений опорный сигнал, полученный от высокоточного кварцевого генератора. Измеряемое напряжение берется с квантового дискриминатора, определяющего стабильность линии мельчайших частиц. Ее изменения вызываются расхождением в количестве атомов образца. Поэтому сейчас – это самый точный прибор измерения.

Существуют и менее точные компараторы массы. Их стоимость гораздо ниже атомных, но для них всех находится работа в промышленности, торговле, стандартизации.

Общие сведения

Компаратор — это сравнивающее устройство. Аналоговый компаратор предназначен для сравнения непрерывно изменяющихся сигналов. Входные аналоговые сигналы компаратора суть Uвх — анализируемый сигнал и Uоп — опорный сигнал сравнения, а выходной Uвых — дискретный или логический сигнал, содержащий 1 бит информации:

|

(1) |

Выходной сигнал компаратора почти всегда действует на входы логических цепей и потому согласуется по уровню и мощности с их входами. Таким образом, компаратор — это элемент перехода от аналоговых к цифровым сигналам, поэтому его иногда называют однобитным аналого-цифровым преобразователем.

Неопределенность состояния выхода компаратора при нулевой разности входных сигналов нет необходимости уточнять, так как реальный компаратор всегда имеет либо конечный коэффициент усиления, либо петлю гистерезиса (рис. 1).

Рис. 1. Характеристики компараторов

Рис. 2. Процессы переключения компараторов

Чтобы выходной сигнал компаратора изменился на конечную величину |U 1 вых — U 0 вых| при бесконечно малом изменении входного сигнала, компаратор должен иметь бесконечно большой коэффициент усиления (эпюра 1 на рис. 2) при полном отсутствии шумов во входном сигнале. Такую характеристику можно имитировать двумя способами — или просто использовать усилитель с очень большим коэффициентом усиления, или ввести положительную обратную связь.

Рассмотрим первый путь. Как бы велико усиление не было, при Uвх близком к нулю характеристика будет иметь вид рис. 1а. Это приведет к двум неприятным последствиям. Прежде всего, при очень медленном изменении Uвх выходной сигнал также будет изменяться замедленно, что плохо отразится на работе последующих логических схем (эпюра 2 на рис. 2). Еще хуже то, что при таком медленном изменении Uвх около нуля выход компаратора может многократно с большой частотой менять свое состояние под действием помех (так называемый «дребезг», эпюра 3). Это приведет к ложным срабатываниям в логических элементах и к огромным динамическим потерям в силовых ключах. Для устранения этого явления обычно вводят положительную обратную связь, которая обеспечивает переходной характеристике компаратора гистерезис (рис. 1б). Наличие гистерезиса хотя и вызывает некоторую задержку в переключении компаратора (эпюра 4 на рис. 2), но существенно уменьшает или даже устраняет дребезг Uвых.

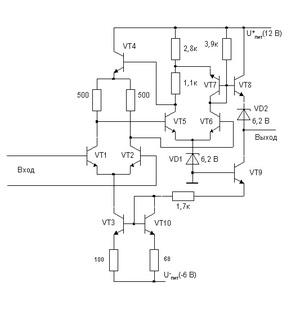

В качестве компаратора может быть использован операционный усилитель (ОУ) так, как это показано на рис. 3. Усилитель включен по схеме инвертирующего сумматора, однако, вместо резистора в цепи обратной связи включены параллельно стабилитрон VD1 и диод VD2.

Рис. 3. Схема компаратора на ОУ

Пусть R1 = R2. Если Uвх — Uоп > 0, то диод VD2 открыт и выходное напряжение схемы небольшое отрицательное, равное падению напряжения на открытом диоде. При Uвх — Uоп m А710 (отечественный аналог — 521СА2), разработанного Р. Видларом (R.J.Widlar) в США в 1965 г., приведена на рис. 4.

Рис. 4. Схема компаратора m А710

Она представляет собой дифференциальный усилитель на транзисторах VT1, VT2, нагруженный на каскады ОЭ на VT5 и VT6. Каскад на VT5 через транзистор VТ4 управляет коллекторным режимом входного каскада и через транзистор в диодном включении VТ7 фиксирует потенциал базы транзистора VT8, делая его независимым от изменений положительного напряжения питания. Каскад на VT6 представляет собой второй каскад усиления напряжения.

Эмиттерные выводы транзисторов VT5 и VT6 присоединены к стабилитрону VD1 с напряжением стабилизации 6,2 В, поэтому потенциалы баз указанных транзисторов соответствуют приблизительно 6,9 В. Следовательно, допустимое напряжение на входах компаратора относительно общей точки может достигать 7 В. На транзисторе VT8 выполнен эмиттерный повторитель, передающий сигнал с коллектора VT6 на выход. Постоянная составляющая сигнала уменьшается до нулевого уровня стабилитроном VD2.

Если дифференциальное входное напряжение превышает +5. +10 мВ, то транзистор VT6 закрыт, а VT5 близок к насыщению. Выходной сигнал компаратора при этом не может превысить +4 В, так как для более положительных сигналов открывается диод на VT7, не допуская излишнего роста выходного напряжения и насыщения VТ5. При обратном знаке входного напряжения VT6 насыщается, потенциал его коллектора оказывается близок к напряжению стабилизации стабилитронов VD1 и VD2, а поэтому потенциал выхода близок к нулю. Транзистор VT9 — источник тока 3 мА для смещения VT8 и VD2. Часть этого тока (до 1,6 мА) может отдаваться в нагрузку, требующую вытекающий ток на входе (один вход логики ТТЛ серии 155 или 133).

В дальнейшем эта схема развивалась и совершенствовалась. Схемы многих компараторов имеют стробирующий вход для синхронизации, а некоторые модификации снабжены на выходе триггерами-защелками, т.е. схемами, фиксирующими состояние выхода компаратора по приходу синхроимпульса. Кроме того, для повышения функциональной гибкости часть ИМС компараторов (например, МАХ917-920) содержит источник опорного напряжения, а у некоторых (например, МАХ910) порог срабатывания устанавливается цифровым кодом от 0 до 2,56 В с дискретностью 10 мВ , для чего на кристалле микросхемы имеются источник опорного напряжения и 8-разрядный цифро-аналоговый преобразователь.

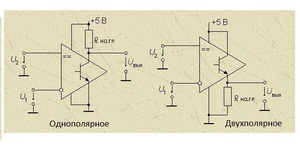

Выходные каскады компараторов обычно обладают большей гибкостью, чем выходные каскады операционных усилителей. В обычном ОУ используют двухтактный выходной каскад, который обеспечивает размах напряжения в пределах между значениями напряжения питания (например, +/-13 В для ОУ типа 140УД7, работающего от источников +/-15 В). В выходном каскаде компаратора эмиттер, как правило, заземлен, и выходной сигнал снимается с «открытого коллектора». Выходные транзисторы некоторых типов компараторов, например, 521СА3 или LM311 имеют открытые, т.е. неподключенные, и коллектор и эмиттер. Две основные схемы включения компараторов такого типа приведены на рис. 5.

Рис. 5. Схемы включения выходного каскада компаратора 521СА3

На рис. 5а выходной транзистор компаратора включен по схеме с общим эмиттером. При потенциале на верхнем выводе резистора равном +5 В к выходу можно подключать входы ТТL, nМОП- и КМОП-логику с питанием от источника 5 В. Для управления КМОП-логикой с более высоким напряжением питания следует верхний вывод резистора подключить к источнику питания данной цифровой микросхемы.

Если требуется изменение выходного напряжения компаратора в пределах от U + пит до U — пит, выходной каскад включается по схеме эмиттерного повторителя (рис. 5б). При этом заметно снижается быстродействие компаратора и происходит инверсия его входов.

Некоторые модели интегральных компараторов (например, AD790, МАХ907) имеют внутреннюю неглубокую положительную обратную связь, обеспечивающую их переходной характеристике гистерезис с шириной петли, соизмеримой с напряжением смещения нуля.

На рис. 6а приведена схема включения компаратора с открытым коллектором на выходе, переходная характеристика которой имеет гистерезис (рис. 1б). Пороговые напряжения этой схемы определяются по формулам

,

,

Из-за несимметрии выхода компаратора петля гистерезиса оказывается несимметричной относительно опорного напряжения.

Рис. 6. Компаратор с положительной обратной связью

В заключение, перечислим некоторые особенности компараторов по сравнению с ОУ.

- Несмотря на то, что компараторы очень похожи на операционные усилители, в них почти никогда не используют отрицательную обратную связь, так как в этом случае весьма вероятно (а при наличии внутреннего гистерезиса — гарантировано) самовозбуждение компараторов.

- В связи с тем, что в схеме нет отрицательной обратной связи, напряжения на входах компаратора неодинаковы.

- Из-за отсутствия отрицательной обратной связи входное сопротивление компаратора относительно низко и может меняться при изменении входных сигналов.

- Выходное сопротивление компараторов значительно и различно для разной полярности выходного напряжения.

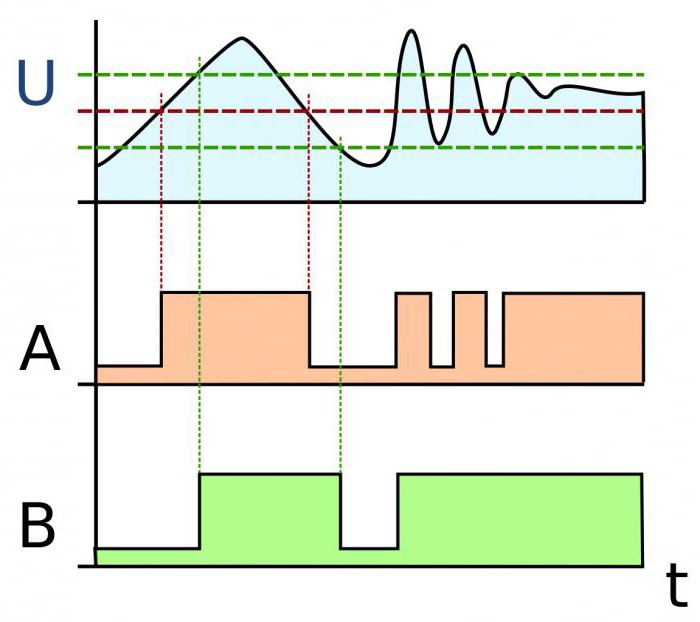

Двухпороговый компаратор

Двухпороговый компаратор (или компаратор «с окном») фиксирует, находится ли входное напряжение между двумя заданными пороговыми напряжениями или вне этого диапазона. Для реализации такой функции выходные сигналы двух компараторов необходимо подвергнуть операции логического умножения (рис. 7а). Как показано на рис. 7б, на выходе логического элемента единичный уровень сигнала будет иметь место тогда, когда выполняется условие U1 m А711 (отечественный аналог — 521СА1).

Рис. 7. Схема двухпорогового компаратора (а) и диаграмма его работы (б)

Параметры компараторов

Параметры, характеризующие качество компараторов, можно разделить на три группы: точностные, динамические и эксплуатационные.

Компаратор характеризуется теми же точностными параметрами, что и ОУ.

Основным динамическим параметром компаратора является время переключения tп. Это промежуток времени от начала сравнения до момента, когда выходное напряжение компаратора достигает противоположного логического уровня. Время переключения замеряется при постоянном опорном напряжении, подаваемом на один из входов компаратора и скачке входного напряжения Uвх, подаваемого на другой вход. Это время зависит от величины превышения Uвх над опорным напряжением. На рис. 8 приведены переходные характеристики компаратора mА710 для различных значений дифференциального входного напряжения Uд при общем скачке входного напряжения в 100 мВ. Время переключения компаратора tп можно разбить на две составляющие: время задержки tз и время нарастания до порога срабатывания логической схемы tн. В справочниках обычно приводится время переключения для значения дифференциального напряжения, равного 5 мВ после скачка.

Рис. 8. Переходная характеристика компаратора m А710 при различных превышениях скачка входного напряжения Uд над опорным: 1 — на 2 мВ; 2 — на 5 мВ; 3 — на 10 мВ; 4 — на 20 мВ

Пороговые устройства, называемые также компараторами, предназначены для преобразования аналогового сигнала в цифровую информацию. Например, на выходе порогового элемента формируется сигнал какого-либо логического уровня, если входной аналоговый сигнал по своему значению меньше определенного напряжения, если же он больше, то на выходе порогового устройства формируется сигнал противоположного логического уровня.

Кроме регистрации или сигнализации о превышении (или снижении) напряжения контролируемого сигнала, пороговые устройства применяют в аналого-цифровых преобразователях, генераторах импульсов различной формы.

В составе некоторых серий аналоговых микросхем есть компараторы, пригодные для совместной работы с цифровыми микросхемами, но они не всегда доступны. Многие из них требуют двухполярного источника питания, что усложняет конструкцию. Поэтому в ряде случаев оказывается целесообразным использовать в качестве пороговых устройств элементы, что обеспечивает полное согласование логических уровней без каких-либо специальных мер.

В принципе, сам элемент представляет собой пороговое устройство, в чем легко убедиться, взглянув на рис. 18, на котором показаны передаточные характеристики идеального порогового устройства 1 и элемента КМОП 2. У идеального порогового устройства прямоугольная характеристика, элемент же имеет характеристику с некоторым наклоном, поэтому вблизи порогового напряжения возникает зона неопределенности, которая в итоге и определяет чувствительность порогового устройства. В тех случаях, когда не требуется высокой точности, в качестве порогового устройства можно использовать логический элемент.

Для повышения точности пороговых устройств на основе элементов применяют специальные схемные решения. Схема простого порогового устройства на двух элементах ТТЛ приведена на рис. 19,а. Благодаря наличию положительной обратной связи (ПОС) по постоянному току через резистор R2 передаточная характеристика становится прямоугольной (рис. 19,6). Устройство работает следующим образом. При входном сигнале меньше порогового на выходе будет напряжение низкого уровня. С увеличением входного напряжения до U2 на выходе элемента DD1.2 напряжение также начнет увеличиваться. Это напряжение через резистор R2 поступит на вход элемента DD1.1, что приведет к еще большему увеличению напряжения на выходе элемента DD1.2 и т. д. Таким образом, пороговое устройство скачком переходит в устойчивое состояние с высоким уровнем напряжения на выходе. Дальнейшее увеличение входного напряжения состояние порогового устройства не изменяет.

Рис. 18. Характеристики порогового устройства и элемента КМОП

При уменьшении входного напряжения до U] пороговое устройство скачком переходит в устойчивое состояние с низким уровнем напряжения на выходе. Разность напряжений U2—U1 называют шириной петли гистерезиса, она зависит от соотношения номиналов резисторов R1 и R2. От этих же резисторов зависит и чувствительность. При увеличении сопротивления резистора R2 и уменьшении R1 чувствительность повышается, а ширина петли гистерезиса уменьшается. Однако элементы ТТЛ работают с входными токами, поэтому сопротивление этих резисторов должны лежать в определенных пределах. Так, для микросхем серий К133 и К155 сопротивление резистора R1 может быть в пределах 0,1 . 2 кОм, a R2 — в пределах 2. 10 кОм.

Такое пороговое устройство не имеет на входе разделительного конденсатора, поэтому нижняя граница его частотной характеристики простирается вплоть до постоянного напряжения, а вот верхняя, из-за наличия к цепи сигнала резистора R1, ограничена частотой 8. 10 МГц.

Если необходимо пороговое устройство, реагирующее только на переменную составляющую сигнала, его следует несколько изменить в соответствии с рис. 20. Сопротивления резисторов R2 и R3 должны быть примерно равны, емкость конденсатора С1 определяет нижнюю частотную границу рабочего диапазона.

Большей граничной частотой обладает пороговое устройство на логических расширителях по ИЛИ микросхемы К155ЛД1 (рис. 21), по схемному построению аналогичное триггеру Шмитта на транзисторах. Порог срабатывания зависит от соотношения номиналов резисторов R1 и R3. Ширина петли гистерезиса составляет около 0,1 В, а порог срабатывания можно регулировать от 0,02 до і В. Номинал резистора SR1! должен быть в пределах 0,(1 . 1 кОм, a R2 — 22.

Рис. 19. Пороговое устройство на элементе ТТЛ

Рис. 20. Принципиальная схема порогового устройства на элементе ТТЛ

Рис. 21. Принципиальная схема порогового устройства на микросхеме К155ЛД1

Недостатком такого устройства является несколько повышенное, чем обычно, напряжение низкого логического уровня, за счет падения напряжения на резисторе R3.

Выполнить пороговый элемент можно и на элементах КМОП (рис. 22). Его отличительной особенностью является экономичность, а недостатком — низкая чувствительность. Поскольку элементы КМОП работают без входных токов и обладают невысокой нагрузочной способностью по току, то сопротивления резисторов R1 и R2 обычіно выбирают большими — десятки и сотни килорм. Для повышения чувствительности устройства на его вход следует подавать начальное смешение от источника питания через делитель R3R4.

При .контроле сигнала, уровень которого может изменяться в больших пределах, например музыкального сигнала, возможна ситуация, когда сигнал на очень короткое время превысит пороговое значение. Хотя устройство и сработает, но этого времени может не хватить, например, для включения индикатора. В таком случае будет полезным пороговое устройство с «памятью» (,рис. 23), которое на определенное время сохранит информацию о том, что сигнал превысил пороговое напряжение или был меньше него. От предыдущего устройства оно отличается тем, что в цепь ПОС между выходом элемента DD1.2 и одним из входов элемента DD1.1 включен конденсатор С2. Как только на выходе элемента DD1.2 появляется напряжение высокого уровня, оно через конденсатор С2 поступает на вход элемента DDL1. В таком состоянии устройство остается до тех пор, пока не зарядится этот конденсатор, даже в том случае, если уровень входного сигнала станет ниже порогового значения. Время, в течение которого информация о превышении сигнала хранится в устройстве, определяется постоянной времени цепи R1C2.

В каких же конструкциях можно применить пороговые устройства? В приборах, сигнализирующих об изменении напряжения, сигнала, в реле времени ^таймеры), различных индикаторах, генераторах и многих других. Цифровые микросхемы широко используют для генерирования сигналов с разными параметрами. Благодаря большому коэффициенту усиления н хорошим частотным свойствам на базе их логических элементов удается реализовать генераторы с частотой от долей герца до десятков и сотен мегагерц, к тому же самой различной формы.

Рис. 22. Принципиальная схема порогового устройства на элементе КМОП

Рис. 23. Принципиальная схема порогового устройства с «памятью»

Литература: И. А. Нечаев, Массовая Радио Библиотека (МРБ), Выпуск 1172, 1992 год.

mytooling.ru

Компараторы цифровых сигналов

Сравнение кодированных сигналов осуществляется с помощью цифровых компараторов. Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном (двоично-десятичном) коде. В зависимости от схемного исполнения компараторы могут определять равенство А = В (А и В – независимые числа с равным количеством разрядов) либо определять вид неравенства: А < В или А > В. Результат сравнения отображается соответствующим логическим уровнем на выходе.

Цифровые компараторы широко применяются для выявления нужного числа (слова) в потоке цифровой информации, для отметки времени в часовых приборах, для выполнения условных переходов в вычислительных устройствах, реализации программно управляемых приоритетов в системах прерывания компьютеров и т. д.

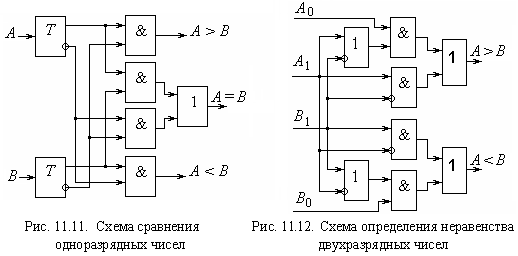

Ниже приведены схемы одноразрядного (рис. 11.11) и двухразрядного компараторов (рис. 11.12).

Рис. 11.11. схема сравнения одноразрядных чисел

Рис. 11.12. схема определения неравенства двухразрядных чисел

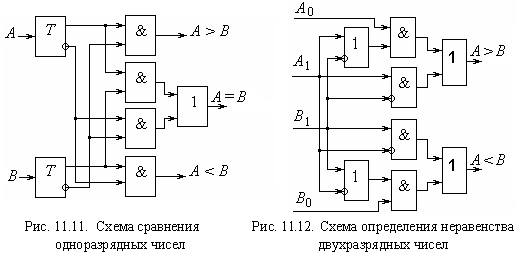

Многоразрядные компараторы строятся на базе одноразрядных. Применяют два способа построения многоразрядных компараторов. При первом способе сравнение идет последовательно разряд за разрядом. При появлении неравенства в каком-либо из разрядов, сравнение прекращается и выдается результат сравнения. Если неравенство оказывается в последнем разряде, то должна быть выполнена операция сравнения для всех разрядов. Это занимает много времени.

Схема сравнения многоразрядных чисел по первому способу представлена на рис. 11.13. Более быстрый способ – сравнение во всех разрядах одновременно и анализ результатов поразрядного сравнения.

Рис. 11.13. Схема сравнения многоразрядных чисел

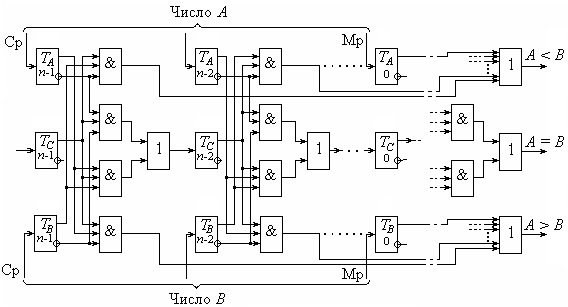

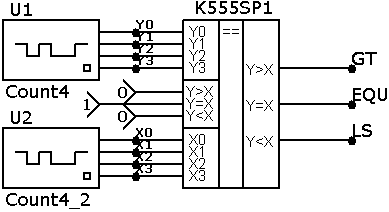

Нашей промышленностью выпускаются компараторы ТТЛ 555СП1, 531СП1, КМОП 561ИП2 и др. Компаратор 555СП1 – четырехразрядный, имеет 11 входов (рис. 11.14). Четыре пары входов принимают для анализа два четырехразрядных слова А0-А3 и В0-В3. Три входа (A < В), (A = В), (A > В) нужны для создания схемы наращивания, т. е. увеличения емкости компаратора. Компаратор имеет три выхода результатов анализа: A > В, A < В, A = В.

Соотношения входных и выходных сигналов компаратора представлены в табл. 11.6. Шесть последних строк таблицы отражают режим наращивания каскадов, который может быть последовательным или параллельным. При последовательном наращивании выходы A > В, A < В, A = В от схемы, анализирующей младшие разряды, следует присоединить к одноименным входам последующего каскада (рис. 11.15). Этим способом при двух компараторах СП1 можно сравнить два восьмиразрядных слова. Нетрудно подсчитать число каскадов для любой большей длины слова. Однако каждый последующий каскад увеличит общее время задержки распространения сигнала на 15 нс.

Рис. 11.14 Условное графическое обозначение микросхемы 555 СП1

Таблица 11.6

|

№ п.п. |

Сравниваемые данные |

Входы наращивания каскадов |

Выходы | |||||||

|

а3, b3 |

а2, b2 |

аb, b1 |

а0, b0 |

A>B |

A<B |

A=B |

A>B |

A<B |

A=B | |

|

1 |

а3>b3 |

X |

X |

X |

X |

X |

X |

1 |

0 |

0 |

|

2 |

а3<b3 |

X |

X |

X |

X |

X |

X |

0 |

1 |

0 |

|

3 |

а3=b3 |

а2>b2 |

X |

X |

X |

X |

X |

1 |

0 |

0 |

|

4 |

а3=b3 |

а2<b2 |

X |

X |

X |

X |

X |

0 |

1 |

0 |

|

5 |

« |

а2=b2 |

a1>b1 |

X |

X |

X |

X |

1 |

0 |

0 |

|

6 |

« |

а2=b2 |

a1<b1 |

X |

X |

X |

X |

0 |

1 |

0 |

|

7 |

« |

« |

a1=b1 |

а0>b0 |

X |

X |

X |

1 |

0 |

0 |

|

8 |

« |

« |

a1=b1 |

а0<b0 |

X |

X |

X |

0 |

1 |

0 |

|

9 |

« |

« |

« |

а0=b0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

10 |

« |

« |

« |

а0=b0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

11 |

« |

« |

« |

« |

0 |

0 |

1 |

0 |

0 |

1 |

|

12 |

« |

« |

« |

« |

X |

X |

1 |

0 |

0 |

1 |

|

13 |

« |

« |

« |

« |

1 |

1 |

0 |

0 |

0 |

0 |

|

14 |

« |

« |

« |

« |

0 |

0 |

0 |

1 |

1 |

1 |

Рис. 11.15. Последовательная схема объединения компараторов

Девятая и десятая строки табл. 11.6 говорят о том, что входы A > В и A < В могут служить пятой парой разрядных входов. Тогда одиночный компаратор можно использовать как пятиразрядный.

При применении компараторов надо учитывать, что при каскадировании задержки микросхем суммируются, и объединенный компаратор, состоящий из n микросхем, будет в n раз медленнее одиночного.

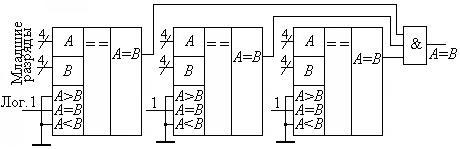

Если важен только факт равенства или неравенства сравниваемых кодов, то увеличить быстродействие при параллельном объединении компараторов можно, путём подачи их выходных сигналов A = В на логический элемент И (рис. 11.16). В этом случае суммарная задержка схемы составит задержку одного компаратора плюс задержку логического элемента И. Более подробные сведения о многокаскадных компараторах можно посмотреть, например, в [9, 11].

Рис. 11.16. Параллельная схема увеличения разрядности для оценки

равенства чисел

Компаратор КМОП серии 561ИП2 имеет несколько отличных режимов работы: например при всех низких уровнях входных сигналов A > В, A = В, A < В выходные A > В, A = В, A < В также низкие (у 555СП1 A > В и A < В высокие), т. е. для анализа работы компаратора надо использовать другую таблицу.

studfile.net

характеристики и описание принципа действия, использование схем сравнения напряжения

В электронных приборах часто можно встретить различные интегральные микросхемы. Одной из них является компаратор. Его применение очень обширно: начиная от сигнализационных датчиков и заканчивая промышленной и автомобильной электроникой. Зная, как работает компаратор, можно самостоятельно собрать различные интересные схемы, например, зарядное устройство, индикаторный узел или даже генератор.

В электронных приборах часто можно встретить различные интегральные микросхемы. Одной из них является компаратор. Его применение очень обширно: начиная от сигнализационных датчиков и заканчивая промышленной и автомобильной электроникой. Зная, как работает компаратор, можно самостоятельно собрать различные интересные схемы, например, зарядное устройство, индикаторный узел или даже генератор.

Описание и схемотехника

Несмотря на кажущуюся простоту, компаратор — куда более интересное устройство, чем может показаться на первый взгляд. В электронике им называют логическую микросхему, предназначенную для сравнения между собой двух электрических сигналов, подающихся на его вход. В зависимости от результатов этого измерения изменяется режим работы прибора.

Термин «компаратор» произошёл от латинского слова «comparare», что дословно переводится на русский язык как сравнивать. Конструктивно устройство может выпускаться в различных корпусах, например, DIP, SOIC, SSOP. Простейшего вида сравнивающий элемент имеет два аналоговых входа и один цифровой выход. В основе его работы лежит дифференциальный каскад, имеющий высокий коэффициент усиления. Поэтому компараторы широко используются в оборудовании, предназначенном для измерения или преобразования аналогового сигнала в цифровой (АЦП).

Термин «компаратор» произошёл от латинского слова «comparare», что дословно переводится на русский язык как сравнивать. Конструктивно устройство может выпускаться в различных корпусах, например, DIP, SOIC, SSOP. Простейшего вида сравнивающий элемент имеет два аналоговых входа и один цифровой выход. В основе его работы лежит дифференциальный каскад, имеющий высокий коэффициент усиления. Поэтому компараторы широко используются в оборудовании, предназначенном для измерения или преобразования аналогового сигнала в цифровой (АЦП).

На схемах и в технической литературе графически устройство обозначается в виде равнобедренного треугольника с тремя выводами. С одной стороны выводы подписываются знаками «+» и «—», соответственно обозначающими неинвертирующий вход и инвертирующий, а с другой — изображается выход, который маркируется символом Uout.

Когда на прямом входе («+») микросхемы уровень сигнала будет больше, чем на инверсном («—»), то на её выходе образуется устойчивое значение. В зависимости от схемотехнического решения компаратора это значение может принимать вид логического ноля или единицы. В цифровой электронике за единицу считается сигнал, уровень напряжения которого составляет пять вольт, а за ноль принимается его отсутствие. То есть состояние выхода устройства определяется как высокое или низкое. Но на практике же за логический ноль принимается значение разности потенциалов до 2,7 В.

Один из входных сигналов, подаваемых на прибор, называется опорным или пороговым напряжением. Именно с этим значением и сравнивается величина сигнала на втором входе. Опорное напряжение может подаваться как на инверсный, так и прямой вход. В зависимости от этого компараторы называются инвертирующими или неинвертирующими. Когда прибор работает с одним опорным напряжением, его называют однопороговым, а если с разным — многовходовым.

Характеристики прибора

По сути, устройство можно рассматривать как простой вольтметр или АЦП. Компаратор, как и любой электронный прибор, имеет ряд технических характеристик, которые можно разделить на два вида: статические и динамические.

К статическим параметрам относятся следующие характеристики:

Предельная чувствительность обозначает пороговые величины сигнала, которые прибор идентифицирует на входе и изменяет потенциал своего выхода на логический ноль или единицу.

Предельная чувствительность обозначает пороговые величины сигнала, которые прибор идентифицирует на входе и изменяет потенциал своего выхода на логический ноль или единицу.- Величина смещения определяется передаточным моментом устройства относительно идеального положения.

- Входной ток — максимальное его значение, которое может пройти через любой вывод, не повредив устройства.

- Выходной ток — значение тока, появляющееся на выходе при переходе устройства в состояние единицы.

- Разность токов — это величина, находимая при вычитании значений токов, протекающих при закороченных входах.

- Гистерезис — разность уровней входного сигнала, приводящая к изменению устойчивого состояния на выходе.

- Коэффициент снижения синфазного сигнала определяется отношением синфазного и дифференциального сигнала, приводящим к переключению режима работы компаратора.

- Входной импеданс — полное сопротивление входа.

- Минимальная и максимальная рабочая температура — диапазон, в котором технические параметры устройства не изменяются.

Важной же динамической характеристикой является время переключения tn. Она определяется интервалом времени от начала сравнения входного сигнала до момента, при котором на выходе компаратора наступает противоположное устойчивое состояние. Это время определяется при одном значении порогового напряжения и его скачке на противоположном входе. Этот интервал времени разделяется на две части — задержки и нарастания.

Все значимые параметры компаратора представляются в виде переходной характеристики. Это график в декартовой плоской системе координат, в которой по оси Х указывается время в наносекундах, а Y — входное и выходное напряжение в вольтах.

Устройство и принцип работы

Схемотехника устройства построена на базе дифференциального операционника с довольно большим коэффициентом усиления. Её различия с простым линейным усилителем заключаются в выполнении входного и выходного каскада.

Вход устройства выдерживает сигнал в широком диапазоне до значений источника питания и полный интервал синфазных напряжений. Выход компаратора совместим с технологиями ТТЛ и ЭСЛ из-за возможности выполнения этого каскада на транзисторе с открытым коллектором. При работе устройства не используется отрицательная обратная связь как в операционном усилителе, а, наоборот, выход охватывается положительной связью, формирующей гистерезисную передаточную характеристику.

Вход устройства выдерживает сигнал в широком диапазоне до значений источника питания и полный интервал синфазных напряжений. Выход компаратора совместим с технологиями ТТЛ и ЭСЛ из-за возможности выполнения этого каскада на транзисторе с открытым коллектором. При работе устройства не используется отрицательная обратная связь как в операционном усилителе, а, наоборот, выход охватывается положительной связью, формирующей гистерезисную передаточную характеристику.

Двухпороговый компаратор называется триггером Шмита или троичным. Для сравнения в нём используется два напряжения. Сигналы в двоичном компараторе разделяются на три диапазона:

- Urf2 > Urf1;

- Uout1 = 0 при Uin < Uref1 или Uout1 = 1, если Uin > Uref1;

- Uout2 = 0 при Uin < Uref2 или Uout1 = 1, если Uin > Uref2.

Uref — напряжение нижнего и верхнего порогов переключения, Uout — уровень выходного сигнала, Uin — напряжение на входе прибора.

Внутренняя схема устройства представляет собой усилитель, собранный на транзисторах VT1-VT2, который нагружен каскадом VT5-VT6, включённым по схеме с общим эмиттером. Через дополнительный ключ VT4 происходит управление коллекторным режимом работы входного сигнала. А через транзистор VT7, работающий в диодном режиме, контролируется уровень сигнала на VT8, что позволяет добиваться его независимости от изменений напряжения питания. Ключи VT5 и VT6 соединяются со стабилитроном VD1. Поэтому через повторитель VT8 входной сигнал поступает на выход с коллекторного вывода VT6.

Внутренняя схема устройства представляет собой усилитель, собранный на транзисторах VT1-VT2, который нагружен каскадом VT5-VT6, включённым по схеме с общим эмиттером. Через дополнительный ключ VT4 происходит управление коллекторным режимом работы входного сигнала. А через транзистор VT7, работающий в диодном режиме, контролируется уровень сигнала на VT8, что позволяет добиваться его независимости от изменений напряжения питания. Ключи VT5 и VT6 соединяются со стабилитроном VD1. Поэтому через повторитель VT8 входной сигнал поступает на выход с коллекторного вывода VT6.

Если входной сигнал не превышает один вольт, то транзистор VT6 закрыт, а VT5 находится в режиме насыщения. Выходной сигнал не сможет превысить четырёх вольт, так как при большей величине откроется диод. При обратном знаке VT6 насытится, и напряжение на выходе станет равным нулю. В современных устройствах используется стробирующий выход или триггеры-защелки, то есть элементы, контролирующие выход компаратора при обнаружении синхроимпульса. Результаты сравнения могут появляться в двух видах: во время строба или в паузах между импульсами.

Простые конструкции

На практике компараторы напряжения нашли широкое применение в радиоэлектронных схемах различного направления. В радиомагазинах можно встретить довольно большое количество различных микросхем. Но наиболее часто используемыми микросхемами среди радиолюбителей являются:

- LM311;

- К554СА3;

- LM339;

- MAX934.

Они доступны в продаже, а их стоимость более чем демократична. Такие компараторы отличаются широким диапазоном входного напряжения и могут работать при однополярном и двуполярном питании.

К выходу устройства может подключаться любая нагрузка с током потребления, обычно не превышающим 50 мА. Это может быть реле, резистор, светодиод, оптрон или любые исполнительные устройства, но с ограничивающими ток элементами. А также возможно подключить и индуктивную нагрузку, но она обычно в этом случае шунтируется диодами. Для работы устройства применяются источники питания с выходным напряжение 5−36 вольт.

К выходу устройства может подключаться любая нагрузка с током потребления, обычно не превышающим 50 мА. Это может быть реле, резистор, светодиод, оптрон или любые исполнительные устройства, но с ограничивающими ток элементами. А также возможно подключить и индуктивную нагрузку, но она обычно в этом случае шунтируется диодами. Для работы устройства применяются источники питания с выходным напряжение 5−36 вольт.

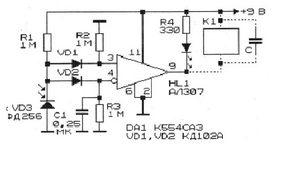

Фотореле контроля

Такое реле собирается навесным монтажом. Его можно использовать в охранной системе или для контроля уровня освещённости. Работа схемы заключается в следующем. Входное напряжение поступает на делитель, состоящий из R1 и фотодиода VD3. Их общая точка соединения через ограничительные диоды VD1 и VD2 подключается к входам компаратора DA1. В результате этого разница потенциалов на входе устройства отсутствует, а значит, и чувствительность прибора максимальная.

Для того чтобы сигнал на выходе инвертировался, понадобится создать разницу на входе всего в один милливольт. Из-за того, что к инверсному входу подключён конденсатор С1 и резистор R1, величина напряжения на нём будет возрастать с небольшой задержкой, равной времени заряда конденсатора.

Для того чтобы сигнал на выходе инвертировался, понадобится создать разницу на входе всего в один милливольт. Из-за того, что к инверсному входу подключён конденсатор С1 и резистор R1, величина напряжения на нём будет возрастать с небольшой задержкой, равной времени заряда конденсатора.

Но этого времени хватит, чтобы на выходе появилась логическая единица, которая перестроит режим работы реле подключённого в качестве нагрузки. Как только освещение опять поменяется, ситуация повторится. Таким образом, направив фотореле на какое-то место, в случае изменения его освещённости на входах компаратора появится разность напряжения. Соответственно будет изменяться и работа реле, к которому может подключаться различного рода нагрузка.

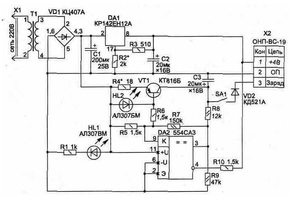

Зарядный блок

Выполненный блок питания из исправных элементов начинает работать сразу. Его настройки сводятся лишь к установке номинального тока заряда и порогов срабатывания компаратора. При включении устройства загорается зелёный светодиод, обозначающий подачу питания. Во время зарядки должен же постоянно светиться красный светодиод, который потухнет, как только аккумулятор зарядится.

Подаваемое напряжение от блока питания регулируется R2, а ток зарядки выставляется R4. Настройка происходит с помощью резистора на 150 Ом, включающегося параллельно контактам держателя батарейки. Сам аккумулятор в него не ставится. Транзистор VT1 устанавливается на радиатор, вместо него можно использовать аналог КТ814Б.

Подаваемое напряжение от блока питания регулируется R2, а ток зарядки выставляется R4. Настройка происходит с помощью резистора на 150 Ом, включающегося параллельно контактам держателя батарейки. Сам аккумулятор в него не ставится. Транзистор VT1 устанавливается на радиатор, вместо него можно использовать аналог КТ814Б.

Такую схему придётся собирать на печатной плате, но в итоге её размер не должен превысить 50 х 50 мм.

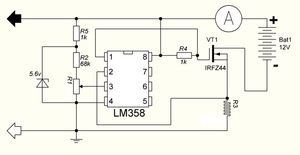

Можно собрать схему попроще, используя принцип работы стабилизатора тока. Подача опорного напряжения на вход LM358 происходит через стабилитрон. Второй вход микросхемы подключается после датчика тока. Если к выходу компаратора подключить разряженный аккумулятор, то в цепи начнёт возрастать ток, а часть напряжения упадёт на низкоомном резисторе.

Можно собрать схему попроще, используя принцип работы стабилизатора тока. Подача опорного напряжения на вход LM358 происходит через стабилитрон. Второй вход микросхемы подключается после датчика тока. Если к выходу компаратора подключить разряженный аккумулятор, то в цепи начнёт возрастать ток, а часть напряжения упадёт на низкоомном резисторе.

Между двумя входами микросхемы возникнет разность напряжения. Схема начнёт компенсировать это различие, увеличивая силу тока на выходе. В процессе заряда аккумулятора напряжение на входе начнёт уменьшаться, что приведёт к снижению тока в цепи. Как только батарея зарядится, транзистор VT1 закроется и нагрузка отключится. Ток заряда же ограничивается с помощью изменения сопротивления R1.

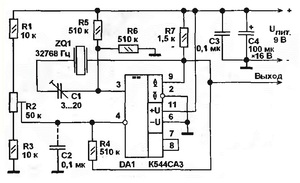

Кварцевый генератор

Такой генератор прямоугольных импульсов, собранный по схеме на отечественном компараторе K544C3, работает на тактовой частоте 32768 Гц. Схема будет работоспособной в диапазоне входного напряжения от 7 до 11 вольт. Частота задаётся кварцем ZQ1, но для работы устройства свыше 50 кГц понадобится уменьшить сопротивление R5 и R6.

При замыкании второго вывода с нулевым проводом выход компаратора оказывается включённым по схеме с открытым коллектором, в которой R7 является нагрузкой. Подстройка частоты выполняется с помощью C1. За счёт резистора R4 происходит автозапуск генератора. Изменяя сопротивление R2, меняется скважность импульсов.

Подбирая ёмкости С1 и С2, генератор можно использовать как бесконтактный датчик жидкости. В качестве детектора для этого понадобится использовать микроконтроллер с программным обеспечением. Хотя можно применить и ещё один компаратор, который будет регистрировать изменения, выпрямленного диодами напряжения.

Таким образом, компаратор напряжения предназначен для сравнения уровней сигналов на своих входах. Если они начинают различаться, то в зависимости от этой разности выход устройства изменяет своё состояние. Этим их свойством и пользуются разработчики, конструируя различные электроприборы.

220v.guru

Компараторы кодов

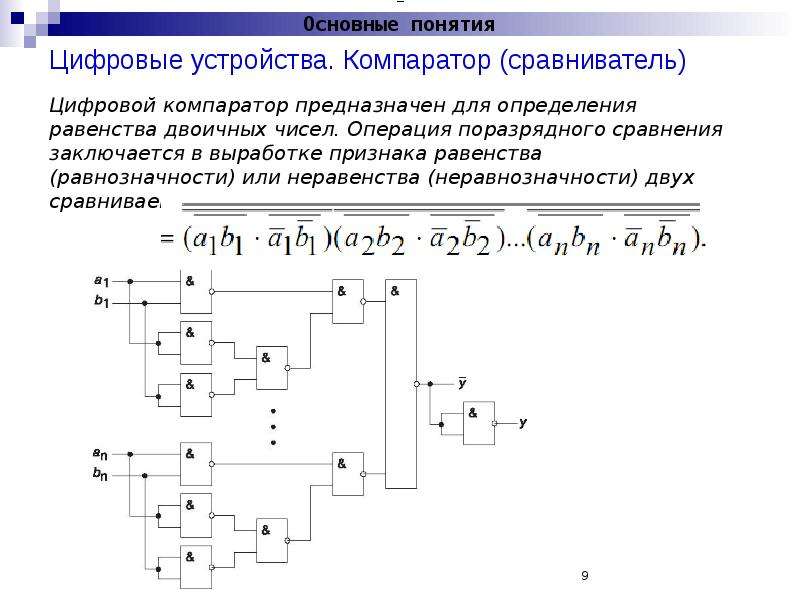

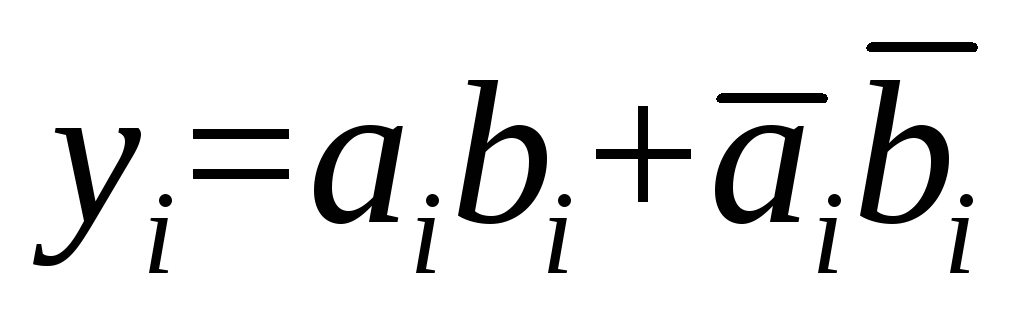

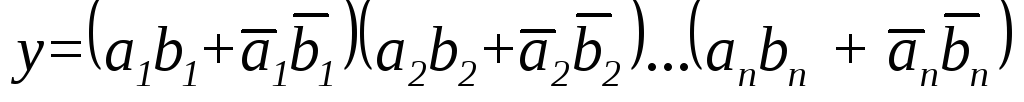

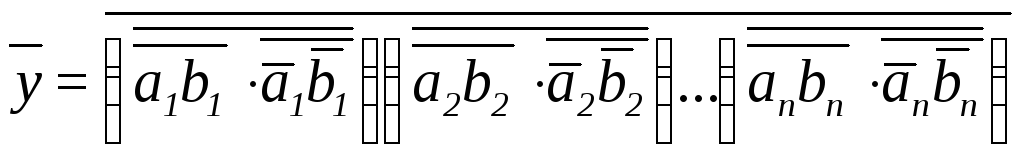

<Цифровой ><компаратор><предназначен><для><определения><равенства><двоичных><чисел.><Опе><рация><поразрядного><сравнения><заключается><в><выработке><признака><равенства><(равно><значности)><или><неравенства><(неравнозначности)><двух><сравниваемых><двоичных><чисел.><Два><числа><равны><при><равенстве><цифр><в><одноименных><разрядах:><ai><=><bi,><><><где><аi><—><цифра><в><i-ом><разряде><одного><числа;><b><i><><—><цифра><в><i-ом><разряде><другого><числа.><Равенство><ai><=b><i,><имеет><место><при><аi><=><1,><bi><=><1><или><при><аi><=><0,><bi><=><0.><Поэтому><логическая><функция,><выражающая><это><равенство,><равна><единице,><если><единице><равно><произведение><этих><цифр><или><произведение><их><инверсных><значений,><т.><е.:>

,<><>

,<><>

<а><логическая><функция,><описывающая><компаратор равенства,><имеет><вид:>

<><>

<><>

<Для><построения><компаратора равенства><только><на><элементах><И-НЕ,><запишем><её><в><другой><форме,><воспользовавшись><формулами><де><Моргана:>

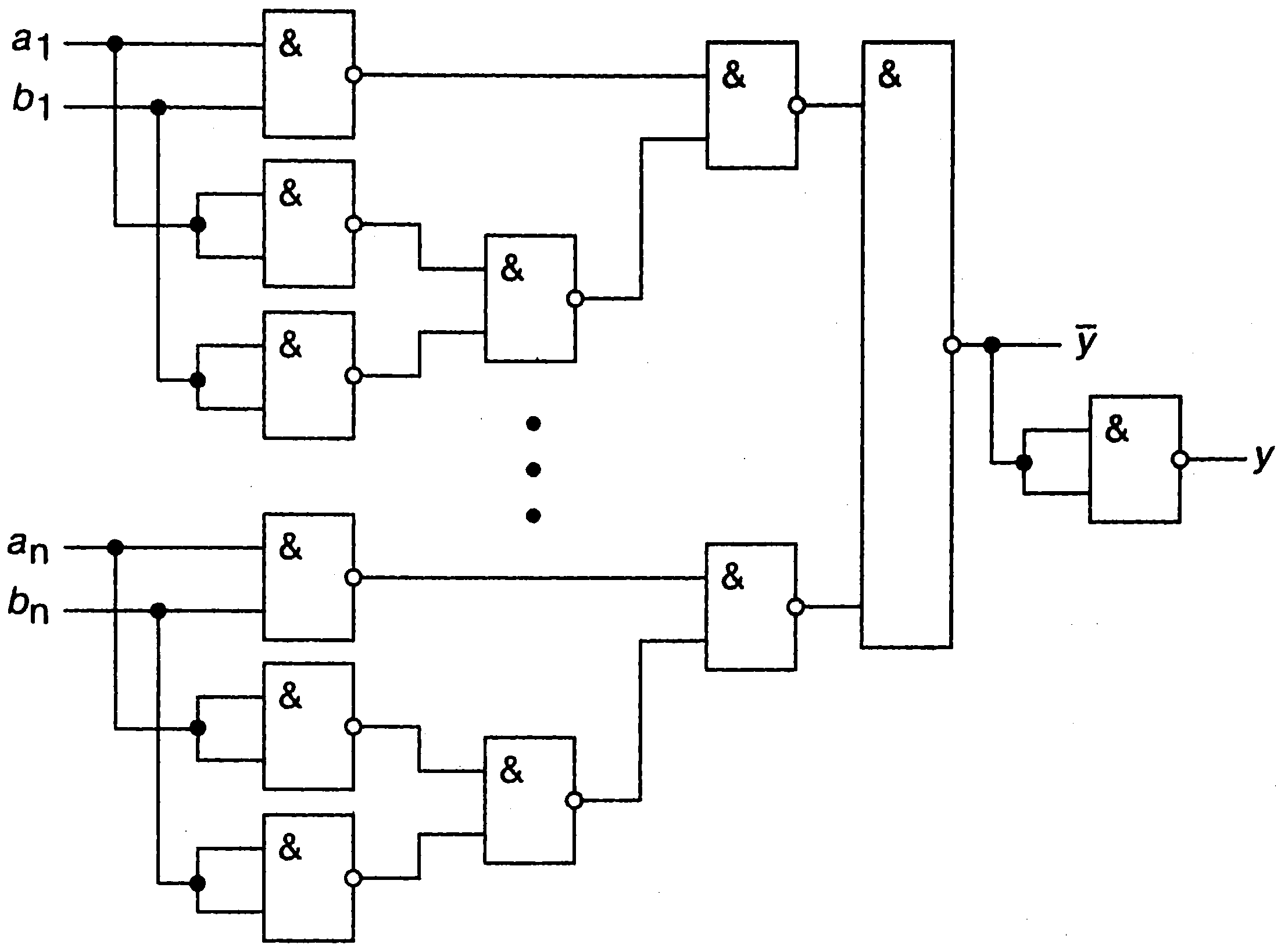

<><><><><><Схема,><реализующая><это><выражение,><приведена><на><рис.>2.13.

Рисунок 2.13 — Схема компаратора 2-х n-разрядных кодов на совпадение в базисе И-НЕ

Помимо совпадения кодов реальные ИМС цифровых компараторов <><могут ><определять и ><><><><><><><><><><><><><><вид их ><неравенства ><А>В ><или ><А<В. Т.е. реальные ИС ><><компараторов ><имеют ><три >выхода. Схема такого одноразрядного компаратора приведена на рис. 2.14.

Рисунок 2.14 — Одноразрядный компаратор с определением равенства и вида неравенства

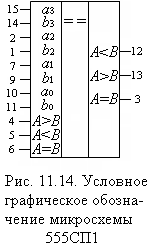

<Цифровые><компараторы><выпускают,><как><правило,><в><виде><самостоятельных><микросхем.><Так, например, имеется ТТЛШ><микросхема К555СП1<(рис.>2.15) и КМОП><К564ИП2, которые являются 4-хразрядными компараторами с определением типа неравенства и возможностью наращивания разрядности.>

Рисунок 2.15 — Включение микросхемы компаратора 4-хразрядных кодов К555СП1

<Если><используется><одна><микросхема,><то><на><ее><вход><Y=X><следует ><подать ><логическую ><1><><><><><><><><><><.>

-

Двоичные полусумматор и сумматор

<Сумматор><—><это устройство><,><в><котором><выполняется><арифметическая><операция><суммирования><цифровых><кодов><двух><двоичных><чисел.><Известно,><что><числа><в><любой><позиционной><си><стеме><счисления><складываются><поразрядно.><Поэтому><для><сложения><двух><чисел><нужно><иметь><типовые><узлы,><реализующие><суммирование><цифр><одного><разряда><слагаемых><с><учетом><возможного><переноса><единицы><из><соседнего><младшего><разряда.><К><таким><узлам><относят><одноразрядные><комбинационные><полусумматоры><и><сумматоры.>

<Полусумматор><предназначен><для><суммирования><двух><одноразрядных><двоичных><чисел.><Он><имеет><два><входа><—><аi><и><bi><и><два><выхода><—><S><i><><иPi+1,><где><S><i><><—><выход><суммы,><а><Pi+1><является><выходом><переноса><(табл.><2.><3).><Логические><функции><для ><><и

><><и ><><и><функциональную><схему><(рис.><2.16><)><этого><узла><легко><построить><на><ос><нове><таблицы><истинности><(таблица><2.3),><используя><элементы><И,><ИЛИ><и><НЕ.>

><><и><функциональную><схему><(рис.><2.16><)><этого><узла><легко><построить><на><ос><нове><таблицы><истинности><(таблица><2.3),><используя><элементы><И,><ИЛИ><и><НЕ.>

Таблица 2.3 — Таблица истинности одноразрядного полусумматора

|

аi |

bi |

Pi+1 |

<S>i<> |

|

<0> |

<0> |

<0> |

<0> |

|

<0> |

<1> |

<0> |

<1> |

|

<1> |

<0> |

<0> |

<1> |

|

<1> |

<1> |

<1> |

<0> |

Рисунок 2.16 — Схема одноразрядного полусумматора

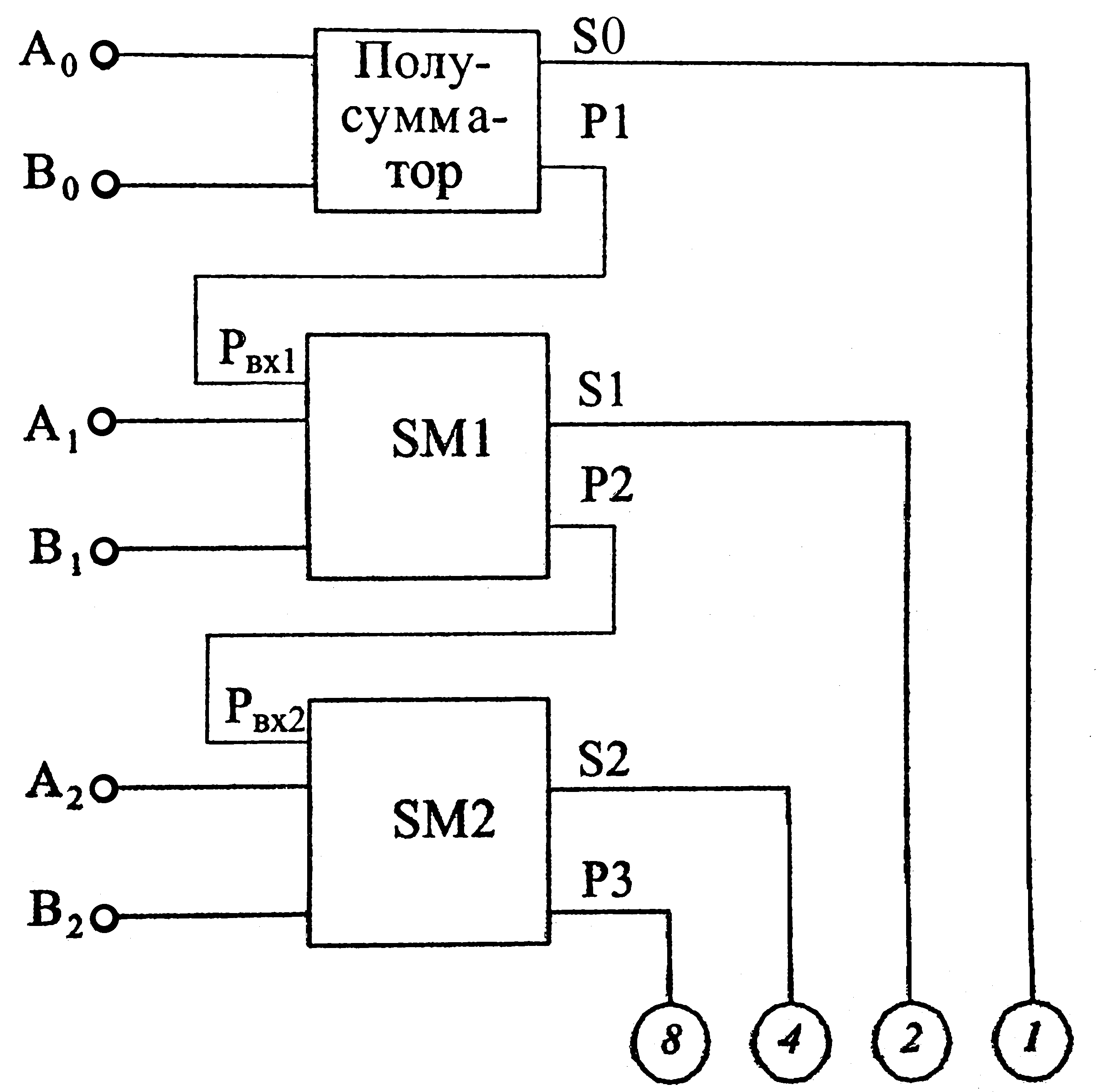

<При><построении><сумматоров><на><интегральных><микросхемах><для><обеспечения><быс><тродействия><и><минимального><количества><однотипных><логических><элементов><необхо><димо><уменьшить><число><последовательно><включенных><элементов.><Анализ><показал,><что><более><экономичной><по><количеству><элементов><и><быстродействующей><является><функ><циональная><схема><полусумматора,><реализующая><переключательную><функцию:>

,

,

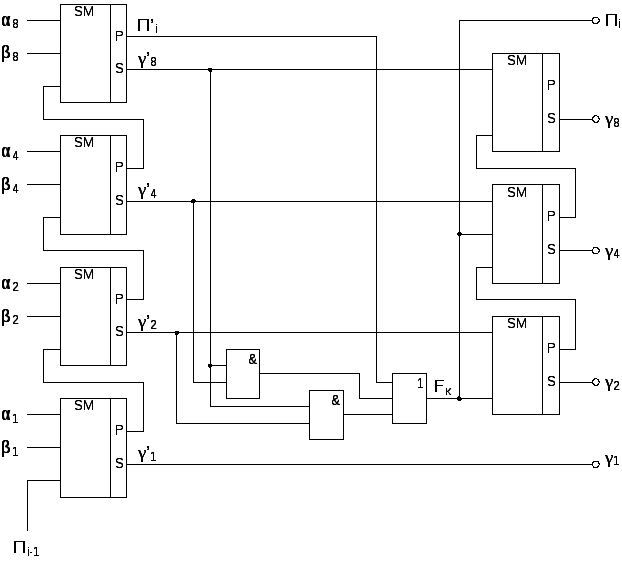

<При><суммировании><двух><многоразрядных><чисел><для><каждого><разряда><(кроме><младшего)><необходимо><использо><вать><устройство,><имеющее><дополнительный><вход><перено><са (из предыдущего более младшего разряда, вспомните правило сложения в столбик).><Такое><устройство><(рис.><2.17)><называют><полным ><сумма><тором><и><его><можно><представить><как><объединение>двух<полусумматоров><(Р><вх><><—><дополнительный><вход><переноса).><Сумматор><обозначают><через>SM.

<В><универсальных><АЛУ,><входящих><в><состав><цифровых><устройств,><одноразрядные><сумматоры><проектируют><из><двух><полусумматоров,><объединенных><в><один><выход><><><S(рис. 2.17).>

Рисунок 2.17 — Одноразрядный полный сумматор на основе двух полусумматоров

<Мно><горазрядные><комбинационные><сумматоры><последовательного><или><параллельного><дей><ствия><строятся><на><основе><одноразрядных><комбинационных><сумматоров,><реализующих><функции для каждого разряда:>

,

,

<По><этим><функциям можно построить><><сумматор и><на><элементах><И-НЕ><или>ИЛИ-НЕ.

<Соединяя><определенным><образом><полусумматоры><и><полные><сумматоры><друг><с><другом,><получают><устройство><для><выполнения><сложения><нескольких><разрядов><двоичных><чи><сел.><В><качестве><примера><рассмотрим><устройство><для><сложе><ния><двух><трехразрядных><двоичных><чисел><А><2>< ><А1, ><А0><и><В><2>< ><В1, ><В0><><,><где><A0 ><и><В><0><><—><младшие><разряды><двоичных><чисел><(рис.><2.18).>

<На ><выходах <S>2…><S0 ><>< ><формируется ><код ><суммы ><чисел ><А><2>< ><А><1>< ><A0 ><и ><В><2>< ><В1 ><В><0><, ><а ><на ><выходе ><Р><3>< ><— ><сигнал ><переноса ><в ><следующую ><микросхему, ><так ><как ><при ><сложении ><двух ><трехразрядных ><дво><ичных ><чисел ><может ><получиться ><четырехразрядное ><число.>

<Следует><отметить,><что><в><рассмотренной структуре><><><для><суммирования><в><каждом><разряде><исполь><зуется><отдельный><сумматор,><но><перенос><из><разряда><в><раз><ряд><осуществляется><последовательно,><что><и><определяет><время><выполнения><суммирования><><><><><><>.<Рассмотренный><сумматор><называется><параллельным ><сумматором c последовательным переносом(К155ИМ3).>

Рисунок 2.18 — Параллельный 3-хразрядный сумматор с последовательным переносом

<Для><повышения><быстродействия><сумматоров><необходи><мо><уменьшить><время><переноса,><что><достигается><использо><ванием><вместо><последовательного><параллельного><переноса. В этом случае в каждом разряде как сигнал суммы, так и сигнал переноса непосредственно формируются из входных переменных.><Так><микросхема><К555ИМ6 (74LS283)><представляет><собой><четырех><разрядный><сумматор><с><параллельным><переносом.>

<В><виде><интегральных><микросхем><выпускаются><однораз><рядные,><двухразрядные><и><четырехразрядные><двоичные><сумматоры (рис. 2.19).>

Рисунок 2.19 — Двоичные сумматоры

<Рассмотренные><сумматоры><могут><использоваться><для><вычитания><двоичных><чисел.><В><этом><случае><операция><вы><читания><заменяется><сложением><уменьшаемого><с><вычита><емым,><представленным><в><дополнительном><коде,><т.><е.><опе><рацией:>

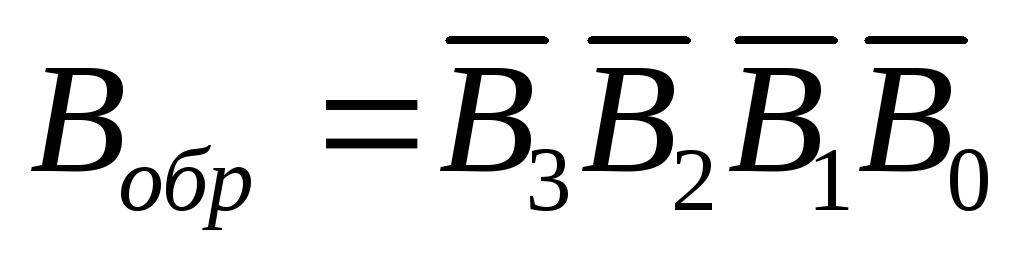

<Апр– Впр = Апр+ Bдоп = Апр+Bобр+1.><><><><><><><><><><><><><><><><><><><><><><><><><>

<где><А={A3A2A1A0}<><><><><><><><><><><,>< >><и><В={B3B2B1B0}><—><многоразрядные><двоичные><числа, здесь для примера><,><четырехразрядные.>

,

,

<>

<>

<Рассмотрим 2 примера вычитания (10-5) и (5-10).>

<Двоичный><эквивалент+><1010=0><><10102, ><а +><510><=0><01012.>

Числа в дополнительных кодах:

–1010=10доп=10110B, –510=5доп=11011B

<Для><реализации><описанного><алгоритма><вычитаемое><нужно><преобразовать><в дополнительный код (см. выше) и сложить с уменьшаемым:><><><><><><><><><><><><><><><><><><><>

0<><><><1010 00101>

1<1011 10110>

< 00101=51011011=–510>

<><Четыре><младших><разряда><результата><представляют><со><бой><результат в дополнительном коде><,><т.><е. десятичное число><5 (в первом случае положительное, а во втором — отрицательное)><.>

<Следует><подчеркнуть,><что><если><А><>><В,><т.><е.><результат><—><положительное><число,><то><ответ><формируется><в><прямом><коде>(знаковый разряд равен 0),<при><этом><формируется><1><переноса><в><более><старший><разряд.><При><А><<><В><ответ><формируется><в дополнительном коде><(знаковый разряд равен 1)><><и><1><переноса><в><более><старший><разряд><не><образуется.>

<Принципиально ><возможно ><построение ><функциональных ><схем ><сумматоров, ><рабо><тающих><в><любой><системе><счисления,><отличающейся><от><двоичной.>

Кроме двоичных, в микропроцессорной технике часто используются так называемые двоично-десятичные коды. Они отображают выраженные в виде последовательности двоичных разрядов десятичные числа. Очевидно, что для представления десятичных цифр необходим, как минимум 4-разрядный двоичный код. При этом из 16 возможных его комбинаций используется только 10. Это предполагает разработку большого числа различных двоично-десятичных кодов (см. табл. 1.5).

На практике большое распространение получил класс так называемых взвешенных кодов. В этих кодах каждому разряду двоичного числа присваивается вполне определенный весовой коэффициент (см. табл. 1.5). В табл. 2.4 приведено соответствие десятичных чисел и их двоичных и двоично-десятичных эквивалентов в коде 8-4-2-1. Весовые коэффициенты его двоичных разрядов соответственно равны 8, 4, 2, 1.

Таблица 2.4. Двоичные и двоично-десятичные коды чисел от 0 до 15

|

<<Двоичный >< ><код > x3x2x1x0 |

<Двоично-десятичный код> |

<Десятичное число> |

|

<0><><><><><><><0><><><><><><><0><><><><><><><0> |

<0><0><0><0> |

<0> |

|

<0><><><><><><><0><><><><><><><0><><><><><><><1> |

<0><0><0><1> |

1 |

|

<0><><0><><10> |

<0><0><10> |

2 |

|

<0><><011><><> |

<0><0><11> |

3 |

|

<0><><10><><0> |

<0><10><0> |

4 |

|

<0><><10><><1> |

<0><1><0><1> |

5 |

|

<0><><1><><1><><><><><><><0> |

<0><110> |

6 |

|

<0><><><><><><><111> |

<0><111> |

7 |

|

<10><><0><><0> |

<10><0><0> |

8 |

|

<10><><0><><1> |

<10><0><1> |

9 |

|

<10><><10> |

<0><0><0><1 >< >< >< >< >< >< >< >< ><0><0><0><0> |

10 |

|

<10><><11> |

<0><0><0><1 >< >< >< >< >< >< >< >< ><0><0><0><1> |

11 |

|

<110><><0> |

<0><0><0><1 >< >< >< >< >< >< >< >< ><0><0><10> |

12 |

|

<110><><1> |

<0><0><0><1 >< >< >< >< >< >< >< >< ><0><0><11> |

13 |

|

<1110> |

<0><0><0><1 ><>< >< >< >< >< >< >< >< ><0><10><0> |

14 |

|

<1><><1><><1><><1> |

<0><0><0><1 >< >< >< >< >< >< >< >< ><0><10><1> |

<15>> |

Из приведенной таблицы следует, что 4-разрядные двоичные коды с 1010 по 1111 не имеют 4-разрядного двоично-десятичного эквивалента. Так, число 12 в двоично-десятичном коде представляется 8-разрядным упакованным кодом 00010010, а число 16 — кодом 00010110.

Описанная особенность двоично-десятичного кода предполагает использование для суммирования специальных логических схем. Смысл их построения состоит в том, что сначала двоично-десятичные коды суммируются как двоичные. Если результатом суммирования является несуществующий двоично-десятичный код, его необходимо уменьшить на 1010, и дополнительно сформировать сигнал переноса. Уменьшение кода на 1010может выполняться его суммированием с дополнительным кодом числа 10 (в двоичной системе –1010= 101102, т.е. фактически прибавлением 610=1102).

Необходимость выполнения такого суммирования согласно табл. 2.4 после минимизации выражается ФАЛ F=x3(x2 + x1).

Очевидно, что такое же суммирование необходимо выполнять и в случае, если в результате суммирования тетрад (BCD-кодов) получен сигнал переноса в старший разряд. С учетом сказанного, ФАЛ необходимости выполнения дополнительного суммирования имеет вид:

F = x3(x2 + x1)+ P(2.1),

где x3, x2, x1, x0— разряды полученного кода в порядке убывания весов,P— перенос, возникший при сложении текущих тетрадBCD-кодов.

Таким образом, для реализации операции сложения двух двоично-десятичных кодов необходимы два 4-хразрядных сумматора и логическая схема, обеспечивающая формирование выходного сигнала в соответствие с ФАЛ (2.1).

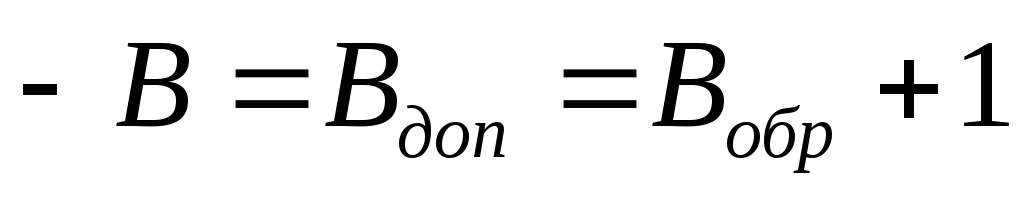

Пример реализации такого устройства показан на рис. 2.20. Четырехразрядный сумматор DD1 выполняет арифметическое сложение исходных двоично-десятичных кодов. Логическая схема на элементахDD2,DD3 иDD4 реализует ФАЛ (2.1), определяя необходимость дополнительного суммирования, выполняемого сумматоромDD5.

<>

Рисунок 2.20 — Сумматор двух BCD-чисел<>

studfile.net

Цифровой компаратор — Карта знаний

-

Цифрово́й компара́тор или компара́тор ко́дов логическое устройство с двумя словарными входами, на которые подаются два разных двоичных слова равной в битах длины и обычно с тремя двоичными выходами, на которые выдаётся признак сравнения входных слов, — первое слово больше второго, меньше или слова равны. При этом выходы «больше», «меньше» имеют смысл, если входные слова кодируют числа в том или ином машинном представлении.

Часто цифровые компараторы не имеют выходов «больше», «меньше», а только выход «равно».

Может быть построен на логических элементах, работа которых основана на самых различных физических принципах, но современные компараторы обычно представляют собой полупроводниковые электронные устройства работающие в двоичной логике.

Промышленностью компараторы выпускаются в виде законченных компонентов — микросхем с разной длиной сравниваемых слов и других параметров. Примеры микросхем цифровых компараторов: КМОП-логика — 4063 и 4585, ТТЛ — 7485 и 74682-89 и многие другие.

Компараторы широко используются в вычислительной технике, измерительной технике, радио- и проводной связи, бытовых приборах. Например, цифровые часы с будильником содержат цифровой компаратор, при совпадении текущего времени с заданным, подается звуковой сигнал.

Аналоговым эквивалентом цифрового компаратора является аналоговый компаратор напряжений или токов. Некоторые микроконтроллеры имеют входные встроенные аналоговые компараторы, состояние выходов которых может быть считано программой контроллера или вызывать её прерывание подпрограммой.

Источник: Википедия

Связанные понятия