Что такое логический элемент 2И-НЕ. Как работает элемент 2И-НЕ. Какие характеристики имеет элемент 2И-НЕ. Где применяется элемент 2И-НЕ в цифровой электронике. Как выглядит условное обозначение элемента 2И-НЕ на схемах.

Принцип работы логического элемента 2И-НЕ

Логический элемент 2И-НЕ (также называемый элементом Шеффера) является одним из базовых элементов цифровой логики. Его работа основана на следующем принципе:

- Элемент имеет два входа и один выход

- Выходной сигнал равен 0 только тогда, когда на оба входа подан сигнал 1

- Во всех остальных случаях на выходе элемента будет 1

Таблица истинности элемента 2И-НЕ выглядит следующим образом:

| Вход A | Вход B | Выход Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Схемотехническая реализация элемента 2И-НЕ

Как реализуется логика элемента 2И-НЕ на транзисторном уровне? Типовая схема на биполярных транзисторах включает в себя:

- Многоэмиттерный входной транзистор

- Фазоинвертор на двух транзисторах

- Выходной каскад с двумя транзисторами

Принцип работы такой схемы следующий:

- При подаче низкого уровня хотя бы на один вход, входной транзистор открывается

- Это приводит к закрытию транзистора фазоинвертора и открытию выходного транзистора

- На выходе формируется высокий уровень

- Только когда на оба входа поданы высокие уровни, входной транзистор закрывается

- Это приводит к открытию транзистора фазоинвертора и закрытию выходного транзистора

- На выходе формируется низкий уровень

Основные характеристики элемента 2И-НЕ

Ключевыми параметрами логического элемента 2И-НЕ являются:

- Напряжение питания: обычно 3.3В или 5В

- Входное напряжение логического нуля: 0-0.8В

- Входное напряжение логической единицы: 2-5В

- Выходное напряжение логического нуля: 0-0.4В

- Выходное напряжение логической единицы: 2.4-5В

- Время задержки распространения: 5-15 нс

- Ток потребления в статическом режиме: 1-2 мА

Конкретные значения могут различаться в зависимости от технологии изготовления и серии микросхем.

Применение элемента 2И-НЕ в цифровых схемах

Элемент 2И-НЕ широко используется в цифровой электронике благодаря своей универсальности. Основные области применения:

- Построение более сложных логических функций

- Реализация триггеров и защелок

- Создание генераторов импульсов

- Формирование задержек сигналов

Рассмотрим некоторые примеры применения подробнее.

Построение других логических функций

На основе элемента 2И-НЕ можно реализовать любую логическую функцию. Например:

- Инвертор: достаточно соединить входы элемента

- Элемент ИЛИ-НЕ: подключить выходы двух элементов 2И-НЕ на вход третьего

- Элемент И: использовать два последовательно включенных элемента 2И-НЕ

Реализация триггеров

RS-триггер легко строится на двух элементах 2И-НЕ с перекрестными обратными связями. Такая схема позволяет хранить 1 бит информации.

Условное графическое обозначение элемента 2И-НЕ

На принципиальных схемах элемент 2И-НЕ обозначается следующим образом:

«` «`Основные элементы обозначения:

- Прямоугольник с закругленной правой стороной — корпус элемента

- Кружок на выходе — признак операции НЕ

- Две входные линии слева

- Одна выходная линия справа

Микросхемы, содержащие элементы 2И-НЕ

Элементы 2И-НЕ выпускаются в составе интегральных микросхем различных серий. Наиболее распространенные варианты:

- К155ЛА3 — 4 элемента 2И-НЕ

- К555ЛА3 — 4 элемента 2И-НЕ

- 74HC00 — 4 элемента 2И-НЕ

- CD4011 — 4 элемента 2И-НЕ

Эти микросхемы содержат по 4 независимых элемента 2И-НЕ в одном корпусе, что удобно для построения более сложных логических схем.

Преимущества и недостатки элемента 2И-НЕ

Каковы основные достоинства и ограничения элемента 2И-НЕ?

Преимущества:

- Универсальность — позволяет реализовать любую логическую функцию

- Простота схемотехнической реализации

- Высокое быстродействие

- Хорошая помехоустойчивость

Недостатки:

- Повышенное энергопотребление по сравнению с КМОП-элементами

- Ограниченная нагрузочная способность выхода

- Необходимость внешних подтягивающих резисторов в некоторых схемах

Несмотря на указанные недостатки, элемент 2И-НЕ остается одним из наиболее распространенных логических элементов в цифровой схемотехнике.

Особенности применения элемента 2И-НЕ

При использовании элемента 2И-НЕ в реальных схемах следует учитывать ряд важных моментов:

- Необходимость подключения неиспользуемых входов к определенному логическому уровню

- Ограничение длины соединительных проводников для минимизации помех

- Установка развязывающих конденсаторов по цепям питания

- Учет времени задержки распространения сигнала при проектировании высокоскоростных схем

Соблюдение этих правил позволяет обеспечить надежную работу цифровых устройств на основе элементов 2И-НЕ.

Заключение

Логический элемент 2И-НЕ является одним из фундаментальных «кирпичиков» цифровой электроники. Его простота, универсальность и хорошие технические характеристики обеспечивают широкое применение в самых разнообразных цифровых устройствах — от простейших логических схем до сложных вычислительных систем.

Понимание принципов работы и особенностей применения элемента 2И-НЕ — важный шаг в освоении цифровой схемотехники. Это базовые знания, необходимые для дальнейшего изучения более сложных цифровых узлов и систем.

Логический элемент 2И-НЕ и его характеристики

Широкое распространение получили логические элементы транзисторно-транзисторной логики (ТТЛ). Рассмотрим принципиальную схему логического элемента 2И-НЕ транзисторно-транзисторной логики со сложным инвертором на выходе. Такие логические элементы имеют хорошую нагрузочную способность.

На рисунке 1.14,а приведена принципиальная схема одного из четырех логических элементов 2И-НЕ микросхемы К134ЛБ1, а на рисунке 1.14,б – условное обозначение этой микросхемы на принципиальных схемах.

На рисунках 1.15,а и 1.15,в приведены принципиальные схемы логических элементов 2И-НЕ соответственно для микросхем К133ЛА3 и К155ЛА3. Каждая их этих микросхем имеет по 4 логических элемента 2И-НЕ, а их условные обозначения на принципиальных схемах совпадают (рис. 1.15,б).

Первые логические элементы ТТЛ не имели на входах защитных диодов. В момент окончания прямоугольного импульса на входе элемента в монтажных цепях цифрового устройства могут возникнуть затухающие колебания. Следствием этих колебаний может быть ложное срабатывание цифрового устройства. В результате доработки логических элементов к каждому входу многоэмиттерного

транзистора были подключены демпфирующие диоды. Первым отрицательным импульсом затухающего колебания демпфирующий диод открывается, и амплитуда затухающих колебаний резко уменьшается. Следующий положительный импульс затухающего колебания уже не может изменить состояние на выходе логического элемента.

Резисторы R4, R5 и транзистор VT5 в логическом элементе 2И-НЕ микросхемы К155ЛА3 (рис. 1.15,в) позволяют получить передаточную характеристику, более близкую к прямоугольной. Это повышает помехозащищенность в состоянии логической единицы на выходе элемента.

Рассмотрим работу логического элемента 2И-НЕ микросхемы К134ЛБ1 (рис. 1.14,а). Для логических элементов транзисторно-транзисторной логики напряжение логического нуля по техническим условиям может быть 0-0,4 В. Напряжение логической единицы — не менее 2,4 В и не более 5 В. Напряжение логического нуля можно подать, соединив вход элемента с общим проводом накоротко, либо через резистор малого сопротивления (не более 300 Ом). Напряжение логической единицы на вход элемента можно подать, соединив вход элемента с плюсовым проводом питания через резистор сопротивлением 1 Ком, либо оставляя вход элемента свободным.

Пусть на входы Х1 и Х2 элемента 2И-НЕ (рис. 1.14,а) поданы напряжения логической единицы. Рассмотрим случай, когда Х1 и Х2 никуда не подключены. В этом случае транзисторы VТ2, VТ4 будут открыты токами базы, протекающими по цепи: + источника, резистор R1, переход база-коллектор VТ1, база-эмиттер VТ2, база-эмиттер VТ4, минус источника. Транзистор VТ3 в этом случае закрыт, т.к. потенциал коллектора транзистора VT2 примерно 0,9 В.

Рассмотрим делитель напряжения, верхнее плечо которого состоит из последовательно соединенных резистора R3, выводов коллектор-эмиттер транзистора VТ3, диода VД1, а нижнее плечо делителя – это выводы коллектор-эмиттер VТ4. В рассматриваемом случае сопротивление верхней части делителя велико, а сопротивление нижней части делителя — мало. Выходное напряжение соответствует логическому нулю.

Если хотя бы на одном из входов Х1, Х2 действует логический нуль, то VТ2, VТ4 закрыты, а VТ3 открыт. Ток базы транзистора VT3 протекает по цепи: плюс источника питания, резистор R2, переход база-эмиттер транзистора VT3, полупроводниковый диод VD1, резистор нагрузки (на схеме не показан), минус источника питания. В этом случае сопротивление между коллектором транзистора VT3 и катодом диода VD1 мало, а сопротивление между коллектором и эмиттером транзистора VT4 велико. Анализируя делитель напряжения, приходим к выводу, что выходное напряжение логического элемента будет соответствовать логической единице.

В вычислительной технике широко применяется устройство с тремя состояниями на выходе. Рассмотрим логический элемент НЕ (инвертор) с тремя состояниями на выходе (рис. 1.16,а). Указанный инвертор легко получается из схемы базового логического элемента 2И-НЕ путем добавления в схему VД2.

Если на вход разрешения V микросхемы подано напряжение логической «1», то диод VД2 оказывается отключенным от схемы, и данный элемент можно рассматривать как логический элемент НЕ. Если на входе Х логическая единица, то транзисторы VT2, VT4 будут открыты, транзистор VT3 закрыт и на выходе элемента будет сигнал логического нуля. Подадим на вход Х сигнал логического нуля. В этом случае транзисторы VT2, VT4 будут закрыты, транзистор VT3 открыт и на выходе элемента будет сигнал логической единицы.

Подадим на вход V напряжение логического «0» , в этом случае окажутся закрытыми VТ2, VТ3, VТ4. Выход Y оказывается отключенным как от плюсового, так и от минусового проводов источника питания. Говорят, что выход элемента находится в третьем высокоимпедансном состоянии (состояние высокого сопротивления, как от клеммы «+», так и от клеммы «-» источника питания). Элементы с тремя состояниями позволяют организовать в компьютерных системах так называемую общую шину.

Элементы с тремя состояниями входят в состав шинных формирователей. Шинные формирователи это устройства, которые обеспечивают передачу сигнала в двух направлениях по одному и тому же проводу. В составе шинного формирователя на каждую линию потребуется 2 элемента с тремя состояниями на выходе.

На рисунке 1.16,б приведена схема логического элемента 2И-НЕ с открытым коллектором на выходе. Выходы нескольких таких элементов подключаются к одному резистору нагрузки, второй вывод которого подключен к плюсовому проводу источника питания.

На рисунке 1.17,а приведена схема подключения приборов для снятия зависимости выходного напряжения логического элемента от тока нагрузки в состоянии логической единицы на выходе элемента, а на рисунке 1.18,а – график этой зависимости. Логические элементы ТТЛ не выходят из строя при коротком замыкании нагрузки для случая логической единицы на выходе элемента, поэтому в цепи нагрузки нет необходимости ставить ограничительный резистор. Если на выходе элемента логический нуль, то при исследовании зависимости выходного напряжения от тока нагрузки необходимо в цепи нагрузки устанавливать ограничительный резистор.

На рисунке 1.17,б приведена схема подключения приборов для снятия зависимости выходного напряжения логического элемента от тока нагрузки в состоянии логического нуля на выходе элемента, а на рисунке 1.18,б – график этой зависимости. Сопротивление ограничительного резистора в цепи нагрузки выбирают примерно таким же, как сопротивление резистора R3 в логическом элементе 2И-НЕ (рисунок 1.15,в), т.е. примерно 100 Ом.

По графикам, приведенным на рисунке 1.18 можно определить коэффициент разветвления или нагрузочную способность логического элемента. По графику рисунка 1.18,а найдем ток нагрузки при выходном напряжении 2,4 В. Зная, что входной ток логической единицы 40 мкА, определим, сколько таких элементов можно подключить в состоянии логической единицы на выходе данного элемента. По рисунку 1.18,б определим ток нагрузки в состоянии логического нуля на выходе элемента при напряжении 0,4 В. Зная, что входной ток логического нуля минус 1,6 мА, определим, сколько таких элементов можно подключить в состоянии логического нуля на выходе данного элемента. Наименьшее из двух полученных значений будет являться коэффициентом разветвления логического элемента. Определение коэффициента разветвления таким способом будет справедливо только для низких частот, когда влиянием входных емкостей элементов и емкости монтажа можно пренебречь.

На рисунке 1.19,а приведена схема для наблюдения на экране осциллографа зависимости выходного напряжения элемента от напряжения на его входе, а на рисунке 1.19,б – график этой зависимости для логического элемента 2И-НЕ ТТЛ. Диод VD1 может быть любым кремниевым малой мощности, т.к. обратное напряжение в данной схеме не превысит 5 В, а ток через диод в прямом направлении выбирается единицы миллиампер. Амплитуда переменного напряжения на выходе источника переменного напряжения не должна превышать 10 В. График зависимости выходного напряжения элемента от напряжения

на его входе называется передаточной характеристикой логического элемента. Из графика передаточной характеристики логического элемента 2И-НЕ видно, что при входных напряжениях менее 0,4 В на выходе элемента напряжение логической единицы, а при входных напряжениях более 2,4 В на выходе элемента напряжение логического нуля. Реально в логическом элементе входное напряжение логического нуля может быть больше 0,4 В, а напряжение логической единицы меньше 2,4 В. Однако, выбирать такой режим работы элемента нецелесообразно, т.к. уменьшается помехоустойчивость логического элемента.

На рисунке 1.20 приведена входная характеристика логического элемента 2И-НЕ, снятая по одному из входов элемента. На втором входе элемента напряжение логической единицы. Точка а на графике входной характеристики соответствует входному напряжению 2,4 В, а точка б – входному напряжению 0,4 В. Входной ток логической единицы не превышает 40 мкА, а входной ток логического нуля менее –1,6 мА. Знак минус означает, что ток вытекает из микросхемы.

На рисунке 1.21,а приведена схема подключения приборов для наблюдения на экране осциллографа зависимости выходного напряжения от тока нагрузки для случая, когда на выходе элемента логическая единица. Ограничительный резистор в цепи нагрузки не предусмотрен, т.к. исследуется логический элемент 2И-НЕ в состоянии логической единицы на выходе. В качестве источника U2 используется В24, с клемм «+» и «–» которого снимается пульсирующее с частотой 100 Гц напряжение. Сопротивление резистора Rэт выбирают как можно меньше (коэффициент отклонения по каналу Х осциллографа должен быть минимальным). Если чувствительность канала Х осциллографа недостаточна, то на вход Х можно подключить предварительный усилитель. Схема усилителя к входу Х осциллографа ОМЛ-3М приведена на рисунке 1.22.

Для питания усилителя используют переменное напряжение 12 вольт. Сопротивление резистора R1 выбирают значительно больше сопротивления эталонного резистора Rэт. Выход предварительного усилителя подключают к входу «Х» осциллографа. Переменным резистором R5 проводят балансировку микросхемы DA1 при отсутствии входного сигнала. Необходимый коэффициент отклонения луча по оси Х устанавливают переменным резистором R4. Стабилитроны VD1 и VD2 выбирают с учетом того, что необходимо обеспечить перемещение луча по оси «Х» из одного крайнего положения экрана в другое при изменении постоянного напряжения на входе усилителя от 0 до максимально возможного. Расчет сопротивлений резисторов R6, R7 параметрического стабилизатора напряжения проводился с учетом того, что для питания усилителя используется переменное напряжение 12 вольт и выбраны стабилитроны КС156А.

На рисунке 1.21,б приведена схема подключения приборов для наблюдения на экране осциллографа зависимости выходного напряжения от тока нагрузки для случая, когда на выходе элемента логическая нуль. На транзисторах VT1 и VT2 собрано токовое зеркало. Особенностью работы токового зеркала является то, что коллекторные токи обоих транзисторов одинаковы и в определенных пределах не зависят от сопротивлений нагрузок. Значения коллекторных токов определяются напряжением на резисторе R2 и сопротивлениями резисторов R1 и R3. Сопротивления резисторов R1 и R3 обычно выбирают одинаковыми. Сопротивление эталонного резистора в данной схеме не обязательно должно быть малым. Транзисторы VT1, VT2 должны иметь примерно одинаковый и достаточно большой коэффициент усиления по току.

В цифровых устройствах на входах логических элементов обычно присутствуют прямоугольные импульсы напряжения. Пусть напряжение на обоих входах логического элемента 2И-НЕ микросхемы К155ЛА3 скачком изменилось с высокого уровня на низкий (рис. 1.15,в). В этом случае транзистор VT3начнет открываться, а транзистор VT4 – закрываться. Транзисторы открываются быстрее, чем закрываются. Поэтому в течение некоторого промежутка времени будут открыты транзисторы VT3 и VT4. Ток, потребляемый логическим элементом от источника питания, ограничивается только резистором R3. Указанный ток короткого замыкания приводит к увеличению потребляемой мощности в динамическом режиме. График зависимости потребляемой от источника питания мощности от частоты прямоугольных импульсов на входе приведен на рисунке 1.23.

логический элемент NAND / 2И-НЕ 74HC00

Микросхема 74HC00 представляет собой сборку из четырех логических элементов NAND ( 2И-НЕ — элемент Шеффера ) в одном корпусе.

Характеристики:

| Модель | 74HC00N |

| Тип логики | CMOS |

|

Рабочее напряжение |

2 — 6 В |

|

Тип корпуса |

DIP (DIP-14) |

|

Потребляемый ток |

20мкА |

|

Диапазон рабочих температур |

-40°C..+125°C |

Таблица истинности для одного элемента NAND ( 2И-НЕ ):

| Вход A | Вход B | Выход Y |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Расположение выводов 74HC00:

Комплектация:

- 1x микросхема 74HC00N — логический элемент NAND / 2И-НЕ 74HC00

Загрузки:

НОУ ИНТУИТ | Лекция | Более сложные логические элементы

Аннотация: В лекции рассказывается о принципах работы, характеристиках и типовых схемах включения логических элементов, выполняющих сравнительно сложные функции – элементов Исключающее ИЛИ, И-ИЛИ-НЕ, триггеров Шмитта, а также приводятся схемотехнические решения, позволяющие реализовать на их основе часто встречающиеся функции.

Элементы Исключающее ИЛИ

Элементы Исключающее ИЛИ (по-английски — Exclusive-OR) также можно было бы отнести к простейшим элементам, но функция, выполняемая ими, несколько сложнее, чем в случае элемента И или элемента ИЛИ. Все входы элементов Исключающее ИЛИ равноправны, однако ни один из входов не может заблокировать другие входы, установив выходной сигнал в уровень единицы или нуля.

| Вход 1 | Вход 2 | Выход |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

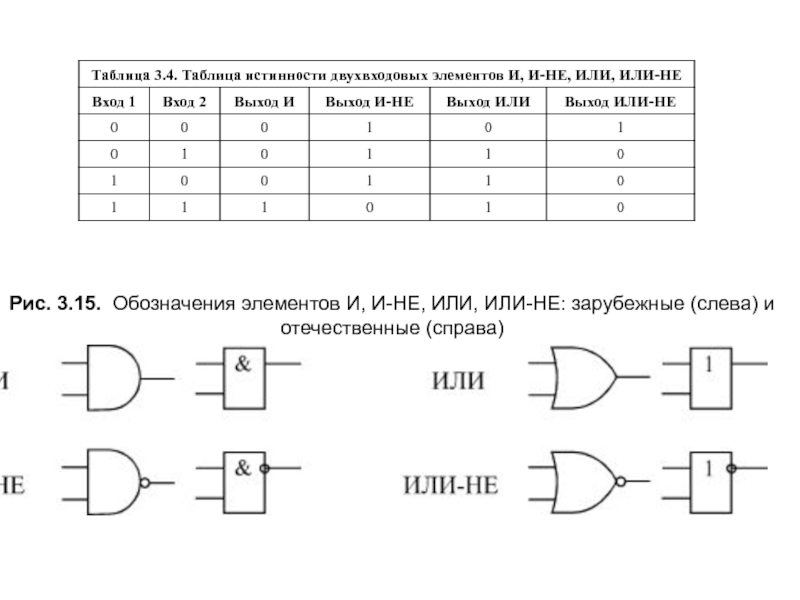

Рис. 4.1. Обозначения элементов Исключающее ИЛИ: зарубежные (слева) и отечественные (справа)

Под функцией Исключающее ИЛИ понимается следующее: единица на выходе появляется тогда, когда только на одном входе присутствует единица. Если единиц на входах две или больше, или если на всех входах нули, то на выходе будет нуль. Таблица истинности двухвходового элемента Исключающее ИЛИ приведена в табл. 4.1. Обозначения, принятые в отечественных и зарубежных схемах, показаны на рис. 4.1. Надпись на отечественном обозначении элемента Исключающее ИЛИ «=1» как раз и обозначает, что выделяется ситуация, когда на входах одна и только одна единица.

Элементов Исключающее ИЛИ в стандартных сериях немного. Отечественные серии предлагают микросхемы ЛП5 (четыре двухвходовых элемента с выходом 2С), ЛЛ3 и ЛП12, отличающиеся от ЛП5 выходом ОК. Слишком уж специфическая функция реализуется этими элементами.

С точки зрения математики, элемент Исключающее ИЛИ выполняет операцию так называемого суммирования по модулю 2. Поэтому эти элементы также называются сумматорами по модулю два. Как уже отмечалось в предыдущей лекции, обозначается суммирование по модулю 2 знаком плюса, заключенного в кружок.

Основное применение элементов Исключающее ИЛИ, прямо следующее из таблицы истинности, состоит в сравнении двух входных сигналов. В случае, когда на входы приходят две единицы или два нуля (сигналы совпадают), на выходе формируется нуль (см. табл. 4.1). Обычно при таком применении на один вход элемента подается постоянный уровень, с которым сравнивается изменяющийся во времени сигнал, приходящий на другой вход. Но значительно чаще для сравнения сигналов и кодов применяются специальные микросхемы компараторов кодов, которые будут рассмотрены в следующей лекции.

В качестве сумматора по модулю 2 элемент Исключающее ИЛИ используется также в параллельных и последовательных делителях по модулю 2, служащих для вычисления циклических контрольных сумм. Но подробно эти схемы будут рассмотрены в лекциях 14,15.

Важное применение элементов Исключающее ИЛИ — это управляемый инвертор (рис. 4.2). В этом случае один из входов элемента используется в качестве управляющего, а на другой вход элемента поступает информационный сигнал. Если на управляющем входе единица, то входной сигнал инвертируется, если же нуль — не инвертируется. Чаще всего управляющий сигнал задается постоянным уровнем, определяя режим работы элемента, а информационный сигнал является импульсным. То есть элемент Исключающее ИЛИ может изменять полярность входного сигнала или фронта, а может и не изменять в зависимости от управляющего сигнала.

Рис. 4.2. Элемент Исключающее ИЛИ как управляемый инвертор

В случае, когда имеется два сигнала одинаковой полярности (положительные или отрицательные), и при этом их одновременный приход исключается, элемент Исключающее ИЛИ может быть использован для смешивания этих сигналов (рис. 4.3). При любой полярности входных сигналов выходные сигналы элемента будут положительными. При положительных входных сигналах элемент Исключающее ИЛИ будет работать как элемент 2ИЛИ, а при отрицательных он будет заменять элемент 2И-НЕ. Такие замены могут быть полезны в тех случаях, когда в схеме остаются неиспользованными некоторые элементы Исключающее ИЛИ. Правда, при этом надо учитывать, что задержка распространения сигнала в элементе Исключающее ИЛИ обычно несколько больше (примерно в 1,5 раза), чем задержка в простейших элементах И, И-НЕ, ИЛИ, ИЛИ-НЕ.

Рис. 4.3. Применение элемента Исключающее ИЛИ для смешивания двух неодновременных сигналов

Рис. 4.4. Выделение фронтов входного сигнала с помощью элемента Исключающее ИЛИ

Еще одно важнейшее применение элемента Исключающее ИЛИ — формирование коротких импульсов по любому фронту входного сигнала (рис. 4.4). В данном случае не важно, положительный фронт входного сигнала или отрицательный, на выходе все равно формируется положительный импульс. Входной сигнал задерживается с помощью конденсатора или цепочки элементов, а затем исходный сигнал и его задержанная копия поступают на входы элемента Исключающее ИЛИ. В обеих схемах в качестве элементов задержки используются также двувходовые элементы Исключающее ИЛИ в неинвертирующем включении (на неиспользуемый вход подается нуль). В результате такого преобразования можно говорить об удвоении частоты входного сигнала, так как выходные импульсы следуют вдвое чаще, чем входные.

Данную особенность элементов Исключающее ИЛИ надо учитывать в том случае, когда на оба входа элемента поступают изменяющиеся одновременно сигналы. При этом на выходе элемента возможно появление коротких паразитных импульсов по любому из фронтов входных сигналов. Исключить их влияние на дальнейшую схему можно, например, с помощью синхронизации, подобной рассмотренной в предыдущем разделе.

| Функциональный состав | Серии | Имя | Аналог |

| 4 логических элемента 2И-НЕ | 164,К176

564,К561 |

ЛА7

ЛА7 |

CD4011

CD4011A |

| 2 логических элемента 4И-НЕ | 164,К176

564,К561 |

ЛА8

ЛА8 |

CD4012

CD4012A |

| 3 логических элемента 3И-НЕ | 164,К176

564,К561 КР1561 |

ЛА9

ЛА9 ЛА9 |

CD4023

CD4023A CD4023BE |

| 2

логических элемента 2И-НЕ

с открытым стоком |

564

КР1561 |

ЛА10

ЛА10 |

CD40107A

CD40107B |

| 4 логических элемента 2ИЛИ-НЕ | 164,К176

564,К561 КР1561 |

ЛЕ5

ЛЕ5 ЛЕ5 |

CD4001

CD4001A CD4001B |

| 2 логических элемента 4ИЛИ-НЕ | 164,К176

564,К561 КР1561 |

ЛЕ6

ЛЕ6 ЛЕ6 |

CD4002

CD4002A CD4002B |

| 3 логических элемента 3ИЛИ-НЕ | 164,К176

564,К561 КР1561 |

ЛЕ10

ЛЕ10 ЛЕ10 |

CD4025

CD4025A CD4025BE |

| 9И + элемент НЕ | 164,К176 | ЛИ1 | Б/А |

| 4 логических элемента 2И | КР1561 | ЛИ2 | CD4081B |

| 6

логических элементов «НЕ»

с блокировкой и запретом |

564,К561 | ЛН1 | MC14502A |

| 6 логических элементов «НЕ» | 564,К561 | ЛН2 | CD4069A |

| 6

повторителей с блокировкой для

видеомагнитофонов с 3 состояниями |

К561 | ЛН3 | MPD4503BC |

| Элемент логический универсальный | 164,К176 | ЛП1 | CD4007 |

| 4 логических элемента «исключающее ИЛИ» | 164,К176

564,К561 |

ЛП2

ЛП2 |

CD4030

CD4030A |

| 2

логических элемента 3ИЛИ-НЕ и

элемент НЕ |

164,К176 | ЛП4 | CD4000 |

| 2

логических элемента 4ИЛИ-НЕ и

элемент НЕ |

164,К176 | ЛП11 | Б/А |

| 2

логических элемента 4И-НЕ и

элемент НЕ |

164,К176 | ЛП12 | Б/А |

| 3 3-входовых мажоритарных элемента | 564,К561 | ЛП13 | Б/А |

| 4 схемы «исключающее ИЛИ» | КР1561 | ЛП14 | CD4070B |

| 5 преобразователей уровня КМОП-ТТЛ | 164,К176 | ПУ1 | Б/А |

| 6

преобразователей уровня

с инверсией КМОП-ТТЛ |

К176 | ПУ2 | CD4009 |

| 6 преобразователей уровня КМОП-ТТЛ | К176 | ПУ3 | CD4010 |

| 6

преобразователей уровня КМОП-ТТЛ

(6 мощных драйверов с защитой от входных перенапряжений) |

564,К561

КР1561 |

ПУ4

ПУ4 |

CD4050A

MC14050B |

| 4

преобразователя уровня с

прямым и инверсным выходами |

К176 | ПУ5 | Б/А |

| 4

преобразователя уровня (4 вентиля с 3

состояниями и индивидуальными запретами) |

564 | ПУ6 | CD40109A |

| 6

преобразователей уровня логической 1

с низкого на высокий с инверсией |

564,К561 | ПУ7 | Б/А |

| 6

преобразователей уровня логической 1

с низкого на высокий без инверсии |

564,К561 | ПУ8 | Б/А |

| 8-разрядный двунаправленный преобразователь уровня для сопряжения ТТЛ-КМОП | 564 | ПУ9 | CD40116 |

| 4 триггера Шмитта с входной логикой 2И-НЕ | 564,К561

КР1561 |

ТЛ1

ТЛ1 |

CD4093A

CD4093BE |

Справочник «Цифровые Интегральные Микросхемы»

Справочник «Цифровые Интегральные Микросхемы» [ Содержание ]2.4.2 Микросхемы типа ЛА, ЛИ

Чтобы рассмотреть схемотехнику, составим таблицу функций элементов И, И-НЕ для двух входов А и В (простейший вариант). Каждая переменная А и В моделируется электронным ключом, который можно замкнуть или разомкнуть. Если ключи соединены последовательно, то они работают согласно логике И: ток в цепи появится, если замкнуть оба ключа: и А и В. Если активными входными сигналами считать замыкание ключей А и В и назвать это событие логической 1, то, последовательно перебирая состояние этих ключей, составим таблицу входных и выходных данных для элементов И и И-НЕ.

| Логический элемент |

Входные переменные |

Выходная функция |

||

|---|---|---|---|---|

| А | B | И | НЕ-И | |

| 0 | 0 | 0 | 1 | |

| 0 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

Рассмотрим способ реализации логической операции И-НЕ на элементах ТТЛ. На рис. 2.8, а приведена принципиальная схема двухвходового логического элемента И-НЕ.

Рис. 2.8.а. Принципиальная схема логического элемента.

Подавая от ключей S1 и S2 на входы А и В напряжение высокого В и низкого Н уровней, составим таблицу выходных уровней элемента.

| Вход | Выход Q(НЕ-И) |

Вход | Выход Q(НЕ-И) |

||

|---|---|---|---|---|---|

| А | B | A | B | ||

| Н | Н | В | 0 | 0 | 1 |

| Н | В | В | 0 | 1 | 1 |

| В | Н | В | 1 | 0 | 1 |

| В | В | Н | 1 | 1 | 0 |

Напряжение низкого уровня Н появляется на выходе Q, когда на обоих входах А и В присутствует высокое напряжение В. Условное графическое обозначение двухвходового логического элемента показано на рис 2.8, в

Рис 2.8.в. Условное обозначение элемента.

Среди простейших ИС ТТЛ преобладают элементы И, И-НЕ. Каждый из корпусов ИС типа ЛА и ЛИ содержит от двух до четырех логических элементов, а микросхемы ЛА2 и ЛА19 содержат по одному логическому элементу И-НЕ на восемь и двенадцать входов соответственно.

Цоколевки микросхем типа ЛА и ЛИ и их условные графические обозначения приведены на рис. 2.9, а основные параметры даны в табл. 2.3.

Рис 2.9. Условные обозначения и цоколевки микросхем ЛИ

Рис 2.9. Условные обозначения и цоколевки микросхем ЛА

Следует особо выделить группу микросхем, логические элементы которых имеют выходы с открытым коллектором (ЛА7…ЛА11, ЛА13. ЛА18), (ЛИ2, ЛИ4, ЛИ5). Схема двухвходового логического элемента И-НЕ с открытым коллектором показана на рис. 2.10, а.

Рис. 2.10а. Принципиальная схема логического элемента И-НЕ

Для формирования выходного перепада напряжения к выходу такого элемента необходимо подключить внешний нагрузочный резистор Rн. Такие микросхемы применяются для обслуживания сегментов индикаторов, зажигания ламп накаливания, светодиодов (рис. 2.10,б).

Рис. 2.10б. Схема подключения ламп накаливания и светодиодов

При необходимости в схемах можно использовать элемент ТТЛ с двухтактным выходом. Для некоторых микросхем с открытым коллекторным выходом (ЛА11) нагрузку можно подключать к более высоковольтному источнику питания (рис. 2.10,в).

Рис. 2.10в. Схема подключения нагрузки к высоковольтному источнику

Такое включение необходимо для зажигания газоразрядных и электролюминесцентных индикаторов. Выходы с открытого коллектора используют для подключения обмоток реле.

Выходы нескольких элементов с открытым коллектором можно присоединять к общей нагрузке Rн (рис. 2.10, г).

Рис. 2.10г. Схема подключения нескольких элементов к общей нагрузке

Такое подключение позволяет реализовать логическую функцию И, называемую «монтажное И». Схему (рис. 2.10. г) используют для расширения числа входов логического элемента.

Следует помнить, что двухтактные выходы ТТЛ нельзя соединять параллельно, это приводит к токовой перегрузке одного из элементов.

Многовходовые составные логические элементы с открытым коллектором и общим сопротивлением нагрузки Rн реализуются наиболее просто, однако они не позволяют получить предельное быстродействие. Более лучший способ увеличения числа входов осуществляется с помощью специальной микросхемы-расширителя, имеющей дополнительные выводы коллектора и эмиттера фазоразделительного каскада VT2 (рис. 2.11). Одноименные вспомогательные выводы нескольких таких элементов можно объединять.

Рис. 2.11а. Принципиальная схема 2И-НЕ с дополнительными выводами коллектора и эмиттера.

Рис. 2.11б. Условное обозначение расширителя и способ соединения нескольких микросхем.

Микросхема К531ЛА16 (магистральный усилитель) может передавать данные в линию с сопротивлением 50 Ом.

Микросхемы ЛА17, ЛА19 — это логические элементы И-НЕ с тремя состояниями на выходе, т. е. они имеют дополнительный вход /ЕО (Enable output), дающий разрешение по выходу. На рис. 2.12 показана схема элемента, который имеет третье выходное состояние Z, когда выход размыкается.

Рис. 2.12. Принципиальная схема логического элемента с тремя состояниями на выходе.

Для этой цели в схему стандартного сложного инвертора ТТЛ вводится дополнительный инвертор DDI и диод VD2. Если на этот вход /ЕО подать от переключателя S1 напряжение высокого уровня — 1, то выходное напряжение инвертора DD1 станет низким, т. е. катод диода VD2 будет практически соединен с корпусом. Из-за этого коллектор транзистора VT2 будет иметь нулевой потенциал, т. е. транзистор VT2 будет закрыт. Транзисторы VT3 и VT4 будут находиться в режиме отсечки, т. е. оба закрыты. Следовательно, выходной вывод как бы «висит» в воздухе, микросхема переходит в состояние Z с очень большим выходным сопротивлением. Если на вход ЕО подается разрешающий низкий уровень — О, то логический элемент И-НЕ работает как в обычном режиме.

| Вход | Выход | ||

|---|---|---|---|

| /EO | I | /Y | |

| 0 | 0 1 | 1 0 | |

| 1 | 0 1 | Z | |

Такие логические элементы разработаны специально для обслуживания проводника шины данных. Если к такому проводнику присоединить много выходов, находящихся в состоянии Z, то они не будут влиять друг на друга. Активным передающим сигналом должен быть лишь один логический элемент, только от его выхода в проводник шины данных будет поступать информация. Следовательно, соединенные вместе выходы не должны быть одновременно активными.

Чтобы сигналом разрешения (низкий уревень — О) , подаваемым на вход /EO, подключался к проводнику выход только одного логического элемента, необходимо предусмотреть дополнительный (защитный) временной интервал, т. е. переключать входы /ЕО различных элементов с паузой. Сигналы разрешения, даваемые выходам разных элементов, не должны перекрываться.

Микросхема К531ЛА19-это 12-входовый логический элемент И-НЕ с дополнительным инверсным входом /ЕО. Сигнал появится на его выходе, если на вход /ЕО подано напряжение низкого уровня — О. Выход логического элемента перейдет в разомкнутое состояние Z, если на вход /ЕО подается напряжение высокого уровня. В состоянии Z элемент потребляет ток Iпот.z=25 мА. Время задержки перехода выхода к разомкнутому состоянию tзд.1z= 16 нс, время задержки перехода выхода tзд.0z= 12 нс (от напряжения низкого выходного уровня), при условии, что Сн = 15 пФ [1].

4 простых конструкции на логических элементах 2И-НЕ | Лампа Эксперт

Сегодня даже заядлые любители цифровой техники в своих конструкциях используют в основном микросхемы большой степени интеграции, а то и готовые отлаженные модули. Удобно, конечно, но знаний об азах электроники и алгебре логики такой подход, увы, не прибавляет. Данная статья предназначена тем, кто хочет не просто собрать что-то действующее, но и понять, как конструкция работает.

Таких людей, не работающих под копирку, а следовательно, способных создать что-то новое, становится все меньше. Но если даже несколько человек найдут в этой статье что-то новое и полезное для себя, то можно сказать, что писалась она не зря. Ну а любителям модульных конструкций и людей с менталитетом «да я лучше готовое куплю» советую просто закрыть страничку, если, конечно, нет желания написать в комментариях какую-нибудь гадость.

Что такое 2И-НЕ и как это работает

Для примера мы рассмотрим состав и принцип работы микросхемы К155ЛА3, как типичного и старейшего представителя «мелкой логики». Взглянем на состав этой микросхемы.

Состав микросхемы К155ЛА3Состав микросхемы К155ЛА3

Мы видим 4 абсолютно одинаковых узла (логических элемента), никак не связанных между собой. Единственными общими для всех элементов выводами являются выводы питания (7 и 14). Рассмотрим работу одного из них, но прежде определимся с понятиями логической единицы и логического нуля (далее «1» и «0»).

- Логическая единица – сигнал высокого уровня. В цифровой схемотехнике «единицей» считается напряжение равное или близкое к напряжению питания микросхемы относительно общего провода.

- Логическая единица – сигнал низкого уровня. В цифровой схемотехнике «нулем» считается напряжение равное или близкое к потенциалу общего провода (0 В).

В цифровой схемотехнике существует общепринятый диапазон величин логического нуля и единицы. Обычно за «1» принимается напряжение выше 0.8 питающего, а за «0» — ниже 0.1 питающего. Для микросхем серии К155 (Uпит. = +5 В), к примеру, единицей будет уровень выше 4 В, а нулем – ниже 0.5 В. Промежуточные значения различными сериями и типами микросхем могут интерпретироваться по-разному, поэтому выходить из указанных диапазонов не рекомендуется.

А теперь вернемся к нашей микросхеме и рассмотрим работу одного из логических элементов. Пока на входах этого элемента (выводы 1 и 2 для верхнего по схеме) низкий логический уровень, на выходе (вывод 3) присутствует высокий. При подаче «1» только на вывод 1 или 2 не изменит состояния выхода. Но если подать «1» одновременно на выводы 1 и 2, то элемент переключится и на его выходе появится «0». Стоит на один из входов подать «0», как независимо от состояния второго входа на выходе установится «1».

Таблица истинности элемента 2И-НЕ

Рассмотрев табличку, несложно понять, откуда взялось название элемента 2И-НЕ. Когда на двух входах будет высокий уровень («2И»), на выходе установится низкий («НЕ»). О том, что это именно элемент «НЕ» говорит кружочек на выводе выхода, а то, что входы работают по алгоритму «И» можно узнать из значка «&», расположенного на логическом элементе. Ну а теперь перейдем к практическому применению полученных знаний, причем в своих конструкциях мы будем использовать микросхемы разных серий.

Электронная сирена

Начнем с самого простого и соберем имитатор звука сирены, который можно использовать для озвучивания игрушечных автомобилей или в качестве велосипедного звонка. Конструкция собрана на двух микросхемах К155ЛА3.

Схема электронной сиреныСхема электронной сирены

Схема состоит из трех генераторов, собранных на элементах DD1.1-DD1.2, DD2.1-DD2.2 и DD2.3-DD2.4. Единственное их отличие друг от друга – различная частота переключения, которая зависит от емкости конденсаторов С1, С2 и С3 соответственно. Рассмотрим работу одного из них, собранного на элементах DD1.1-DD1.2.

При подаче питания один из элементов переключается в произвольное положение. Предположим, Это DD1.1, выставивший на своем выходе «1». Эта единичка переключает DD1.2 в низкий уровень. Через цепь R1, выход DD1.1 и выход DD1.2 начинается зарядка конденсатора С1. Скорость его зарядки зависит от номинала резистора и емкости самого конденсатора.

Как только С1 зарядится до определенного значения, на входах DD1.1 появится высокий логический уровень. DD1.1, а за ним и DD1.2 переключатся, и конденсатор начнет перезаряжаться напряжением обратной полярности через те же цепи. По мере его зарядки напряжение на входах DD11 снизится до логического нуля и элементы снова переключатся. Далее процесс повторится.

Генератор, работу которого мы разобрали, переключается с частотой около 1 Гц. Два остальных, собранных на DD2.1-DD2.2 и DD2.3-DD2.4, работают на звуковых частотах 500 и 1000 Гц. Управляет ими наш первый. Он поочередно запускает генераторы – один сигналом с выхода 6, второй тем же сигналом, проинвертированным элементом DD1.3.

При этом остановленный генератор выдает на свой выход «1». Это позволяет использовать элемент DD1.4 в качестве коммутатора. На его выходе первые 0.5 сек присутствует сигнал с частотой 500, а вторые 0.5 сек 1000 Гц. Этот сигнал усиливается транзистором T1 и поступает на громкоговоритель ВА1, который воспроизводит звук изменяющейся тональности.

В конструкции можно применить аналогичные микросхемы серии 133, 555 и 1533. При использовании серии 133 потребление энергии будет максимальным, а серия 1533 самая экономичная. Цоколевка всех серий одинакова. На месте T1 может работать любой маломощный кремниевый транзистор структуры n-p-n. Источник питания – любой напряжением 4.5 – 5 В. Динамическая головка должна иметь сопротивление обмотки 4-8 Ом и мощностью до 1 Вт.

При желании скорость переключения тонов и их частоты можно изменить подбором емкости конденсаторов С1, С2 и С3. Уровень громкости можно изменить подбором номинала резистора R4.

«Живой» мышонок

Эта конструкция позволит оживить игрушечного мышонка или любую другую игрушку. При поднесении к зверьку руки, он начинает попискивать и моргать глазами. В датчике использованы все те же элементы 2И-НЕ, но микросхема выбрана серии 561.

Отличие серии 561 от той же 155 состоит в том, что она собрана не на обычных кремниевых n-p (технология ТТЛ), а на полевых транзисторах с изолированным затвором (технология КМОП). Это не только существенно (до микроампер) снижает ток потребления самой микросхемой, но и обеспечивает высокое (десятки МОм) сопротивление по входам.

Схема датчик электромагнитного поляСхема датчик электромагнитного поля

Рассмотрим работу схемы. Напряжение, наведенное электромагнитным полем в антенне Ant1, поступает на логический элемент DD1.1 и детектируется цепью D1,D2, С2. Далее сигнал подается на ключ, собранный на элементе DD1.4, нагрузкой которого служат светодиоды LED1 и LED2 (глаза зверька). Этот же сигнал управляет работой генератора звуковой частоты, собранного на элементах DD1.2, DD1.3. Принцип работы такого генератора мы разбирали в предыдущей конструкции, а нагружен он на пьезоэлектрический звонок BQ1.

Таким образом, если подойти близко к антенне, то электромагнитное поле, наведенное в нашем теле домовой проводкой и электроприборами, вызовет срабатывание схемы – «глаза» мышонка начнут помигивать, а пьезозвонок попискивать. Если подойти к антенне совсем близко, то «глаза» будут гореть постоянно и звук в излучателе станет непрерывным.

В конструкции можно использовать любой пъезоэлектрический излучатель и любые индикаторные светодиоды. Микросхему 561ЛА7 можно заменить на аналогичную серий 564 или 176. Во втором случае напряжение питания должно быть не ниже 9 В. Поскольку конструкция в ждущем режиме потребляет минимум энергии, выключателя питания не предусмотрено. Частоту звукового генератора можно изменить подбором емкости конденсатора С3 и номиналом резистора R2.

Если укоротить антенну до нескольких сантиметров, то игрушка может превратиться в прибор для поиска скрытой проводки.

Терменвокс

Несмотря на свою простоту, эта конструкция является самым настоящим музыкальным инструментом, созданным советским изобретателем Л. С. Терменом в далеком 1920 году. Немного попрактиковавшись, на нем можно исполнять достаточно сложные произведения. Взглянем на схему инструмента.

Схема терменвокса на логических элементахСхема терменвокса на логических элементах

Перед нами уже знакомые нам генераторы, собранные на элементах микросхем DD1.1 – DD1.3 и DD2.1 – DD2.3. Частотозадающими цепями этих генераторов являются С2, R1 и С3, R2, P1. Кроме того, в первый генератор (верхний по схеме) добавлены элементы Ant1 и конденсатор С1. Они являются дополнительной частотозадающей цепью, емкость которой изменяется в зависимости от положения тела исполнителя (обычно руки) относительно антенны.

Сигналы с обоих генераторов поступают на смеситель, выполненный на микросхеме DD3, все элементы которого соединены параллельно для увеличения выходной мощности. Задача смесителя – сравнить частоты генераторов и выделить их разность – так называемую частоту биений. Полученный сигнал через согласующий трансформатор поступает на динамическую головку. Резистор P2 служит для регулировки громкости звука.

Рассмотрим процессы, происходящие в приборе во время его работы. Изначально оба генератора настраиваются на одну и ту же частоту (в нашем случае несколько десятков килогерц) – это делает исполнитель перед выступлением при помощи переменного резистора P1. Поскольку частоты, поступающие на вход смесителя, одинаковы, разность частот на его выходе равна нулю, в громкоговорителе звука нет.

Если теперь поднести руку к антенне Ant1, то частота первого генератора за счет добавленной телом оператора емкости начнет уменьшаться. Чем ближе рука к антенне, тем ниже частота. Второй же генератор продолжает работать в том же режиме, на который был настроен. В результате на выходе смесителя появится частота, соответствующая разности частот генераторов, и лежать она будет в звуковом диапазоне. В динамической головке появится звук определенного тона, который тем выше, чем ближе мы подносим руку к антенне.

Важно! Для того, чтобы генераторы не влияли на работу друг друга по линии питания, их собрали на разных микросхемах, которые запитали каждую от своего развязывающего RC фильтра (цепочки R3, С5 и R4, С6).

В конструкции вместо 176ЛА7 можно использовать 561ЛА7 или 564ЛА7. При этом напряжение питание допустимо снизить до 5 В. Трансформатор Tr1 – выходной трансформатор от транзисторного приемника или абонентского громкоговорителя (можно взять вместе с переменным резистором и динамиком). Антенна Ant1 – металлический штырь длиной 30-40 см или телескопическая антенна от радиоприемника.

Играют на инструменте следующим образом: после включения питания резистором P1 подстраивают частоту второго генератора так, чтобы в громкоговорителе пропал звук (нулевые биения). Подносят правую руку к антенне и извлекают звук нужного тона – чем ближе рука, тем выше нота. При этом левой рукой регулируют громкость звука при помощи потенциометра P2.

Лев Термен играет на созданном им инструментеЛев Термен играет на созданном им инструменте

Чувствительность антенны терменовокса настолько высока, что изменять высоту ноты можно даже изменением положения пальцев. Это удобно использовать для создания эффекта «вибрато».

Охранная сигнализация

И напоследок конструкция, которая позволит организовать охрану закрытого объекта, к примеру, дачного домика. Интересна эта конструкция тем, что на базе уже знакомых нам элементов 2И-НЕ в ней собран триггер – устройство с двумя устойчивыми состояниями. Взглянем на схему сигнализации.

Схема простой охранной сигнализацииСхема простой охранной сигнализации

При подаче питания один из элементов микросхемы переключается в произвольное состояние. Предположим, у DD1.1 на выходе появилась «1» (вывод 3). Этот сигнал поступил на вход элемента DD1.2 (вывод 4). На втором его входе тоже «1», поскольку он «подтянут» к + 5 В резистором R3, а кнопка S2 разомкнута (вывод 5). В результате на выходе DD1.2 появляется «0», схема заняла одно из устойчивых состояний. Если первым в «1» установится элемент DD1.2, то он аналогичным образом переключит DD1.1 в «0».

Для активации режима охраны необходимо кратковременно нажать на кнопку S2 «сброс». При этом элементы DD1.1 и DD1.2 принудительно примут состояние «0» и «1» соответственно, независимо от их предыдущего положения (следим за состоянием входов при нажатии на кнопку сброса).

Если теперь нажать на кнопку S2 «тревога», то на вход первого элемента поступит «0», на его выходе появится «1», которая переключит DD1.2 в противоположное состояние (на выходе «0») и поступит на исполнительное устройство, включающее сигнал тревоги.

Важно! Если отпустить кнопку S1, то состояние логических элементов не изменится и сигнал тревоги снят не будет. Для того, чтобы вернуть схему в исходное состояние, необходимо кратковременно нажать на кнопку S2.

С этим все понятно, но где же этот триггер, о котором шла речь? Элементы DD1.2 и DD1.2, соединенные таким «перекрестным» образом, и есть триггер с двумя устойчивыми состояниями, который называют RS-триггером. На схеме он обозначается так:

Схематическое обозначение RS-триггераСхематическое обозначение RS-триггера

А RS-триггер, собранный на элементах 2И-НЕ, будет иметь следующие соответствия:

RS-триггер на логических элементахRS-триггер на логических элементах

Таблица же истинности этого узла выглядит следующим образом:

Таблица истинности для RS-триггераТаблица истинности для RS-триггера

В RS-триггерах в интегральном исполнении вход R (reset, англ. сброс) имеет приоритет. Он сбрасывает триггер (Q = «0», Q инверсный = «1») независимо от состояния входа S.

На месте DD1 могут работать аналогичные микросхемы серий 133, 555, 1533. Кнопка S2 устанавливается в любом удобном месте и, естественно, скрытно. S1 – концевой выключатель, срабатывающий на открытие двери или окна. Если окон много, то кнопку можно продублировать, подключив параллельно S1 необходимое количество дополнительных. В этом случае сигнал тревоги будет подаваться при срабатывании любой из этих кнопок. Конденсатор С1 помехозащитный. Он исключает ложные срабатывания системы из-за электромагнитных наводок на кнопку S1 и ее провод.

На этом обзор устройств, собранных на элементах 2И-НЕ, можно завершить. Теперь мы знаем, как работает этот логический элемент, и можем использовать его в самостоятельных разработках.

Элементы Исключающее ИЛИ/Исключающее ИЛИ-НЕ/Нечётность/Чётность

| Библиотека: | Базовые |

| Введён в: | 2.0 Beta 1 для Исключающее ИЛИ/Нечётность/Чётность; 2.0 Beta 6 для Исключающее ИЛИ-НЕ |

| Внешний вид: |

Поведение

Элементы Исключающее ИЛИ, Исключающее ИЛИ-НЕ, Нечётность и Чётность вычисляют соответствующую функцию от значений на входах и выдают результат на выход.

По умолчанию, неподключенные входы игнорируются — то есть, если входы действительно не имеют ничего подключенного к ним — даже провода. Таким образом, вы можете добавить 5-входовый элемент, но подключить только два входа, и он будет работать как 2-входовый элемент; это избавляет вас от необходимости беспокоиться о настройке количества входов каждый раз при создании элемента. (Если все входы не подключены, то на выходе значение ошибки X.) Некоторые пользователи, однако, предпочитают, чтобы Logisim настаивал, чтобы все входы были подключены, поскольку это соответствует реальным элементам. Вы можете включить это поведение, выбрав меню Проект > Параметры…, перейдя на вкладку Моделирование, и выбрав вариант Ошибка для неопределённых входов

для Выход элемента при неопределённости

.

Двухвходовая таблица истинности для элементов следующая.

| x | y | Исключающее ИЛИ | Исключающее ИЛИ-НЕ | Нечётность | Чётность |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 |

Как вы можете видеть, элементы Нечётность и Исключающее ИЛИ ведут себя одинаково в случае двух входов; аналогично, элементы Чётность и Исключающее ИЛИ-НЕ ведут себя одинаково. Но если входов с определённым значением больше двух, то элемент Исключающее ИЛИ будет давать на выходе 1, когда единица строго на одном входе, тогда как элемент Нечётность даст на выходе 1, когда единица на нечётном количестве входов. Элемент Исключающее ИЛИ-НЕ будет давать на выходе 1, когда входов с единицей строго не один, тогда как элемент Чётность даст 1, когда входов с единицей чётное количество. Элементы Исключающее ИЛИ и Исключающее ИЛИ-НЕ имеют атрибут, названный Многовходовое поведение, который позволяет настроить их на использование поведения элементов Нечётность и Чётность.

Если на каких-либо входах значение ошибки (например, если противоречивые значения поступают на один и тот же провод) или плавающее значение, то на выходе будет значение ошибки.

Многобитные версии каждого элемента будут выполнять свои однобитные преобразования над входами поразрядно.

Примечание: многие специалисты утверждают, что поведение фигурного элемента Исключающее ИЛИ должно соответствовать поведению элемента Нечётность, но по этому вопросу нет согласия. Поведение Logisim по умолчанию для элемента Исключающее ИЛИ основано на стандарте IEEE 91. Это также согласуется с интуитивным пониманием термина Исключающее ИЛИ: официант, спрашивающий, хотите вы гарнир из картофельного пюре, моркови, зеленого горошка, или шинкованной капусты, примет только один выбор, а не три, независимо от того, что вам могут сказать некоторые специалисты. (Должен признать, однако, что я не подвергал это заявление серьезным испытаниям.) Вы можете настроить элементы Исключающее ИЛИ и Исключающее ИЛИ-НЕ на использование одного из вариантов, меняя его атрибут Многовходовое поведение

.

Контакты (предполагается, что компонент направлен на восток)

- Западный край (входы, разрядность соответствует атрибуту Биты данных)

Входы компонента. Их будет столько, сколько указано в атрибуте Количество входов.

Заметьте, что если вы используете фигурные элементы, то западный край элементов Исключающее ИЛИ и Исключающее ИЛИ-НЕ будет искривлён. Тем не менее, входные контакты расположены вряд. Logisim отрисовывает короткие отрезки чтобы показать это; если вы перекроете отрезок, программа будет без предупреждений предполагать, что вы не хотели перекрыть его. При использовании «Вида для печати», эти отрезки не будут отрисованы, если не подключены к проводам.

- Восточный край (выход, разрядность соответствует атрибуту Биты данных)

Выход элемента, значение на котором вычисляется на основании текущих значений на входах, как описано выше.

Атрибуты

Когда компонент выбран, или уже добавлен, клавиши от 0 до 9 меняют его атрибут Количество входов

, комбинации от Alt-0 до Alt-9 меняют его атрибут Биты данных

, а клавиши со стрелками меняют его атрибут Направление

.

- Направление

- Направление компонента (его выхода относительно его входов).

- Биты данных

- Разрядность входов и выходов компонента.

- Размер элемента

- Определяет, следует отрисовывать широкую или узкую версию компонента. Это не влияет на количество входов, которое определяется атрибутом Количество входов; правда, если количество входов превышает 3 (для узкого компонента) или 5 (для широкого), то элемент будет отрисовываться с «крыльями», чтобы вместить запрошенное количество входов.

- Количество входов

- Определяет, сколько контактов на западном крае будет иметь компонент.

- Многовходовое поведение (только для Исключающее ИЛИ и Исключающее ИЛИ-НЕ)

- Когда входов три или более, то значение на выходе элементов Исключающее ИЛИ и Исключающее ИЛИ-НЕ будет основано или на том, что 1 строго на одном входе (по умолчанию), или на нечётном количестве входов.

Поведение Инструмента Нажатие

Нет.

Поведение Инструмента Текст

Нет.

Назад к Справке по библиотеке

Таблицы истинности логической алгебры для логических вентильных функций

Помимо стандартного логического выражения, входная и выходная информация любого логического элемента Logic Gate или схемы может быть представлена в стандартной таблице, чтобы дать визуальное представление о функции переключения системы.

Таблица, используемая для представления логического выражения функции логического вентиля, обычно называется таблицей истинности . Таблица истинности логического элемента показывает каждую возможную комбинацию входов для элемента или схемы с результирующим выходом в зависимости от комбинации этих входов.

Например, рассмотрим одну логическую схему с двумя входами с входными переменными, обозначенными как A и B. Существует «четыре» возможных комбинации входов или 2 2 из «OFF» и «ON» для двух входов. Однако, имея дело с логическими выражениями и особенно с таблицами истинности логических вентилей, мы обычно не используем «ON» или «OFF», а вместо этого даем им битовые значения, которые представляют логический уровень «1» или логический уровень «0» соответственно.

Тогда четыре возможных комбинации A и B для логического элемента с 2 входами задаются как:

- Комбинация входов 1.- «ВЫКЛ» — «ВЫКЛ» или (0, 0)

- Комбинация входов 2. — «ВЫКЛ» — «ВКЛ» или (0, 1)

- Комбинация входов 3. — «ВКЛ» — «ВЫКЛ» или (1, 0)

- Комбинация входов 4. — «ВКЛ» — «ВКЛ» или (1, 1)

Следовательно, логическая схема с 3 входами будет иметь 8 возможных комбинаций входов или 2 3 , а логическая схема с 4 входами будет иметь 16 или 2 4 и так далее по мере увеличения количества входов. Тогда логическая схема с числом входов «n» будет иметь 2 n возможных комбинаций входов как «ВЫКЛ», так и «ВКЛ».

Итак, чтобы упростить понимание, в этом руководстве мы будем иметь дело только со стандартными логическими вентилями типа с двумя входами , но принципы остаются теми же самыми для вентилей с более чем двумя входами.

Тогда таблицы истинности для логического элемента И с 2 входами, логического элемента ИЛИ с 2 входами и логического элемента НЕ с одним входом представлены как:

2 входа И ворота

Для логического элемента И с двумя входами, выход Q является истинным, если ОБА входа A «И», вход B оба истинны, что дает логическое выражение: (Q = A и B).

| Символ | Таблица истинности | ||

| A | B | Q | |

| 0 | 0 | 0 | |

| 0 | 1 | 0 | |

| 1 | 0 | 0 | |

| 1 | 1 | 1 | |

| Логическое выражение Q = A.B | Если прочитать как A и B, получится Q | ||

Обратите внимание, что логическое выражение для логического элемента И с двумя входами может быть записано как: A.B или просто AB без десятичной точки.

2-входное ИЛИ (включительное ИЛИ) Gate

Для логического элемента ИЛИ с 2 входами выход Q является истинным, если ЛИБО вход A «ИЛИ», вход B истинен, что дает логическое выражение: (Q = A или B).

| Символ | Таблица истинности | ||

| A | B | Q | |

| 0 | 0 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | |

| 1 | 1 | 1 | |

| Логическое выражение Q = A + B | При чтении A ИЛИ B дает Q | ||

НЕ затвор (инвертор)

Для одиночного входного логического элемента НЕ выход Q истинен ТОЛЬКО, когда вход «НЕ» истинен, выход является инверсией или дополнением входа, дающим логическое выражение: (Q = НЕ А).

| Символ | Таблица истинности | |

| A | Q | |

| 0 | 1 | |

| 1 | 0 | |

| Логическое выражение Q = НЕ A или A | Если при инверсии A получается Q | |

Вентили И-НЕ и ИЛИ-ИЛИ представляют собой комбинацию вентилей И и ИЛИ, соответственно, с вентилем НЕ (инвертор).

2-входная И-НЕ (не И), вентиль

Для логического элемента И-НЕ с двумя входами выход Q НЕ истинен, если ОБЕИХ вход A и вход B истинны, что дает логическое выражение: (Q = not (A AND B)).

| Символ | Таблица истинности | ||

| A | B | Q | |

| 0 | 0 | 1 | |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | |

| 1 | 1 | 0 | |

| Логическое выражение Q = A .B | При чтении как A и B получается НЕ-Q | ||

2 входа NOR (Not OR) Gate

Для логического элемента ИЛИ-ИЛИ с 2 входами выход Q является истинным, если ОБА вход A и вход B НЕ истинны, что дает логическое выражение: (Q = not (A OR B)).

| Символ | Таблица истинности | ||

| A | B | Q | |

| 0 | 0 | 1 | |

| 0 | 1 | 0 | |

| 1 | 0 | 0 | |

| 1 | 1 | 0 | |

| Логическое выражение Q = A + B | При чтении как A ИЛИ B дает НЕ-Q | ||

Помимо стандартных логических вентилей, существуют также два специальных типа функций логических вентилей, которые называются вентилем исключающее ИЛИ и вентилем исключающее ИЛИ.Логическое выражение, указывающее на функцию «Исключающее ИЛИ» или «Исключающее ИЛИ», относится к символу со знаком плюс внутри круга (⊕).

Коммутационные действия обоих этих типов вентилей могут быть созданы с использованием вышеуказанных стандартных логических вентилей. Однако, поскольку они являются широко используемыми функциями, теперь они доступны в стандартной форме IC и включены здесь в качестве справочных.

2 входа EX-OR (Исключающее ИЛИ) Gate

Для логического элемента Ex-OR с 2 входами выход Q является истинным, если ЛИБО вход A или вход B истинен, но НЕ оба дают логическое выражение: (Q = (A и NOT B) или (NOT A и Б)).

| Символ | Таблица истинности | ||

| A | B | Q | |

| 0 | 0 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | |

| 1 | 1 | 0 | |

| Логическое выражение Q = A ⊕ B | |||

2 входа EX-NOR (Exclusive NOR) Gate

Для логического элемента Ex-NOR с 2 входами выход Q является истиной, если ОБА вход A и вход B одинаковы, либо истина, либо ложь, что дает логическое выражение: (Q = (A и B) или (NOT A а НЕ Б)).

| Символ | Таблица истинности | ||

| A | B | Q | |

| 0 | 0 | 1 | |

| 0 | 1 | 0 | |

| 1 | 0 | 0 | |

| 1 | 1 | 1 | |

| Логическое выражение Q = A ⊕ B | |||

Обзор логических вентилей с 2 входами

В следующей таблице истинности сравниваются логические функции вышеупомянутых логических вентилей с 2 входами.

| Входы | Вывод таблицы истинности для каждого гейта | ||||||

| А | B | И | NAND | ИЛИ | NOR | EX-OR | EX-NOR |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

В следующей таблице приведен список общих логических функций и их эквивалентные логические обозначения.

| Логическая функция | Логическая запись |

| И | A.B |

| ИЛИ | А + В |

| НЕ | A |

| NAND | A .B |

| NOR | А + В |

| EX-OR | (A.B) + (A.B) или A ⊕ B |

| EX-NOR | (A.B) + (A.B) или A ⊕ B |

Таблицы истинности логических вентилей с 2 входами приведены здесь в качестве примеров работы каждой логической функции, но есть намного больше логических вентилей с 3, 4 и 8 отдельными входами.Множественные входные вентили ничем не отличаются от простых вентилей с 2 входами, описанных выше. Таким образом, вентиль И с 4 входами по-прежнему требует наличия ВСЕХ 4 входов для получения требуемого выхода на Q, и его большая таблица истинности будет отражать это.

Что такое логический вентиль (AND, OR, XOR, NOT, NAND, NOR и XNOR)? Определение с сайта WhatIs.com

Логический вентиль — это устройство, которое действует как строительный блок для цифровых схем.Они выполняют основные логические функции, которые являются фундаментальными для цифровых схем. В большинстве электронных устройств, которые мы используем сегодня, есть логические вентили. Например, логические вентили могут использоваться в таких технологиях, как смартфоны, планшеты или в устройствах памяти.

В схеме логические вентили будут принимать решения на основе комбинации цифровых сигналов, поступающих с их входов. Большинство логических вентилей имеют два входа и один выход. Логические вентили основаны на булевой алгебре. В любой момент каждый терминал находится в одном из двух двоичных состояний: ложно, или истинно, .Ложь представляет 0, а истина представляет 1. В зависимости от типа используемого логического элемента и комбинации входов двоичный выход будет отличаться. Логический вентиль можно представить себе как выключатель света, в котором в одном положении выход выключен — 0, а в другом — включен — 1. Логические вентили обычно используются в интегральных схемах (IC).

Базовые логические вентили

Существует семь основных логических вентилей: И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, НЕ, И-НЕ, ИЛИ-ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ.

И | ИЛИ | XOR | НЕ | NAND | NOR | XNOR

Логический элемент И назван так потому, что, если 0 называется «ложным», а 1 называется «истинным», элемент действует так же, как логический оператор «И».На следующем рисунке и в таблице показаны символы схемы и логические комбинации для логического элемента И. (В символе входные клеммы находятся слева, а выходная клемма — справа.) Выходной сигнал «истина», когда оба входа «истина». В противном случае вывод будет «ложным». Другими словами, выход равен 1 только тогда, когда оба входа один И два равны 1.

И ворота

| Вход 1 | Ввод 2 | Выход |

| 1 | ||

| 1 | ||

| 1 | 1 | 1 |

Логический элемент ИЛИ получил свое название благодаря тому факту, что он ведет себя по образцу логического включающего «или».«Выход -« истина », если один или оба входа« истина ». Если оба входа« ложь », то выход« ложь ». Другими словами, для выхода будет 1, по крайней мере, вход один ИЛИ два должны быть 1.

OR ворота

| Вход 1 | Ввод 2 | Выход |

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 | 1 |

Логический элемент XOR ( исключающее ИЛИ ) вентиль действует так же, как логическое «или / или».«Выходной сигнал« истина », если один из входов, но не оба, являются« истиной ». Выходной сигнал« ложь », если оба входа« ложь »или если оба входа« истина ». Другой способ взглянуть на это Схема должна следить за тем, чтобы на выходе было 1, если входы разные, и 0, если входы одинаковые.

Логический элемент XOR

| Вход 1 | Ввод 2 | Выход |

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 |

Логический инвертор , иногда называемый логическим элементом НЕ , чтобы отличать его от других типов электронных инверторных устройств, имеет только один вход.Он меняет логическое состояние на обратное. Если на входе 1, то на выходе 0. Если на входе 0, то на выходе 1.

Инвертор или НЕ вентиль

Логический элемент И-НЕ работает как логический элемент И, за которым следует элемент НЕ. Он действует как логическая операция «и» с последующим отрицанием. На выходе будет «ложь», если оба входа «истина». В противном случае на выходе будет «истина».

Логический элемент NAND

| Вход 1 | Ввод 2 | Выход |

| 1 | ||

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 |

Логический элемент ИЛИ представляет собой комбинацию логического элемента ИЛИ, за которым следует инвертор.Его выход будет «истина», если оба входа «ложь». В противном случае вывод будет «ложным».

NOR ворота

| Вход 1 | Ввод 2 | Выход |

| 1 | ||

| 1 | ||

| 1 | ||

| 1 | 1 |

Логический элемент XNOR (исключающее ИЛИ) — это комбинированный вентиль XOR, за которым следует инвертор.Его вывод — «истина», если входы одинаковые, и «ложь», если входы разные.

Вентиль XNOR

| Вход 1 | Ввод 2 | Выход |

| 1 | ||

| 1 | ||

| 1 | ||

| 1 | 1 | 1 |

Сложные операции могут выполняться с использованием комбинаций этих логических вентилей.Теоретически нет ограничений на количество ворот, которые могут быть объединены в одно устройство. Но на практике существует ограничение на количество ворот, которые могут быть упакованы в данное физическое пространство. Массивы логических вентилей находятся в цифровых ИС. По мере развития технологии ИС требуемый физический объем для каждого отдельного логического элемента уменьшается, и цифровые устройства того же или меньшего размера становятся способными выполнять все более сложные операции с постоянно увеличивающейся скоростью.

Состав логических вентилей

Высокий или низкий двоичные состояния представлены разными уровнями напряжения.Логическое состояние терминала может и обычно часто изменяется по мере того, как схема обрабатывает данные. В большинстве логических вентилей низкое состояние составляет приблизительно ноль вольт (0 В), а высокое состояние — приблизительно пять вольт положительного напряжения (+5 В).

Логические вентили могут быть выполнены из резисторов и транзисторов или диодов. Резистор обычно можно использовать как подтягивающий или понижающий резистор. Подтягивающие и понижающие резисторы используются, когда есть какие-либо неиспользуемые входы логического элемента для подключения к логическому уровню 1 или 0.Это предотвращает ложное переключение ворот. Подтягивающие резисторы подключены к Vcc (+ 5 В), а подтягивающие резисторы подключены к земле (0 В).

Обычно используются логические вентили TTL и CMOS. ИС TTL или транзисторно-транзисторной логики будут использовать биполярные переходные транзисторы типа NPN и PNP. КМОП, или дополнительные металл-оксидно-кремниевые ИС, построены из полевых транзисторов типа MOSFET или JFET. ИС TTL обычно обозначаются как микросхемы серии 7400, в то время как КМОП-микросхемы часто обозначаются как микросхемы серии 4000.

Digital Logic — learn.sparkfun.com

Добавлено в избранное Любимый 32Комбинационная логика

Комбинационные схемы состоят из пяти основных логических элементов:

- И вентиль — выход равен 1, если ОБЕИХ входов 1

- вентиль ИЛИ — выход равен 1, если по крайней мере один вход равен 1

- вентиль XOR — выход равен 1, если ТОЛЬКО один вход равен 1

- вентиль И-НЕ — выход равен 1, если по крайней мере один вход 0

- вентиль ИЛИ-НЕ — выход равен 1, если ОБЕИХ входов 0

В цифровой логике есть шестой элемент, инвертор (иногда называемый вентилем НЕ).Инверторы на самом деле не ворота, поскольку они не принимают никаких решений. Выход инвертора равен 1, если вход равен 0, и наоборот.

Несколько замечаний по поводу изображения выше:

- Обычно название ворот — , а не ; Предполагается, что символа достаточно для идентификации.

- Обозначение клемм типа A-B-Q является стандартным, хотя в логических схемах они обычно не используются для сигналов, которые не являются входами или выходами для системы в целом.

- Стандартно два устройства ввода, но иногда можно встретить устройства с более чем двумя входами. Однако у них будет только один выход.

Цифровые логические схемы обычно представлены с использованием этих шести символов; входы слева, а выходы справа. Хотя входы могут быть соединены вместе, выходы никогда не должны быть связаны друг с другом, только с другими входами. Однако один выход может быть подключен к нескольким входам.

Таблицы истинности

Описания выше подходят для описания функциональности отдельных блоков, но есть более полезный инструмент: таблица истинности.Таблицы истинности — это простые графики, которые объясняют выход схемы с точки зрения возможных входов для этой схемы. Вот таблицы истинности, описывающие шесть основных элементов:

Таблицы истинности могут быть расширены до произвольного масштаба, с таким количеством входов и выходов, с которым вы можете справиться, прежде чем ваш мозг растает. Вот как выглядит схема с четырьмя входами и таблица истинности:

Записанная логическая логика

Конечно, полезно иметь возможность записать в простом математическом формате уравнение, представляющее логическую операцию.Для этого существуют математические символы для уникальных операций: AND, OR, XOR и NOT.

- A AND B следует записывать как AB (или иногда A • B)

- A OR B следует записать как A + B

- A XOR B следует записать как A ⊕ B

- НЕ А следует писать как А ‘или А

Вы заметите, что в этом списке отсутствуют два элемента: NAND и NOR. Обычно они просто дополняются соответствующим представлением:

- NAND B записывается как (AB) ‘, (A • B)’ или (AB)

- A NOR B записывается как (A + B) ‘или (A + B)

← Предыдущая страница

Введение

Логические ворота

- Изучив этот раздел, вы должны уметь:

- Опишите действие логических вентилей.

- • AND, OR, NAND, NOR, NOT, XOR и XNOR.

- • Использование логических выражений.

- • Использование таблиц истинности.

- Разберитесь в использовании универсальных ворот.

- • NAND.

- • НОР.

- Распознавать общие микросхемы серии 74, содержащие стандартные логические вентили.

Логические ворота

Семь базовых логических вентилей

Фиг.2.1.1 Символы ворот ANSI и IEC

Цифровая электроника полагается на действия всего семи типов логических вентилей, называемых И, ИЛИ, И-НЕ (Не И), ИЛИ (Не ИЛИ), XOR (Исключающее ИЛИ), XNOR (Исключающее ИЛИ) и НЕ.

Рис. 2.1.1 иллюстрирует выбор основных логических вентилей, которые доступны от ряда производителей в стандартных семействах интегральных схем. Каждое семейство логики спроектировано таким образом, чтобы вентили и другие логические ИС в этом семействе (и других связанных семействах) можно было легко комбинировать и встраивать в более крупные логические схемы для выполнения сложных функций с минимумом дополнительных компонентов.

В двоичной логике разрешены только два состояния: 1 и 0 или «включено и выключено». слово НЕ в мире двоичной логики означает «противоположность». Если что-то не 1, это должно быть 0, если оно не включено, оно должно быть выключено. Таким образом, NAND (не AND) просто означает, что вентиль NAND выполняет функцию, противоположную вентилю AND.

Логический вентиль — это небольшая транзисторная схема, в основном тип усилителя, который реализован в различных формах внутри интегральной схемы. Каждый тип ворот имеет один или несколько (чаще всего два) входа и один выход.

Принцип работы состоит в том, что схема работает только на двух уровнях напряжения, называемых логическим 0 и логическим 1. Эти значения представлены двумя разными уровнями напряжения. В 5-вольтовой логике 1 идеально представлена 5 В, а 0 — 0 В, а в 3,3 В логическая 1 идеально представлена 3,3 В, а логический 0 — 0 В. Когда любой из этих уровней напряжения подается на входы, выход затвора реагирует, принимая уровень 1 или 0, в зависимости от конкретной логики затвора. Логические правила для каждого типа ворот можно описать по-разному; письменным описанием действия, таблицей истинности или оператором булевой алгебры.

Логические выражения

Рис. 2.1.2 Логические символы для ворот

Действия любого из этих вентилей также можно описать с помощью логических операторов. В них используются буквы из начала алфавита, такие как A, B, C и т. Д., Для обозначения входов и буквы из второй половины алфавита, очень часто X или Y (а иногда Q или P) для обозначения выходных данных. Буквы сами по себе не имеют никакого значения, кроме обозначения различных точек в цепи. Затем буквы соединяются логическим символом, указывающим логическое действие ворот.

Символ • обозначает И, хотя во многих случаях символ • может быть опущен. (A • B может также записываться как AB или A.B)

+ обозначает ИЛИ

⊕ означает XOR (Исключающее ИЛИ)

Хотя символы • и + такие же, как и символы, используемые в нормальной алгебре для обозначения произведения (умножения) и суммы (сложения) соответственно, в двоичной логике символ + не совсем соответствует сумме. В цифровой логике 1 + (ИЛИ) 1 = 1, но двоичная сумма 1 + 1 = 10 2 , поэтому в цифровой логике + всегда следует рассматривать как ИЛИ.

Три дополнительных типа логических вентилей дают выходной сигнал, который является инвертированной версией трех основных функций вентилей, перечисленных выше, и они обозначены полосой, нарисованной над оператором, с использованием символов И, ИЛИ или ИСКЛЮЧАЮЩЕЕ ИЛИ для обозначения И-НЕ, ИЛИ ИЛИ и XNOR.

A • B означает A AND B, но A • B означает A NAND B

Таким образом, действие любого из вентилей может быть описано с помощью его булевого уравнения.

Например, вентиль И дает выход логической 1, когда вход A И вход B находятся на логической 1, но вентиль И-НЕ дает выход логического 0 для тех же условий входа.Также, если вентиль И дает логический ноль для конкретной входной комбинации, вентиль И-НЕ даст логическую 1. Таким образом, буква «N» в имени логического элемента или полоса над логическим выражением указывает на то, что выходная логика «инвертирована». . В цифровой логике NAND — это NOT AND или противоположность AND. Точно так же NOR — это «NOT» OR, а XNOR — это «NOT» XOR.

Описание действия логических вентилей

В качестве альтернативы действие любого из 7 типов логического элемента может быть описано с использованием письменного описания его логической функции.

- Выход логического элемента И находится на уровне логической 1, когда и только когда все его входы находятся на уровне логической 1, в противном случае выход находится на уровне логического 0.

- Выход логического элемента ИЛИ является логической 1, когда один или несколько его входов находятся на уровне логической 1. Если все его входы имеют логическую единицу, выход имеет логический 0.

- Выход логического элемента И-НЕ имеет логический 0 тогда и только тогда, когда все его входы имеют логическую 1. В противном случае выход находится в логическом 0.

- Выход логического элемента ИЛИ-НЕ имеет логический 0, когда один или несколько его входов имеют логическую 1.Если все его входы имеют логический 0, выход — логический 1.

- Выход логического элемента XOR имеет логическую 1, когда и только один из его входов имеет логическую 1. В противном случае выход имеет логический 0.

- Выход логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, когда один и только один из его входов находится в состоянии логической 1. В противном случае выход имеет логическую единицу (поэтому он аналогичен элементу ИСКЛЮЧАЮЩЕЕ ИЛИ, но его выход инвертирован).

- Выход логического элемента НЕ находится на уровне логического 0, когда его единственный вход находится на уровне логической 1, и на уровне логической 1, когда его единственный вход находится на уровне логического 0.По этой причине его часто называют ИНВЕРТОРОМ.

дел>

Рис. 2.1.3 Таблицы истинности

Таблицы истинности

Еще один полезный способ описать действие цифрового шлюза (или всего цифрового cicuit) — использовать таблицу истинности. Каждая таблица состоит из двух или более столбцов, по одному столбцу для каждого ввода или вывода; количества строк в столбце будет достаточно для записи всех возможных логических состояний для этого входа или выхода. На рис. 2.1.3 показаны две типичные таблицы истинности для схем разного уровня сложности.

Верхний стол для простого двух входов и ворот. У него есть два входа, обозначенные A и B, и один столбец (X) для вывода. Сравнивая таблицу истинности с письменным описанием в разделе «Описание действия логических вентилей» (выше), можно увидеть, что таблица истинности следует письменному описанию, показывая, что выход X находится на уровне 1, только когда входы A и B находятся на уровне логики. 1, в противном случае (где три верхние строки — 00, 01 и 10) на выходе будет логический 0.

Вторая таблица на рис.2.1.3 описывает более сложную схему (из пяти вентилей NAND, имитирующих вентиль XOR). Обратите внимание, что теперь таблица истинности расширена, чтобы проиллюстрировать логические уровни на четырех дополнительных входах или выходах в дополнение к входам A и B до того, как окончательный выход X будет проиллюстрирован в правом столбце. Такие сложные таблицы могут иметь большое значение как при проектировании цифровых схем, так и при поиске неисправностей.

И Выход

NAND Gate

OR Выход

NOR Gate

Шлюз XOR

Выход XNOR

НЕ Выходной

Фиг.2.1.4 Анимация логических ворот (щелкните любой вентиль)

Анимация логических ворот

На рис. 2.1.4 вы можете проверить работу основных логических вентилей. Анимация ворот позволяет вам выбрать любой из 7 основных ворот и увидеть новую страницу с анимированным изображением действующих ворот. Используйте анимацию, чтобы познакомиться с работой каждого из ворот. Чтобы вернуться на эту страницу, просто закройте страницу с анимацией.

Чтобы легко понять более сложные цифровые схемы, важно создать хорошее мысленное представление об ожидаемом выходе каждого логического элемента для любого возможного входа.