Как собрать схему для ПЛИС Altera и загрузить в нее конфигурацию. Какие этапы включает процесс создания конфигурации ПЛИС. Как настроить Quartus Programmer для работы с USB Blaster. Как выполнить компиляцию проекта и загрузить его в микросхему.

Этапы создания конфигурации ПЛИС Altera

Процесс создания конфигурации для программируемой логической интегральной схемы (ПЛИС) Altera включает следующие основные этапы:

- Проектирование цифровой схемы

- Анализ созданной схемы на наличие ошибок

- Привязка входов и выходов схемы к конкретным выводам ПЛИС

- Компиляция проекта и создание двоичных файлов для конфигурирования ПЛИС

- Конфигурирование ПЛИС посредством программатора USB Blaster

В данной статье мы подробно рассмотрим последние два этапа этого процесса — компиляцию проекта и загрузку готовой конфигурации в микросхему ПЛИС.

Компиляция проекта в Quartus

Компиляция проекта в среде разработки Quartus выполняется в несколько этапов:

- Анализ и синтез (Analysis & Synthesis)

- Размещение и трассировка (Fitter)

- Сборка (Assembler)

- Временной анализ (TimeQuest Timing Analyzer)

Для запуска полной компиляции проекта необходимо нажать кнопку «Start Compilation» на панели инструментов Quartus или выбрать пункт меню Processing → Start Compilation.

Анализ и синтез

На этапе анализа и синтеза выполняется проверка корректности проекта и создается предварительная схема коммутации блоков ПЛИС. По завершении этого этапа формируется отчет с информацией об использованных ресурсах микросхемы.

Размещение и трассировка

Fitter выполняет размещение синтезированных блоков на кристалле ПЛИС с учетом заданных ограничений по температуре, энергопотреблению, временным задержкам и другим параметрам. Результаты работы Fitter также отображаются в отчете о компиляции.

Сборка

Assembler генерирует файлы для загрузки конфигурации в ПЛИС. Основным результатом его работы является файл с расширением .pof, содержащий конфигурацию для программирования микросхемы.

Временной анализ

TimeQuest Timing Analyzer проверяет соответствие синтезированной схемы заданным временным ограничениям, например, возможность работы на определенной частоте. В простых проектах этот этап можно пропустить.

Настройка Quartus Programmer

Для загрузки скомпилированной конфигурации в ПЛИС используется инструмент Quartus Programmer. Рассмотрим основные шаги по его настройке:

- Запустите Programmer через меню Tools → Programmer или соответствующую кнопку на панели инструментов

- В открывшемся окне нажмите кнопку «Hardware Setup» для выбора программатора

- На вкладке «Hardware Settings» выберите USB-Blaster из списка доступных устройств

- Закройте окно настройки. В основном окне Programmer должно отобразиться название выбранного программатора

Если USB-Blaster не отображается в списке, проверьте его подключение и при необходимости установите драйвер из папки с Quartus.

Загрузка конфигурации в ПЛИС

После настройки программатора можно приступать к загрузке конфигурации в микросхему ПЛИС. Для этого выполните следующие действия:

- В окне Programmer на панели «Device Chain» должна отображаться используемая модель ПЛИС

- На панели «Device Tree» в колонке «File» укажите путь к сгенерированному .pof файлу

- Установите флажок «Program/Configure» для CFM (Configuration Flash Memory)

- Нажмите кнопку «Start» для начала процесса программирования

Процесс загрузки конфигурации включает стирание предыдущей прошивки, проверку на пустоту, запись новой конфигурации и ее верификацию. Прогресс и результат отображаются в строке состояния Programmer.

Проверка работоспособности схемы

После успешной загрузки конфигурации в ПЛИС можно приступать к проверке работоспособности реализованной схемы. Подайте необходимые входные сигналы и убедитесь, что выходные сигналы соответствуют ожидаемым.

При необходимости внесения изменений в проект повторите процесс компиляции и загрузки новой конфигурации в микросхему.

Часто задаваемые вопросы

Что делать, если Quartus Programmer не видит USB-Blaster?

Если USB-Blaster не отображается в списке доступных программаторов, попробуйте следующее:

- Проверьте физическое подключение USB-Blaster к компьютеру

- Переустановите драйвер USB-Blaster из папки с Quartus

- Попробуйте использовать другой USB-порт

- Перезапустите Quartus и компьютер

Как исправить ошибку «No Hardware» в Quartus Programmer?

Ошибка «No Hardware» обычно означает, что программатор не настроен. Для исправления:

- Нажмите кнопку «Hardware Setup» в окне Programmer

- Выберите USB-Blaster на вкладке «Hardware Settings»

- Закройте окно настройки

Если USB-Blaster отсутствует в списке, см. предыдущий вопрос.

Что означают предупреждения о временном анализе при компиляции?

Предупреждения вроде «No clocks defined in design» при временном анализе обычно не критичны для простых проектов без тактового сигнала. Их можно игнорировать, если схема не предполагает работу на высоких частотах.

Заключение

Освоение процесса компиляции проекта и загрузки конфигурации в ПЛИС является важным этапом в изучении технологии программируемой логики. Понимание этих процессов позволяет эффективно разрабатывать и отлаживать цифровые схемы на базе ПЛИС Altera.

В данной статье мы рассмотрели основные этапы создания конфигурации ПЛИС, настройку Quartus Programmer для работы с USB-Blaster, а также процесс загрузки готовой конфигурации в микросхему. Эти знания послужат хорошей основой для дальнейшего изучения более сложных аспектов проектирования цифровых устройств на базе ПЛИС.

ПЛИС Altera. Часть 6: сборка схемы и загрузка конфигурации

Это заключительная часть цикла посвященная программируемой логике и среде разработки Quartus компании Altera (Intel).

Ссылки на предыдущие части:

ПЛИС Altera. Часть 1: установка и настройка среды разработки

ПЛИС Altera. Часть 2: проектирование цифровой схемы

ПЛИС Altera. Часть 3: первая компиляция проекта

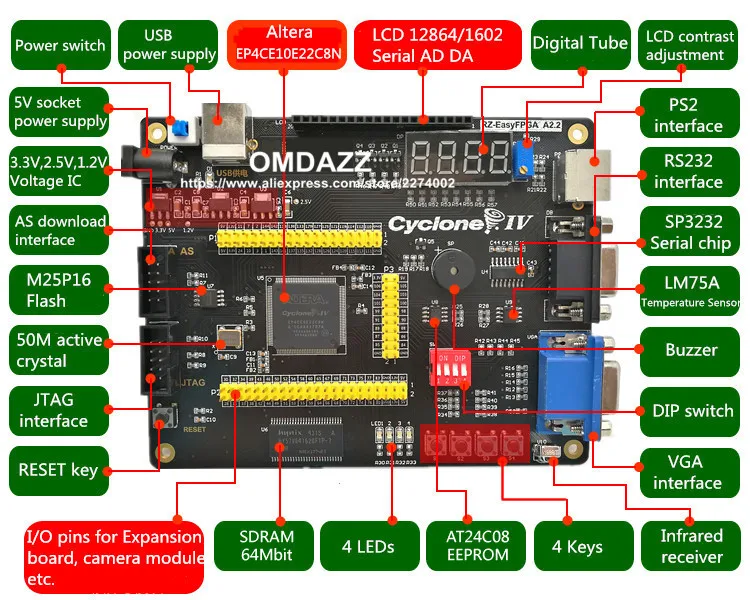

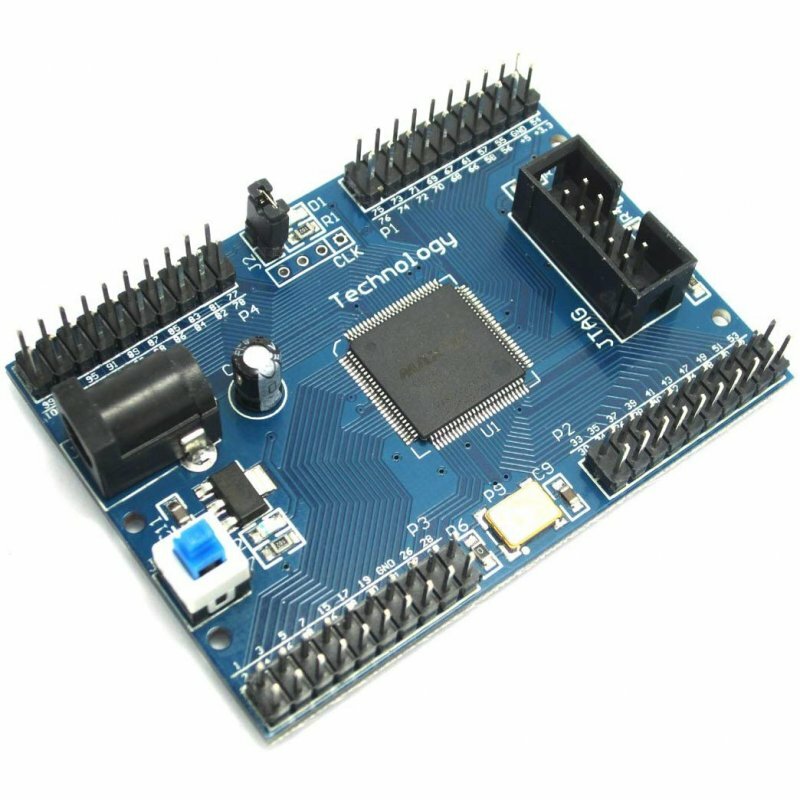

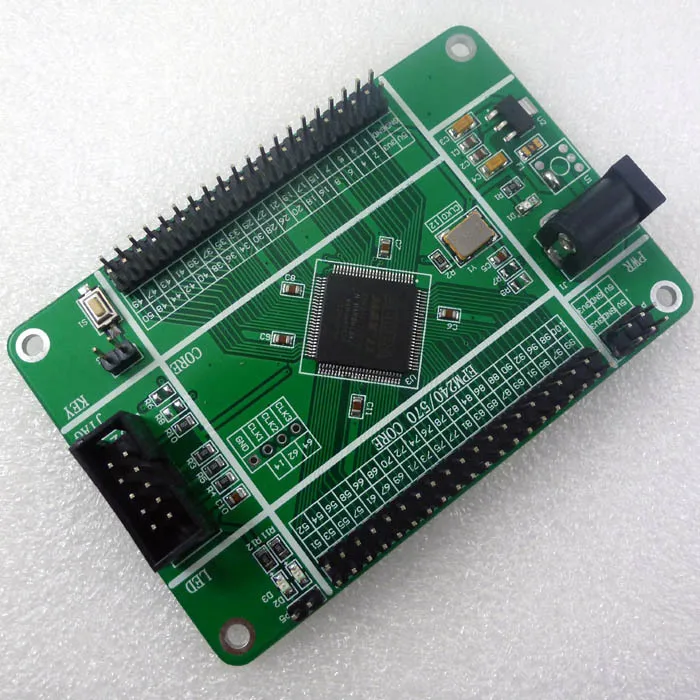

ПЛИС Altera. Часть 4: доработка схемы и плата CTRL-CPLD-EPM570

ПЛИС Altera. Часть 5: Quartus Pin Planner

В первой части рассказывалось о загрузке и установке Quartus. О создании пустого проекта с помощью мастера.

Во второй части рассматривалось проектирование цифровой схемы, определялась последовательность шагов для создания конфигурации ПЛИС.

В третьей части выполнялась настройка главного модуля проекта, был выполнен анализ и синтез схемы. Разбирались наиболее вероятные ошибки, которые могут быть выявлены при анализе и синтезе.

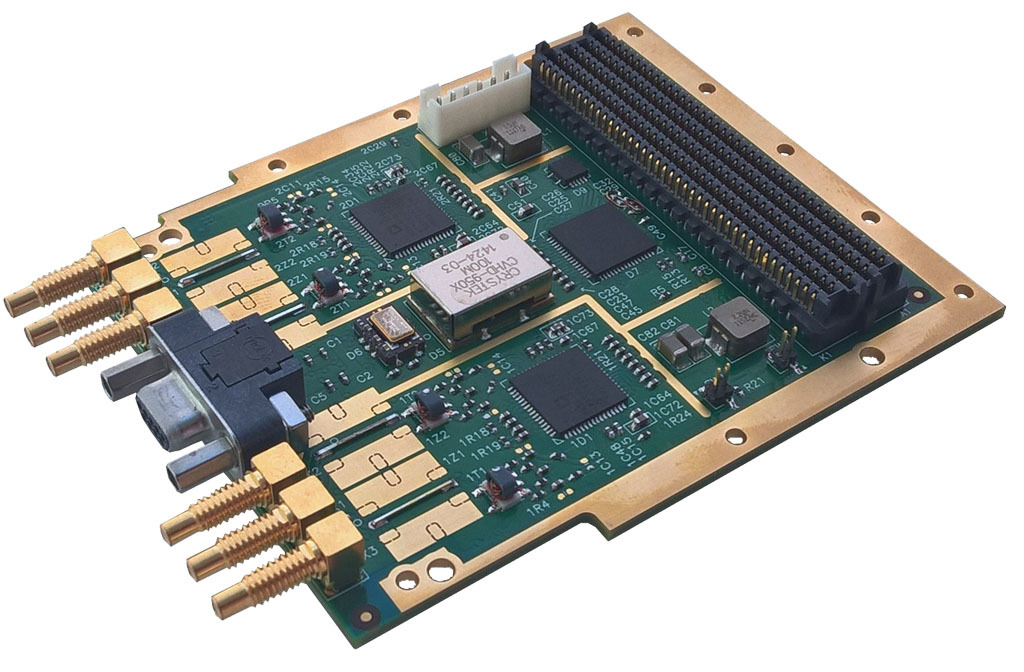

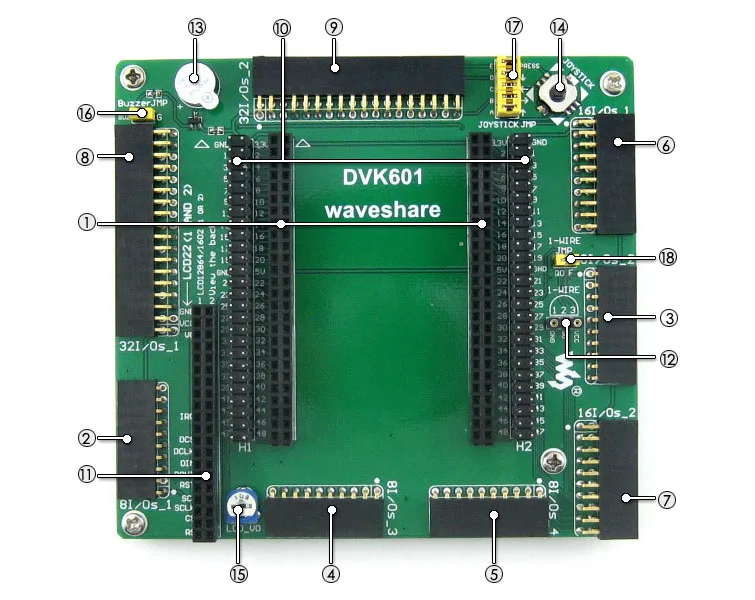

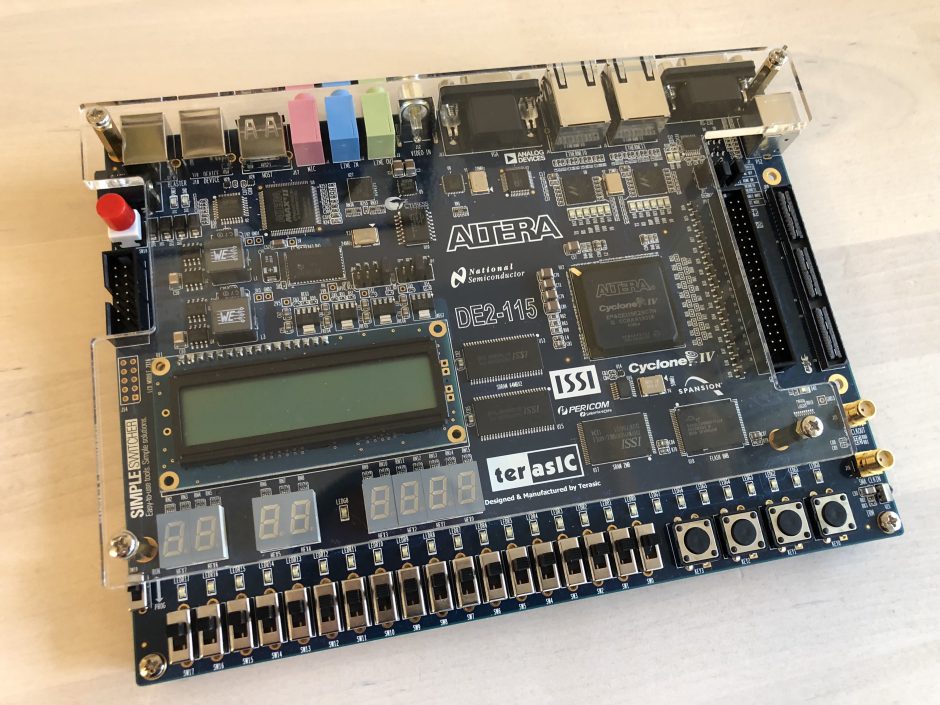

Четвертая часть была полностью посвящена электрической части проекта: доработка схемы проекта и знакомство с платой CTRL-CPLD-EPM570.

В пятой части рассказывается как связать цифровую схему проекта с физическими выводами микросхемы ПЛИС. Это третий этап создания конфигурации.

Напоминаю, что процесс создания конфигурации предусматривает следующие этапы:

- проектирование цифровой схемы;

- анализ созданной схемы на наличие ошибок;

- привязка входов и выходов схемы к конкретным выводам ПЛИС;

- компиляция проекта и создание двоичных файлов для конфигурирования ПЛИС;

- конфигурирование ПЛИС посредством USB Blaster.

Шестая часть описывает последние два этапа процесса: компиляцию проекта и загрузку конфигурации в микросхему. Большая часть этой статьи посвящена настройке Quartus «Programmer».

Заключительная компиляция

Выполнение полной компиляции запускается с помощью кнопки «Start Compilation» на стандартной панели инструментов Quartus. Данная кнопка идет одиннадцатой справа, она выделена на следующем рисунке.

Также можно использовать меню Processing → Start Compilation.

Выполнение полной компиляции начинается с процесса анализа проекта и синтеза предварительной схемы коммутации блоков ПЛИС – «Analysis & Synthesis». Затем следует «Fitter», который выполняет размещение блоков синтезированной схемы на кристалле ПЛИС с учетом заданных: диапазона рабочих температур, энергопотребления схемы связанного с используемым стандартом ввода‑вывода, диапазона допустимых временных задержек указанных в проекте и многих других параметров. Для простых проектов подходят значения перечисленных параметров по умолчанию.

Обобщенный отчет о результатах работы «Fitter» (Fitter → Summary) выводится по окончании всего процесса компиляции.

В основном, данный отчет не отличается от аналогичного отчета выводимого по завершении «Analysis & Synthesis». Добавляются лишь соотношения использованных и доступных ресурсов выбранной микросхемы ПЛИС: логических элементов и выводов. Эта информация выделена на рисунке выше.

После «Fitter»

свою работу выполняет «Assembler»,

который осуществляет генерацию файлов

для загрузки в ПЛИС.

Заключительный этап компиляции – это «TimeQuest Timing Analyzer». Данный инструмент осуществляет проверку синтезированного дизайна на соответствие заданным в проекте временным ограничениям. Например, проверка возможности работы схемы на определенной частоте. В Вашем проекте нет таких ограничений, так как схема управляется человеком непосредственно и не предполагает работы на запредельных частотах. Тем не менее, отсутствие данных ограничений Quartus считает серьезным недостатком, о чем он и сообщает пользователю сразу двумя критическими предупреждениями: «Critical Warning: Synopsys Design Constraints File file not found: ‘firstproject.sdc’. A Synopsys Design Constraints File is required by the TimeQuest Timing Analyzer to get proper timing constraints.

Помимо критических предупреждений Вам будет выдано и несколько (около трех) обычных предупреждений такого содержания: «Warning: No clocks defined in design.». Они также связаны с «TimeQuest Timing Analyzer». В проекте не определены параметры тактового сигнала схемы, так как схема не предполагает работу с таким сигналом. Следовательно, Вы можете смело игнорировать эти предупреждения, как и предыдущие два.

Кроме перечисленных, также будут выведены несколько уже знакомых коммерческих предупреждений.

При наличии других критических предупреждений, или даже ошибок, необходимо внимательно изучить содержание окна «Messages» и отчет о компиляции. Разделы отчета содержащие информацию об ошибках будут выделены красным шрифтом. Так же, можно повторно выполнить соответствующий этап компиляции с помощью меню Processing → Start, для того чтобы сократить число сообщений в окне «Messages» или для проверки сделанных исправлений.

Окно сообщений успешно откомпилированного проекта с некритичным числом предупреждений приводится на следующем рисунке.

После успешно выполненной компиляции проекта можно переходить к заключительному этапу: сборке схемы и загрузке синтезированной конфигурации в ПЛИС.

Сборка схемы и подключение программатора

Прежде чем подать питание на ПЛИС и загрузить в нее проект необходимо собрать спроектированную схему. Подключать что‑либо к ПЛИС «на горячую» нельзя!

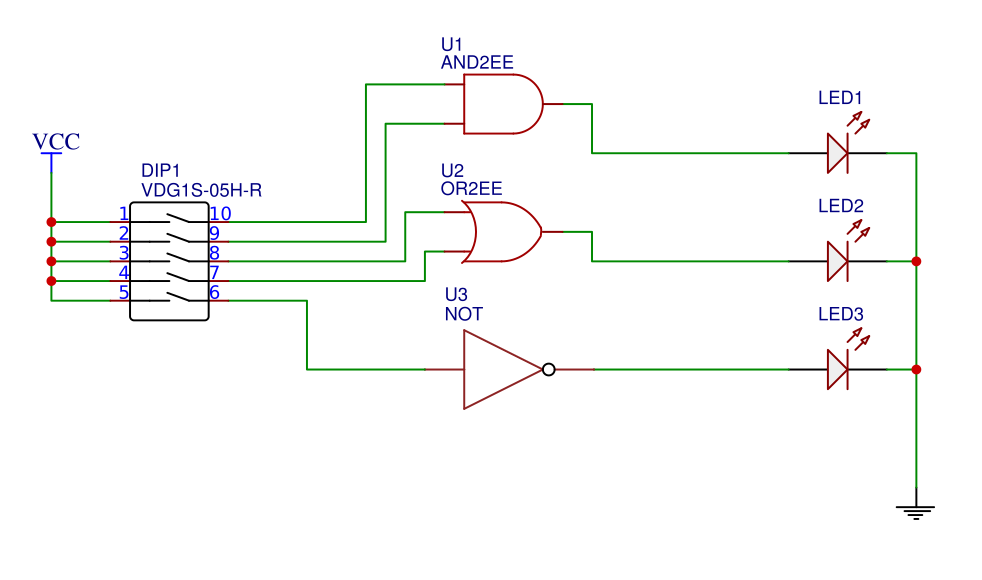

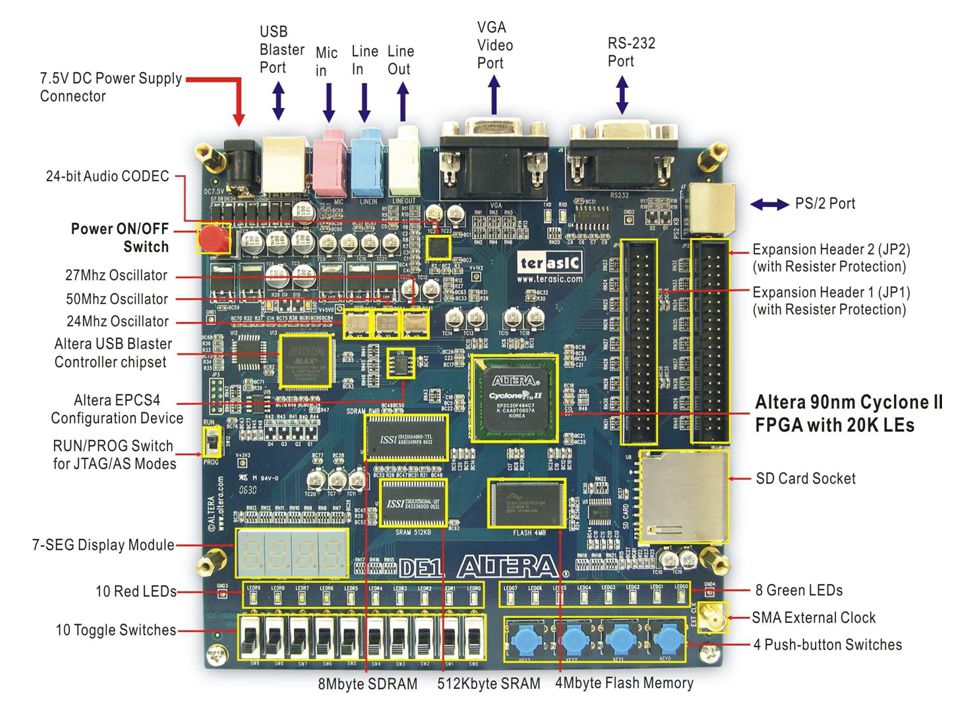

Проектирование схемы было завершено в четвертой части серии статей. Для удобства эта схема приводится повторно.

Номера выводов ПЛИС указаны согласно настройкам в «Pin Planner» сделанным в пятой части серии.

После завершения сборки можно подключать программатор Altera USB Blaster. Altera/Intel рекомендует подключать программатор соблюдая следующую последовательность действий:

- отключить питание от платы «CTRL‑CPLD‑EPM570»;

- подключить программатор к USB порту включенного компьютера;

- соединить включенный программатор с гнездом «JTAG» платы с ПЛИС;

- включить питание платы с ПЛИС.

После выполнения этих действий можно загружать конфигурацию в ПЛИС.

Внимание! И при подключении программатора к плате с ПЛИС и при его отключении необходимо предварительно выключать питание платы!

При первом подключении к компьютеру программатора USB Blaster необходимо будет установить соответствующий драйвер. Все необходимые драйвера имеются в дистрибутиве Quartus. При установке Quartus они копируются в следующую директорию: «altera\13.1\quartus\drivers\usb-blaster». Имеются драйвера как для 32‑х так и для 64‑разрядных ОС Windows. Установка драйвера выполняется вручную, путем выбора директории с драйвером для автоматического поиска и установки необходимых файлов. Либо прямым указанием файла «usbblstr.inf».

Отсоединять программатор необходимо в обратной последовательности:

- отключить питание платы с ПЛИС;

- отсоединить программатор от гнезда «JTAG» платы;

- отключить программатор от USB порта компьютера.

Сам программатор должен быть включен при любых манипуляциях с разъемом JTAG. Такая последовательность действий обусловлена тем, что у оригинального программатора Altera USB Blaster есть проблема с питанием выходного буфера, из‑за которой он может быть выведен из строя при включении/отключении питания программатора соединенного с платой ПЛИС.

На этом работа с электрической часть проекта завершена. Можно переходить к загрузке конфигурации.

Quartus Programmer: настройка программатора

Для загрузки конфигурации используется инструмент «Programmer» среды Quartus. Этот инструмент можно вызвать с помощью меню Tools → Programmer. Либо посредством соответствующей кнопки на стандартной панели инструментов. Кнопка идет четвертой справа на панели. Она выделена на рисунке ниже.

При запуске «Programmer» откроется новое окно, вид которого приводится на следующем рисунке.

Первое, на что необходимо обратить внимание — это кнопка «Hardware Setup…» в верхнем левом углу окна «Programmer». На рисунке она обозначена цифрой 1. С ее помощью выполняется выбор программатора. Модель используемого программатора выводится в текстовом поле справа от кнопки (цифра 2 на рисунке). Сейчас там присутствует надпись «No Hardware», это означает что программатор требует настройки.

На рисунке она обозначена цифрой 1. С ее помощью выполняется выбор программатора. Модель используемого программатора выводится в текстовом поле справа от кнопки (цифра 2 на рисунке). Сейчас там присутствует надпись «No Hardware», это означает что программатор требует настройки.

Нажмите кнопку «Hardware Setup…» чтобы открыть одноименное окно. Изображение окна приводится ниже.

Данное окно содержит две вкладки: «Hardware Settings» и «JTAG Settings».

«JTAG Settings» используется для настройки доступа к серверам JTAG. Можно как добавлять удаленные сервера, к которым присоединяются конфигурируемые ПЛИС, так и настраивать доступ к серверу JTAG запущенному на Вашем компьютере.

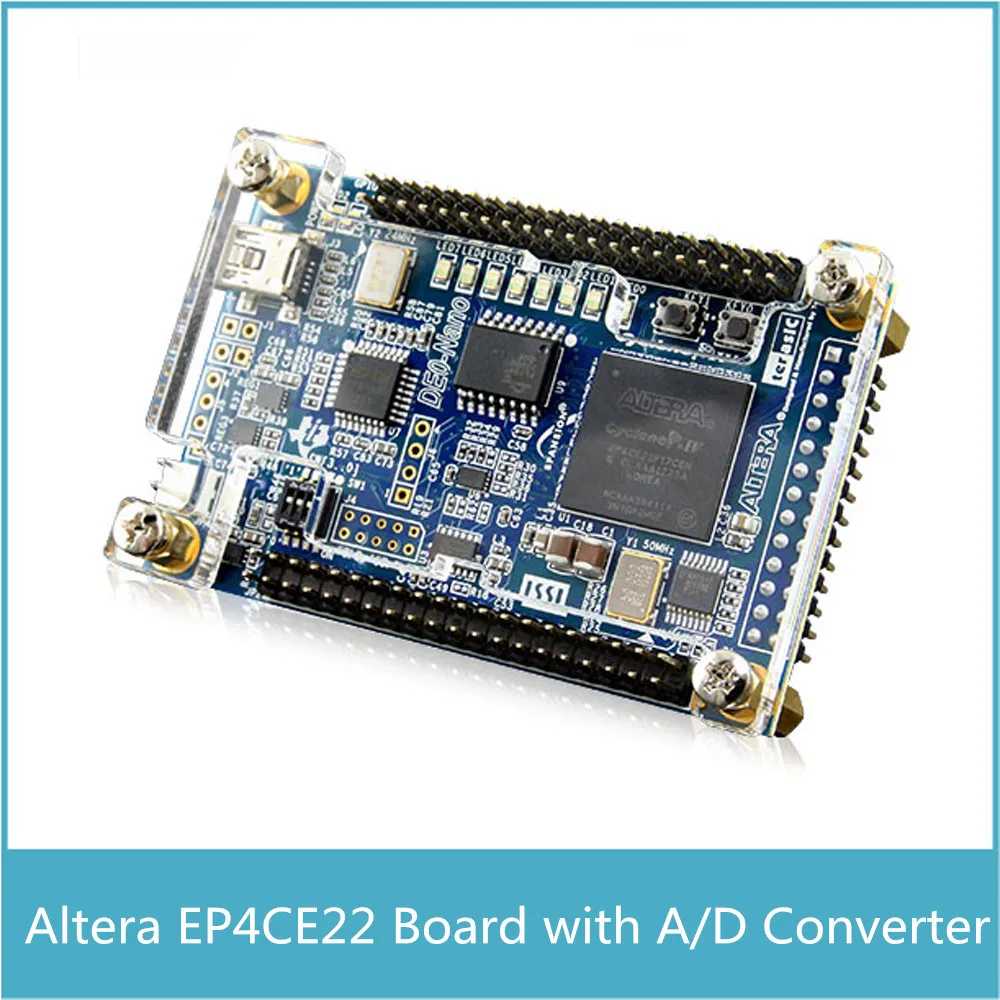

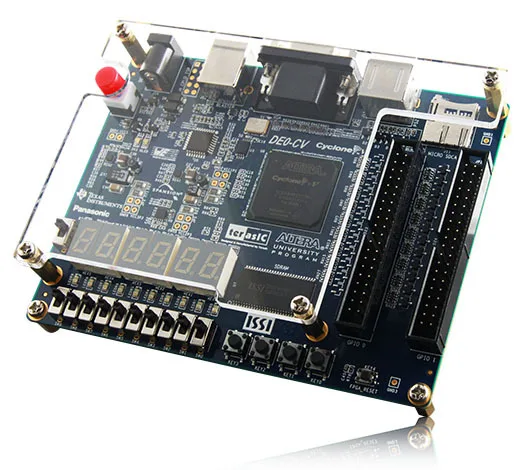

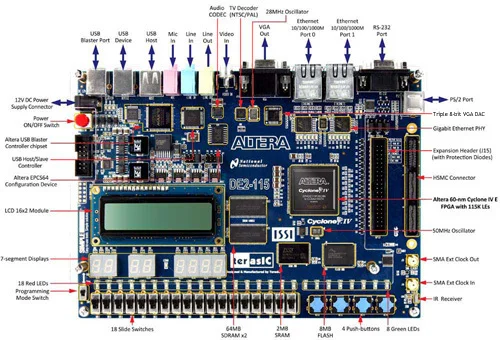

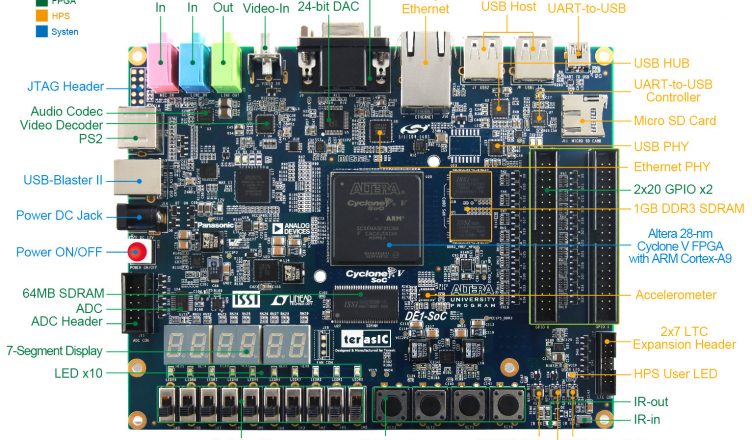

Quartus «Programmer» работает по клиент‑серверной модели. В ней есть сервер — это специальная служба «jtagserver», которая запускается вместе с «Programmer» и непосредственно работает с программатором. И есть клиент — «Programmer», который обеспечивает пользовательский интерфейс для выбора и загрузки конфигурации ПЛИС. Клиент и сервер могут располагаться на разных компьютерах, которые могут находиться на разных концах света. Таким образом, можно организовать удаленную работу со схемой в лаборатории собранной на базе дорогой платы разработчика (например, платы на базе Stratix III в среднем стоят более 4 000 долларов).

Клиент и сервер могут располагаться на разных компьютерах, которые могут находиться на разных концах света. Таким образом, можно организовать удаленную работу со схемой в лаборатории собранной на базе дорогой платы разработчика (например, платы на базе Stratix III в среднем стоят более 4 000 долларов).

При локальной работе достаточно проверить статус сервера на вкладке «JTAG Settings». В списке «JTAG Servers» должен быть как минимум один сервер «Local» и «Connection Status», состояние подключения до него, «OK».

Если список серверов пуст, то скорее всего, возникла проблема с самим программатором: он перестал отвечать на запросы службы «jtagserver». В таком случае необходимо:

- закрыть окно «Hardware Setup»;

- подключить/переподключить программатор;

- открыть окно «Hardware Setup» и проверить наличие сервера «Local», состояние подключения к серверу (смотрите рисунок ниже).

Вторая вкладка — «Hardware Settings», она открывается по умолчанию. Эта вкладка используется для выбора конкретного программатора из множества доступных. Содержимое вкладки представлено на рисунке ниже.

Содержимое вкладки представлено на рисунке ниже.

Доступные программаторы перечисляются в блоке «Available hardware items». Устройства в этот список добавляются пользователем вручную или самой средой автоматически. Автоматическое обнаружение доступно не для всех моделей программаторов. Вручную требуется добавлять либо устаревшие модели устройств, соединяющиеся с компьютером через LPT‑порт (это ByteBlaster II и ByteBlasterMV), либо «EthernetBlaster», который работает с компьютером как удаленный JTAG сервер. USB Blaster добавляется автоматически, поэтому пользователю достаточно проверить наличие USB программатора в списке.

Выбор программатора для прошивки ПЛИС осуществляется с помощью выпадающего списка, справа от надписи «Currently selected hardware». Программатор можно выбрать из списка непосредственно, либо выполнив двойной клик левой кнопкой мыши на соответствующем элементе столбца «Hardware» в «Available hardware items». В обоих случаях значение «No Hardware» заменится названием выбранного программатора. Вид вкладки после выполнения настройки приведен на рисунке выше.

Вид вкладки после выполнения настройки приведен на рисунке выше.

Теперь можно закрыть окно «Hardware Setup». В результате, в окне «Programmer» надпись «No Hardware», рядом с кнопкой «Hardware Setup», сменится названием выбранного программатора.

Quartus Programmer: Device Chain

Все остальные настройки производятся в основном окне «Programmer». В верхней части окна, помимо «Hardware Setup» для настройки доступны еще два параметра: «Mode» и «Enable real-time ISP to allow background programming (for MAX II and MAX V) devices».

Параметр «Mode» определяет режим загрузки конфигурации в ПЛИС. По умолчанию установлен режим JTAG, его и необходимо использовать. Так как «Passive Serial Programming» и «Active Serial Programming» не совместимы с MAX II, а «In-Socket Programming» не поддерживается USB Blaster’ом.

Второй параметр — «Enable real-time ISP to allow background programming (for MAX II and MAX V) devices» активирует загрузку новой конфигурации на лету, без отключения ПЛИС от схемы на время прошивки. Новая конфигурация, в таком случае, будет применена только после перезагрузки ПЛИС по питанию. Эта возможность сокращает время простоя устройств на базе ПЛИС серии MAX, но действительно полезна только в промышленном применении. Поэтому данный параметр можно оставить в состоянии по умолчанию — отключенным.

Новая конфигурация, в таком случае, будет применена только после перезагрузки ПЛИС по питанию. Эта возможность сокращает время простоя устройств на базе ПЛИС серии MAX, но действительно полезна только в промышленном применении. Поэтому данный параметр можно оставить в состоянии по умолчанию — отключенным.

Большую часть окна занимают две панели: «Device Tree» и «Device Chain». На рисунке выше они обозначены окружностями с цифрами 1 и 2 соответственно. Их отображение можно включить (выключить) с помощью меню View → Show Device Tree и View → Show Device Chain.

Часть настроек панелей установлены Quartus автоматически. В «Device Tree», в колонку «File» подставляется имя файла конфигурации, созданного во время последней компиляции. А в «Device Chain» из этого же файла подставляется модель используемой микросхемы.

Панель «Device Chain» (цифра 2) используется для наглядного представления упрощенной схемы соединения ПЛИС и программатора. На ней отображаются только линии приема и передачи данных. Эта информация может оказаться полезной в случае конфигурирования сложных схем на базе нескольких ПЛИС. Дело в том, что JTAG‑интерфейс позволяет строить цепочки из последовательно соединенных (линиями TDI — TDO) устройств. Такое подключение позволяет использовать один программатор для конфигурирования всех устройств цепочки. «Device Chain» позволяет сориентироваться в порядке соединения этих устройств.

Эта информация может оказаться полезной в случае конфигурирования сложных схем на базе нескольких ПЛИС. Дело в том, что JTAG‑интерфейс позволяет строить цепочки из последовательно соединенных (линиями TDI — TDO) устройств. Такое подключение позволяет использовать один программатор для конфигурирования всех устройств цепочки. «Device Chain» позволяет сориентироваться в порядке соединения этих устройств.

Плата «CTRL‑CPLD‑EPM570» несет на своем борту только одну микросхему, поэтому схема «Device Chain» предельно проста и, обычно, не требует вмешательства пользователя. Если же в «Device Chain» нет ни одного устройства, то можно попробовать добавить его с помощью автоматического поиска устройств на JTAG‑интерфейсе. Автоматический поиск запускается с помощью кнопки «Auto Detect» (третья сверху), расположенной в столбце кнопок у левого края окна. Данная кнопка активна только в том случае, когда в «Hardware Setup» настроен программатор.

При выполнении автоматического поиска заодно будет проверена работа JTAG‑интерфейса в целом. Если устройства не будут обнаружены, то «Programmer» предложит запустить отладку JTAG подключения, которая позволяет пользователю вручную выполнять команды на интерфейсе. При возникновении такой проблемы необходимо проверить соединение программатора с платой «CTRL‑CPLD‑EPM570» и наличие питания на микросхеме ПЛИС (включена ли плата). После устранения проблем необходимо повторно запустить поиск устройств.

Если устройства не будут обнаружены, то «Programmer» предложит запустить отладку JTAG подключения, которая позволяет пользователю вручную выполнять команды на интерфейсе. При возникновении такой проблемы необходимо проверить соединение программатора с платой «CTRL‑CPLD‑EPM570» и наличие питания на микросхеме ПЛИС (включена ли плата). После устранения проблем необходимо повторно запустить поиск устройств.

Обнаруженные устройства добавляются и на схему «Device Chain», и в список «Device Tree».

Quartus Programmer: Device Tree

В «Device Tree» настраивается сам процесс конфигурирования/программирования устройств. Эта панель оформлена в виде таблицы из двенадцати колонок: «File», «Device», «Checksum», «Usercode», «Program/Configure», «Verify», «Blank-Check», «Examine», «Security Bit», «Erase», «ISP CLAMP», «ISP File». Автоматически заполняются первые четыре колонки.

Первое на что необходимо обратить внимание в этой таблице — это колонка «File». В ней обязательно должен быть указан файл конфигурации, синтезированной при компиляции проекта. Колонка может быть пустой в случае, если в «Device Chain» а, соответственно, и в «Device Tree» нет ни одного устройства. Тогда, необходимо добавить устройство с помощью автоматического обнаружения.

Колонка может быть пустой в случае, если в «Device Chain» а, соответственно, и в «Device Tree» нет ни одного устройства. Тогда, необходимо добавить устройство с помощью автоматического обнаружения.

«File» будет содержать значение , если устройство было добавлено пользователем с помощью автоматического поиска или вручную. В этом случае файл необходимо добавить вручную с помощью кнопки «Change File…», которая располагается через две кнопки ниже кнопки «Auto Detect». Тоже действие можно выполнить и с помощью меню Edit → Change File…

Кнопка «Change File…» становится доступна только при выборе микросхемы ПЛИС в «Device Chain» или «Device Tree». Таким образом, для добавления файла потребуется сначала выбрать микросхему в «Device Chain», а за тем нажать на кнопку «Change File…». Порядок действий и сама кнопка обозначены на следующем рисунке.

Для добавления файла используется стандартное диалоговое окно Windows. Необходимо найти и выбрать с его помощью файл «firstproject.pof».

По умолчанию, файлы конфигурации сохраняются в папке «output_files» в основной директории проекта. Если требуемого файла там нет, то необходимо свериться с отчетом о полной компиляции проекта. Для этого потребуется закрыть окно «Programmer» и открыть раздел «Assembler» → «Generated Files» отчета компиляции в основном окне Quartus. Сам отчет о компиляции можно открыть с помощью меню Processing → Compilation Report. Если раздел «Assembler» отсутствует в отчете, то это означает что данный этап не был выполнен. Запустите полную компиляцию и добавьте полученный файл конфигурации в «Device Tree».

После добавления файла «firstproject.pof» панель «Device Tree» обретет вид аналогичный рисунку, который приведен в начале раздела. Из файла были автоматически подставлены значения в колонки «File», «Device», «Checksum» и «Usercode». А именно:

- в File» были добавлены две новые строки: CFM и UFM;

- наименование модели микросхемы ПЛИС в «Device» уточнено;

- в «Checksum» было добавлено значение контрольной суммы хранящейся в файле конфигурации;

- в «Usercode» подставлен JTAG код устройства.

CFM (Configuration Flash Memory) и UFM (User Flash Memory) это две части внутренней Flash‑памяти MAX II. CFM используется исключительно для хранения конфигурации, откуда она автоматически вычитывается при каждом включении микросхемы. UFM может быть использована для хранения пользовательских данных. Объем UFM составляет 8 Кбит.

Значение «Checksum» рассчитывается только для конфигурационных данных в pof‑файле (для всего файла вычисляется CRC). Эта информация используется для сравнения конфигурации в pof‑файле с конфигурацией загруженной в ПЛИС.

«Usercode» — JTAG‑код автоматически сгенерированный Quartus или указанный пользователем вручную в настройках проекта. Автоматически генерируемый код меняется при компиляции, после каждого редактирования цифровой схемы. Таким образом, автоматический JTAG‑код позволяет различать разные версии одной конфигурации.

Остальные столбцы определяют режимы и параметры процесса работы с конфигурацией, которые настраиваются пользователем. Большинство параметров может быть применено отдельно к CFM или UFM.

Большинство параметров может быть применено отдельно к CFM или UFM.

Назначение каждого параметра рассматривается ниже.

«Program/Configure» — загрузка конфигурации из pof‑файла или буфера «Programmer» в ПЛИС. Можно прошить каждый из блоков CFM и UFM внутренней памяти по отдельности или оба разом.

«Verify» — вычитывание конфигурации ПЛИС и ее сравнение (по Checksum) с конфигурацией в pof‑файле. Если обнаружены различия, то проверка завершается с ошибкой.

«Blank-Check» — проверить, записана ли в памяти ПЛИС какая‑либо конфигурация. Если в устройство загружена конфигурация, то проверка завершается с ошибкой.

«Examine» — считать конфигурацию из ПЛИС в буфер «Programmer». После, загруженную конфигурацию можно сохранить в новый pof‑файл.

«Security Bit» — защищает ПЛИС от чтения конфигурации. При попытке чтения возвращаются некорректные значения, обычно — 0xFF. По этой причине функция «Verify» также перестает работать. Сбросить защиту можно только загрузив в ПЛИС конфигурацию без использования «Security Bit» или выполнив «Erase».

«Erase» — удаление данных конфигурации с ПЛИС.

«ISP CLAMP» — фиксация состояния каждого вывода ПЛИС на высоком, низком логическом уровне или в высокоимпендансном состоянии во время ее конфигурирования. Состояние выводов можно настраивать независимо друг от друга. С помощью данного режима можно выставить на выводах ПЛИС комбинацию сигналов сигнализирующих о том что микросхема находится в состоянии перепрошивки. Полезно для устройств на базе нескольких ПЛИС.

«IPS File» (I/O Pin State файл) — это файл описывающий состояние каждого вывода ПЛИС для режима ISP CLAMP. Без его наличия использование режима ISP CLAMP невозможно.

Загрузка и сохранение конфигурации

Для выполнения каких‑либо действий с конфигурацией ПЛИС необходимо выбрать это действие в списке «Device Tree», а именно — проставить галочку в соответствующем столбце. После, в ряду кнопок у левого края окна станет доступна кнопка «Start» (первая сверху). Нажатием на данную кнопку запускается выполнение выбранного действия. Прогресс выполнения и итоговый статус можно отследить по строке прогресса в верхнем правом углу окна «Programmer» (справа от надписи «Progress:»). Сообщения, выводимые в процессе работы «Programmer», можно увидеть в основном окне Quartus на панели «Messages», вкладка «System».

Прогресс выполнения и итоговый статус можно отследить по строке прогресса в верхнем правом углу окна «Programmer» (справа от надписи «Progress:»). Сообщения, выводимые в процессе работы «Programmer», можно увидеть в основном окне Quartus на панели «Messages», вкладка «System».

Таким образом, для сохранения загруженной в ПЛИС конфигурации достаточно выбрать действие «Examine» в «Device Tree» и нажать кнопку «Start». Значение в поле «File» скрывается при выборе «Examine».

После нажатия на «Start» в строке прогресса будет выводится как, собственно, прогресс чтения конфигурации, так и его результат. При достижении 100% (Successful) в поле «File» будет подставлено имя временного файла «untitled1.pof». Для сохранения «untitled1.pof» необходимо выбрать его в списке и нажать кнопку «Save File» у левого края окна (четвертая снизу). Будет открыт стандартный диалог открытия/сохранения файла.

Вид окна «Programmer» и описанная последовательность действий обозначены на рисунке выше.

Загрузка конфигурации производится аналогично:

- выбрать действие — «Program/Configure»;

- нажать кнопку «Start»;

- дождаться 100% (Successful) в строке прогресса.

Не забудьте в поле «File» указать верный файл конфигурации перед прошивкой. Заменить файл на необходимый можно с помощью кнопки «Change File…».

На рисунке выше видно, что в столбце «Program/Configure» поставлена только одна галочка — в строке CFM. Так как проект не содержит информации для UFM, то выбирать для прошивки эту часть памяти не обязательно.

Сам процесс прошивки в «Programmer» состоит из следующей последовательности действий: Erase, Blank-Check (если выбрано), Program/Configure и Verify. При ошибке на любой из стадий процесс будет прерван.

Лог процесса прошивки выводится в основное окно Quartus на панели «Messages», вкладка «System».

Прервать выполнение процесса чтения/записи можно и вручную, с помощью кнопки «Stop» (вторая сверху). Данная кнопка становится доступна только на время выполнения чтения/записи конфигурации.

Всего, у левого края окна «Programmer» расположено десять кнопок. Часть из них была рассмотрена выше. Ниже описывается назначение оставшихся пяти кнопок:

- «Delete» — активна только при выборе устройства в «Device Chain» или файла в «Device Tree». Удаляет выбранное устройство и связанный с ним pof‑файл из «Programmer».

- «Add File…» — активна всегда. Используется для добавления pof‑файла в «Device Tree». В «Device Chain» будет автоматически добавлено соответствующее устройство. При добавлении нового файла существующие файлы не удаляются из списка «Device Tree».

- «Add Device…» — активна всегда. Используется для ручного добавления устройств в «Device Chain». При нажатии на кнопку открывается диалоговое окно, в котором можно выбрать одну или несколько микросхем по их маркировке.

- «Up» и «Down» — активны только тогда, когда в «Programmer» добавлено несколько микросхем ПЛИС. Используются для изменения порядка устройств в цепочке JTAG.

Все кнопки продублированы одноименными пунктами в меню «Edit» главного меню окна «Programmer».

Настройки «Device Tree» и «Device Chain» можно сохранить в общем файле с расширением cdf, который располагается в «output_files» в основной директории проекта. В проекте firstproject этот файл называется «firstproject.cdf». Относительный путь до него выводится в квадратных скобках в шапке окна «Programmer». Настройки сохраняются с помощью меню File → Save или File → «Save as». Также, «Programmer» будет предлагать сохранить файл cdf при попытке закрыть его окно, в случае если в настройки были внесены изменения.

Заключение

На этом изучение Quartus «Programmer» завершено. Осталось лишь подключить программатор к плате «CTRL‑CPLD‑EPM570». Включить саму плату. Настроить «Programmer» и загрузить конфигурацию в ПЛИС. При этом конфигурация счетчика в микросхеме будет заменена конфигурацией Вашего проекта и схема из трех независимых логических элементов готова к работе.

В результате получится устройство аналогичное изображенному на фотографии. Теперь можно опробовать работу каждого логического элемента на практике.

Пришло время подвести итоги.

В шестой части серии статей о Quartus был разобран процесс полной компиляции проекта, подключение и настройка USB Blaster. Большая часть статьи посвящена настройке Quartus «Programmer».

Сама серия на этом завершается. В статьях были затронуты основы цифровой схемотехники. Рассмотрены ключевые функции ПО Quartus. Инструмента, которым пользуются и профессионалы. Поздравляю всех дошедших до финала!

Полученные знания можно использовать для освоения проектирования цифровых схем. Начать, лучше всего, с комбинационных схем и основ математической логики. Так как комбинационные схемы строятся из базовых логических элементов. После, можно перейти к схемам с памятью — последовательным схемам. Последовательные схемы это цифровые схемы объединяющие комбинационные схемы и ячейки памяти — триггеры. Последовательные и комбинационные схемы являются фундаментом для проектирования более сложных цифровых схем: сумматоров, схем сдвига, конвейеров и т. п. А обзаведясь таким багажом знаний Вы сможете проектировать специализированные микросхемы прямо у себя дома! Первый шаг сделан.

А обзаведясь таким багажом знаний Вы сможете проектировать специализированные микросхемы прямо у себя дома! Первый шаг сделан.

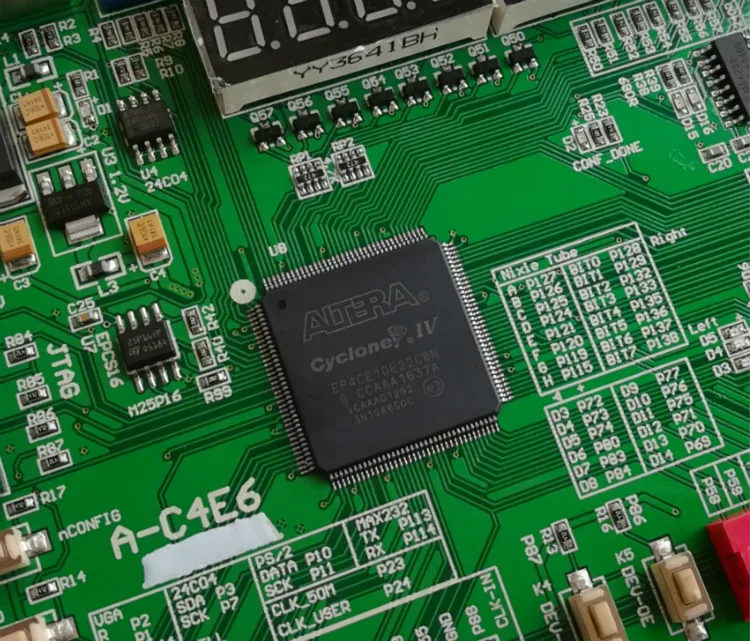

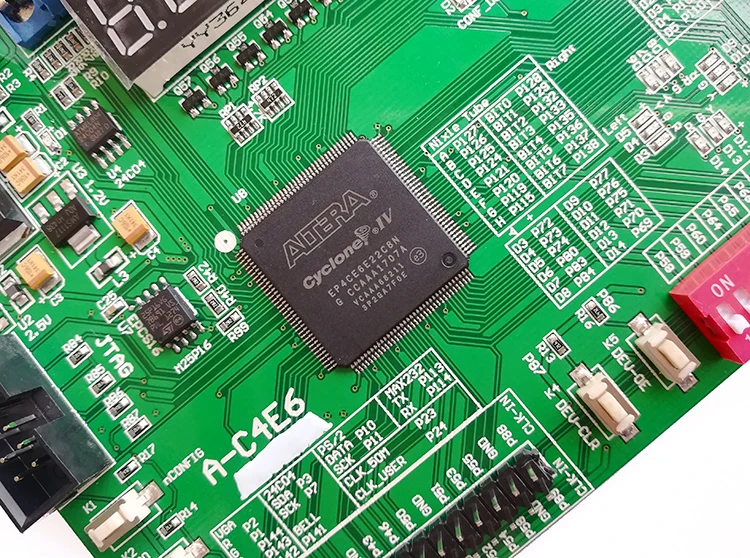

Семейства FPGA Altera

Таблица семейств ПЛИС фирмы Altera

|

Семейство |

анонс |

ТП (техпроцесс), нм |

Реком. к применению в новых разр. |

Эквив. лог. вентилей*, тыс шт. |

|

|

Stratix |

2002 |

130 |

— |

— |

|

|

Cyclone |

2002 |

130 |

+ |

— |

|

|

Straix GX |

2003 |

130 |

— |

— |

|

|

Stratix II |

2004 |

90 |

+ |

15. |

|

|

Cyclone II |

2004 |

90 |

+ |

— |

|

|

Stratix II GX |

2005 |

90 |

+ |

33.88-90.96 |

|

|

Stratix III |

2006 |

65 |

+ |

47.5-338 |

|

|

Arria GX |

2007 |

90 |

+ |

21. |

|

|

Cyclone III |

2007 |

65 |

+ |

— |

|

|

Stratix IV |

2008 |

40 |

+ |

73-813 |

|

|

Arria II GX |

2009 |

40 |

+ |

43-244 |

|

|

Cyclone IV |

2009 |

60 |

+ |

— |

|

|

Arria II GZ |

2010 |

40 |

+ |

224-349 |

|

|

Stratix V |

2010 |

28 |

+ |

236-952 |

|

|

Arria II GZ |

2010 |

40 |

+ |

— |

|

|

Cyclone V |

2011 |

28 |

+ |

25-301 |

|

|

Arria V |

2011 |

28 |

+ |

— |

|

|

Arria 10 |

2013 |

20 |

+ |

160-1150 |

|

|

Stratix 10 |

2013 |

14 |

*Эквивалентный вентиль (ЭВ) — группа

элементов БМК, соответствующая

возможности реализации логической

функции вентиля (обычно это двухвходовой

элемент И-НЕ либо ИЛИ-НЕ).

Выводы:

-

Наблюдается существенный рост внутренних ресурсов ПЛИС (в эквивалентных вентилях) от семейства к семейству

-

Практически каждый год выходит новое семейство кристаллов

-

Идет постоянное уменьшение технологических норм изготовления микросхем

-

Существует три ветки семейств – недорогие Cyclone, средней ценовой категории Arria, топовые наиболее дорогие и производительные кристаллы Stratix

-

Первым по новым технормам выпускается очередное семейство Stratix, позже Cyclone и Arria

-

Большая часть кристаллов до сих пор поддерживается и рекомендована для применения в новых разработках (т.е. не снимается с производства)

Таблица кристаллов ПЛИС семейства Stratix 10

|

10 Product Line |

GX 160 |

GX 220 |

GX 270 |

GX 320 |

GX 480 |

GX 570 |

GX 660 |

GX 900 |

GX 1150 |

GT 900 |

GT 1150 |

|

Part # Reference |

10AX016 |

10AX022 |

10AX027 |

10AX032 |

10AX048 |

10AX057 |

10AX066 |

10AX090 |

10AX115 |

10AT090 |

10AT115 |

|

Equivalent LEs |

160K |

220K |

270K |

320K |

480K |

570K |

660K |

900K |

1150K |

900K |

1150K |

|

Adaptive logic modules (ALMs) |

61,510 |

83,730 |

101,620 |

118,730 |

181,790 |

217,080 |

250,540 |

339,620 |

427,200 |

339,620 |

427,200 |

|

Registers |

246,040 |

334,920 |

406,480 |

474,920 |

727,160 |

868,320 |

1,002,160 |

1,358,480 |

1,708,800 |

1,358,480 |

1,080,800 |

|

Maximum transceiver count |

12 |

12 |

24 |

24 |

36 |

48 |

48 |

96 |

96 |

96 |

96 |

|

M20K memory blocks |

440 |

588 |

750 |

891 |

1,438 |

1,800 |

2,133 |

2,423 |

2,713 |

2,423 |

2,713 |

|

M20K memory (Mb) |

9 |

11 |

15 |

17 |

28 |

35 |

42 |

47 |

53 |

47 |

53 |

|

MLAB memory (Mb) |

1. |

1.8 |

2.4 |

2.8 |

4.3 |

5.0 |

5.7 |

9.2 |

12.7 |

9.2 |

12.7 |

|

Variable-precision digital signal processing (DSP) blocks |

156 |

191 |

830 |

985 |

1,368 |

1,523 |

1,688 |

1,518 |

1,518 |

1,518 |

1,518 |

|

18×19 multipliers |

312 |

382 |

1,660 |

1,970 |

2,736 |

3,046 |

3,376 |

3,036 |

3,036 |

3,036 |

3,036 |

|

Peak GMACS |

343 |

420 |

1,826 |

2,167 |

3,010 |

3,351 |

3,714 |

3,340 |

3,340 |

3,340 |

3,340 |

|

Single-precision floating-point multipliers |

156 |

191 |

830 |

985 |

1,368 |

1,523 |

1,688 |

1,518 |

1,518 |

1,518 |

1,518 |

|

Single-precision floating-point adders |

156 |

191 |

830 |

985 |

1,368 |

1,523 |

1,688 |

1,518 |

1,518 |

1,518 |

1,518 |

|

Peak giga floating-point operation per second (GFLOPs) |

140 |

172 |

747 |

887 |

1,231 |

1,371 |

1,519 |

1,366 |

1,366 |

1,366 |

1,366 |

|

PCI Express® (PCIe®) hardened intellectual property (IP) block(s) (up to Gen3) |

1 |

1 |

2 |

2 |

2 |

2 |

2 |

4 |

4 |

4 |

4 |

Выводы:

-

ПЛИС имеют встроенные умножители 18×19 от 312 штук в младшем кристалле, до весьма значительного количества 3036 в старшем кристалле семейства.

Встроенные

умножители могут образовывать DSP-блоки,

позволяющие проводить вычисления с

плавающей точкой.

Встроенные

умножители могут образовывать DSP-блоки,

позволяющие проводить вычисления с

плавающей точкой. -

ПЛИС имеют встроенные блоки оперативной памяти от 440 до 2713.

-

ПЛИС имеют высокоскоростные трансиверы от 12 до 96.

Соседние файлы в папке ПЛИС_20_01_15

- #

12.02.2015633.16 Кб13Achronix Speedster22i_Product_Brief_PB024_RUS.pdf

- #

12.02.2015361.78 Кб15Actel.pdf

- #

12.02.201533.28 Кб13Вопросы к экзамену_2013_2014+.doc

- #

12.02.2015208.9 Кб33Конфигурирование микросхем Cyclone II.doc

- #

12.02.2015102.4 Кб23Семейства FPGA Altera.doc

- #

12.02.201580.38 Кб13Список доп. вопросов_2014+.doc

- #

12.02.2015759.

81 Кб35Учебное пособие Архитектура микросхем семейства Cyclone II_3.doc

81 Кб35Учебное пособие Архитектура микросхем семейства Cyclone II_3.doc - #

12.02.201584.48 Кб25Учебное пособие Основы VHDL_3.doc

Intel Plus Altera

Системы и дизайн

МНЕНИЕ

Почему за этой сделкой стоит следить с помощью мощного увеличительного стекла.

С тех пор, как в начале этого месяца сделка Intel-Altera достигла стадии рукопожатия, было выдвинуто множество теорий и поднято множество вопросов. И было очень мало ответов, отчасти потому, что сделка еще не завершена, а отчасти потому, что этому браку потребуется время, чтобы разыграться на рынке — может быть, годы.

Но, наряду с объединением GlobalFoundries и IBM, это еще одна действительно потрясающая для отрасли сделка. Оба будут иметь постоянные последствия, которые будут ощущаться в глобальном масштабе.

Соперничество Intel и Altera имеет последствия для литейного бизнеса Intel, для оборонной промышленности США, для проникновения Intel на рынки, где она имела лишь ограниченный успех, и для оплота Intel внутри корпоративных центров обработки данных.

Semiconductor Engineering задает вопросы с тех пор, как слухи об этой сделке начали доходить до множества руководителей и инженеров, о том, что эта сделка означает для них и как они видят ее развитие. И почти со всех сторон эта сделка имеет огромный смысл — стратегически и тактически.

Послужной список Intel в области приобретений в лучшем случае неоднозначен, и предыдущая история действительно вызывает некоторые законные вопросы. На протяжении 1990-х и начала 2000-х компания пыталась войти в бизнес коммуникационных серверов, покупая такие компании, как Dialogic и Voice Technologies и Xircom, но никогда не имела четкого плана того, как ей победить на этом рынке. Intel на какое-то время тоже занялась производством ПК с белыми ящиками, но бросила все это, когда вернулась к осознанию того, что в глубине души это процессорная компания.

Успех Intel связан с большими процессорами — такими, которые могут обрабатывать миллиарды транзакций внутри центров обработки данных, будь то внутренние облака, публичные облака или любая другая конфигурация или имя, которое вы, возможно, захотите присвоить им, — и процессоры меньшего размера. которые могут питать настольные или портативные компьютеры. Компания полностью упустила революцию в области мобильных телефонов, упустила многие вертикальные возможности, которые появились на домашнем, автомобильном и промышленном рынках, и остаются вопросы о том, насколько успешной она будет на рынке устройств IoT.

которые могут питать настольные или портативные компьютеры. Компания полностью упустила революцию в области мобильных телефонов, упустила многие вертикальные возможности, которые появились на домашнем, автомобильном и промышленном рынках, и остаются вопросы о том, насколько успешной она будет на рынке устройств IoT.

Но когда речь идет о стандартных продуктах, то есть о снижении затрат, уменьшении маржи, сокращении возможностей, разработке новых технологических процессов и выводе на рынок мощных, энергосберегающих и проверенных на рынке чипов, Intel выигрывает. Что делает сделку с Altera такой интересной, так это то, что, как и процессоры Intel, FPGA являются стандартными продуктами. Они придерживаются закона Мура. Но они также предлагают гибкость, позволяющую настраивать серверы в облаке, чтобы их можно было использовать в качестве гетерогенных многоядерных машин, что означает, что они могут быть очень энергоэффективными или чрезвычайно мощными, или и тем, и другим. И их можно настроить на любую конфигурацию и перенастроить позже.

Эти микросхемы также могут быть объединены в стек с использованием переходников, мостов или сквозных переходных отверстий в кремнии, в зависимости от того, как Intel решит упаковать эти микросхемы, чтобы повысить как производительность, так и снизить энергопотребление. На самом деле, комбинация этих технологий обеспечит такие преимущества в мощности/производительности, которых не было со времен классического масштабирования, до 90 нм и, возможно, даже больше. Intel публично заявила, что стековые архитектуры будут иметь важное значение для продолжения действия закона Мура. Чего он не сказал, так это того, как он туда попадет. Altera — ключевой элемент этой головоломки.

С тактической точки зрения сделка Intel-Altera имеет и другие преимущества. Во-первых, это обеспечивает крупного клиента для Intel Custom Foundry и стабильный поток доходов, который может помочь покрыть огромные затраты на содержание передовой фабрики. Стоимость разработки передового техпроцесса и наполнения его новым оборудованием настолько высока, что даже Intel приходится открывать свое производство для других производителей микросхем. Это как открыть большой дом для постояльцев, чтобы субсидировать его содержание. Во-вторых, это открывает для Intel доступ к рынкам, где FPGA сильны, — связи, сети, автомобилестроению, тестированию и измерению, телевизионным приставкам и телевизорам, а также обороне.

Это как открыть большой дом для постояльцев, чтобы субсидировать его содержание. Во-вторых, это открывает для Intel доступ к рынкам, где FPGA сильны, — связи, сети, автомобилестроению, тестированию и измерению, телевизионным приставкам и телевизорам, а также обороне.

Аспект защиты интересен в свете продажи заводов IBM компании GlobalFoundries. Американская оборонная промышленность изо всех сил пытается обеспечить безопасность своей цепочки поставок, но с уходом IBM у нее есть только один другой вариант для передового цифрового литейного завода в Соединенных Штатах — Intel. (См. Соответствующую статью здесь.) Это может оказаться новым и прибыльным рынком для литейных услуг Intel.

Так что же станет с браком между этими компаниями? Если сделка будет одобрена регулирующими органами, она может иметь серьезные последствия для многих рынков. В отличие от предыдущих сделок, когда Intel либо поглощала компании, как гигантскую черную дыру, либо более поздних сделок, таких как McAfee и Wind River, где эти компании сохранялись как полунезависимые операции, сделка Altera сулит огромные перспективы при правильном управлении. Конечно, время покажет, будет ли управляться должным образом, и отчасти это будет зависеть от того, насколько хорошо будут сочетаться культуры двух компаний. Но это, безусловно, определяющая для отрасли сделка, и на нее стоит обратить внимание через мощное увеличительное стекло.

Конечно, время покажет, будет ли управляться должным образом, и отчасти это будет зависеть от того, насколько хорошо будут сочетаться культуры двух компаний. Но это, безусловно, определяющая для отрасли сделка, и на нее стоит обратить внимание через мощное увеличительное стекло.

Теги: Altera бизнес Министерство обороны Dialogic FPGA GlobalFoundries IBM Intel M&A McAfee Moore’s Law Stacked Die Голосовые технологии Wind River Xircom

Intel Plus Altera – EEJournal

На этой неделе активно обсуждались слухи о том, что Intel в переговорах о покупке Altera — в сделке, которая должна стоить более десяти миллиардов и которая станет крупнейшим приобретением в истории Intel. Хотя ни одна из компаний пока ничего не говорит публично, имеется значительный объем доступной информации, из которой можно оценить потенциальное влияние такого шага и высказать предположения о его причинах.

Мы фактически предсказали это восемь месяцев назад в нашей статье с метким названием « Когда Intel покупает Altera » (тонкое название, не так ли?), и аргументы, которые мы привели тогда, актуальны и сегодня. Но, имея за плечами почти еще один год прогресса, мы должны быть в состоянии значительно повысить разрешение нашего хрустального шара. Хотя эти слухи привлекли значительное внимание прессы и аналитиков, мы считаем, что аналитики в значительной степени ошибаются. Мы рассмотрим проблемы с аналитическими теориями отдельно, а пока вот наше мнение:

Но, имея за плечами почти еще один год прогресса, мы должны быть в состоянии значительно повысить разрешение нашего хрустального шара. Хотя эти слухи привлекли значительное внимание прессы и аналитиков, мы считаем, что аналитики в значительной степени ошибаются. Мы рассмотрим проблемы с аналитическими теориями отдельно, а пока вот наше мнение:

Также обратите внимание, что на момент написания этой статьи не было объявлено ни о какой сделке. Мы здесь спекулируем – будьте бдительны.

Холодная война вычислительной техники

Intel, как всем известно, десятилетиями доминировала в производстве процессоров для персональных компьютеров и центров обработки данных. Однако в последние годы рынок персональных компьютеров не изменился, а маржа и прибыль от персональных компьютеров упали. Intel все чаще полагалась на высокопроизводительные процессоры для центров обработки данных, чтобы обеспечить маржу и прибыль, которые необходимы крупнейшей в мире полупроводниковой компании, чтобы оставаться на плаву и оставаться актуальным.

Но Intel ни в коем случае не является ведущим поставщиком процессоров. Если мы сравним количество процессоров, развернутых по всему миру, вклад Intel затмит вклад ARM. С бурным развитием мобильных вычислений ARM быстро завоевала титул самой производительной процессорной архитектуры — ежегодно по всему миру устанавливаются миллиарды процессоров. Intel несколько раз пыталась (и потерпела неудачу) попасть в мобильную игру. Несмотря на благородные усилия, такие как семейство процессоров Atom, компании не удалось добиться такой тяги, необходимой для того, чтобы сделать хотя бы крошечную брешь в доминировании ARM на мобильных устройствах. Это оставило мир процессоров в своего рода негласном соглашении — разрядке, если хотите — с Intel, оставшейся на высокопроизводительной стороне нейтральной зоны, а ARM сосредоточилась на сверхмаломощных мобильных вычислениях.

Новое поле битвы — центр обработки данных

В течение многих лет доминирование центров обработки данных было связано с кубическими MIPS. Тяжелые процессоры, которые обеспечивали максимальную вычислительную производительность, правили насестом — будь проклята цена и мощность. Именно этот факт удерживает маржу и прибыль Intel на плаву. А глобальный перенос вычислительной нагрузки в облако породил избыток гигагерц, и огромные новые серверные фермы заполнили свои голодные стойки дойными коровами Intel, загруженными кешем.

Тяжелые процессоры, которые обеспечивали максимальную вычислительную производительность, правили насестом — будь проклята цена и мощность. Именно этот факт удерживает маржу и прибыль Intel на плаву. А глобальный перенос вычислительной нагрузки в облако породил избыток гигагерц, и огромные новые серверные фермы заполнили свои голодные стойки дойными коровами Intel, загруженными кешем.

Но затем тревожная тенденция рынка и технологий нарушила стабильное спокойствие нашего соглашения о процессорах. Изменились приоритеты центров обработки данных. Самой большой статьей расходов в центрах обработки данных была мощность, поэтому энергопотребление (а не скорость процессора) стало ходовым товаром в серверном оборудовании. Подсчитано, что в настоящее время центры обработки данных потребляют от одного до десяти процентов электроэнергии, вырабатываемой в мире. И это число, по прогнозам, значительно возрастет. Сегодня при строительстве нового центра обработки данных наивысшим приоритетом является доступ к дешевой электроэнергии, в результате чего многие огромные установки располагаются вблизи плотин гидроэлектростанций и других объектов, где доступно огромное количество недорогой электроэнергии и охлаждения.

ARM быстро заметили эту тенденцию и отреагировали, смело перейдя в нейтральную зону. Компания создала серию высокопроизводительных процессорных архитектур уровня центра обработки данных, которые в полной мере используют арсенал вычислительных технологий ARM с низким энергопотреблением. Полученные продукты представляют серьезную угрозу для Intel в новом поколении маломощных процессоров для центров обработки данных.

У ARM, конечно же, нет фабрики, которую нужно поддерживать, и ей не нужно держать маржу на чипах. Эта проблема оставлена на усмотрение бешеной толпы лицензиатов ARM — все они более чем готовы обменять маржу на долю рынка в отчаянной надежде прорваться в какую-нибудь туманную прибыльную позицию в будущем. Результатом может стать целая серия вариантов на базе ARM, которые проталкиваются в большие запросы предложений по серверному кремнию.

Intel до сих пор успешно защищала свою территорию от микросерверов на базе ARM. Они сделали это, используя подход «охватить все базы»: расширение многоядерных устройств Xeon до 18 ядер; включение микросерверов на базе Atom с очень похожими на ARM показателями мощности/производительности; и создание сопроцессора Xeon Phi с 61 ядром. Все вышеперечисленное поставляется сегодня на 22-нм FinFET. Количество ядер, безусловно, будет больше на 14-нм FinFET, а мощность / производительность получит существенный толчок с грядущей микроархитектурой Skylake. Короче говоря, Intel развернула впечатляющие обычные средства защиты, чтобы защитить себя от обычных атак.

Все вышеперечисленное поставляется сегодня на 22-нм FinFET. Количество ядер, безусловно, будет больше на 14-нм FinFET, а мощность / производительность получит существенный толчок с грядущей микроархитектурой Skylake. Короче говоря, Intel развернула впечатляющие обычные средства защиты, чтобы защитить себя от обычных атак.

Если мы настроим наш хрустальный шар на точную частоту оперативной комнаты в Intel, мы, вероятно, сможем предсказать, о чем думает мозговой трест Intel: «Пока все хорошо — микросерверы действительно не повлияли на центр обработки данных существенным образом. , и, если они это сделают, мы можем ответить всем нашим колчаном альтернатив ».

Мозговой трест также, вероятно, был утешен тем фактом, что крепость центра обработки данных Intel окружена вездесущим огромным рвом x86 — миллиардами строк кода устаревших приложений для центров обработки данных, уже оптимизированных и отлаженных с учетом серверов X86. «Мы в безопасности», — вероятно, думали они. «Никакая новая архитектура не сможет пересечь ров, что приведет к переписыванию всего этого работающего программного обеспечения». Intel также воспользовалась своим преимуществом в технологии FinFET, особенно в линейке продуктов Xeon, где улучшенная мощность/производительность оказала наибольшее влияние.

Intel также воспользовалась своим преимуществом в технологии FinFET, особенно в линейке продуктов Xeon, где улучшенная мощность/производительность оказала наибольшее влияние.

Оружие судного дня — гетерогенные вычисления на основе ПЛИС

Для тех, кто полагается на защиту на основе рва, нет ничего более неприятного, чем прибытие катапульты. И в середине 2014 года катапульта, несомненно, появилась — ее выкатили на поле битвы не кто иной, как ребята из Bing из Microsoft. «Катапульта» — это (по иронии судьбы) название проекта Microsoft , который ускорил алгоритмы поисковой системы Bing с использованием вычислений гибридного процессора FPGA. Согласно документу, упомянутому выше, «[Проект Catapult] показал, что среднемасштабное развертывание FPGA может увеличить пропускную способность ранжирования в производственной поисковой инфраструктуре на 95% при сравнимой задержке с программным решением. Добавленные вычислительные платы FPGA увеличили энергопотребление только на 10%».

Это большое дело. Нет, это большое дело. Если объединение обычных процессоров с FPGA может значительно снизить энергопотребление центра обработки данных, это может стать достаточной мотивацией для больших армий, чтобы попытаться переплыть ров. Если бы это сработало для Bing, не требовалось особого видения, чтобы представить таких игроков, как Google, Facebook, YouTube, Amazon и Netflix, высовывающих свои перископы, чтобы увидеть, могут ли вычисления на основе FPGA сократить их счета за электроэнергию на ноль или два. Было бы целесообразно вложить значительные средства в повторную оптимизацию программного обеспечения, чтобы значительно снизить энергопотребление. Пункт проверки катапульты показал, что это можно сделать.

Убежденные приверженцы философии Энди Гроува «выживают только параноики», мозговой трест Санта-Клары ясно осознал появление этой поистине разрушительной морфологической технологии. Действительно, Intel не только зарегистрировала эту новую технологию, , но и анонсировала гибридный продукт Xeon-FPGA . Как мы отметили во время упомянутого объявления, ряд важных элементов, как ни странно, отсутствовал: идентификатор производителя FPGA (одна маленькая деталь) и название продукта . Само собой разумеется, что цены и доступности также нигде не было.

Как мы отметили во время упомянутого объявления, ряд важных элементов, как ни странно, отсутствовал: идентификатор производителя FPGA (одна маленькая деталь) и название продукта . Само собой разумеется, что цены и доступности также нигде не было.

Между тем, Xilinx и Altera представили настоящие, осязаемые, работающие семейства чипов для гибридных вычислений, которые не только были запущены в производство, но и имели реальные названия продуктов (Zynq и SoC FPGA соответственно). Оба этих семейства имели полноценные многоядерные процессорные подсистемы ARM с высокоскоростными встроенными соединениями с матрицей FPGA. Intel пока не о чем беспокоиться, верно? Ведь эти устройства предназначены для встраиваемых приложений, а не центров обработки данных. Но, очевидно, монолитная интеграция этих устройств давала существенные преимущества перед простой парковкой процессоров рядом с ПЛИС. Соединение на кристалле между процессором и матрицей FPGA дает значительные преимущества в производительности и энергопотреблении, и ничто из того, что Intel может сделать, просто партнерство с компаниями, производящими FPGA, не компенсирует это потенциальное преимущество. С точки зрения Intel, это может вызывать беспокойство.

С точки зрения Intel, это может вызывать беспокойство.

Еще более тревожным был тот факт, что Altera активно рекламировала процесс проектирования, основанный на OpenCL (язык программирования, предназначенный для ускорения высокопроизводительных вычислительных алгоритмов на высокопараллельных графических процессорах), что позволяет «компилировать» код OpenCL для ПЛИС. Затем, в конце прошлого года, Xilinx анонсировала свою платформу SDAccel — , четко позиционирующую устройства Zynq для приложений центров обработки данных . Итак, вот оно. Altera в качестве «заклятого врага» с их потоком OpenCL FPGA, а Xilinx с мощным монолитным гибридным вычислительным устройством, уже находящимся в серийном производстве, с реальным потоком рабочих инструментов. Похоже, Zynq и SoC FPGA в конце концов предназначены не только для встраиваемых систем. Эти новые платформы ПЛИС представляют явную и реальную опасность — ракеты со значительной разрушительной силой. И они, кажется, нацелены прямо на родину Intel.

Еще больше усилив потенциальное беспокойство, компания Xilinx объявила около месяца назад, что будущие устройства Zynq UltraScale+ на базе 16-нм FinFET перейдут на четырехъядерный 64-разрядный процессор ARM Cortex-A53, а также множество специальных целевые процессоры — все они тесно связаны с высокопроизводительной матрицей FPGA. Можно себе представить, как все это вызывает серьезное колебание по шкале Рихтера на измерителе паранойи в Санта-Кларе. «Что, если эта модель гибридных вычислений взлетит? И что еще более важно, что, если эта модель гибридных вычислений начнет работать с процессорами ARM?» Это КЛАССИЧЕСКИЙ материал Клейтона Кристенсена: скромные встраиваемые устройства, Zynq и SoC FPGA, могут чувствовать себя комфортно в центре обработки данных.

Очевидно, что все, что потенциально может быть запущено в центре обработки данных с процессорами ARM, должно вызвать «все руки на палубе» в Intel. Чем больше они изучали возможности, тем серьезнее, вероятно, относились к гибридным вычислениям. Несколько абзацев назад мы использовали термин «морфологический», и вам, возможно, до сих пор интересно, что это слово означает. В данном контексте это означает взять набор существующих технологий и объединить их вместе для создания совершенно новой технологии. Процессоры с хорошими характеристиками мощности/производительности, проверьте. Ткань FPGA с гораздо лучшими характеристиками мощности/производительности, проверьте.

Несколько абзацев назад мы использовали термин «морфологический», и вам, возможно, до сих пор интересно, что это слово означает. В данном контексте это означает взять набор существующих технологий и объединить их вместе для создания совершенно новой технологии. Процессоры с хорошими характеристиками мощности/производительности, проверьте. Ткань FPGA с гораздо лучшими характеристиками мощности/производительности, проверьте.

И, наконец, сквозной поток разработки программного обеспечения, подходящий для разработки и развертывания приложений для центров обработки данных, основанный на передовых технологиях, таких как высокоуровневый синтез, позволяющий смертным программистам эффективно использовать модель гибридных вычислений, ммм… своего рода проверка… — Иш? О, ладно, может быть, не совсем так. Давайте поговорим об этом подробнее через минуту.

Добро пожаловать в дивный новый мир гетерогенных вычислений на основе FPGA.

Те читатели, которые уделяют пристальное внимание, могут подумать, что гибридные процессоры Xeon-FPGA, которые еще не получили названия, могли бы стать вполне разумным первым шагом для Intel, если они когда-нибудь потрудятся назвать их. Однако, если гибридные вычисления на основе FPGA играют больше, чем символическую роль в дорожной карте центров обработки данных Intel, поставка этих устройств в партнерстве с Altera просто не поможет. Intel должна владеть всеми элементами, которые мы отметили в предыдущем абзаце.

Однако, если гибридные вычисления на основе FPGA играют больше, чем символическую роль в дорожной карте центров обработки данных Intel, поставка этих устройств в партнерстве с Altera просто не поможет. Intel должна владеть всеми элементами, которые мы отметили в предыдущем абзаце.

Чтобы защитить свое господствующее положение в центрах обработки данных, Intel необходимо владеть обычным процессором. Это может быть процессор Atom (который в 64-битных четырехъядерных воплощениях уже не является Atom вашего отца) или это может быть процессор Xeon, но, рискуя констатировать весьма очевидное, Intel действительно, действительно нуждается в нем, чтобы НЕ быть процессором ARM. Кроме того, если часть уравнения, связанная с обычными процессорами, основана на x86, Intel получает возможность свободно преодолевать собственный ров. Весь этот устаревший серверный код будет работать как есть, и клиенты смогут в свободное время перепроектировать свое программное обеспечение, чтобы воспользоваться преимуществами повышения мощности/производительности за счет матрицы FPGA.

Но для преодоления проблем, присущих двухчиповому решению, Intel необходимо владеть структурой FPGA. Не просто производить, а владеть. Конечно, Intel могла бы сначала использовать «готовые» устройства Stratix, оснащенные процессорами Xeon, но им быстро понадобится матрица FPGA, предназначенная для гибридных вычислений, и они быстро захотят преодолеть задержку, производительность и снижение энергопотребления, связанные с подключением процессоры в структуру FPGA с помощью чего-то вроде QPI Express. Конечным этапом являются полностью интегрированные монолитные решения, разработанные специально для центра обработки данных, что положительно требует наличия фабрики FPGA.

Корпорация Intel должна владеть всей цепочкой инструментов для гибридных вычислений и управлять экосистемой, что является ключевыми компетенциями.

Программные средства — ахиллесова пята

Проблема с доказательством Catapult заключается в том, что не каждое приложение центра обработки данных так просто, как поиск . Если вы можете изолировать один или два важных фрагмента кода в своем приложении и потратить время и энергию на их оптимизацию, чтобы воспользоваться преимуществами фабрики FPGA на гибридной платформе, вы сможете получить огромные преимущества в плане мощности и производительности. Bing и Google могли позволить себе привлечь к решению этой проблемы много талантов.

Если вы можете изолировать один или два важных фрагмента кода в своем приложении и потратить время и энергию на их оптимизацию, чтобы воспользоваться преимуществами фабрики FPGA на гибридной платформе, вы сможете получить огромные преимущества в плане мощности и производительности. Bing и Google могли позволить себе привлечь к решению этой проблемы много талантов.

Но, чтобы помочь в общем случае приложений центра обработки данных, вам нужен поток инструментов, который намного ближе к «компилятору» — что-то, что вы могли бы указать на кучу устаревшего кода и сказать: «Заставьте это работать!» Программные инструменты, которые могут выполнить эту задачу, все еще далеки.

И для Intel даже программные инструменты, которые могут заставить матрицу FPGA вообще что-то делать, очень далеки. На самом деле, программные инструменты — это самая мощная защита, которую Altera и Xilinx используют для отражения атак на их дуополию FPGA. Снова и снова стартапы FPGA привлекали финансирование, создавали впечатляющие чипы, но терпели крах и сгорали, потому что не могли получить надежный, работающий поток инструментов, который позволял бы клиентам использовать их. Программные инструменты Xilinx и Altera претерпели десятилетия эволюции сотен талантливых инженеров с использованием десятков тысяч разработок клиентов, доказывая клиентам, что они могут надежно перейти от кода к работающей FPGA, подвиг, которого не достигла ни одна другая компания.

Программные инструменты Xilinx и Altera претерпели десятилетия эволюции сотен талантливых инженеров с использованием десятков тысяч разработок клиентов, доказывая клиентам, что они могут надежно перейти от кода к работающей FPGA, подвиг, которого не достигла ни одна другая компания.

Как мы говорили в первой статье, Intel, вероятно, могла бы поручить каждому инженеру задачу разработки инструментов FPGA на следующее десятилетие, и они не смогли бы достичь того уровня, который сегодня занимают Xilinx и Altera.

Но Xilinx и Altera по-прежнему далеки от инструментальной среды, необходимой для того, чтобы инженеры-программисты центров обработки данных могли использовать преимущества гибридных процессоров FPGA. Да, Altera использует методологию OpenCL, которая позволяет использовать код высокопроизводительных вычислений, изначально написанный для графических процессоров (GPU), и заставить его работать на FPGA. У Xilinx есть свой SDAccel с технологией HLS, который может использовать алгоритмы, написанные на C, C++ и OpenCL, и (при участии компетентных инженеров по оборудованию) получить что-то, что будет работать на гибридной платформе, такой как их устройства Zynq. Фактически, только на прошлой неделе Xilinx немного удвоился — объявляет о своей «платформе SDSoC ». SDSoC позволяет командам специалистов как по программному, так и по аппаратному обеспечению работать вместе, чтобы воплотить в жизнь гибридные вычислительные приложения.

Фактически, только на прошлой неделе Xilinx немного удвоился — объявляет о своей «платформе SDSoC ». SDSoC позволяет командам специалистов как по программному, так и по аппаратному обеспечению работать вместе, чтобы воплотить в жизнь гибридные вычислительные приложения.

Чтобы вывести инструменты разработки на новый уровень для приложений для центров обработки данных, Intel необходимо сделать больше, чем просто сотрудничать с Xilinx или Altera. Предоставленные сами себе, эти две компании продолжат свою многолетнюю вражду — борьбу за превосходство на рынке коммуникационной инфраструктуры и попытки расширения путем перемещения своих устройств Zynq и SoC FPGA на развивающиеся рынки, такие как встроенное зрение, промышленная автоматизация, автомобильные и другие приложения под эгидой «IoT». В конечном итоге они могут добраться до центра обработки данных — если это будет удобно.

Практический результат

Чтобы защитить свой центр обработки данных от надвигающейся угрозы повстанцев на базе ARM и FPGA, Intel необходимо владеть Xilinx или Altera.