Что такое ПЛИС и FPGA. Как устроены программируемые логические интегральные схемы. Какие бывают типы ПЛИС. Для чего применяются ПЛИС в электронике. Преимущества и недостатки ПЛИС по сравнению с другими решениями.

Что такое ПЛИС (FPGA) и как они устроены

ПЛИС (программируемая логическая интегральная схема) или FPGA (Field Programmable Gate Array) — это электронный компонент, используемый для создания цифровых интегральных схем. Главное отличие ПЛИС от обычных цифровых микросхем заключается в том, что логика их работы не определяется при изготовлении, а задаётся посредством программирования.

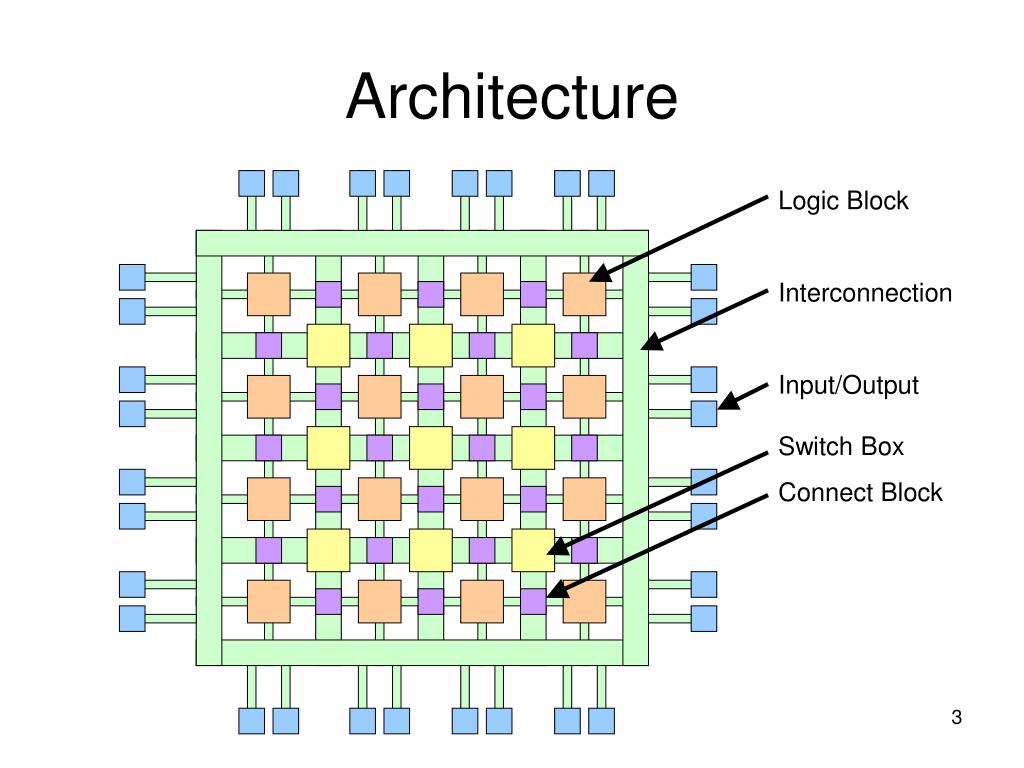

Основные составляющие архитектуры ПЛИС:

- Конфигурируемые логические блоки, реализующие требуемые логические функции

- Программируемые электронные связи между логическими блоками

- Программируемые блоки ввода/вывода для связи с внешними выводами микросхемы

- Блоки памяти, DSP-блоки, умножители, PLL и другие специализированные компоненты (в современных ПЛИС)

Для программирования ПЛИС используются специальные средства — программаторы и среды разработки, позволяющие задать структуру цифрового устройства в виде принципиальной схемы или программы на языках описания аппаратуры (Verilog, VHDL и др.).

Основные типы ПЛИС по способу хранения конфигурации

Существует несколько основных типов ПЛИС, различающихся по способу хранения конфигурации:

SRAM-based ПЛИС

Одна из наиболее распространенных разновидностей. Конфигурация хранится в ячейках статической памяти. Преимущества:

- Возможность многократного перепрограммирования

- Относительно низкая стоимость

Недостатки:

- Необходимость перезагрузки конфигурации после включения питания

- Требуется дополнительная микросхема для хранения конфигурации

Flash-based ПЛИС

Хранение конфигурации во внутренней Flash или EEPROM памяти. Преимущества:

- Сохранение конфигурации при отключении питания

- Не требуется дополнительных микросхем памяти

Недостатки:

- Более высокая стоимость из-за сложности производства

- Ограниченное количество циклов перезаписи

Antifuse ПЛИС

Однократно программируемые ПЛИС. Преимущества:

- Высокое быстродействие

- Высокая надежность

- Устойчивость к радиации

Недостатки:

- Невозможность перепрограммирования

- Высокая стоимость

Сферы применения ПЛИС

ПЛИС находят применение во многих областях электроники и вычислительной техники:

- Цифровая обработка сигналов

- Прототипирование ASIC

- Реализация нейронных сетей

- Криптография

- Высокоскоростная передача данных

- Аэрокосмическая и военная техника

- Системы машинного зрения

- Автомобильная электроника

Преимущества и недостатки ПЛИС

Основные преимущества ПЛИС по сравнению с другими решениями:

- Гибкость и возможность перепрограммирования

- Быстрая разработка и отладка устройств

- Возможность параллельной обработки данных

- Низкая стоимость при мелкосерийном производстве

Недостатки ПЛИС:

- Более высокое энергопотребление по сравнению с ASIC

- Меньшая производительность по сравнению с заказными микросхемами

- Высокая сложность разработки для сложных проектов

- Необходимость специального ПО и навыков программирования

Процесс разработки проектов на ПЛИС

Разработка проектов для ПЛИС обычно включает следующие этапы:

- Создание описания проекта на языке описания аппаратуры (Verilog, VHDL) или в виде схемы

- Функциональное моделирование для проверки логики работы

- Синтез проекта — преобразование описания в список цепей

- Размещение и трассировка — распределение логических ресурсов ПЛИС

- Временное моделирование с учетом задержек

- Генерация конфигурационного файла для программирования ПЛИС

- Загрузка конфигурации в ПЛИС и отладка на реальном устройстве

Ведущие производители ПЛИС

Основными производителями ПЛИС на мировом рынке являются:

- Xilinx — крупнейший производитель, серии Virtex, Kintex, Artix

- Intel (Altera) — серии Stratix, Arria, Cyclone

- Lattice Semiconductor — серии ECP, iCE, MachXO

- Microchip (Microsemi) — серии PolarFire, IGLOO, ProASIC

Каждый производитель предлагает свои линейки ПЛИС с различными характеристиками и областями применения.

Заключение

ПЛИС представляют собой мощный и гибкий инструмент для разработки цифровых устройств. Несмотря на сложность освоения, они открывают широкие возможности для создания эффективных аппаратных решений в различных областях электроники. По мере развития технологий ПЛИС становятся все более производительными и доступными, что способствует их все более широкому применению.

Технология FPGA для тысячи применений / Хабр

Трудно представить другую технологию, которая настолько разносторонняя как FPGA.FPGA — Field-Programmable Gate Array, то есть программируемая логическая матрица (ПЛМ), программируемая логическая интегральная схема (ПЛИС). Это технология, при которой создается микросхема с набором логических элементов, триггеров, иногда оперативной памяти и программируемых электрических связей между ними. При этом программирование FPGA оказывается похоже на разработку электрической схемы, а не программы. Пользуюсь данной технологией давно и попробую описать самые полезные с моей точки зрения применения по мере их усложнения.

1. Помощь при разводке плат

Многие наверняка сталкивались, что центральный процессор, память, другие многоногие микросхемы создавали люди, редко задумывающиеся о том, как они будут соединяться на печатной плате. Протянуть шину разрядностью 32 или 64 бита — задача не решаемая без многослойной платы. Но стоит поставить между микросхемами FPGA как разводка становится на несколько порядков проще:

И все это благодаря возможности внутренней перекоммутации сигналов внутри FPGA.

2. Согласование уровней сигналов

Часть микросхем имеет интерфейс 1.2В, другая 1.5, 1.8, 2.5, 3.3В, и все эти микросхемы можно подключить к одной FPGA и обеспечить двусторонний обмен за счет того, что любая FPGA имеет несколько банков ввода-вывода, каждый из которых может иметь свое опорное напряжение сигналов. Например, так:

3. Обеспечение надежности устройства

FPGA достаточно дорогие, но надежные устройства. Они начинают включаться при меньшем напряжении, чем номинальное, выдерживают импульсные наводки, часто короткое замыкание на ножках IO, быстро загружаются и могут использоваться для контроля и управления процессорами и умной периферией. Плюс могут реализовывать вспомогательные функции коммутации, задержек, моргания светодиодом и так далее. Мне очень нравится использовать FPGA (маленький PLD) как умный сторожевой таймер и схема запуска — ни разу не подводил.

4. Автоматы состояний или аппаратное программирование

Если на процессоре сначала создается «исполнитель команд», то есть процессор, а потом в него загружается последовательность команд, то на FPGA можно писать программу с командами, вшитыми в структуру прошивки. При этом отсутствует избыточность процессора, появляется малое потребление при той же скорости и функциональности, гарантированное время выполнения и высокая надежность. Пример такого автомата состояний:

5. Создание процессора внутри FPGA

Считается, что каждый программист должен написать хотя бы один компилятор, а каждый инженер должен разработать хотя бы один процессор. Это очень интересный и важный процесс, позволяющий лучше понять как работают микропроцессоры, при этом можно оптимизировать под свои задачи систему команд, встраивать большое количество одновременно работающих процессоров в одну микросхему и получать настоящую многозадачность с низким энергопотреблением. При этом структура процессора проста и легко реализуема на FPGA:

Недостатком такого процессора является отсутствие готовых компиляторов и отладчиков.

6. Использование готовых библиотек процессоров для FPGA

Библиотеки готовых процессоров есть у любого производителя FPGA (от 8086 до ARM), позволяют быстро создать процессор с определенным набором периферии и вставить его в проект FPGA. К процессору прилагается компилятор и отладчик. Быстро, удобно, но избыточно и потому ограничено по быстродействию. Пример структуры готовой библиотеки процессора:

7. Объединять процессор и периферию в одной микросхеме — SoC (System-On-Chip)

SoC — достаточно новая технология, решающая самую страшную проблему инженера, необходимость протаскивать по плате много высокоскоростных интерфейсов, которых всегда оказывается недостаточно, и которые необходимо программно поддерживать. Технология SoC позволяет в одной микросхеме иметь полноценный центральный процессор (поддерживающий операционную систему Linux, например) или микроконтроллер и большую FPGA, соединенные логическими сигналами, общей внутренней памятью и интерфейсами к внешней. То есть проблема эффективной, простой и быстрой передачи информации между FPGA и процессором успешно решена! Пример структуры SoC:

8. Модные приложения типа crypto mining

Вспоминая, что FPGA — это набор логических ячеек и триггеров, работающих параллельно, на FPGA можно проводить много параллельных операций, что отличает от процессора, параллельность которого ограничена количеством ядер и потоков. Поэтому можно использовать FPGA как сопроцессор к центральному процессору, вынося на FPGA все самые требовательные к вычислительной мощности операции. Например, центральный процессор занимается логической обработкой задачи, а FPGA параллельно вычисляет контрольные суммы, хэши, ищет совпадения, перебирает варианты и так далее. Быстродействие FPGA ограничено только количеством параллельных блоков и временем выполнения одной операции. Отладив таким образом вычисления можно заказать ASIC, то есть заказную микросхему, выполняющую те же функции, но дешевле (при массовом производстве) и с меньшим энергопотреблением. И данная идея оказалась настолько перспективной и удобной, что гиганты разработки FPGA начали создавать специальное ПО, позволяющее интерактивно переносить части вычислений из программы на C/C++ в FPGA и контролировать быстродействие (HLS, High-Level Synthesis). Есть готовые платы с быстрыми интерфейсами для этого и средства отладки. Очень интересная и перспективная тема для использования.

9. Реализация нейронных сетей на FPGA

Нейронные сети и глубокие нейронные сети сейчас активно используются в разных областях, но реализация их на процессоре оказывается неэффективной — существует много вычислений, которые можно распараллелить (нейроны одного слоя, например, вычисляются независимо).

Поэтому перенеся нейронную сеть на FPGA удается на много порядков ускорить работу нейронной сети, остается обеспечить высокоскоростной интерфейс для загрузки исходных данных и получения результата. В качестве примера — реализация системы распознавания лиц на процессоре i7/9Gen распознает до 20 лиц за секунду с одной видеокамеры HD, реализация на FPGA — порядка 1000 лиц с нескольких камер. Структура используемой глубокой нейронной сети:

Это только часть применений FPGA, с которыми можно столкнуться.

И жаль, что не так много людей ее активно используют и развивают.

ПЛИС — это… Что такое ПЛИС?

CPLD ПЛИС Altera MAX 7128, эквивалентная 2500 вентилям

CPLD ПЛИС Altera MAX 7128, эквивалентная 2500 вентилям

Программи́руемая логи́ческая интегра́льная схе́ма (ПЛИС, англ. programmable logic device, PLD) — электронный компонент, используемый для создания цифровых интегральных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования). Для программирования используются программаторы и отладочные среды, позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или программы на специальных языках описания аппаратуры: Verilog, VHDL, AHDL и др. Альтернативой ПЛИС являются: программируемые логические контроллеры (ПЛК), базовые матричные кристаллы (БМК), требующие заводского производственного процесса для программирования; ASIC — специализированные заказные большие интегральные схемы(БИС), которые при мелкосерийном и единичном производстве существенно дороже; специализированные компьютеры, процессоры (например, цифровой сигнальный процессор) или микроконтроллеры, которые из-за программного способа реализации алгоритмов в работе медленнее ПЛИС.

Некоторые производители ПЛИС предлагают программные процессоры для своих ПЛИС, которые могут быть модифицированы под конкретную задачу, а затем встроены в ПЛИС. Тем самым обеспечивается уменьшение места на печатной плате и упрощение проектирования самой ПЛИС, за счёт быстродействия.

Некоторые сферы применения

ПЛИС широко используется для построения различных по сложности и по возможностям цифровых устройств.

Это приложения, где необходимо большое количество портов ввода-вывода (бывают ПЛИС с более чем 1000 выводов («пинов»)), цифровая обработка сигнала (ЦОС), цифровая видеоаудиоаппаратура, высокоскоростная передача данных, криптография, проектирование и прототипирование ASIC, в качестве мостов (коммутаторов) между системами с различной логикой и напряжением питания, реализация нейрочипов, моделирование квантовых вычислений.

В современных периферийных и основных компьютерных устройствах платы расширения в системе Plug and Play имеют специальную микросхему — ПЛИС, которая позволяет плате сообщать свой идентификатор и список требуемых и поддерживаемых ресурсов.

Типы ПЛИС

Ранние ПЛИС

В 1970 году компания Texas Instruments разработала маскируемые (программируемые с помощью маски, англ. mask-programmable) ИС основанные на ассоциативном ПЗУ (ROAM) фирмы IBM. Эта микросхема, TMS2000, программировалась чередованием металлических слоёв в процессе производства ИС. TMS2000 имела до 17 входов и 18 выходов с 8-ю JK-триггерами в качестве памяти. Для этих устройств компания TI ввела термин Programmable Logic Array(PLA) — программируемая логическая матрица.

PAL

Основная статья: PAL (ПЛИС)

PAL (англ. Programmable Array Logic) — программируемый массив (матрица) логики. В СССР PLA и PLM не различались и обозначились как ПЛМ. Разница между ними состоит в доступности программирования внутренней структуры (матриц) ПЛМ.

GAL

Основная статья: GAL

CPLD

Основная статья: CPLDCPLD (англ. complex programmable logic device — сложные программируемые логические устройства) содержат относительно крупные программируемые логические блоки — макроячейки, соединённые с внешними выводами и внутренними шинами. Функциональность CPLD кодируется в энергонезависимой памяти, поэтому нет необходимости их перепрограммировать при включении. Может применяться для расширения числа входов/выходов рядом с большими кристаллами, или для предобработки сигналов (например, контроллер COM-порта, USB, VGA).

FPGA

Основная статья: FPGAFPGA (англ. field-programmable gate array) содержат блоки умножения-суммирования, которые широко применяются при обработке сигналов (DSP), а также логические элементы (как правило, на базе таблиц перекодировки — таблиц истинности) и их блоки коммутации. FPGA обычно используются для обработки сигналов, имеют больше логических элементов и более гибкую архитектуру, чем CPLD. Программа для FPGA хранится в распределённой памяти, которая может быть выполнена как на основе энергозависимых ячеек статического ОЗУ (подобные микросхемы производят, например, фирмы Xilinx и Altera) — в этом случае программа не сохраняется при исчезновении электропитания микросхемы, так и на основе энергонезависимых ячеек Flash-памяти или перемычек antifuse (такие микросхемы производит фирма Actel и Lattice Semiconductor) — в этих случаях программа сохраняется при исчезновении электропитания. Если программа хранится в энергозависимой памяти, то при каждом включении питания микросхемы необходимо заново конфигурировать её при помощи начального загрузчика, который может быть встроен и в саму FPGA. Альтернативой ПЛИС FPGA являются более медленные цифровые процессоры обработки сигналов. FPGA применяются также, как ускорители универсальных процессоров в суперкомпьютерах (например: Cray — XD1, SGI — Проект RASC).

Прочие

Некоторые ведущие мировые производители ПЛИС

Основной производитель кристаллов для ПЛИС

См. также

Примечания

Ссылки

Архитектура ПЛИС (FPGA)

FPGA – это сокращение от английского словосочетания Field Programmable Gate Array.

ПЛИС – это сокращение от словосочетания «Программируемая Логическая Интегральная Схема». Слово ПЛИС встречается в русскоязычных документациях и описаниях вместо слова FPGA. Далее по тексту в основном будет использоваться этот термин — ПЛИС.

ПЛИС и FPGA – это аббревиатуры, обозначающие один и тот же класс электронных компонентов, микросхем. Это микросхемы, применяемые для создания собственной структуры цифровых интегральных схем.

Логика работы ПЛИС определяется не на фабрике изготовителем микросхемы, а путем дополнительного программирования (в полевых условиях, field-programmable) с помощью специальных средств: программаторов и программного обеспечения.

Микросхемы ПЛИС – это не микропроцессоры, в которых пользовательская программа выполняется последовательно, команда за командой. В ПЛИС реализуется именно электронная схема, состоящая из логики и триггеров.

Проект для ПЛИС может быть разработан, например, в виде принципиальной схемы. Еще существуют специальные языки описания аппаратуры типа Verilog или VHDL.

В любом случае, и графическое и текстовое описание проекта реализует цифровую электронную схему, которая в конечном счете будет «встроена» в ПЛИС.

Обычно, сама микросхема ПЛИС состоит из:

- конфигурируемых логических блоков, реализующих требуемую логическую функцию;

- программируемых электронных связей между конфигурируемыми логическими блоками;

- программируемых блоков ввода/вывода, обеспечивающих связь внешнего вывода микросхемы с внутренней логикой.

Строго говоря это не полный список. В современных ПЛИС часто бывают встроены дополнительно блоки памяти, блоки DSP или умножители, PLL и другие компоненты. Здесь, в этой статье я их рассматривать не буду.

Разработчик проекта для ПЛИС обычно абстрагируется от внутреннего устройства конкретной микросхемы. Он просто описывает желаемую логику работы «своей» будещей микросхемы в виде схемы или текста на Verilog/ VHDL. Компилятор, зная внутреннее устройство ПЛИС сам пытается разместить требуемую схему по имеющимся конфигурируемым логическим блокам и пытается соединить эти блоки с помощью имеющихся программируемых электронных связей. В общем случае размещение и трассировка связей между логическими блоками в ПЛИС остается за компилятором.

Классификация ПЛИС по типу хранения конфигурации.

SRAM-Based.

Это одна из самых распространенных разновидностей ПЛИС. Конфигурация ПЛИС хранится ячейках статической памяти, изготовленной по стандартной технологии CMOS.

Достоинство этой технологии – возможность многократного перепрограммирования ПЛИС. Недостатки – не самое высокое быстродействие, после включения питания прошивку нужно вновь загружать. Значит на плате должен еще стоять загрузчик, специальная микросхема FLASH или микроконтроллер – все это удорожает конечное изделие.

Flash-based.

В таких микросхемах хранение конфигурации происходит во внутренней FLASH памяти или памяти типа EEPROM. Такие ПЛИС лучше тем, что при выключении питания прошивка не пропадает. После подачи питания микросхема опять готова к работе. Однако, у этого типа ПЛИС есть и свои недостатки. Реализация FLASH памяти внутри CMOS микросхемы – это не очень просто. Требуется совместить два разных техпроцесса для производства таких микросхем. Значит они получаются дороже. Кроме того, такие микросхемы, как правило, имеют ограниченное количество циклов перезаписи конфигурации.

Antifuse.

Специ

Архитектура ПЛИС (FPGA)

FPGA – это сокращение от английского словосочетания Field Programmable Gate Array.

ПЛИС – это сокращение от словосочетания «Программируемая Логическая Интегральная Схема». Слово ПЛИС встречается в русскоязычных документациях и описаниях вместо слова FPGA. Далее по тексту в основном будет использоваться этот термин — ПЛИС.

ПЛИС и FPGA – это аббревиатуры, обозначающие один и тот же класс электронных компонентов, микросхем. Это микросхемы, применяемые для создания собственной структуры цифровых интегральных схем.

Логика работы ПЛИС определяется не на фабрике изготовителем микросхемы, а путем дополнительного программирования (в полевых условиях, field-programmable) с помощью специальных средств: программаторов и программного обеспечения.

Микросхемы ПЛИС – это не микропроцессоры, в которых пользовательская программа выполняется последовательно, команда за командой. В ПЛИС реализуется именно электронная схема, состоящая из логики и триггеров.

Проект для ПЛИС может быть разработан, например, в виде принципиальной схемы. Еще существуют специальные языки описания аппаратуры типа Verilog или VHDL.

В любом случае, и графическое и текстовое описание проекта реализует цифровую электронную схему, которая в конечном счете будет «встроена» в ПЛИС.

Обычно, сама микросхема ПЛИС состоит из:

- конфигурируемых логических блоков, реализующих требуемую логическую функцию;

- программируемых электронных связей между конфигурируемыми логическими блоками;

- программируемых блоков ввода/вывода, обеспечивающих связь внешнего вывода микросхемы с внутренней логикой.

Строго говоря это не полный список. В современных ПЛИС часто бывают встроены дополнительно блоки памяти, блоки DSP или умножители, PLL и другие компоненты. Здесь, в этой статье я их рассматривать не буду.

Разработчик проекта для ПЛИС обычно абстрагируется от внутреннего устройства конкретной микросхемы. Он просто описывает желаемую логику работы «своей» будещей микросхемы в виде схемы или текста на Verilog/ VHDL. Компилятор, зная внутреннее устройство ПЛИС сам пытается разместить требуемую схему по имеющимся конфигурируемым логическим блокам и пытается соединить эти блоки с помощью имеющихся программируемых электронных связей. В общем случае размещение и трассировка связей между логическими блоками в ПЛИС остается за компилятором.

Классификация ПЛИС по типу хранения конфигурации.

SRAM-Based.

Это одна из самых распространенных разновидностей ПЛИС. Конфигурация ПЛИС хранится ячейках статической памяти, изготовленной по стандартной технологии CMOS.

Достоинство этой технологии – возможность многократного перепрограммирования ПЛИС. Недостатки – не самое высокое быстродействие, после включения питания прошивку нужно вновь загружать. Значит на плате должен еще стоять загрузчик, специальная микросхема FLASH или микроконтроллер – все это удорожает конечное изделие.

Flash-based.

В таких микросхемах хранение конфигурации происходит во внутренней FLASH памяти или памяти типа EEPROM. Такие ПЛИС лучше тем, что при выключении питания прошивка не пропадает. После подачи питания микросхема опять готова к работе. Однако, у этого типа ПЛИС есть и свои недостатки. Реализация FLASH памяти внутри CMOS микросхемы – это не очень просто. Требуется совместить два разных техпроцесса для производства таких микросхем. Значит они получаются дороже. Кроме того, такие микросхемы, как правило, имеют ограниченное количество циклов перезаписи конфигурации.

Архитектура ПЛИС (FPGA)

FPGA – это сокращение от английского словосочетания Field Programmable Gate Array.

ПЛИС – это сокращение от словосочетания «Программируемая Логическая Интегральная Схема». Слово ПЛИС встречается в русскоязычных документациях и описаниях вместо слова FPGA. Далее по тексту в основном будет использоваться этот термин — ПЛИС.

ПЛИС и FPGA – это аббревиатуры, обозначающие один и тот же класс электронных компонентов, микросхем. Это микросхемы, применяемые для создания собственной структуры цифровых интегральных схем.

Логика работы ПЛИС определяется не на фабрике изготовителем микросхемы, а путем дополнительного программирования (в полевых условиях, field-programmable) с помощью специальных средств: программаторов и программного обеспечения.

Микросхемы ПЛИС – это не микропроцессоры, в которых пользовательская программа выполняется последовательно, команда за командой. В ПЛИС реализуется именно электронная схема, состоящая из логики и триггеров.

Проект для ПЛИС может быть разработан, например, в виде принципиальной схемы. Еще существуют специальные языки описания аппаратуры типа Verilog или VHDL.

В любом случае, и графическое и текстовое описание проекта реализует цифровую электронную схему, которая в конечном счете будет «встроена» в ПЛИС.

Обычно, сама микросхема ПЛИС состоит из:

- конфигурируемых логических блоков, реализующих требуемую логическую функцию;

- программируемых электронных связей между конфигурируемыми логическими блоками;

- программируемых блоков ввода/вывода, обеспечивающих связь внешнего вывода микросхемы с внутренней логикой.

Строго говоря это не полный список. В современных ПЛИС часто бывают встроены дополнительно блоки памяти, блоки DSP или умножители, PLL и другие компоненты. Здесь, в этой статье я их рассматривать не буду.

Разработчик проекта для ПЛИС обычно абстрагируется от внутреннего устройства конкретной микросхемы. Он просто описывает желаемую логику работы «своей» будещей микросхемы в виде схемы или текста на Verilog/ VHDL. Компилятор, зная внутреннее устройство ПЛИС сам пытается разместить требуемую схему по имеющимся конфигурируемым логическим блокам и пытается соединить эти блоки с помощью имеющихся программируемых электронных связей. В общем случае размещение и трассировка связей между логическими блоками в ПЛИС остается за компилятором.

Классификация ПЛИС по типу хранения конфигурации.

SRAM-Based.

Это одна из самых распространенных разновидностей ПЛИС. Конфигурация ПЛИС хранится ячейках статической памяти, изготовленной по стандартной технологии CMOS.

Достоинство этой технологии – возможность многократного перепрограммирования ПЛИС. Недостатки – не самое высокое быстродействие, после включения питания прошивку нужно вновь загружать. Значит на плате должен еще стоять загрузчик, специальная микросхема FLASH или микроконтроллер – все это удорожает конечное изделие.

Flash-based.

В таких микросхемах хранение конфигурации происходит во внутренней FLASH памяти или памяти типа EEPROM. Такие ПЛИС лучше тем, что при выключении питания прошивка не пропадает. После подачи питания микросхема опять готова к работе. Однако, у этого типа ПЛИС есть и свои недостатки. Реализация FLASH памяти внутри CMOS микросхемы – это не очень просто. Требуется совместить два разных техпроцесса для производства таких микросхем. Значит они получаются дороже. Кроме того, такие микросхемы, как правило, имеют ограниченное количество циклов перезаписи конфигурации.

Antifuse.

Специальная технология по которой выполняются однократно прогр

FPGA. Первые шаги / Хабр

В силу своей профессиональной деятельности мне приходится очень тесно работать с программированием микроконтроллеров и FPGA. Но если освоение МК более-менее подвластно даже домохозяйке, то с FPGA могут возникнуть некоторые сложности. Именно о подводных камнях и взгляде на них сверху и хотелось бы рассказать.

Шаг 0. Знакомство

Мое первое

Шаг 1. Ногодрыгалка

Ну конечно же, для программиста-железячника hello world — это поморгать светодиодами. Ведь для того, что бы отправить заветные два слова в терминал — еще надо дорасти. За основу в данном случае следует взять языки аппаратного описания: сладкую парочку Verilog и VHDL. К ним же можно добавить и возможность построения схем на примитивных логических элементах. Сразу же вспоминается институтский курс по вычислительной технике: триггеры, регистры, логические элементы, счетчики, мультиплексоры. Но не будем забегать далеко вперед, тем более что это описывалось на хабре и до меня. Оговорюсь, языки Verilog/VHDL далеко не тривиальны, даже по сравнению с ассемблером, поэтому для их понимания нужен совсем другой подход.

Шаг 2. А если посложнее?

Несмотря на своеобразие, которым языки аппаратного описания могут отпугнуть неискушенного пользователя, у них есть огромный плюс: на FPGA можно реализовать действительно очень быстродействующее устройство, а модули DSP открывают просто колоссальные возможности для цифровой обработки сигналов. Если к этому добавить еще и готовые библиотеки с уже реализованными модулями (IP Cores), то возможности становятся все более и более значительными. Однако, здесь не обошлось и без ложки дегтя — трудоемкость, или как говорится, без бутылки не разберешься.

Для воплощения в жизнь первых двух шагов подойдет связка ISE (он же Project Navigator) + ISim (симуляция) + Impact ( прошивка FPGA).

Шаг 3. Старый добрый микроконтроллер

Иногда ну просто очень хочется чего-нибудь приятного… Пожалуйста, вспомним о SoC (System-on-Chip) — системе на кристалле. В нашем случае, это процессор, шина, память и куча всякой периферии. Можно попытаться сделать самому подобную систем (см. шаг 2), можно прикрутить найденные IP Cores на просторах интернета. Но зачем же изобретать велосипед? Умными ребятами из конторы Xilinx уже придуманы софт-процессоры PicoBlaze и MicroBlaze. Первый — это восьмиразрядный процессор, который морально устарел, уже давно не внедряется в SoC и имеет открытый исходный код. Второй же, MicroBlaze, имеет неплохие перспективы: 32 разряда, RISC-архитектура и т.д, и т.п.

В качестве памяти может быть использована как внешняя память, подключаемая к FPGA, так и внутренняя, реализованная непосредственно внутри FPGA. Как правило, вторая часто применяется для кеширования инструкций и данных, находящихся в первой. Помимо того, довольно широко используются системы, содержащие более одного процессора и использующие для межпроцессорного взаимодействия специальные модули коммуникации.

Существует гигантская куча всевозможной периферии, которую можно задействовать в огромных количествах — все ограничено лишь ресурсами FPGA. Кроме того, на шину обмена с периферией PLB можно добавить и «самопальные» модули, но только при условии их корректной работы.

На данном этапе важнейшим инструментом является Xilinx Project Stuido (XPS) из состава Emedded Development Kit (EDK), по большому счету именно она на выходе позволяет получить готовый файл аппаратной конфигурации FPGA с размещенной на ней SoC.

Шаг 4. А теперь покодим

Теперь, что же касается написания программы для того же MicroBlaze. В комплекте ПО Xilinx существует Software Development Kit (SDK), позволяющий писать программы на С/С++. Да-да, вы не ослышались, С++ действительно редкость для железок, но не в нашем случае. К слову сказать, SDK у нас Eclipse-based, поэтому тут есть и content assist, и человеческий рефакторинг, и еще вагон вкусных плюшек. Не стоит забывать и про ассемблер: порой иногда вставки на асме бывают очень кстати.

В качестве компилятора используется GCC, заточенный под нужды нашего софт-процессора, возможно использование RTOS под выразительным названием XilKernel, которая, кстати, является POSIX-совместимой. Это значит, что если человек не по наслышке знаком с мьютексами, тредами и семафорами в UNIX-based системах, то разобраться в XilKernel для него не составит и труда.

Шаг 5. Вместо резюме

FPGA — это мощный и гибкий инструмент, который может позволить решить огромное количество задач. Однако, не стоит пытаться забивать гвозди микроскопом — многие задачи прекрасно решаются на тех же микроконтроллерах более дешевыми и доступными способами (Cortex M3, привет!).

Verilog, VHDL, Behavioral, Implementation — эти и многие другие слова могут свести с ума и надолго отпугнуть от разработки с использованием FPGA, однако иногда можно заменить кучу устаревшей рассыпухи с дюжиной древних МК на одну изящную микросхему и при этом получить огромное моральное удолетворение!

Первое знакомство с ПЛИС Xilinx.

РадиоКот >Обучалка >Микроконтроллеры и ПЛИС >Осваиваем ПЛИС Xilinx >Первое знакомство с ПЛИС Xilinx.

Итак, начну свое повествование о программируемой логике фирмы Xilinx, в котором постараюсь помочь начинающим с освоением этих замечательных микросхем. Начнем с самого главного — что эти микросхемы из себя представляют, и с чем их едят. Ну-с, приступим! Эта контора (Xilinx, разумеется) выпускает несколько семейств микросхем программируемой логики, предназначенных для различных целей и отличающихся между собой ценой и объемом (эквивалентным количеством логических вентилей). Микросхемы разделяются между собой на три основных группы: CPLD (CMOS Programmed Logic Device), FPGA (Field Programmed Gate Array) и конфигурационные ПЗУ для FPGA, разделенные между собой на три семейства — XC17xx, XC18xx и Platform Flash. Рассмотрим подробней что из себя представляют все эти группы и какие микросхемы в них входят.

Начнем с CPLD. Эти микросхемы отличаются наиболее простой структурой и значительными ограничениями при проектировании устройств на них, но у них есть и одно достоинство — им не нужно конфигурационное ПЗУ (что это такое — будет рассказано чуть позже). К ограничением относятся «жадность» на триггеры и недостаточная гибкость. Однако CPLD легки в освоении и, поэтому, идеально подходят для начала работы с ПЛИС вообще.

С FPGA дело обстоит несколько иначе — эти микросхемы гораздо сложнее устроены (некоторые даже содержат в себе по несколько процессорных ядер PowerPC), требуют наличия конфигурационного ПЗУ (это объясняется тем, что сами микросхемы построены по технологии Static RAM, то есть при каждом включении их нужно «загружать»), однако они способны вместить в себя гораздо более сложные и большие проекты, нежели CPLD и достаточно гибки для проектировщика (в частности снимается ограничение по количеству триггеров).

Конфигурационные ПЗУ предназначены для загрузки статической памяти FPGA. Семейство XC17xx — самое старое, представляет собой однократно программируемые микросхемы. XC18xx — EEPROM, а значит, их можно перепрограммировать многократно. Platform Flash — новое семейство конфигурационных микросхем, выполненных по технологии Flash ROM.

Архитектуру упомянутых выше микросхем мы не будем рассматривать в этой статье, потому что каждое семейство ПЛИС отличается собственной архитектурой и на это тему написано достаточно много книг, да и в даташите на любое семейство микросхем эта архитектура хорошо «разжевана». А говорить мы здесь будем непосредственно о том, как начать работать с этими замечательными микросхемами.

Итак, начнем! Для начала нам понадобится собрать программатор и установить необходимое ПО на свой компьютер. Вот схема программатора:

Как видите — все просто и никаких мудреностей ненужно. Такой программатор позволяет работать с многими типам ПЛИС и конфигурационных ПЗУ Xilinx. Теперь о софте — основной продукт для разработке устройств на ПЛИС Xilinx — это Xilinx ISE. ISE существует в нескольких вариантах, однако доступней всех — дистрибутив ISE Webpack, который можно скачать отсюда, правда для этого придется зарегистрироваться. Денег никто просить не будет, поэтому все останутся довольны и никто не будет обманут. Итак, программатор собран, ISE установлен — можно начинать!

С чего же мы начнем? Чтобы начать проектировать на ПЛИС нам нужно определиться с микросхемой, на которой мы будем проектировать. Возьмем XC95144 — это КМОП ПЛИС, с архитектурой CPLD, с 5-и вольтовым вводом-выводом, содержащая 144 макроячейки. Макроячейка — это основной кирпичик CPLD. Каждая макроячейка содержит запоминающий элемент, который может быть запрограммирован как D-триггер или как тактируемый триггер-защелка, а может быть и не использован вовсе. Отсюда и такое ограничение по триггерам (144 макроячейки=144 триггера). Микросхема XC95144 поддерживает внутрисистемное программирование — то есть ее можно перепрограммировать сколько угодно (в пределах ее ресурса, конечно!) раз, прямо на плате, на которой она используется. Еще одно важное замечание — XC95144 производится в нескольких корпусах — TQFP-100, PQFP-100 и PQFP-160, которые отличаются распиновкой и количеством выводов, доступных для программирования пользователем. Мы будем рассматривать вариант микросхемы в корпусе PQFP-160. Вот так она выглядит:

Ну что, страшно? Да ничего страшного — бывают корпуса и пострашнее!

Ну а теперь, непосредственно приступим к делу! Запускаем ISE с помощью ярлыка на рабочем столе, который был создан инсталлятором. Открывается пустое окно с двумя боковыми панелями, рядом кнопок наверху и менюшкой. Зачем это все нужно — разберемся позже — сейчас нам нужно создать проект.

Выбираем в меню File->New Project, вводим имя проекта, путь, где наш проект будет располагаться и выбираем Top->Level Source Type->Schematic. Это означает, что основной модуль нашего проекта (в иерархической системе) будет введен в виде схемы.

Щелкаем Next — перед нами появляется окно с кучей параметров нашего проекта. Поле Product Category нас сейчас мало волнует (честно говоря, вообще не пойму, как оно отражается на проекте). Family — это семейство ПЛИС, с которым мы будем работать — выбираем 9500 CPLDs. Device — непосредственно микросхема, под которую будет создаваться проект — тут выбираем угадайте что? Правильно — XC95144! Package — тип корпуса у нашей микросхемы — выбираем PQ160. Speed — скоростной параметр микросхемы (на фотке микросхемы выше обозначен как 15С в самом низу. А вообще этот параметр обозначает минимальную задержку распространения сигнала в ПЛИС «контакт-контакт» в наносекундах. То есть в указанной микросхеме такая задержка равна 15нс — таким образом можно рассчитать максимальную тактовую частоту — около 66МГц. Остальные параметры касаются синтеза (процесса перегонки нашего проекта в вид, в котором он будет расположен на кристалле) и симуляции проекта. Выбираем XST в качестве Synthesis Tool, симулятор ISE Simulator (что характерно) и Preferred Language — VHDL. VHDL — потому что этот язык гораздо «ближе» к Xilinx, нежели Verilog.

Когда мы все заполнили — самое время нажать Next и добавить «головной» файл проекта в появившемся диалоге выбираем тип Schematic и вводим имя файла, пускай это будет main.sch. Далее нажимаем еще несколько раз Next, Finish и проект создан.

Что мы видим: пустое поле, где мы будем вводить схему, две панели с вкладками и окошко с консолью снизу. Сейчас нас интересует панель, на которой присутствуют четыре вкладки — Sources, Shapshots, Libraries и Symbols. Зайдем на вкладку Symbols — остальные нас пока не интересуют. Перед нами два списка — Categories и Symbols. Догадаться не сложно — в первой у нас находится список категорий символов (арифметика, буферы и т.п.) а во второй — сами символы. При выбранной категории All Symbols — в нижнем списке отображаются все символы, которые мы можем использовать в нашем проекте. Для разных семейств ПЛИС эти списки могут отличаться.

Попробуем построить какую-нибудь схему, например счетчик, считающий до 10. Для этого выберем категорию Counter, а в ней элемент — cb4ce. Выделив этот компонент мы можем «бросить» на схему сколь угодно таких счетчиков — прекратить это можно нажатием на правую кнопку мыши (появится контекстное меню) или выбором инструмента «стрелочка» на панели вверху. Итак, кидаем на схему один такой счетчик.

Для начала разберемся с назначением его выводов:

CE — вход разрешения счета, можно повесить на него какую-нибудь логику, а можно просто подтянуть на «плюс питания» с помощью компонента Vcc из категории General, что мы и сделаем.

С — собственно счетный вход нашего счетчика, сюда будем подавать тактовый сигнал.

CLR — асинхронный сброс счетчика, счетчик находится в состоянии сброса всегда, когда на этом входе присутствует логическая «1».

Q0..Q3 — выходы счетчика, как несложно догадаться.

CEO — выход разрешения счета, его значение соответствует значению, поданному на вход CE — предназначен для каскадирования счетчиков

TC — окончание счета — при переполнении счетчика на этом выходе появляется лог. «1».

Отлично, счетчик у нас есть, но он будет считать не до 10, как нам нужно а от 0 до 15 — значит нам понадобится цепь сброса. Спроектировать ее можно так: поставить логику на выход счетчика, которая будет отлавливать число «11» на его выходе и сразу при его появлении сбрасывать счетчик. Для этих целей нам хорошо подойдет компонент and4b3 — (b3 здесь означает, что 2 входа вентиля «И» в данном случае инверсные). Но мы пойдем иным путем, и вот почему. Допустим, счетчик у нас должен считать не до 10, а, скажем до 1234, а это 11 разрядов — придется городить логику, что не есть хорошо, когда все можно сделать просто и красиво. Воспользуемся компаратором. Выбираем категорию Comparator и компонент comp4. Компаратор работает просто — при равенстве чисел, поданных на входы A[1..4] и B[1..4] он выдает логическую единицу на своем единственном выходе EQ. Подсоединим входы «А» нашего компаратора к выходам счетчика, а выход компаратора соединим с входом асинхронного сброса счетчика. Для этого на панели сверху выберем инструмент Add Wire, нажав на кнопку, на которой нарисован карандаш рисующий провод. Итак, счетчик с компаратором у нас соединены, осталось подать число «11» на вход компаратора обозначенный как «В». Можно просто подтянуть на питание и землю (c помощью компонентов vcc и gnd) входы компаратора, а можно сделать тоже самое с помощью компонента Constant из категории General. Бросим этот компонент на нашу схему. По умолчанию в него записана константа FFFF, но нам нужно записать туда число «В» в шестнадцатеричной системе счисления равное 11. Для этого два раза щелкнем мышкой на этом компоненте, чтобы отредактировать его свойства. В открывшемся окне нас интересует свойство Cvalue — туда запишем «В», причем безо всяких нулей и нажмем «ОК». После нажатия «ОК» мы видим на схеме, что значение константы равно «В», то есть 11 в десятеричной системе. И тут мы сталкиваемся с одной трудностью: входов у компаратора четыре, а выход у константы всего один! Как быть? Дело в том, что выход компонента Constant представляет собой шину, этим-то мы и воспользуемся! Выберем уже знакомый инструмент Add Wire с помощью кнопки с карандашом и «соединим» нашу константу с пустым местом на схеме — просто немного «протянем от нее провод» и закрепим его двойным щелчком рядом с компонентом. Это и будет наша шина. Чтобы можно было работать с этой шиной — ей нужно присвоить имя. Выбираем инструмент Add Net Name, кнопкой, на которой нарисован провод с буквами «ABC» и на панели, на которой всего две вкладки (на скриншотах — слева) выбираем вкладку Options, где в поле Name вводим: «count_max(3:0)»

После ввода имени шины курсор стал выглядеть как крестик с надписью «count_max(3:0)» — подведем курсор к красному квадратику с края «провода» у компонента с константой и щелкнем. Таким образом мы только что присвоили имя шине, которая подключена у нас к компоненту constant. Теперь можно с помощью этой шины подключить константу ко входу «В» компаратора. Для этого уже знакомым образом соединим входы «В» компаратора с пустым местом на схеме. И с помощью инструмента присвоения имени цепи подключим компаратор к константе таким образом:

Итак, перед нами почти завершенная схема — теперь осталось создать порты для связи с внешним миром. В этом нам поможет инструмент Add I/O Marker. Выглядит он вот так: . Просто выбираем этот инструмент, щелкаем по квадратику радом с выводом «С» нашего счетчика и тут же вход счетчика становится портом. Осталось его только переименовать в нечто удобочитаемое, скажем в «CLK». Для этого два раза щелкнем мышкой на маркер и в окне свойств введем имя «CLK». Теперь осталось сделать тоже самое с выходами счетчика. Так как они уже заняты компаратором — придется их «вытягивать» наружу, чтобы можно было подключить к ним маркеры. Протянем четыре «провода» от выходов счетчика в свободное место на схеме, прямо из середины, вот так:

Теперь можно подключить к ним маркеры и присвоить им имена, допустим такие Q0, Q1, Q2 и Q3. Когда все сделано правильно — схема должна выглядеть вот так:

Теперь проект можно сохранять и компилировать. Сохраним проект тривиальным образом, нажав кнопку с дискеткой на панели. Теперь его надо откомпилировать. Для этого на панели с четырьмя вкладками выберем Sources, а на той панели, которая с двумя вкладками выберем Processes. Под «процессами» тут подразумевается набор действий, который мы можем сделать с выбранным исходником. Для этого выбираем наш «головной» файл main.sch. Смотрим, что мы можем с ним сделать. На этом этапе нас интересует процесс Implement Design — это собственно компиляция проекта. Раскроем дерево.

Перед нами четыре этапа компиляции проекта — Synthesize — это собственно синтез проекта, разложение того, что мы только что нарисовали на элементарные части, входящие в макроячейку. Translate — перевод всего этого на язык описания аппаратуры (кстати, на нем тоже можно прекрасно проектировать, но это я оставлю для самостоятельного изучения, ибо VHDL не уместить даже в десятке подобных статей). Fit — это оптимизация нашего проекта под выбранную ПЛИСину и, наконец, Generate Programming File — это и есть генерация кода, который будет записан в ПЛИС. Щелкнем два раза по «корню» дерева — Implement Design. Начался процесс компиляции проекта — спокойно дождемся когда он закончится. Зайдем на вкладку Warnings на панели с логом компиляции внизу. Там нам сообщают, что мы не подключили выходы счетчика CEO и TC, которые нам собственно не нужны, и что также, не подключен вход счетчика CE (разрешение счета) и поэтому он установлен в «0». Это говорит о том, что счетчик работать не будет — исправим эту ошибку, подтянув этот вход к питанию, с помощью компонента Vcc.

Сохраним и заново перекомпилируем проект. Как мы видим предупреждение о неподключенном входе разрешения счета исчезло — можно продолжать. Чтобы проверить работоспособность нашего проекта — его нужно просимулировать, чем мы сейчас и займемся. В левой панели сверху мы видим список, в котором сейчас выбрано Synthesis/Implementation. Для симуляции проекта нам нужно выбрать пункт Behavioral Simulation в котором щелкнув правой кнопкой мыши по списку исходников создать новый файл в проекте. Для симуляции нам нужно задать входные параметры — это мы и сделаем с помощью добавления в проект файла типа Test Bench Waveform, который назовем counter_test.tbw.

Нам предложат выбрать элемент проекта, который мы хотим просимулировать — так как у нас в проекте всего один файл — выбираем его. Появляется окно, в котором надо указать параметры симуляции проекта.

Оставим там все как есть и нажмем Finish. Файл с данными для симуляции создан, однако на экране мы видим всего четыре тактовых импульса, чего явно недостаточно для полноценной проверки работоспособности нашего счетчика. Увеличим виртуальное время симуляции проекта щелкнув правой кнопкой на нашей свежесозданной временной диаграмме и выбрав пункт Set end of test bench. Пускай это будет 10000 nS — этого времени нам будет достаточно, чтобы увидеть как наш счетчик досчитает до 10 и сбросится. Сохраним наш файл с временной диаграммой и посмотрим, что можно с ним сделать во вкладке Processes (как это сделать, надеюсь, запомнили?) Помимо предложений создать новый исходник и просмотреть то, что мы только что натворили в виде VHDL нам предлагают просимулировать наш проект, что мы сейчас и сделаем. Раскрываем «дерево» Xilinx ISE Simulator и запускаем процесс Simulate Behavioral Model. Итак, в панели с логом побежали сообщения, комп задумался и выдал нам временную диаграмму симуляции нашего проекта. И о чудо! Счетчик действительно считает до 10-и!

Ну что же, проект создан, проверен на работоспособность — неплохо бы его и в ПЛИСину зашить? Ну тогда приступим к подготовительным мероприятиям. Задумайся, читатель — у нашей микросхемы XC95144 аж целых 160 ног, а в нашем проекте использованы только 5, к каким же ногам подключать осциллограф и куда подавать тактовые импульсы? В этом нам поможет утилита PACE, которую можно найти в меню Пуск->Программы->Xilinx ISE 9.2i->Accessories. Запустим эту программу. Перед нами открылось пустое окно — нужно создать новый файл распиновки. Выбираем в меню пункт File->New и перед нами появляется окно для создания нового файла. В поле New Constrains (UCF) file укажем путь, где будет располагаться наш файл с распиновкой. Самым правильным будет создать его в директории проекта и назвать так же, как головной модуль проекта. В поле Input Design File необходимо указать файл с данными о компиляции проекта (с расширением .ngd) и в третьем поле, с помощью кнопки Select Part выбрать семейство (9500 CPLDs), микросхему (XC95144), корпус (PQ160) и скоростную способность (-15) микросхемы. Завершающим этапом создания нового файла будет нажатие кнопки ОК. Итак, перед нами окно в котором мы видим схематическое изображение корпуса ПЛИСины, и список сигналов нашего проекта (на нижней панели слева). Как мы видим, на схематичном изображении корпуса микросхемы выводы помечены разными цветами. Выводы помеченные красным, светло-зеленым и фиолетовым это питание ядра, земля и питание выходных буферов соответственно. Желтые выводы — это выводы JTAG, предназначенные для программирования микросхемы — именно их нужно подключать к программатору. Еще видны выводы, обведенные красным, черным и синим цветами — это GSR (Global Set/Reset), который можно использовать для установки или сброса всех триггеров в проекте (для этого достаточно их назначить), GTS (Global Tri-State) — для перевода всех буферов ПЛИС в «третье» состояние и GCK (Global Clock) — для подачи тактового сигнала. Пусть наш тактовый сигнал будет подключен к GCK1 (33-я нога ПЛИС), остальные сигналы нашего проекта можно расположить произвольно. Однако для определенности пусть они будут подключены к выводам 11,12,13 и 14 по возрастанию. Если все сделано правильно — должно получиться вот так:

Теперь нужно сохранить наш файл и вернуться в ISE, чтобы добавить его в проект. Только чтобы его добавить нужно вернуться в список исходников Synthesis/Implementation. После добавления файла с распиновкой можно закрыть PACE и перекомпилировать проект. Для верности — можно заглянуть в раздел Pin List отчета, который создается после каждой перекомпиляции проекта.

На этом этапе проект готов — можно делать макетную плату с ПЛИСиной и тактовым генератором и проверять проект на «живом железе», но это я, пожалуй, оставлю для самостоятельной работы. Скажу лишь то, что для программирования ПЛИС предназначена утилита iMPACT, запустить которую можно прямо из ISE. Много материалов по программированию доступно на сайте Xilinx, поэтому повторяться не буду.

Вопросы, как обычно, складываем тут.

|

Как вам эта статья? |

Заработало ли это устройство у вас? |

Эти статьи вам тоже могут пригодиться:

пли — Викисловарь

албанский [править]

Этимология 1 [править]

От протоалбанского * plitś (i) — , от протоиндоевропейского * (s) pel- (t-) («отколоть, отколоть, отколоться»). [1] В качестве альтернативы от протоалбанского * plitja , снова родственного санскриту 000 (phálati, «лопнуть, расколотый»), латинский spolium («раздетая кожа»). [2]

Альтернативные формы [править]

Существительное [править]

plis m ( неопределенное множественное число plisa , определенное единственное число plisi , определенное множественное число plisat )

- ком (земли), ком

- кожа сумка, пачка

Синонимы [править]

Производные термины [править]

Этимология 2 [править]

От протоалбанского * p (i) litja , родственный древне-немецкому filz , латинский pellis , греческий πςλος (pῖlos), протославянский * pьlstь . [3]

Существительное [править]

plis m ( неопределенное множественное число plisa , определенное единственное число plisi , определенное множественное число plisat )

- шерстяной войлок

- войлочная тюбетейка

- фетровая прокладка, помещенная под хомут или вьючное седло, для защиты шеи тягловых животных

Производные термины [править]

Список литературы [править]

- ^ Demiraj, Bardhyl (1997). , Амстердам, Атланта: Родопи, стр. 326

- ^ Орел, Владимир (2000) Краткая историческая грамматика албанского языка , Лейден: Брилл, стр. 155

- ^ Орел, Владимир (1998), «плис», в Албанский этимологический словарь , Лейден, Бостон, Кельн: Брилл, стр. 335

Существительное [править]

плиз м

- множественное число пли

Анаграммы [править]

гаитянский креольский [править]

Этимология [править]

с французского плюс («больше»)

определитель [править]

плиз

- более

См. Также [править]

Этимология [править]

Родственный Baldemu Pilish , который ищет больше родственных.

Существительное [править]

плиз

- лошадь

Список литературы [править]

- Zygmunt Frajzyngier, Erin Shay, Грамматика Hdi (2002, → ISBN

- Темы в чадской лингвистике 3 , том 3 (2007), стр. 71

Маврикийский креольский [править]

Произношение [редактировать]

Этимология 1 [править]

с французского плюс .

Существительное [править]

плиз

- плюс

- добавление

- выгода, преимущество

Связанные условия [править]

Этимология 2 [править]

с французского éplucher .

Глагол [править]

плиз

- Медиальная форма Плиз ; очищать.

Tok Pisin [редактировать]

Этимология [править]

С английского , пожалуйста, .

Междометие [править]

плиз

- пожалуйста

Что означает PLI?

PLI Pali

Региональные »Языковые коды (3 буквы)

Оценить:

PLI Академический юридическийПрактика

Практика юриспруденции Университеты — и многое другое …

Оценить:

PLI Язык программирования Интерфейс

Вычисления »Общие вычисления

Оцените:

PLI Институт пастырского лидерства

Сообщество »Религия

Оценить:

Компании и Фирмы 900 15 Оценить:

PLI Личные линии Страхование

Бизнес »Страхование

Оценить:

0

15 Информация о местоположении Правительственные »Военные

Оцените это:

PLI Государственные земли и учреждения

Правительственные» Институты

0 Оцените:

PLI Институт родительского лидерства

Сообщество »Обучающие»

Оцените:

PLI 9000ry Светлые шары Пейнтбол

Оценить:

PLI Юридические расследования в Тихоокеанском регионе

Бизнес »Компании и фирмы

PLI Peripheral Land, Inc.

Бизнес »Компании и Фирмы

Оценить:

PLI Pro-language Institute

Академические и научные науки» Университеты

Оцените:

PLI Иммунореактивность поджелудочной липазы

Разное »Не классифицировано

Все еще не найдены Бизнес »Маркетинг

Оценить:

PLI Потенциальный любовный интерес

Разное» Несекретные

PLI Палм-Айленд, Наветренные острова

Региональные »Коды аэропортов

Оценить:

PLI Уязвимость пересылки через Интернет

Ур.

Оценить:

PLI Индикатор ограничения высоты тона

Разное »Авиация и авиация

Страхование ответственности за качество продукции

Бизнес »Общий бизнес

Оценить:

PLI Программирование Logique Индуктивный

0 Разное» Разное 4

Оценить:

PLI Главный институт лидерства

Правительственные »Институты

Юридический институт-практик Правительственные »Институты

Оцените это:

PLI Практикующий юридический институт

Правительственные» Институты

0

0 Оцените:

,

PLI Prêt Locatif Intermédiaire

Разное »Не классифицировано

Оценить:

plis — перевод — Гаитянско-английский словарь

ht и его авангард, посвященный английскому языку, два десятилетия 1996 года, посвященные языкам 1996 года.

newswire-hten ru Получи свет!

newswire-hten ru Получи свет! ht Apre sa, li bay plis esplikasyon sou verite fondamantal sa a, li fè konnen mó yo pa ka ni renmen, ni rayi, li li fè konnen “pa gen ni travay, ni pwojè, ni konesans, ni sajès [тонн нан] ».

jw2019 ru Наркоман любит свою иголку? — Хммм

jw2019 ru Наркоман любит свою иголку? — Хммм ht Anpil nan moun ki te vin kwayan yo te soti byen lwen e y a pa he genze or me you pou you te pase plis tan Jerizalèm.

jw2019 ru давай. не будь таким. я плачу вам комплимент

jw2019 ru давай. не будь таким. я плачу вам комплимент ht Nou ankouraje w pou w chcheche konneen ki lang etranje moun yo plis бледный Nan Téritwa Pa W La.

jw2019 ru Удерживающий зазор # m x # mm i.д. подключен к CP-WAX # CB столбец # mx # mm id

jw2019 ru Удерживающий зазор # m x # mm i.д. подключен к CP-WAX # CB столбец # mx # mm id ht 3 toujou negatif 1/6 egal a 2 fwa 1 plis 6.

QED ru Происхождение и статус программы государственного сектора

QED ru Происхождение и статус программы государственного сектора ht Okenn fréch negosiyasyon te pwograme grév la plizan pli kriyèl pa dezyèm pli gwo peyi a inyon te kont kareè pakè nasyon Доминиканская империя в возрасте до 12 лет. йо те травай аплен загар.

newswire-hten ru У меня уже есть заказы

newswire-hten ru У меня уже есть заказы ht 14 Ki jan n ka pran plis plezi nan aktivite teyokratik yo?

jw2019 ru Но сделайте это правильно, и у вас есть достаточно мощный магнит … чтобы стереть любой магнитный носитель, который вам удастся приблизить к

jw2019 ru Но сделайте это правильно, и у вас есть достаточно мощный магнит … чтобы стереть любой магнитный носитель, который вам удастся приблизить к ht 2 300 ланг.

jw2019 ru О, почему бы вам, ах, почему у вас нет акцента?

jw2019 ru О, почему бы вам, ах, почему у вас нет акцента? ht Ki jan n ap rive konnen kalite Jewova yo plis toujou?

jw2019 ru В этой дискуссии больше не будет вопросов синей карточки.У нас нет времени.

jw2019 ru В этой дискуссии больше не будет вопросов синей карточки.У нас нет времени. ht Pou w jwenn plis enfòmasyon sou depresyon, gade Volim 1 an, chapit 13.

jw2019 ru Кошки Кандии?

jw2019 ru Кошки Кандии? ht Kidonk, nou menm ansyen nou renmen anpil yo, toutpandan n ap bay fmamason se pou n montre no plis pase yon senp anseyan, nou dwe montre no se se yon zanmi tou. — Пво.

jw2019 ru Эти конфискованные писем … говорят о убийстве короля

jw2019 ru Эти конфискованные писем … говорят о убийстве короля ht 13 Но ты не должен быть, ты живешь, как ты любишь.

jw2019 ru Полагаю, нам нужно быть немного хитрее в том, как мы опередили железнодорожные пути, да?

jw2019 ru Полагаю, нам нужно быть немного хитрее в том, как мы опередили железнодорожные пути, да? ht N ap pale plis sou sa nan leson 11 Наименование: «Бледный взгляд на аве сантимана».

jw2019 ru О, нет, ты должен поесть перед операцией

jw2019 ru О, нет, ты должен поесть перед операцией ht Poukisa Jezi te bay kåmandman pou gen plis ouvriye?

jw2019 ru Я не мог сдержать свои негативные мысли и чувства к ней

jw2019 ru Я не мог сдержать свои негативные мысли и чувства к ней ht Ки джан фейсон йе трете Тимутон Пак ла фин н вин плиз конфенсан нп шофеси йо?

jw2019 ru Бессилен, чтобы остановить неизбежное

jw2019 ru Бессилен, чтобы остановить неизбежное ht 65 Мужчин, лет и дней назад, Плис Пас, Кенз-Милдола-Котизасйон Нэн Мен Окенн Моун.

LDS ru Если нет, то что намеревается сделать Комиссия, чтобы устранить этот тип нетарифного барьера и гарантировать доступ на китайский рынок на справедливых условиях?

LDS ru Если нет, то что намеревается сделать Комиссия, чтобы устранить этот тип нетарифного барьера и гарантировать доступ на китайский рынок на справедливых условиях? ht Pou plis enfòmasyon, gade chapit 12 ak chapit 19 liv sa a, Ki sa Labib anseye toutbonvre?

jw2019 ru «Река течет в веселой пустыне …», чтобы встретить океан

jw2019 ru «Река течет в веселой пустыне …», чтобы встретить океан ht Se yon priyè ki gen anpil sans, e lè nou konsidere twa premye demann ki ladan l yo, sa pral ede nou aprann plis toujou sou sa Labib anseye toutbonvre.

jw2019 ru Ничто так не заставляет вас чувствовать себя более мощным

jw2019 ru Ничто так не заставляет вас чувствовать себя более мощным ht Donk, nou bezwen gen plis pase sa.

jw2019 ru затем это были те, кто отрезал свои товары

jw2019 ru затем это были те, кто отрезал свои товары ht Olye w panse w konn meyè fason pou w montre konsiderasyon pou konjwen w, poukisa w pa mande l ki sa li ta pis renmen w f ?

jw2019 ru Я тоже буду с вами откровенен. Позвоните ему, уйдет

jw2019 ru Я тоже буду с вами откровенен. Позвоните ему, уйдет ht GEN plis pase santan depi istwa modèn Temwen Jewova yo kòmanse.

jw2019 ru Я перезвоню вам

jw2019 ru Я перезвоню вам ht 22 Toutotan ane yo ap pase, maryaj la ap pote plis satakainaksyon toujou.

jw2019 ru Во-первых, озабоченность на уровне национального правительства разнообразием форм собственности все больше фокусируется на вертикальных и перекрестных концентрациях среды (они будут определены в следующем разделе).

jw2019 ru Во-первых, озабоченность на уровне национального правительства разнообразием форм собственности все больше фокусируется на вертикальных и перекрестных концентрациях среды (они будут определены в следующем разделе). ht Ekwasyon liy sa se poutèt y egal moins 3 x plis 2. mx plis b.

QED ru Я уделил мне время для того синего, светлого и квадратного

QED ru Я уделил мне время для того синего, светлого и квадратного ht Anfèt, nan fen mwa sa a, me te peze plis pase kèlkeswa epòk nan lavi m.

jw2019 ru КР будет следить за тем, чтобы не дублировать какие-либо инициативы, инициированные Комиссией в этой области.

jw2019 ru КР будет следить за тем, чтобы не дублировать какие-либо инициативы, инициированные Комиссией в этой области. ht Теперь вы должны готовиться к встрече с другими людьми ».

jw2019 ru У него нет ощущения, что он родился.

jw2019 ru У него нет ощущения, что он родился.определение плиссе по Свободный словарь

ПЕРЕДНЯЯ ЗАДНЯЯ ЧАСТЬ ПЕРВАЯ ASOS DESIGN: наденьте этот кроп-топ с сеткой добби с рукавом блузона, одетыми или спущенными, PS25, www.asos.com PS13.99, www.shein.co.uk РОЗОВЫЙ ПЕЧАТНЫЙ РУЧКА NECK PLISSE TOP: Kick Начните лето с выбора смелых, тропических принтов и ярких дизайнов. Это также оставило место для кропотливых рубашек темно-синего и оранжевого плисса ручной работы, чтобы творить свое волшебство. Navabi; Сандалии на лямках с ремешком от Danielle, PS35, Marks & Spencer. Наряды либо красиво подогнаны, либо восхитительно драпированы, а у плиссированных шелков есть приятные приливы и отливы.8 Широкие брюки с плиссированным принтом черного цвета, River Island. Плиссированный лиф или плиссированная подкладка для всех, у кого есть грудь, как у Евгении, никогда не окажет вам никакой пользы. Читайте: «Плисс с защипом вырезан в предвзятости и смешанных с фирменными шторами. В письме добавлено: «Мы не можем закрыться — мы маэстро Плиссе». У владельцев не было ответа от правительства. Западная джинсовая куртка с вышивкой PS39, белое платье с бахромой PS49 , вся одежда от Miss Selfridge Украшенное многоуровневое макси-платье PS95 Слева: золотой металлик PS20, шорты с пуговицами для PS30, красные кроссовки PS22; справа: бахрома с шейным вырезом (миниатюрная) PS22, джинсовая юбка с боковыми полосками PS32, над ней слоган с надписью PS3.50, высокие бахромы PS32 Справа: белый бандо PS5, сумка с поясом с шипами PS18, мини-юбка с пайетками PS25; Слева: праздничное тело для блесток PS35, задняя сумка на молнии PS18, укороченные брюки plisse PS28, юбка с кисточками PS20, юбка с кисточками PS30 Слева: бюстгальтер с красной вышивкой PS32, подходящая мини-юбка PS45, стеганая сумка на пояс PS18; Справа: галстук спереди сверху PS18, вышитые шорты PS22A quelques километров Мекнеса; Организация Объединенных Наций мобилизует все силы и заботы о депрессии и депрессии. Мой атлас плиссирует партию [изобилует моими руками], бесчеловечны и безрассудно настроены [изящная музыка плюс великая королева].ДЖЕММА АРТЕРТОН, 32 года. Великолепная красавица с легкостью сняла свое платье от Alberta Ferretti. ,.