Что представляет собой плисовая ткань. Какие существуют виды плиса. Какими свойствами обладает плис. Как ухаживать за изделиями из плиса. Где применяется плисовая ткань в современном мире.

Что такое плис и история его появления

Плис — это ворсовая хлопчатобумажная ткань, внешне напоминающая бархат. Название «плис» происходит от шведского слова «plys», что в переводе означает «плюш». Эта ткань известна еще с XVII века и изначально использовалась как более дешевый аналог дорогого бархата.

История плиса началась в Европе, где его впервые начали производить. В России плисовая ткань появилась в XVIII веке. Плис быстро обрел популярность среди мелкого дворянства и зажиточных крестьян, которые не могли позволить себе настоящий бархат, но хотели выглядеть модно и богато.

Интересный факт: упоминания о плисе можно найти в произведениях русских классиков. Например, в «Барышне-крестьянке» А.С. Пушкина фигурирует плисовая куртка, а в «Мертвых душах» Н.В. Гоголя описывается обувь из плиса у знатной дамы.

Особенности и состав плисовой ткани

Плис представляет собой ворсовую ткань, в основе которой лежит хлопчатобумажное полотно. Основные особенности плиса:

- Короткий стриженый ворс, который длиннее, чем у бархата

- Полотняное или саржевое плетение основы

- Основа из хлопка, реже используется шерсть

- Относится к уточно-ворсовым тканям

- Ворс образуется петлями утка, которые затем состригаются и прочесываются

Технология производства плиса заключается в следующем: хлопчатобумажная основа переплетается с утком, образующим петли. Затем эти петли состригаются и прочесываются, формируя ворс. Такая технология обеспечивает прочное закрепление ворса в структуре ткани.

Разновидности плисовой ткани

Существует несколько основных видов плиса, которые различаются по составу и назначению:

Бивер

Бивер — это плотная и прочная разновидность плиса. Его особенности:

- Основа из полиэфирной нити

- Высокая прочность и стойкость к загрязнениям

- Используется для пошива рабочей одежды

- Как правило, имеет темные или яркие сигнальные оттенки

Вельвет (вельветин)

Вельвет — это разновидность плиса с характерными продольными рубчиками. Его отличия:

- Наличие продольных рубчиков на поверхности

- Изначально использовался для пошива штор

- Сейчас широко применяется для одежды и обуви

Мебельный плис

Мебельный плис предназначен специально для обивки мебели. Его характеристики:

- Повышенная прочность и износостойкость

- Уток из шерсти

- Очень плотное плетение основы

- Устойчивость к истиранию и выцветанию

Свойства плисовой ткани

Плис обладает рядом важных свойств, которые определяют области его применения:

- Мягкость и приятная на ощупь текстура

- Прочность и износостойкость

- Устойчивость к образованию складок

- Хорошие теплоизоляционные свойства

- Способность «дышать» при правильном уходе

- Склонность к накоплению пыли из-за ворсистой поверхности

Важное преимущество плиса — его устойчивость к образованию складок. Это свойство делает плис удобным материалом для одежды, так как вещи из него практически не нуждаются в глажке.

Правила ухода за изделиями из плиса

Чтобы изделия из плиса долго сохраняли свой внешний вид, необходимо соблюдать ряд правил по уходу:

- Стирать плисовые вещи следует вручную или в деликатном режиме стиральной машины при температуре не выше 30°C.

- Использовать мягкие моющие средства без отбеливателей.

- Не выкручивать и не отжимать изделия — лучше дать воде стечь естественным путем.

- Сушить в расправленном виде вдали от прямых солнечных лучей и источников тепла.

- После стирки ворс может «прилечь» — его нужно расчесать мягкой щеткой или отпарить.

- Гладить плисовые вещи не рекомендуется, но при необходимости можно отпарить с изнаночной стороны.

Важно помнить, что плис чувствителен к воде и высоким температурам. После контакта с водой ворс может «прилечь» к основе, создавая эффект «прилизанности». Чтобы восстановить фактуру ткани, необходимо расчесать ворс мягкой щеткой или применить отпаривание.

Современное применение плисовой ткани

Несмотря на то, что плис известен уже несколько столетий, он не теряет своей актуальности и в наши дни. Основные сферы применения плиса в современном мире:

Одежда

Плис используется для пошива различных предметов одежды:

- Верхняя одежда (куртки, пальто)

- Брюки и юбки

- Платья и сарафаны

- Головные уборы

Обувь

Плисовая обувь популярна благодаря своей мягкости и комфорту. Из плиса часто изготавливают:

- Домашние тапочки

- Мокасины

- Зимние ботинки (в качестве подкладки)

Мебель и интерьер

В интерьере плис находит широкое применение:

- Обивка мягкой мебели

- Декоративные подушки

- Шторы и портьеры

- Покрывала и пледы

Аксессуары

Из плиса изготавливают различные аксессуары:

- Сумки и клатчи

- Перчатки

- Шарфы и палантины

Плис в современной моде

Плис периодически возвращается на подиумы в коллекциях известных дизайнеров. Его ценят за:

- Богатый внешний вид, напоминающий бархат

- Комфорт при носке

- Широкую цветовую палитру

- Возможность создания интересных фактур и узоров

Современные технологии позволяют создавать плис с различными эффектами: тиснением, принтами, вышивкой. Это делает материал еще более привлекательным для модельеров и дизайнеров интерьера.

Преимущества и недостатки плиса

Как и любой материал, плис имеет свои сильные и слабые стороны. Рассмотрим основные преимущества и недостатки плисовой ткани:

Преимущества плиса:

- Прочность и долговечность при правильном уходе

- Приятная на ощупь текстура

- Хорошие теплоизоляционные свойства

- Устойчивость к образованию складок

- Богатый внешний вид, напоминающий бархат

- Относительно доступная цена по сравнению с натуральным бархатом

Недостатки плиса:

- Склонность к накоплению пыли из-за ворсистой поверхности

- Требует деликатного ухода

- Может терять форму после стирки, если не соблюдать правила ухода

- Не подходит для жаркого климата из-за плохой воздухопроницаемости

При выборе изделий из плиса важно учитывать эти особенности и соотносить их с вашими потребностями и образом жизни.

Экологичность плисовой ткани

В современном мире все больше внимания уделяется экологичности материалов. Как же обстоят дела с плисом?

- Плис на основе натурального хлопка считается относительно экологичным материалом

- Синтетические разновидности плиса менее экологичны, но более долговечны

- Производство плиса требует меньше ресурсов, чем производство натурального бархата

- Некоторые производители используют переработанные материалы для создания экологичного плиса

При выборе плисовых изделий обращайте внимание на состав ткани и репутацию производителя в отношении экологических стандартов. Это поможет сделать более осознанный и экологичный выбор.

Заключение

Плис — это уникальная ткань, сочетающая в себе богатый внешний вид, практичность и относительную доступность. Несмотря на свою многовековую историю, плис не теряет актуальности и находит применение в самых разных сферах: от модной одежды до интерьерного дизайна.

Благодаря своим свойствам — прочности, мягкости, теплоизоляции — плис остается популярным выбором для многих потребителей. При этом важно помнить о правильном уходе за плисовыми изделиями, чтобы они долго сохраняли свой привлекательный внешний вид.

Современные технологии позволяют создавать новые вариации плиса, делая его еще более привлекательным для дизайнеров и потребителей. Будь то классический плис для элегантного пальто или инновационный экологичный плис для современной мебели — этот материал продолжает удивлять своей универсальностью и адаптивностью к меняющимся трендам.

Плис — что за ткань?

Что такое плис и с чем его носить

«Дешевый бархат», «бумажный бархат» — как только не называли плис за века его использования. Ткань приобрела популярность еще в семнадцатом веке, когда мелкое дворянство и зажиточные крестьяне начали шить из него одежду. Именно такая целевая аудитория поясняется доступной стоимостью плиса и его схожестью с дорогостоящим бархатом. Следовательно, его выбирали любители шика, которые не могли позволить себе натуральный бархат. В России эта ткань появилась веком позже, а изначально плис производили только в Европе. Упоминание о плисовой ткани можно найти даже в литературных произведениях российских классиков: в пушкинской «Барышне-крестьянке» упоминается плисовая куртка, а в гоголевских «Мертвых душах» у знатной дамы была обувь из плиса. В определенных сферах плис не теряет популярности и в наши дни.

Что собой представляет плисовая ткань

Само слово «плис» пришло к нам из шведского языка, хотя, с французского это слово переводится как «плюш».

Для создания основы применяется полотняное или саржевое плетение. Плюс такой технологии в том, что петли ворса будут очень прочно держаться в плетении и не начнут сыпаться даже после многократных стирок. Но это же плетение очень затрудняет пошив плисовых изделий. Поэтому мелкие и сложные детали из плиса обычно не делают. Ну и, конечно, сам ворс является прекрасным пылесборником, как любая подобная ткань.

Виды плиса и их спецификация

Самые распространенные разновидности плиса на данный момент это:

- бивер;

- вельветин;

- мебельный плис.

Бивер сделан на основе полиэфирной нити, которая отличается прочностью и стойкостью к загрязнениям. Не трудно догадаться, что ткань с такими параметрами (кстати, бивер еще и очень дешевый) используется для пошива рабочей одежды. Поэтому, если вы зададитесь целью купить себе отрез бивера, он, скорее всего, будет или очень темным, или наоборот, максимально яркого сигнального оттенка (как в форменной одежде работников ГАИ, ЖКХ и т.д). Впервые эта ткань появилась на ткацких фабриках Манчестера.

Вельвет (он же вельветин) мало отличается от самого плиса. Основное отличие – продольные рубчики, выстриженные на ткани. Изначально эту ткань использовали для пошива штор. В данный момент, нас окружает большое количество одежды и обуви с использованием вельвета.

Мебельный плис отличается своей прочностью и стойкостью к повреждениям. Уток плетется из шерсти, для основы подбирается максимально плотное плетение. Благодаря этим параметрам мебель, обшитая плисом, не протирается и не линяет достаточно долго, и может пережить несколько аккуратных чисток.

Свойства плиса и правила ухода

Изначально плис выпускали только однотонным, для одежды, обуви. Позднее, из плиса начали изготавливать шикарные гобелены, которые можно назвать настоящим произведением искусства. Сегодня узорчатый плис чаще всего используется для отделки мебели.

Для пошива изделий из плисовой ткани практически нет никаких особенных правил (за исключением вельвета, в котором следует избегать швов, повторяющих полосы на самой ткани). Самое главное, это тщательно и аккуратно отделать края, чтобы впоследствии они не начали рассыпаться.

Сейчас плис производят на многих ткацких фабриках в России и по всей Европе. Качество ткани из разных регионов мало отличается, поэтому особого значения фирма-производитель не имеет.

Одно из самых главных преимуществ – устойчивость к складкам. Да-да, плис практически не мнется, гладить его не нужно. Этот нюанс особенно важен для одежды из плиса, уход за которой не доставит вам особенных хлопот. Но не стоит забывать, что плис довольно чувствителен к стирке. Как уже было сказано, ворсинки он не теряет, однако, после контакта с водой ворс «склоняется» к основе. То есть, ткань выглядит «прилизанной». Этот эффект можно устранить только прочесав ткань мягкой щеточкой или отпарив ее.

Плисовая обувь

Обувь из плиса, как правило, домашняя. Она отличается мягкостью, дает возможность отдохнуть с комфортом и без каких-либо неудобств. Протирается или рвется она довольно редко, что дает ей явное преимущество.

Что и как носить

Плисовые ткани подойдут далеко не к любому гардеробу. Но, поверьте, оригинальность и красота такой одежды стоят того, чтобы немного поработать над своим образом.

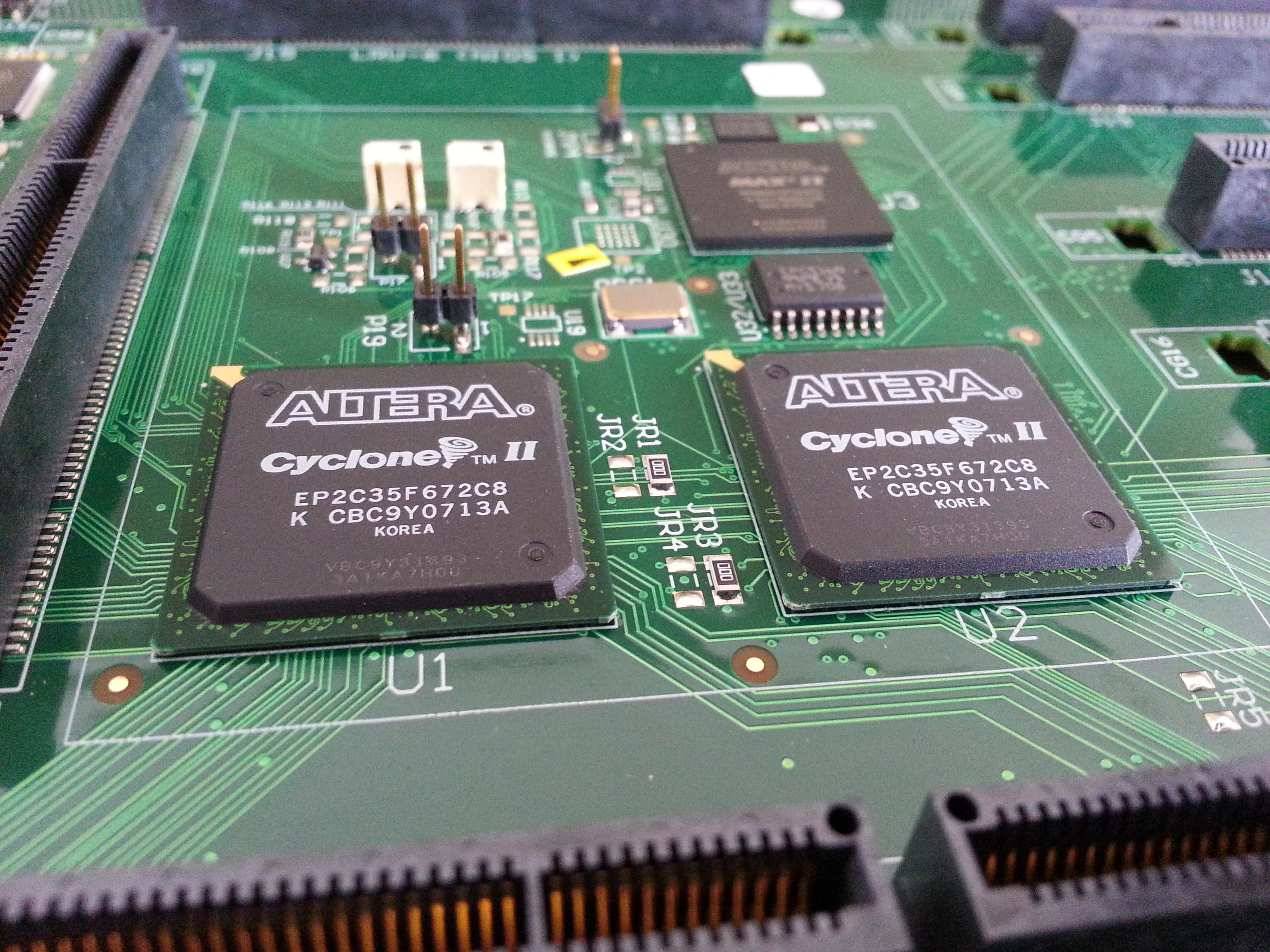

FPGA. Разбираемся, как устроены программируемые логические схемы и чем они хороши

Содержание статьи

Представь, что процессор вместо того, чтобы выполнять набор инструкций, будет перестраиваться под каждую программу и превращать алгоритм непосредственно в «железо». Именно так и работают FPGA! В этой статье я расскажу, как такое возможно, и познакомлю тебя с разными способами проектирования FPGA.

Может быть, ты умеешь взламывать устройства на другом конце света или кодить крутые веб-приложения, но понимаешь ли ты, как работает твой компьютер? И речь не о том, что делает операционка, как функционирует garbage collector в Java или как устроен компилятор C++. Я говорю о самом низком, аппаратном уровне, ниже ассемблера: как работает железо.

Что происходит в микросхеме сетевой карты, когда приходит пакет Ethernet? Как этот пакет передается дальше в оперативную память компьютера через шину PCI Express? Как работают самые быстрые системы распознавания изображений на аппаратном уровне?

Для ответа на эти вопросы надо немного разбираться в цифровой логике работы микросхем ASIC, но начинать с них очень сложно и дорого, и вместо этого лучше начать с FPGA.

INFO

FPGA расшифровывается как field-programmable gate array, по-русски — программируемые пользователем вентильные матрицы, ППВМ. В более общем случае они называются ПЛИС — программируемые логические интегральные схемы.

С помощью FPGA можно в буквальном смысле проектировать цифровые микросхемы, сидя у себя дома с доступной отладочной платой на столе и софтом разработчика за пару килобаксов. Впрочем, есть и бесплатные варианты. Заметь: именно проектировать, а не программировать, потому что на выходе получается физическая цифровая схема, выполняющая определенный алгоритм на аппаратном уровне, а не программа для процессора.

Работает это примерно так. Есть готовая печатная плата с набором интерфейсов, которые подключены к установленной на плате микросхеме FPGA, вроде крутой платы для дата-центра или отладочной платы для обучения.

Пока мы не сконфигурируем FPGA, внутри микросхемы просто нет логики для обработки данных с интерфейсов, и потому работать ничего, очевидно, не будет. Но в результате проектирования будет создана прошивка, которая после загрузки в FPGA создаст нужную нам цифровую схему. Например, так можно создать контроллер 100G Ethernet, который будет принимать и обрабатывать сетевые пакеты.

Важная особенность FPGA — возможность реконфигурации. Сегодня нам нужен контроллер 100G Ethernet, а завтра эта же плата может быть использована для реализации независимых четырех интерфейсов 25G Ethernet.

Существуют два крупных производителя FPGA-чипов: Xilinx и Intel, которые контролируют 58 и 42% рынка соответственно. Основатели Xilinx изобрели первый чип FPGA в далеком 1985 году. Intel пришла на рынок недавно — в 2015 году, поглотив компанию Altera, которая была основана в то же время, что и Xilinx. Технологии Xilinx и Altera во многом схожи, как и среды разработки. Чаще я работал с продуктами компании Xilinx, поэтому не удивляйся ее постоянному упоминанию.

FPGA широко применяются в разных устройствах: потребительской электронике, оборудовании телекома, платах-ускорителях для применения в дата-центрах, различной робототехнике, а также при прототипировании микросхем ASIC. Пару примеров я разберу чуть ниже.

Также рассмотрим технологию, которая обеспечивает аппаратную реконфигурацию, познакомимся с процессом проектирования и разберем простой пример реализации аппаратного счетчика на языке Verilog. Если у тебя есть любая отладочная плата FPGA, ты сможешь повторить это самостоятельно. Если платы нет, то все равно сможешь познакомиться с Verilog, смоделировав работу схемы на своем компе.

Принцип работы

Микросхема FPGA — это та же заказная микросхема ASIC, состоящая из таких же транзисторов, из которых собираются триггеры, регистры, мультиплексоры и другие логические элементы для обычных схем. Изменить порядок соединения этих транзисторов, конечно, нельзя. Но архитектурно микросхема построена таким хитрым образом, что можно изменять коммутацию сигналов между более крупными блоками: их называют CLB — программируемые логические блоки.

Также можно изменять логическую функцию, которую выполняет CLB. Достигается это за счет того, что вся микросхема пронизана ячейками конфигурационной памяти Static RAM. Каждый бит этой памяти либо управляет каким-то ключом коммутации сигналов, либо является частью таблицы истинности логической функции, которую реализует CLB.

Так как конфигурационная память построена по технологии Static RAM, то, во-первых, при включении питания FPGA микросхему обязательно надо сконфигурировать, а во-вторых, микросхему можно реконфигурировать практически бесконечное количество раз.

Очень упрощенная 2D-структура микросхемы без конфигурационной памятиБлоки CLB находятся в коммутационной матрице, которая задает соединения входов и выходов блоков CLB.

Схема коммутационной матрицыНа каждом пересечении проводников находится шесть переключающих ключей, управляемых своими ячейками конфигурационной памяти. Открывая одни и закрывая другие, можно обеспечить разную коммутацию сигналов между CLB.

CLBCLB очень упрощенно состоит из блока, задающего булеву функцию от нескольких аргументов (она называется таблицей соответствия — Look Up Table, LUT) и триггера (flip-flop, FF). В современных FPGA LUT имеет шесть входов, но на рисунке для простоты показаны три. Выход LUT подается на выход CLB либо асинхронно (напрямую), либо синхронно (через триггер FF, работающий на системной тактовой частоте).3 = 8 значений. Каждое из них соответствует своей комбинации входных сигналов. Эти значения вычисляются программой для разработки прошивки ПЛИС и записываются в специальные ячейки конфигурационной памяти.

Значение каждой из ячеек подается на свой вход выходного мультиплексора LUT, а входные аргументы булевой функции используются для выбора того или иного значения функции. CLB — важнейший аппаратный ресурс FPGA. Количество CLB в современных кристаллах FPGA может быть разным и зависит от типа и емкости кристалла. У Xilinx есть кристаллы с количеством CLB в пределах примерно от четырех тысяч до трех миллионов.

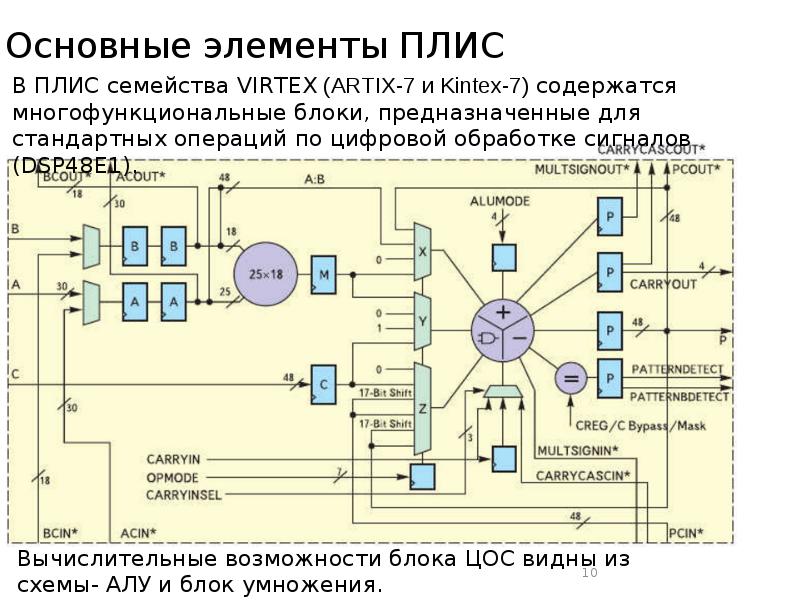

Помимо CLB, внутри FPGA есть еще ряд важных аппаратных ресурсов. Например, аппаратные блоки умножения с накоплением или блоки DSP. Каждый из них может делать операции умножения и сложения 18-битных чисел каждый такт. В топовых кристаллах количество блоков DSP может превышать 6000.

Другой ресурс — это блоки внутренней памяти (Block RAM, BRAM). Каждый блок может хранить 2 Кбайт. Полная емкость такой памяти в зависимости от кристалла может достигать от 20 Кбайт до 20 Мбайт. Как и CLB, BRAM и DSP-блоки связаны коммутационной матрицей и пронизывают весь кристалл. Связывая блоки CLB, DSP и BRAM, можно получать весьма эффективные схемы обработки данных.

Применение и преимущества FPGA

Первый чип FPGA, созданный Xilinx в 1985 году, содержал всего 64 CLB. В то время интеграция транзисторов на микросхемах была намного ниже, чем сейчас, и в цифровых устройствах часто использовались микросхемы «рассыпной логики». Были отдельно микросхемы регистров, счетчиков, мультиплексоров, умножителей. Под конкретное устройство создавалась своя печатная плата, на которой устанавливались эти микросхемы низкой интеграции.

Использование FPGA позволило отказаться от такого подхода. Даже FPGA на 64 CLB значительно экономит место на печатной плате, а доступность реконфигурации добавила возможность обновлять функциональность устройств уже после изготовления во время эксплуатации, как говорят «in the field» (отсюда и название — field-programmable gate array).

За счет того, что внутри FPGA можно создать любую аппаратную цифровую схему (главное, чтобы хватило ресурсов), одно из важных применений ПЛИС — это прототипирование микросхем ASIC.

Разработка ASIC очень сложна и затратна, цена ошибки очень высока, и вопрос тестирования логики критичен. Поэтому одним из этапов разработки еще до начала работы над физической топологией схемы стало ее прототипирование на одном или нескольких кристаллах FPGA.

Для разработки ASIC выпускают специальные платы, содержащие много FPGA, соединенных между собой. Прототип микросхемы работает на значительно меньших частотах (может быть, десятки мегагерц), но позволяет сэкономить на выявлении проблем и багов.

Однако, на мой взгляд, существуют более интересные применения ПЛИС. Гибкая структура FPGA позволяет реализовывать аппаратные схемы для высокоскоростной и параллельной обработки данных с возможностью изменить алгоритм.

Сравнение аппаратных платформДавай подумаем, чем принципиально отличаются CPU, GPU, FPGA и ASIC. CPU универсален, на нем можно запустить любой алгоритм, он наиболее гибок, и использовать его легче всего благодаря огромному количеству языков программирования и сред разработки.

При этом из-за универсальности и последовательного выполнения инструкций CPU снижается производительность и повышается энергопотребление схемы. Происходит это потому, что на каждую полезную арифметическую операцию CPU совершает много дополнительных операций, связанных с чтением инструкций, перемещением данных между регистрами и кешем, и другие телодвижения.

На другой стороне находится ASIC. На этой платформе требуемый алгоритм реализуется аппаратно за счет прямого соединения транзисторов, все операции связаны только с выполнением алгоритма и нет никакой возможности изменить его. Отсюда максимальная производительность и наименьшее энергопотребление платформы. А вот перепрограммировать ASIC невозможно.

Справа от CPU находится GPU. Изначально эти микросхемы были разработаны для обработки графики, но сейчас используются и для майнинга вычислений общего назначения. Они состоят из тысяч небольших вычислительных ядер и выполняют параллельные операции над массивом данных.

Если алгоритм можно распараллелить, то на GPU получится добиться значительного ускорения по сравнению с CPU. С другой стороны, последовательные алгоритмы будут реализовываться хуже, поэтому платформа оказывается менее гибкой, чем CPU. Также для разработки под GPU надо иметь специальные навыки, знать OpenCL или CUDA.

Наконец, FPGA. Эта платформа сочетает эффективность ASIC с возможностью менять программу. ПЛИС не универсальны, но существует класс алгоритмов и задач, которые на них будут показывать лучшую производительность, чем на CPU и даже GPU. Сложность разработки под FPGA выше, однако новые средства разработки делают этот разрыв меньше.

Решающее же преимущество FPGA — это способность обрабатывать данные в темпе их поступления с минимальной задержкой реакции. В качестве примера можешь вообразить умный сетевой маршрутизатор с большим количеством портов: при поступлении пакета Ethernet на один из его портов необходимо проверить множество правил, прежде чем выбрать выходной порт. Возможно, потребуется изменение некоторых полей пакета или добавление новых.

Использование FPGA позволяет решать эту задачу мгновенно: байты пакета еще только начали поступать в микросхему из сетевого интерфейса, а его заголовок уже анализируется. Использование процессоров тут может существенно замедлить скорость обработки сетевого трафика. Ясно, что для маршрутизаторов можно сделать заказную микросхему ASIC, которая будет работать наиболее эффективно, но что, если правила обработки пакетов должны меняться? Достичь требуемой гибкости в сочетании с высокой производительностью поможет только FPGA.

Таким образом, FPGA используются там, где нужна высокая производительность обработки данных, наименьшее время реакции, а также низкое энергопотребление.

FPGA in the cloud

В облачных вычислениях FPGA применяются для быстрого счета, ускорения сетевого трафика и осуществления доступа к массивам данных. Сюда же можно отнести использование FPGA для высокочастотной торговли на биржах. В серверы вставляются платы FPGA с PCI Express и оптическим сетевым интерфейсом производства Intel (Altera) или Xilinx.

На FPGA отлично ложатся криптографические алгоритмы, сравнение последовательностей ДНК и научные задачи вроде молекулярной динамики. В Microsoft давно используют FPGA для ускорения поискового сервиса Bing, а также для организации Software Defined Networking внутри облака Azure.

Бум машинного обучения тоже не обошел стороной FPGA. Компании Xilinx и Intel предлагают средства на основе FPGA для работы с глубокими нейросетями. Они позволяют получать прошивки FPGA, которые реализуют ту или иную сеть напрямую из фреймворков вроде Caffe и TensorFlow.

Причем это все можно попробовать, не выходя из дома и используя облачные сервисы. Например, в Amazon можно арендовать виртуальную машину с доступом к плате FPGA и любым средствам разработки, в том числе и machine learning.

FPGA on the edge

Что еще интересное делают на FPGA? Да чего только не делают! Робототехника, беспилотные автомобили, дроны, научные приборы, медицинская техника, пользовательские мобильные устройства, умные камеры видеонаблюдения и так далее.

Традиционно FPGA применялись для цифровой обработки одномерных сигналов (и конкурировали с процессорами DSP) в устройствах радиолокации, приемопередатчиках радиосигналов. С ростом интеграции микросхем и увеличением производительности платформы FPGA стали все больше применяться для высокопроизводительных вычислений, например для обработки двумерных сигналов «на краю облака» (edge computing).

Эту концепцию легче всего понять на примере видеокамеры для анализа автомобильного трафика с функцией распознавания номеров машин. Можно взять камеру с возможностью передачи видео через Ethernet и обрабатывать поток на удаленном сервере. С ростом числа камер будет расти и нагрузка на сеть, что может привести к сбоям системы.

Вместо этого лучше реализовать распознавание номеров на вычислителе, установленном прямо в корпус видеокамеры, и передавать в облако номера машин в формате текста. Для этого даже можно взять сравнительно недорогие FPGA с низким энергопотреблением, чтобы обойтись аккумулятором. При этом остается возможность изменять логику работы FPGA, например, при изменении стандарта автомобильных номеров.

Что до робототехники и дронов, то в этой сфере как раз особенно важно выполнять два условия — высокая производительность и низкое энергопотребление. Платформа FPGA подходит как нельзя лучше и может использоваться, в частности, для создания полетных контроллеров для беспилотников. Уже сейчас делают БПЛА, которые могут принимать решения на лету.

Как разрабатывать проект на FPGA?

Существуют разные уровни проектирования: низкий, блочный и высокий. Низкий уровень предполагает использование языков типа Verilog или VHDL, на которых ты управляешь разработкой на уровне регистровых передач (RTL — register transfer level). В этом случае ты формируешь регистры, как в процессоре, и определяешь логические функции, изменяющие данные между ними.

Схемы FPGA всегда работают на определенных тактовых частотах (обычно 100–300 МГц), и на уровне RTL ты определяешь поведение схемы с точностью до такта системной частоты. Эта кропотливая работа приводит к созданию максимально эффективных схем с точки зрения производительности, потребления ресурсов кристалла FPGA и энергопотребления. Но тут требуются серьезные скиллы в схемотехнике, да и с ними процесс небыстрый.

На блочном уровне ты занимаешься в основном соединением уже готовых крупных блоков, которые выполняют определенные функции, для получения нужной тебе функциональности системы на кристалле (system-on-chip).

На высоком уровне проектирования ты уже не будешь контролировать данные на каждом такте, вместо этого сконцентрируешься на алгоритме. Существуют компиляторы или трансляторы с языков C и C++ на уровень RTL, например Vivado HLS. Он довольно умный и позволяет транслировать на аппаратный уровень широкий класс алгоритмов.

Главное преимущество такого подхода перед языками RTL — ускорение разработки и особенно тестирования алгоритма: код на C++ можно запустить и верифицировать на компьютере, и это будет намного быстрее, чем тестировать изменения алгоритма на уровне RTL. За удобство, конечно, придется заплатить — схема может получиться не такой быстрой и займет больше аппаратных ресурсов.

Часто мы готовы платить эту цену: если грамотно использовать транслятор, то эффективность не сильно пострадает, а ресурсов в современных FPGA достаточно. В нашем мире с критичным показателем time to market это оказывается оправданным.

Часто в одном дизайне нужно совместить все три стиля разработки. Допустим, нам нужно сделать устройство, которое мы могли бы встроить в робота и наделить его способностью распознавать объекты в видеопотоке — например, дорожные знаки. Возьмем микросхему видеосенсора и подключим ее напрямую к FPGA. Для отладки можем использовать монитор HDMI, тоже подключенный к FPGA.

Кадры с камеры будут передаваться в FPGA по интерфейсу, который заведомо определен производителем сенсора (USB тут не катит), обрабатываться и выводиться на монитор. Для обработки кадров понадобится фреймбуфер, который обычно находится во внешней памяти DDR, установленной на печатной плате рядом с микросхемой FPGA.

Типичная блок-схема проекта FPGAЕсли производитель видеосенсора не предоставляет Interface IP для нашей микросхемы FPGA, то нам придется писать его самостоятельно на языке RTL, считая такты, биты и байты в соответствии со спецификацией протокола передачи данных. Блоки Preprocess, DDR Controller и HDMI IP мы, скорее всего, возьмем готовые и просто соединим их интерфейсы. А блок HLS, который выполняет поиск и обработку поступающих данных, мы можем написать на C++ и транслировать при помощи Vivado HLS.

Скорее всего, нам еще потребуется какая-то готовая библиотека детектора и классификатора дорожных знаков, адаптированная для использования в FPGA. В этом примере я, конечно, привожу сильно упрощенную блок-схему дизайна, но логику работы она отражает корректно.

Рассмотрим путь проектирования от написания кода RTL до получения конфигурационного файла для загрузки в FPGA.

Путь проектированияИтак, ты пишешь код RTL, который реализует нужную тебе схему. Прежде чем его проверять на реальном железе, надо убедиться, что он верный и корректно решает требуемую задачу. Для этого используется RTL-моделирование в симуляторе на компьютере.

Ты берешь свою схему, представленную пока только в коде RTL, и помещаешь ее на виртуальный стенд, где подаешь последовательности цифровых сигналов на входы схемы, регистрируешь выходные диаграммы, зависимости от времени выходных сигналов и сравниваешь с ожидаемыми результатами. Обычно ты находишь ошибки и возвращаешься к написанию RTL.

Далее логически верифицированный код подается на вход программе-синтезатору. Она преобразует текстовое описание схемы в связанный список цифровых элементов из библиотеки, доступной для данного кристалла FPGA. В этом списке будут отображены такие элементы, как LUT, триггеры, и связи между ними. На этой стадии элементы пока никак не привязаны к конкретным аппаратным ресурсам. Чтобы это сделать, требуется наложить на схему ограничения (Constraints) — в частности, указать, с какими физическими контактами ввода-вывода микросхемы FPGA связаны логические входы и выходы твоей схемы.

В этих ограничениях также требуется указать, на каких тактовых частотах должна работать схема. Выход синтезатора и файл ограничений отдаются процессору Implementation, который, помимо прочего, занимается размещением и трассировкой (Place and Route).

Процесс Place каждый пока еще обезличенный элемент из netlist привязывает к конкретному элементу внутри микросхемы FPGA. Далее начинает работу процесс Route, который пытается найти оптимальное соединение этих элементов для соответствующей конфигурации коммутационной матрицы ПЛИС.

Place и Route действуют, исходя из ограничений, наложенных нами на схему: контактами ввода-вывода и тактовой частотой. Период тактовой частоты очень сильно влияет на Implementation: он не должен быть меньше, чем временная задержка на логических элементах в критической цепи между двумя последовательными триггерами.

Часто сразу удовлетворить это требование не удается, и тогда надо вернуться на начальный этап и изменить код RTL: например, попытаться сократить логику в критической цепи. После успешного завершения Implementation нам известно, какие элементы где находятся и как они связаны.

Только после этого запускается процесс создания бинарного файла прошивки FPGA. Остается его загрузить в реальное железо и проверить, работает ли оно так, как ожидалось. Если на этом этапе возникают проблемы, значит, моделирование было неполным и на этом этапе не были устранены все ошибки и недочеты.

Можно вернуться на стадию симуляции и смоделировать нештатную ситуацию, а если и это не сработает, на крайний случай предусмотрен механизм отладки непосредственно в работающем железе. Ты можешь указать, какие сигналы хочешь отслеживать во времени, и среда разработки сгенерирует дополнительную схему логического анализатора, которая размещается на кристалле рядом с твоей разрабатываемой схемой, подключается к интересующим тебя сигналам и сохраняет их значения во времени. Сохраненные временные диаграммы нужных сигналов можно выгрузить на компьютер и проанализировать.

Существуют и высокоуровневые средства разработки (HLS, High-level synthesis), и даже готовые фреймворки для создания нейросетей в ПЛИС. Эти средства на выходе генерят код RTL на языках VHDL или Verilog, который дальше спускается по цепочке Synthesis → Implementation → Bitstream generation. Ими вполне можно пользоваться, но, чтобы использовать их эффективно, надо иметь хотя бы минимальное представление о языках уровня RTL.

Продолжение следует

Надеюсь, теория тебя не слишком загрузила! В следующей статье я расскажу о практике: мы посмотрим, что конкретно нужно делать, чтобы запрограммировать FPGA.

Что такое ПЛИС и с чего начать изучение FPGA Altera

С чего начать изучение FPGA Altera?

Что такое ПЛИС?

Современные ПЛИС – программируемые логические микросхемы, выполняемые по технологии от 10 нм и содержащие большое количество логических элементов. Элементы могут выполнять простые логические операции «И», «ИЛИ» и др. или реализовывать функции умножителей, сумматоров, мультиплексоров и более сложных устройств.

FPGA – это микросхемы, в которых производителем не определены связи между логическими элементами. Разработчику необходимо самому определять взаимосвязи, назначение выводов и пути прохождения сигналов. В этом заключается большой плюс ПЛИС, так как следствием такого подхода становятся исключительно гибкая архитектура и быстродействие полученной электронной схемы. Но за это приходится платить увеличенным временем разработки устройства.

Как определить срок хранения и срой службы импортных микросхем?

По этим причинам ПЛИС нашли широкое применение в радиоэлектронной аппаратуре, устройствах высокоскоростной параллельной обработки сигналов, микропроцессорной технике.С чего начать?

К большому сожалению, литературы на русском языке, описывающей принципы функционирования, программирования FPGA практически нет. Нет и чёткого понимания, даже у специалистов, когда применять ПЛИС, а когда программируемый микроконтроллер в повседневных задачах (не связанных с управлением космическими аппаратами или опасным промышленным производством).Начать нужно с главного вопроса – какие задачи вы планируете решать с использованием FPGA?

Если вы разрабатываете шину передачи данных для своего устройства или конструируете плату обработки сигналов с разложением в ряд Фурье, то ПЛИС — это то, что необходимо. Прекрасным решением является и построение отказоустойчивых систем с быстрым временем реакции на основе ПЛИС в системах автоматики.

Это лишь некоторые примеры, позволяющие оценить мощь и гибкость FPGA. Поэтому главными критериями при выборе определим быстродействие и оригинальную архитектуру, ради которых стоит пойти на дополнительные трудозатраты.

Что означают сокращения PCN, EOL, NRND в data sheet импортных электронных компонентов?

Приняв по тем или иным причинам твёрдое решение освоить ПЛИС, встают следующие вопросы – с чего начать и насколько это затратно?По поводу денежных затрат – микросхемы начального уровня, средства программирования и отладки ненамного дороже микроконтроллеров. Освоение сред разработки и языков программирования нисколько не сложнее тех же МК. Всё вышесказанное относится к продукции компании Altera, которую и рассмотрим более детально.

Средства разработки и отладки

Возникает справедливый вопрос: а как же проектировать и отлаживать такой «зоопарк» различных серий и их версий? Altera позаботилась об этом, создав единую среду проектирования и отладки Quartus.К достоинствам продукта относятся:

- Возможность создания проекта на языках VHDL, Verilog или в графическом редакторе.

- Ведение всей фоновой работы по созданию конфигурационного файла ПЛИС, включая разводку в кристалле.

- Загрузка конфигурационного файла в ПЛИС и внутрисхемная отладка.

Для загрузки и отладки проектов в микросхемах поставляются программаторы в двух исполнениях – для LPT и USB портов.

Начало работы с FPGA Altera

Оптимальным для работы с продуктами Altera будет следующий алгоритм действий:1. Чётко сформулировать задачу, для решения которой предполагается использование ПЛИС

- Определите необходимое количество входов/выходов

- Уровень напряжения

- Перечень логических операций

- Допустимую задержку прохождения сигнала от входа на выход

- Другие параметры, критичные при выполнении задачи.

Ознакомиться с документацией на ПЛИС, скачав руководство с сайта производителя.

3. Скачать по этой ссылке и установить среду разработки Quartus.

Для продуктов Quartus Prime Lite Edition, Quartus II Web Edition, ModelSlim-Intel FPGA Starter Edition лицензия не требуется. Бесплатной версии вполне хватит для ознакомления со средой. Изучить среду разработки, пользуясь встроенной справкой и документацией на сайте Altera.

4. Приобрести ПЛИС Altera и программатор с параллельным или usb-портом.

5. Разработать и отладить проект своего устройства на ПЛИС.

Собрать электрическую схему, загрузить проект в микросхему, проверить полученный результат. При необходимости внести изменения в проект, воспользоваться возможностями внутрисхемной отладки.

Заявка на поставку импортных ПЛИС Altera

Кроме этого, мы выполняем полный комплекс услуг по организации проверки и испытаниям электронных компонентов импортного производства, включая входной контроль, проверку на работоспособность, а также специальные проверки, механические и климатические испытания.

Если вы заинтересованы в работы с нами, то заполните форму по ссылке: www.el-ra.ru/zayavka

IP-ядра для проектирования ПЛИС и ИС

IP-ядра — сложные функциональные блоки для ускорения разработки ПЛИС или ИС

Предлагаем разработчикам RTL-кода для ПЛИС (FPGA) или ИС (интегральных микросхем) воспользоваться библиотекой готовых IP-ядер (сложных функциональных блоков, IP-core) от компании SmartDV — одного из лидеров рынка — для проектирования или верификации современных интерфейсов в составе вашего проекта ПЛИС или ИС.

Ассортимент IP-блоков варьируется от IP для проектирования и проверки, IP для формальной проверки (утверждения), IP для проверки в кремнии, и до портфолио синтезируемых моделей преобразователей (трансакторов) для ускорения тестирования на системном уровне, тестирования систем на кристалле (SoC) на аппаратных эмуляторах или прототипирующих платформах ПЛИС (FPGA). Запатентованная технология, основанная на автоматической компиляции, обеспечивает быструю поставку IP-блоков, соответствующих спецификациям стандартных протоколов, для новых или развивающихся сетевых интерфейсов, систем хранения, автомобильных стандартов, шин обмена данными, протоколов MIPI, видео, а также аэрокосмических приложений. В результате компания SmartDV часто поставляет первые на рынке решения для проектирования и проверки, практически одновременно с появлением нового отраслевого стандарта протокола.

IP-ядра интерфейсов для проектирования ПЛИС и ИС

Мы разрабатываем IP-блоки для проектирования ПЛИС и ИС (FPGA и ASIC), используя наш богатый опыт проектирования ASIC / SoC и возможности Verilog и VHDL. Наши IP-блоки — это конфигурируемые и многократно используемые решения plug-and-play для стандартных интерфейсов на основе Verilog и VHDL. Все наши IP-блоки имеют расширенную конфигурацию и интерфейс отчетов о состоянии. Все IP-блоки проверяются с использованием наших верификационных IP-ядер, которые использовались нашими клиентами для производства множества ASIC. Также каждый из IP-блоков тестируется на платформе FPGA. Мы используем средства автоматизации для написания IP-блоков, поэтому время на разработку любого нового IP-блока может быть очень коротким. Если вам нужен какой-либо IP-блок, которого нет в списке ниже, сообщите нам об этом. Мы можем разработать его для вас очень быстро.

Даташит и стоимость конкретных IP-блоков высылается по запросу.

Примечание: Наши интерфейсные IP-блоки проверены и на ASIC, и на FPGA.

Память DDR Controller, DMA Controller, Flash Controller

LPDDR, LPDDR2, LPDDR3, LPDDR4, LPDDR5, LPDDR5X,

DDR, DDR2, DDR3, DDR3L, DDR4, DDR5,

HBM2, HBM2E, HBM3, GDDR2, GDDR3, GDDR3L, GDDR4, GDDR5, GDDR5X, GDDR6,

DFI LPDDR5 PHY, TS5 Master, TS5 Slave,

DMA Controller with AHB, DMA Controller with AXI, DMA Controller with OCP, DMA Controller with TileLink,

Serial Flash, XSPI, OCTAL SPI Master, QUAD SPI MASTER,

SDIO Host, SDIO Device, eMMC Host, eMMC Device

Скоростные интерфейсы Ethernet, PCIe, RapidIO, CXL

Ethernet 1G MAC, 10G, 25G, 40G, 50G, 100G, 200G, 400G, 800G,

1G TSN, 10G TSN, 25G TSN, 40/100G TSN, 200/400G TSN,

1G PCS, 10G XAUI PCS, 10G KR PCS, 25G PCS,

AFDX 1G, Switch, EtherCAT 1G, EtherCAT 10G, eCPRI Controller,

PCIE Controller,

RAPIDIO EndPoint Controller,

CXL Controller

Последовательные интерфейсы

IEC7816 Slave, I2C Slave, PCI Master Slave, SPI Slave, MIL STD 1553 Controller,

PMBUS Master Controller, PMBUS Slave,

SMBUS Master, SMBUS Slave, AVSBUS Master, AVSBUS Slave,

IEEE 1149.7 COMPACT TAP, IEEE 1149.7 DTS ADAPTER,

eSPI Controller, eSPI MASTER, eSPI SLAVE, eSPI SLAVE SOC, JESD207 RFIC,

JESD207 BBIC, I2C Master, LPC HOST, LPC DEVICE, eSPI LPC BRIDGE,

UART Controller, GPIO Controller, Virtual GPIO, Timer, INTC, RTC, Watchdog Timer

Аудио/видео

I2S Master Controller, AC97 Controller,

VBYONE Transmitter, V-By-One Receiver,

VESA DSC Decoder, VESA DSC Encoder,

VDC-M Decoder, VDC-M Encoder, HDCP 2.x Transmitter,

HDCP 2.x Receiver,

HDMI CEC, CXP DEVICE, CXP HOST, SLVS-EC Transmitter, SLVS-EC Receiver,

HDMI eARC Transmitter, HDMI eARC Receiver,

DISPLAY PORT Receiver, DISPLAY PORT Transmitter,

eDP Receiver, eDP Transmitter,

HDMI SINK, HDMI SOURCE,

SMPTE SDI Transmitter, SMPTE SDI Receiver

MIPI (Mobile Industry Processor Interface)

MIPI RFFE Slave, RFFE Master, SPMI Slave, ASPMI Slave, SPMI Master, BIF Slave, BIF Master, RFFE SPI Slave, RFFE SPI I2C Slave, DSI-2 Transmitter, DSI-2 Receiver, CSI-2 Transmitter, CSI-2 Receiver, I3C Master, I3C Slave, STP Master, UNIPRO

Автомобильные интерфейсы

LIN Controller,

CAN Controller,

FLEXRAY Controller,

SAE J2716 Sensor, SAE J2716 Device, SAE J1850,

JESD204B Transmitter, JESD204B Receiver,

JESD204C Transmitter, JESD204C Receiver,

AVB MAC,

IEEE 1588

Мосты

Tilelink To APB Bridge, Tilelink To AHB Bridge,

I2C Slave To AHB Bridge, I2C Slave To AXI Bridge,

MIPI I3C Slave To AHB Bridge, MIPI I3C Slave To AXI Bridge,

SPI Slave To AHB Bridge, SPI Slave To AXI Bridge,

AHB To APB Bridge, AHB Multilayer Interconnect, AHB Arbiter, AHB Decoder

IP-ядра для верификации (VIP)

Мы разрабатываем блоки для проверки интерфейсных IP, используя наш богатый опыт в проверке проектирования ASIC / SoC и возможностей языков проверки высокого уровня (HVL). Наши верификационные IP-ядра — это настраиваемые, многократно используемые решения plug-and-play для стандартных интерфейсов, на основе HVL. В настоящее время мы поддерживаем SystemVerilog, Vera, SystemC, Specman E и Verilog. Все наши VIP-блоки изначально поддерживаются в SystemVerilog VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E и в нестандартных средах проверки.

Все наши IP-блоки поставляются с расширенными командами, конфигурациями и интерфейсом отчетов о состоянии. Их очень просто использовать и отлаживать. Мы используем средства автоматизации для разработки верификационных IP-ядер, поэтому время для разработки нового верификационного IP-ядра очень короткое. Если вам нужен проверочный IP-блок для стандарта, которого нет в списке ниже, сообщите нам об этом. Мы можем разработать его для вас очень быстро.

Более 100 клиентов — ведущих мировых разработчиков проектов ПЛИС и ИС — используют наши верификационные IP-ядра. Большинство ведущих полупроводниковых компаний являются нашими клиентами.

Даташит и стоимость конкретных VIP-блоков высылается по запросу.

Скоростные интерфейсы VIP

AMBA, Avalon, AVCI (Advanced VCI), BVCI (Basic VCI),

CPRI, OBSAI, eCPRI, RoE, ORAN,

Ethernet — up to 800G, MII/SMII/RMII/GMII/RGMII, SGMII/1000Base-KX,

GMII TBI (8b/10b) Ethernet,

2.5GBase-KX/5GBase-KR/2.5GBase-T/5GBase-T, XGMII Ethernet,

10GBase-KR Ethernet, 10G 64b/66b WIS Ethernet, 10G XAUI/10GBase-KX4 Ethernet, 10G TBI (PCS) Ethernet, 25GBase-R/KR,

XLGMII 40G Ethernet, 40GBase-KR4/CR4/SR4/LR4/KR2, 50GBase-KR/KR2,

CGMII 100G Ethernet, 100GBase-KR10/CR10/SR10/LR4, 200GBase-KR8/KR4/KR2,

400GBase-KR4/KR8/KR16,

Ethernet 1G, Ethernet 10G, Ethernet 25G,50G, Ethernet 40G,100G,

Ethernet 200G,400G, 800G Ethernet, Ethernet AVB, Ethernet TSN,

100BASE-T1, RoCE, Ethercat, G.999.1, Interlaken, AMBA LPI, OCP,

PVCI (Peripheral VCI),

RapidIO, SDIO 8.0, SDIO UHS II, SD Express, TileLink,

USB 4.0, USB 3.0/3.1/3.2/SSIC, USB 1.0/1.1/2.0, USB PD, USB TYPE-C, eUSB, QI, OpenCores Wishbone B3

Автомобильные и последовательные интерфейсы VIP

ARINC 419, ARINC 429, ARINC 825, AVSBus, BISS,

CAN, CJTAG IEEE 1149.7, DALI, DMX, FlexRay, GCI, I2C, IPMB,

SMBus, PMBus, XMBus, TS5, SVID, SWD, I2S, IEC61162,

SmartCard (IEC7816), JESD204, JESD207,

JTAG IEEE 1149.1/1149.6, LIN, LPC, LVDS,

Microwire, Microsecond Channel (MSC),

MIL STD 1553, MIL STD 1773, NFC, SENT (SAE J2716), SAE J1850,

Safe-By-Wire Plus, SDI,

SIMCARD, SpaceWire, SpaceFibre,

SPI (Serial Peripheral Interface), SPI (Serial Peripheral Interface) Flash,

SPI/BOSCH, SPI/EEPROM, SPI/FRAM, SPI/MACRONIX, SPI/MOTOROLA, SPI/RTC, SPI/SERIAL FLASH, SPI/SPANSION FLASH, SPI/ST MEMS,

Serial Flash, SSI (Synchronous Serial Interface),

xSPI (Expanded Serial Peripheral Interface),

eSPI (Enhanced Serial Peripheral Interface), QSPI (Quad Serial Peripheral Interface), Octal SPI (Serial Peripheral Interface), SafeSPI, SPIStack, UART

Мониторы памяти VIP

DDR2 Monitor, DDR3 Monitor

Системы хранения данных, видео и аудио VIP

Fibre Channel, PCI Express, MPCIE, NVMe,

PCI, OpenCAPI, CCIX 1.0, GENZ, SAS, SATA, CXL, SRIOV, Compact Flash,

Serial Front Panel Data Port (SFPDP), FCoE,

Display Port, Display Port 2.0, Embedded Display Port, eMMC,

HDMI 1.4/2.0/2.1, MHL, MPEG2TS, SMPTE Serial Data Interface (SDI),

SPDIF (IEC60958), VBYONE,

Даташит и стоимость конкретных IP-блоков высылается по запросу.ARINC 818, TDM, PDM, CoaXPress (CXP),

Camera Link HS, Camera Parallel Interface (CPI), Trusted Platform Module (TPM),

SLVS-EC, Open LVDS Display Interface (OpenLDI), UFS

MIPI (Mobile Industry Processor Interface) VIP

BIF, DBI, DigRF, DPI, HSI, HTI, I3C, LLI, MPHY, DPHY, CPHY, APHY, RFFE, SLIMBUS, CSI-2, CSI-3, DSI, DSI-2, GbD USB, SoundWire, SoundWire I3S, SPMI, STP, UniPro, SPP, VGI

Модели памяти

Наши модели памяти разработаны с использованием богатого опыта в проверке конструкций ASIC / SoC и возможностей языков проверки высокого уровня (HVL). Наши модели памяти — это настраиваемые, многократно используемые решения проверки plug-and-play для стандартных интерфейсов на основе HVL. В настоящее время мы поддерживаем SystemVerilog, Vera, SystemC, Specman E и Verilog. Все наши модели памяти изначально поддерживаются в SystemVerilog VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E и нестандартной среде проверки.

Все модели памяти поставляются с расширенными командами, конфигурациями и интерфейсом отчетов о состоянии. Их очень просто использовать и отлаживать. Мы используем средства автоматизации для написания моделей памяти, поэтому время для разработки любой новой модели памяти очень короткое. Если вам нужна какая-либо модель памяти, которая не указана ниже, сообщите нам об этом. Мы можем разработать ее для вас очень быстро.

Даташит и стоимость конкретных моделей высылается по запросу.

Модели DDR SDRAM

DDR, DDR2, DDR3 3DS, DDR3, DDR3L, DDR4 3DS, DDR4, DDR5

Модели памяти Low Power

LPDDR, LPDDR2, LPDDR3, LPDDR4, LPDDR5, LPDDR5X, LPSDR

Модели графической памяти

GDDR2, GDDR3, GDDR3L, GDDR4, GDDR5, GDDR5X, GDDR6, GDDR7, MDRAM, VRAM, SGRAM

Модели флэш-памяти

Open Nand Flash Interface (ONFI), Toggle Flash, NAND Flash, Parallel NOR Flash, Serial NOR Flash, SLC NAND, SPI NAND Flash, Xccela Flash, Twin Quad NOR Flash, Wide Range VCC Flash

Модели памяти High Bandwidth

HBM, HBM2E, HBM3, GHBM

Модели SDRAM и SRAM

EDORAM, FCRAM, HMC, RLDRAM, RLDRAM2, RLDRAM3, SDRAM, WIDE IO, WIDE IO2, QDR2, QDR4, SBSRAM, SRAM, SSRAM

Модели Non-Volatile memory и DIMM DDR

DDR5 NVRAM, MRAM, nvSRAM, RERAM,

DDR3 DIMM, DDR4 DIMM, DDR4 3DS DIMM, DDR5 DIMM, DDR4DB, DDR4 RCD, NVDIMM-P

Вспомогательные модели

External Memory Interface (EMIF), FPMRAM, FRAM, HyperBus, HyperRAM, HyperFlash, Low Latency DRAM, Parallel PCRAM, Parallel PCM, PSRAM,

Xccela PSRAM, CRAM, OCTARAM, RDRAM, Serial PCRAM, Serial PCM, TCAM, Excelon FRAM

Верификационные IP-ядра DFI (DDR-PHY INTERFACE VIP)

DDR, DDR2, DDR3, DDR4, DDR5,

LPDDR, LPDDR2, LPDDR3, LPDDR4, LPDDR5,

HBM, HBM2E,

GDDR2, GDDR3, GDDR3L, GDDR4, GDDR5, GDDR5X, GDDR6, GDDR7

Модели для аппаратной эмуляции или

прототипирования в ПЛИС — библиотека SimXL

Мы разрабатываем синтезируемые модели (трансакторы) для эмуляторов, под торговой маркой SimXL, используя наш богатый опыт в проверке проектирования ASIC / SoC и возможности языков проверки высокого уровня (HVL) и эмуляторов. Наши модели могут работать в таких аппаратных эмуляторах, как Veloce / Palladium / Zebu, и на любой пользовательской платформе FPGA. Наши синтезируемые модели — это настраиваемые, многократно используемые решения проверки plug-and-play для стандартных интерфейсов, на основе HVL. В настоящее время мы поддерживаем Verilog для синтезируемых трансакторов с интерфейсом UVM / OVM / SystemVerilog / SystemC / C для управления моделями. Все синтезируемые трансакторы были разработаны таким образом, чтобы иметь те же функции, что и наши верификационные ядра VIP, и имеют хорошую производительность.

Все наши синтезируемые трансакторы поставляются с расширенными командами, конфигурациями и интерфейсом отчетов о состоянии. Их очень просто использовать и отлаживать. Мы используем средства автоматизации для разработки синтезируемых трансакторов, поэтому время для разработки новых моделей, если их нет в списке, может быть довольно коротким.

Многие ведущие полупроводниковые компании используют наши синтезируемые трансакторы.

Даташит и стоимость конкретных моделей высылается по запросу.

Сетевые интерфейсы

AMBA, CPRI,

Ethernet, MII/RMII/GMII/RGMII, XGMII, 10GBase-KR, 25GBase-R/KR,

40G, 50G, 100G, 200G, 400G, Ethercat, Interlaken, OBSAI, OCP, PVCI,

RapidIO, SDIO 8.0, TileLink, USB PD, OpenCores Wishbone B3

Автомобильные и последовательные интерфейсы

ARINC, AVSBus, CAN, DALI, DMX, FlexRay, GCI,

I2C, I2C/SMBus, I2S, SmartCard, JESD204, JESD207,

JTAG, LIN, LPC, LVDS, Microwire, MIL STD 1553, MIL STD 1773,

NFC, SMBus, PMBus, SENT, SpaceWire, SPI, Serial Flash, XSPI, UART

Системы хранения и видео

Camera Parallel Interface (CPI), Display Port, Fibre Channel, HDMI 1.4/2.0/2.1, OpenCAPI, PCI, PCI Express, PDM, SAS, SATA, SMPTE Serial Data Interface (SDI), SPDIF, TDM, VBYONE, UFS

DDR-память и LPDDR

DDR, DDR2, DDR3 3DS, DDR3, DDR3L, DDR4 3DS, DDR4, DDR5,

LPDDR, LPDDR2, LPDDR3, LPDDR4, LPDDR5, LPDDR5X, LPSDR

Графическая память

GDDR2, GDDR3, GDDR3L, GDDR4, GDDR5, GDDR5X, GDDR6

Flash-память

eMMC, Open Nand Flash Interface (ONFI), NAND Flash, Parallel NOR Flash, Serial NOR Flash, SLC NAND

Память High Bandwidth

HBM, HBM2E, HBM3, GHBM

Память SRAM, NV, DIMM, и другие

FCRAM, HMC, RLDRAM, RLDRAM2, RLDRAM3, SDRAM, WIDE IO, WIDE IO2

QDR2, QDR4, MRAM, NVDIMM-P, HyperBus, Low Latency DRAM, TCAM

MIPI (Mobile Industry Processor Interface)

MIPI CSI-2, CSI-3, DSI, DSI-2, HTI, I3C, MPHY, RFFE, SLIMBUS, SPMI, SOUNWIRE,

STP, Unipro

DFI (DDR-PHY INTERFACE)

DDR3, DDR4, DDR5, LPDDR3, LPDDR4, LPDDR5, HBM, HBM2E, GDDR6

IP-ядра формальной верификации (утверждения)

Наши IP-ядра для формальной проверки (Assertion IP) — это настраиваемые, повторно используемые решения для проверки plug-and-play для стандартных интерфейсов. В настоящее время мы поддерживаем язык SystemVerilog.

Все наши IP-ядра для формальной проверки имеют расширенные настройки и интерфейс отчетности о покрытии. Их очень просто использовать и отлаживать. Мы используем средства автоматизации для разработки IP-ядер для формальной проверки, поэтому время для разработки нового IP-ядра для формальной проверки будет очень быстрым. Если вам нужно какое-либо IP-ядро для формальной проверки для интерфейса или стандарта, который не указан ниже, сообщите нам об этом. Мы можем разработать его для вас очень быстро.

Даташит и стоимость конкретных Assertion IP высылается по запросу.

Сетевые интерфейсы

AMBA, Avalon, OCP, TileLink

DDR и LPDDR

DDR, DDR2, DDR3, DDR4, DDR5,

LPDDR, LPDDR2, LPDDR3, LPDDR4, LPDDR5, LPDDR5X

Графическая память. память High Bandwidth, память SDRAM

GDDR5, GDDR5X, GDDR6, HBM, HBM2E, HBM3, SDRAM

DFI (DDR-PHY INTERFACE)

DDR, DDR2, DDR3, DDR4, DDR5, LPDDR, LPDDR2, LPDDR3, LPDDR4, LPDDR5,

HBM, HBM2E, GDDR6

Последовательные интерфейсы

eSPI, I2C, JTAG, LPC, PMBUS, SMBUS, SPI, UART

Комплект поставки

Как правило, в комплект поставки входят следующие составляющие (различается в зависимости от типа ядра и решаемых задач).

-

Интерфейсное IP-ядро доступно в виде исходного кода и netlist.

-

Исходный код поставляется в формате Verilog. При необходимости также может быть предоставлен код VHDL, SystemC.

-

Предоставляется простая в использовании среда тестирования Verilog с тестовыми наборами Verilog.

-

Предоставляются скрипты Lint, CDC, Synthesis, Simulation Scripts с файлами отказа (waiver files).

-

Карта адресов, сгенерированная IP-XACT RDL.

-

Код прошивки и пакет драйверов Linux.

-

Документация содержит руководство пользователя и примечания к выпуску.

Варианты лицензирования

-

Вариант лицензии на один сайт предоставляется компаниям, проектирующим на одном сайте.

-

Вариант лицензии на несколько площадок предоставляется компаниям, разрабатывающим на нескольких площадках.

-

Лицензия на единый дизайн позволяет реализовать IP-ядро в одном проекте FPGA и ASIC.

-

Лицензия Unlimited Designs позволяет реализовать IP-ядро в неограниченном количестве проектов (прошивок) FPGA и ASIC.

что это, преимущества и недостатки

Сейчас ASIC начинают обгонять добычу криптовалюты на GPU (видеокартах), выходят асики под новые и новые алгоритмы. Однако появилась альтернатива ASIC и GPU.

Сегодня мы расскажем о программируемой логической интегральной схеме или кратко FPGA.

Эти электронные элементы объединяют то, что мы любим больше всего в видеокартах и в ASIC.

Единственная проблема в том, что на сегодняшний день этих плат очень мало, и если Вы хотите зайти в майнинг на FPGA, Вы должны это сделать … сейчас.

Чем FPGA интересен для майнинга?

Смотрите видео:

Два основных вопроса, которые FPGA должны решить

Криптовалюты волатильны и нестабильны. Криптомир можно сравнить с бурным океаном – если Вы хотите заниматься серфингом, Вы должны быть готовы к маневрированию.

Раньше, когда для добычи большинства популярных монет было выгодно использование CPU (процессоров) или GPU (видеокарт), Вы всегда имели возможность быстро адаптироваться к криптовалютному рынку. Как только курс монеты падает, Вы можете сразу запустить другой майнер (программу для добычи криптовалют) и начать добычу более прибыльной монеты. Мы все прыгали из Ethereum к Monero, а затем к Zcash: туда и обратно, в зависимости от прибыльности монет.

Сейчас, когда ASIC штурмуют майнинг пулы большинства монет, существует всего одна стратегия: выбрать монету, купить под нее ASIC и молиться, чтобы монета быстро окупалась. GPU майнинг по-прежнему является вариантом, но количество монет, которые Вы можете добывать, теперь ограничено.

Проблема ASIC заключается в том, что они предлагают нулевую гибкость, когда дело доходит до монеты, которую Вы можете добывать. ASIC разрабатывается только под один алгоритм. Если по какой-то причине алгоритм становится непопулярным или нерентабельным, купленный ASIC становится бесполезным. Так как они очень много стоят, то покупать их очень рискованно.

Есть ли третий вариант?

Всегда есть третий вариант, верно? Если бы было только такое аппаратное обеспечение, которое бы сочетало гибкость выбора алгоритма для добычи (как у видеокарт) и мощность хэширования ASIC … все бы использовали это оборудование, верно?

FPGA — это такое оборудование, поэтому он – новый фаворит в сообществе майнеров. Неудивительно, почему спрос на него огромен.

FPGA существует с 1982 года. Они использовались и продолжают использоваться в науке, моделировании транспортных средств и даже в военных технологиях.

Первым производителем этих устройств была американская технологическая компания под названием Xilinx. Позже, другая американская компания под названием Altera (теперь входящая в состав Intel) присоединилась к этой отрасли и с тех пор является основным конкурентом Xilinx.

Внедрение и развитие схем ПЛИС (программируемых логических интегральных схем), разновидностью которых является FPGA, очень приветствовалось во многих отраслях промышленности, и спрос на такое оборудование и технологии все еще растет. Например, в 2013 году размер объема рынка для плат FPGA составил 5,4 миллиарда долларов США, и, согласно оценкам, он достигнет отметки в 9,8 миллиардов долларов США в 2020 году.

Прежде, чем говорить о технической стороне, ответим на вопрос: «Если FPGA настолько хороши, почему бы людям не использовать их для майнинга с самого начала?»

Почему FPGA никогда не использовались в майнинге?

На самом деле, как только Bitcoin стал популярен, некоторые люди, у кого были ПЛИС старого образца, начали добывать первую криптовалюту на своем оборудовании. Но в массы это не пошло.

Есть две причины, почему платы FPGA для майнинга массово начинают использовать только сейчас.

Первая причина заключается в том, что благодаря гибкости и архитектуре платы FPGA нелегко настроить. Их можно запрограммировать на что угодно. Это хорошо, хотя это также означает, что для использования платы FPGA Вы должны знать, как программировать ее.

В отличие от графического процессора (GPU), который Вы можете настроить с помощью BIOS и майнера, плата FPGA должна быть запрограммирована с нуля, чтобы она могла добыть определенный алгоритм. Для этого вам нужно написать код на языке Verilog или VHDL — ни Python, ни C ++ не работают.

Так как только некоторые программисты способны это сделать, потребуется время, чтобы они выполнили эту работу. Затем эти программисты должны будут сделать бизнес-модель для продажи программ для общественности и так далее. Это, в конечном счете, произойдет, но пока они это делали, появилась причина №2.

Вторая причина — создание первой ASIC для добычи криптовалют. В отличие от FPGA, ASIC не нужно настраивать: подключи и он работает. Любой может использовать его. Очевидно, что это само по себе было решающим фактором. Кроме того, было много альтернатив для майнинга ASIC — таких, как возможность использовать фермы GPU и добывать меньше монет.

Теперь, когда ASIC доминируют в майнинг пулах, а графические процессоры немного отстают, FPGA становятся все более интересными для среднего майнера.

В двух словах: что такое FPGA?

Итак, что такое программируемая пользователем вентильная матрица (field-programmable gate array)?

FPGA — это часть аппаратного обеспечения, которая очень похожа на ASIC с одним исключением. ASIC — это чип, который был настроен для жесткого выполнения одного типа вычислений (например, для майнинга алгоритма Equihash). FPGA — это чип, который можно перепрограммировать для выполнения любых операций. В области добычи криптовалют Вы можете перенастроить свою FPGA от CryptoNight до добычи Lyra2z в течение секунды.

CPU и GPU тоже могут это делать, хотя по нескольким причинам FPGA работает быстрее. Для этого есть несколько причин – о некоторых мы расскажем чуть позже.

Платы FPGA работают в несколько раз лучше, чем GPU с одинаковым энергопотреблением. В зависимости от алгоритма FPGA может не отставать от ASIC по хэшам.

С одной стороны FPGA — это:

- Полная гибкость при использовании любых алгоритмов — никакие программные форки не могут повлиять на ваш майнинг, пока Вы обновляете битовый поток FPGA.

- Огромная энергоэффективность по сравнению с GPU

С другой стороны FPGA:

- Должны быть подключены к ПК, как и графические процессоры

- Пока недоступны для массового майнинга

- Очень дорогие по сравнению с GPU

- Может немного превосходить ASIC в зависимости от алгоритма

Bitstream

Bitstream — это в программа, написанная на языке программирования (Verilog или VHDL), который сообщает FPGA, что делать. Если Вы хотите добывать определенный алгоритм, Вы должны иметь бит-поток, который сообщает FPGA, как добывать этот конкретный алгоритм. Bitstreams загружаются в FPGA после загрузки системы.

Битовый поток загружается в энергозависимую память ПЛИС. Да, это все та же память DDR4. Модель FPGA имеет 64 ГБ. Это огромное количество оперативной памяти позволяет FPGA хранить сотни бит-потоков и переключаться между ними в доли секунды.

Как Вы, вероятно, ожидаете, эта функциональность позволяет FPGA добывать такие алгоритмы, как Timetravel10, X11Evo, X16R и X16S, которые требуют, чтобы чип переключался между различными «меньшими» алгоритмами хэширования каждые несколько минут.

В то время как битовый поток может быть изменен за долю секунды, плата может по-прежнему добывать только один алгоритм за раз с несколькими редкими исключениями.

Первоначальное предложение

Около полутора месяцев назад три члена майнинг сообщества упорно работали над созданием первых битовых потоков, чтобы некоторые модели FPGA (Xilinx VU9P) могли добывать различные алгоритмы.

Сегодня у этой команды есть магазин, где они разместили первые платы, а также страница на Bitcointalk. Одним из членов команды является GPUhoarder, известный за свой проект Squirrels Research.

Эти ребята в основном используют универсальные платы FPGA Xilinx VU9P и модифицируют их, чтобы они были пригодны для майнинга. «Vanilla» Xilinx VU9P поставляется с довольно плохим охлаждением, поэтому для хорошей работы в майнинге необходимо вручную выполнить требуемые настройки и улучшения.

Благодаря партнерству команды программистов с Xilinx, они дают нам возможность покупать эти платы в розницу. Кроме того, модификации, которые они делают (улучшенный радиатор и охлаждение), не мешают официальной гарантии Xilinx.

В дополнение к этому, они работают над экосистемой, окружающей карты, с необходимыми программными инструментами, структурой поддержки и т.д. Это позволит как начальным разработчикам, так и сообществу писать свои собственные потоки данных и размещать их в зашифрованном блокчейне, доступном только для людей, которые приобрели FPGA «интеллектуального выпуска».

Затем любой может создавать битовые потоки для существующих майнинг алгоритмов, а Zetheron (название компании) будет взимать фиксированную плату от имени разработчиков. Это обеспечит:

- безопасность разработчикам битовых потоков — они будут получать оплату за свою работу

- не будет членского взноса для владельцев FPGA: Вы платите только если скачали битовый поток для майнинга определенного алгоритма

- доступ к разнообразию битового потока, созданного сообществом, безусловно, гарантирует, что скоро можно будет добывать практически любые алгоритмы

Что касается сегодняшнего дня, то Zethereon разработал рабочий битовый поток для алгоритмов Cryptonote и Lyra2z.

«Текущий план — выпускать примерно один алгоритм в месяц, пока не будут охвачены все основные алгоритмы»,

— пишет команда Zethereon.

Это означает, что благодаря работе, которую эти ребята сделали, теперь у нас будет готовая разработка для настройки наших плат FPGA. Созданная экосистема Zetheron даст нам все варианты битового потока, которые нужны, чтобы добывать любой популярный алгоритм без необходимости знать что-либо о программировании. Кроме того, разработчики будут мотивированы, чтобы продвинуть планку выше и создать лучшие битовые потоки.

Это все прекрасно, но есть подвох. Платы, которые Zethereon предложили публике, были проданы в течение нескольких часов. По-видимому, идея иметь плату, которая сочетала бы гибкость графического процессора и возможности ASIC, была слишком хороша, чтобы ее можно было упустить.

Хешрейт 1900 MH/s — фейк?

В сети ходят слухи, что устройства FPGA VCU1525 способны выдавать 1900 MH/s на Ethash алгоритме Эфириума. Скорее всего это фейк.

По нашим подсчетам, одно FPGA устройство не может выдавать 1900 MH/s, вероятнее это риг из 6 FPGA дает такой показатель.

FPGA может быть мощнее видеокарты в 10 раз, но не более.

1900 MH/s был бы способен выдавать ASIC, если бы его смогли произвести.

Создают ли угрозу GPU майнерам FPGA?

Устройство стоит в районе 4000$ и скорее всего мощнее видеокарт в 10 раз.

При этом, гарантия на видеокарты обычно составляет 3 года, а у FPGA вендоров — всего 3 месяца.

Вероятнее всего, устройства подойдут только для крупных, «промышленных» майнеров. На данный момент проще купить видеокарт, т.к. окупаемость почти одинаковая.

Где взять FPGA сейчас?

FPGA нет в наличии у Zethereon, но есть другой вариант — Mineority.

Mineority была основана OhGodACompany — командой программистов, которые сделали ETHnlargementPill и других хорошо известные программные обеспечения для майнинга. Они объединились с Stayfirst, Mind Dev и Di Support, чтобы открыть Mineority.

На своем официальном сайте Mineority заявляет, что они являются «платформой для покупки, оптимизации, размещения и торговли видеокартами».

Mineority — это компания, специализирующаяся на торговле оборудованием для майнинга. Они также производят в Китае собственные карты, ориентированные на добычу криптовалют, и продают их. Что отличает Mineority от других компаний, так это то, что они предлагают облачный майнинг.

За определенную плату Вы можете купить свою карточку и оставить ее на одном из объектов Mineority в США или Европе. Вы можете арендовать место в майнинг ферме на срок до трех лет, после чего ваша карта будет отправлена вам. Или Вы можете попросить компанию сразу же отправить вам видеокарту, как только Вы ее купите. Существует также возможность перепродавать карту на рынке Mineority.

Компания гарантирует, что Вы получаете купленную вами карту: детали и уникальный номер вашей карты и чипа прикреплены к незаменимому токену ERC-721 – Вы всегда можете проверить, совпадают ли детали.

Не так давно Mineority начали перепродавать карту Xilinx V9UP, модифицированную так, чтобы быть «лучшей среди конкурентов в майнинге». Эта версия карты включает в себя требуемые 64 ГБ установленной DDR4 RAM и специальную систему охлаждения, которая позволяет карте использовать всю свою вычислительную мощность в майнинге (исходный Xilinx V9UP не может работать со 100% отдачей без перегрева). Mineority также дает владельцу доступ к постоянно растущей базе битовых потоков для добычи различных алгоритмов.

Плохая новость заключается в том, что запас этих карт ограничен, но будут и новые FPGA.

Вывод

FPGA стоит от $3600 долларов, но если все пойдет так, как планировалось, эти платы позволят нам в любой момент добывать практически любой алгоритм. В отличие от ASIC, которая требует, чтобы Вы инвестировали большие средства в разработку одного алгоритма, FPGA должна стать универсальным решением для майнинга.

это бархатистый материал с натуральным составом, фото

Плис – это ворсовый материал из чистого хлопка или с добавкой синтетики. Считается разновидностью бархата, но отличается более длинным ворсом. Ткань популярна в изготовлении одежды, интерьерных вещей, обивке мебели.

СодержаниеПоказать

Описание

Плис по внешнему виду схож с бархатом. У него такая же ворсистая поверхность, но с меньшим блеском.

Справка. Название материала происходит от латинского слова pilus, означающего «волос».

Плис ткань появилась в Европе в XVIII столетии как одна из разновидностей бархата. Но в отличие от дорогого материала, у которого в составе обязательно присутствовал шелк, изготавливалась она из хлопковой пряжи, за что получила название бумажный бархат.

Вскоре плис стали ткать из шерстяных волокон, что также способствовало росту популярности. Но наиболее широкое распространение текстиль получил спустя столетие, когда было налажено промышленное производство ткани в Манчестере. Материал выпускался однотонным, преимущественно нейтральных, темных и черных цветов, поскольку использовался главным образом в пошиве мужской одежды.

Интересно. Плис упоминается в произведениях А. Пушкина, Н. Гоголя, И. Гончарова.

В России материал появился в XVIII веке и сразу нашел своих поклонников, хотя считался менее престижным, чем бархат. Дворянство и богатые люди носили домашние плисовые вещи и обувь, купеческое сословие и зажиточные крестьяне ценили заменитель бархата за декоративность, поэтому заказывали из него костюмы для торжественных случаев.

Позже появился новый вариант плиса – мебельного. Материю делали из шерстяной пряжи, которая стоила дешевле настоящего бархата, поэтому пользовалась успехом.

Состав и свойства

Современный плис – это ткань с длиной ворса 5-6 мм, неотличимый на фото с бархатом. Изготавливается преимущественно из хлопчатобумажной или шерстяной пряжи, либо с добавками синтетики.

Материал производят на специальных станках бархатным плетением. Само полотно образуется за счет использования нескольких нитей: помимо утка и основы, в состав входит дополнительная, — формирующая петли. Волокна переплетаются очень туго, приподнимая уточные нити. Далее петли подстригают, шлифуют, в результате чего на лицевой стороне получается мягкая плюшевая поверхность.

Важно. Ткань в шитье достаточно сложна: ворсовый материал сыпется на срезах, сдвигается при раскрое.

Виды

Современный рынок предлагает разные вариации плиса. Наиболее популярные виды:

| Название | Характеристика |

|---|---|

| Бивер | Плотный текстиль, у которого основа изготавливается из полиэфира, ворс – из хлопка. Лицевая сторона обладает свойствами натурального материала, а изнанка обеспечивает долговечность, стойкость к загрязнениям, влажности. |

| Вельветин | Мягкая, деликатная тонкая ткань с хлопковым ворсом. Производится из самых тонких нитей. |

| Мебельный плис | Бывает чисто- или полушерстяным. Основа более крепкая и плотная, чем у других видов ткани. |

Плюсы и минусы

Плис материал из натуральной пряжи обладает рядом особенностей. Подобно любой ткани, имеет преимущества и недостатки.

Плюсы:

Автор:

Анастасия Кукушкина

Надеюсь, вам нравится статья, которую я для вас подготовила! Если вы нашли в ней ошибки — напишите мне об этом! Я отвечу на любые ваши вопросы, задавайте их! 🙂

Задать вопрос автору- экологичность: плис безопасен для окружающей среды, здоровья человека и животных;

- гипоаллергенность: ворсовая ткань не наносит вреда организму;

- терморегуляция: в одежде из плиса не холодно в прохладную погоду, комфортно летом;

- антибактериальность: хлопковый ворс препятствует развитию патогенных микроорганизмов;

- гигроскопичнсость: натуральные волокна эффективно поглощают влагу;

- декоративность: выразительная фактура, привлекательный внешний вид;

- пластичность: ткань хорошо драпируется;

- приятные тактильные качества: плис приятен на ощупь.

Факт. Благодаря тугому плетению основы, ткань износостойка и долговечна.

Минусы у ткани тоже есть, хотя немного:

- ворсовая поверхность притягивает пыль, удерживает мелкий сор;

- сложности ухода: при несоблюдении условий быстро теряет привлекательность, выходит из строя.

Использование

Ворсовый материал популярен в пошиве множества изделий:

- скатерти, покрывала, портьеры, декоративные подушки;

- повседневная одежда: платья, костюмы, куртки, юбки;

- домашний гардероба: халаты, пижамы, костюмы, штаны;

- сценические и маскарадные костюмы;

- спецодежда, униформа;

- обивка мебели.

Используется плис также в изготовлении домашних тапочек, рукоделии. Из него шьют игрушки, интерьерные вещи, сумочки, аксессуары.

Уход

Изделия из плиса прослужат долго, если помнить об особенностях материала. Ткань несложна в уходе, но требует соблюдения правил:

- Материалу из натуральных волокон разрешена только химчистка, текстиль с синтетикой можно стирать, но исключительно вручную при 25-30 °C. Сильно не тереть, не пользоваться жесткими щетками.

- Применять жидкие моющие средства: они быстрее проникают внутрь волокон, легче выполаскиваются.

- Не отбеливать.

- Запрещено сильно выкручивать и отжимать. Для удаления воды изделие следует закатать в полотенце, подержать, пока впитается влага. Либо поместить после стирки на возвышение, чтобы вода стекла естественным образом.

- Сушить вдали от отопительных приборов.

- Гладить с изнанки теплым утюгом. Чтобы ворс не примялся, материал следует положить лицевой стороной вниз на такую же ткань или махровое полотенце. Но лучшим вариантом разглаживания считается вертикальное отпаривание.

Важно. Изделия, не подлежащие стирке, рекомендуется регулярно вытряхивать, пылесосить или чистить щеткой.

Заключение

Плис – бюджетный аналог велюра, ворсовая ткань. Производится из хлопка или шерсти. Используется в пошиве одежды, домашней обуви и текстиля.

Что такое JTAG и как это применить для тестирования печатных плат? — Основы

JTAG – это нечто большее, чем просто отладка и перепрограммирование микросхем

Если Вы применяли какие-либо инструменты, использующие JTAG, то Вы уже знакомы с этим интерфейсом. Например, процессоры часто используют JTAG для доступа к своим отладочным функциям, также все ПЛИС используют JTAG для перепрограммирования.

JTAG – это НЕ ТОЛЬКО отладка процессоров.

JTAG – это НЕ ТОЛЬКО программирование ПЛИС/CPLD.

Название JTAG чаще всего ассоциируется с инструментами отладки и перепрограммирования микросхем. Однако, в этих инструментах реализована только часть возможностей JTAG.

Эта часть возможностей, известная под названием Test Access Port или, сокращённо, TAP, является частью стандарта IEEE Std. 1149.1. Этот стандарт был разработан для тестирования сборок печатных плат (Printed Circuit Board Assemblies – PCBA) без необходимости доступа на так называемом «низком» (физическом) уровне, который требуется для анализа «сложных» случаев. Стандарт также не предусматривает разработку и использование специфических функциональных тестов. Изначально TAP был разработан только для взаимодействия с дополнительными регистрами, специально вставляемыми в микросхему с целью реализации данного метода тестирования.

Однако достаточно быстро производители микросхем заметили потенциал использования TAP и для других целей, например, для доступа к регистрам, предназначенным для отладки и перепрограммирования микросхем.

Теперь в микросхемы добавляется специальный регистр для тестирования через JTAG под названием Boundary Scan Register (BSR). Как и подразумевает название этого регистра, отдельные его части (или, по-другому, ячейки (Cells)) являются «пограничными» для микросхемы, так как располагаются между функциональным ядром и контактами корпуса микросхемы. По этой причине тестирование через JTAG часто называют пограничным сканированием (boundary scan).

Как технология пограничного сканирования, реализуемая стандартом JTAG, используется для тестирования печатных плат?

Ячейки регистра пограничного сканирования (Boundary Scan Register) могут работать в одном из двух режимов: 1) функциональный режим – ячейки не влияют на работу прибора, прибор работает в своём обычном виде; 2) тестирующий режим – ячейки отсоединяют функциональное ядро микросхемы от контактов корпуса. Тестирующий режим используется для управления значениями на контактах корпуса микросхемы (и в соответствующих цепях печатной платы), а также для считывания значений с подключённых цепей печатной платы.

Отключение функционального ядра микросхемы существенно упрощает разработку тестов, так как использование пограничного сканирования (boundary scan) позволяет не разрабатывать программу для микропроцессора или прошивку для ПЛИС и не включать прибор в «рабочем» режиме. Механизм управления и наблюдения за контактами корпуса микросхемы через четырёх-контактный TAP, JTAG интерфейс позволяет получить низкоуровневый доступ к контактам микросхемы для физического тестирования печатной платы.