Как работают преобразователи кодов из параллельного формата в последовательный и обратно. Какие элементы используются для построения таких схем. На каких принципах основана работа параллельно-последовательных и последовательно-параллельных преобразователей.

Принципы преобразования параллельного кода в последовательный

Преобразование параллельного кода в последовательный необходимо при передаче информации на большие расстояния для минимизации числа каналов связи. Основные принципы такого преобразования:

- Одновременная подача всех элементов параллельного кода на входы преобразователя

- Поочередное считывание каждого элемента кода

- Сохранение соответствия между элементами входного и выходного кода

- Изменение только пространственно-временных соотношений между элементами кода

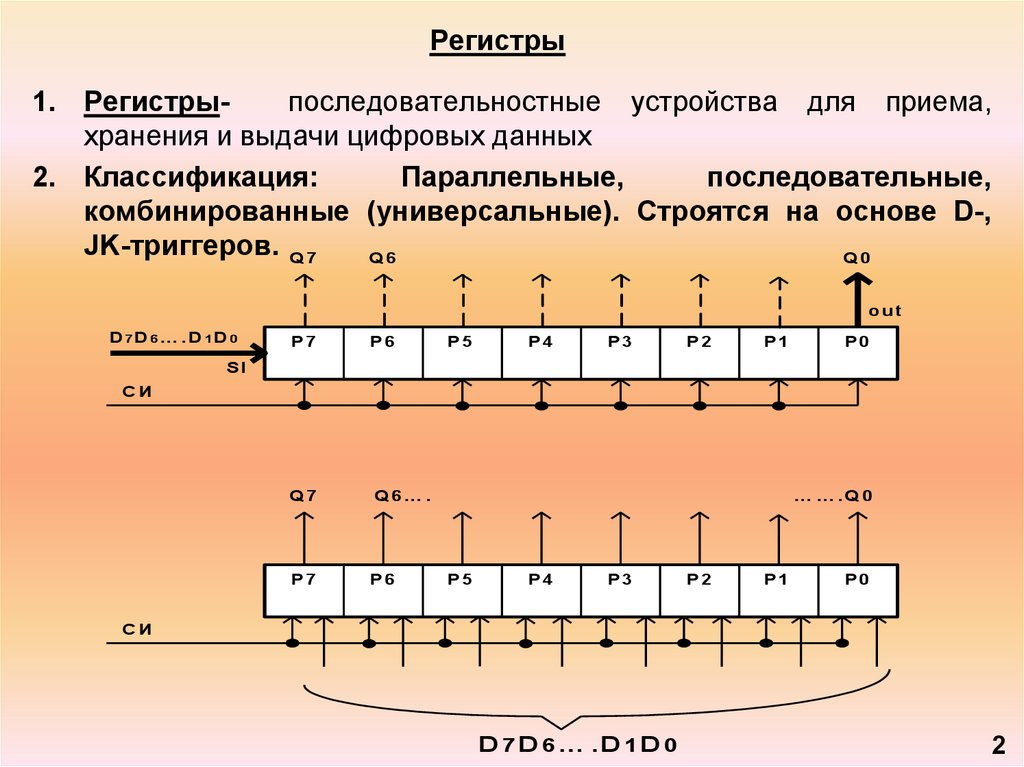

Для реализации преобразователей параллельного кода в последовательный используются два основных типа схем:

- На основе мультиплексоров

- На основе регистров сдвига

Схемы преобразователей на основе мультиплексоров

Мультиплексоры позволяют эффективно реализовать преобразование параллельного кода в последовательный. Как работает такая схема?

- На информационные входы мультиплексора подаются разряды параллельного кода

- На адресные входы поступают сигналы от двоичного счетчика

- Счетчик последовательно перебирает адреса входов мультиплексора

- На выходе мультиплексора формируется последовательный код

Преимущества схемы на мультиплексоре — простота реализации и высокое быстродействие. Недостаток — ограниченная разрядность преобразуемого кода.

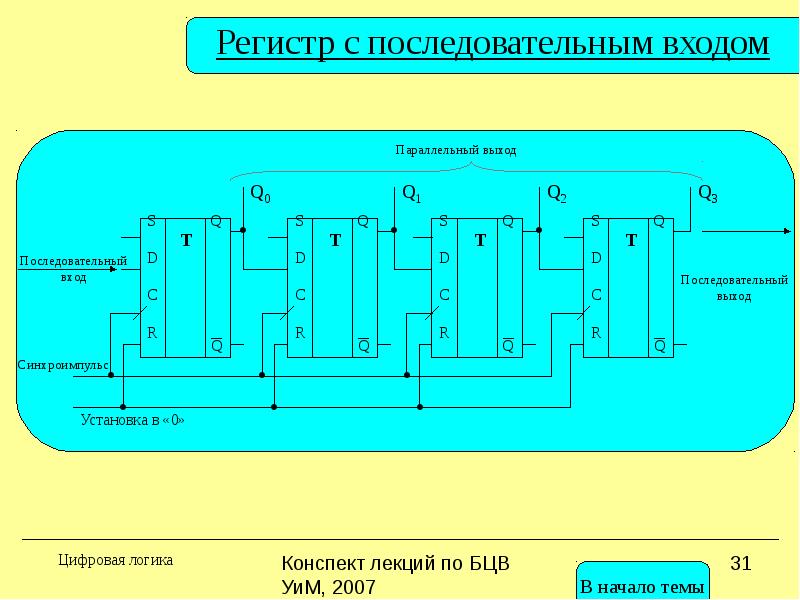

Преобразователи на основе регистров сдвига

Регистры сдвига позволяют создать более универсальные преобразователи параллельного кода в последовательный. Принцип работы такой схемы:

- Параллельный код записывается в регистр сдвига

- Выполняется последовательный сдвиг разрядов регистра

- С выхода последнего разряда снимается последовательный код

Преимущества схемы на регистре сдвига — универсальность и возможность работы с кодами любой разрядности. Недостаток — более низкое быстродействие по сравнению с мультиплексорной схемой.

Преобразование последовательного кода в параллельный

Для преобразования последовательного кода в параллельный используются схемы на основе демультиплексоров или регистров сдвига. Основные принципы работы таких преобразователей:

- Последовательная запись входного кода по одному каналу

- Синхронизация записи с тактовыми импульсами

- Одновременное считывание всей принятой кодовой комбинации

- Число выходных каналов соответствует разрядности кода

Схемы на основе демультиплексоров

Демультиплексоры позволяют эффективно распределить биты последовательного кода по параллельным выходам. Принцип работы такой схемы:

- Последовательный код подается на информационный вход демультиплексора

- Адресные входы управляются счетчиком

- Счетчик последовательно перебирает адреса выходов

- Биты кода распределяются по выходам демультиплексора

Преимущества схемы на демультиплексоре — простота и высокое быстродействие. Недостаток — ограниченная разрядность преобразуемого кода.

Преобразователи на регистрах сдвига

Регистры сдвига позволяют создать универсальные преобразователи последовательного кода в параллельный. Как работает такая схема?

- Последовательный код поразрядно записывается в регистр сдвига

- После записи всех разрядов выполняется параллельное считывание

- На выходах регистра формируется параллельный код

Главное преимущество — возможность работы с кодами любой разрядности. Недостаток — более низкое быстродействие по сравнению со схемой на демультиплексоре.

Практическое применение преобразователей кодов

Где на практике применяются рассмотренные преобразователи кодов?

- В системах передачи данных для согласования параллельных и последовательных интерфейсов

- В устройствах ввода-вывода компьютеров и микропроцессорных систем

- В схемах сопряжения цифровых и аналоговых устройств

- В системах цифровой обработки сигналов

- В устройствах кодирования и декодирования информации

Синхронизация в преобразователях кодов

Важный аспект работы преобразователей кодов — правильная синхронизация. Какие методы синхронизации применяются?

- Использование тактовых импульсов для синхронизации записи и сдвига

- Применение счетчиков для формирования адресных сигналов

- Синхронизация по переднему или заднему фронту импульсов

- Использование стробирующих сигналов для управления записью

Правильная синхронизация обеспечивает корректное преобразование кодов и отсутствие ошибок при передаче данных.

Особенности проектирования преобразователей кодов

При разработке схем преобразователей кодов следует учитывать ряд важных факторов:

- Требуемую разрядность преобразуемых кодов

- Необходимое быстродействие схемы

- Универсальность или специализация преобразователя

- Возможность работы в ручном и автоматическом режимах

- Наличие средств индикации и контроля

- Совместимость с другими элементами системы

Оптимальный выбор элементной базы и структуры схемы позволяет создать эффективный преобразователь для конкретной задачи.

Устройство преобразования последовательного кода в параллельный

Устройство преобразования последовательного кода в параллельный относится к вычислительной технике и может быть использовано для преобразования биполярного трехуровневого последовательного кода в однополярный параллельный код. Изобретение позволяет повысить скорость передачи информации за счет сокращения времени передачи информационного бита. Для этого устройство содержит согласующий трансформатор, два однополупериодных выпрямителя, два элемента НЕ, два D-триггера, пять элементов ИЛИ — НЕ, таймер, счетчик, счетчик по модулю два, дешифратор, элемент И и сдвиговый регистр. Наличие двух D-триггеров и таймера позволяет снизить вероятность потери информации в канале связи за счет повышения помехозащищенности устройства. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано для преобразования биполярного трехуровневого последовательного кода в однополярный параллельный код.

Известно устройство для преобразования последовательного кода в параллельный [1], содержащее два делителя напряжения, два усилителя-ограничителя, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента НЕ, регистр сдвига, два триггера и два элемента И. К недостаткам этого устройства следует отнести большое количество сопровождающих обмен интерфейсных сигналов, что затрудняет использование его при больших расстояниях между передатчиком и приемником информации. Кроме того, увеличение помехоустойчивости канала связи достигается посредством запроса повторения передаваемого слова, что снижает скорость передачи данных.

К недостаткам этого устройства следует отнести большое количество сопровождающих обмен интерфейсных сигналов, что затрудняет использование его при больших расстояниях между передатчиком и приемником информации. Кроме того, увеличение помехоустойчивости канала связи достигается посредством запроса повторения передаваемого слова, что снижает скорость передачи данных.

Наиболее близким по технической сущности и достигаемому результату к заявляемому техническому решению является преобразователь последовательного кода в параллельный [2], выбранный за прототип. Устройство-прототип содержит согласующий трансформатор, первый и второй однополупериодные выпрямители, сдвиговый регистр, счетчик, дешифратор, первый элемент И, счетчик по модулю два. Эти признаки совпадают с существенными признаками заявляемого технического решения. Устройство содержит также первый и второй элементы задержки, второй элемент И, третий элемент И, триггер, элемент ИЛИ, первый и второй таймеры. К недостаткам прототипа следует отнести наличие элементов задержки на время То/4, где To — время битового интервала, что требует паузы в передачи информационных сигналов на время, >То/4 для восстановления устройства. Кроме того, искажение формы (разрывы), как в первой четверти, так и во второй четверти информационного сигнала То вследствие воздействия помех приводит к неправильному декодированию информации (многократной записи в сдвиговый регистр). Случайный импульс на входе устройства запускает второй таймер и время восстановления устройства составляет тогда целое слово n.To, где n — число информационных бит в слове.

К недостаткам прототипа следует отнести наличие элементов задержки на время То/4, где To — время битового интервала, что требует паузы в передачи информационных сигналов на время, >То/4 для восстановления устройства. Кроме того, искажение формы (разрывы), как в первой четверти, так и во второй четверти информационного сигнала То вследствие воздействия помех приводит к неправильному декодированию информации (многократной записи в сдвиговый регистр). Случайный импульс на входе устройства запускает второй таймер и время восстановления устройства составляет тогда целое слово n.To, где n — число информационных бит в слове.

Целью изобретения является повышение скорости передачи информации за счет сокращения времени передачи информационного бита.

Кроме того, предложенное техническое решение позволяет снизить вероятность потери информации в канале связи за счет повышения помехозащищенности устройства. Это является дополнительной целью изобретения.

Это является дополнительной целью изобретения.

Поставленная цель достигается тем, что устройство преобразования последовательного кода в параллельный содержит согласующий трансформатор, первый и второй однополупериодные выпрямители, сдвиговый регистр, счетчик, счетчик по модулю два, дешифратор и элемент И, выход которого является выходом устройства. Вход согласующего трансформатора является входом устройства. Первый и второй выходы согласующего трансформатора соединены с входами соответственно первого и второго однополупериодных выпрямителей. Первые входы счетчика и счетчика по модулю два объединены соответственно с входами С и сдвигового регистра, группа выходов которого является группой выходов устройства. Группа выходов счетчика соединена с группой входов дешифратора, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом счетчика по модулю два. Эти признаки являются общими для прототипа и заявляемого технического решения.

Устройство содержит также первый и второй элементы НЕ, первый, второй, третий, четвертый и пятый элементы ИЛИ-НЕ, таймер, первый и второй D-триггеры, R-входы которых объединены со вторыми входами счетчика и счетчика по модулю два и соединены с выходом таймера. Выход первого однополупериодного выпрямителя через первый элемент НЕ соединен с первым входом первого элемента ИЛИ-НЕ, первым входом таймера и первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с инверсным выходом первого D-триггера, прямой выход которого соединен со вторым входом первого элемента ИЛИ-НЕ, выход которого соединен с S-входом второго D-триггера, прямой выход которого соединен с первым входом третьего элемента ИЛИ-НЕ, выход которого соединен с S-входом первого D-триггера. Выход второго однополупериодного выпрямителя через второй элемент НЕ соединен со вторым входом третьего элемента ИЛИ-НЕ, вторым входом таймера и первым входом четвертого элемента ИЛИ-НЕ, второй вход которого объединен с D-входом сдвигового регистра и соединен с инверсным выходом второго D-триггера, С-вход которого объединен с С-входом первого D-триггера, первым входом счетчика и соединен с выходом пятого элемента ИЛИ-НЕ, первый и второй входы которого соединены с выходами соответственно второго и четвертого элементов ИЛИ-НЕ. Эти признаки присущи только заявляемому устройству.

Эти признаки присущи только заявляемому устройству.

Совокупность приведенных выше существенных признаков по сравнению с прототипом позволяет в два раза сократить паузу между информационными импульсами, т. о. на 25% сократить время битового интервала, что эквивалентно повышению скорости передачи данных на 25%.

Наличие двух D-триггеров, кроме того, делает устройство нечувствительным к искажениям (провалам до уровня 0 вольт) формы сигнала в первой трети битового интервала, обусловленным воздействием помех, так как такие искажения не приводят к изменению состояния D-триггеров. Наличие двухвходового таймера, анализирующего временной интервал, представленный уровнем 0 вольт на входе устройства, ко всему прочему, позволяет переводить устройство в исходное состояние, если указанный временной интервал превышает времени Т3 (где Т — время битового интервала), что исключает накопление информации в сдвиговом регистре по шумам и по сравнению с прототипом в n раз сокращает время восстановления устройства после воздействия импульсной помехи, где n-число бит в слове. Указанные особенности приводят к снижению вероятности потери информации в канале связи.

Указанные особенности приводят к снижению вероятности потери информации в канале связи.

На фиг. 1 представлена функциональная схема устройства; на фиг.2 — временные диаграммы работы устройства.

Устройство преобразования последовательного кода в параллельный содержит согласующий трансформатор 1, первый и второй однополупериодные выпрямители 2 и 3, первый и второй элементы НЕ, 4 и 5, первый элемент ИЛИ-НЕ 6, таймер 7, первый D-триггер 8, второй D-триггер 9, второй элемент ИЛИ-НЕ 10, третий элемент ИЛИ-НЕ 11, четвертый элемент ИЛИ-НЕ 12, пятый элемент ИЛИ-НЕ 13, сдвиговый регистр 14, дешифратор 15, счетчик 16, счетчик 17 по модулю два, элемент И 18, вход 19 устройства, группу 20 выходов устройства, выход 21 устройства. Первый выход согласующего трасформатора 1 через первый однополупериодный выпрямитель 2 и первый элемент НЕ 4 соединен с первым входом первого элемента ИЛИ-НЕ 6, первым входом таймера 7 и первым входом второго элемента ИЛИ-НЕ 19, второй вход которого соединен с инверсным выходом первого D-триггера 8, прямой выход которого соединен с вторым входом первого элемента ИЛИ-НЕ 6, выход которого соединен с S-входом второго D-триггера 9, прямой выход которого соединен с первым входом третьего элемента ИЛИ-НЕ 11, выход которого соединен с S-входом первого D-триггера 8.

Второй выход согласующего трансформатора 1 через второй однополупериодный выпрямитель 3 и второй элемент НЕ соединен с вторым входом третьего элемента ИЛИ-НЕ 11, вторым входом таймера 7 и первым входом четвертого элемента ИЛИ-НЕ 12. Первый и второй входы пятого элемента ИЛИ-НЕ 13 соединены с выходами соответственно второго элемента ИЛИ-НЕ 10 и четвертого элемента ИЛИ-НЕ 12. Выход пятого элемента ИЛИ-НЕ 13 соединен с С-входами первого и второго триггеров 8 и 9, первым входом счетчика 16 и С-входом сдвигового регистра 14. Инверсный выход второго D-триггера 9 соединен со вторым входом четвертого элемента ИЛИ-НЕ 12, D-входом сдвигового регистра 14 и первым входом счетчика 17 по модулю два. Выход таймера 7 соединен с R-входами первого и второго D-триггеров 8 и 9, вторым входом счетчика 16 и вторым входом счетчика 17 по модулю два. Группа выходов счетчика 16 соединена с группой входов дешифратора 15, выход которого соединен с первым входом элемента И 18, второй вход которого соединен с выходом счетчика 17 по модулю два. Вход согласующего трансформатора 1 является входом 19 устройства. Группа выходов сдвигового регистра 14 является группой 20 выходов устройства, выход элемента И 18 является выходом 21 устройства.

Вход согласующего трансформатора 1 является входом 19 устройства. Группа выходов сдвигового регистра 14 является группой 20 выходов устройства, выход элемента И 18 является выходом 21 устройства.

Устройство преобразования последовательного кода в параллельный работает следующим образом.

В исходном состоянии при включении питания и отсутствии сигналов на входах элементов НЕ 4 и 5 таймер 7 принудительно удерживает D-триггеры 8 и 9, а также счетчики 16 и 17 в состоянии установки в ноль. Информационное слово подается на вход 19 устройства последовательно бит за битом, начиная с первого разряда слова. При этом входные сигналы определяются тремя уровнями напряжения: +U, -U, 0. Информация в течение бит-интервала Т представляется двухполярными импульсами (фиг.2, а). Информационный бит «1» кодируется как последовательное состояние уровней +U, -U, 0. Информационный бит «0» кодируется как последовательное состояние уровней -U, +U, 0. Двухполярный импульс бита подается на вход согласующего трансформатора 1, который формирует на его первом выходе прямое значение напряжения входного бита, а на втором выходе — инверсное значение напряжений входного бита (фиг.2, б, в). Эти напряжения подаются на входы соответствующих однополупериодных выпрямителей 2 и 3, которые формируют на своих выходах однополярные импульсы длительностью Т/3, причем импульс на выходе первого однополупериодного выпрямителя 2 соответствует положительной части входного бита, а импульс на выходе однополупериодного выпрямителя 3 — отрицательной части бита (фиг.2, г, д). С выходов однополупериодных выпрямителей 2 и 3 импульсы поступают на входы соответствующих элементов НЕ 4 и 5, выходые сигналы которых приведены на фиг. 2, е, ж соответственно. Эти сигналы поступают на соответствующие входы таймера 7 и переводят его на время, большее Т/3, в состояние, при котором его выходной сигнал (фиг.2, з) разрешает прием входных информационных сигналов D-триггерам 8 и 9, счетчикам 16 и 17.

Двухполярный импульс бита подается на вход согласующего трансформатора 1, который формирует на его первом выходе прямое значение напряжения входного бита, а на втором выходе — инверсное значение напряжений входного бита (фиг.2, б, в). Эти напряжения подаются на входы соответствующих однополупериодных выпрямителей 2 и 3, которые формируют на своих выходах однополярные импульсы длительностью Т/3, причем импульс на выходе первого однополупериодного выпрямителя 2 соответствует положительной части входного бита, а импульс на выходе однополупериодного выпрямителя 3 — отрицательной части бита (фиг.2, г, д). С выходов однополупериодных выпрямителей 2 и 3 импульсы поступают на входы соответствующих элементов НЕ 4 и 5, выходые сигналы которых приведены на фиг. 2, е, ж соответственно. Эти сигналы поступают на соответствующие входы таймера 7 и переводят его на время, большее Т/3, в состояние, при котором его выходной сигнал (фиг.2, з) разрешает прием входных информационных сигналов D-триггерам 8 и 9, счетчикам 16 и 17.

Кроме того, сигнал с выхода первого элемента НЕ 4 поступает на первые входы первого и второго элементов ИЛИ-НЕ 6 и 10, а сигнал с выхода второго элемента НЕ 5 поступает на входы третьего и четвертого элементов ИЛИ-НЕ 11 и 12. На второй вход первого элемента ИЛИ-НЕ 6 поступает потенциал логического «0» с прямого выхода D-триггера 8 (фиг.2, и), а на другой вход третьего элемента ИЛИ-НЕ 11 поступает потенциал логического «0» с прямого выхода D-триггера 9 (фиг. 2, к). На выходах элементов ИЛИ-НЕ 6 и 11 происходит выделение сигналов, управляющих S-входами D-триггеров 9 и 8 (фиг.2, л, м) соответственно. При поступлении бита, соответствующего логической «1», первым формируется сигнал, поступающий на S-вход D-триггера 9, что приводит к его синхронному переключению в состояние логической «1». Это переключение запрещает прохождение импульса на S-вход D-триггера 8. Переключение D-триггера 9 разрешает прохождение импульса с первого входа четвертого элемента ИЛИ-НЕ 12 на его выход (фиг. 2, н) и далее через соответствующий вход пятого элемента ИЛИ-НЕ 13 на его выход (фиг.2, п). Сигнал с выхода элемента ИЛИ-НЕ 13, воздействуя на синхронные входы D-триггеров 8 и 9 и сдвигового регистра 14, обеспечивают запись логической «1» в регистр 14 и сброс D-триггеров 8 и 9 в исходное нулевое состояние.

2, н) и далее через соответствующий вход пятого элемента ИЛИ-НЕ 13 на его выход (фиг.2, п). Сигнал с выхода элемента ИЛИ-НЕ 13, воздействуя на синхронные входы D-триггеров 8 и 9 и сдвигового регистра 14, обеспечивают запись логической «1» в регистр 14 и сброс D-триггеров 8 и 9 в исходное нулевое состояние.

При поступлении на вход устройства бита информации, соответствующего логическому «0», первым формируется сигнал, поступающий на S-вход D-триггера 8, что приводит к его переключению в состояние логической «1». Это переключение запрещает прохождение импульса на S-вход D-триггера 9 и разрешает прохождение импульса с первого входа второго элемента ИЛИ-НЕ 10 на его выход (фиг.2, о) и далее через соответствующий вход пятого элемента ИЛИ-НЕ 13 на его выход (фиг.2, п). Сигнал с выхода элемента ИЛИ-НЕ 13 обеспечивает запись логического «0» в сдвиговый регистр 14 и сброс D-триггеров 8 и 9 в исходное нулевое состояние.

Таким образом происходит накопление и сдвиг кодовых импульсов в сдвиговом регистре 14.

Кроме того, импульсы с выхода пятого элемента ИЛИ-НЕ 13 подаются на счетный вход счетчика 16. Состояние счетчика 16 декодируется дешифратором 15. При достижении в счетчике 16 числа, разного числу бит входного слова, на выходе дешифратора 15 фоpмируется сигнал, соответствующий приему всех бит входного слова. Этот сигнал подается на соответствующий вход элемента И 18.

Информационные импульсы с инверсного выхода D-триггера 9 подаются на счетный вход счетчика 17 по модулю два. При поступлении в течение информационного слова нечетного числа логических «1», конечное состояние счетчика 17 будет единичным, что соответствует правильному приему слова. При поступлении в течение информационного слова четного числа логических «1», конечное состояние счетчика 17 будет нулевым, что соответствует неправильному приему слова.

При наличии сигналов исправности с выходов счетчика 17 и дешифратора 15, поступающих на соответствующие входы элемента И 18, на его выходе формируется сигнал исправности, который подается на выход 21 устройства и свидетельствует о правильности преобразования кода. Пользователь считывает параллельный код с выходов 20 сдвигового регистра 14 при наличии сигнала на выходе элемента И 18.

Пользователь считывает параллельный код с выходов 20 сдвигового регистра 14 при наличии сигнала на выходе элемента И 18.

По окончании преобразования входного слова отсутствие информации на входе 19 устройства в течение времени Т/3 переводит таймер 7 в состояние, при котором он устанавливает в ноль D-триггеры 8, 9, счетчики 16 и 17. Устройство готово к преобразованию следующего слова.

При наличии ошибок, сбоев, потери бит и т.п. счетчики 16 и 17 не формируют сигналы правильности преобразования, элемент И 18 остается закрытым и сигнал исправности на выходе 21 устройства отсутствует.

Формула изобретения

УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ, содержащее согласующий трансформатор, вход которого является входной шиной, а первый и второй выходы соединены с входами соответственно первого и второго однополупериодных выпрямителей, счетчик и счетчик по модулю два, счетные входы которых объединены соответственно с C- и D-входами сдвигового регистра, инверсные выходы которого являются первой выходной шиной устройства, второй выходной шиной которого является выход элемента И, первый и второй входы которого соединены соответственно с выходом счетчика по модулю два и выходом дешифратора, входы которого соединены с соответствующими выходами счетчика, вход установки в «0» которого объединен с одноименным входом счетчика по модулю два и подключен к выходу таймера, отличающееся тем, что в него введены два элемента НЕ, пять элементов ИЛИ — НЕ, два D-триггера, R-входы которых соединены с выходом таймера, выход первого однополупериодного выпрямителя через первый элемент НЕ соединен с первым входом первого элемента ИЛИ — НЕ, первым входом таймера и первым входом второго элемента ИЛИ — НЕ, второй вход которого объединен с D-входом сдвигового регистра и соединен с инверсным выходом первого D-триггера, прямой выход которого соединен с вторым входом первого элемента ИЛИ — НЕ, выход которого соединен с S-входом второго D-триггера, прямой выход которого соединен с первым входом третьего элемента ИЛИ — НЕ, выход которого соединен с S-входом первого D-триггера, выход второго однополупериодного выпрямителя через второй элемент НЕ соединен с вторым входом третьего элемента ИЛИ — НЕ, вторым входом таймера и первым входом четвертого элемента ИЛИ — НЕ, второй вход которого соединен с инверсным выходом второго D-триггера, C-вход которого объединен с C-входом первого D-триггера, счетным входом счетчика и подключен к выходу пятого элемента ИЛИ — НЕ, первый и второй входы которого соединены с выходами соответственно второго и четвертого элементов ИЛИ — НЕ.

РИСУНКИ

Рисунок 1, Рисунок 2

Преобразования кодов из параллельного формата в последовательный и из последовательного в параллельный

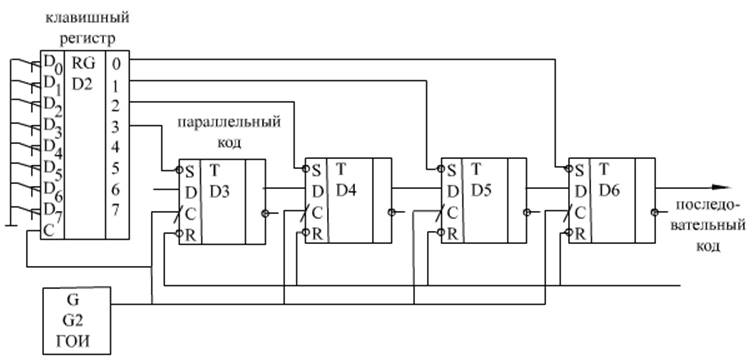

Часть 1. “Преобразования кода из параллельного формата в последовательный”

Цель работы – построение и изучение схем преобразователей параллельного кода в последовательный с использованием мультиплексоров и регистров сдвига.

1. Общие сведения

При обработке информации в вычислительный устройствах сообщения, как правило, представляются в параллельном коде, позволяющем минимизировать время передачи и обработки. При передаче информации на значительные расстояния, когда существенной становится стоимость линий связи, необходимо минимизировать число каналов связи. Это достигается путем преобразования на передающей стороне закодированного сообщения из параллельного формата в последовательный и передачи по каналу связи кодовой комбинации в последовательном коде. Интервал времени, необходимый для передачи сообщения, становится значительно большим по сравнению со временем передачи того же сообщения, представленным в параллельном коде, но вместо N каналов для передачи N-разрядного кода часто достаточно одного канала.

Для выполнения операции преобразования параллельного формата в последовательный применяются параллельнопоследовательные преобразователи на основе мультиплексоров или регистров сдвига. Принцип действия параллельнопоследовательных преобразователей состоит в одновременной подачи на их входы всех элементов кода с последующим поочередным считыванием каждого элемента. Особенностью этих преобразователей является то, что элементы выходного кода соответствуют в явном виде элементам входного кода, а изменяются лишь их пространственно-временные соотношения.

2. Описание лабораторной установки

Лабораторная работа выполняется с использованием сменной панели “Преобразователи параллельного кода в последовательный” лабораторного стенда ЛАТ-01. На этой панели размещены:

• тумблеры “20”…“215” для формирования входного двоичного

кода;

• кнопка “Пуск”, тумблеры “цикл/спор”, “1 Гц / 1 кГц”, “(руч / авт)”

– органы управления работой генератора;

• тумблеры “вкл”, “20”…“23”, светодиоды “1-2-4-8” – органы управления и индикации работы счетчика СТ;

• светодиоды “20”…“215” для визуального контроля состояния

выходов регистра индикации;

• кнопка “сброс” для установки в “нулевое” состояние регистра индикации;

• коммутационные гнезда;

• графические изображения тумблеров, кнопок, мультиплексоров, регистров, генератора, счетчика, регистра индикации, логических элементов, необходимых для сборки схем преобразователей параллельного кода в последовательный.

Узел мультиплексоров состоит из:

• селектора-мультиплексора на 16 каналов со стробированием

К155КП1;

• двух сдвоенных селекторов-мультиплексоров на 4 канала со стробированием К155КП2;

• двух коммутаторов 8×1 без стробирования К155КП5;

• двух коммутаторов 8×1 со стробированием К155КП7.

Узел регистров сдвига состоит из:

• четырех четырехразрядных универсальных регистров сдвига

• двух восьмиразрядных реверсивных регистров сдвига

К155ИР13.

Набор логических элементов и элементы задержки, необходимые при построении схем преобразователей, реализованы на интегральных микросхемах серии К155.

Формирование сигналов управления мультиплексорами и регистрами осуществляется генератором и счетчиком с соответствующими органами управления.

Регистр индикации образован из двух восьмиразрядных регистров сдвига К155ИР13.

3. Порядок выполнения работы

3.1. Разработать и собрать схему преобразования кодовой комбинации из параллельного формата в последовательный в ручном и автоматическом режимах управления с использованием мультиплексора MUX. Разрядность кодовой комбинации задается преподавателем.

Разрядность кодовой комбинации задается преподавателем.

3.2. Задание кодовой комбинации требуемой разрядности выполняется тумблерами “20”…“215”. Для удобства визуального контроля процесса преобразования этой комбинации в последовательный формат и её отображения в регистре индикации в первом и последнем разрядах следует установить уровень логической “1”.

3.3. В качестве входных сигналов адресной части мультиплексора MUX использовать выходные сигналы двоичного счетчика

СТ.

3.4. Модуль счета счетчика СТ определяется разрядностью преобразуемого кода и задается тумблерами “20”…“23”.

3.5. Тумблером “(руч / авт)” генератор G переводится в ручной или автоматический режим управления. В ручном режиме каждый импульс на выходе генератора G формируется нажатием кнопки “Пуск”. В автоматическом режиме однократное нажатие кнопки “Пуск” формирует последовательность импульсов на выходе генератора G. Длительность этой последовательности, то есть число импульсов, которое она будет содержать, определяется заданным модулем счета счетчика СТ.

3.6. Тумблером “1 Гц / 1 кГц” задается частота следования импульсов на выходе С генератора G. Для ручного режима 1 кГц, для автоматического – 1 Гц.

3.7. Ограничение числа повторений сформированной последовательности импульсов генератора G задается тумблером “Цикл / Спор”. В спорадическом режиме эта последовательность генерируется только один раз. В циклическом режиме число повторений этой последовательности не ограничено.

3.8. Синхронизация сигналов записи и сдвига разрядов кода, поступающего в гнездо “Вход” регистра индикации, осуществляется подачей импульсов генератора G на вход “Синхр” регистра индикации. Синхронизация может выполняться либо по переднему С,

либо по заднему С фронту выходных импульсов генератора.

3.9. Перед началом каждого нового цикла преобразования кода кнопкой “Сброс” следует обнулять содержимое регистра индикации.

3.10. При использовании в качестве параллельнопоследовательного преобразователя 16-канального селекторамультиплексора обязательно выполнить необходимое подключение его стробирующего входа “S”.

3.11. Разработать и собрать схему преобразования кода из параллельного формата в последовательный с использованием регистров сдвига RG в ручном и автоматическом режимах управления. Разрядность кода задается преподавателем.

3.12. Для формирования кода в параллельном формате, генерации необходимой импульсной последовательности, хранения и отображения кода в последовательном формате использовать элементы управления согласно пунктам 1.1., 1.3. – 1.8.

3.13. Составить временные диаграммы работы преобразователей по пунктам 1 и 2.

Содержание отчета

1. Название отчета.

2. Схемы, временные диаграммы.

3. Выводы по работе.

Контрольные вопросы

1. С какими целями осуществляется преобразование параллельных кодов в последовательные?

2. На основе каких типовых логических элементов возможна реализация преобразователей параллельного кода в последовательный?

3. Объясните принцип действия параллельно последовательного преобразователя, построенного на мультиплексоре.

4. Объясните принцип действия параллельно последовательного преобразователя, построенного на регистре сдвига.

5. Приведите примеры практического изменения параллельно-последовательных преобразователей.

Часть 2. “Преобразования кода из последовательного формата в параллельный”

Цель работы – построение и изучение схем преобразователей последовательного кода в параллельный с использованием демультиплексоров и регистров сдвига.

1. Общие сведения

Минимальное время передачи и обработки информации в вычислительных устройствах достигается для сообщений, представленных в параллельных кодах. В тех случаях, когда источники сообщений находятся на значительном удалении от приемников, передача осуществляется в последовательных кодах. В этой связи на приемной стороне системы необходимо осуществлять преобразование сообщений из последовательного формата в параллельный. Для выполнения таких операций применяются преобразователи последовательно-параллельного типа. Принцип действия последовательно-параллельных преобразователей заключается в последовательной записи передаваемого кода по одному входному каналу синхронно с тактовыми импульсами и в последующем одновременном считывании всей принятой кодовой комбинации по выходным каналам, число которых соответствует разрядности передаваемого кода. Схемы последовательно-параллельных преобразователей могут быть реализованы на основе демультиплексоров или регистров сдвига.

Принцип действия последовательно-параллельных преобразователей заключается в последовательной записи передаваемого кода по одному входному каналу синхронно с тактовыми импульсами и в последующем одновременном считывании всей принятой кодовой комбинации по выходным каналам, число которых соответствует разрядности передаваемого кода. Схемы последовательно-параллельных преобразователей могут быть реализованы на основе демультиплексоров или регистров сдвига.

2. Описание лабораторной установки

Лабораторная работа выполняется с использованием сменной панели “Преобразователи последовательного кода в параллельный” лабораторного стенда ЛАТ-01. На этой панели размещены:

• светодиоды “20”…“215” для визуального наблюдения за работой схем преобразователей;

• коммутационные гнезда;

• графические изображения счетчика, демультиплексора, RSтриггеров, регистров сдвига, элементов задержки и логических элементов, светодиодов с ограничивающими резисторами.

Основными элементами, необходимыми для реализации преобразователей, являются:

• четырехразрядный двоично-десятичный реверсивный счетчик

К155ИЕ5;

• дешифратор-демультиплексор 4×16 К155ИД3;

• четыре четырехразрядных универсальных регистра сдвига

К155ИР1;

• четыре восьмиразрядных реверсивных регистра сдвига

К155ИР13;

• набор логических элементов из серии интегральных микросхем

К155.

Коммутация различных элементов в необходимых сочетаниях для сборки схем преобразователей осуществляется установкой внешних соединителей в коммутационные гнезда.

3. Порядок выполнения работы

3.1. Разработать и собрать схему преобразования кодовой комбинации из последовательного формата в параллельный в ручном и автоматическом режимах управления с использованием дешифратора-демультиплексора DC. Разрядность кодовой комбинации задается преподавателем.

3.2. Отдельным проводом соединить одно из гнезд (┴) панели преобразователей параллельного кода в последовательный с

одним из аналогичных гнезд (┴) панели преобразователей последовательного кода в параллельный.

3.3. Последовательная кодовая комбинация заданной разрядности формируется на панели параллельно-последовательных преобразователей. Для этого любой из тумблеров “20”…“23” соединить с гнездом “Вход” регистра индикации, а выход С генератора импульсов G соединить с гнездом “Синхр” регистра индикации. Тумблер “(руч / авт)” перевести в положение “(руч)”. Тумблер “1 Гц /

Тумблер “(руч / авт)” перевести в положение “(руч)”. Тумблер “1 Гц /

1 кГц” перевести в положение 1 кГц. Последовательно устанавливая выбранный тумблер задания кодовой комбинации в желаемое положение “0” или “1” и затем нажимая кнопку “Пуск”, записать в регистр индикации требуемый код. Для удобства визуального контроля процесса преобразования в первом и последнем разрядах задаваемого кода следует установить уровень логической “1”. Если записанная кодовая комбинация имеет меньшую разрядность, чем регистр индикации, то, предварительно переведя тумблер задания в положение “0”, кнопкой “Пуск” сдвинуть кодовую комбинацию так, чтобы её крайний правый разряд был записан в старшем разряде регистра индикации.

3.4. Обнулить счетчик СТ и в соответствии с разрядностью преобразуемого кода, тумблерами “20”…“23” задать модуль счета счетчика СТ.

3.5. Последовательный код со старшего разряда регистра индикации подается на вход дешифратора-демультиплексора DC панели последовательно-параллельного преобразования, в котором преобразуется в код параллельного формата.

3.6. Синхронизация работы регистра индикации и дешифратора-демультиплексора осуществляется импульсами генератора G с помощью счетчика СТ2 панели последовательно-параллельного преобразования.

3.7. Полученный параллельный код поразрядно переписывается в регистр, образованный блоком триггеров Т.

3.8. Содержимое блока триггеров Т индицируется светодиодами “20”…“23”.

3.9. Тумблером “(руч/авт)” генератор G переводится в ручной или автоматический режим управления. В ручном режиме каждый импульс на выходе генератора G формируется нажатием кнопки “Пуск”. В автоматическом режиме однократное нажатие кнопки “Пуск” формирует последовательность импульсов на выходе генератора G. Длительность этой последовательности, то есть число импульсов, которое она будет содержать, определяется заданным модулем счета счетчика СТ.

3.10. Тумблером “1 Гц / 1 кГц” задается частота следования импульсов на выходе С генератора G. Для ручного режима 1 кГц, для автоматического – 1 Гц.

3.11. Ограничение числа повторений сформированной последовательности импульсов генератора G задается тумблером “Цикл / Спор”. В спорадическом режиме эта последовательность генерируется только один раз. В циклическом режиме число повторений этой последовательности не ограничено.

3.12. Разработать и собрать схему преобразования кода из последовательного формата в параллельный с использованием регистров сдвига RG в ручном и автоматическом режимах управления. Разрядность кода задается преподавателем.

3.13. Для формирования кода в последовательном формате, генерации необходимой импульсной последовательности, хранения и отображения кода в параллельном формате использовать элементы управления согласно пунктам 1.1.1.3., 1.6. 1.10.

3.14. Составить временные диаграммы работы преобразователей по пунктам 1 и 2.

Содержание отчета

1. Название отчета.

2. Схемы, временные диаграммы.

3. Выводы по работе.

Контрольные вопросы

1. С какими целями осуществляется преобразование последовательных кодов в параллельные?

2. На основе каких типовых логических элементов возможна реализация преобразователей последовательного кода в параллельный?

На основе каких типовых логических элементов возможна реализация преобразователей последовательного кода в параллельный?

3. Объясните принцип действия последовательно параллельного преобразователя, построенного на демультиплексоре.

4. Объясните принцип действия последовательно параллельного преобразователя, построенного на регистрах сдвига.

5. Приведите примеры практического применения последовательно параллельных преобразователей.

Материал взят из книги Системы преобразования, передачи и отображения информации в транспортной телематике (В.Г. Соколов)

В чем разница между последовательной и параллельной обработкой в компьютерной архитектуре

24 февраля 2019 г.

от Lithmee

Чтение через 4 мин.

Основное различие между последовательной и параллельной обработкой в компьютерной архитектуре заключается в том, что последовательная обработка выполняет одну задачу за раз, а параллельная обработка выполняет несколько задач одновременно.

Компьютерная архитектура определяет функциональность, организацию и реализацию компьютерной системы. В нем объясняется, как устроена компьютерная система и с какими технологиями она совместима. Процессор является одним из важнейших компонентов компьютерной системы. Он выполняет инструкции и выполняет поставленные перед ним задачи. Существует два основных типа обработки: последовательная и параллельная обработка.

Ключевые области

1. Что такое последовательная обработка в компьютерной архитектуре

– Определение, функциональность

2. Что такое параллельная обработка в компьютерной архитектуре

– Определение, функциональность

3. Что такое разница между последовательной и параллельной обработкой в архитектуре компьютера

– Сравнение ключевых различий

Ключевые термины

Архитектура компьютера, параллельная обработка, последовательная обработка

Что такое последовательная обработка в компьютерной архитектуре

При последовательной обработке процессор выполняет одну задачу за раз. После этого он последовательно выполняет другие задачи. Операционная система выполняет множество программ, и каждая из них имеет несколько задач. Процессор должен выполнить все эти задачи, но он выполняет одну задачу за раз. Остальные задачи ждут в очереди, пока процессор не завершит текущую задачу. Другими словами, все задачи обрабатываются последовательно. Следовательно, этот тип обработки называется последовательной обработкой или последовательной обработкой. Такие машины, как Pentium 3 и Pentium 4, выполняют последовательную обработку.

После этого он последовательно выполняет другие задачи. Операционная система выполняет множество программ, и каждая из них имеет несколько задач. Процессор должен выполнить все эти задачи, но он выполняет одну задачу за раз. Остальные задачи ждут в очереди, пока процессор не завершит текущую задачу. Другими словами, все задачи обрабатываются последовательно. Следовательно, этот тип обработки называется последовательной обработкой или последовательной обработкой. Такие машины, как Pentium 3 и Pentium 4, выполняют последовательную обработку.

Мы можем понять функциональность последовательной обработки, используя следующую аналогию. Предположим, супермаркет с несколькими очередями и только с одним кассиром. Кассир завершает выставление счетов за продукты одного покупателя, а затем переходит к другому покупателю. Он выполняет выставление счетов один за другим.

Что такое параллельная обработка в компьютерной архитектуре

В параллельной обработке задействовано несколько процессоров. Каждый процессор выполняет возложенные на него задачи одновременно. Процессоры используют шину для связи друг с другом и для доступа к основной памяти. Каждый процессор работает со своими локальными данными. Поскольку процессоры работают независимо, отказ одного процессора не влияет на функциональность другого процессора. Таким образом, параллельная обработка увеличивает пропускную способность, а также повышает надежность. Большинство современных компьютеров поддерживают параллельную обработку для повышения производительности.

Каждый процессор выполняет возложенные на него задачи одновременно. Процессоры используют шину для связи друг с другом и для доступа к основной памяти. Каждый процессор работает со своими локальными данными. Поскольку процессоры работают независимо, отказ одного процессора не влияет на функциональность другого процессора. Таким образом, параллельная обработка увеличивает пропускную способность, а также повышает надежность. Большинство современных компьютеров поддерживают параллельную обработку для повышения производительности.

Мы можем понять функциональность параллельной обработки, используя следующий пример. В супермаркете есть несколько очередей, и для каждой очереди есть кассир. Каждый кассир выставляет счета покупателям в свою очередь.

Разница между последовательной и параллельной обработкой в компьютерной архитектуре

Определение

Последовательная обработка — это тип обработки, при котором одна задача выполняется за раз, а все задачи выполняются процессором в определенной последовательности. Параллельная обработка — это тип обработки, при котором несколько задач выполняются одновременно разными процессорами. Таким образом, это фундаментальное различие между последовательной и параллельной обработкой.

Параллельная обработка — это тип обработки, при котором несколько задач выполняются одновременно разными процессорами. Таким образом, это фундаментальное различие между последовательной и параллельной обработкой.

Количество процессоров

Основное различие между последовательной и параллельной обработкой заключается в том, что при последовательной обработке используется один процессор, а при параллельной — несколько.

Производительность

Таким образом, производительность параллельной обработки выше, чем при последовательной обработке.

Рабочая нагрузка

При последовательной обработке рабочая нагрузка процессора выше. Однако при параллельной обработке нагрузка на процессор ниже. Таким образом, это важное различие между последовательной и параллельной обработкой.

Передача данных

Более того, при последовательной обработке данные передаются в побитовом формате. Однако при параллельной обработке данные передаются в байтовой форме (8 бит).

Требуемое время

Затрачиваемое время также является разницей между последовательной и параллельной обработкой. То есть; последовательная обработка требует больше времени, чем параллельная обработка для выполнения задачи.

Стоимость

Кроме того, параллельная обработка является более дорогостоящей, чем последовательная, поскольку при ней используется несколько процессоров.

Заключение

В компьютерной системе существует два типа обработки: последовательная и параллельная. Основное различие между последовательной и параллельной обработкой в компьютерной архитектуре заключается в том, что последовательная обработка выполняет одну задачу за раз, а параллельная обработка выполняет несколько задач одновременно. Короче говоря, производительность параллельной обработки выше, чем у последовательной.

Код:

1. «Что такое последовательный процессор? — Определение из Techopedia». Techopedia.com, доступно здесь.

2. «Что такое компьютерная архитектура? — Определение из Techopedia». Techopedia.com, доступно здесь.

Techopedia.com, доступно здесь.

3. «Архитектура компьютера». Википедия, Фонд Викимедиа, 31 января 2019 г., доступно здесь.

4. «Что такое параллельная обработка? – Определение от WhatIs.com». SearchDataCenter, доступно здесь.

Изображение любезно предоставлено:

1. «Технологическая процессорная плата компьютерного процессора» (общедоступное достояние CC0) через Max Pixel

Об авторе: Литми

Литми имеет степень бакалавра наук в области разработки компьютерных систем и готовится к получению степени магистра компьютерных наук. Она страстно любит делиться своими знаниями в области программирования, науки о данных и компьютерных систем.

Просмотреть все сообщения

Вам также могут понравиться эти

Сравнительное исследование последовательной и параллельной обработки в Python | от Савон | Аналитика Vidhya

Photo by Shahadat Rahman on Unsplash

Ampere, полупроводниковый стартап, основанный и возглавляемый бывшим исполнительным директором Intel Рене Джеймсом, представил новый 128-ядерный…

www. crn.com

crn.com

«128 ядер Altra Max вдвое больше, чем у AMD . 64-ядерные процессоры EPYC Rome, но такое же количество потоков, 128, потому что Altra Max не поддерживает гиперпоточность. Но даже без гиперпоточности компания заявила, что может обеспечить «идеальное масштабирование производительности».

Небольшой поиск в гугле дал такой результат. Исходя из этого результата, мы можем справедливо сказать, что рост технологий был экспоненциальным, особенно в последние дни. В настоящее время, как разработчик, мы часто пытаемся максимально использовать наши ресурсы для работы с большим объемом данных. В больших данных сложность мирового пространства больше не является фактором, но тем не менее программистам приходится иметь дело со сложностью времени. Следовательно, концепция последовательной обработки устаревает. Параллельная обработка — это не что иное, как компьютер, использующий более одного ЦП за раз . Прежде чем перейти к техническим терминам, давайте разберемся в теме с точки зрения непрофессионала.

Как мы все знаем, у каждого человека есть пять органов чувств, и когда человек использует два или более органов чувств, они на самом деле являются многопроцессорными. Например, человек слушает песню, а также обедает. Хотя некоторые люди называют это многозадачностью, в технической области определение многозадачности сильно отличается от многопроцессорности.

Так же, как органы чувств в современных компьютерах, доступно несколько ядер. Всякий раз, когда программист пишет код, и этот код выполняется несколькими процессорами параллельно, это называется параллельным программированием.

Часто люди путаются в многопоточности и многопроцессорности, оба метода имеют дело с разными концепциями, например, первый работает с параллелизмом, а второй — с параллельным программированием.

Многопроцессорность и многопоточность По сути, многопоточность создает иллюзию, что все потоки выполняются параллельно. На самом деле эти потоки работают параллельно. Но в случае многопроцессорности код полностью использует ядра ЦП, и каждое ядро работает параллельно. Оба этих метода используются для повышения производительности системы, но в разных ситуациях. Когда код требует большого объема вычислений, используется многопроцессорная обработка, а если код требует большого количества операций ввода-вывода или сетей, то многопоточность является лучшим вариантом из-за его низких накладных расходов.

Оба этих метода используются для повышения производительности системы, но в разных ситуациях. Когда код требует большого объема вычислений, используется многопроцессорная обработка, а если код требует большого количества операций ввода-вывода или сетей, то многопоточность является лучшим вариантом из-за его низких накладных расходов.

Недавно я имел дело с гиперспектральными изображениями для анализа данных дистанционного зондирования. В отличие от изображений RGB (3 канала) он имеет более 100 каналов или спектра. Для проекта я должен очистить спектр изображения от шума. Первоначально использовался линейный метод с циклом for.

для i в диапазоне (padded_X.shape[0]):waveletX[i]=sp.spec_trans(threshold_val,wav_fam,thresh_type,padded_X[i])

здесь каждая полоса последовательно очищается от шума и время, затрачиваемое системой есть:

общее время, затраченное на последовательную обработку: 46,92178964614868

Здесь я имел дело с изображением, которое имело 103 канала. Поскольку небольшой файл (162 МБ) требует такого количества времени для последовательной обработки, мы можем представить, что файл гораздо большего размера (более 1 ГБ) может занять огромное время, если следовать линейному методу. Поэтому я перешел на параллельное программирование. В питоне есть пакет под названием «Многопроцессорность». С помощью этого пакета достигаются параллельные вычисления.

Поскольку небольшой файл (162 МБ) требует такого количества времени для последовательной обработки, мы можем представить, что файл гораздо большего размера (более 1 ГБ) может занять огромное время, если следовать линейному методу. Поэтому я перешел на параллельное программирование. В питоне есть пакет под названием «Многопроцессорность». С помощью этого пакета достигаются параллельные вычисления.

p = mp.Pool(4)# первые 3 аргумента для spec_trans будут wav_fam, threshold_val и thresh_typeworker = partial(spec_trans, wav_fam, threshold_val, thresh_type)suitable_chunksize = calculate_chunksize(4, padded_X.shape[0])transformedX = list (p.imap(рабочий, padded_X, chunksize=suitable_chunksize))

здесь объект создается путем передачи номера процессора, который будет использовать программа. Затем функция передается в функцию imap (точно так же, как функция imap из itertools) с размером фрагмента.

imap имеет преимущество перед картой , когда длина данных слишком велика и не уже список.