Что такое регистры сдвига. Какие бывают основные типы регистров сдвига. Как работают регистры сдвига с последовательным и параллельным вводом/выводом. Для чего применяются регистры сдвига в цифровых схемах. Какие преимущества дает использование регистров сдвига.

Что такое регистры сдвига и зачем они нужны

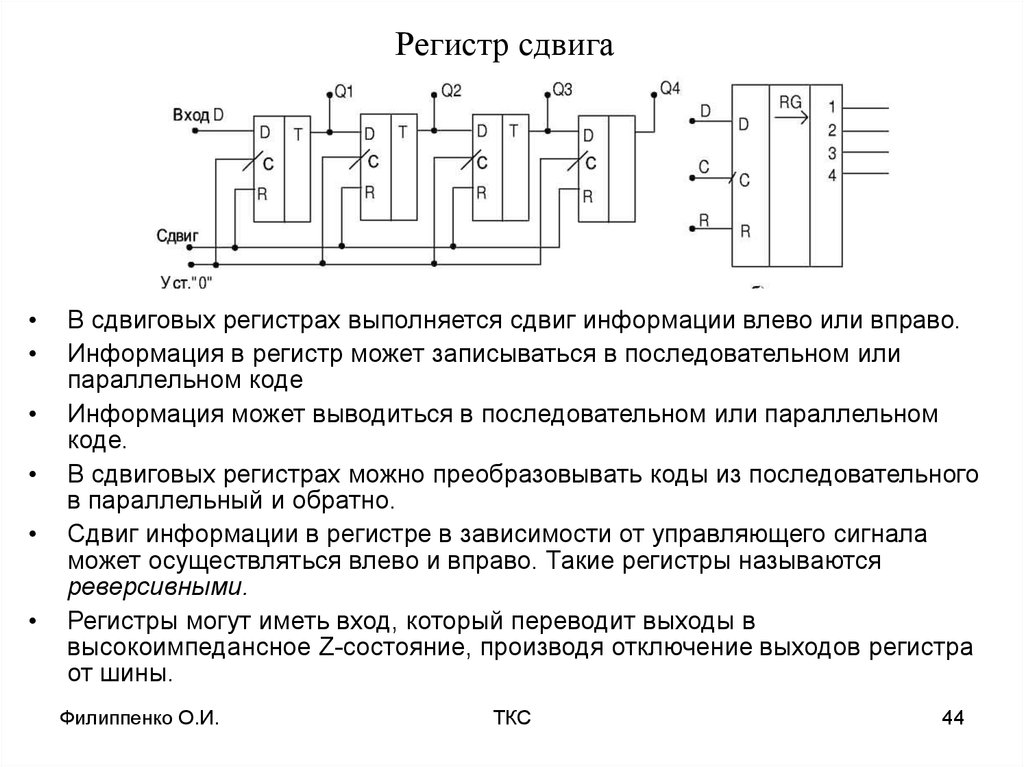

Регистры сдвига — это последовательные цифровые устройства, состоящие из цепочки триггеров, в которых информация может сдвигаться от одного разряда к другому под действием тактовых импульсов. Они выполняют важные функции в цифровых схемах:

- Преобразование последовательного кода в параллельный и наоборот

- Временная задержка сигналов

- Хранение и перемещение многоразрядных двоичных чисел

- Выполнение арифметических и логических операций

Регистры сдвига позволяют эффективно обрабатывать последовательные потоки данных и являются важным элементом многих цифровых устройств.

Основные типы регистров сдвига

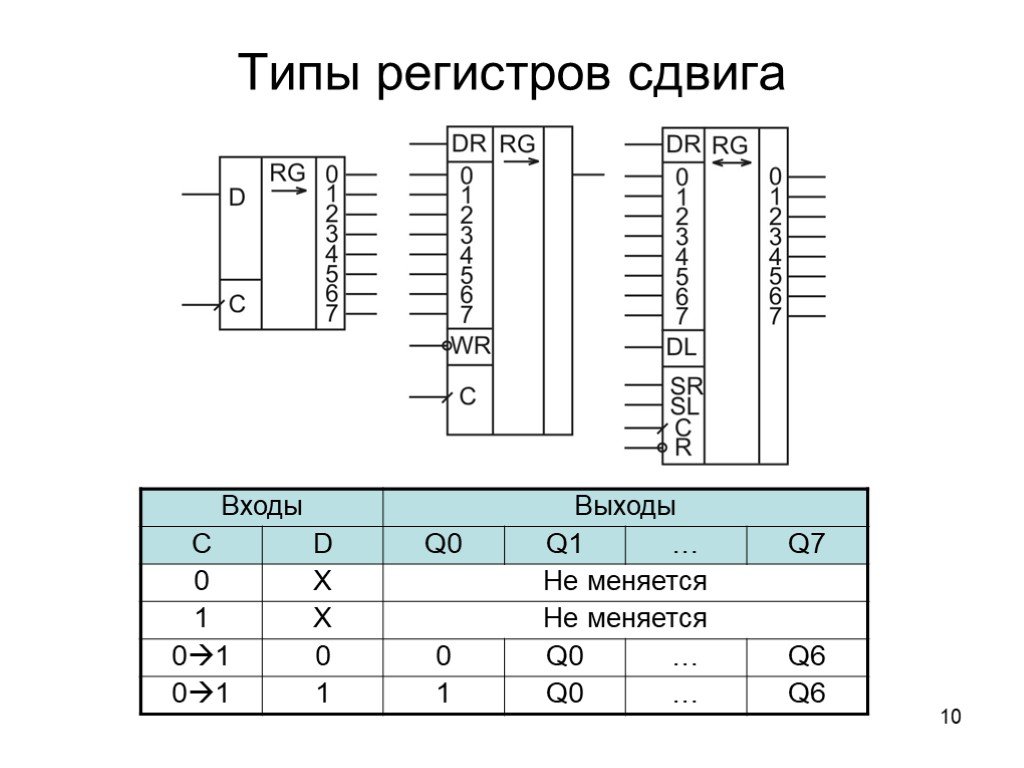

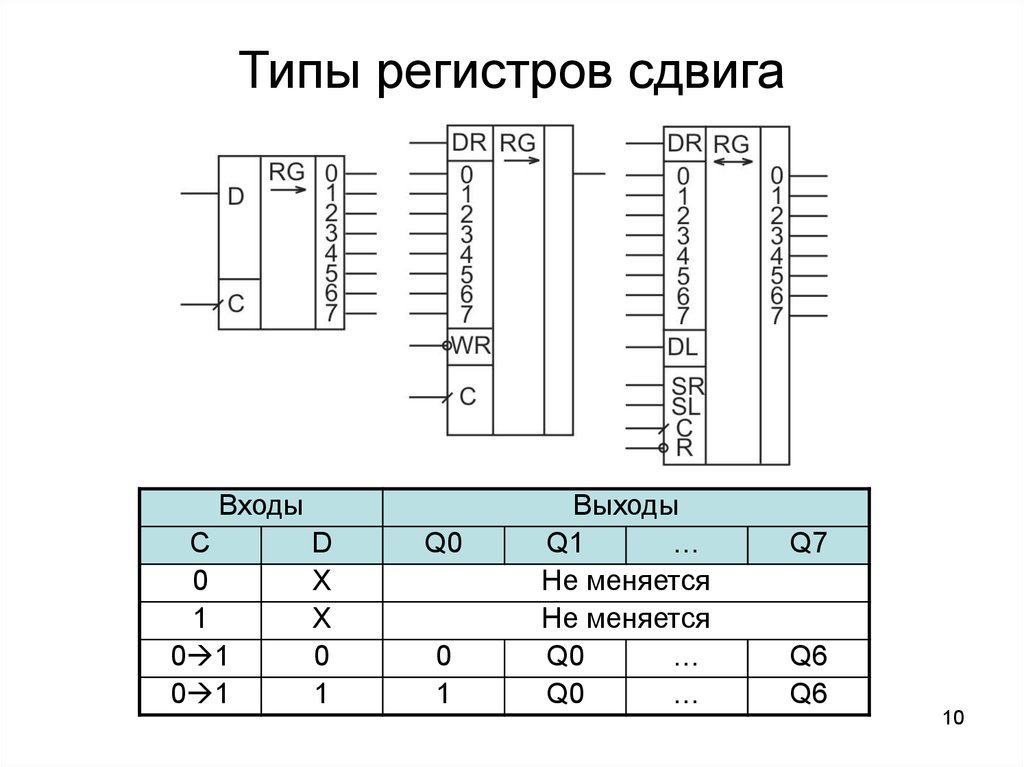

В зависимости от способа ввода и вывода информации выделяют следующие основные типы регистров сдвига:

- Последовательный вход — последовательный выход (SISO)

- Последовательный вход — параллельный выход (SIPO)

- Параллельный вход — последовательный выход (PISO)

- Параллельный вход — параллельный выход (PIPO)

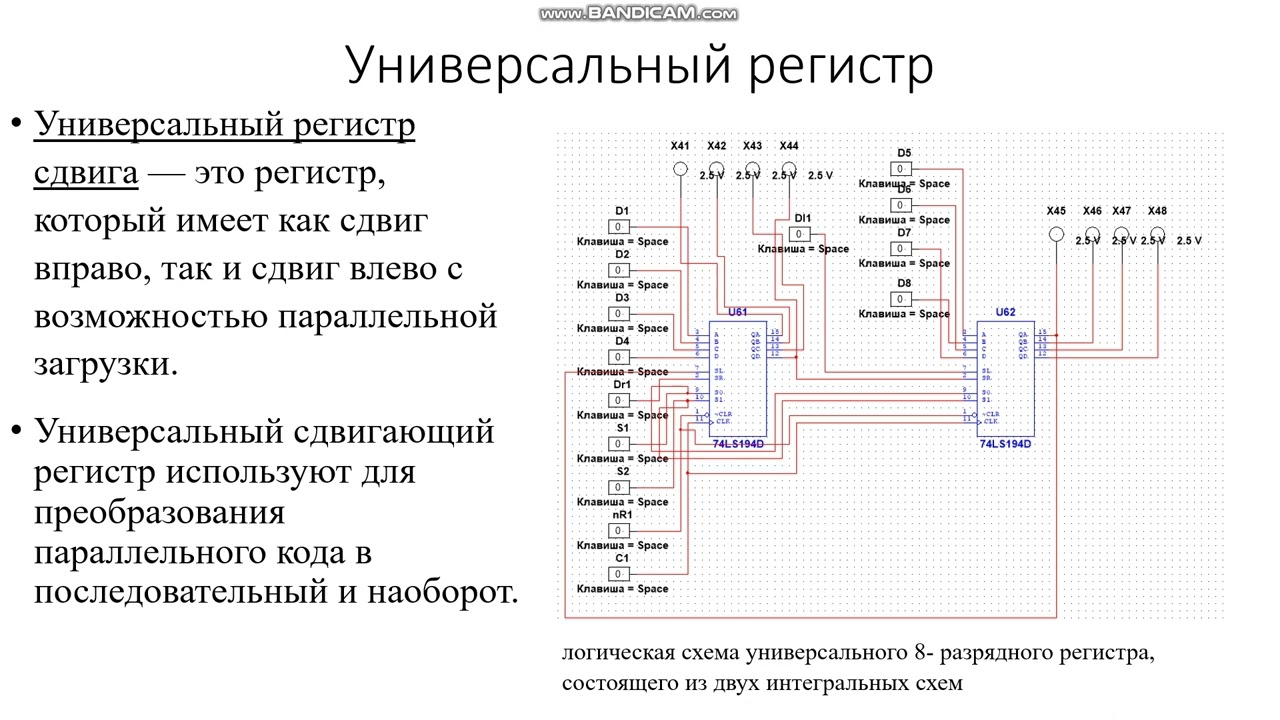

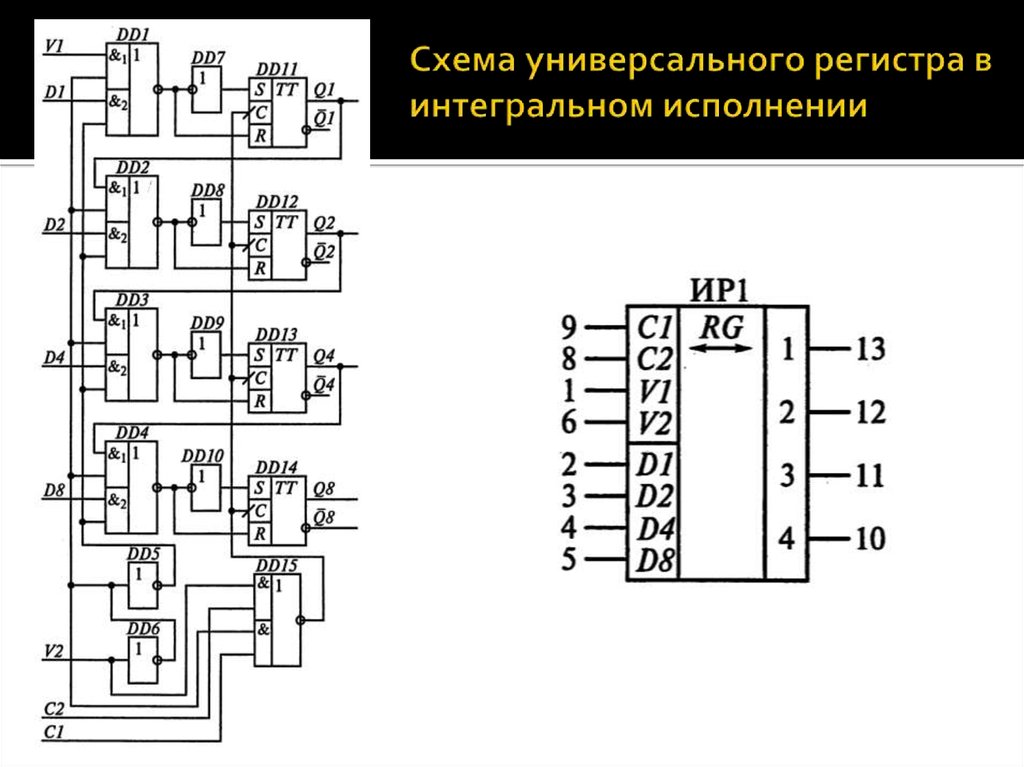

Также существуют двунаправленные и универсальные регистры сдвига, позволяющие выполнять сдвиг в обоих направлениях и комбинировать различные режимы работы.

Как работает регистр сдвига с последовательным входом и выходом

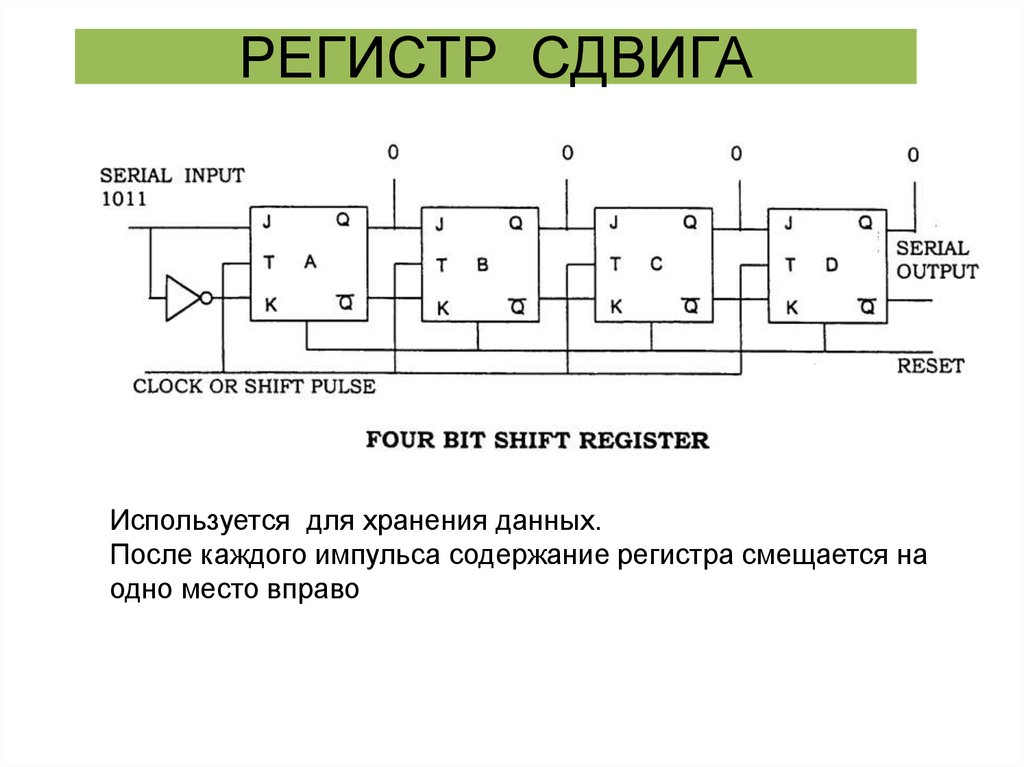

Регистр SISO состоит из цепочки D-триггеров, соединенных последовательно. Принцип его работы:

- На вход первого триггера подаются биты входных данных

- По фронту тактового сигнала происходит сдвиг — каждый триггер принимает значение предыдущего

- Выходом является последний триггер в цепочке

Таким образом, входная последовательность битов проходит через всю цепочку триггеров, создавая задержку. Это позволяет использовать такие регистры в качестве линий задержки.

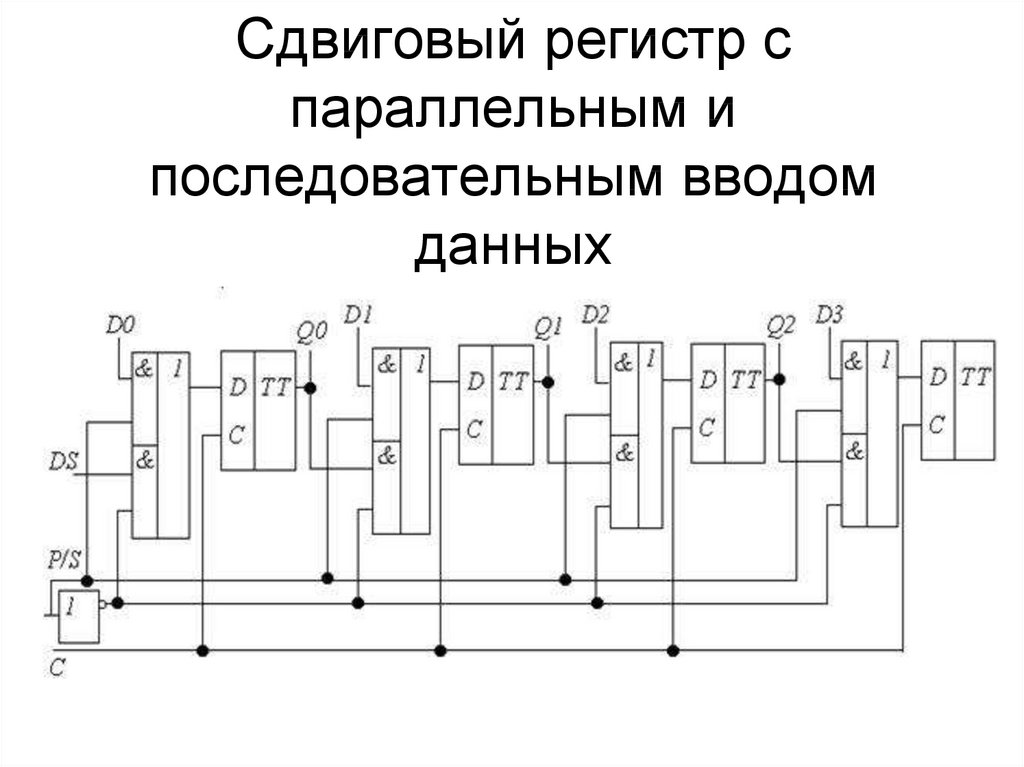

Регистр сдвига с параллельным входом и последовательным выходом

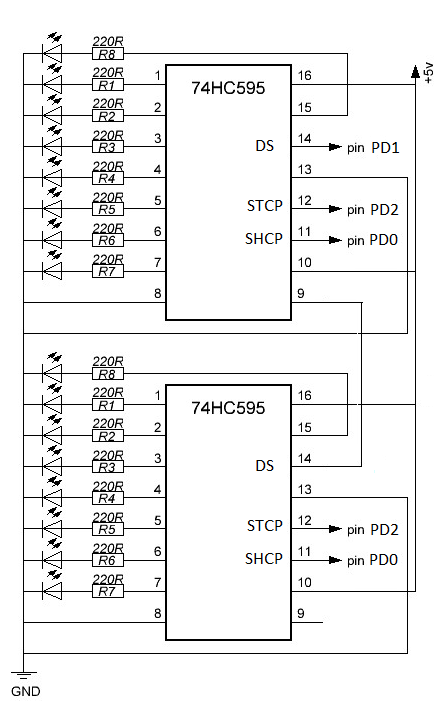

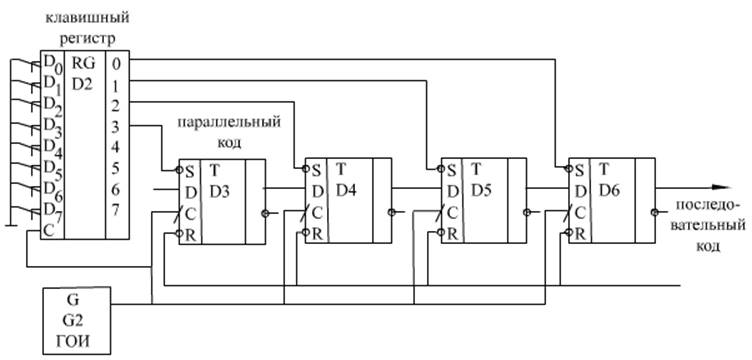

Регистр PISO позволяет загрузить параллельные данные и затем выводить их последовательно. Его работа:

- Параллельные данные загружаются во все разряды одновременно

- Затем включается режим сдвига — данные последовательно выдвигаются через последний разряд

- На выходе формируется последовательный код

Такие регистры применяются для преобразования параллельного кода в последовательный, например, при передаче данных по последовательному интерфейсу.

Применение регистров сдвига в цифровых устройствах

Регистры сдвига широко используются в различных цифровых схемах:

- Генераторы псевдослучайных последовательностей

- Делители частоты

- Преобразователи кодов

- Формирователи временных интервалов

- Цифровые фильтры

- Схемы управления и синхронизации

Они позволяют эффективно выполнять многие операции над последовательными потоками данных, что делает их незаменимыми во многих приложениях цифровой электроники.

Преимущества использования регистров сдвига

Применение регистров сдвига в цифровых схемах дает ряд важных преимуществ:

- Уменьшение количества межсоединений при передаче данных

- Снижение энергопотребления по сравнению с параллельными схемами

- Упрощение синхронизации в последовательных системах

- Возможность легко масштабировать разрядность обрабатываемых данных

- Эффективное выполнение некоторых алгоритмов обработки данных

Это обуславливает широкое применение регистров сдвига в современных цифровых устройствах, несмотря на их кажущуюся простоту.

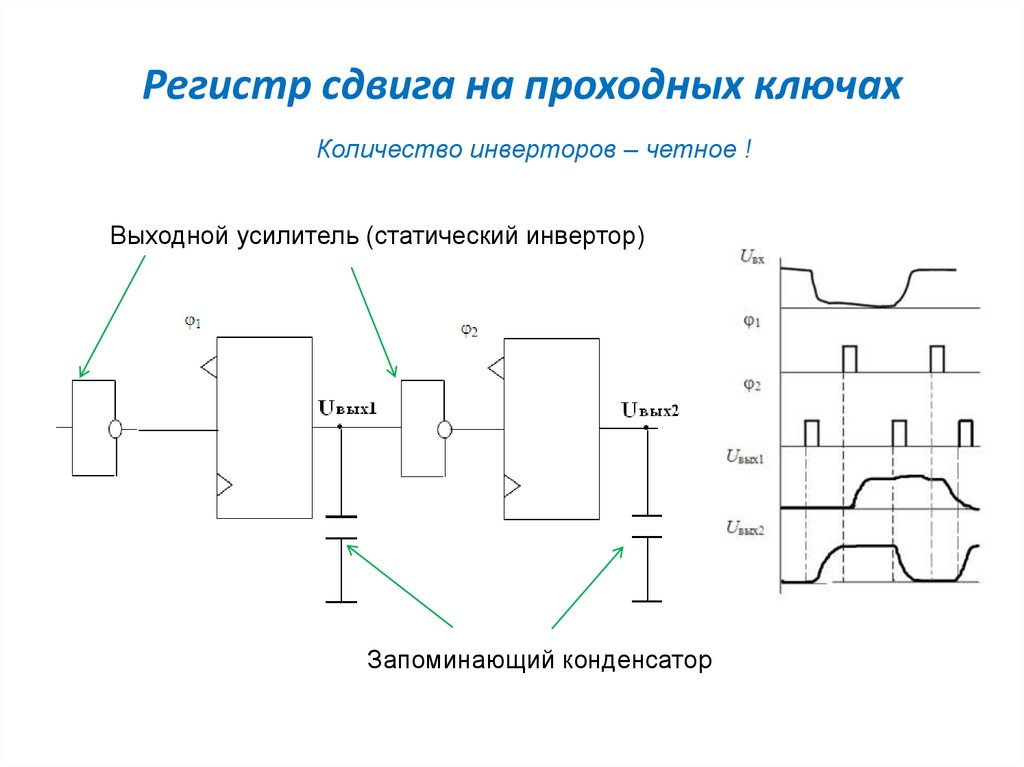

Реализация регистров сдвига на различных элементах

Регистры сдвига могут быть реализованы на различных логических элементах:

- D-триггеры — классическая реализация

- JK-триггеры — позволяют создавать универсальные регистры

- Программируемые логические интегральные схемы (ПЛИС)

- Специализированные микросхемы регистров сдвига

Выбор элементной базы зависит от конкретного применения, требуемого быстродействия, энергопотребления и других параметров разрабатываемого устройства.

Заключение

Регистры сдвига являются важным строительным блоком цифровых схем, позволяющим эффективно обрабатывать последовательные потоки данных. Они находят широкое применение в различных областях цифровой электроники благодаря своей универсальности и эффективности. Понимание принципов работы различных типов регистров сдвига необходимо для разработки современных цифровых устройств.

Принцип работы РСЛОС / Хабр

Введение

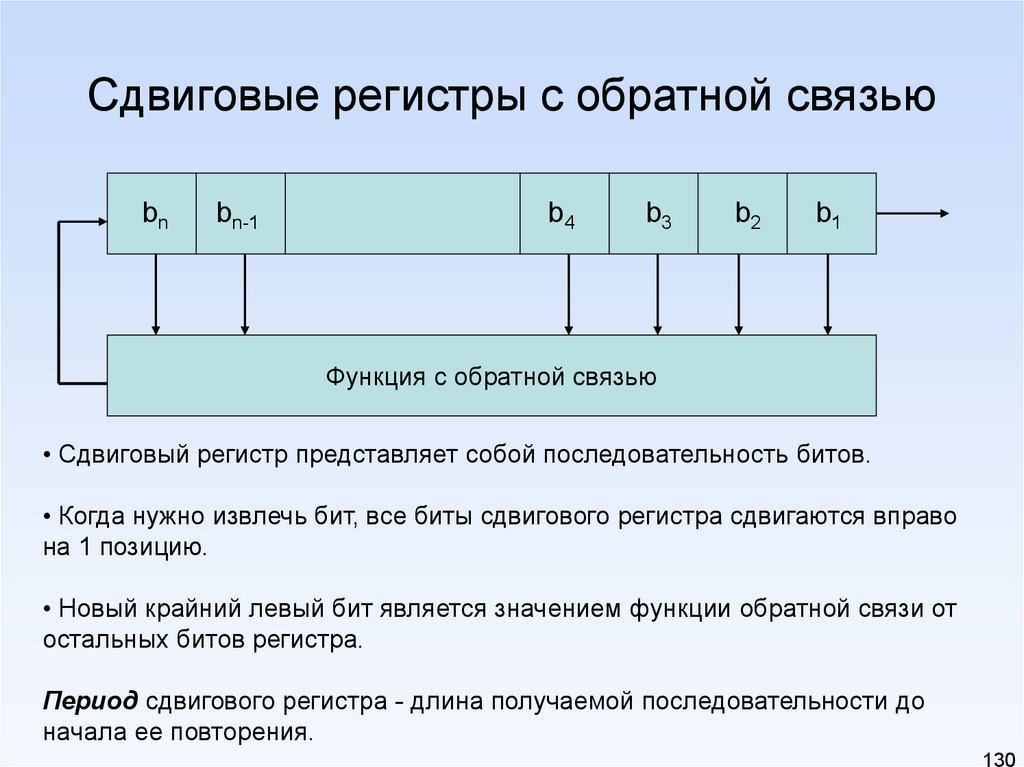

Регистр сдвига с линейной обратной связью (РСЛОС, англ. Linear Feedback Shift Register, LFSR) — сдвиговый регистр битовых слов, у которого значение входного бита однозначно задается некоторой функцией, исходя из значений остальных битов регистра до сдвига. Регистр сдвига может представлять собой некоторую электрическую схему, составленную из дискретных компонентов: транзисторов, резисторов, также может быть интегрирован в микросхему или же реализован в программе. Добавление обратной связи превращает регистр сдвига в генератор псевдослучайных чисел, который находит широкое применение в криптографии. В статье мы разберем принцип работы РСЛОС от hardware до различных его применений.

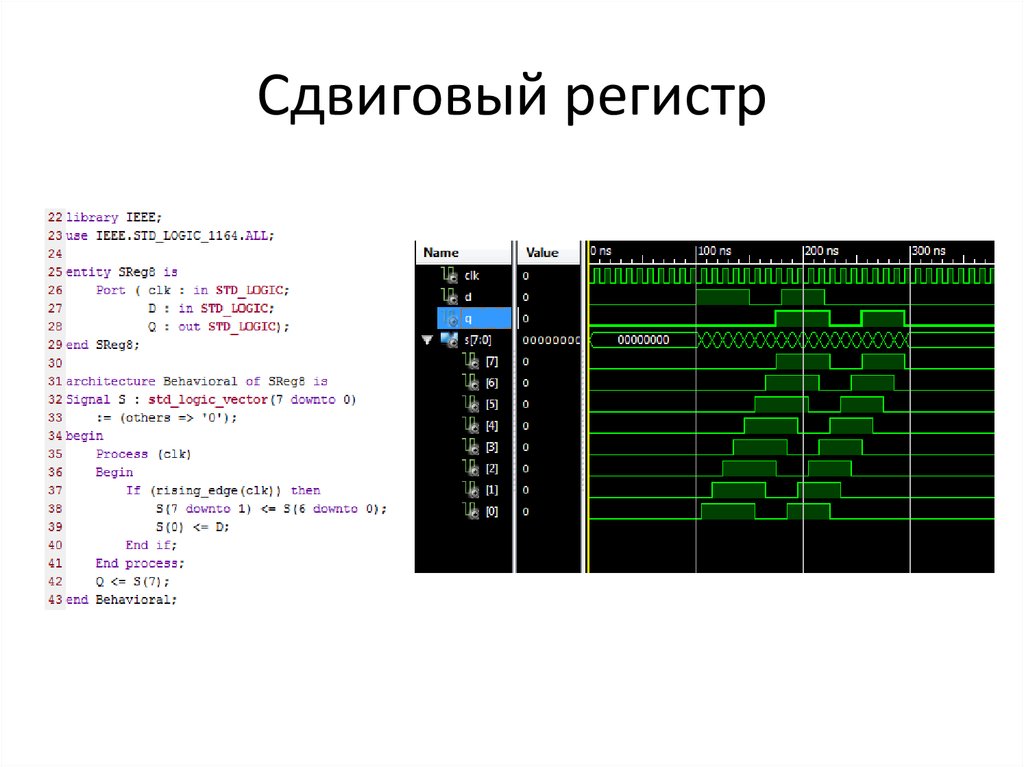

Регистр, в общем случае – это схема, состоящая из связанных между собой однобитовых элементов памяти. Такие схемы умеют записывать, хранить, считывать n-разрядные двоичные данные. В статье рассматривается вид регистра, называемый регистром сдвига. Чаще всего регистр сдвига собирается на основе последовательно соединенных D-триггеров, притом количество этих триггеров равно числу разрядов n. С принципов работы D-триггера мы и начинаем статью.

С принципов работы D-триггера мы и начинаем статью.

D-триггер

Кратко затронем самые основы. Глобально, электронику можно разделить на два раздела: аналоговый и цифровой. Принципиальная особенность второго заключается в том, что сигналы задаются дискретными уровнями напряжения. Притом дискретных уровня всего два. Таким образом, вместо того, чтобы записывать напряжение в вольтах, достаточно просто называть один из двух дискретных уровней. Так и появляются названия «ноль» и «единица». В действительности, они определяют некоторые уровни напряжения, которые могут быть какими угодно. Хотя, в большинстве случаев, «ноль» обозначает уровень 0 Вольт, а «единица» уровень 5 В, 3.3 В, 1.8 В, 1.5 В и т.д. Таким образом, фраза «на входе ноль, на выходе единица» обозначает: «на входе напряжение, соответствующее уровню ноль, на выходе напряжение, соответствующее уровню единица».

Двигаемся далее. Теперь у нас есть цифровой сигнал, что же интересного можно с ним сделать? Подать на D-триггер и посмотреть, что будет! Но сначала дадим пару определений.

Триггер – электронное устройство, обладающее способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов.

D-триггер – триггер, сохраняющий состояние входа. Притом, это состояние отображается на выходе

На электрической схеме устройства D-триггер выглядит ровно так же, как на рисунке ниже. Такой вид триггера обязательно имеет три вывода: D (вход), C (вход синхронизации, вход тактирования, тактовый вход, clk, clock) и Q (выход). Помимо них могут иметься еще: инвертированный выход, входы сброса и установки значения на выходе, вход разрешения работы. Однако, суть работы заключается именно во взаимодействии трех обязательных выводов, поэтому именно их мы и рассмотрим.

рис. 1 — условное графическое обозначение D-триггера

Принцип работы D-триггера следующий: при подаче тактового сигнала на вход C, состояние на выходе становится равным состоянию на входе. Т. е. если в какой-то момент времени на входе был «ноль», а на выходе «единица», то в момент подачи тактового сигнала выход примет состояние входа и станет «нулём».

Т. е. если в какой-то момент времени на входе был «ноль», а на выходе «единица», то в момент подачи тактового сигнала выход примет состояние входа и станет «нулём».

Начальное состояние | Состояние после подачи тактового импульса | ||

Вход (D) | Выход (Q) | Вход (D) | Выход (Q) |

0 | 0 | 0 | 0 |

0 | 1 | 0 | 0 |

1 | 0 | 1 | 1 |

1 | 1 | 1 | 1 |

Отдельно стоит обсудить фразу «подача тактового сигнала». Дело в том, что срабатывание триггера (перенос значения от входа к выходу) может происходить по разным событиям. Например, когда на тактовом входе установлена логическая единица или логический ноль. Или по фронту импульса на тактовом входе, т.е. в момент перехода нуля в единицу или единицы в ноль. То, каким образом срабатывает триггер, зависит от его конструкции и обозначается на схеме специальными символами. На приведенном рисунке изображен триггер, срабатывающий по нарастающему фронту.

Например, когда на тактовом входе установлена логическая единица или логический ноль. Или по фронту импульса на тактовом входе, т.е. в момент перехода нуля в единицу или единицы в ноль. То, каким образом срабатывает триггер, зависит от его конструкции и обозначается на схеме специальными символами. На приведенном рисунке изображен триггер, срабатывающий по нарастающему фронту.

Заметим, что сигнал на выходе никак не меняется без подачи тактового сигнала. Это позволяет использовать D-триггер как буфер. Мы подаем тактовый сигнал, триггер считывает состояние на входе и передает его на выход. После этого мы можем хранить считанное значение в триггере, сколько нам нужно, даже когда значение на входе уже стало другим. На этом заканчивается краткий обзор принципов работы D-триггера, и мы переходим к регистрам сдвига.

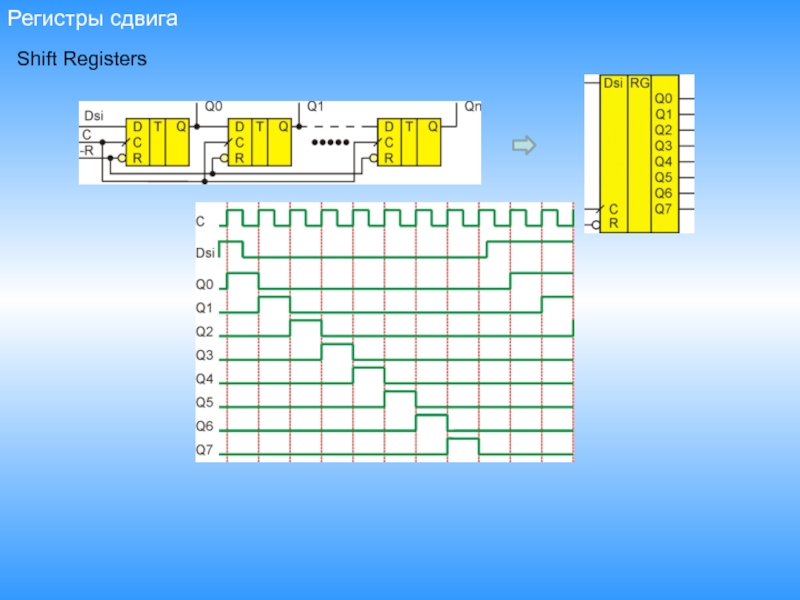

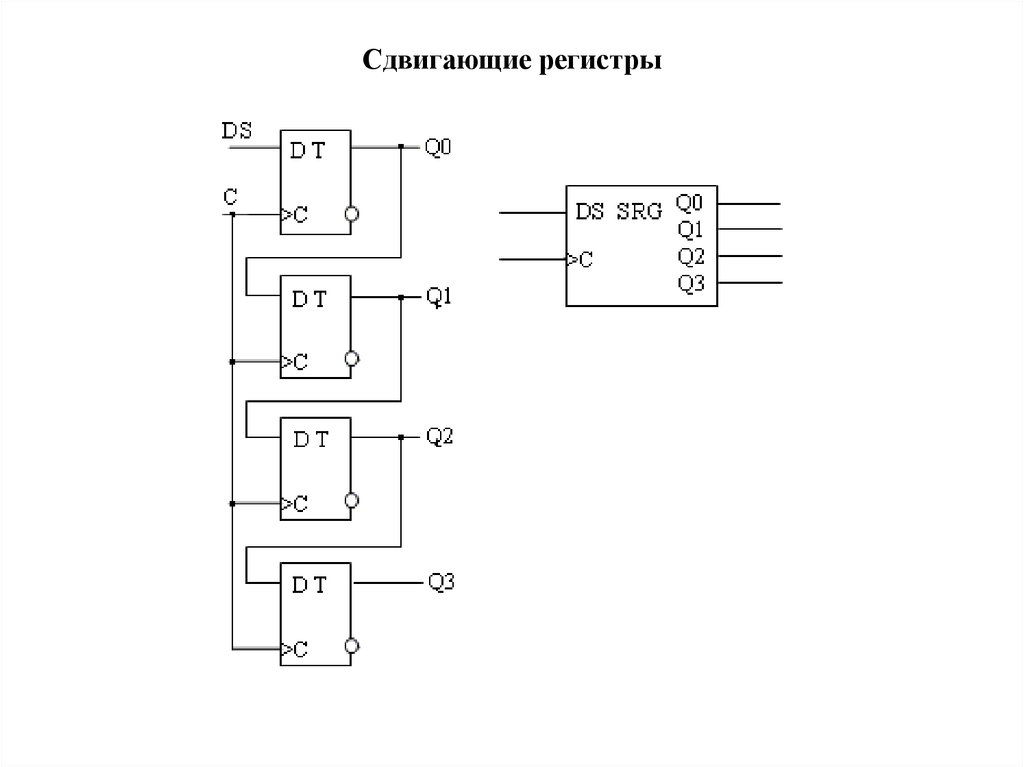

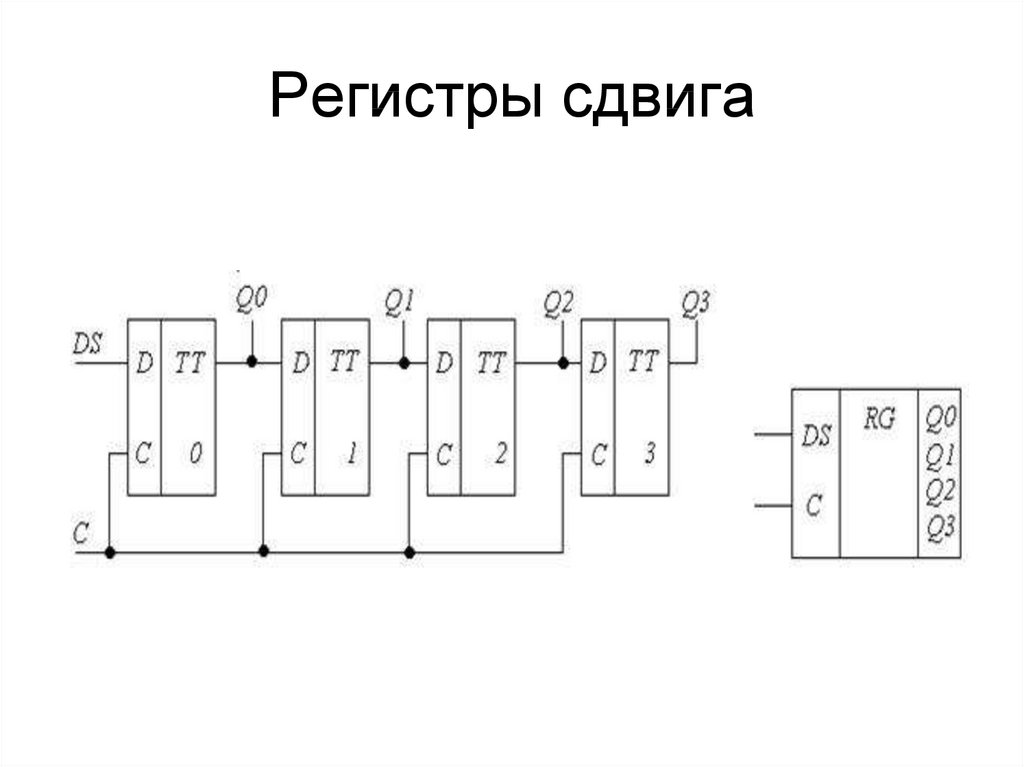

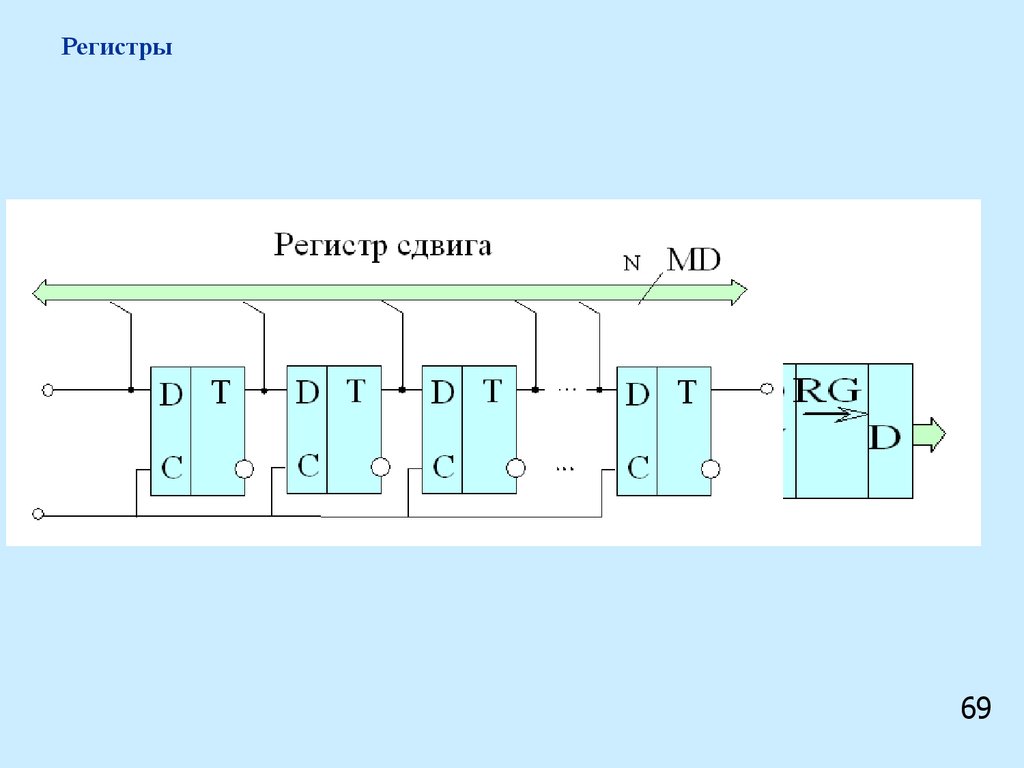

Регистр сдвига

Регистр сдвига получается тогда, когда мы соединяем вместе n D-триггеров. Входы тактирования соединяются вместе и являются входом тактирования регистра сдвига. Выход каждого триггера является выходом сдвигового регистра и, одновременно, подключается к входу следующего триггера. Вход нулевого триггера является входом регистра сдвига.

Выход каждого триггера является выходом сдвигового регистра и, одновременно, подключается к входу следующего триггера. Вход нулевого триггера является входом регистра сдвига.

Что же получилось в итоге? Представим, что на тактовый вход постоянно подается сигнал, и триггеры периодически срабатывают, т. е. «переносят» сигнал со своего входа на выход. Допустим, во время первого такта мы подали единичку на вход регистра, а в остальное время там ноль. Как будут меняться сигналы на нашем регистре с течением времени? С первым тактом единица с входа нулевого триггера попадет на его выход (он также является и входом первого). По второму такту единичка попадает на выход первого и т. д. Таким образом, по мере поступления тактовых импульсов, наша единица будет смещаться вправо каждый такт, т. е. сдвигаться. Дойдя до последнего триггера, единица из него выйдет, но никуда уже не попадет. И так происходит со всеми данными, поступающими на вход регистра сдвига: с каждым тактом они сдвигаются вправо.

Такт№ | Вход | Выход 0 | Выход 1 | Выход 2 | Выход 3 |

0 | 1 | 0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 | 0 | 0 |

2 | 0 | 0 | 1 | 0 | 0 |

3 | 0 | 0 | 0 | 1 | 0 |

4 | 0 | 0 | 0 | 0 | 1 |

5 | 0 | 0 | 0 | 0 | 0 |

Регистр сдвига с линейной обратной связью

Наконец-то мы подошли к основному предмету нашего рассмотрения. В предыдущем примере мы сами подавали некоторые числа на вход регистра сдвига. А что если регистр будет сам себе подавать на вход некоторое значение? Притом, оно будет определяться значениями на выходе регистра. В таком случае мы как раз и получим регистр сдвига с линейной обратной связью. Значение, подаваемое на вход, считается с помощью булевой линейной функции, представленной ниже, аргументами которой являются сигналы на выходах сдвигового регистра. Факт подачи сигнала с выхода регистра на его вход создает обратную связь.

В предыдущем примере мы сами подавали некоторые числа на вход регистра сдвига. А что если регистр будет сам себе подавать на вход некоторое значение? Притом, оно будет определяться значениями на выходе регистра. В таком случае мы как раз и получим регистр сдвига с линейной обратной связью. Значение, подаваемое на вход, считается с помощью булевой линейной функции, представленной ниже, аргументами которой являются сигналы на выходах сдвигового регистра. Факт подачи сигнала с выхода регистра на его вход создает обратную связь.

В формуле hi — это некоторые коэффициенты или веса, принимающие значение ноль или один. Сумма считается по модулю два.

Как работает РСЛОС? Пусть изначально мы имеем некоторые значения на выходе регистра. Булева функция, исходя из этих значений, подает на вход регистра некоторое число. Затем, как только мы подаем тактовый сигнал, все значения сдвигаются на 1 вправо, в нулевой триггер попадает тот самый результат булевой функции. Теперь значения на выходе регистра совсем другие. Булева функция заново считает результат и подает его на вход. Далее следующий такт, и все повторяется.

Булева функция заново считает результат и подает его на вход. Далее следующий такт, и все повторяется.

Генератор псевдослучайных чисел

Оказывается, что РСЛОС уже является генератором псевдослучайных чисел. Как получить эти числа? На самом деле, они уже есть, просто в двоичном виде. Ведь мы имеем n бит, n выходов регистра. Это и есть то самое число, которое будет меняться каждый такт. Будем обозначать его Xi. Такой генератор имеет ряд характерных свойств, одно из которых периодичность. Т. е. существует такое N, что Xi+N = Xi для любого i. Если количество элементов такой последовательности равно 2n-1, то такая последовательность называется максимальной или М-последовательностью. Период любой последовательности, сгенерированной таким образом, не может быть больше 2n-1. При анализе РСЛОС используется математический аппарат теории конечных полей. Свойства выдаваемой РСЛОС последовательности тесно связаны со свойствами многочлена

над полем GF(2). Такой многочлен называется образующим многочленом РСЛОС. Общий вид формулы следующего состояния регистра в момент времени t + 1, соответствующего образующему многочлену Ф(x) степени p:

Такой многочлен называется образующим многочленом РСЛОС. Общий вид формулы следующего состояния регистра в момент времени t + 1, соответствующего образующему многочлену Ф(x) степени p:

где Y(t) вектор состояния регистра в момент времени t. T – квадратная матрица порядка n вида:

Для того, чтобы длина последовательности РСЛОС была максимальной, многочлен Ф должен быть примитивным. Однако, вычисление примитивного многочлена над полем GF(2) — достаточно сложная математическая задача: для генерации примитивного многочлена степени k нужно знать множители числа 2k-1. Поэтому для нахождения таких многочленов проще случайным образом выбрать многочлен и проверить его на примитивность. Или же, можно взять известные примеры примитивных многочленов. Стоит учесть, что у генератора любой заданной длины может быть более одного примитивного многочлена согласно их свойствам. Несколько примеров примитивных многочленов приведены ниже.

n | LFSR-2 | LFSR-4 |

2 | 2, 1 | |

3 | 3, 2 | |

4 | 4, 3 | |

5 | 5, 3 | 5, 4, 3, 2 |

6 | 6, 5 | 6, 5, 3, 2 |

7 | 7, 6 | 7, 6, 5, 4 |

8 | 8, 6, 5, 4 |

В таблице представлены степени многочлена Ф, притом, нулевая степень опущена. Для примера, для n= 8 примитивный многочлен будет иметь вид:

Для примера, для n= 8 примитивный многочлен будет иметь вид:

Получившийся генератор чисел обладает многими преимуществами. Одно из самых заметных: он быстродействующий. Для генерации нового числа достаточно всего лишь подать очередной тактовый импульс. К недостаткам можно отнести периодичность, возможность определения последовательности на выходе. Таким образом, генератор чисел на основе РСЛОС стоит рассматривать как доступный, быстрый, но имеющий слабую криптостойкость. Однако известны различные методы повышения криптостойкости генераторов псевдослучайных чисел на основе РСЛОС. Один из них: использование нескольких генераторов.

Каждый генератор выдает свое случайное число. Затем эти числа становятся аргументами некоторой булевой функции. И результатом работы такой схемы является как раз значение этой булевой функции. Данный способ позволяет сильно увеличить период последовательности. Если длина последовательностей РСЛОС порядка 2n1 , 2n2, и т. д., то длина периода всего генератора будет порядка 2n1+n2+… при условии, что n1, n2, … взаимно просты.

Литература

Слеповичев И. И. Генераторы псевдослучайных чисел. — 2017. — 117 с.

Ларин А. Л. Основы цифровой электроники. — МФТИ, 2008. — 314 с.

Eastlake D., Schiller J., Crocker S. Randomness requirements for security. — 2005. — 48 с.

НОУ ИНТУИТ | Лекция | Регистры

< Дополнительный материал || Лекция 8: 1234567

Аннотация: В лекции рассказывается о параллельных регистрах и регистрах сдвига, об алгоритмах их работы, параметрах, типовых схемах включения, а также о реализации на их основе некоторых часто встречающихся функций.

Ключевые слова: Register, ПО, параллельный регистр, сдвиговый регистр, выход, триггер, входной, тактовый сигнал, очередь, управляющий сигнал, положительный фронт сигнала, бит, регистр, память, инверсный выход, байт, таблица истинности, диаграмма, значение, операции, запись, сумматор, конвейерная обработка, быстродействие, комбинационная схема, накапливающий сумматор, функция, переполнение, схема без возобновления, цикл работы, вес, экстремум, инвертор, единица, максимум, компаратор кодов, минимум, latch, буфер, входная информация, отрицательный фронт сигнала, информация, повторитель, фронт сигнала, передний фронт сигнала, вложенные циклы, регистр-защелка, связь, shift register, регистр сдвига, прямой, параллельная запись, объединение, SL, загрузка, шина данных, разрядность, цифровая информация, целое число, управляемый код, мультиплексор, погрешность, генератор, фирма

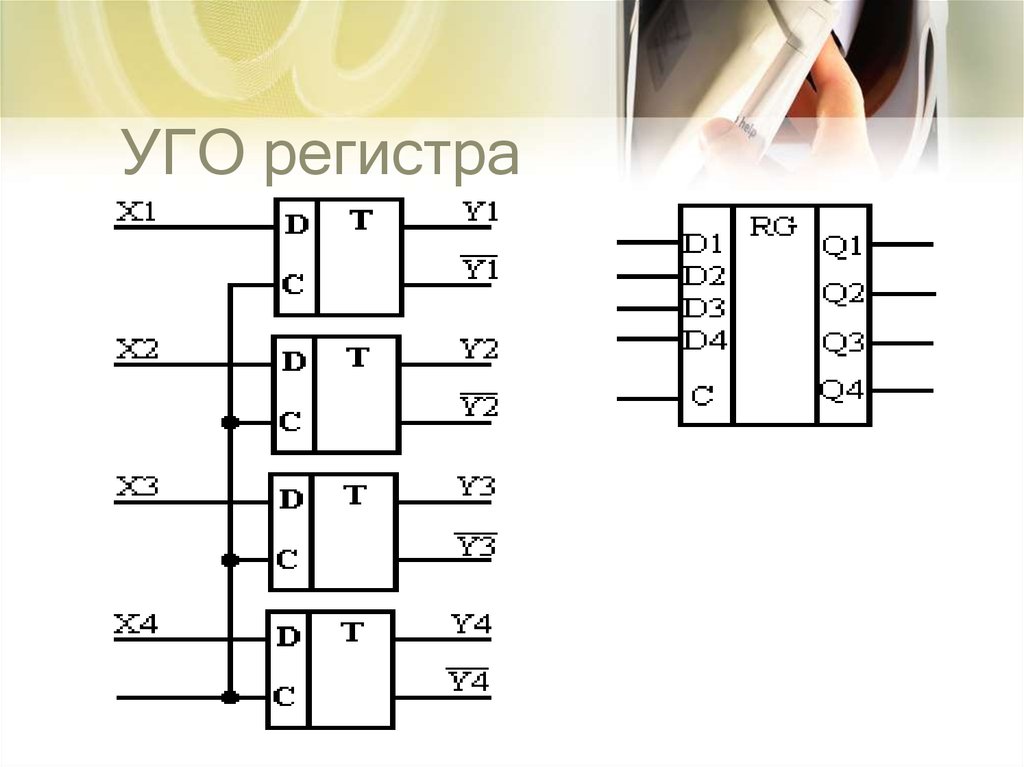

intuit.ru/2010/edi»>Регистры (англ. register) представляют собой, по сути, несколько D-триггеров (обычно от 4 до 16), соединенных между собой тем или иным способом. Поэтому принципиальной разницы между ними и отдельными D-триггерами не существует. Правда, триггеры, входящие в состав регистров, не имеют такого количества разнообразных управляющих входов, как одиночные триггеры.На схемах регистры обозначаются буквами RG. В отечественных сериях микросхем регистрам соответствуют буквы ИР. Все регистры делятся на две большие группы (рис. 8.1):

- Параллельные регистры;

- Регистры сдвига (или сдвиговые регистры).

Существуют регистры и других типов, но они применяются гораздо реже, чем параллельные и сдвиговые, так как имеют узкоспециальное назначение.

В параллельных регистрах (а) каждый из триггеров имеет свой независимый информационный вход (D) и свой независимый

информационный выход. Тактовые входы (С) всех триггеров соединены между собой. В результате параллельный регистр

представляет собой многоразрядный, многовходовый триггер.

Тактовые входы (С) всех триггеров соединены между собой. В результате параллельный регистр

представляет собой многоразрядный, многовходовый триггер.

Рис. 8.1. Структура параллельного регистра (а)и сдвигового регистра (б)

В сдвиговых регистрах (б) все триггеры соединены в последовательную цепочку (выход каждого предыдущего триггера соединен со входом D следующего триггера). Тактовые входы всех триггеров (С) объединены между собой. В результате такой триггер может рассматриваться как линия задержки, входной сигнал которой последовательно перезаписывается из триггера в триггер по фронту тактового сигнала С. Информационные входы и выходы триггеров могут быть выведены наружу, а могут и не выводиться — в зависимости от функции, выполняемой регистром.

Параллельные регистры, в свою очередь, делятся на две группы:

- intuit.ru/2010/edi»>Регистры, срабатывающие по фронту управляющего сигнала С (или тактируемые регистры).

- Регистры, срабатывающие по уровню управляющего сигнала С (или стробируемые регистры).

Чаще всего в цифровых схемах используются регистры, управляемые фронтом (то есть тактируемые), однако и стробируемые регистры имеют свой круг задач, в которых их ничто не может заменить.

Регистры, срабатывающие по фронту

Память регистра сохраняется

до момента выключения питания схемы.

Память регистра сохраняется

до момента выключения питания схемы.Рис. 8.2. Параллельные регистры стандартных серий, срабатывающие по фронту

В стандартные серии входит несколько типов параллельных регистров, срабатывающих по фронту (рис. 8.2). Различаются они количеством разрядов, наличием или отсутствием инверсных выходов, наличием или отсутствием входа сброса (–R) или разрешения записи (–WE), а также типом выходных каскадов (2С или 3С) и, соответственно, наличием или отсутствием входа разрешения –EZ. Иногда на схемах тактовый вход С обозначается WR — сигнал записи в регистр.Большинство регистров имеют восемь разрядов, то есть запоминают один байт информации. Регистр ТМ8 в справочниках

обычно называется счетверенным D-триггером (он и в наименовании несет буквы ТМ), хотя он вполне может рассматриваться и

как регистр, так как тактовый вход С и вход сброса –R у всех четырех триггеров объединены между собой.

Таблицы истинности регистров очень просты и не отличаются принципиально от таблицы истинности D-триггеров. Отличие от триггеров появляется только в случае наличия у регистра дополнительных управляющих входов разрешения записи –WE и разрешения выхода –EZ. В качестве примеров в табл. 8.1 приведена таблица истинности регистра ИР27, а в табл. 8.2 — регистра ИР37. По переходу тактового сигнала С из 0 в 1 (положительный фронт) оба регистра записывают в себя входную информацию.

| Входы | Выходы | |||

|---|---|---|---|---|

| -WE | C | D | Q | |

| 0 | 0 1 | 0 | 0 | |

| 0 | 0 1 | 1 | 1 | |

| 0 | 0 | X | Не меняется | |

| 0 | 1 | Х | Не меняется | |

| 1 | Х | Х | Не меняется | |

| Входы | Выходы | |||

|---|---|---|---|---|

| -EZ | C | D | Q | |

| 0 | 0 1 | 0 | 0 | |

| 0 | 0 1 | 1 | 1 | |

| 0 | 0 | X | Не меняется | |

| 0 | 1 | Х | Не меняется | |

| 1 | Х | Х | Z | |

intuit.ru/2010/edi»>Все регистры, имеющие выход с тремя состояниями, обеспечивают повышенную нагрузочную способность. Задержка переключения регистров примерно соответствует задержке переключения триггеров. Все временные ограничения, накладываемые на входные сигналы в случае триггеров, справедливы и для входных сигналов регистров. Например, не должна быть слишком малой длительность сигнала С, а также не должна быть слишком малой задержка между установлением сигнала D и приходом положительного фронта сигнала С. Иначе работа регистра может быть нестабильной или даже неправильной.

Одно из основных применений регистров состоит в хранении требуемого кода в течение нужного времени. Если для работы остальной части схемы необходимо иметь входной код, который можно легко изменять, то для этого как раз подходит регистр.

Дальше >>

< Дополнительный материал || Лекция 8: 1234567

Сдвиговые регистры в цифровой электронике

|

следующий → ← предыдущая Группа триггеров, которая используется для хранения нескольких битов данных, и данные перемещаются с одного триггера на другой, известна как Сдвиговый регистр . Сдвиговый регистр может сдвигать биты либо влево, либо вправо. Сдвиговый регистр , который сдвигает бит влево, известен как «Сдвиг левого регистра» , и он сдвигает бит вправо, известный как «Правый левый регистр» . Сдвиговый регистр подразделяется на следующие типы:

Последовательный вход Последовательный выход В «Serial Input Serial Output» данные сдвигаются «IN» или «OUT» последовательно. Изначально все триггеры находятся в состоянии «сброс», т.е. Y 3 = Y 2 = Y 1 = Y 0 = 0. Если мы передаем двоичное число 1111, младший бит бита номер сначала применяется к биту Din. Вход D3 третьего триггера, т. е. FF-3, напрямую подключен к входу последовательных данных D3. Выход Y 3 передается на вход данных d 2 следующего триггера. Этот процесс остается таким же для остальных триггеров. Блок-схема «Serial IN Serial OUT» приведена ниже. Блок-схема:Операция Когда приложение тактового сигнала отключено, выходы Y 3 Y 2 Y 1 Y 0 = 0000. Младший бит числа передается на вход данных D в , т. е. D 3 . Мы применим часы, и на этот раз значение D 3 равно 1. Устанавливается первый триггер, т. Следующий бит двоичного числа, т. е. 1, передается на вход данных D 2 . Второй триггер, т. е. FF-2, установлен, и слово сохраняется, когда попадает следующий отрицательный фронт часов. Сохраненное слово изменено на 1100. Следующий бит двоичного числа, т. е. 1, передается на вход данных D 1 и применяются часы. Устанавливается третий триггер, т. е. FF-1, и слово сохраняется, когда снова попадает отрицательный фронт часов. Сохраненное слово изменено на 1110. Аналогично, последний бит двоичного числа, т. е. 1, передается на вход данных D 0 и применяются часы. Устанавливается последний триггер, то есть FF-0, и слово сохраняется, когда приходит отрицательный фронт часов. Сохраненное слово изменяется на 1111. Таблица правдыСигналыПоследовательный ВХОД Параллельный ВЫХОД В сдвиговом регистре «Serial IN Parallel OUT» данные последовательно передаются на триггер, а выходные данные выбираются параллельно. Ниже приведена блок-схема 4-битного 9Последовательный номер 0008 в параллельном регистре сдвига . Схема с четырьмя D-триггерами содержит сигнал очистки и тактовый сигнал для сброса этих четырех триггеров. В SIPO вход второго триггера является выходом первого триггера и так далее. Один и тот же тактовый сигнал применяется к каждому триггеру, так как триггеры синхронизируются друг с другом. Параллельные выходы используются для связи. Блок-схемаПараллельный ВХОД Последовательный ВЫХОД В «Параллельный ВХОД, Последовательный ВЫХОД» , данные вводятся параллельно, а результат поступает последовательно. Четырехбитный регистр «Parallel IN Serial OUT» разработан ниже. Режим загрузкиБиты B 0 , B 1 , B 2 и B 3 передаются на соответствующие триггеры, когда активны второй, четвертый и шестой вентили «И». Эти ворота активны, когда линия сдвига или загрузки установлена на 0. Двоичные входы B0, B1, B2 и B3 будут загружены в соответствующие триггеры, когда фронт тактового сигнала низкий. Таким образом, происходит параллельная загрузка. Сменный режим Второй, четвертый и шестой вентили неактивны, когда линия загрузки и сдвига установлена на 0. Таким образом, мы не можем загружать данные параллельно. Блок-схемаПараллельный ВХОД Параллельный ВЫХОДВ «Parallel IN Parallel OUT» входы и выходы поступают в регистр параллельно. Входы А 0 , A 1 , A 2 и A 3 напрямую передаются на входы данных D 0 , D 1 , D 2 , и резкий поворот. Биты двоичного входа загружаются в триггеры при подаче отрицательного фронта тактового сигнала. Тактовый импульс необходим для загрузки всех битов. На выходе появляются загруженные биты. Блок-схемаДвунаправленный сдвиговый регистр Двоичное число после сдвига каждого бита числа влево на одну позицию будет эквивалентно числу, полученному путем умножения исходного числа на 2. Таким же образом, двоичное число после сдвига каждого бита числа вправо на одну позицию будет эквивалентно числу, полученному делением исходного числа на 2. Для выполнения операций умножения и деления с использованием сдвигового регистра требуется, чтобы данные перемещались в обоих направлениях, т. е. влево или вправо в регистре. Такие регистры называются сдвиговым регистром «Двунаправленный» . Ниже приведена схема 4-битного «двунаправленного» регистра сдвига , где D R — это «последовательный ввод данных сдвига вправо» , D L — это «ввод данных сдвига влево» , а M — это «ввод выбора режима» . Блок-схемаОперации1) Сдвиг вправо (M=1)

2) Сдвиг влево (M=0)

Универсальный сдвиговый регистрРегистр, в котором данные сдвигаются в одном направлении, известен как «однонаправленный» сдвиговый регистр. Регистр, в котором данные сдвигаются в обоих направлениях, известен как «двунаправленный» сдвиговый регистр . Регистр сдвига «Универсальный» — это особый тип регистра, который может загружать данные параллельно и сдвигать эти данные в обоих направлениях, т. е. вправо и влево. Вход M, т. е. вход управления режимом, устанавливается в 1 для выполнения операции параллельной загрузки. Блок-схемаСледующая темаСчетчики ← предыдущая следующий → |

Узнайте, как сдвигать регистры в LabVIEW

При программировании с использованием циклов часто требуется доступ к данным из предыдущих итераций цикла. Например, у вас может быть ВП, который считывает температуру и отображает ее на графике. Если вы хотите также отобразить скользящее среднее значение температуры, вам необходимо использовать данные, сгенерированные в предыдущих итерациях. Два способа доступа к этим данным включают сдвиговый регистр и узел обратной связи.

Два способа доступа к этим данным включают сдвиговый регистр и узел обратной связи.

Циклы While создают данные по умолчанию, когда регистр сдвига не инициализирован. Циклы For выдают данные по умолчанию, если вы подключаете 0 к клемме счетчика цикла For или если вы подключаете пустой массив к циклу For в качестве входных данных с включенной автоматической индексацией. Цикл не выполняется, и любой выходной туннель с отключенным автоиндексированием содержит значение по умолчанию для типа данных туннеля. Используйте регистры сдвига для передачи значений через цикл независимо от того, выполняется ли цикл.

Если вы хотите расширить свою карьеру с сертифицированным специалистом по Android, посетите Mindmajix — глобальную платформу онлайн-обучения: « LabVIEW training » Курс. Этот курс поможет вам достичь совершенства в этой области.

Сдвиговые регистры используются с циклами For и While для передачи значений от одной итерации цикла к другой. Сдвиговые регистры похожи на статические переменные в текстовых языках программирования. Сдвиговый регистр выглядит как пара терминалов, показанных на рис. 4.11, прямо напротив друг друга на вертикальных сторонах границы цикла. Терминал в правой части цикла содержит стрелку вверх и хранит данные о завершении итерации. LabVIEW передает данные, связанные с правой частью регистра, на следующую итерацию. После выполнения цикла терминал в правой части цикла возвращает последнее значение, сохраненное в сдвиговом регистре. Создайте регистр сдвига, щелкнув правой кнопкой мыши левую или правую границу цикла и выбрав «Добавить регистр сдвига» в контекстном меню.

Сдвиговые регистры похожи на статические переменные в текстовых языках программирования. Сдвиговый регистр выглядит как пара терминалов, показанных на рис. 4.11, прямо напротив друг друга на вертикальных сторонах границы цикла. Терминал в правой части цикла содержит стрелку вверх и хранит данные о завершении итерации. LabVIEW передает данные, связанные с правой частью регистра, на следующую итерацию. После выполнения цикла терминал в правой части цикла возвращает последнее значение, сохраненное в сдвиговом регистре. Создайте регистр сдвига, щелкнув правой кнопкой мыши левую или правую границу цикла и выбрав «Добавить регистр сдвига» в контекстном меню.

Сдвиговый регистр передает данные любого типа и автоматически изменяется на тип данных первого объекта, подключенного к сдвиговому регистру. Данные, которые вы подключаете к клеммам каждого сдвигового регистра, должны быть одного типа. Вы можете добавить более одного регистра сдвига в цикл. Если у вас есть несколько операций, которые используют значения предыдущей итерации в нашем цикле, вы можете использовать несколько сдвиговых регистров для хранения значений данных из этих разных процессов в структуре, как показано на рисунке 4. 12.

12.

Часто задаваемые вопросы и ответы из интервью LabVIEW

Инициализация сдвигового регистра сбрасывает значение, которое сдвиговый регистр передает на первую итерацию цикла при запуске ВП. Инициализируйте регистр сдвига, подключив элемент управления или константу к клемме регистра сдвига в левой части цикла. Если вы не инициализируете сдвиговый регистр, цикл использует значение, записанное в сдвиговый регистр при последнем выполнении цикла, или значение по умолчанию для типа данных, если цикл никогда не выполнялся.

Используйте цикл с неинициализированным сдвиговым регистром для многократного запуска ВП, чтобы при каждом запуске ВП начальным выводом сдвигового регистра было последнее значение предыдущего выполнения. Используйте неинициализированный сдвиговый регистр для сохранения информации о состоянии между последующими запусками ВП. После выполнения цикла последнее значение, сохраненное в сдвиговом регистре, остается на правом терминале. Если вы подключаете правую клемму вне цикла, то провод передает последнее значение, сохраненное в сдвиговом регистре. Вы можете добавить более одного регистра сдвига в цикл.

Вы можете добавить более одного регистра сдвига в цикл.

Если у вас есть несколько операций, использующих значения предыдущих итераций внутри цикла, используйте несколько регистров сдвига для хранения значений данных из этих разных процессов в структуре, как показано на рис. 4.13. Цикл For выполняется пять раз. К значению сдвигового регистра добавляются последующие числа, начиная с 1 до 5. После пяти итераций цикла For, сдвиговый регистр передает индикатору окончательное значение 15, и ВП останавливается. Каждый раз, когда вы запускаете ВП, сдвиговый регистр начинается со значения 0. Сдвиговый регистр используется без инициализации. При первом запуске ВП сдвиговый регистр начинается со значения 0, которое является значением по умолчанию для 32-битного целого числа. После пяти итераций цикла For сдвиговый регистр передает индикатору конечное значение 15 и завершает работу. При следующем запуске ВП сдвиговый регистр начинается со значения 15, которое было последним значением предыдущего выполнения. После пяти итераций цикла For сдвиговый регистр передает индикатору окончательное значение 30. Если вы снова запустите ВП, сдвиговый регистр будет начинаться со значения 30 и так далее. Неинициализированные сдвиговые регистры сохраняют значение предыдущей итерации до тех пор, пока вы не закроете ВП.

После пяти итераций цикла For сдвиговый регистр передает индикатору окончательное значение 30. Если вы снова запустите ВП, сдвиговый регистр будет начинаться со значения 30 и так далее. Неинициализированные сдвиговые регистры сохраняют значение предыдущей итерации до тех пор, пока вы не закроете ВП.

Регистры сдвига с накоплением

Регистры сдвига с накоплением позволяют получить доступ к данным из предыдущих итераций цикла. Регистры сдвига с накоплением запоминают значения из нескольких предыдущих итераций и переносят эти значения на следующие итерации. Этот метод полезен для усреднения точек данных. Чтобы создать составной регистр сдвига, щелкните правой кнопкой мыши левый терминал и выберите «Добавить элемент» в контекстном меню.

Стекированные сдвиговые регистры, как показано на рис. 4.14, могут встречаться только в левой части цикла, поскольку правый терминал передает только данные, сгенерированные на текущей итерации, на следующую итерацию. Если вы добавите еще один элемент в левый терминал, значение из двух последних итераций переносится на следующую итерацию, при этом значение самой последней итерации сохраняется в верхнем регистре сдвига. Второй терминал хранит данные, переданные ему с предыдущей итерации. Вы можете добавить более двух терминалов в сдвиговый регистр. Если вы добавите еще два элемента в левый терминал, второй терминал сохранит данные, переданные ему с предыдущей итерации, а нижний терминал сохранит данные, переданные ему с двух итераций назад.

Второй терминал хранит данные, переданные ему с предыдущей итерации. Вы можете добавить более двух терминалов в сдвиговый регистр. Если вы добавите еще два элемента в левый терминал, второй терминал сохранит данные, переданные ему с предыдущей итерации, а нижний терминал сохранит данные, переданные ему с двух итераций назад.

Замена туннелей сдвиговыми регистрами

При необходимости туннели можно заменить сдвиговыми регистрами. Чтобы заменить туннель сдвиговым регистром, щелкните правой кнопкой мыши туннель и выберите «Заменить сдвиговым регистром». Если на границе цикла напротив туннеля, по которому вы щелкнули правой кнопкой мыши, туннеля нет, LabVIEW автоматически создаст пару терминалов регистра сдвига. Если на границе цикла напротив туннеля, по которому вы щелкнули правой кнопкой мыши, существует один или несколько туннелей, указатель мыши превратится в символ сдвигового регистра. Вы можете выбрать конкретный туннель, который должен быть преобразован в регистр сдвига, щелкнув мышью по этому туннелю, как показано на рис. 4.15.

4.15.

Ознакомьтесь с учебными пособиями по LabVIEW

Замена регистров сдвига туннелями

Замените регистры сдвига туннелями, если вам больше не нужно передавать значения из одной итерации цикла в другую. Чтобы заменить сдвиговый регистр туннелем, щелкните правой кнопкой мыши сдвиговый регистр и выберите «Заменить на туннели». Если вы замените терминал выходного регистра сдвига туннелем в цикле For, связь с любым узлом за пределами цикла разорвется, поскольку цикл For Loop по умолчанию включает автоиндексацию, как показано на рис. 4.16. Щелкните правой кнопкой мыши автоиндексированный туннель и выберите «Отключить индексирование» в туннеле, чтобы исправить сломанный провод. Эта проблема не возникает в циклах «пока», так как автоматическое индексирование отключено по умолчанию в циклах «пока».

Узлы обратной связи

Когда выход узла подключен непосредственно к входу, узел обратной связи генерируется автоматически. Узел обратной связи, показанный на рис. 4.17, автоматически появляется в циклах For или While, если мы подключаем выход узла или группы узлов к входу этого узла или группы узлов. Подобно сдвиговому регистру, узел обратной связи сохраняет данные, когда цикл завершает итерацию, отправляет это значение на следующую итерацию цикла и передает данные любого типа. Используйте узел обратной связи, чтобы избежать излишне длинных проводов в петлях. Стрелка узла обратной связи указывает направление, в котором данные передаются по проводу. Стрелка автоматически меняет направление при изменении направления потока данных.

4.17, автоматически появляется в циклах For или While, если мы подключаем выход узла или группы узлов к входу этого узла или группы узлов. Подобно сдвиговому регистру, узел обратной связи сохраняет данные, когда цикл завершает итерацию, отправляет это значение на следующую итерацию цикла и передает данные любого типа. Используйте узел обратной связи, чтобы избежать излишне длинных проводов в петлях. Стрелка узла обратной связи указывает направление, в котором данные передаются по проводу. Стрелка автоматически меняет направление при изменении направления потока данных.

Вы также можете выбрать узел обратной связи на палитре структур и поместить его в цикл For или цикл While. Если вы разместите узел обратной связи на проводе до ответвления провода, соединяющего данные с туннелем, как показано на рис. 4.18, узел обратной связи передает каждое значение в туннель. Если вы поместите узел обратной связи на провод после того, как разветвите провод, соединяющий данные с туннелем, узел обратной связи передает каждое значение обратно на вход ВП или функции, а затем передает последнее значение в туннель.

Инициализация узла обратной связи

Инициализация узла обратной связи, как показано на рис. 4.19, сбрасывает начальное значение, которое узел обратной связи передает в первый раз, когда цикл выполняется при запуске ВП. Если вы не инициализируете узел обратной связи, узел обратной связи передает последнее значение, записанное в узел, или значение по умолчанию для типа данных, если цикл никогда не выполнялся. Если вы оставите ввод терминала инициализатора неподключенным, каждый раз, когда запускается ВП, начальным вводом узла обратной связи будет последнее значение из предыдущего выполнения.

Чтобы инициализировать узел обратной связи, щелкните правой кнопкой мыши узел обратной связи и выберите «Терминал инициализатора» в контекстном меню и добавьте значение вне контура к терминалу инициализатора. Когда вы выбираете узел обратной связи на палитре функций или преобразуете инициализированный регистр сдвига в узел обратной связи, цикл появляется с терминалом инициализатора.

Чтобы заменить узел обратной связи сдвиговыми регистрами, щелкните правой кнопкой мыши узел обратной связи и выберите «Заменить сдвиговым регистром» в контекстном меню.

Чтобы заменить регистры сдвига узлом обратной связи, щелкните правой кнопкой мыши регистры сдвига и выберите в контекстном меню пункт «Заменить узлом обратной связи».

Ознакомьтесь с образцами резюме LabVIEW! Скачивайте и редактируйте, чтобы вас заметили лучшие работодатели! Скачать сейчас!

Course Schedule

| Name | Dates | |

|---|---|---|

| LabVIEW Training | Jan 07 to Jan 22 | |

| LabVIEW Training | Jan 10 to Jan 25 | |

| LabVIEW Training | Jan 14 to Jan 29 | |

| LabVIEW Training | Jan 17 to Feb 01 |

Last updated: 04 January 2023

Об авторе

Ручита Джибу

Я Ручита, работаю автором контента для технологий MindMajix.

2.

Таблица истинности регистра ИР37

2.

Таблица истинности регистра ИР37 Биты, хранящиеся в регистрах, сдвигаются, когда тактовый импульс применяется внутри и внутри или снаружи регистров. Чтобы сформировать n-битный регистр сдвига, мы должны соединить n триггеров. Итак, количество битов двоичного числа прямо пропорционально количеству триггеров. Триггеры соединены таким образом, что выход первого триггера становится входом другого триггера.

Биты, хранящиеся в регистрах, сдвигаются, когда тактовый импульс применяется внутри и внутри или снаружи регистров. Чтобы сформировать n-битный регистр сдвига, мы должны соединить n триггеров. Итак, количество битов двоичного числа прямо пропорционально количеству триггеров. Триггеры соединены таким образом, что выход первого триггера становится входом другого триггера.  В SISO один бит сдвигается за раз в правом или левом направлении под управлением часов.

В SISO один бит сдвигается за раз в правом или левом направлении под управлением часов.  е. FF-3, и слово сохраняется в регистре по первому заднему фронту часов. Теперь сохраненное слово 1000.

е. FF-3, и слово сохраняется в регистре по первому заднему фронту часов. Теперь сохраненное слово 1000.  Данные передаются в регистр побитно, а выход остается отключенным до тех пор, пока данные не будут переданы на вход данных. Когда данные передаются в регистр, выходы активируются, а триггеры содержат возвращаемое значение

Данные передаются в регистр побитно, а выход остается отключенным до тех пор, пока данные не будут переданы на вход данных. Когда данные передаются в регистр, выходы активируются, а триггеры содержат возвращаемое значение  Вход триггера является выходом предыдущего триггера. Входы и выходы соединены комбинационной схемой. Через эту комбинационную схему пропускаются двоичные входы B 0 , B 1 , B 2 , B 3 . Режим смены и режим загрузки — это два режима, в которых «ПИСО» схема работает.

Вход триггера является выходом предыдущего триггера. Входы и выходы соединены комбинационной схемой. Через эту комбинационную схему пропускаются двоичные входы B 0 , B 1 , B 2 , B 3 . Режим смены и режим загрузки — это два режима, в которых «ПИСО» схема работает.  В это время будут активированы первый, третий и пятый вентили, а сдвиг данных будет осуществляться влево вправо. Таким образом, происходит операция «Parallel IN Serial OUT» .

В это время будут активированы первый, третий и пятый вентили, а сдвиг данных будет осуществляться влево вправо. Таким образом, происходит операция «Parallel IN Serial OUT» .

Таким образом, происходит операция сдвига вправо.

Таким образом, происходит операция сдвига вправо.  Если этот вход установлен на 0, то выполняется операция последовательного переключения. Если соединить вход управления режимами с землей, то схема будет работать как «двунаправленный» регистр . Схема универсального сдвигового регистра приведена ниже. Когда ввод передается на последовательный ввод , регистр выполняет операцию «последовательный левый». Когда ввод передается на ввод D , регистр выполняет операцию последовательного права.

Если этот вход установлен на 0, то выполняется операция последовательного переключения. Если соединить вход управления режимами с землей, то схема будет работать как «двунаправленный» регистр . Схема универсального сдвигового регистра приведена ниже. Когда ввод передается на последовательный ввод , регистр выполняет операцию «последовательный левый». Когда ввод передается на ввод D , регистр выполняет операцию последовательного права.