Что такое сдвиговый регистр в цифровой логике. Какие бывают типы сдвиговых регистров. Как работают сдвиговые регистры SISO, SIPO, PISO и PIPO. Для чего используются сдвиговые регистры в электронике.

Что такое сдвиговый регистр в цифровой логике

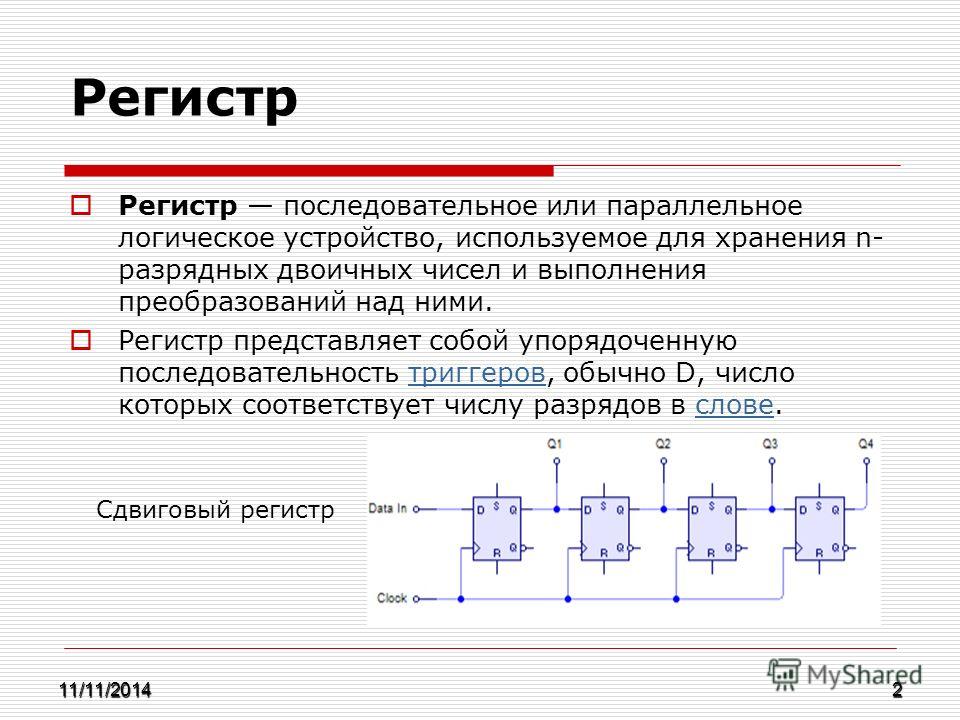

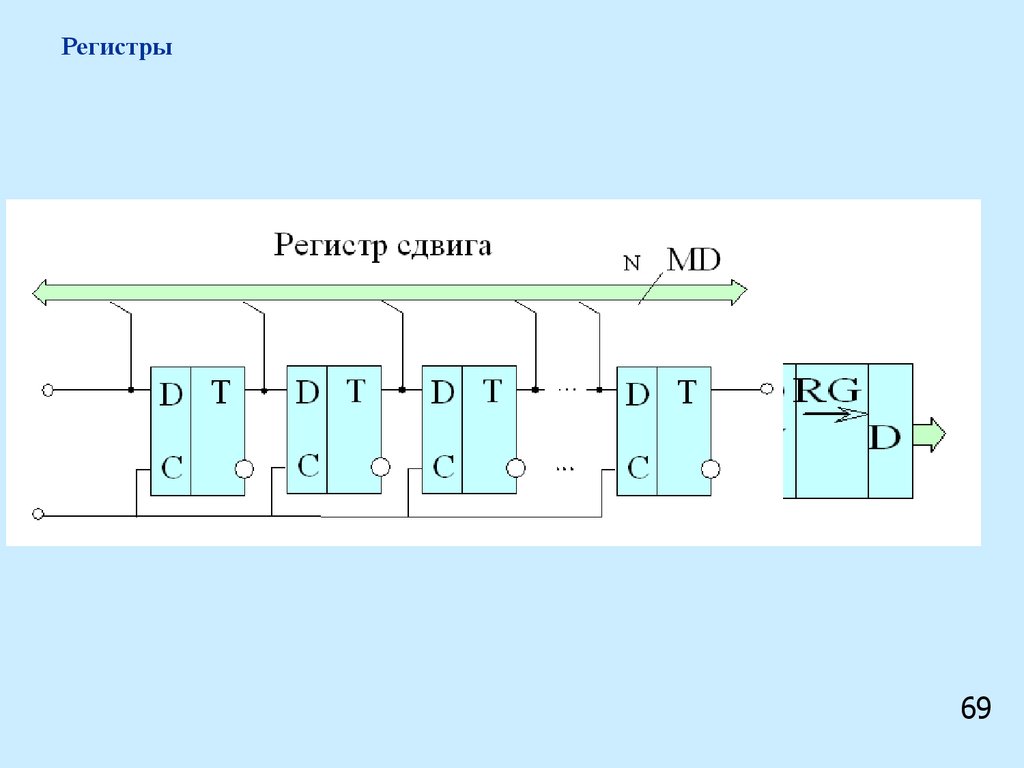

Сдвиговый регистр — это последовательность триггеров, соединенных таким образом, что содержимое каждого триггера может передаваться («сдвигаться») в соседний триггер при подаче тактового сигнала. Сдвиговые регистры используются для хранения и передвижения цифровых данных.

Основные особенности сдвиговых регистров:

- Состоят из последовательно соединенных триггеров (обычно D-триггеров)

- Могут сдвигать данные влево или вправо

- Используются для временного хранения и преобразования данных

- Бывают последовательные и параллельные по входу/выходу

- Управляются тактовыми импульсами

Основные типы сдвиговых регистров

Существует 4 основных типа сдвиговых регистров в зависимости от способа ввода и вывода данных:

- SISO (Serial In — Serial Out) — последовательный вход, последовательный выход

- SIPO (Serial In — Parallel Out) — последовательный вход, параллельный выход

- PISO (Parallel In — Serial Out) — параллельный вход, последовательный выход

- PIPO (Parallel In — Parallel Out) — параллельный вход, параллельный выход

Рассмотрим подробнее принцип работы каждого из этих типов.

Сдвиговый регистр SISO (последовательный вход — последовательный выход)

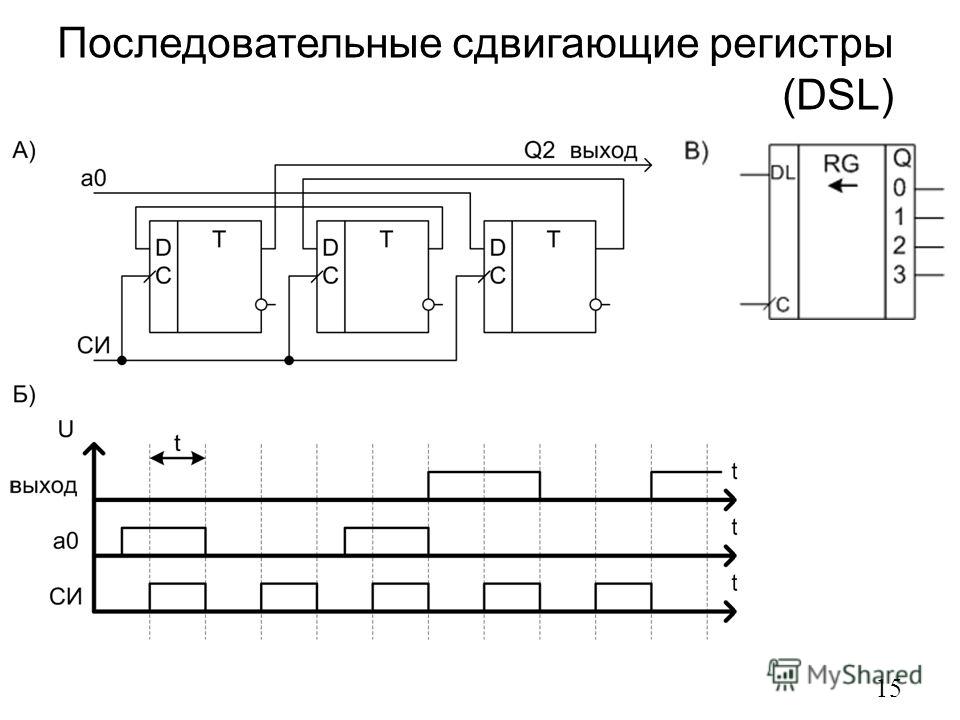

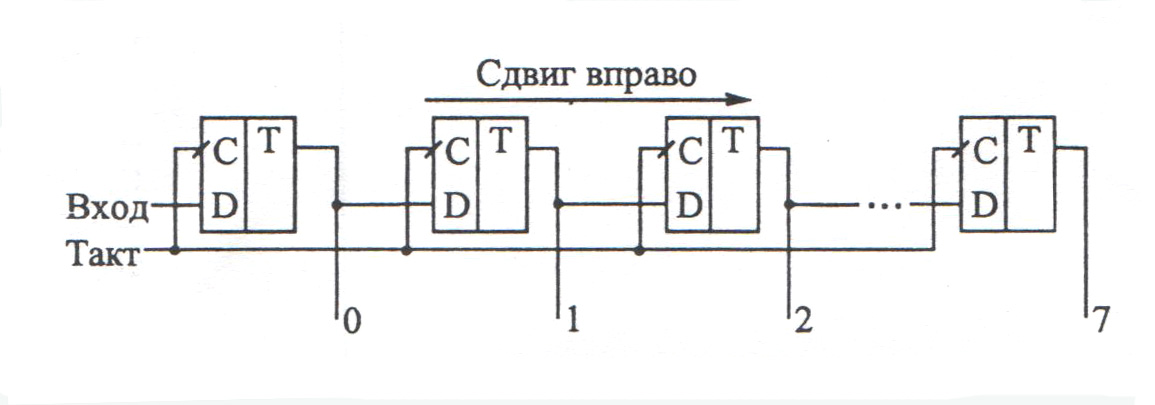

Схема сдвигового регистра SISO состоит из последовательно соединенных D-триггеров. Данные поступают на вход первого триггера и при каждом тактовом импульсе сдвигаются на один разряд вправо.

Принцип работы SISO регистра:

- Данные подаются последовательно на вход первого триггера

- При каждом тактовом импульсе содержимое каждого триггера сдвигается в следующий

- С выхода последнего триггера снимаются выходные данные в последовательном виде

SISO регистры используются в основном как линии задержки сигнала.

Сдвиговый регистр SIPO (последовательный вход — параллельный выход)

SIPO регистр также состоит из цепочки D-триггеров, но имеет параллельные выходы с каждого триггера.

Принцип работы:

- Данные подаются последовательно на вход

- При каждом такте данные сдвигаются на один разряд

- Выходные данные снимаются параллельно со всех триггеров

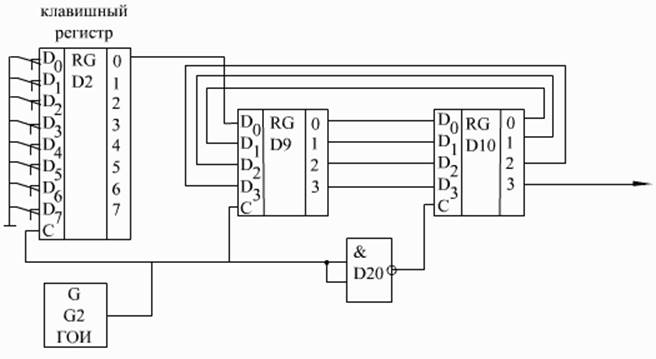

SIPO регистры применяются для преобразования последовательного кода в параллельный.

Сдвиговый регистр PISO (параллельный вход — последовательный выход)

PISO регистр имеет параллельные входы для загрузки данных и последовательный выход.

Принцип работы:

- Данные загружаются параллельно во все триггеры

- При тактировании данные последовательно выдвигаются через последний триггер

PISO регистры используются для преобразования параллельного кода в последовательный.

Сдвиговый регистр PIPO (параллельный вход — параллельный выход)

PIPO регистр имеет параллельные входы и выходы для каждого разряда.

Принцип работы:

- Данные загружаются параллельно во все триггеры

- При тактировании данные сдвигаются на один разряд

- Выходные данные снимаются параллельно со всех триггеров

PIPO регистры применяются для временного хранения и задержки многоразрядных двоичных чисел.

Применение сдвиговых регистров в цифровой электронике

Основные области применения сдвиговых регистров:

- Временное хранение данных

- Преобразование последовательного кода в параллельный и наоборот

- Создание линий задержки сигнала

- Реализация сдвига двоичных чисел (умножение/деление на 2)

- Формирование последовательностей импульсов

- Построение счетчиков и генераторов

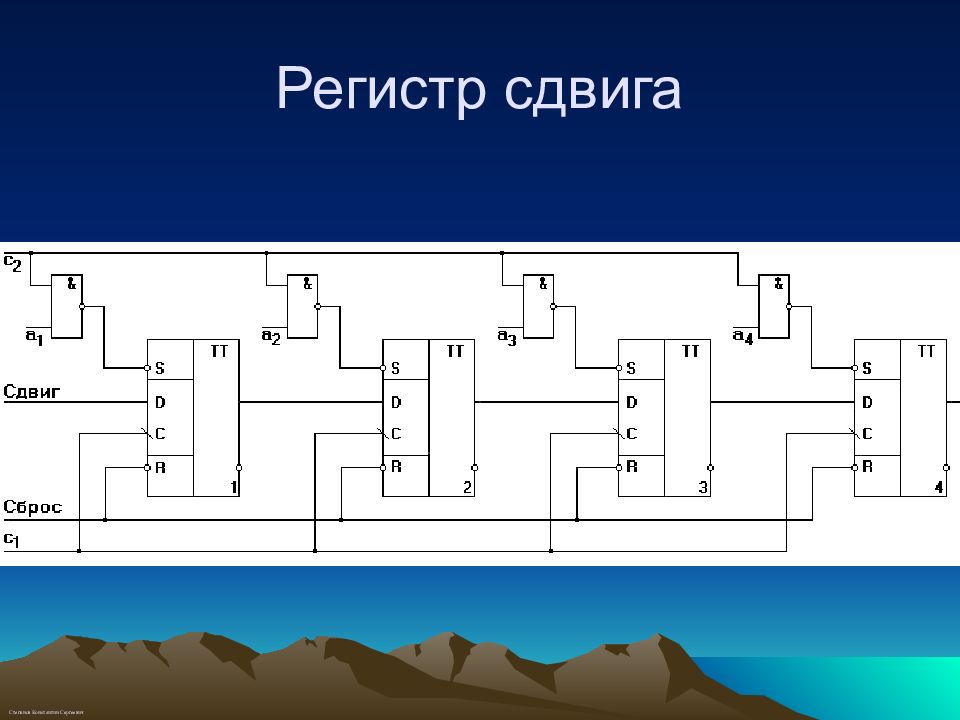

Двунаправленные сдвиговые регистры

Двунаправленные сдвиговые регистры позволяют сдвигать данные как вправо, так и влево. Направление сдвига задается управляющим сигналом.Возможности двунаправленных регистров:

- Сдвиг влево — эквивалентно умножению на 2

- Сдвиг вправо — эквивалентно делению на 2

- Гибкое манипулирование двоичными числами

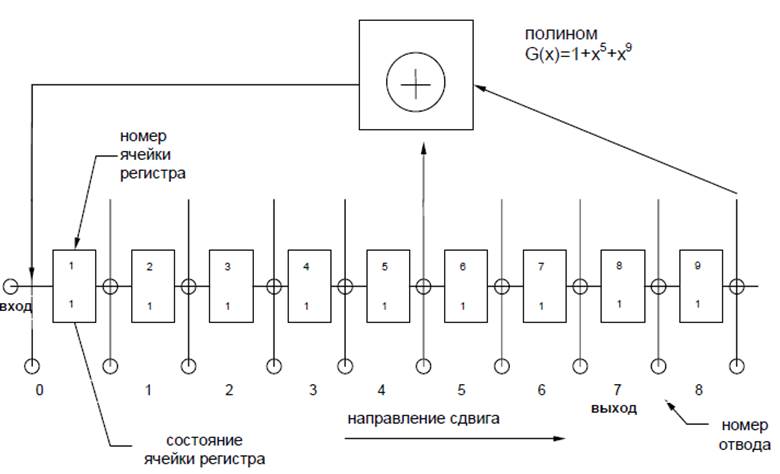

Кольцевые счетчики на основе сдвиговых регистров

Кольцевой счетчик — это сдвиговый регистр, у которого выход последнего разряда соединен со входом первого. При циклическом сдвиге формируется последовательность состояний.

Особенности кольцевых счетчиков:

- Простая реализация на сдвиговом регистре

- Самодекодирование состояний

- Применяются в распределителях импульсов

Счетчик Джонсона на основе сдвигового регистра

Счетчик Джонсона — это кольцевой счетчик с инверсной обратной связью. Он формирует последовательность из 2n состояний на n-разрядном регистре.

Преимущества счетчика Джонсона:

- Удвоенное количество состояний по сравнению с обычным кольцевым счетчиком

- Простая схема декодирования состояний

- Применяется в генераторах последовательностей

Заключение

Сдвиговые регистры являются важными функциональными узлами цифровых устройств. Они позволяют манипулировать двоичными данными, выполнять преобразования кодов, реализовывать задержки и формировать последовательности. Понимание принципов работы различных типов сдвиговых регистров необходимо для проектирования цифровых схем.

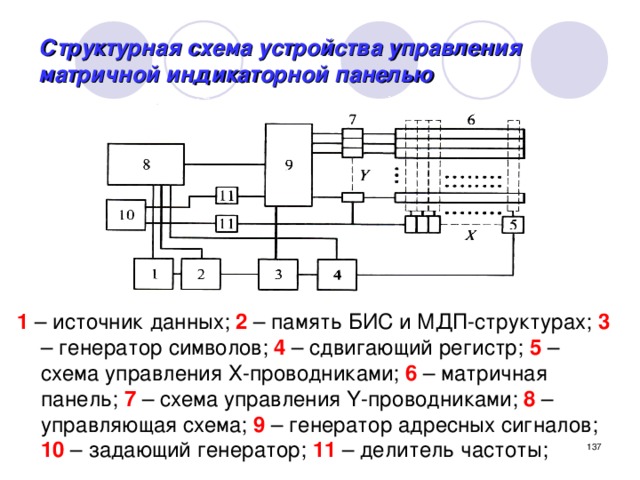

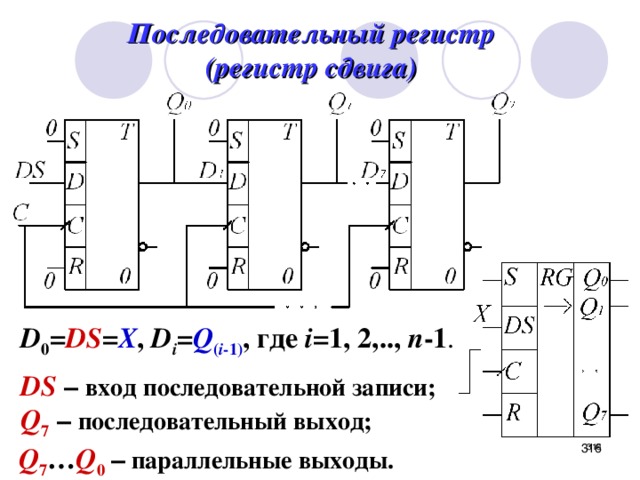

1.5 Сдвигающие регистры

Сдвигающий регистр служит для хранения кода числа и выполнения операции сдвига кода. Сдвиг кода – это перемещение в регистре кода числа на какое-либо число разрядов влево или вправо. В этом случае разряды числа, вышедшие из разрядной сетки регистра влево или вправо, теряются, а в освободившиеся при сдвиге разряды регистра записываются нули. Поскольку для позиционных систем счисления вес каждого символа кода определяется его положением в коде, то сдвиг кода числа на один разряд влево относительно принятой разрядной сетки соответствует умножению величины числа на основание системы счисления, а сдвиг вправо – делению при условии, что справа и слева есть свободные разряды и не происходит потеря единиц. Сдвигающий регистр используется также для преобразования параллельного кода в последовательный и наоборот.

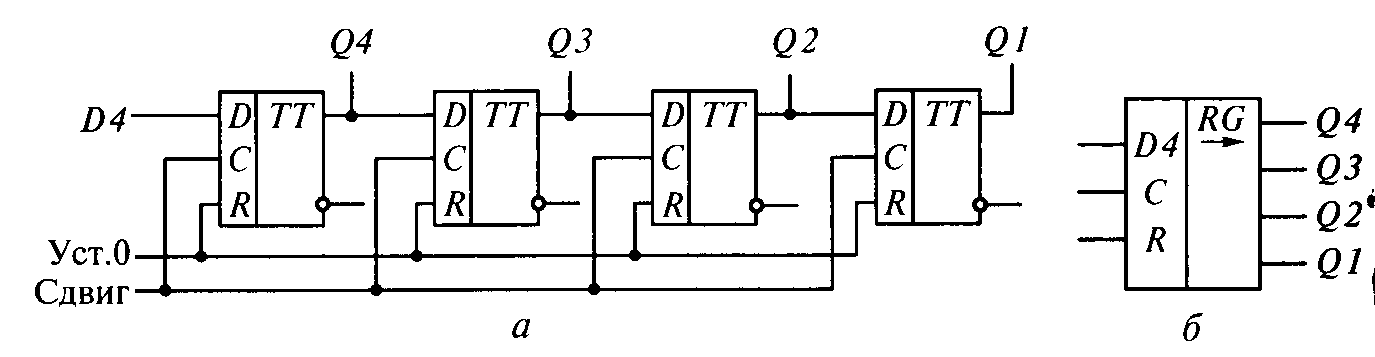

Для

осуществления операции сдвига вводят

специальные цепи сдвига. Структура

сдвигающего регистра зависит от типа

используемых элементов, от требуемого

быстродействия и от ограничений,

налагаемых на количество оборудования. На рисунке 7.6 изображена схема парафазного

сдвигающего регистра на RS-триггерах.

Здесь кроме основных триггеров,

выполняющих функции хранения кода

числа, имеются дополнительные, буферные

или промежуточные триггеры (понятие

основных и дополнительных чисто

условное). Очевидно, что нельзя записывать

в триггер

На рисунке 7.6 изображена схема парафазного

сдвигающего регистра на RS-триггерах.

Здесь кроме основных триггеров,

выполняющих функции хранения кода

числа, имеются дополнительные, буферные

или промежуточные триггеры (понятие

основных и дополнительных чисто

условное). Очевидно, что нельзя записывать

в триггер

В схеме на рисунке 2.6 будем считать триггеры Ti-1, Ti, Ti+1 основными, в которых хранится код числа, подлежащего сдвигу, а триггеры , , – дополнительными или промежуточными.

При

подаче управляющего сигнала Y1

код i

1 разряда слова передается в промежуточный

триггер

,

а

в

и т.

Рисунок 7.6 – Схема сдвигающего регистра

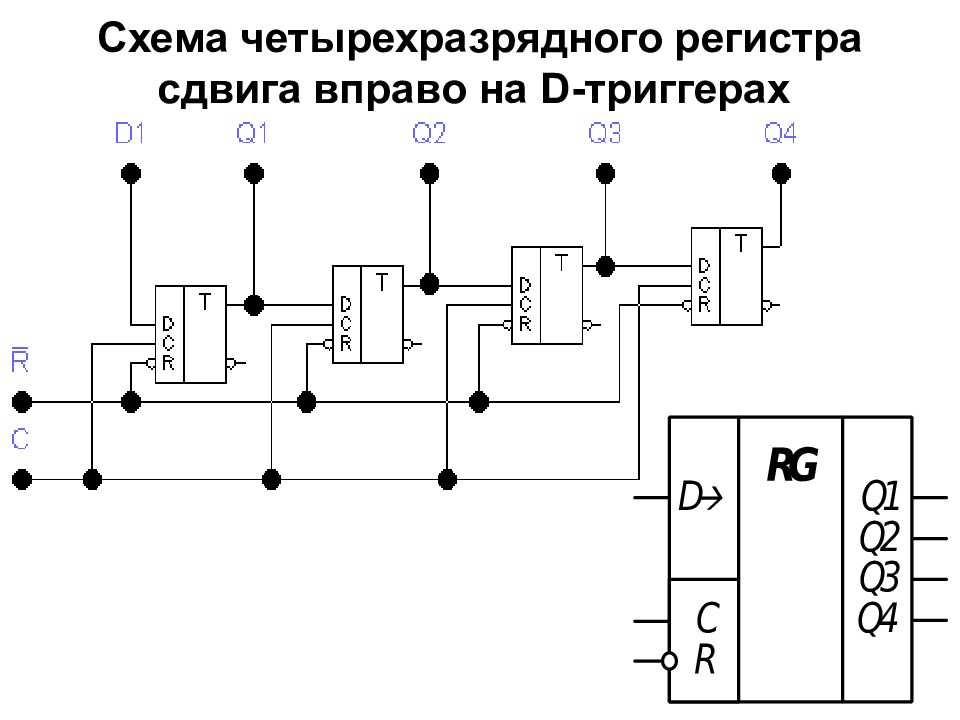

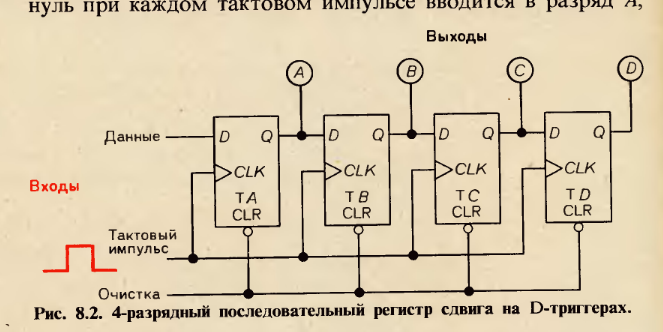

Естественно, что в регистрах, построенных на двухъярусных триггерах, не требуется применение элементов задержки или дополнительных промежуточных триггеров, так как начало (фронт) тактового импульса в таком триггере производит запись в ведущий триггер, а конец тактового импульса (срез) переписывает этот код из ведущего в ведомый, т. е. функции дополнительного триггера в каждом разряде выполняет ведущий триггер, а основного – ведомый, с которого и снимается информация. На рисунке 7.7 изображена схема регистра сдвига вправо на двух- ярусных

Работает схема следующим образом. Подачей сигнала y1 все триггеры устанавливаются в состояние «0». Далее производится запись кода числа х1, х2, х3, х4, например, 1l01, по установочным входам S-триггеров. Затем подачей тактовых импульсов y2 на шину синхронизации С производится сдвиг вправо кода числа, записанного в регистр. Состояния триггеров регистра после подачи тактовых импульсов T1 – Т4 сведены в таблицу 7.1.

Следует отметить, что входы J и К первого триггера заземлены, что соответствует коду «0», который и записывается в первый триггер после прихода каждого тактового импульса.

На рисунке 7.8 приведены временные диаграммы, поясняющие принцип работы схемы.

Рисунок 7.7 – Схема регистра сдвига вправо на JK-триггерах

Т

а б л и ц а 7. 1 – Состояния

триггеров регистра

1 – Состояния

триггеров регистра

|

Тактовые импульсы |

Выходы триггеров | |||

|

Q1 |

Q2 |

Q3 |

Q4 | |

|

T0 |

1 |

1 |

0 |

1 |

|

T1 |

0 |

1 |

1 |

0 |

|

T2 |

0 |

0 |

1 |

1 |

|

T3 |

0 |

0 |

0 |

1 |

|

Т4 |

0 |

0 |

0 |

0 |

Существуют

схемы реверсивных сдвиговых регистров,

которые позволяют производить сдвиг

кода числа как вправо, так и влево. Они

могут быть однотактными и двухтактными

с однофазными и парафазными цепями

передачи, с параллельной и последовательной

записью.

Они

могут быть однотактными и двухтактными

с однофазными и парафазными цепями

передачи, с параллельной и последовательной

записью.

Рисунок 7.8 – Временная диаграмма регистра

Цифровые схемы — сдвиговые регистры

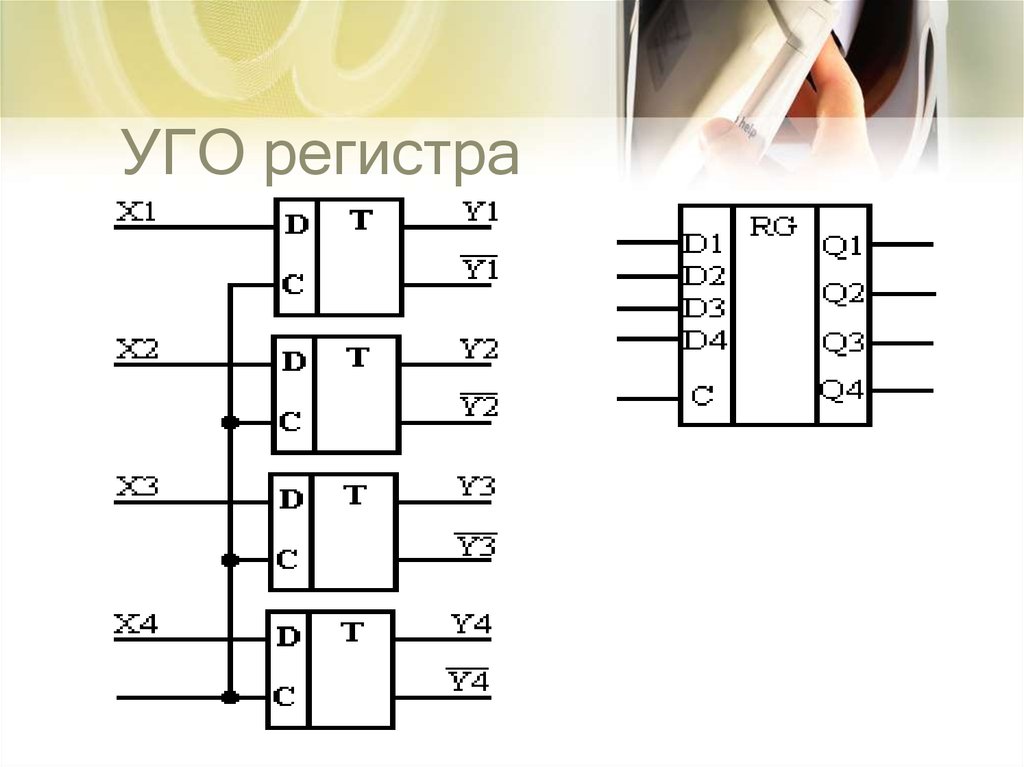

Мы знаем, что один триггер может хранить один бит информации. Чтобы хранить несколько битов информации, нам нужно несколько триггеров. Группа триггеров, которые используются для хранения (хранения) двоичных данных, называется регистром .

Если регистр способен сдвигать биты либо вправо, либо влево, это называется регистром сдвига . Регистр сдвига битов «N» содержит триггеры «N». Ниже приведены четыре типа регистров сдвига, основанные на применении входов и доступе к выходам.

- Serial In – сдвиговый регистр Serial Out

- Серийный вход – параллельный выходной регистр сдвига

- Параллельный вход – сдвиговый регистр последовательного выхода

- Параллельный вход – сдвиговый регистр параллельного выхода

Серийный вход – Серийный выход (SISO) Сдвиговый регистр

Сдвиговый регистр, который допускает последовательный ввод и производит последовательный вывод, известен как сдвиговый регистр Serial In – Serial Out (SISO) . Блок-схема 3-битного регистра сдвига SISO показана на следующем рисунке.

Блок-схема 3-битного регистра сдвига SISO показана на следующем рисунке.

Эта блок-схема состоит из трех D-триггеров, которые каскадируются . Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронны друг с другом, поскольку к каждому из них применяется один и тот же тактовый сигнал.

В этом регистре сдвига мы можем посылать биты последовательно со входа самого левого D-триггера. Следовательно, этот вход также называется последовательным входом . При каждом срабатывании положительного фронта тактового сигнала данные перемещаются с одной ступени на другую. Таким образом, мы можем получать биты последовательно с выхода самого правого D-триггера. Следовательно, этот выход также называется последовательным выходом .

пример

Давайте посмотрим, как работает 3-битный регистр сдвига SISO, посылая двоичную информацию «011» из LSB в MSB последовательно на входе.

Предположим, что начальный статус D-триггеров слева направо равен Q2Q1Q0=000. Мы можем понять работу 3-битного регистра сдвига SISO из следующей таблицы.

| Нет положительного края часов | Последовательный ввод | Q 2 | Q 1 | Q 0 |

|---|---|---|---|---|

| 0 | – | 0 | 0 | 0 |

| 1 | 1 (LSB), | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0 (СЗБ) | 0 | 1 | 1 (LSB), |

| 4 | – | – | 0 | 1 |

| 5 | – | – | – | 0 (СЗБ) |

Начальное состояние D-триггеров в отсутствие тактового сигнала: Q2Q1Q0=000. Здесь последовательный вывод исходит из Q0. Таким образом, LSB (1) принимается на 3- м положительном фронте тактового сигнала, а MSB (0) принимается на 5- м положительном фронте тактового сигнала.

Следовательно, 3-битный сдвиговый регистр SISO требует пяти тактовых импульсов для получения действительного выхода. Аналогично, N-битный сдвиговый регистр SISO требует 2N-1 тактовых импульсов для сдвига «N» битовой информации.

Сдвиговый регистр Serial In – Parallel Out (SIPO)

Сдвиговый регистр, который допускает последовательный ввод и производит параллельный вывод, известен как сдвиговый регистр Serial In – Parallel Out (SIPO) . Блок-схема 3-битного регистра сдвига SIPO показана на следующем рисунке.

Эта схема состоит из трех D-триггеров, которые каскадно. Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронны друг с другом, поскольку к каждому из них применяется один и тот же тактовый сигнал.

В этом регистре сдвига мы можем посылать биты последовательно со входа самого левого D-триггера. Следовательно, этот вход также называется последовательным входом . При каждом срабатывании положительного фронта тактового сигнала данные перемещаются с одной ступени на другую. В этом случае мы можем получить доступ к выходам каждого D триггера параллельно. Итак, мы получим параллельные выходы из этого регистра сдвига.

При каждом срабатывании положительного фронта тактового сигнала данные перемещаются с одной ступени на другую. В этом случае мы можем получить доступ к выходам каждого D триггера параллельно. Итак, мы получим параллельные выходы из этого регистра сдвига.

пример

Давайте посмотрим, как работает 3-битный регистр сдвига SIPO, посылая двоичную информацию «011» из LSB в MSB последовательно на входе.

Предположим, что начальный статус D-триггеров слева направо равен Q2Q1Q0=000. Здесь Q2 & Q0 – это MSB и LSB соответственно. Мы можем понять работу 3-битного сдвигового регистра SIPO из следующей таблицы.

| Нет положительного края часов | Последовательный ввод | Q 2 (MSB) | Q 1 | Q 0 (LSB) |

|---|---|---|---|---|

| 0 | – | 0 | 0 | 0 |

| 1 | 1 (LSB), | 1 | 0 | 0 |

| 2 | 1 | 1 | 1 | 0 |

| 3 | 0 (СЗБ) | 0 | 1 | 1 |

Начальное состояние D-триггеров в отсутствие тактового сигнала: Q2Q1Q0=000. Двоичная информация «011» получается параллельно на выходах D триггеров для третьего положительного фронта тактового сигнала.

Двоичная информация «011» получается параллельно на выходах D триггеров для третьего положительного фронта тактового сигнала.

Итак, 3-битный сдвиговый регистр SIPO требует три тактовых импульса для получения действительного выхода. Аналогично, N-битный сдвиговый регистр SIPO требует N тактовых импульсов для сдвига «N» битовой информации.

Сдвиговый регистр параллельного входа – последовательного выхода (PISO)

Сдвиговый регистр, который допускает параллельный ввод и производит последовательный выход, известен как сдвиговый регистр Parallel In-Serial Out (PISO) . Блок-схема 3-битного регистра сдвига PISO показана на следующем рисунке.

Эта схема состоит из трех D-триггеров, которые каскадно. Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронны друг с другом, поскольку к каждому из них применяется один и тот же тактовый сигнал.

В этом регистре сдвига мы можем применить параллельные входы к каждому D-триггеру, установив Preset Enable в 1. Для каждого срабатывания положительного фронта тактового сигнала данные сдвигаются от одного этапа к следующему. Итак, мы получим последовательный вывод с самого правого D-триггера.

Для каждого срабатывания положительного фронта тактового сигнала данные сдвигаются от одного этапа к следующему. Итак, мы получим последовательный вывод с самого правого D-триггера.

пример

Давайте посмотрим, как работает 3-битный регистр сдвига PISO, применяя двоичную информацию «011» параллельно через предустановленные входы.

Так как предустановленные входные данные применяются до положительного фронта тактового сигнала, начальное состояние D-триггеров от крайнего левого к правому будет Q2Q1Q0=011. Мы можем понять работу 3-битного регистра сдвига PISO из следующей таблицы.

| Нет положительного края часов | Q 2 | Q 1 | Q 0 |

|---|---|---|---|

| 0 | 0 | 1 | 1 (LSB), |

| 1 | – | 0 | 1 |

| 2 | – | – | 0 (LSB) |

Здесь последовательный вывод исходит из Q0. Таким образом, LSB (1) принимается до применения положительного фронта тактового сигнала, а MSB (0) принимается на 2- ом положительном фронте тактового сигнала.

Таким образом, LSB (1) принимается до применения положительного фронта тактового сигнала, а MSB (0) принимается на 2- ом положительном фронте тактового сигнала.

Следовательно, 3-битный регистр сдвига PISO требует двух тактовых импульсов для получения действительного выхода. Аналогично, N-битный регистр сдвига PISO требует N-1 тактовых импульсов, чтобы сдвигать N-битную информацию.

Регистр сдвига параллельного входа – параллельного выхода (PIPO)

Сдвиговый регистр, который допускает параллельный ввод и производит параллельный вывод, известен как сдвиговый регистр Parallel In – Parallel Out (PIPO) . Блок-схема 3-битного регистра сдвига PIPO показана на следующем рисунке.

Эта схема состоит из трех D-триггеров, которые каскадно. Это означает, что выход одного D-триггера подключен как вход следующего D-триггера. Все эти триггеры синхронны друг с другом, поскольку к каждому из них применяется один и тот же тактовый сигнал.

В этом регистре сдвига мы можем применить параллельные входы к каждому D-триггеру, установив Preset Enable в 1. Мы можем применить параллельные входы через предустановку или сброс. Эти два являются асинхронными входами. Это означает, что триггеры производят соответствующие выходные данные, основываясь на значениях асинхронных входных данных. В этом случае влияние выходов не зависит от тактового перехода. Итак, мы получим параллельные выходы от каждого D-триггера.

пример

Давайте посмотрим, как работает 3-битный регистр сдвига PIPO, применяя двоичную информацию «011» параллельно через предустановленные входы.

Так как предустановленные входные данные применяются до положительного фронта тактового сигнала, начальное состояние D-триггеров от крайнего левого к правому будет Q2Q1Q0=011. Таким образом, двоичная информация «011» получается параллельно на выходах D триггеров перед применением положительного фронта тактового сигнала.

Следовательно, 3-битный регистр сдвига PIPO требует нулевых тактовых импульсов для получения действительного выхода. Аналогично, N-битный регистр сдвига PIPO не требует никакого тактового импульса для сдвига информации «N» битов.

Сдвиговые регистры в цифровой логике

Триггеры могут использоваться для хранения одного бита двоичных данных (1 или 0). Однако для хранения нескольких битов данных нам нужно несколько триггеров. Необходимо подключить N триггеров, чтобы хранить n бит данных. Регистр — это устройство, которое используется для хранения такой информации. Это группа последовательно соединенных триггеров, используемых для хранения нескольких битов данных.

Информация, хранящаяся в этих регистрах, может быть передана с помощью регистры сдвига . Сдвиговый регистр — это группа триггеров, используемых для хранения нескольких битов данных. Биты, хранящиеся в таких регистрах, могут перемещаться внутри регистров и в/из регистров с помощью тактовых импульсов. N-битный сдвиговый регистр может быть сформирован путем соединения n триггеров, где каждый триггер хранит один бит данных.

N-битный сдвиговый регистр может быть сформирован путем соединения n триггеров, где каждый триггер хранит один бит данных.

Регистры, которые сдвигают биты влево, называются «регистрами сдвига влево».

Регистры, которые сдвигают биты вправо, называются «регистрами сдвига вправо».

Сдвиговые регистры бывают четырех типов. Это:

- Последовательный вход Последовательный выход

- Последовательный вход Параллельный выход

- Параллельный вход Последовательный выход

- Параллельный вход

Последовательный вход Сдвиговый регистр (SISO) –

Сдвиговый регистр, который обеспечивает последовательный ввод (один бит за другим через одну линию данных) и производит последовательный вывод, называется регистром сдвига Serial-In Serial-Out. Поскольку есть только один выход, данные покидают регистр сдвига по одному биту за раз в последовательном шаблоне, отсюда и название регистра сдвига с последовательным вводом и выводом.

Приведенная ниже логическая схема показывает сдвиговый регистр последовательного ввода-вывода. Схема состоит из четырех D-триггеров, соединенных последовательно. Все эти триггеры синхронны друг с другом, поскольку на каждый триггер подается один и тот же тактовый сигнал.

Схема состоит из четырех D-триггеров, соединенных последовательно. Все эти триггеры синхронны друг с другом, поскольку на каждый триггер подается один и тот же тактовый сигнал.

Вышеприведенная схема является примером сдвигового правого регистра, принимающего последовательные входные данные с левой стороны триггера. В основном SISO используется в качестве элемента задержки.

Регистр сдвига последовательного входа и параллельного выхода (SIPO) —

Сдвиговый регистр, который обеспечивает последовательный ввод (один бит за другим через одну линию данных) и производит параллельный вывод, известен как сдвиговый регистр Serial-In Parallel-Out.

Приведенная ниже логическая схема представляет сдвиговый регистр с последовательным входом и параллельным выходом. Схема состоит из четырех D-триггеров, которые соединены между собой. Сигнал очистки (CLR) подключается в дополнение к тактовому сигналу ко всем 4 триггерам для их СБРОСА. Выход первого триггера подключается ко входу следующего триггера и так далее. Все эти триггеры синхронны друг с другом, поскольку на каждый триггер подается один и тот же тактовый сигнал.

Все эти триггеры синхронны друг с другом, поскольку на каждый триггер подается один и тот же тактовый сигнал.

Вышеприведенная схема представляет собой пример сдвига правого регистра, который принимает последовательные входные данные с левой стороны триггера и производит параллельный вывод. Они используются в линиях связи, где требуется демультиплексирование линии данных на несколько параллельных линий, поскольку основное использование регистра SIPO заключается в преобразовании последовательных данных в параллельные данные.

Сдвиговый регистр с параллельным вводом и последовательным выводом (PISO) —

Сдвиговый регистр, допускающий параллельный ввод (данные подаются отдельно на каждый триггер и одновременно) и производящий последовательный вывод, называется параллельным вводом. Сдвиговый регистр последовательного выхода.

Приведенная ниже логическая схема показывает сдвиговый регистр с параллельным входом и последовательным выходом. Схема состоит из четырех D-триггеров, которые соединены между собой. Тактовый вход напрямую подключен ко всем триггерам, но входные данные подключаются к каждому триггеру индивидуально через мультиплексор на входе каждого триггера. Выход предыдущего триггера и параллельный ввод данных подключены к входу MUX, а выход MUX подключен к следующему триггеру. Все эти триггеры синхронны друг с другом, поскольку на каждый триггер подается один и тот же тактовый сигнал.

Тактовый вход напрямую подключен ко всем триггерам, но входные данные подключаются к каждому триггеру индивидуально через мультиплексор на входе каждого триггера. Выход предыдущего триггера и параллельный ввод данных подключены к входу MUX, а выход MUX подключен к следующему триггеру. Все эти триггеры синхронны друг с другом, поскольку на каждый триггер подается один и тот же тактовый сигнал.

Сдвиговый регистр Parallel in Serial out (PISO), используемый для преобразования параллельных данных в последовательные данные.

Сдвиговый регистр с параллельным вводом и параллельным выводом (PIPO) —

Сдвиговый регистр, допускающий параллельный ввод (данные подаются на каждый триггер отдельно и одновременно), а также производящий параллельный вывод, известен как параллельный вывод. Сдвиговый регистр с параллельным выходом.

Приведенная ниже логическая схема показывает сдвиговый регистр с параллельным входом и выходом. Схема состоит из четырех D-триггеров, которые соединены между собой. Сигнал очистки (CLR) и тактовые сигналы подключены ко всем 4 триггерам. В этом типе регистра нет взаимосвязей между отдельными триггерами, поскольку не требуется последовательного сдвига данных. Данные подаются в качестве входных данных отдельно для каждого триггера, и таким же образом выходные данные также собираются отдельно для каждого триггера.

Сигнал очистки (CLR) и тактовые сигналы подключены ко всем 4 триггерам. В этом типе регистра нет взаимосвязей между отдельными триггерами, поскольку не требуется последовательного сдвига данных. Данные подаются в качестве входных данных отдельно для каждого триггера, и таким же образом выходные данные также собираются отдельно для каждого триггера.

Сдвиговый регистр с параллельным выходом (PIPO) используется в качестве временного запоминающего устройства и, подобно сдвиговому регистру SISO, действует как элемент задержки.

Двунаправленный сдвиговый регистр —

Если мы сдвинем двоичное число влево на одну позицию, это будет эквивалентно умножению числа на 2, а если мы сдвинем двоичное число вправо на одну позицию, это будет эквивалентно делению число на 2. Для выполнения этих операций нам нужен регистр, который может сдвигать данные в любом направлении.

Двунаправленные сдвиговые регистры — это регистры, способные сдвигать данные вправо или влево в зависимости от выбранного режима. Если выбран режим 1 (высокий), данные будут сдвинуты вправо, а если выбран режим 0 (низкий), данные будут сдвинуты влево.

Если выбран режим 1 (высокий), данные будут сдвинуты вправо, а если выбран режим 0 (низкий), данные будут сдвинуты влево.

Приведенная ниже логическая схема показывает двунаправленный сдвиговый регистр. Схема состоит из четырех D-триггеров, которые соединены между собой. Входные данные подключаются к двум концам схемы и в зависимости от выбранного режима выбирается только один и вентиль находится в активном состоянии.

Счетчик регистров сдвига –

Счетчики регистров сдвига – это регистры сдвига, в которых выходы соединяются обратно со входами для создания определенных последовательностей. В основном они бывают двух типов:

- Кольцевой счетчик –

Кольцевой счетчик – это, по сути, счетчик сдвигового регистра, в котором выход первого триггера соединен со следующим триггером и т. д., а выход последнего триггер снова подается обратно на вход первого триггера, отсюда и название кольцевого счетчика. Шаблон данных в регистре сдвига будет циркулировать до тех пор, пока применяются тактовые импульсы.

Приведенная ниже логическая схема показывает счетчик звонков. Схема состоит из четырех D-триггеров, которые соединены между собой. Поскольку схема состоит из четырех триггеров, шаблон данных будет повторяться через каждые четыре тактовых импульса, как показано в приведенной ниже таблице истинности:

Кольцевой счетчик обычно используется, поскольку он является самодекодирующим. Для определения состояния счетчика не требуется дополнительная схема декодирования.

- Счетчик Джонсона –

Счетчик Джонсона в основном представляет собой счетчик регистра сдвига, в котором выход первого триггера подключается к следующему триггеру и т. д., а инвертированный выход последнего триггера снова подается обратно на вход первого триггера. . Они также известны как счетчики с витыми кольцами.Приведенная ниже логическая схема представляет собой счетчик Джонсона. Схема состоит из четырех D-триггеров, которые соединены между собой. Счетчик Джонсона с n стадиями дает последовательность счета из 2n различных состояний, поэтому он также известен как счетчик mod-2n.

Поскольку схема состоит из четырех триггеров, шаблон данных будет повторяться каждые восемь тактовых импульсов, как показано в таблице истинности ниже:0005

Поскольку схема состоит из четырех триггеров, шаблон данных будет повторяться каждые восемь тактовых импульсов, как показано в таблице истинности ниже:0005 Основное преимущество счетчика Джонсона состоит в том, что ему требуется всего n триггеров по сравнению с кольцевым счетчиком для передачи заданных данных для генерации последовательности из 2n состояний.

Применение сдвиговых регистров –

- Сдвиговые регистры используются для временного хранения данных.

- Сдвиговые регистры также используются для передачи данных и обработки данных.

- Сдвиговые регистры последовательного ввода-вывода и параллельного ввода-вывода используются для создания временной задержки в цифровых схемах.

- Сдвиговый регистр с последовательным входом и параллельным выходом используется для преобразования последовательных данных в параллельные данные, поэтому они используются в линиях связи, где требуется демультиплексирование линии данных на несколько параллельных линий.

- A Параллельный регистр последовательного вывода, используемый для преобразования параллельных данных в последовательные.

Ссылка –

Регистры – ee.usyd.edu.au

ОШИБКА — 404 — НЕ НАЙДЕНО

- Дом

- ☠

Наши серверные гномы не смогли найти страницу, которую вы ищете.

Похоже, вы неправильно набрали URL-адрес в адресной строке или перешли по старой закладке.

Возможно, некоторые из них могут вас заинтересовать?

Преобразователь RS232 SMD — MAX3232

В наличии COM-00589

Избранное Любимый 4

Список желаний

MIKROE Преобразование текста в речь Нажмите

Нет в наличии DEV-18873

45,95 $

Избранное Любимый 3

Список желаний

MIKROE BroadR-Reach Click

Нет в наличии КОМ-20200

69,95 $

Избранное Любимый 0

Список желаний

МИКРОЭ РН4678 Щелчок

Нет в наличии WRL-20279

38,95 $

Избранное Любимый 0

Список желаний

Обновление Qwiic для самодельной клавиатуры

11 февраля 2020 г.

Пересмотр и обновление моего проекта с раздельной клавиатурой с помощью нового Qwiic Pro Micro C.

Избранное Любимый 2

Топ-20 за 20 лет

4 января 2023 г.

Присоединяйтесь к нам в праздновании 20-летия SparkFun со скидками до 50 процентов на наши 20 лучших продуктов!

Избранное Любимый 0

Qwiic VR IMU (BNO080) Руководство по подключению

30 апреля 2018 г.

Выясните, как объекты ориентированы, с надежным 9 степенями свободы (DOF) BNO080 IMU. Может быть, вы даже сделаете свои собственные приложения виртуальной реальности (VR), если чувствуете себя сообразительными.

Избранное Любимый 2

Руководство по подключению средства обновления MicroMod

25 февраля 2021 г.