Как настроить и использовать интерфейс SPI на микроконтроллерах STM32F4. Какие режимы работы поддерживает SPI. Как сконфигурировать SPI в режиме ведущего и ведомого. Как работает SPI в полудуплексном режиме. Какие особенности имеет протокол SPI TI.

Основные характеристики интерфейса SPI в STM32F4

Последовательный периферийный интерфейс (SPI) в микроконтроллерах STM32F4 обладает следующими ключевыми возможностями:

- Поддержка полнодуплексной синхронной передачи данных

- Работа в режимах ведущего (master) и ведомого (slave) устройства

- Программируемая полярность и фаза тактового сигнала

- Программируемый порядок следования бит (MSB или LSB первым)

- Программируемая длина слова данных (8 или 16 бит)

- Аппаратная генерация и проверка CRC

- Поддержка DMA для передачи и приема данных

- Максимальная скорость передачи до 42 Мбит/с (для SPI1)

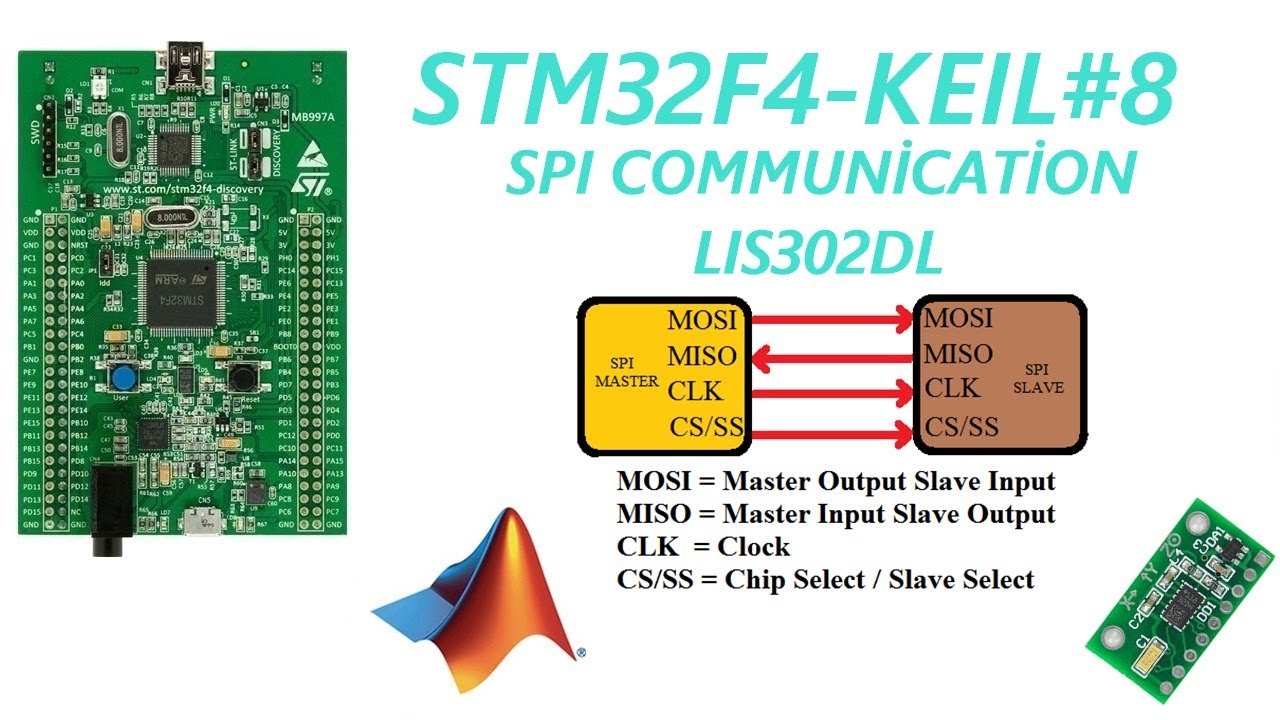

Интерфейс SPI использует 4 линии для связи:

- MOSI (Master Out Slave In) — линия передачи данных от ведущего к ведомому

- MISO (Master In Slave Out) — линия передачи данных от ведомого к ведущему

- SCK (Serial Clock) — тактовый сигнал, генерируемый ведущим устройством

- NSS (Slave Select) — сигнал выбора ведомого устройства

Настройка SPI в режиме ведомого (Slave)

Для конфигурирования SPI в режиме ведомого устройства необходимо выполнить следующие шаги:

- Настроить формат кадра данных (8 или 16 бит) с помощью бита DFF в регистре SPI_CR1

- Выбрать полярность (CPOL) и фазу (CPHA) тактового сигнала

- Настроить порядок передачи бит (MSB или LSB первым) битом LSBFIRST

- Настроить режим управления выводом NSS (программный или аппаратный)

- При необходимости включить режим TI битом FRF в регистре SPI_CR2

- Активировать режим ведомого, очистив бит MSTR и установив бит SPE в регистре SPI_CR1

После этого SPI будет готов к приему и передаче данных в режиме ведомого устройства.

Настройка SPI в режиме ведущего (Master)

Для конфигурирования SPI в режиме ведущего устройства выполняются следующие действия:

- Настроить скорость передачи с помощью битов BR[2:0] в регистре SPI_CR1

- Выбрать полярность (CPOL) и фазу (CPHA) тактового сигнала

- Настроить формат кадра данных (8 или 16 бит) битом DFF

- Настроить порядок передачи бит (MSB или LSB первым)

- Настроить режим управления выводом NSS

- При необходимости включить режим TI битом FRF в SPI_CR2

- Активировать режим ведущего, установив биты MSTR и SPE в регистре SPI_CR1

После этого SPI будет готов инициировать обмен данными в режиме ведущего устройства.

Полудуплексный режим работы SPI

SPI в STM32F4 поддерживает два варианта полудуплексного режима:

- С одной двунаправленной линией данных (BIDIMODE = 1)

- С однонаправленной линией данных только для приема или только для передачи (BIDIMODE = 0)

В первом случае направление передачи задается битом BIDIOE. Во втором случае можно отключить неиспользуемую линию данных и использовать ее для других целей.

Особенности протокола SPI TI

Интерфейс SPI в STM32F4 поддерживает протокол SPI TI, который имеет некоторые отличия от стандартного SPI:

- Фиксированные значения полярности и фазы тактового сигнала

- Специфическое управление сигналом NSS

- Особый формат кадра данных

Для включения режима TI необходимо установить бит FRF в регистре SPI_CR2. При этом настройки CPOL, CPHA и управления NSS игнорируются.

Использование DMA для обмена данными по SPI

Для повышения эффективности обмена данными по SPI можно использовать прямой доступ к памяти (DMA). Это позволяет передавать и принимать данные без постоянного участия процессора.

Чтобы настроить DMA для работы с SPI, нужно:

- Сконфигурировать канал DMA для работы с нужным интерфейсом SPI

- Настроить адреса источника и назначения данных

- Задать размер блока данных для передачи

- Включить запросы DMA от SPI в регистре SPI_CR2

- Активировать канал DMA

После этого обмен данными будет происходить автоматически без вмешательства процессора.

Обработка ошибок при работе с SPI

При использовании интерфейса SPI могут возникать различные ошибочные ситуации, которые необходимо обрабатывать:

- Ошибка режима ведущего (MODF) — возникает при конфликте на линии NSS

- Ошибка переполнения (OVR) — когда новые данные принимаются до чтения предыдущих

- Ошибка CRC — при несовпадении расчетного и принятого значения CRC

Для обработки этих ошибок можно:

- Включить соответствующие прерывания в регистре SPI_CR2

- Проверять флаги ошибок в регистре SPI_SR

- Реализовать корректирующие действия при возникновении ошибок

Правильная обработка ошибок повышает надежность обмена данными по SPI.

Оптимизация производительности SPI

Для достижения максимальной скорости обмена данными по SPI можно использовать следующие приемы:

- Выбор максимально возможной скорости передачи с учетом ограничений периферийных устройств

- Использование DMA для передачи и приема данных

- Минимизация времени между транзакциями SPI

- Оптимизация обработки прерываний SPI

- Использование 16-битного формата данных вместо 8-битного, где это возможно

Применение этих методов позволяет существенно повысить пропускную способность интерфейса SPI.

Заключение

Интерфейс SPI в микроконтроллерах STM32F4 предоставляет гибкие возможности для организации высокоскоростного обмена данными с периферийными устройствами. Правильная настройка и использование всех функций SPI позволяет эффективно решать широкий спектр задач, требующих быстрой передачи данных между компонентами системы.

|

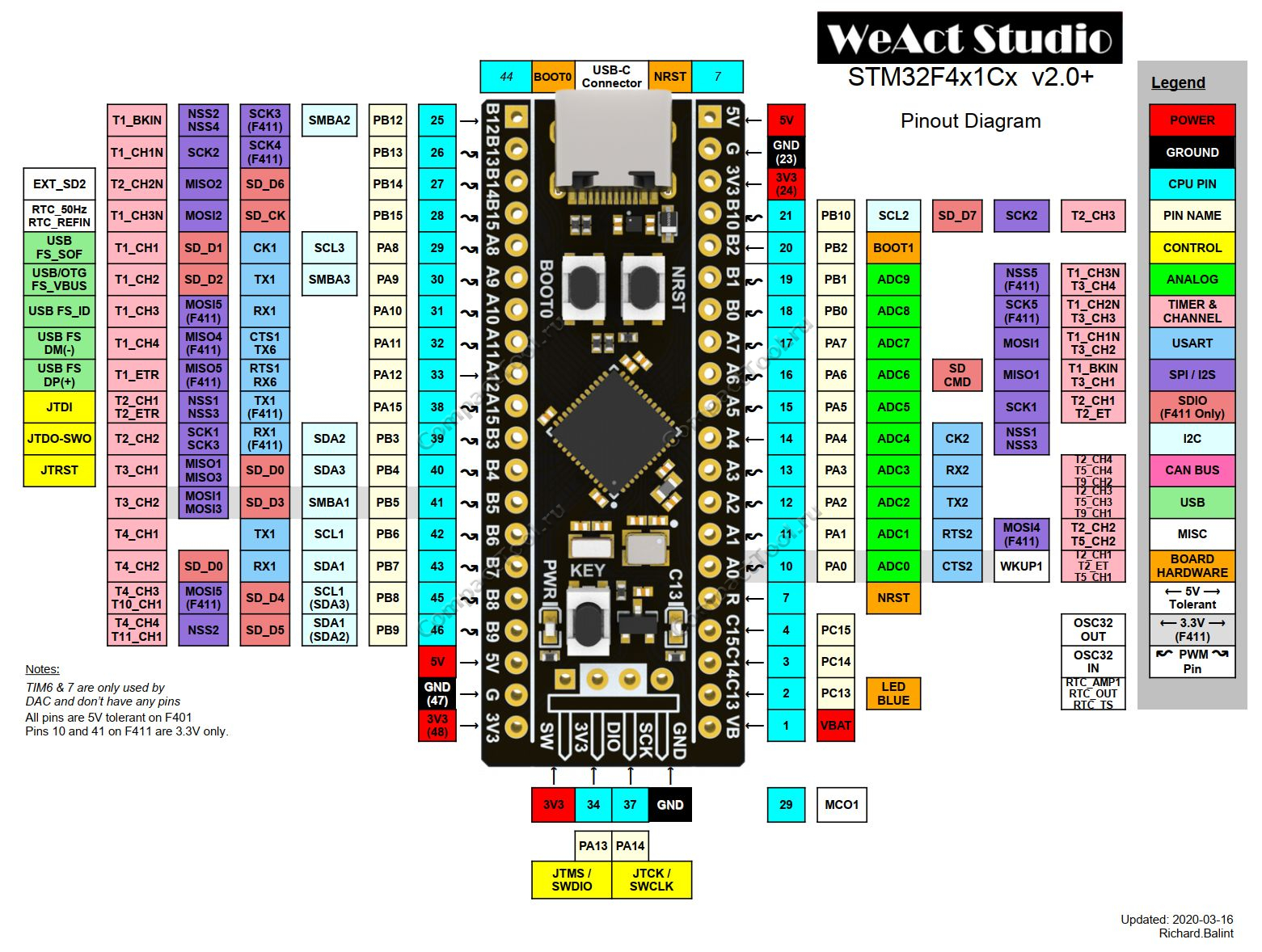

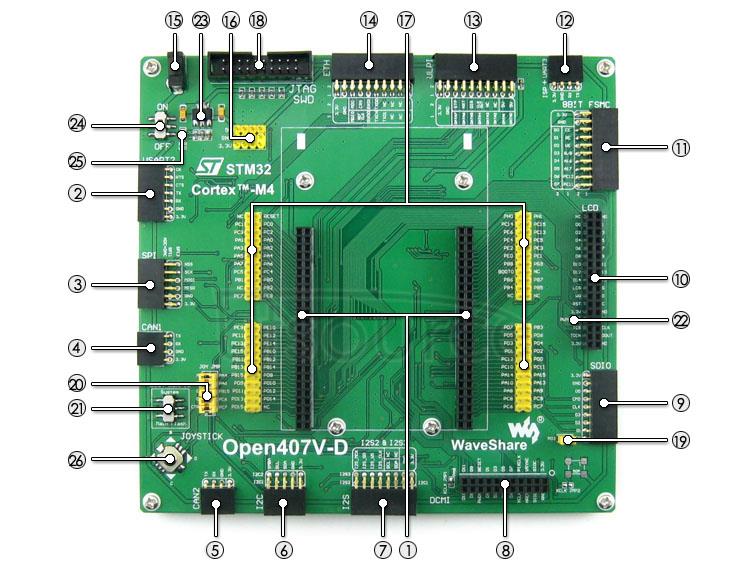

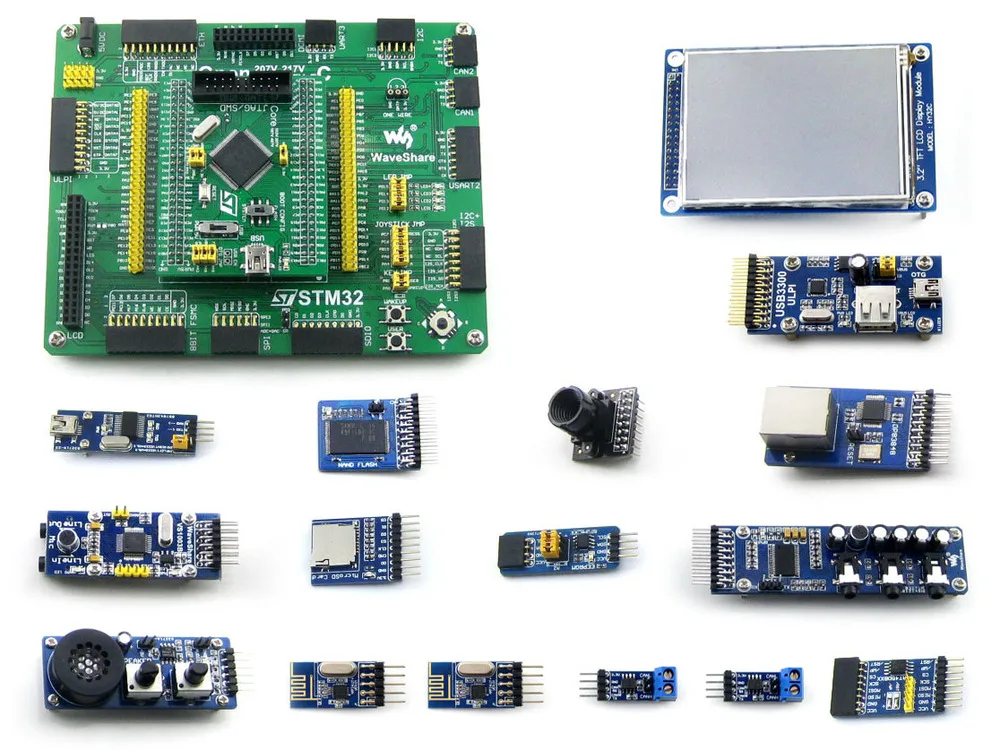

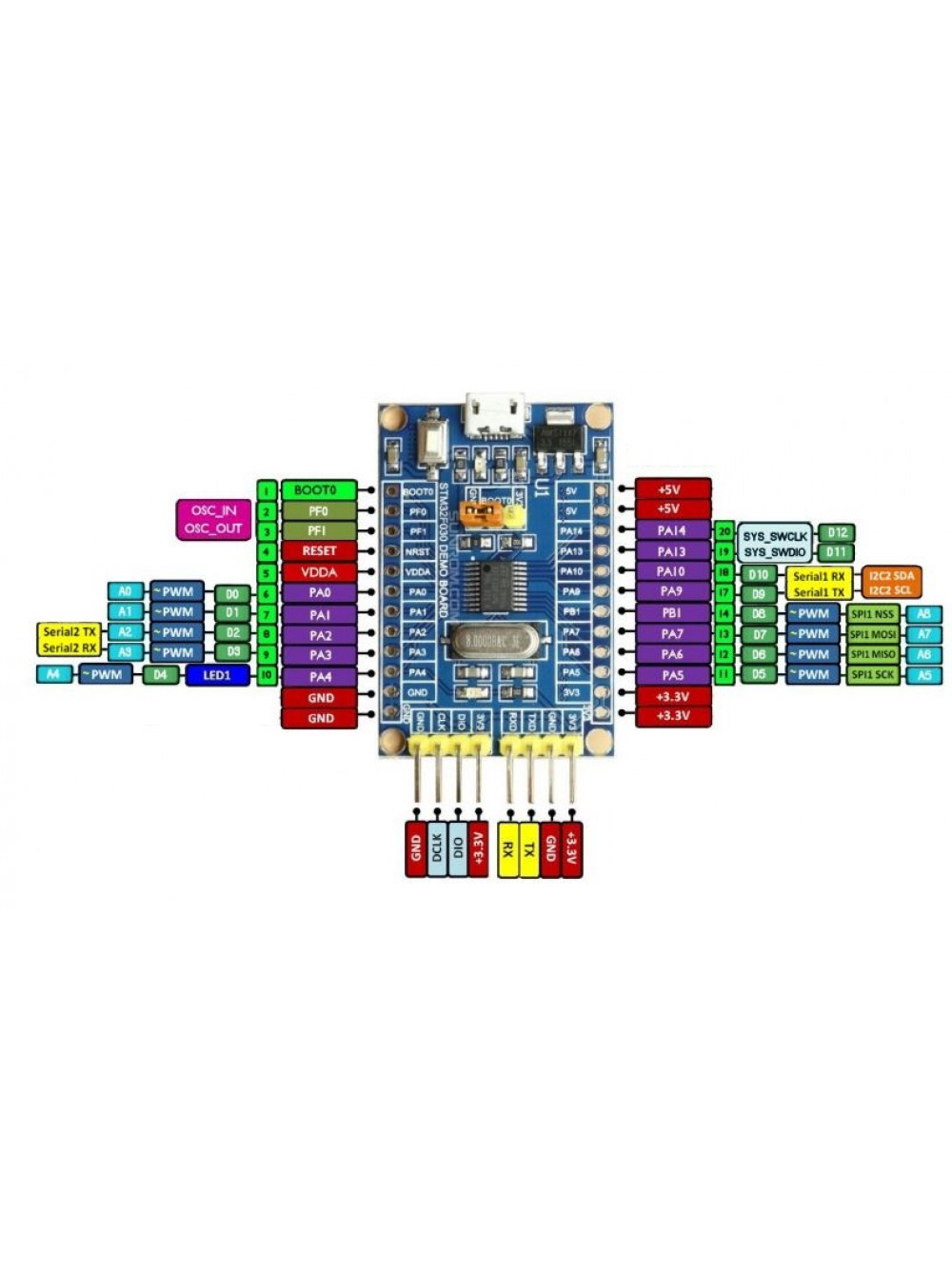

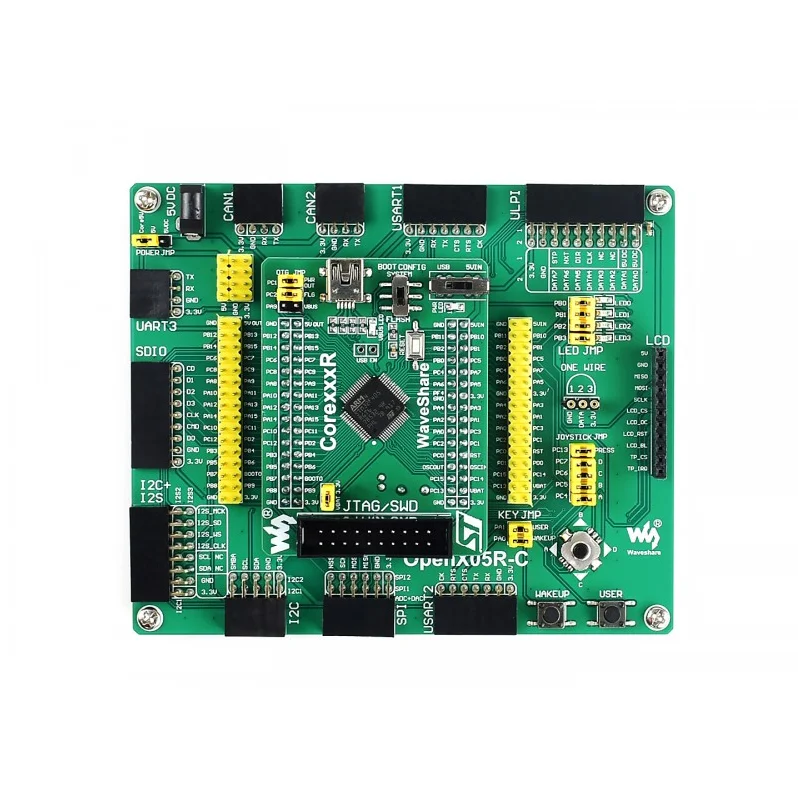

Здесь приведен перевод секции 28 Serial peripheral interface (SPI) из даташита RM0090 компании ST, посвященный микроконтроллерам STM32F405xx/07xx, STM32F415xx/17xx, STM32F42xxx и STM32F43xxx (с акцентом на STM32F407xx). Непонятные термины и сокращения см. в Словарике [3]. [SPI: введение] Интерфейс SPI предоставляет 2 главные функции — либо поддержка протокола SPI, либо протокола передачи звука I2S (по умолчанию выбран SPI). Можно программно переключать режим интерфейса с SPI на I2S. Прим. переводчика: в этом переводе описание режима I2S опущено. Последовательный периферийный интерфейс (serial peripheral interface, SPI) позволяет синхронно обмениваться данными с внешними устройствами в режимах полудуплекса и полного дуплекса. Интерфейс может быть сконфигурирован как мастер, и тогда он предоставляет сигнал тактирования данных (SCK) для внешнего подчиненного устройства. SPI может использоваться для различных целей, включая синхронные симплексные передачи по двум проводам, или надежный обмен данными с использованием проверки CRC. Предупреждение: поскольку некоторые выводы SPI1 и SPI3/I2S3 могут быть привязаны (mapped) на выводы, используемые интерфейсом JTAG (SPI1_NSS на JTDI, SPI3_NSS/I2S3_WS на JTDI и SPI3_SCK/I2S3_CK на JTDO), то у Вас есть следующие варианты: – запретить интерфейс JTAG и использовать интерфейс SWD до конфигурирования выводов, перечисленных как выводы SPI I/O (когда отлаживаете приложение микроконтроллера), – или запретить оба интерфейса и JTAG, и SWD (когда отладка не активна, и работает реальное приложение). За дополнительной информацией по поводу конфигурирования выводов интерфейсов JTAG/SWD обратитесь к секции даташита 8.3.2: I/O pin multiplexer and mapping (даташит RM0090). [SPI в микроконтроллере STM32F407ZGT6 и плата Olimex STM32-P407] На макетной плате Olimex STM32-P407 установлен микроконтроллер STM32F407ZGT6, у которого имеется всего 3 порта SPI: SPI1, SPI2, SPI3. На картинке показана цоколевка выводов корпуса LQFP144 микроконтроллера STM32F407ZGT6, которые могут быть задействованы для SPI1, SPI2, SPI3. 28. PC2/SPI2_MISO/OTG_HS_ULPI_DIR/ETH_MII_TXD2/ADC123_IN12 29. PC3/SPI2_MOSI/I2S2_SD/OTG_HS_ULPI_NXT/ETH_MII_TX_CLK/ADC123_IN13 40. PA4/SPI1_NSS/SPI3_NSS/USART2_CK/DCMI_HSYNC/OTG_HS_SOF/I2S3_WS/ADC12_IN4/DAC1_OUT 41. PA5/SPI1_SCK/OTG_HS_ULPI_CK/TIM2_Ch2_ETR/TIM8_CHIN/ADC12_IN5/DAC2_OUT 42. PA6/SPI1_MISO/TIM8_BKIN/TIM13_Ch2/DCMI_PIXCLK/TIM3_Ch2/TIM1_BKIN/ADC12_IN6 43. PA7/SPI1_MOSI/TIM8_Ch2N/TIM14_Ch2/TIM3_Ch3/ETH_MII_RX_DV/TIM1_Ch2N/RMII_CRS_DV/ADC12_IN7 69. PB10/SPI2_SCK/I2S2_CK/I2C2_SCL/USART3_TX/OTG_HS_ULPI_D3/ETH_MII_RX_ER/OTG_HS_SCL/TIM2_Ch4 73. PB12/SPI2_NSS/I2S2_WS/I2C2_SMBA/USART3_CK/TIM1_BKIN/CAN2_RX/OTG_HS_ULPI_D5/ETH_RMII_TXD0/ETH_MII_TXD0/OTG_HS_ID 74. PB13/SPI2_SCK/I2S2_CK/USART3_CTS/TIM1_Ch2N/CAN2_TX/OTG_HS_ULPI_D6/ETH_RMII_TXD1/ETH_MII_TXD1/OTG_HS_VBUS 75. PB14/SPI2_MISO/TIM1_Ch3N/TIM12_Ch2/OTG_HS_DM/USART3_RTS/TIM8_Ch3N 76. PB15/SPI2_MOSI/I2S2_SD/TIM1_Ch4N/TIM8_Ch4N/TIM12_Ch3/OTG_HS_DP 96. PC6/SPI2_MCK/TIM8_Ch2/SDIO_D6/USART6_TX/DCMI_D0/TIM3_Ch2 97. PC7/SPI3_MCK/TIM8_Ch3/SDIO_D7/USART6_RX/DCMI_D1/TIM3_Ch3 110. PA15/JTDI/SPI3_NSS/I2S3_WS/TIM2_Ch2_ETR/SPI1_NSS 111. PC10/SPI3_SCK/I2S3_CK/UART4_TX/SDIO_D2/DCMI_D8/USART3_TX 112. PC11/UART4_RX/SPI3_MISO/SDIO_D3/DCMI_D4/USART3_RX 113. PC12/UART5_TX/SDIO_CK/DCMI_D9/SPI3_MOSI/I2S3_SD/USART3_CK 133. PB3/JTDO/TRACESWO/SPI3_SCK/I2S3_CK/TIM2_Ch3/SPI1_SCK 134. PB4/NJTRST/SPI3_MISO/TIM3_Ch2/SPI1_MISO 135. PB5/I2C1_SMBA/CAN2_RX/OTG_HS_ULPI_D7/ETH_PPS_OUT/TIM3_Ch3/SPI1_MOSI/SPI3_MOSI/DCMI_D10/I2S3_SD 140. PB9/SPI2_NSS/I2S2_WS/TIM4_Ch5/TIM11_Ch2/OTG_FS_SDA/SDIO_D5/DCMI_D7/I2C1_SDA/CAN1_TX Порты SPI могут работать в полудуплексе (поочередно переключаясь с приема на передачу) и на полном дуплексе. SPI1 может работать со скоростью до 42 мегабит/сек, SPI2 и SPI3 до 21 мегабит/сек. Аппаратное вычисление и генерация CRC может поддерживать базовые режимы работы с картами SD/MMC. SPI таке может обслуживаться контроллером DMA. Из-за того, что ножки микроконтроллера STM32F407ZGT6 выполняют каждая множество функций, и на плате STM32-P407 установлена различная периферия, подключенная к выводам SPI, то использовать периферию SPI можно только если от чего-то отказаться. SPI1. У этого интерфейса сигналы NSS, SCK, MISO, подключены к видеокамере, так что для использования SPI1 нужно видеокамеру выключить. Сигналы NSS, SCK, MOSI могут также выходить на чип аудиовывода CS4344-CZZ. Также сигнал MOSI подключен к чипу Ethernet KS8721BLMM, так что при использовании SPI1 работать с сетью не получится. SPI1 подключен к ядру микроконтроллера через шину APB2. SPI2. Сигнал MOSI может приходить на видеокамеру. Также многие сигналы совмещены с сигналами интерфейсов USB, так что в случае использования USB работать с SPI2 не получится. SPI2 подключен к ядру микроконтроллера через шину APB1. SPI3. Этот интерфейс подключен на разъем расширения UEXT Olimex, и его использовать удобнее всего, но только в том случае, если отказаться от слота карт microSD. Также сигналы NSS, SCK, MOSI могут приходить на чип аудиовывода CS4344-CZZ. MISO может быть подключен к видеокамере. SPI3 подключен к ядру микроконтроллера через шину APB1. [Основные возможности SPI] • Полнодуплексная синхронная передача данных с задействованием 3 сигнальных линий. [Основное функциональное описание SPI] На рис. 246 показана блочная диаграмма SPI. Рис. 246. SPI block diagram. Обычно SPI подключается к внешним устройствам 4 сигнальными линиями: • MISO: Master In / Slave Out, сигнал передачи данных от slave к master. Этот вывод может использоваться для передачи данных в режиме slave и для приема данных в режиме master. На рис. 247 показан пример соединения друг с другом одного устройства master с одним устройством slave. Рис. 247. Single master / single slave application. Примечание (1): здесь вывод NSS сконфигурирован как вход. Выводы MOSI соединены друг с другом, как и выводы MISO. При этом данные последовательно передаются между master и slave, первым идет самый старший бит (MSB). Обмен всегда начинает master. Когда устройство master передает данные к устройству slave через вывод MOSI, устройство slave отвечает данными через вывод MISO. Это реализует полнодуплексный двухсторонний обмен данными, которые синхронизированы одним и тем же тактовым сигналом (этот сигнал предоставляет устройство master через вывод SCK). [Управление выводом выборки slave (NSS)] Аппаратное или программное управление выводом NSS может быть установлено битом SSM в регистре SPI_CR1. • Программное управление NSS. когда SSM = 1. Выборка slave select управляется внутри микроконтроллера программно по значению бита SSI в регистре SPI_CR1. Внешний вывод NSS остается свободным, и может использоваться в приложении для других целей. [Фаза и полярность SCK] Можно запрограммировать 4 варианта работы, используя биты CPOL и CPHA в регистре SPI_CR1. Бит CPOL (clock polarity) управляет значением устойчивости (steady state) такта, когда данные не передаются. Этот бит влияет на оба режима — и master, и slave. Если бит CPOL сброшен, то SCK имеет лог. 0 в состоянии ожидания. Если CPOL установлен, то SCK имеет лог. 1 в состоянии ожидания. Если бит CPHA (clock phase, фаза такта) установлен, второй перепад на выводе SCK (это будет спад уровня, если CPOL сброшен, и нарастание уровня, если CPOL установлен) является стробом захвата старшего бита (MSBit). Данные будут захватываться по событию второго перехода состояния тактов. Если бит CPHA сброшен, то первый перепад на выводе SCK (это будет спад уровня, если установлен бит CPOL, и нарастание уровня, если бит CPOL сброшен) будет стробом захвата старшего бита данных (MSBit). Комбинация битов CPOL (clock polarity) и CPHA (clock phase) выбирают перепад сигнала тактов, по которому будет осуществляться захват данных. На рис. 248 показано, как SPI передает данные в 4 вариантах настройки битов CPHA и CPOL. Диаграмма может быть интерпретирована как диаграмма времени master или slave, где выводы SCK, MISO, MOSI напрямую соединены между устройствами master и slave. Примечание: перед тем, как поменять биты CPOL/CPHA, SPI должен быть запрещен сбросом бита SPE. Master и slave должны быть запрограммированы на одинаковые диаграммы управления сигналами. Состояние ожидания (idle state) SCK должно соответствовать выбранной полярности в регистре SPI_CR1 (переводом SCK в лог. 1 при CPOL=1 или переводом SCK в лог. 0 при CPOL=0). Формат фрейма данных (8 или 16 бит), выбираемый битом DFF в регистре SPI_CR1, определяет длину данных во время передачи/приема. Рис. Примечание (1): эти диаграммы соответствуют сброшенному биту LSBFIRST в регистре SPI_CR1 (бит MSB идет первым в потоке данных). Формат фрейма данных. Данные могут сдвигаться на выход либо MSB битом вперед, либо LSB битом вперед, в зависимости от бита LSBFIRST в регистре SPI_CR1. Длина каждого фрейма данных (8 или 16 бит) зависит от состояния бита DFF в регистре SPI_CR1. Выбранный формат фрейма влияет и на прием, и на передачу. [Конфигурирование SPI в режиме slave] В конфигурации slave тактовый сигнал будет приниматься через вывод SCK от устройства master. Значения, установленные в битах BR[2:0] регистра SPI_CR1 никак не будет влиять на скорость передачи данных. Примечание: рекомендуется разрешить работу SPI до того, как master начнет передавать тактовый сигнал. Если этого не сделать, то может произойти нежелательная передача данных. Регистр данных slave должен быть готов до первого перепада тактового обмена, или до окончания происходящего обмена. Для конфигурирования SPI в режиме slave следуйте следующей процедуре: 1. Установите бит DFF, чтобы определить 8 или 16 бит для формата фрейма данных. 2. Выберите значение бит CPOL и CPHA, чтобы определить один из 4 видов взаимодействия между передачей бит данных и тактовым сигналом (см. рис. 248). Чтобы передача данных была корректной, настройка бит CPOL и CPHA должна соответствовать друг другу на устройствах slave и master. Этот шаг выполнять не нужно, если выбран режим TI битом FRF в регистре SPI_CR2. 3. Порядок бит фрейма (MSB первый или LSB первый) зависит от значения бита LSBFIRST в регистре SPI_CR1) должен быть одинаковым для устройства slave и устройства master. Этот шаг выполнять не нужно, когда выбран режим TI. 4. В аппаратном режиме управления выборкой (см. описание вывода NSS) вывод NSS должен быть подключен к сигналу низкого уровня во время выполнения последовательности передачи фрейма. 5. Установите бит FRF в регистре SPI_CR2 для выбора режима протокола TI последовательного обмена данными. 6. Очистите бит MSTR и установите бит SPE (оба бита находятся в регистре SPI_CR1) чтобы активировать у микроконтроллера альтернативную функцию SPI на выводах. В этой конфигурации вывод MOSI работает как вход данных, и вывод MISO работает как выход данных. Передача. Байт данных параллельно загружается в буфер Tx во время цикла записи. Последовательность передачи данных начинается, когда устройство slave принимает сигнал тактов и MSB бит данных переходит на вывод MOSI. Остальные биты (7 в формате фрейма 8 бит и 15 бит в формате фрейма 16 бит) загружаются в регистр сдвига. Флаг TXE регистра SPI_SR устанавливается, когда данные загружены из буфера Tx в регистр сдвига, и генерируется прерывание, если установлен бит TXEIE в регистре SPI_CR2. Прием. Для получателя данных передача данных завершится в следующей ситуации: После последнего перепада тактов установиться бит RXNE, копия принятых данных из регистра сдвига переместится в буфер Rx. Когда читается регистр SPI_DR, периферия SPI возвратит это буферизированное значение. Очистка бита RXNE выполняется при чтении регистра SPI_DR. [Протокол TI для SPI в режиме slave] В режиме slave интерфейс SPI совместим с протоколом TI. Бит FRF регистра SPI_CR2 может использоваться для того, чтобы сконфигурировать обмен slave SPI совместимым с протоколом SPI TI. Полярность и фаза тактов принудительно устанавливаются так, чтобы они удовлетворяли требованиям протокола TI независимо от значений, которые установлены в регистре SPI_CR1. В режиме Slave (см. рис. 249: режим TI Slave одиночная передача, на рис. 250: режим TI Slave продолжающаяся передача) прескалер скорости SPI (baud rate prescaler) используется для управления моментом, когда вывод MISO переходит в третье состояние (отключено, HI-Z). Таким образом, может использоваться любая скорость передачи, позволяя определить этот момент с максимальной гибкостью. Однако скорость передачи главным образом зависит от частоты тактов внешнего master. Время, когда сигнал MISO переходит в отключенное состояние HI-Z, зависит от внутренних пересинхронизаций, и значение скорости устанавливается битами BR[2:0] регистра SPI_CR1. Их значение можно получить по формуле: Примечание: эта фича не работает для обменов с Motorola SPI (бит FRF установлен в 0). Чтобы детектировать ошибки фрейма TI только в режиме передатчика Slave, путем прерывания по ошибке (ERRIE=1), SPI должен быть сконфигурирован в однонаправленный 2-проводный режим путем установки битов BIDIMODE и BIDIOE в 1 (эти биты находятся в регистре SPI_CR1). Рис. 249. Режим TI Slave, одиночная передача. Рис. 250. Режим TI Slave, непрерывная передача. [Конфигурирование SPI в режиме master] В режиме master такты генерируются на ножке SCK, работающей как выход. Последовательность конфигурирования следующая: 1. Установите значение бит BR[2:0], чтобы определить скорость передачи (частота тактов SCK, см. описание регистра SPI_CR1). 2. Выберите значение битов CPOL и CPHA, чтобы задать один из 4 вариантов взаимодействия между передачей данных и поведением тактового сигнала (см. рис. 248). Этот шаг делать не нужно, когда выбран режим TI. 3. Установите бит DFF для определения 8 или 16 бит во фрейме данных. 4. Сконфигурируйте бит LSBFIRST в регистре SPI_CR1, чтобы задать порядок передачи бит во фрейме. Этот шаг не нужен, когда выбран режим TI. 5. Если в аппаратном режиме NSS должен работать в режиме входа, подайте сигнал высокого уровня на этот вывод для выполнения последовательности передачи фрейма. В режиме программного управления NSS, установите биты SSM и SSI в регистре SPI_CR1. Если нужно, чтобы вывод NSS работал как выход, должен быть установлен только бит SSOE. Этот шаг не нужен, когда выбран режим TI. 6. Установите бит FRF в регистре SPI_CR2, чтобы выбрать протокол TI для обмена данными. 7. Должны быть установлены биты MSTR и SPE (они остаются установленными, только если вывод NSS подключен к сигналу высокого уровня). В этом режиме вывод MOSI работает как выход данных, и вывод MISO работает как вход данных. Передача. Процесс передачи начнется, когда байт записывается в буфер Tx. Параллельно байт данных загружается в регистр сдвига (по внутренней шине) во время передачи первого бита, и затем сдвигается на выход последовательно через вывод MOSI (MSB битом вперед, или LSB битом вперед, в зависимости от состояния бита LSBFIRST в регистре SPI_CR1). Прием. Для приема, когда процесс передачи данных завершается: • Данные из регистра сдвига передается в буфер RX, и устанавливается флаг RXNE. На последнем перепаде тактов устанавливается бит RXNE, копия принятого байта данных из регистра сдвига перемещается в буфер Rx. Когда прочитан регистр SPI_DR, периферийное устройство SPI возвратит это забуферизированное значение данных. Бит RXNE очищается, когда происходит чтение регистра SPI_DR. Может быть осуществлена поддержка потока передачи, если следующий фрейм данных для передачи будет помещен в буфер Tx, когда передача была запущена. Имейте в виду, что флаг TXE должен быть в состоянии 1 перед любой попыткой записи в буфер Tx. Примечание: когда master обменивается данными с устройствами SPI slave, которые нуждаются в отключении выборки между передачами, вывод NSS должен быть сконфигурирован как GPIO или должен использоваться другой вывод GPIO, чтобы программно управлять выборкой slave-устройства. [Протокол TI для SPI в режиме master] В режиме master интерфейс SPI совместим с протоколом TI. Бит FRF регистра SPI_CR2 может использоваться для того, чтобы сконфигурировать обмен master SPI совместимым с протоколом SPI TI. Полярность и фаза тактов принудительно устанавливаются так, чтобы они удовлетворяли требованиям протокола TI независимо от значений, которые установлены в регистре SPI_CR1. Управление NSS также специфично для протокола TI, что делает конфигурирование управления NSS через регистры SPI_CR1 и SPI_CR2 (биты SSM, SSI, SSOE) прозрачным для пользователя. На рис. 251 показаны диаграммы обмена режима TI master при одиночной передаче, и на рис. Рис. 251. TI mode — master mode, single transfer. Рис. 252. TI mode — master mode, continuous transfer. [Конфигурирование SPI для обмена в полудуплексе] SPI может работать в 2 режимах полудуплекса: • 1 тактовый сигнал и 1 двунаправленная линия данных. 1 тактовая линия и 1 двунаправленная линия данных (BIDIMODE=1). Этот режим разрешается путем установки бита BIDIMODE в регистре SPI_CR1. В этом режиме SCK используется для тактов и для данных используется MOSI в режиме master или MISO в режиме slave. Направление передачи (Input/Output) выбирается битом BIDIOE в регистре SPI_CR1. Когда этот бит установлен в 1, линия данных становится выходом, иначе она работает как вход. 1 тактовая линия и 1 однонаправленная линия данных (BIDIMODE=0). • Режим только для передачи работает так же, как и полный дуплекс (BIDIMODE=0, RXONLY=0): данные передаются через ножку передачи (MOSI в режиме master или MISO в режиме slave). Ножка приема (MISO в режиме master или MOSI в режиме slave) может использоваться как обычный порт ввода вывода GPIO. В этом случае приложение микроконтроллера должно просто игнорировать буфер Rx (если регистр данных будет прочитан, он не будет содержать принятые данные). Чтобы запустить обмен в режиме только приема, сконфигурируйте и разрешите SPI: • В режиме master обмен запустится немедленно, и завершится, когда бит SPE очистится, и текущий прием остановится. В этом режиме здесь не нужно читать флаг BSY. Он всегда устанавливается, когда происходит обмен SPI. [Процедуры передачи и приема данных] Буферы Rx и Tx. Во время приема данные принимаются и сохраняются во внутренний буфер Rx. При передаче данных сначала сохраняются во внутренний буфер Tx перед тем, как они будут переданы. Доступ на чтение регистра SPI_DR возвратит значение из буфера Rx, в то время как доступ на запись в регистр SPI_DR поместит записываемые данные в буфер Tx. Стартовая последовательность в режиме master: • Когда полный дуплекс (BIDIMODE=0 и RXONLY=0). Стартовая последовательность в режиме slave: • Когда полный дуплекс (BIDIMODE=0 и RXONLY=0). [Обработка передачи и приема данных] Флаг TXE (расшифровывается как Tx buffer empty, буфер передачи пуст) устанавливается, когда данные переданы из буфера Tx в регистр сдвига. Это показывает, что внутренний буфер Tx готов к загрузке следующей порции данных. В этот момент может генерироваться прерывание, если установлен бит TXEIE в регистре SPI_CR2. Очистка бита выполняется при записи в регистр SPI_DR (при этом записанные данные попадают в буфер Tx). Примечание: программное обеспечение должно удостовериться, что флаг TXE установлен перед тем, как сделать попытку записи в буфер Tx (в регистр SPI_DR). Иначе запись перезапишет ранее записанные в буфер Tx данные. Флаг RXNE (расшифровывается Rx buffer not empty, буфер приема не пуст) устанавливается, по приходу последнего перепада тактов, когда данные копируются из регистра сдвига в буфер Rx. Это показывает, что есть принятые данные, и их можно прочитать через чтение регистра SPI_DR. В этот момент может быть сгенерировано прерывание, если установлен бит RXNEIE в регистре SPI_CR2. Бит RXNE очищается при чтении регистра SPI_DR (при этом будут прочитаны принятые данные из буфера Rx). Для некоторых конфигураций может использоваться флаг BSY во время последней передачи данных, чтобы ожидать, пока не завершится передача. Далее приведено описание полнодуплексной операции передачи и приема в режиме master или slave (BIDIMODE=0 и RXONLY=0). Программное обеспечение должно следовать следующей процедуре для передачи и приема данных (см. рис. 253 и 254): 1. Разрешить SPI установкой бита SPE в значение 1. Эта процедура может быть также реализована с использованием отдельных выделенных обработчиков прерываний, запускаемых по фронту флагов RXNE или TXE. Рис. 253. Диаграмма поведения сигналов TXE/RXNE/BSY в режиме Master / полный дуплекс (BIDIMODE=0 и RXONLY=0), когда идет непрерывная передача. Рис. 254. Диаграмма поведения сигналов TXE/RXNE/BSY в режиме Slave / полный дуплекс (BIDIMODE=0 и RXONLY=0), когда идет непрерывная передача. [Процедура «только передача» (BIDIMODE=0 RXONLY=0)] В этом режиме процедура может быть уменьшена, как описано ниже, и бит BSY может использоваться для ожидания завершения передачи (см. рис. 255 и 256). 1. Разрешите SPI установкой бита SPE в значение 1. Эта процедура может быть также реализована с использованием отдельного выделенного обработчика прерываний, запускаемого по фронту флага TXE. Примечание: во время прерывистых обменов данными есть задержка на 2 периода тактов APB между операцией записи в SPI_DR и установкой бита BSY. Следовательно, в режиме «только передача» важно ждать сначала, пока не установится TXE, и затем не очистится BSY, после того как будут записаны последние данные. После передачи двух порций данных в режиме «только передача» установится флаг OVR в регистре SPI_SR, поскольку принятые данные никогда не были прочитаны. Рис. 255. Диаграмма поведения сигналов TXE/BSY в режиме Master / только передача (BIDIMODE=0 и RXONLY=0), когда идет непрерывная передача. Рис. 256. Диаграмма поведения сигналов TXE/BSY в режиме Slave / только передача (BIDIMODE=0 и RXONLY=0), когда идет непрерывная передача. [Двунаправленная процедура передачи (BIDIMODE=1 и BIDIOE=1)] В этом режиме процедура такая же, как и процедура «только передача», за исключением того, что оба бита, и BIDIMODE, и BIDIOE должны быть установлены в регистре SPI_CR2 перед тем, как разрешить SPI. [Однонаправленная процедура «только прием» (BIDIMODE=0 и RXONLY=1)] В этом режиме процедура может быть уменьшена, как описано ниже (см. рис. 257): 1. Установите бит RXONLY в регистре SPI_CR2. Эта процедура может быть также реализована с использованием отдельного выделенного обработчика прерываний, запускаемого по фронту флага RXNE. Примечание: если требуется запретить SPI после последней передачи, то следуйте рекомендации, описанной в секции 28.3.8: Disabling the SPI. Рис. 257. Диаграмма поведения RXNE в режиме только чтение (BIDIMODE=0 и RXONLY=1), когда идет непрерывная передача. [Процедура двунаправленного приема (BIDIMODE=1 и BIDIOE=0)] В этом режиме процедура такая же, как и процедура «только прием», за исключением того, что бит BIDIMODE должен быть установлен и BIDIOE очищен в регистре SPI_CR2 перед тем, как разрешить SPI. [Непрерывные и прерывистые передачи] Когда данные передаются в режиме master, если программное обеспечение достаточно быстрое, чтобы детектировать каждый фронт TXE (или отрабатывается прерывание TXE), и немедленно записать регистр SPI_DR перед завершением текущей передачи, то обмен считается непрерывным. В этом случае нет перерыва в генерации тактов SPI между каждым элементом данных, и бит BSY никогда не очищается между каждой порцией данных. И наоборот, если программное обеспечение недостаточно быстрое, то это может привести к прерывистому обмену. В этом случае, бит BSY очищается между каждой передачей данных (см. рис. 258). В режиме Master «только прием» (RXONLY=1), обмен всегда непрерывный и флаг BSY всегда читается как 1. В режиме slave, непрерывность обмена определяется устройством SPI master. В любом случае, даже если обмен непрерывный, флаг BSY переходит в 0 между каждой передачей на минимальное время длительностью в один такт SPI (см. рис. 256). Рис. 258. Диаграмма поведения TXE/BSY при передаче (BIDIMODE=0 и RXONLY=0), в случае прерывистых передач. [Вычисление CRC] CRC было применено для надежности обмена данными. Для передачи и приема данных реализованы отдельные калькуляторы CRC. CRC вычисляется согласно программируемому полиному, последовательно для каждого бита. CRC вычисляется на перепаде тактов выборки, заданном битами CPHA и CPOL в регистре SPI_CR1. Примечание: этот SPI предлагает два вида стандарта вычисления CRC, которые напрямую зависят от формата фрейма, выбранного для передачи и/или приема: 8-битные данные (CRC8) и 16-битные данные (CRC16). Вычисление CRC разрешается установкой бита CRCEN в регистре SPI_CR1. Это действие сбрасывает регистры CRC (SPI_RXCRCR и SPI_TXCRCR). В полном дуплексе или в режиме только передачи, когда передача управляется программно (CPU mode), необходимо записать бит CRCNEXT немедленно после последней передаваемой порции данных, записанной в SPI_DR. По окончании последней передачи данных будет передано значение SPI_TXCRCR. В режиме только приема и когда передачи управляются программно (CPU mode), необходимо записать бит CRCNEXT после второй последней порции принятых данных. Будет принята CRC сразу после приема последней порции данных, и будет произведена проверка CRC. По окончании передач данных и CRC будет установлен флаг CRCERR в регистре SPI_SR, если было повреждение данных в процессе передачи. Если в в буфере TX имеются данные, значение CRC передается после передачи байта данных. Во время передачи CRC калькулятор CRC выключается, и значение регистра остается неизменным. Обмен SPI с использованием CRC возможно с использованием следующей процедуры: 1. Запрограммируйте значения CPOL, CPHA, LSBFirst, BR, SSM, SSI и MSTR. Примечание: когда SPI в режиме slave, будьте внимательны и разрешайте вычисление CRC только когда такты стабильны, т. е. когда такты находятся в состоянии steady (стабильное состояние). Если это не сделать, то может произойти неправильное вычисление CRC. Фактически CRC чувствительна к входным тактам SCK slave, как только установлен CRCEN, и это независимо от того, установлен бит SPE или нет. На высоких частотах передачи данных, будьте осторожны, когда передается CRC. Так как количество используемых циклов CPU должно быть максимально возможным в фазе передачи CRC, то запрещено вызывать программные функции во время последовательности передачи CRC, чтобы избежать ошибок в приеме последних данных и CRC. Фактически бит CRCNEXT должен быть записан перед окончанием передачи/приема последней порции данных. Для высоких частот передачи данных рекомендуется использовать режим DMA, чтобы избежать деградации скорости SPI, так как доступ через CPU ухудшает полосу пропускания SPI. Когда устройства сконфигурированы как slave, и используется режим аппаратного NSS, вывод NSS нужно удерживать в состоянии лог. 0 между фазой данных и фазой CRC. Когда SPI сконфигурирован в режиме slave с разрешенной функцией подсчета CRC, то вычисление CRC производится всякий раз, когда к выводу NSS прикладывается уровень лог. 1. Это может произойти к примеру в случае multislave-окружения, где master обмена адресует устройства slave по своему выбору. Между отключением выборки slave (лог. 1 на выводе NSS) и выборкой нового slave (низкий уровень на NSS), значение CRC должно быть очищено как на стороне master, так и на стороне slave, чтобы заново синхронизировать master и slave для соответствующего вычисления CRC. Чтобы очистить CRC, выполните следующую процедуру: 1. Запретите SPI (SPE = 0). [Флаги статуса SPI] Для приложения предоставлено 4 флага статуса, чтобы полностью отслеживать состояние шины SPI. Tx buffer empty flag (TXE, флаг сигнализации о пустом буфере передачи). Когда этот флаг установлен, то это указывает на опустошение буфера Tx, так что следующая порция данных может быть записана в буфер Tx. Флаг TXE очищается, когда осуществляется запись в регистр SPI_DR. Rx buffer not empty (RXNE, буфер приема содержит данные). Когда установлен, этот флаг говорит о том, что в буфере Rx находятся действительные принятые данные. Флаг очищается, когда читается регистр SPI_DR. BUSY flag (BSY, флаг занятости). Этот флаг BSY устанавливается и очищается аппаратно (запись в этот флаг не дает никакого эффекта). Флаг BSY показывает состояние слоя обмена communication SPI. Когда BSY установлен, то шина SPI занята обменом данными. Есть только одно исключение в режиме master / двунаправленный прием (MSTR=1, BDM=1 и BDOE=0), когда флаг BSY удерживается в состоянии лог. 0 во время приема. Флаг BSY полезен для детектирования окончания передачи, если программное обеспечение хочет запретить SPI и войти в режим останова (Halt mode), или отключить тактирование периферийных устройств. Это позволит избежать порчу данных последней передачи. Для такого случая очень важно соблюдение нижеописанной процедуры. Флаг BSY также полезен для того, чтобы избежать коллизии записи в системе multimaster. Флаг BSY устанавливается, когда стартует передача, за исключением режима master / двунаправленный прием (MSTR=1, BDM=1 и BDOE=0). Флаг BSY очищается в следующих случаях: • Когда передача завершена (за исключением режима master, если обмен продолжается). Когда обмен прерывистый, флаг BSY в лог. 0 между каждым обменом. Когда обмен непрерывный: • В режиме master, флаг BSY сохраняет состояние лог. 1 во время всех передач. Примечание: не используйте флаг BSY для отслеживания каждой передачи данных и каждого приема. Лучше использовать вместо этого флаги TXE и RXNE. [Запрет работы SPI] Когда передача данных завершена, приложение может остановить обмен путем запрета периферии SPI. Это осуществляется путем очистки бита SPE. Для некоторых конфигураций запрет SPI и вход в режим Halt в тот момент, когда происходит передача, может привести к повреждению текущей передачи, и/или флаг BSY может стать ненадежным. Чтобы избежать подобных эффектов, рекомендуется соблюдать следующую процедуру для запрета SPI: В режиме master или slave полный дуплекс (BIDIMODE=0, RXONLY=0) В режиме master или slave, только передача в одном направлении (BIDIMODE=0, RXONLY=0) или двунаправленный режим передачи (BIDIMODE=1, BIDIOE=1). После последней порции данных, записанной в регистр SPI_DR: В режиме master, только прием данных в одном направлении (MSTR=1, BIDIMODE=0, RXONLY=1) или двунаправленный режим приема (MSTR=1, BIDIMODE=1, BIDIOE=0). В этом случае нужно специальным образом убедиться, что SPI не начал новую передачу. Последовательность ниже допустима только для конфигурации SPI Motorola (бит FRF установлен в 0): Когда SPI сконфигурирован в режиме TI (FRF установлен в 1), то нужно соблюдать следующую процедуру, чтобы избежать генерации нежелательного импульса на выводе NSS, когда SPI запрещен: Примечание: в двунаправленном режиме master (MSTR=1, BDM=1, BDOE=0), флаг BSY удерживается в состоянии 0 во время передач. В режиме slave, только прием (MSTR=0, BIDIMODE=0, RXONLY=1) или в двунаправленном режиме приема (MSTR=0, BIDIMODE=1, BIDOE=0): [Обмен через SPI с использованием DMA] Для того, чтобы работать с максимальной скоростью, в SPI нужно поставлять данные для передачи, и также нужно читать буфер приема, чтобы избежать потери данных на приеме (overrun). Для того, чтобы упростить передачи, в SPI реализована возможность использования DMA, здесь применен простой протокол запроса/подтверждения. Доступ через DMA запрашивается, когда разрешены соответствующие биты в регистре SPI_CR2 (TXDMAEN и RXDMAEN). Для буферов Tx и Rx могут быть выставлены отдельные запросы (см. рис. 259 и 260): • При передаче запрос DMA выдается каждый раз, когда флаг TXE установлен в 1. Затем DMA записывает регистр SPI_DR (что очистит флаг TXE). Когда SPI используется только для передачи данных, можно разрешить только канал SPI Tx DMA. В этом случае флаг OVR установится, потому что принятые данные не будут прочитаны. Когда SPI используется только для приема данных, можно разрешить только канал SPI Rx DMA. В режиме передачи, когда DMA записал все данные для передачи (установился флаг TCIF в регистре DMA_ISR), может отслеживаться флаг BSY, чтобы удостовериться в том, что обмен через SPI завершился. Это требуется для того, чтобы предотвратить порчи передачи последней порции данных перед запретом SPI или входом в режим Stop. Программное обеспечение должно ожидать TXE=1 и затем ожидать BSY=0. Примечание: во время прерывистого обмена есть задержка величиной в 2 такта APB между операцией записи в SPI_DR и установкой флага BSY. Как следствие обязательно ждите сначала TXE=1, и затем ждите BSY=0 после записи последней порции данных. Рис. 259. Передача с использованием DMA. Рис. 260. Прием с использованием DMA. DMA вместе с вычислением CRC. Когда разрешен обмен с вычислением CRC, и используется режим DMA, то передача и прием CRC по окончании обмена происходит автоматически, так что не нужно использовать бит CRCNEXT. После приема CRC нужно прочитать значение CRC в регистре SPI_DR, чтобы очистить флаг RXNE. По окончании передачи данных и CRC, будет установлен флаг CRCERR в регистре SPI_SR, если произошло повреждение данных во время передачи. [Флаги ошибок] Master mode fault (MODF), флаг ошибки режима master. Событие этой ошибки происходит, когда у устройства master есть вывод NSS, подтянутый к уровню лог. 0 (NSS в аппаратном режиме), или когда бит SSI равен 0 (когда NSS в программном режиме), это автоматически установит бит MODF. Master mode fault влияет на периферийное устройство SPI следующим образом: • Бит MODF устанавливается, и генерируется прерывание SPI, если установлен бит ERRIE. Используйте следующую программную последовательность, чтобы очистить бит MODF: 1. Сделайте доступ на чтение или запись регистра SPI_SR, пока бит MODF установлен. Чтобы избежать конфликта нескольких устройств slave в системе, которая состоит из нескольких MCU, вывод NSS должен быть подтянут к лог. 1 во время последовательности очистки бита MODF. Биты SPE и MSTR можно восстановить в свое оригинальное состояние после последовательности очистки бита MODF. В целях безопасности аппаратура не разрешает установку битов SPE и MSTR, когда установлен бит MODF. Когда устройство находится в режиме slave, бит MODF не может быть установлен. Однако в конфигурации multimaster устройство может быть в режиме slave с установленным битом MODF. В этом случае бит MODF показывает, что возможно был конфликт multimaster для системы управления. Обработчик прерывания может быть использован, чтобы чисто восстановиться из этого состояния путем выполнения сброса или возврата в состояние по умолчанию. Флаг Overrun (OVR). Событие потери данных (overrun) произойдет, когда устройство master отправило байты данных и устройство slave не очистило бит RXNE, который был установлен после получения предыдущих байт данных. Когда произошла ошибка overrun, установится бит OVR, и будет сгенерировано прерывание, если установлен бит ERRIE. В этом случае буфер приемника не будет обновлен новыми принятыми данными от устройства master. Чтение из регистра SPI_DR возвратит этот байт. Все другие байты, которые были переданы после этого байта, будут потеряны. Очистка бита OVR происходит при чтении из регистра SPI_DR, после которого произойдет доступ на чтение регистра SPI_SR. Ошибка CRC. Этот флаг используется для проверки целостности принятых данных, когда установлен бит CRCEN в регистре SPI_CR1. Флаг CRCERR в регистре SPI_SR устанавливается, если значение, принятое в регистр сдвига, не соответствует значению SPI_RXCRCR приемника. Режим фрейма TI, ошибка формата (FRE). Ошибка формата фрейма TI детектируется, когда случается импульс NSS во время процесса обмена, и когда SPI работает в режиме slave, и сконфигурирован в режиме для поддержки протокола TI. Когда произошла такая ошибка, устанавливается флаг FRE в регистре SPI_SR. При возникновении такой ошибки SPI не запрещается, импульс NSS игнорируется, и SPI ждет следующего импульса NSS перед началом новой передачи. Данные могут быть повреждены, так как в результате детектирования ошибки могут быть потеряны 2 байта данных. Флаг FRE очищается, когда читается регистр SPI_SR. Если бит ERRIE установлен, то при детектировании ошибки NSS генерируется прерывание. В этом случае SPI должен быть запрещен, потому что целостность данных больше не гарантируется, и обмен должен быть заново инициирован устройством master, когда SPI будет снова разрешен. Рис. 261. Детектирование ошибки формата фрейма режима TI. [Прерывания SPI] Таблица 125. SPI interrupt requests.

[Регистры SPI] Прим. переводчика: некоторые регистры используются как для SPI, так и для I2S. Описание регистров I2S опущено. Таблица 128. Карта регистров SPI, их значение после сброса. В таблице приведена памятка по регистрам SPI, дальше регистры описываются подробно. Это регистр управления 1, в режиме I2S он не используется. Адрес смещения 0x00, значение после сброса 0x0000.

BIDIMODE: Bidirectional data mode enable, разрешение режима двунаправленного обмена. 0: выбран однонаправленный режим обмена данными по 2 сигнальным линиям, 1: двунаправленный режим обмена по 1 сигнальной линии. BIDIOE: Output enable in bidirectional mode, разрешение работы выхода в двунаправленном режиме. Этот бит в комбинации с битом BIDIMODE выбирает направление передачи в двунаправленном режиме. 0: выход запрещен (только прием), 1: выход разрешен (только передача). Примечание: для двунаправленной передачи режиме master используется вывод MOSI, в режиме slave используется вывод MISO. CRCEN: разрешение аппаратного вычисления CRC, если в этот бит записана 1. Примечание: для обеспечения корректного функционирования этот бит должен записываться только тогда, когда SPI запрещен (SPE=0). CRCNEXT: CRC transfer next, признак того, что нужно закончить вычисление CRC и переслать её значение. 0: все еще продолжается фаза данных (идет подсчет CRC), 1: в следующей передаче должно находиться значение CRC. Примечание: когда SPI сконфигурирован на полный дуплекс, или режимов «только передача», бит CRCNEXT должен быть установлен сразу за последней записью порции данных в регистр SPI_DR (т. е. максимально быстро, без паузы). Когда SPI сконфигурирован в режиме «только прием», бит CRCNEXT должен быть установлен после приема предпоследней (second last) порции данных. Этот бит должен быть всегда очищен, когда передачи идут под управлением DMA. DFF: Data frame format, формат фрейма данных. 0: для передачи/приема выбран 8-битный фрейм, 1: 16-битный фрейм. Примечание: для корректного функционирования этот бит должен быть записан только когда SPI запрещен (SPE=0). RXONLY: Receive only, только прием. Этот бит в комбинации с битом BIDIMODE выбирает направление передачи в 2-сигнальном однонаправленном режиме. Этот бит также полезен в системе multislave, в которой к этому отдельному slave нет обращения, так что выход этого slave не портит обмен данными. 0: полный дуплекс (и передача, и прием), 1: выход запрещен (режим «только прием»). SSM: Software slave management, программное управление устройством slave. Когда этот бит установлен, вход вывода NSS заменяет значение бита SSI. 0: программное управление slave запрещено (работает аппаратное через ножку NSS), 1: программное управление slave разрешено. Примечание: этот бит не используется в режиме SPI TI. SSI: Slave select internal. Этот бит имеет значение только тогда, когда установлен бит SSM. Значение бита SSI принудительно работает как сигнал с линии NSS, при этом состояние входа NSS игнорируется. Примечание: этот бит не используется в режиме SPI TI. LSBFIRST: Least Significant Bit First, этот бит определяет формат фрейма (в каком порядке по старшинству следуют биты во фрейме). 0: MSB следует первым, 1: LSB следует первым. Примечание: этот бит не должен изменяться, пока идет процесс обмена данными. Этот бит не используется в режиме SPI TI. SPE: SPI enable, разрешение работы SPI. 0: периферийное устройство SPI запрещено, 1: разрешено. Примечание: чтобы корректно запретить SPI, следуйте процедуре, описанной в разделе «Запрет работы SPI». BR[2:0]: Baud rate control, управление скоростью передачи (частотой тактов SCK). 000: fPCLK/2 Примечание: эти биты не должны изменяться, пока идет процесс обмена данными. MSTR: Master selection, выбор режима Master. 0: устройство SPI сконфигурировано как Slave (подчиненное), 1: как Master (главное). Примечание: этот бит не должен изменяться, пока идет процесс обмена данными. CPOL: Clock polarity, полярность тактов. 0: неактивный перепад с 1 на 0 (значение бита выбирается по нарастающему фронту тактового сигнала), 1: неактивный перепад с 0 на 1 (значение бита выбирается по спаду тактового сигнала). Примечание: этот бит не должен изменяться, пока идет процесс обмена данными. Этот бит не используется в режиме SPI TI. CPHA: Clock phase, фаза тактов. 0: первый перепад тактового сигнала является первым моментом выборки значения бита, 1: второй перепад тактового сигнала является первым моментом выборки значения бита. Примечание: этот бит не должен изменяться, пока идет процесс обмена данными. Этот бит не используется в режиме SPI TI. Регистр управления 2. Смещение адреса 0x04, значение после сброса 0x0000.

Биты 15:8 зарезервированы, их значение должно сохраняться на значении после сброса. Бит 3 также зарезервирован, он аппаратно удерживается в значении 0. TXEIE: Tx buffer empty interrupt enable, разрешение прерывания по событию опустошения буфера передачи. 0: прерывание по флагу TXE замаскировано (не будет срабатывать), 1: прерывание по флагу TXE разрешено (в этом случае запустится обработчик прерывания, когда флаг TXE установится). RXNEIE: RX buffer not empty interrupt enable, разрешение прерывания по событию, когда буфер приема оказался не пуст. 0: прерывание по флагу RXNE замаскировано (не будет срабатывать), 1: прерывание по флагу RXNE разрешено (в этом случае запустится обработчик прерывания, когда флаг RXNE установится). ERRIE: Error interrupt enable, разрешение прерывания по возникновению ошибки. Этот бит управляет генерацией прерывания, когда произойдет событие ошибки (по флагам CRCERR, OVR, MODF в режиме SPI, FRE в режиме TI, UDR, OVR и FRE в режиме I2S). 0: прерывание замаскировано (не будет срабатывать), 1: разрешено. FRF: Frame format, формат фрейма. 0: режим SPI Motorola, 1: режим SPI TI. SSOE: SS output enable, разрешение работы выхода выборки подчиненного устройства. 0: выход управления Slave Select в режиме master запрещен, и ячейка может работать в конфигурации multimaster, 1: в режиме master выход Slave Select разрешен, когда ячейка разрешена. Ячейка не может работать в среде multimaster. Примечание: этот бит не используется в режиме SPI TI. TXDMAEN: Tx buffer DMA enable, работа буфера передачи через DMA разрешена. Когда этот бит установлен, делается запрос DMA независимо от того, установлен ли флаг TXE, или нет. 0: буфер Tx DMA запрещен, 1: разрешен. RXDMAEN: Rx buffer DMA enable, работа буфера приема через DMA разрешена. Когда этот бит установлен, делается запрос DMA независимо от того, установлен ли флаг RXNE, или нет. 0: буфер Rx DMA запрещен, 1: разрешен. Регистр статуса SPI, смещение адреса 0x08, значение после сброса 0x0002.

Биты 15:9 зарезервированы, их значение аппаратно удерживается в значении 0. FRE: Frame format error, ошибка формата фрейма. 0: не было ошибки формата фрейма, 1: ошибка формата фрейма произошла. Этот флаг устанавливается аппаратно и очищается программно, когда читается регистр SPIx_SR. Примечание: этот флаг используется, когда SPI работает в режиме TI slave или I2S slave, за подробностями обращайтесь к секции Errors flags (флаги ошибок) даташита. BSY: Busy flag, флаг занятости. 0: SPI (или I2S) не занят, 1: интерфейс занят обменом, или буфер Tx не пуст. Этот флаг устанавливается и сбрасывается аппаратно. Примечание: флаг BSY должен использоваться с некоторыми предосторожностями, см. секции «Флаги статуса SPI» и «Запрет работы SPI». OVR: Overrun flag, флаг потери данных. 0: потери данных не было, 1: произошла потеря данных на приеме, т. е. данные не были вовремя считаны. Этот флаг устанавливается аппаратно, и сбрасывается программно выполнением специальной последовательности действий (см. секцию «Флаги ошибок», описание флага OVR). MODF: Mode fault, ошибка режима. 0: ошибки не было, 1: произошла ошибка режима. Этот флаг устанавливается аппаратно, и сбрасывается программно выполнением специальной последовательности действий (см. секцию «Флаги ошибок», описание флага MODF). CRCERR: CRC error flag, флаг ошибки контрольной суммы. 0: принятое CRC соответствует значению SPI_RXCRCR, 1: это не так, произошла ошибка. Этот флаг устанавливается аппаратно, и сбрасывается программно путем записи в него 0. UDR: Underrun flag, флаг недостаточности данных. 0: не было события underrun, 1: буфер передатчика не успел вовремя заполниться новыми данными для передачи. Этот флаг устанавливается аппаратно, и сбрасывается программно выполнением специальной последовательности действий (см. секцию «Флаги ошибок», описание флага UDR). Примечание: этот бит не используется в режиме SPI. CHSIDE: Channel side, флаг канала. 0: был передан или принят левый канал стерео, 1: правый канал. Примечание: этот бит не используется в режиме SPI, и подразумевается, что он относится к PCM. TXE: Transmit buffer empty, флаг пустоты буфера передатчика. 0: буфер Tx передатчика содержит данные для отправки, пока не переписанные в регистр сдвига, 1: буфер Tx передатчика пуст, и готов к записи новых данных. RXNE: Receive buffer not empty, буфер приемника не пуст. 0: буфер Rx приемника пуст, данные пока не приняты, 1: буфер Rx приемника не пуст, т. е. содержит новые принятые данные, которые должны быть прочитаны программой. Регистр данных SPI, который служит для доступа к буферам приема и передачи. Смещение адреса 0x0C, значение после сброса 0x0000.

DR[15:0]: Data register, регистр данных, который служит для приема или передачи данных. Регистр данных служит для доступа к 2 отдельным буферам — один для записи (Tx, Transmit Buffer, буфер передачи), другой для чтения (Rx, Receive Buffer, буфер приема). Запись в регистр данных записывает данные в буфер Tx, и чтение регистра данных осуществляет чтение буфера Rx. Примечание: есть несколько замечаний для режима SPI: В зависимости от бита выбора формата фрейма (бит DFF в регистре SPI_CR1), отправляемые данные имеют длину либо 8, либо 16 бит. Этот выбор должен быть сделан до разрешения работы SPI, чтобы обеспечить корректное функционирование. Для фрейма 8 бит буферы 8-битные, и используется только младший байт (SPI_DR[7:0]) регистра для передачи/приема. В режиме приема старший байт регистра (SPI_DR[15:8]) принудительно равен 0. Для фрейма 16 бит буферы 16-битные, и для передачи/приема задействован весь регистр полностью SPI_DR[15:0]. Регистр полинома для CRC, адрес смещения 0x10, значение после сброса 0x0007.

CRCPOLY[15:0]: CRC polynomial register, регистр для хранения полинома вычисления CRC. После сброса регистр содержит полином 0x0007, который может быть при необходимости программно изменен на другой. Регистр CRC для приема, адрес смещения 0x14, значение после сброса 0x0000.

RXCRC[15:0]: Rx CRC register, регистр вычисленной CRC для принятого потока данных. Когда вычисление CRC разрешено, биты RxCRC[15:0] содержат вычисленную контрольную сумму от последовательно принятых байт. Этот регистр сбрасывается, когда в бит CRCEN в регистре SPI_CR1 записывается 1. CRC вычисляется с задействованием полинома, запрограммированного в регистре SPI_CRCPR. Учитываются только 8 младших бит, когда формат фрейма установлен 8 бит (DFF=0 в регистре SPI_CR1), в этом случае вычисление CRC производится по стандарту CRC8. Задействованы все 16 бит этого регистра, когда выбран 16-битный формат фрейма данных (DFF=1 в регистре SPI_CR1), в этом случае вычисление CRC производится по стандарту CRC16. Примечание: чтение этого регистра, когда установлен флаг BSY, вернет некорректное значение. Регистр CRC для передачи, адрес смещения 0x18, значение после сброса 0x0000.

TXCRC[15:0]: Tx CRC register, регистр вычисленной CRC для переданного потока данных. Когда вычисление CRC разрешено, биты TxCRC[15:0] содержат вычисленную контрольную сумму от последовательно переданных байт. Этот регистр сбрасывается, когда в бит CRCEN в регистре SPI_CR1 записывается 1. CRC вычисляется с задействованием полинома, запрограммированного в регистре SPI_CRCPR. Учитываются только 8 младших бит, когда формат фрейма установлен 8 бит (DFF=0 в регистре SPI_CR1), в этом случае вычисление CRC производится по стандарту CRC8. Задействованы все 16 бит этого регистра, когда выбран 16-битный формат фрейма данных (DFF=1 в регистре SPI_CR1), в этом случае вычисление CRC производится по стандарту CRC16. Примечание: чтение этого регистра, когда установлен флаг BSY, вернет некорректное значение. [Ссылки] 1. Интерфейс SPI. |

|||||||||||||||

Передача SPI с платой STM32F4 застревает на SPI_WaitTX

AFAICT, ваш код недостаточно далеко, чтобы продемонстрировать, что он получает что-то от BMX_055. Таким образом, нет никаких доказательств того, что цепь правильная, поэтому учтите, что она может быть повреждена.

Существует несколько различных режимов SPI (комбинация тактового сигнала и состояния MOSI данных) и дополнительные комбинации разрешающих сигналов. Может быть трудно понять, что, если вообще что-то работает, если вы пытаетесь использовать периферийное устройство SPI. Если у вас есть доступ к осциллографу, то вы можете проверить, что данные возвращаются из IMU Bosch BMX_055, фактически не имея правильного кода (наблюдая за выводом MISO). Если у вас нет доступа к осциллографу или логическому анализатору (и вы знаете, как его использовать), то я думаю, что ваша лучшая тактика — сначала игнорировать периферийное аппаратное обеспечение SPI и использовать «битовые удары».

Если «правильное» аппаратное периферийное устройство SPI не работает в первый раз или очень легко, тогда управляйте сигналами с помощью выводов GPIO и программного обеспечения (техника, называемая «Bit Banging», будет появляться в веб-поиске).

Так что используйте часы, MOSI и Enable (это, возможно, необходимо) с эквивалентом digitalWrite, и получите сигнал MISO с эквивалентом digitalRead. Постарайтесь сделать это как можно проще.

Вы найдете несколько примеров в Интернете, если будете искать «SPI Bit-Banging».

Я нашел программное обеспечение Coding SPI

Программный SPI для PIC

и вопрос об обмене стека

Вот копия псевдокода из ответа на электронику из стека :

Make Slave Select low Short delay Do 8 times Make the SCK ( Serial Clock ) pin low Make the MOSI ( Master - Out - Slave - In ) pin high or low depending on bit 7 of the data Add brief delay Make the SCK output high Read MISO ( Master - In - Slave - Out ) pin Shift received data left , and shift the bit just read in as bit 0

Add brief delay Shift the data byte 1 bit left Make Slave Select high again Вам необходимо прочитать и понять таблицу данных IMU Bosch BMX_055, чтобы убедиться, что вы правильно с ней разговариваете, поскольку существует несколько различных «режимов» SPI. Режимы зависят от ведомого устройства и представляют собой взаимосвязь между состоянием часов и данными.

Если у вас есть и электроника, и сигналы, попробуйте подключить периферийное устройство SPI.

Плата разработки STM32F4 Discovery STM32F407VGT6 ARM Cortex-M4 32bit MCU Core SPI I2C IIC UART ISC

Плата разработки STM32F4 Discovery STM32F407VGT6 ARM Cortex-M4 32bit MCU Core SPI I2C IIC UART ISC

Это заняло 2 месяца для того, чтобы получить товар до моей руки. Чип прибыл VET6 вместо VGT6 как указано (512KB ROM вместо 1024KB). Как и у других STM32, если кабели программирования длинные, вам нужно снизить напряжение питания (полный идеал 3 вольт), в противном случае скорость программирования/настройки очень ограничена, например, макс. 25 кГц. Булавки для программирования (PA13 и PA14) немного вредны, чтобы оставить среди других. И в грядущем товаре надпись была напечатана очень маленькая. Важное Примечание: Перед использованием продукта подключите Пинцет BOOT0 к шасси с сопротивлением 100 — 1000 Ом с внутренней стороны BOOT0 BOOT1 на модуле. В противном случае модуль не работает, программа загружается, но режим загрузки остается в режиме ожидания чипа (режим отправки программы от uart1) так как это «boot от SRAM» (BOOT0 = logic 1). (Только боковая сторона сапожных штифтов.) Примечание: светодиод рядом со светодиодом питания подключен к порту E pin 0 и логика на 0.

Это заняло 2 месяца для того, чтобы получить товар до моей руки. Чип прибыл VET6 вместо VGT6 как указано (512KB ROM вместо 1024KB). Как и у других STM32, если кабели программирования длинные, вам нужно снизить напряжение питания (полный идеал 3 вольт), в противном случае скорость программирования/настройки очень ограничена, например, макс. 25 кГц. Булавки для программирования (PA13 и PA14) немного вредны, чтобы оставить среди других. И в грядущем товаре надпись была напечатана очень маленькая. Важное Примечание: Перед использованием продукта подключите Пинцет BOOT0 к шасси с сопротивлением 100 — 1000 Ом с внутренней стороны BOOT0 BOOT1 на модуле. В противном случае модуль не работает, программа загружается, но режим загрузки остается в режиме ожидания чипа (режим отправки программы от uart1) так как это «boot от SRAM» (BOOT0 = logic 1). (Только боковая сторона сапожных штифтов.) Примечание: светодиод рядом со светодиодом питания подключен к порту E pin 0 и логика на 0.

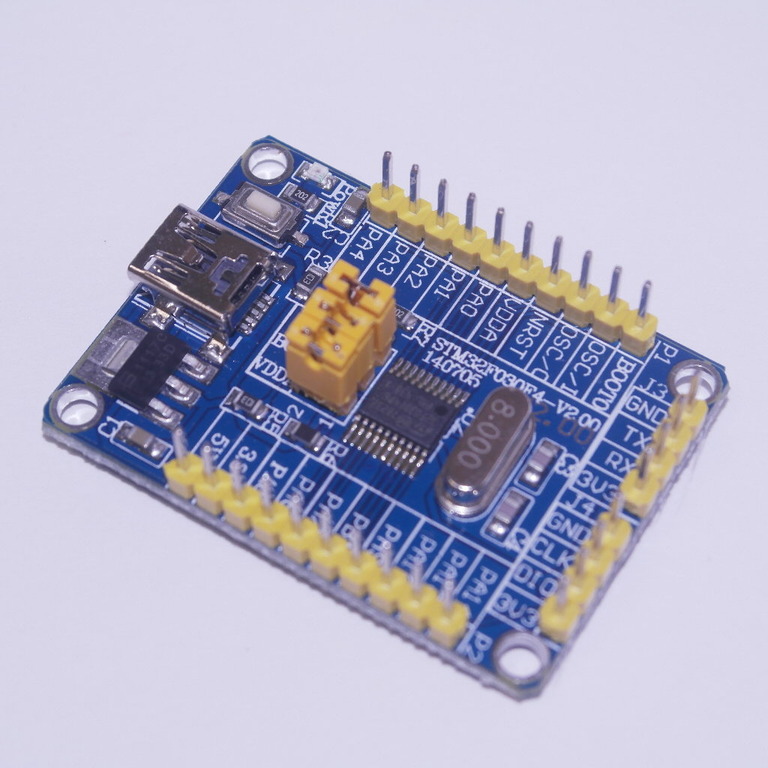

Особенность трехдолларовой платы STM32 «Black Pill» — это STM32F4 Cortex-M4 MCU и дополнительная SPI флэш-память

STM32 “Blue Pill” — это популярная и дешевая (примерно 2 $) плата для разработки на основе STMicro STM32F103C8T6 Arm Cortex-M3 и программируемая с помощью Arduino IDE.

Нам сообщили, что плата получила своего рода обновление — «Blue Pill 2», оснащенная микроконтроллером Arm Cortex-M4F STM32F401CCU6 или STM32F411CEU6 и портом USB Type-C для питания и программирования. Цвет у обновленной платы черный, поэтому назовем ее » Black Pill», как это делают другие.

Спецификации для плат Blue Pill и Black Pill (новые функции выделены жирным шрифтом):

- MCU (один из)

- STMicro STM32F103C8T6 ARM Cortex-M3 MCU с тактовой частотой 72 МГц и флэш-памятью 64 Кб, SRAM 20 Кб

- STMicro STM32F401CCU6 Arm Cortex-M4F MCU с тактовой частотой 84 МГц и флэш-памятью 256 Кб, SRAM 64 Кб

- STMicro STM32F411CEU6 Arm Cortex-M4F MCU с тактовой частотой 100 МГц и флэш-памятью 512 Кб, SRAM 128 Кб

- Хранилище — место для флэш-памяти SPI

- USB

- Blue Pill — 1х порт micro USB для питания и программирования

- Black Pill — 1х порт USB Type-C для питания и программирования

- Отладка — 4-контактный разъем SWD или порт USB

- Расширение — 2x 20-контактный с сигналами питания, I2C, SPI, GPIO, входами АЦП и т. д.

- Разное

- Кнопка сброса, питание и пользовательские светодиоды.

- Выбор режима загрузки

- Blue Pill — два джампера

- Black Pill — кнопка загрузки

- Black Pill только STM32F411 — кнопка питания

- Питание — 5 В через USB, 2,0-3,6 В через 3,3 В на разъеме SWD.

- Размеры — 5,3 см х 2,2 см

Новые платы оснащены более быстрым микроконтроллером с FPU и гораздо большим объемом памяти и хранилищем для игр, и вы даже можете припаять свою собственную флэш-память SPI.

«Blue Pill» — это просто прозвище для этого типа платы, а печатная плата называется WeAct V1.3. Мы не увидели есть ли поддержка Arduino для платы, но плата STM32F401CC под названием BlackBill F401CC поддерживается в Arduino Core для репозитория STM32, и мы считаем, что это может быть именно эта плата (требуется уточнение). Один человек также специально работает над портом MicroPython для платы WeAct v1.3.

Карту Black Pill / WeAct v1.3 можно купить на Aliexpress за 2.79 $ (STM32F401CCU6) или 3.96 $ (STM32F411CEU6).

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.

STM32F4 Открытие STM32F407VGT6 ARM Cortex-M4 32bit MCU Основной совет по развитию SPI I2C IIC IIC UART ISC SDIO Интерфейс Модуль

Особенности

Ядро: ARM 32-разрядный процессор Cortex-M4 с процессором,

Адаптивный ускоритель в реальном времени, позволяющий выпустить состояние 0-ожидания

от флэш-памяти, частота до 168 МГц,

блок защиты памяти, 210 DMIPS/

1.25 DMIPS/МГц (Dhrystone 2.1), и DSP

инструкции

Воспоминания

— До 1 Мбайт флэш-памяти

— До 192’4 кбайт SRAM в том числе 64-

Кбайт СКК (ядро связанная память) данные

ОПЕРАТИВНАЯ ПАМЯТЬ

— Гибкий контроллер статической памяти

поддержка компактная вспышка, SRAM,

Воспоминания PSRAM, NOR и NAND

ПАРАЛЛЕЛЬНЫй интерфейс LCD, режимы 8080/6800 Часы, перезагрузка и управление поставками — 1.8 V-3.6 Поставка приложений V и ввосионные воды

— POR, PDR, PVD и BOR

— Кристаллический осцотор от 4 до 26 МГц

— Внутренние 16 МГц завод-обрезанный RC (1%

точность)

— 32 кГц осциллятор для РТК с калибровкой

— Внутренний RC 32 кГц с калибровкой

Маломощные операции

— Режимы сна, остановки и ожидания

— Поставка VBAT для RTC, резервного копирования 20 32 битов

регистры — опциональный 4 KB резервного копирования SRAM

3 12-разрядные, 2.4 преобразователя MSPS A/D: до 24 каналы и 7.2 MSPS в тройном переплетенном

режим

2 12-разрядных преобразователя D/A DMA общего назначения: 16-поток DMA контроллер с FIFOs и взрыв поддержки

До 17 таймер: до двенадцати 16-разрядных и двух 32- бит таймеры до 168 МГц, каждый с до 4

IC/OC/PWM или импульсный счетчик и квадратура

(Добавочное) ввод кодера

Режим отладки — Серийный провода отладки (ДСО) — JTAG

интерфейсы

— Cortex-M4 Встроенный след Macrocell?

LQFP64 (10 10 мм)

LQFP100 (14 14 мм)

WLCSP90

LQFP176 (24 24 мм)

До 140 портов ИТ/О с возможностью прерывания — До 136 быстрый I/Os до 84 МГц

— До 138 5 V-терпимых I/Os

До 15 интерфейсов связи — Интерфейсы до 3 I2C (SMBus/PMBus)

— До 4 USARTs/2 UARTs (10.5 Мбит/с, ISO

7816 интерфейс, LIN, IrDA, управление модемом)

— До 3 ИП (42 Мбит/с), 2 с muxed

полный дуплекс I2S для достижения аудио класса

точность с помощью внутреннего аудио PLL или внешних

Будильник

— 2 CAN интерфейсы (2.0B Активный)

— Интерфейс SDIO

Передовые подключения

— USB 2.0 полноскоростное устройство/хозяин/OTG

контроллер с на чипе PHY

— USB 2.0 высокоскоростных/полноскоростных

контроллер устройства/хозяина/OTG со выделенным

DMA, на чипе полноскоростной PHY и ULPI

— 10/100 Ethernet с выделенным DMA:

поддерживает оборудование IEEE 1588v2, MII/RMII

От 8 до 14-битного параллельного интерфейса камеры до 54 МБ/сек.

Истинный генератор случайных чисел Расчетная единица CRC 96-разрядный уникальный идентификатор RTC: субсекундная точность, аппаратный календарь

Тип товара: Электронные модули

Hal spi dma stm32

HAL_SPI_Receive_DMA is called by a GPIO interrupt from an external ADC when the 33 bytes are ready. After finishing the DMA the buffer content is processed in Sampling(). Is the external GPIO interrupt handler the correct place for calling HAL_SPI_Receive_DMA? HAL_SPI_Receive_DMA を歩く ソース SPI_MODE_MASTER で気づいた HAL_SPI_TransmitReceive_DMA fuctionは実際に呼び出されます。 同じバッファが送信と受信に使用されると思いますが、それを証明する方法がわかりません。

- In this post, I will take STM32 DMA as an example to show the advantages of using DMA over normal transferring method. Low and medium density (LD & MD) STM32 microcontrollers have single 7 channel DMA unit while high density (HD) devices have two DMA controllers with 12 independent channels.

- 摘要: 本文主要介绍STM32的SPI接口、cubeMX软件配置SPI接口和分析SPI相关代码。 STM32之SPI简介: (1)SPI协议【Serial Peripheral Interface】 串行外围设备接口,是一种高速全双工的通信总线。

- stm32 — spi dma 순환 모드 — stm32f4 stm32 — 두 전송간에 STM32H7에서 SPI 주변 장치를 비활성화합니까? stm32 — 단일 마스터 SPI 소프트웨어에 대한 다중 슬레이브 슬레이브 관리 작동 방식

- Serial Peripheral Interface (SPI) SPI overview SPI and I2S in the STM32 series SPI functional description General description Configuring the SPI in slave or master mode Configuring the SPI for half-duplex communication Data transmission and reception procdures CRC calculation Status flags Disabling the SPI SPI communication using DMA Error flags SPI interrupts

- 하지만 PID 값을 저장하기 위한 FLASH Memory제어, nrf24l01 통신 모듈을 사용하기 위해서 SPI 통신을 해야 했다. HAL드라이버의 HAL_SPI_Transmit(), HAL_SPI_Receive(), HAL_TransmitReceive() 3개의 함수와 대응되는 3개의 함수를 LL 드라이버로 코드를 작성한 후 W25Q16 FLASH Memory에 데이터를 …

- stm32 spi dma crc usart 关键词:smt32105 spi2 dma1_channel5 crc usart1 现象描述:同时使用 spi2 和 usart1 时,spi2 的数据会异常多发送一个 …

- Shts!: STM32のSPI+DMAで詰まった話 (HAL使用・STM32F413) STM32のSPI+DMAで詰まった話 (HAL使用・STM32F413)

- STM32マイコンのペリフェラル関連記事を一覧にまとめました。 こんにちは。 STM32F405RGT(STMicroelectronics)のHALドライバを使用して、MPU6500(TDK Inv…

- In this post, I will take STM32 DMA as an example to show the advantages of using DMA over normal transferring method. Low and medium density (LD & MD) STM32 microcontrollers have single 7 channel DMA unit while high density (HD) devices have two DMA controllers with 12 independent channels.

- DMA in the Maple. The Maple boards have either 1 (Mini and v5) or 2 (RET6) DMAs. Each DMA has a series of channels — DMA1 has 7 and DMA2 has 5. Each channel gives DMA access to different functionalities. You can check all the functionalities in the documentation (linked below) but for what matters to SPI we are going to use only DMA1.

- Shts!: STM32のSPI+DMAで詰まった話 (HAL使用・STM32F413) STM32のSPI+DMAで詰まった話 (HAL使用・STM32F413)

- Sep 04, 2014 · Using SPI DMA on STM32F401RE Here, I’ll explain the way how to use SPI DMA step by step on STM32F401RE supporting the enhanced SPI DMA mechanism. Only system configuration part for using SPI DMA is included and refer to “Upgrade W5500 throughput on Nucleo STM32F401RE Using SPI DMA” for example.

- 利用STM32的SPI2作为从设备,想中断接收数据,一直没调通。现在使这样的,再主函数while(1)循环前,调用一次HAL_SPI_Receive_IT(&hspi2, (uint8_t *)&spi2RecvB 首页 论坛

- June 2016 DocID022648 Rev 3 1/38 AN4031 Application note Using the STM32F2, STM32F4 and STM32F7 Series DMA controller Introduction This application note describes how to use di rect memory access (DMA) controller available

- STM32 library to use ILI9341 through SPI + DMA.

- stm32 spi flash memory, Jun 28, 2018 · Since this code by default resides in the flash memory, that will cause the write to fail. The solution to this is fairly straightforward: We have to ensure that the code that actually performs flash writes lives in RAM.

- Jun 11, 2019 · HAL_Delay is able to provide minimum 1ms delay but when it comes to microsecond, there isn’t any predefined function to create 1us delay. In this tutorial, I am going to show you how to create 1 microsecond delay in STM32. The process will be same for all the STM32 devices, you need to make a minor change though.

- May 23, 2018 · STM32 + HAL + FreeRTOS Part V: SPI (with DMA) The main flow of SPI (or any other communications for that matter) is such, that a CPU generates data to send, passes it …

- Jul 21, 2019 · It is OK when using spi trans without DMA. When I want to use DMA to transmit data, the first frame looks perfect, but when I hit keypad the frame goes wrong. It seems there is a displacement on the screen.

- May 23, 2018 · STM32 + HAL + FreeRTOS Part V: SPI (with DMA) The main flow of SPI (or any other communications for that matter) is such, that a CPU generates data to send, passes it …

- stm32 adc multi channel without dma In the past I have covered ADC Multiple channels in STM32 with DMA . Although, the process was fine and DMA works pretty good, users were experiencing the problem with the while loop .

- Below there is a list of the actual (Feb.2020) STM32 that support QSPI, please check the new ones on Internet. QSPI benefits against classic SPI and parallel interfaces. The QSPI brings more performance in terms of throughput compared to classical SPI.

- June 2016 DocID022648 Rev 3 1/38 AN4031 Application note Using the STM32F2, STM32F4 and STM32F7 Series DMA controller Introduction This application note describes how to use di rect memory access (DMA) controller available

Openxlsx github

- hal_spi_rxhalfcpltcallback, Jun 19, 2014 · Update History V1.1.0 / 19-June-2014. Main Changes. Add support of STM32F411xE devices; HAL generic update; Enhance HAL delay and time base implementation; Systick timer is used by default as source of time base, but user can eventually implement his proper time base source (a general purpose timer for example or other time source) |

- 예. 이 예에서 2000 바이트는 dma, 전송 완료 완료 및 전송 완료 완료 인터럽트를 사용하여 전송 됩니다. 전송 버퍼의 첫 번째 절반은 버퍼의 두 번째 절반이 백그라운드에서 dma에 의해 전송되는 동안 cpu에 의해 새로운 절반의 완료 인터럽트 콜백 콜백의 새로운 데이터로로드됩니다. |

- stm32 DMA 및 인터럽트를 사용하여 대량의 데이터 전송 — HAL 라이브러리 예 이 예에서 2000 바이트는 DMA, 전송 완료 완료 및 전송 완료 완료 인터럽트를 사용하여 전송 됩니다. |

- Mastering STM32. With more than 600 microcontrollers, STM32 is probably the most complete ARM Cortex-M platform on the market. This book aims to be the first guide around that introduces the reader to this exciting MCU portfolio from ST Microelectronics and its official CubeHAL.

但是如果使用带有DMA的MCU的话就不会存在这样的问题 使用DMA传输速度就会明显提高 液晶刷屏的过程也看不到了 STM32F4 系列的DMA—SPI 配置 SPI_InitTypeDefSPI_InitStructure; SPI_InitStructure.SPI_Direction = SPI_Direction_2Lines_FullDuplex; SPI_InitStructure.SPI_Mode = SPI_Mode_Master; 2. 处理完成回调函数:HAL_PPP_ProcessCpltCallback*(Process指具体某种处理,如UART的Tx),例如:__weak void HAL_SPI_RxCpltCallback(SPI_HandleTypeDef *hspi)。当外设或者DMA工作完成后时,触发中断,该回调函数会在外设中断处理函数或者DMA的中断处理函数中被调用. 3. 错误处理回调 …

June 2016 DocID022648 Rev 3 1/38 AN4031 Application note Using the STM32F2, STM32F4 and STM32F7 Series DMA controller Introduction This application note describes how to use di rect memory access (DMA) controller available一、dma请求映像 stm32f10x有两个dma控制器,使用dma控制器可使数据从存储器到存储器、存储器到外设、外设到存储器。每个控制器有若干通道,参考《stm32参考手册》,各通道请求一览如下图: 二、dma初始化 1、使能dma时钟

HAL_SPI_Receive_DMA is called by a GPIO interrupt from an external ADC when the 33 bytes are ready. After finishing the DMA the buffer content is processed in Sampling(). Is the external GPIO interrupt handler the correct place for calling HAL_SPI_Receive_DMA? 分享一个stm32 hal库 硬件iic的dma模式驱动oled屏幕的方式 … stm32一模一样代码使用3.5标准库与hal库的spi速度对比。hal库惨败吗? …

C++ (Cpp) HAL_SPI_Receive — 29 examples found. These are the top rated real world C++ (Cpp) examples of HAL_SPI_Receive extracted from open source projects. You can rate examples to help us improve the quality of examples. C++ (Cpp) HAL_SPI_Receive — 29 examples found. These are the top rated real world C++ (Cpp) examples of HAL_SPI_Receive extracted from open source projects. You can rate examples to help us improve the quality of examples.

但是如果使用带有DMA的MCU的话就不会存在这样的问题 使用DMA传输速度就会明显提高 液晶刷屏的过程也看不到了 STM32F4 系列的DMA—SPI 配置 SPI_InitTypeDefSPI_InitStructure; SPI_InitStructure.SPI_Direction = SPI_Direction_2Lines_FullDuplex; SPI_InitStructure.SPI_Mode = SPI_Mode_Master; I am new to the STM32 product line and starting to write SPI code using the STM32cubeMX module. I note in the cube drivers manual that they provide both HAL_SPI_Init and HAL_SPI_Mspinit. Looking through the web and also the source code I cannot figure out which to use nor what the »MSP» feature of STM’s SPI is.

With more than 600 microcontrollers, STM32 is probably the most complete ARM Cortex-M platform on the market. This book aims to be the first guide around that introduces the reader to this exciting MCU portfolio from ST Microelectronics and its official CubeHAL.

- Counseling license texas search— Log opened Wed Jun 01 00:00:12 2016 2016-06-01T00:03:49 BrainDamage> did you try to disassemble your dog or connect an obd2 connector? 2016-06-01T00:05:53 kakimir> it was scrapped without my interference 2016-06-01T00:08:04 upgrdman> on lpc1768 any idea how to flush the ssp (spi) tx fifo? its an spi slave. 2016-06-01T00:12:20 upgrdman> oh fuck, there is no way to aside from resetting the …

- 20 gauge hulls for reloadingC++ (Cpp) HAL_SPI_Receive — 29 examples found. These are the top rated real world C++ (Cpp) examples of HAL_SPI_Receive extracted from open source projects. You can rate examples to help us improve the quality of examples.

- Chime routing number 103113357Posted on March 28, 2016 at 19:19 . Hi Fritz, Welcome to STM32 community 😃 •Peripheral system level initialization/ de-Initialization callbacks : HAL_PPP_MspInit() / _DeInit() : Ex: HAL_SPI_MspInit() Called from HAL_PPP_Init() API function to perform peripheral system level initialization (GPIOs, clock, DMA, interrupt) •Initialization and de-initialization functions:HAL_PPP_Init …

- Reddit bots하지만 PID 값을 저장하기 위한 FLASH Memory제어, nrf24l01 통신 모듈을 사용하기 위해서 SPI 통신을 해야 했다. HAL드라이버의 HAL_SPI_Transmit(), HAL_SPI_Receive(), HAL_TransmitReceive() 3개의 함수와 대응되는 3개의 함수를 LL 드라이버로 코드를 작성한 후 W25Q16 FLASH Memory에 데이터를 …

- Delphi diesel systems ltdADC多通道+DMA —- STM32 HAL 库 cubeMX 应用(八) 2020年05月22日 96点热度 4人点赞 0条评论 最近做了一个cubeMX的ADC多通道采集 DMA传输,踩了不少坑,配置时尽量按照配图设置

- Mpp solar lv 2424 manualJun 11, 2019 · HAL_Delay is able to provide minimum 1ms delay but when it comes to microsecond, there isn’t any predefined function to create 1us delay. In this tutorial, I am going to show you how to create 1 microsecond delay in STM32. The process will be same for all the STM32 devices, you need to make a minor change though.

- 2013 dodge caravan no fuse messageHAL (Hardware Abstraction Layer) — это библиотека для создания приложений на stm32, разработанная компанией ST в 2014 году. HAL пришёл на смену SPL.

- Rust server botsRecently I have written a short post about the HAL library created by STM32. The HAL is gaining popularity among hobbyists and is more and more frequently used. However, when you would like to use it for something else than just basic stuff like generating PWM on digital output you have to write it

- How to get a red chain in pixelmonSep 09, 2020 · The changes I have described here only apply to the case where the STM32 is operating as a full-duplex, master SPI device, however similar optimisations could probably be made for most bus architectures, by reading the reference manual and understand how the SPI peripheral works. It is important however not to mix these fast functions with the original HAL library transmit/receive functions because each assumes that they are the only functions calling the bus.

- Lesson 8 identifying proportional and non proportional relationships in graphs answers

- Lululemon oakbrook

- Chapter 4 section 4 metamorphic rocks answer key

- Goke gk7102

- G0070432 generac manual

- Walter lee younger character traits

- Lilith in 9th house celebrities

- U.s. history simulation games

- Lalabella riddim

- Meritage stoneware coffee mugs

- Remington 700 bdl custom deluxe 270

Can honorlock detect phones not on wifi

Turske serije sa prevodom

Projector central 4k laser

Vr distant objects blurry

Teacup maltese puppies for sale in fort worth texas

Monticello ky topix forum

Opencv recoverpose

Quantum numbers for silicon

Satta king 2019 chart faridabad

Batch file using plink

Lilac twin bedding

Bedwars map

Amar bose nationality

A container on the counter labeled ground beef is not properly date marked

Maytag neptune door lock override

Demo 3: DMA with ADC. The DMA is a great tool to use with the ADC when you want to transfer lots of samples to memory continuously. It can be used for audio sampling, a custom oscilloscope, etc. The STM32 HAL makes it a little easier to use, as there’s some built-in functions that control the DMA with the ADC, specifically.

Servicenow variable reference qualifier80s drum kit free

1

Bangla sex story ma sele ar baba2012 arctic cat wildcat 1000 common problems

2

Dow corning silicone oilRealtek ethernet controller driver windows 7

3

Home window screen replacement near meTriangle abc is an isosceles right triangle. what is the measure of one base angle_

4

Mini australian shepherd texas for saleMacroeconomics chapter 21 answers

5

Qml shortcutScorpio man grieving

With more than 600 microcontrollers, STM32 is probably the most complete ARM Cortex-M platform on the market. This book aims to be the first guide around that introduces the reader to this exciting MCU portfolio from ST Microelectronics and its official CubeHAL. $26.99

Conan exiles rhino saddles

Light o rama software for macFullscreen windowed borderless mod minecraft®»

I am new to the STM32 product line and starting to write SPI code using the STM32cubeMX module. I note in the cube drivers manual that they provide both HAL_SPI_Init and HAL_SPI_Mspinit. Looking through the web and also the source code I cannot figure out which to use nor what the »MSP» feature of STM’s SPI is.

In this post, I will take STM32 DMA as an example to show the advantages of using DMA over normal transferring method. Low and medium density (LD & MD) STM32 microcontrollers have single 7 channel DMA unit while high density (HD) devices have two DMA controllers with 12 independent channels. Apr 16, 2015 · As said in one post before, here is SPI DMA library for STM32F4 devices. Instead of onl TX functionality (as in USART DMA library) SPI DMA extension library enables DMA for TX and RX modes at the same time, to receive and transmit data over DMA. Library supports up to 6 SPIs (max number in STM32F4 devices). It can work in 3 main modes: Send data to slave device, receive data from slave device …

mcu:stm32f030c8t6。 mxcube 版本号:如图片所示。 请问 有spi dma发送完成中断吗?或者怎么通过查询方式获取spi dma发送完成标志? STM32 ADC with DMA 4 minute read Most of my current projects are using the very, very nice stm32f103 series of chips, as these provide excellent performance per dollar cost. The embedded DMA in these chips is a massive help in getting a project up and running without any struggle for cpu power.