Что такое регистр TCCR1B в микроконтроллерах AVR. Какие биты входят в его состав. Как настроить работу таймера/счетчика 1 с помощью TCCR1B. Для чего используются биты ICNC1, ICES1, WGM13, WGM12, CS12, CS11, CS10.

Структура и назначение регистра TCCR1B

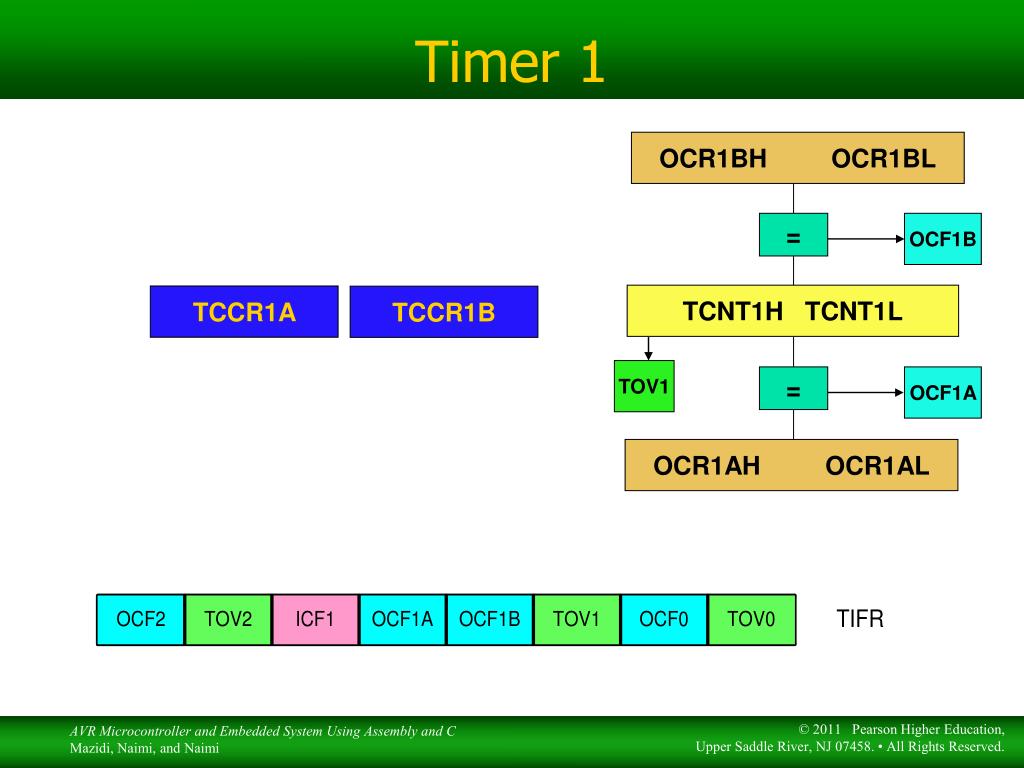

Регистр TCCR1B (Timer/Counter Control Register B) является одним из ключевых регистров для управления работой 16-битного таймера/счетчика 1 в микроконтроллерах семейства AVR. Он позволяет настроить режим работы таймера, источник тактирования и другие параметры.

Регистр TCCR1B имеет следующую структуру:

- Бит 7 — ICNC1: Подавление шума входа захвата

- Бит 6 — ICES1: Выбор фронта сигнала захвата

- Бит 5 — Зарезервирован

- Бит 4 — Зарезервирован

- Бит 3 — WGM13: Режим генерации формы сигнала

- Бит 2 — WGM12: Режим генерации формы сигнала

- Биты 1-0 — CS12, CS11, CS10: Выбор источника тактирования

Настройка подавления шума на входе захвата (ICNC1)

Бит ICNC1 позволяет включить функцию подавления шума для входа захвата ICP1. Как это работает?

- ICNC1 = 0: Подавление шума отключено

- ICNC1 = 1: Подавление шума включено

При включенном подавлении шума сигнал на входе ICP1 фильтруется. Для фиксации события захвата требуется 4 последовательных одинаковых отсчета. Это вносит задержку в 4 такта, но повышает помехозащищенность.

Выбор фронта сигнала для захвата (ICES1)

Бит ICES1 определяет, по какому фронту входного сигнала будет происходить захват значения таймера/счетчика:

- ICES1 = 0: Захват по спадающему фронту

- ICES1 = 1: Захват по нарастающему фронту

При наступлении выбранного фронта текущее значение таймера/счетчика копируется в регистр захвата ICR1. Также устанавливается флаг прерывания захвата ICF1.

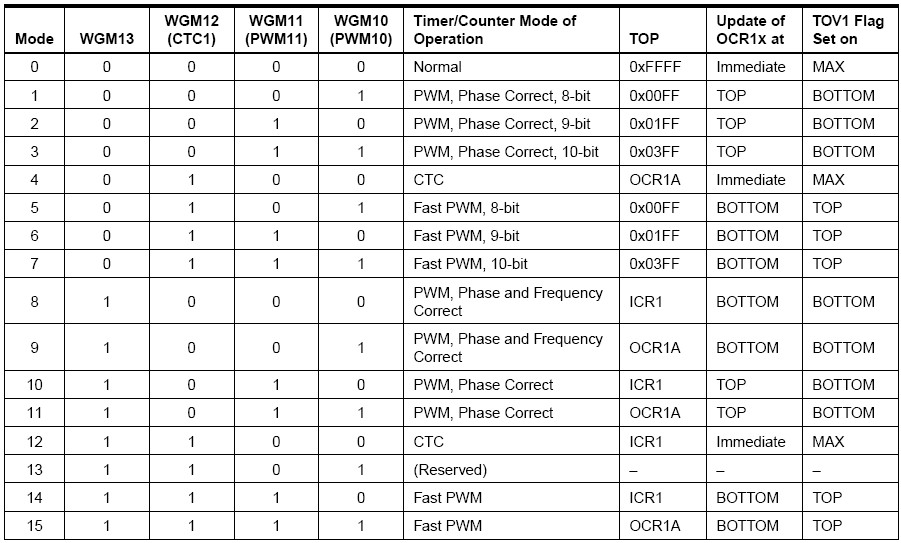

Настройка режима работы таймера/счетчика (WGM13, WGM12)

Биты WGM13 и WGM12 в сочетании с битами WGM11 и WGM10 из регистра TCCR1A задают режим работы таймера/счетчика 1. Какие режимы доступны?

- Нормальный режим

- Режим ШИМ с коррекцией фазы и частоты

- Режим ШИМ с коррекцией фазы

- Режим ШИМ Fast PWM

- Режим CTC (сброс при совпадении)

Выбор конкретного режима осуществляется комбинацией битов WGM13:0 согласно таблице в документации микроконтроллера.

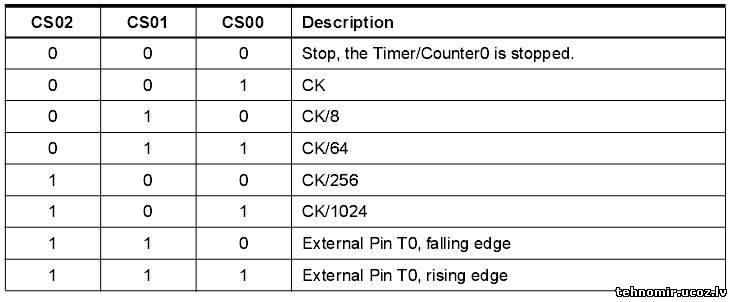

Выбор источника тактирования (CS12, CS11, CS10)

Биты CS12, CS11 и CS10 позволяют выбрать источник тактовых импульсов для таймера/счетчика 1. Какие варианты доступны?

- 000 — Таймер/счетчик остановлен

- 001 — Тактирование напрямую от системной частоты (CK)

- 010 — Системная частота, деленная на 8 (CK/8)

- 011 — Системная частота, деленная на 64 (CK/64)

- 100 — Системная частота, деленная на 256 (CK/256)

- 101 — Системная частота, деленная на 1024 (CK/1024)

- 110 — Внешний источник на выводе T1, по спадающему фронту

- 111 — Внешний источник на выводе T1, по нарастающему фронту

Выбор подходящего предделителя позволяет настроить частоту работы таймера под конкретную задачу.

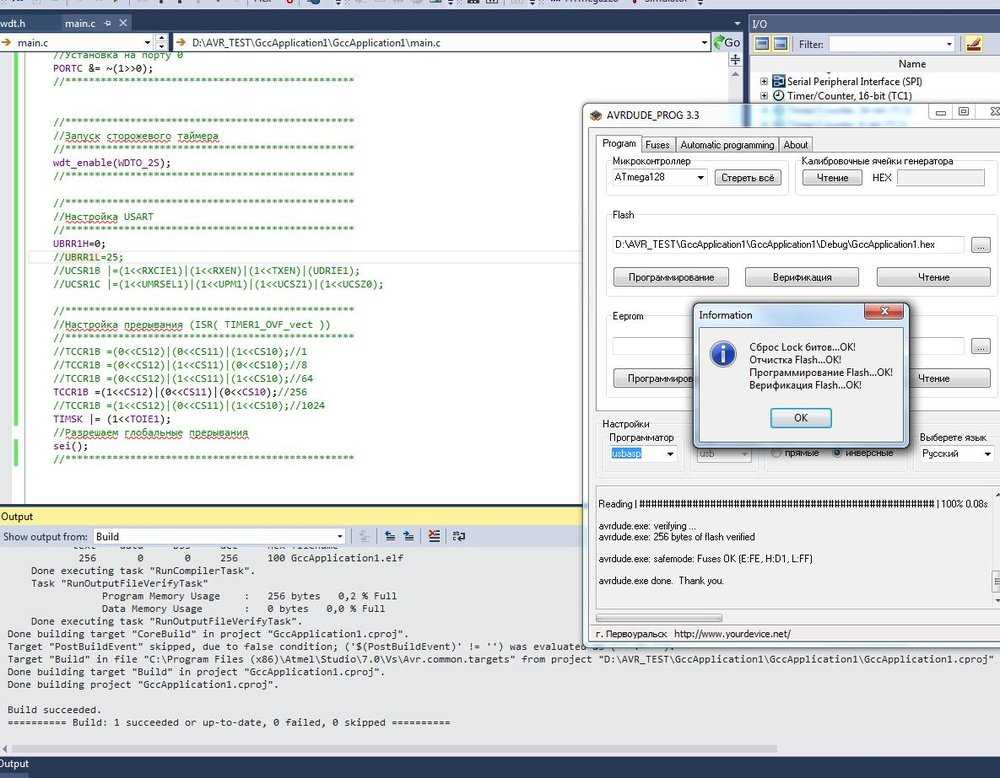

Пример настройки TCCR1B для генерации ШИМ-сигнала

Рассмотрим пример настройки таймера/счетчика 1 для генерации ШИМ-сигнала с частотой около 490 Гц:

// Настройка Fast PWM режима, TOP = 0x00FF

TCCR1A |= (1 << WGM10);

TCCR1B |= (1 << WGM12);

// Предделитель 64

TCCR1B |= (1 << CS11) | (1 << CS10);

// Включаем выход OC1A

TCCR1A |= (1 << COM1A1);

В этом примере мы настроили таймер на работу в режиме Fast PWM с 8-битным разрешением, выбрали предделитель 64 и включили выход OC1A для генерации ШИМ-сигнала.

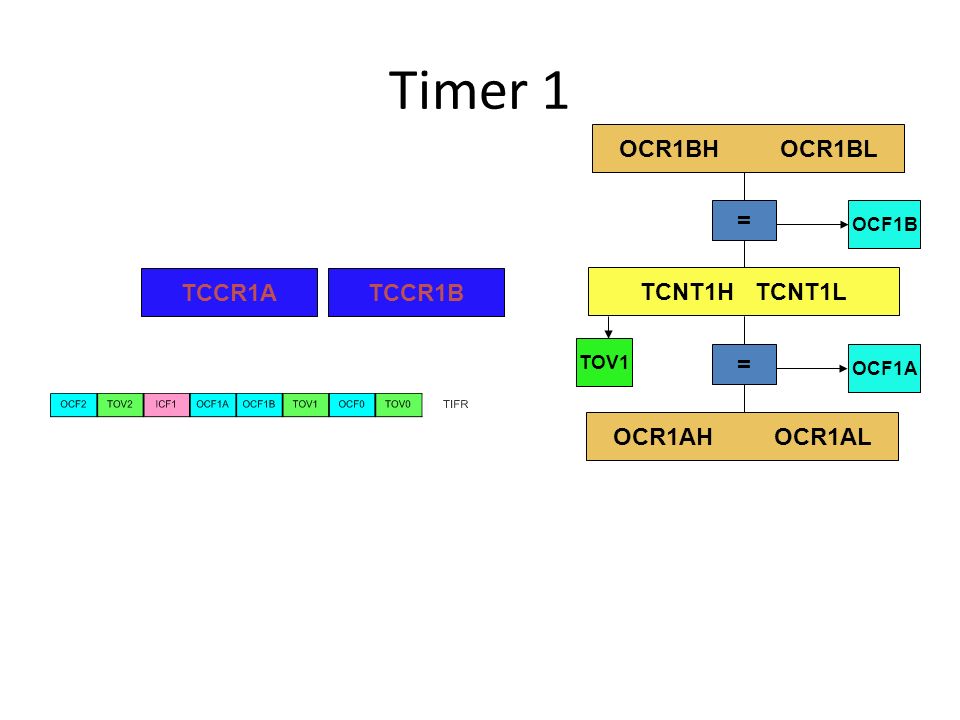

Взаимодействие TCCR1B с другими регистрами таймера/счетчика 1

Регистр TCCR1B тесно взаимодействует с другими регистрами таймера/счетчика 1. Как они связаны между собой?

- TCCR1A - дополняет TCCR1B в настройке режима работы и управлении выходами

- TCNT1 - содержит текущее значение счетчика

- OCR1A и OCR1B - регистры сравнения

- ICR1 - регистр захвата

- TIMSK1 - управляет прерываниями таймера

- TIFR1 - содержит флаги прерываний таймера

Правильная настройка всех этих регистров в комплексе позволяет реализовать широкий спектр задач таймирования и генерации сигналов.

Особенности использования TCCR1B в различных режимах работы таймера

В зависимости от выбранного режима работы таймера/счетчика 1, некоторые биты TCCR1B могут иметь особое значение. Какие особенности нужно учитывать?

- В режиме CTC бит WGM12 определяет, используется ли OCR1A или ICR1 в качестве TOP-значения

- В режимах ШИМ биты WGM13:0 определяют разрешение и тип ШИМ (с коррекцией фазы или Fast PWM)

- При использовании внешнего тактирования (CS12:10 = 110 или 111) важно правильно настроить соответствующий вывод микроконтроллера

Учет этих особенностей позволяет максимально эффективно использовать возможности таймера/счетчика 1.

Изменение настроек TCCR1B во время работы программы

Можно ли изменять настройки TCCR1B во время выполнения программы? Да, это возможно, но требует соблюдения некоторых правил:

- Изменение предделителя (CS12:10) приведет к немедленному изменению частоты работы таймера

- Изменение режима работы (WGM13:0) может вызвать нежелательные эффекты, если не синхронизировано с работой таймера

- Изменение настроек захвата (ICNC1, ICES1) может повлиять на текущую операцию захвата

Рекомендуется временно останавливать таймер перед существенным изменением его настроек, чтобы избежать непредсказуемого поведения.

Типичные ошибки при работе с регистром TCCR1B

При работе с регистром TCCR1B новички часто допускают определенные ошибки. Каковы самые распространенные из них?

- Забывают инициализировать все необходимые биты, что приводит к неправильной работе таймера

- Не учитывают взаимосвязь с другими регистрами, например, TCCR1A

- Неправильно выбирают предделитель, что приводит к неожиданной частоте работы таймера

- Изменяют настройки без учета текущего состояния таймера, что может вызвать сбои

Внимательное изучение документации и понимание принципов работы таймера поможет избежать этих ошибок.

РЕГИСТР B УПРАВЛЕНИЯ ТАЙМЕРОМ/СЧЕТЧИКОМ 1

РЕГИСТР B УПРАВЛЕНИЯ ТАЙМЕРОМ/СЧЕТЧИКОМ 1 - TCCR1B — Мегаобучалка

Eh(4Eh) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |||

| ICNC1 | ICES1 | - | - | CTC1 | CS12 | CS11 | CS10 | ||||

| R\W | R\W | R | R | R\W | R\W | R\W | R \ W | ||||

| Начальное значение | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Бит7 - ICNC1: Подавитель входного шума входа захвата: Если этот бит сброшен (0), подавление входного шума входа захвата запрещено.

Бит 6 - ICES1: выбор фронта сигнала захвата: Если бит ICES1 сброшен (0) содержимое таймера/счетчика 1 переписывается в регистр захвата по спадающему фронту сигнала на выводе ICP. Если бит установлен - по нарастающему фронту сигнала.

Биты 5,4 - зарезервированы. В AT90S2333/4433 эти биты зарезервированы и всегда читаются как 0.

Бит 3 - CTC1: Очистка таймера счетчика 1 по совпадению: Если бит установлен (1), таймер/счетчик 1 устанавливается в 0000h в такте следующем за событием совпадения. Если бит сброшен, таймер/счетчик 1 продолжает считать, совпадение не отражается на состоянии таймера/счетчика.

за событием совпадения, в следующем после совпадения такте в счетчик запишется число на 1 большее значения регистра совпадения. При коэффициенте деления 1, установке регистра совпадения на величину С и установленном бите CTC1, таймер принимает следующие значения:

...С-1,С,С+1,0,1...

при делении тактовой частоты на 8:

...С-1,С-1,С-1,С-1,С-1,С-1,С-1,С-1,С,С,С,С,С,С,С,С, С+1,0,0,0,0,0,0,0,0,1...

В режиме ШИМ этот бит не работает.

Биты 2,1,0 - CS12, CS11, CS10: выбор тактирования: Эти биты определяют источник счетных импульсов для таймера/счетчика 1.

Таблица 11. Выбор источника счетных импульсов

| CS12 | CS11 | CS10 | Описание |

| 0 | 0 | 0 | Таймер/счетчик 1 остановлен |

| 0 | 0 | 1 | CK |

| 0 | 1 | 0 | CK/8 |

| 0 | 1 | 1 | CK/64 |

| 1 | 0 | 0 | CK/256 |

| 1 | 0 | 1 | CK/1024 |

| 1 | 1 | 0 | Спадающий фронт на выводе T1 |

| 1 | 1 | 1 | Нарастающий фронт на выводе T1 |

Условие Stop запрещает/разрешает функционирование таймера/счетчика.

ТАЙМЕР/СЧЕТЧИК 1 - TCNT1H И TCNT1L

TCNT 1 H

| 2Dh(4Dh) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| MSB | - | - | - | - | - | - | - | |

| R\W | R\W | R\W | R\W | R\W | R\W | R\W | R\ W | |

| Начальное значение | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

TCNT1L

| 2Ch(4Ch) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LSB | ||||||||

| R\W | R\W | R\W | R\W | R\W | R\W | R\W | R\ W | |

| Начальное значение | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Это 16-разрядный регистр, содержащий текущее значение таймера/счетчика 1. Чтобы чтение и запись двух байт счетчика происходило синхронно, для работы с ним используется временный регистр (TEMP). Этот вре-

Чтобы чтение и запись двух байт счетчика происходило синхронно, для работы с ним используется временный регистр (TEMP). Этот вре-

менный регистр также используется при доступе к регистрам OCR1 и ICR1.

Если доступ к регистру с использованием TEMP производится и в основной программе и в обработчике прерывания, на время доступа к регистру из основной программы прерывания должны быть запрещены.

- Запись в таймер счетчик 1: При записи старшего байта в TCNT1H, записываемые данные помещаются в регистр TEMP. Затем, при записи младшего байта, он вместе с данными из TEMP переписывается в таймер/счетчик 1. Таким образом, при записи 16-разрядного значения первым должен записываться байт в TCNT1H.

- Чтение таймера/счетчика 1: При чтении младшего байта из TCNT1L, он посылается в процессор, а данные из TCNT1H переписываются в регистр TEMP, то есть одновременно читаются все 16-разрядов. При последующем чтении регистра TCNT1H, данные берутся из регистра TEMP. То есть при чтении 16-разрядного значения счетчика первым должен читаться регистр TCNT1L.

То есть при чтении 16-разрядного значения счетчика первым должен читаться регистр TCNT1L.

Таймер/счетчик 1 организован как суммирующий счетчик (в режиме ШИМ - суммирующий/вычитающий) с возможностью чтения и записи. Если задан источник тактовых импульсов для таймера/счетчика 1, после записи в него нового значения, счет продолжается с следующем за операцией записи

периоде тактовой частоты.

РЕГИСТР СОВПАДЕНИЯ ТАЙМЕРА/СЧЕТЧИКА 1 - OCR1H И OCR1L

OCR1H

| 2Bh(4Bh) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| MSB | ||||||||

| R\W | R\W | R\W | R\W | R\W | R\W | R\W | R\ W | |

| Начальное значение | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

OCR1L

| 3Dh(5Dh) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| LSB | ||||||||

| R\W | R\W | R\W | R\W | R\W | R\W | R\W | R\ W | |

| Начальное значение | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Регистр совпадения 16-разрядный регистр, доступный для чтения и записи. В этом регистре хранятся данные, которые непрерывно сравниваются с текущим значением таймера/счетчика 1. Действие по совпадению задается регистрами управления таймером/счетчиком 1 и регистром состояния. Поскольку регистр OCR1A является 16-разрядным, при записи нового значения в регистр, для того чтобы оба байта регистра записывались одновременно, используется временный регистр (TEMP). При записи старшего байта, данные помещаются во временный регистр, который переписывается в OCR1AH при записи младшего байта в OCR1AL. Таким образом, для записи в регистр первым должен записываться старший байт. Регистр TEMP используется при доступе к TCNT1 и ICR1, поэтому если временный регистр используется в основной программе и в прерываниях, при доступе к TEMP из основной программы прерывания должны запрещаться.

В этом регистре хранятся данные, которые непрерывно сравниваются с текущим значением таймера/счетчика 1. Действие по совпадению задается регистрами управления таймером/счетчиком 1 и регистром состояния. Поскольку регистр OCR1A является 16-разрядным, при записи нового значения в регистр, для того чтобы оба байта регистра записывались одновременно, используется временный регистр (TEMP). При записи старшего байта, данные помещаются во временный регистр, который переписывается в OCR1AH при записи младшего байта в OCR1AL. Таким образом, для записи в регистр первым должен записываться старший байт. Регистр TEMP используется при доступе к TCNT1 и ICR1, поэтому если временный регистр используется в основной программе и в прерываниях, при доступе к TEMP из основной программы прерывания должны запрещаться.

РЕГИСТР ЗАХВАТА ТАЙМЕРА/СЧЕТЧИКА 1 - ICR1H И ICR1L

ICR1H

H(45h)

ICR1L

H(44h)

Регистр захвата 16-разрядный регистр доступный только для чтения. По нарастающему или спадающему фронту (в соответствии с выбором фронта импульса захвата ICES1) сигнала на выводе ICP текущее значение таймера/счетчика 1 переписывается в регистр захвата ICR1. В это же время устанавливается флаг захвата ICF1. Поскольку регистр захвата является 16-разрядным, для чтения его значения, чтобы оба байта прочитались одновременно, используется временный регистр. При чтении младшего байта ICR1L, он посылается в ЦПУ, а старший байт регистра ICR1H переписывается во временный регистр (TEMP). При чтении старшего байта, он принимается из временного регистра. Таким образом для чтения 16-разрядного регистра первым должен читаться младший байт. Регистр TEMP используется при доступе к TCNT1 и OCR1, поэтому если временный регистр используется в основной программе и в прерываниях, при доступе к TEMP из основной программы прерывания должны запрещаться.

По нарастающему или спадающему фронту (в соответствии с выбором фронта импульса захвата ICES1) сигнала на выводе ICP текущее значение таймера/счетчика 1 переписывается в регистр захвата ICR1. В это же время устанавливается флаг захвата ICF1. Поскольку регистр захвата является 16-разрядным, для чтения его значения, чтобы оба байта прочитались одновременно, используется временный регистр. При чтении младшего байта ICR1L, он посылается в ЦПУ, а старший байт регистра ICR1H переписывается во временный регистр (TEMP). При чтении старшего байта, он принимается из временного регистра. Таким образом для чтения 16-разрядного регистра первым должен читаться младший байт. Регистр TEMP используется при доступе к TCNT1 и OCR1, поэтому если временный регистр используется в основной программе и в прерываниях, при доступе к TEMP из основной программы прерывания должны запрещаться.

Читайте также:

©2015-2020 megaobuchalka.ru Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. (172)

(172)

Почему 1285321 студент выбрали МегаОбучалку...

Система поиска информации

Мобильная версия сайта

Удобная навигация

Нет шокирующей рекламы

(0.004 сек.)

| //Таймер0 | |

| TCCR0B = (TCCR0B и 0b11111000) | 0x01; //62,5 [кГц] | |

| TCCR0B = (TCCR0B и 0b11111000) | 0x02; //7,8125 [кГц] | |

| TCCR0B = (TCCR0B и 0b11111000) | 0x03; //976,5625 [Гц] | |

| TCCR0B = (TCCR0B и 0b11111000) | 0x04; //244.140625 [Гц] | |

| TCCR0B = (TCCR0B и 0b11111000) | 0x05; //61.03515625 [Гц] | |

| //Таймер1 | |

| TCCR1B = (TCCR1B и 0b11111000) | 0x01; //31,37255 [кГц] | |

| TCCR1B = (TCCR1B и 0b11111000) | 0x02; //3,92116 [кГц] | |

| TCCR1B = (TCCR1B и 0b11111000) | 0x03; //490,20 [Гц] | |

| TCCR1B = (TCCR1B и 0b11111000) | 0x04; //122,55 [Гц] | |

| TCCR1B = (TCCR1B и 0b11111000) | 0x05; //30,64 [Гц] | |

| //Таймер2 | |

| TCCR2B = (TCCR2B и 0b11111000) | 0x01; //31,37255 [кГц] | |

| TCCR2B = (TCCR2B и 0b11111000) | 0x02; //3,92116 [кГц] | |

| TCCR2B = (TCCR2B и 0b11111000) | 0x03; //980,39 [Гц] | |

| TCCR2B = (TCCR2B и 0b11111000) | 0x04; //490,20 [Гц] | |

| TCCR2B = (TCCR2B и 0b11111000) | 0x05; //245,10 [Гц] | |

| TCCR2B = (TCCR2B и 0b11111000) | 0x06; //122,55 [Гц] | |

| TCCR2B = (TCCR2B и 0b11111000) | 0x07; //30,64 [Гц] | |

| //Таймер3 | |

| TCCR3B = (TCCR3B и 0b11111000) | 0x01; //31,37255 [кГц] | |

| TCCR3B = (TCCR3B и 0b11111000) | 0x02; //3,92116 [кГц] | |

| TCCR3B = (TCCR3B и 0b11111000) | 0x03; //490,20 [Гц] | |

| TCCR3B = (TCCR3B и 0b11111000) | 0x04; //122,55 [Гц] | |

| TCCR3B = (TCCR3B и 0b11111000) | 0x05; //30,64 [Гц] | |

| //Таймер4 | |

| TCCR4B = (TCCR4B и 0b11111000) | 0x01; //31,37255 [кГц] | |

| TCCR4B = (TCCR4B и 0b11111000) | 0x02; //3,92116 [кГц] | |

| TCCR4B = (TCCR4B и 0b11111000) | 0x03; //490,20 [Гц] | |

| TCCR4B = (TCCR4B и 0b11111000) | 0x04; //122,55 [Гц] | |

| TCCR4B = (TCCR4B и 0b11111000) | 0x05; //30,64 [Гц] |

TCCR1B Регистр управления таймером/счетчиком 1 B

TCCR1B Регистр ATmega8

Бит 7 ICNC1: Шумоподавление захвата ввода

Wenn dieses Bit gesetzt ist, ist der Rauschunterdrcker aktiviert. Wenn der Rauschunterdrcker aktiviert ist, wird der Eingang des Input Capture Pins gefiltert. Die Filterfunktion erfordert vier erfolgreiche gleiche Wertabtastungen des ICP1 Pins um seinen Ausgang zu ndern. Der Input Capture ist daher um vier Takte verzgert, wenn der Rauschunterdrcker freigegeben ist.

Wenn der Rauschunterdrcker aktiviert ist, wird der Eingang des Input Capture Pins gefiltert. Die Filterfunktion erfordert vier erfolgreiche gleiche Wertabtastungen des ICP1 Pins um seinen Ausgang zu ndern. Der Input Capture ist daher um vier Takte verzgert, wenn der Rauschunterdrcker freigegeben ist.

Бит 6 ICES1: Выбор края захвата ввода

Быстрый бит лучше всего, если входной пин-код Capture Pin (ICP1) не работает, а только Capture Ereignis zu Triggern. Wenn das ICES1 Bit auf 0 gesetzt wird, wird eine отрицательный/fallende Flanke als Trigger verwendet, wenn das ICES1 Bit auf 1 gesetzt ist, wird eine положительный/steigende Flanke als Trigger verwendet.

Wenn ein Trigger entsprechend der Einstellung des Bits erfolgt, wird der Wert des Zlers in das Input Capture Register (ICR1) kopiert. Das Ereignis setzt ebenfalls das Input Capture Flag (ICF1), das verwendet werden kann, um einen Interrupt auszulsen, wenn dieser freigegeben ist.