Что такое универсальный регистр. Как работает универсальный регистр сдвига. Какие бывают виды универсальных регистров. Где применяются универсальные регистры в цифровой электронике.

Что такое универсальный регистр и как он работает

Универсальный регистр — это устройство цифровой электроники, предназначенное для приема, хранения и преобразования двоичных чисел. Основные функции универсального регистра:

- Прием данных в параллельном или последовательном коде

- Хранение двоичного числа

- Сдвиг хранимого числа влево или вправо

- Выдача данных в параллельном или последовательном коде

Универсальный регистр состоит из набора триггеров, число которых определяет его разрядность. Управление режимами работы осуществляется с помощью дополнительных логических элементов.

Основные виды универсальных регистров

В зависимости от функциональных возможностей выделяют следующие виды универсальных регистров:

1. Регистры хранения

Простейший вид, предназначенный только для приема и хранения двоичного числа. Число записывается параллельным кодом и хранится до следующей записи или сброса.

2. Регистры сдвига

Помимо хранения, позволяют осуществлять сдвиг записанного числа влево или вправо. Бывают однонаправленные (только влево или только вправо) и двунаправленные.

3. Реверсивные регистры сдвига

Универсальные регистры, позволяющие выполнять сдвиг в обоих направлениях. Направление сдвига задается управляющим сигналом.

4. Кольцевые регистры

Разновидность сдвиговых регистров, в которых выход последнего разряда соединен со входом первого. Позволяют циклически сдвигать записанное число.

Принцип работы универсального регистра сдвига

Рассмотрим принцип работы универсального 4-разрядного регистра сдвига на примере микросхемы 74ALS299:

- Параллельная загрузка данных на входы D0-D3

- Запись данных во внутренние триггеры по тактовому импульсу

- Выбор режима работы (хранение/сдвиг) управляющими сигналами

- Сдвиг данных влево или вправо на один разряд за такт

- Вывод результата на параллельные выходы Q0-Q3

Направление сдвига задается отдельным входом. Последовательные входы/выходы позволяют объединять несколько регистров в цепочку для обработки длинных двоичных чисел.

Применение универсальных регистров в цифровой технике

Универсальные регистры широко используются в различных узлах цифровой электроники:

- Оперативные запоминающие устройства

- Арифметико-логические устройства процессоров

- Счетчики и делители частоты

- Устройства задержки цифровых сигналов

- Преобразователи кодов

- Генераторы псевдослучайных последовательностей

Важной областью применения являются микропроцессоры и микроконтроллеры, где универсальные регистры используются для временного хранения операндов, адресов и результатов вычислений.

Преимущества использования универсальных регистров

Универсальные регистры обладают рядом преимуществ по сравнению с другими цифровыми устройствами:

- Многофункциональность — возможность работы в разных режимах

- Высокое быстродействие за счет параллельной обработки данных

- Простота каскадирования для увеличения разрядности

- Возможность преобразования данных из последовательной формы в параллельную и обратно

- Компактность реализации на интегральных микросхемах

Эти качества делают универсальные регистры незаменимыми компонентами современных цифровых систем.

Примеры микросхем универсальных регистров

Некоторые распространенные микросхемы универсальных регистров:

- К155ИР1 — 4-разрядный универсальный регистр сдвига

- 74ALS194 — 4-разрядный двунаправленный универсальный регистр сдвига

- 74ALS299 — 8-разрядный универсальный регистр сдвига/хранения

- ИР8 — 8-разрядный универсальный регистр с тремя состояниями на выходе

При выборе конкретной микросхемы учитываются разрядность, быстродействие, энергопотребление и другие параметры, важные для конкретного применения.

Заключение

Универсальные регистры являются важнейшими функциональными узлами цифровой техники. Их многофункциональность и гибкость позволяют создавать эффективные решения для широкого спектра задач обработки цифровой информации. Глубокое понимание принципов работы универсальных регистров необходимо для проектирования современных цифровых устройств и систем.

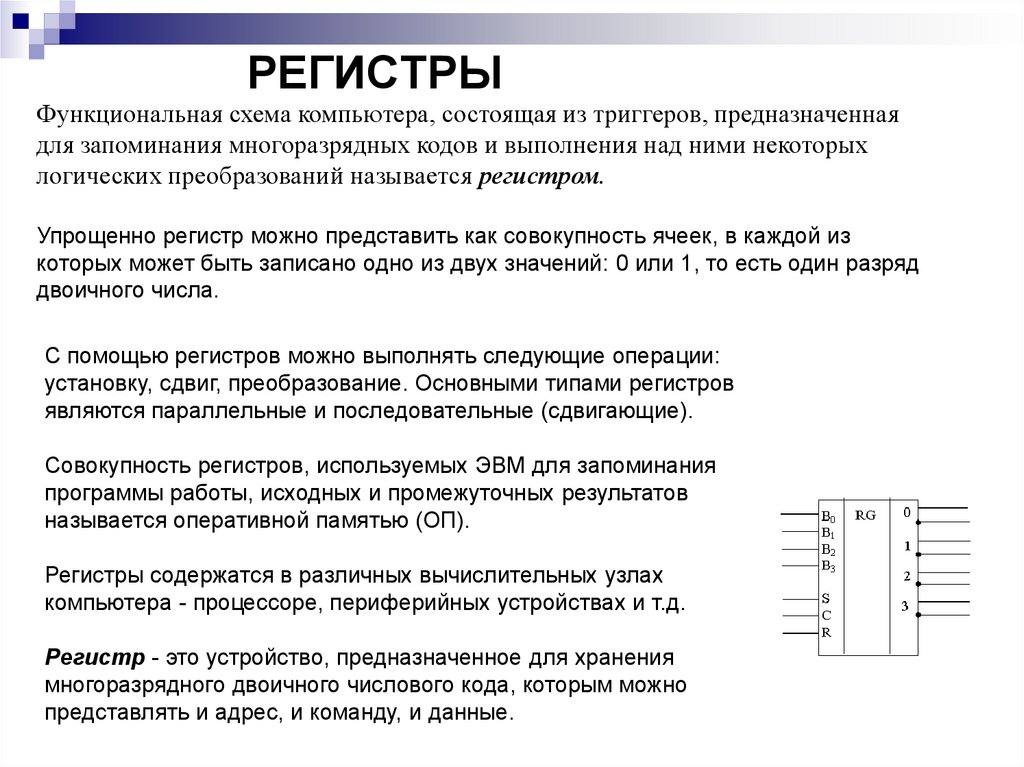

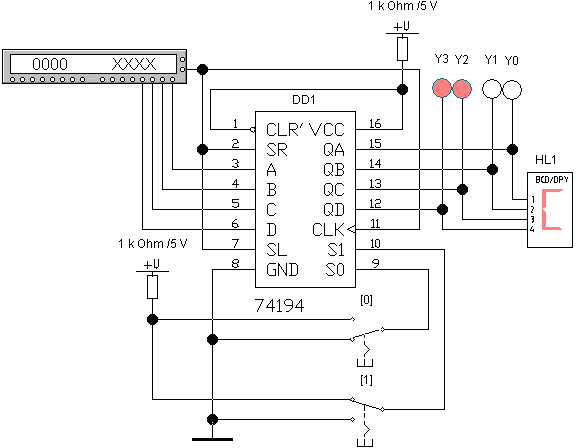

УНИВЕРСАЛЬНЫЙ РЕГИСТР

На основе отдельных триггеров строится целый спектр приборов цифровой электроники без которых нельзя себе представить какую-либо относительно сложную конструкцию. Одним из таких приборов является регистр. Регистр служит для приема и хранения двоичных чисел. Работу данного типа приборов можно рассмотреть на базе универсального регистра К155ИР1. Питание подается на 14 выход микросхемы, общий провод 7. Питание осуществляется от стабилизированного источника питания напряжением 5 В.

Этот регистр может работать как в последовательном, так и в параллельном режиме. Выбор режима осуществляется установкой низкого, либо высокого потенциала на входе v. Если на вход v подан потенциал низкого уровня, то регистр работает в последовательном режиме по тактовым сигналам со входа С1 при этом данные считываются со входа D0. Если на вход v подан потенциал высокого уровня, то регистр работает по тактовым сигналам со входа С2 при этом данные считываются со входов D1-D4 [Ямпольский В.С. Основы автоматики и электронно-вычислительной техники – М. Просвещение, 1991].

При организации работы регистра в параллельном режиме следует помнить, что ТТЛ-логика воспринимает неподключенный вход микросхемы как высокий логический уровень.

Для демонстрации работы регистра в последовательном режиме потребуется источник синхроимпульсов. Подачи синхроимпульсов осуществляется с мультивибратора на микросхеме К155ЛА3.

При этом регистр производит сдвиг записанной информации в сторону возрастания номеров выходов (сдвиг вправо). Небольшое преобразование схемы позволяет организовать сдвиг влево.

Видео

Автор обзора: Denev.

Форум

Форум по обсуждению материала УНИВЕРСАЛЬНЫЙ РЕГИСТР

Что такое регистр? Регистр сдвига.

Регистр. Регистр сдвига

Регистр это устройство, выполненное на триггерах для выполнения ряда действий с двоичными числами. Для тех, кто не знает, что такое триггер, рекомендуем познакомиться с простейшим RS-триггером.

Наиболее простая функция регистров — это запоминание числа и его длительное хранение. Эти устройства так и называются – регистры хранения. Вот простейший пример.

На входы D0 – D2 подаётся число, которое необходимо сохранить. Как только на входе С появляется импульс синхронизации, число записывается в триггер, изменяя их состояние. На рисунке показан трёхразрядный регистр хранения. При подаче на входы числа 1112 оно же появится на прямых выходах триггеров (Q0 — Q2). На инверсных выходах (Q0 — Q2) будет, естественно 0002. Сигналом R (Reset) или сброс, триггеры устанавливаются в нулевое состояние.

Обычно используются регистры, состоящие из 4, 8, или 16 триггеров. Изображение четырёхразрядного регистра на принципиальных схемах может быть таким.

На рисунке не показаны инверсные выхода триггеров и сигнал R. Регистры всегда обозначаются латинскими буквами RG. Если регистр сдвигающий, то под обозначением рисуется стрелка направленная влево, вправо или двойная.

Сдвигающие регистры или регистры сдвига.

Регистр сдвига это устройство, состоящее из нескольких последовательно соединённых триггеров, число которых определяет разрядность регистра. Регистры широко используются в вычислительной технике для преобразования кодов. Параллельного в последовательный и наоборот.

Кроме того сдвигающие регистры являются основой (АЛУ) арифметико-логического устройства, так как при сдвиге записанного в регистр двоичного числа на один разряд влево производится умножение числа на два, а при сдвиге числа на один разряд вправо число делится на два. Поэтому наибольшее распространение получили реверсивные или двунаправленные регистры.

Рассмотрим четырёхразрядный регистр сдвига, преобразующий последовательный двоичный код в параллельный. Применение последовательного кода оправдано тем, что по одной линии можно передавать огромные массивы информации. Таким примером может служить универсальная последовательная шина — USB порт любого устройства. Число триггеров в данном регистре может быть любым. Достаточно соединить прямой выход

Регистр работает следующим образом. Первый информационный бит поступает на вход D0. Одновременно с этим битом приходит тактовый синхроимпульс на вход С. Входы С всех триггеров входящих в регистр, объединены между собой. С приходом первого тактового импульса уровень, находящийся на входе D0 записывается в первый триггер и с выхода Q0 приходит на вход следующего триггера, но записи во второй триггер не происходит, так как синхроимпульс уже закончился.

При поступлении следующего тактового импульса уровень, присутствующий на входе второго триггера запоминается в нём и поступает на вход третьего триггера. Одновременно следующий информационный бит запоминается в первом триггере. После прихода четвёртого тактового импульса в четырёх триггерах регистра будут записаны логические уровни, которые последовательно поступали на вход D0.

Допустим это уровни 01102. Тогда это двоичное число можно отобразить, подключив к выходам триггеров светодиоды. Так рассмотренный регистр изображается на принципиальной схеме.

Видно, что на условном изображении присутствует стрелка — указатель того, что это сдвиговый регистр.

Рассмотрим, как работает четырёх разрядный универсальный регистр сдвига К155ИР1 (аналог — SN7495N). Вот его внутреннее устройство.

Регистр содержит четыре D-триггера, которые соединены между собой с помощью дополнительных логических элементов И – ИЛИ, которые позволяют реализовать различные функции. На схеме:

V2 – вход управления. С его помощью выбирается режим работы регистра.

Q1 – Q4 выходы триггеров с которых снимается параллельный код.

V1 – вход для подачи последовательного кода.

C1, C2 – тактовые синхроимпульсы.

D1 – D4 – входы для записи параллельного кода.

Алгоритм работы регистра следующий. Если на вход V2 подать низкий потенциал, тактовые импульсы на C1, а на вход V1 подавать информационные биты, то регистр осуществляет сдвиг вправо. После приёма четырёх разрядов на выходах триггеров Q1 – Q4 мы получаем параллельный код. Таким образом осуществляется преобразование последовательного кода в параллельный.

Для обратного преобразования параллельный код записывается по входам D1 – D4, с подачей на вход V2 высокого потенциала и тактовых импульсов на вход С2. Затем подавая на вход V2 низкий потенциал, а тактовые импульсы на вход С1 мы сдвигаем записанный код, а с выхода последнего триггера снимается последовательный код.

По своей структуре это один из самых простых регистров сдвига.

Регистры сдвига в цифровой технике могут послужить основой, на которой собираются узлы с интересными свойствами. Это, например, кольцевые счётчики, которые называются счётчики Джонсона. Такой счётчик имеет количество состояний вдвое большее, чем число составляющих его триггеров. Например, если кольцевой счётчик состоит из трёх триггеров, то он будет иметь шесть устойчивых состояний. На вход счётчика ничего не подаётся кроме синхроимпульсов. В первоначальном состоянии все триггеры «сброшены», то есть на прямых выходах триггеров логические нули, а вот на входе D первого триггера с инверсного выхода третьего триггера находится логическая единица. Начнём подавать тактовые импульсы и процесс пошёл.

На таблице истинности хорошо видно, как изменяется двоичный код при поступлении шести тактовых импульсов.

| N | Q2 | Q1 | Q0 |

|---|---|---|---|

| 1 | 0 | 0 | 1 |

| 2 | 0 | 1 | 1 |

| 3 | 1 | 1 | 1 |

| 4 | 1 | 1 | 0 |

| 5 | 1 | 0 | 0 |

| 6 | 0 | 0 | 0 |

Теперь вы знаете, что такое регистр и как он может использоваться на практике. Основа любого регистра — это триггер. Число триггеров в регистре определяет его разрядность. Те, кто увлекается микроконтроллерами знает, что важнейший элемент любого микроконтроллера, будь то PIC, AVR, STM или MSP, это регистр.

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

Универсальный регистр — Большая Энциклопедия Нефти и Газа, статья, страница 3

Универсальный регистр

Cтраница 3

Базовый адрес хранится в одном из универсальных регистров, а исполнительный адрес формируется путем сложения текущего и базового адресов. [31]

Другой способ состоит в передаче параметров через универсальные регистры. [32]

Необходимо отметить, что только стандартные имена универсальных регистров процессора определены в самом Макро, а все другие символы, обозначающие аппаратные регистры и их разряды, должны определяться в тексте программы. [33]

В составе процессоров СМ-ЗП и СМ-4П имеется восемь универсальных регистров, каждый длиной в одно слово — регистры общего назначения, используемые как для размещения обрабатываемой информации, так и для размещения постоянных величин. [34]

Простейшим способом передачи параметров в подпрограмму является использование универсальных регистров. Регистры при этом могут использоваться как для передачи непосредственно данных, так и для передачи их адресов. [35]

На рис. 12 — 11 показан способ организации 16-разрядного универсального регистра. [37]

Если у подпрограммы отсутствуют аргументы или они передаются через универсальные регистры, регистр связи используется только для хранения адреса возврата и в качестве него можно использовать счетчик команд PC. В этом случае ассемблер допускает более наглядные обозначения для команд JSR PC, SUBR и RTS PC: CALL SUBR и RETURN соответственно. [38]

Как вы только что видели, микросхема 74194, представляющая собой 4-разрядный двунаправленный универсальный регистр сдвига, является многофункциональным устройством. [39]

На рис. 3 приведена схема канала связи, в котором предусмотрен универсальный регистр для приема, хранения и поразрядного сдвига информации в магистральную линию. [40]

Если регистры 4-байтовые или 8-байтовые, их имена несколько изменяются, например 4-байтовые универсальные регистры АХ, ВХ, СХ, DX именуются соответственно ЕАХ, ЕВХ, ЕСХ, EDX. При этом если используется их двухбайтовая или однобайтовая часть, наименования этих частей регистров соответствуют рассматриваемым ниже. [41]

Стековая память, развитая система адресации и прерываний, наличие восьми универсальных регистров в центральном процессоре обеспечивает высокое быстродействие при решении различных системных и вычислительных задач. [42]

I — С помощью пульта СМ-1П оператор может вызвать останов выполняемой программы, загрузку инструкций и данных, проверку содержимого ячеек памяти и универсальных регистров, инициировать выполнение любой программы, находящейся в памяти, произвести генерацию начального загрузчика. [43]

При окончании входной последовательности, что фиксируется конъюнктором 11 с появлением во всех разрядах счетчика тактов 3 единиц, сигналы с выходов счетчика единиц 1 и мультиплексора 7 записываются в выходные универсальные регистры 2 и 12 параллельным кодом и становятся доступными для дальнейшего использования. [45]

Страницы: 1 2 3 4

Параллельный, параллельный, универсальный сдвиговый регистр — сдвиговые регистры

Параллельный, параллельный, универсальный регистр сдвига

Глава 12 — Регистры сдвига

Назначение сдвигового регистра параллельного ввода / параллелирования состоит в том, чтобы принимать параллельные данные, сдвигать их, а затем выводить их, как показано ниже. Универсальный сдвиговый регистр является устройством «все-все» в дополнение к функции параллельного ввода / параллельного вывода.

Выше мы применяем четыре бита данных в сдвиговый регистр параллельного входа / параллельного вывода в D A D B D C D D. Управление режимом, которое может быть несколькими входами, управляет параллельной загрузкой и переключением. Управление режимом также может управлять направлением смещения на некоторых реальных устройствах. Данные будут сдвинуты на одну битовую позицию для каждого тактового импульса. Сдвинутые данные доступны на выходах Q A Q B Q C Q D. «Данные в» и «данные» предоставляются для каскадирования нескольких этапов. Хотя, выше, мы можем только каскадировать данные для правого сдвига. Мы могли бы разместить каскадные данные левого сдвига, добавив пару левых указательных сигналов, «данные в» и «данные» выше.

Ниже приводятся внутренние детали сдвигового регистра сдвига вправо / параллельный выход. Буферы с тремя состояниями не являются строго необходимыми для сдвигового регистра параллельного входа / параллельного вывода, но являются частью реального устройства, показанного ниже.

74LS395 так близко соответствует нашей концепции гипотетического сдвигового сдвигового сдвига с параллельным входом / параллельным выводом, в котором мы используем слишком упрощенную версию данных, приведенную выше. Более подробно см. Ссылку на полный лист данных позже в этой главе.

LD / SH ‘ управляет мультиплексором AND-OR при вводе данных в FF. Если LD / SH ‘= 1, верхние четыре логических элемента И позволяют активировать параллельные входы D A D B D C D D для четырех входов данных FF. Обратите внимание на инверторный пузырь на входе часов четырех FF. Это указывает на то, что 74LS395 синхронизирует данные о отрицательных ходах, что является переходом с высокого на низкий. Четыре бита данных будут синхронизироваться параллельно от D A D B D C D D до Q A Q B Q C Q D на следующем отрицательном ходу. В этой «реальной части» OC должен быть низким, если данные должны быть доступны на фактических выходных выводах, а не только на внутренних FF.

Ранее загруженные данные могут быть сдвинуты вправо на одну битовую позицию, если LD / SH ‘= 0 для последующих отрицательных фронтов тактовых импульсов. Четыре такта сместили бы данные полностью из нашего 4-битного регистра сдвига. Данные будут потеряны, если наше устройство не будет каскадировано из Q D ‘ в SER другого устройства.

Выше, структура данных представлена на входы D A D B D C D D. Образец загружается в Q A Q B Q C Q D. Затем он сдвигается на один бит вправо. Входящие данные обозначаются символом X, то есть мы не знаем, что это такое. Если вход ( SER ) был заземлен, например, мы бы знали, какие данные ( 0 ) были сдвинуты. Также показано, что сдвиг справа на две позиции, требующие двух часов.

Вышеприведенный рисунок служит ссылкой на аппаратное обеспечение, связанное с правильным перемещением данных. Это слишком просто, чтобы даже потрудиться с этим рисунком, за исключением сравнения с более сложными цифрами.

Правильное смещение данных приведено выше для ссылки на предыдущий правый переключатель.

Если нам нужно сдвинуть влево, FF необходимо будет переписать. Сравните с предыдущим правым переключателем. Кроме того, SI и SO были отменены. SI переходит в Q C. Q C сдвигается до Q B. Q B переходит в Q A. Q A уходит на SO- соединение, где он может каскадироваться на другой коммутатор SI . Эта последовательность левого сдвига находится в обратном порядке от последовательности правого сдвига.

Выше мы сдвигаем один и тот же шаблон данных, оставшийся на один бит.

Существует одна проблема с изображением «сдвиг влево» выше. Для этого рынка нет. Никто не производит сдвиг-левую часть. «Реальное устройство», которое сдвигается в одном направлении, может быть подключено снаружи, чтобы сдвинуть другое направление. Или, скажем, нет левого или правого в контексте устройства, которое перемещается только в одном направлении. Тем не менее, существует рынок для устройства, которое будет перемещаться влево или вправо по команде с помощью управляющей линии. Конечно, левые и правые действительны в этом контексте.

То, что мы имеем выше, представляет собой гипотетический сдвиговый регистр, способный сдвигать любое направление под контролем L ‘/ R. Устанавливается с L ‘/ R = 1, чтобы сдвинуть нормальное направление, вправо. L ‘/ R = 1 позволяет мультиплексору и вентилям с меткой R. Это позволяет данным следовать по пути, показанному стрелками, когда применяется часы. Путь соединения такой же, как и «слишком простой» «сдвиговый правый» рисунок выше.

Данные сдвигаются в SR, до Q A, до Q B, до Q C, где он выходит на каскаде SR . Этот штифт может управлять SR другого устройства вправо.

Что, если мы изменим L ‘/ R на L’ / R = 0 «//www.beautycrew.com.au//sub.allaboutcircuits.com/images/04420.png»>

Когда L ‘/ R = 0, мультиплексоры AND, помеченные буквой L, активируются, что дает путь, показанный стрелками, так же, как и предыдущая цифра «сдвиг влево». Данные сдвигаются на SL, до Q C, до Q B, до Q A, где он выходит на SL-каскаде . Этот штифт может управлять SL другого устройства слева.

Главным достоинством двух приведенных выше рисунков, иллюстрирующих «регистр сдвига влево / вправо», является простота. Операция левого правого управления L ‘/ R = 0 легко отслеживается. Коммерческая часть требует параллельной загрузки данных, подразумеваемой заголовком раздела. Это показано на рисунке ниже.

Теперь, когда мы можем сдвинуть как левое, так и правое через L ‘/ R, добавим SH / LD’, shift / load и логические элементы AND с надписью «load», чтобы обеспечить параллельную загрузку данных с входов D A D B D C, Когда SH / LD ‘= 0, а блоки R и L отключены, И «нагрузка» активируется для передачи данных D A D B D C на входы данных FF. следующий такт CLK будет синхронизировать данные с Q A Q B Q C. Пока присутствуют одни и те же данные, он будет перезагружен на последующих часах. Однако данные, присутствующие только для одного такта, будут потеряны с выходов, если они больше не присутствуют на входах данных. Одним из решений является загрузка данных на один такт, а затем переход к следующим четырем часам. Эта проблема устранена в 74ALS299 путем добавления другого мультипликатора AND к мультиплексору.

Если SH / LD ‘ изменено на SH / LD’ = 1, то логика AND с надписью «load» отключена, позволяя левому / правому управлению L ‘/ R устанавливать направление сдвига на вентилях L или R AND. Смещение происходит так же, как на предыдущих рисунках.

Единственное, что необходимо для создания жизнеспособного интегрированного устройства, — это добавить четвертый логический элемент AND в мультиплексор, как это указано для 74ALS299. Это показано в следующем разделе этой части.

Давайте подробнее рассмотрим регистраторы с последовательным входом / параллельным выходом, доступные в виде интегральных схем, любезно предоставленные Texas Instruments. Для полных листов данных устройства следуйте ссылкам.

- SN74LS395A параллельный вход / параллельный 4-разрядный регистр сдвига (*)

- SN74ALS299 параллельный вход / параллельный 8-разрядный универсальный сдвиговый регистр (*)

Мы уже рассмотрели внутренние детали SN74LS395A, см. Выше предыдущий рисунок, 74LS395 с параллельным входом и параллельным выводом с трехфазным выходом. Непосредственно выше символ ANSI для 74LS395.

Почему только 4-бит, как указано SRG4 выше «// www.beautycrew.com.au//sub.allaboutcircuits.com/images/04423.png»>

В приведенной выше таблице, сжатой из данных «299», суммируется работа универсального регистра смены / хранения 74ALS299. Следуйте приведенной выше ссылке «299». Ворота мультиплексора R, L работают так же, как и в предыдущих позициях «сдвиг влево / вправо». Разница заключается в том, что входы режима S1 и S0 выбирают сдвиг влево, сдвиг вправо и нагрузку с режимом, установленным на S1 S0 = до 01, 10 и 11 соответственно, как показано в таблице, включение мультиплексорных ворот L, R и нагрузки соответственно, См. Таблицу. Небольшое различие — это путь параллельной нагрузки от выходов трех состояний. На самом деле буферы с тремя состояниями (должны быть) отключены S1 S0 = 11, чтобы плавать шину ввода / вывода для использования в качестве входных данных. Шина представляет собой набор подобных сигналов. Входы применяются к A, B- H (такие же контакты, как Q A, Q B, через Q H ), и направляются на затвор нагрузки в мультиплексорах, а также на входы D FF. Данные представляют собой параллельную нагрузку на тактовый импульс.

Единственным новым затвором мультиплексора является фиксация символа И, помеченная знаком S1 S0 = 00 . Удерживающий затвор позволяет получить путь от выхода Q FF до удерживающего затвора до входа D того же FF. В результате с режимом S1 S0 = 00 выход непрерывно перезагружается с каждым новым тактовым импульсом. Таким образом, данные сохраняются. Это обобщается в таблице.

Для считывания данных с выходов Q A, Q B через Q H буферы с тремя состояниями должны быть активированы с помощью OE2 ‘, OE1’ = 00 и mode = S1 S0 = 00, 01 или 10 . То есть, режим — это что угодно, кроме нагрузки . См. Вторую таблицу.

Данные правого сдвига из пакета влево смещаются на вход SR . Любые данные сдвигались вправо от этапа Q H каскадов вправо через Q H ‘. Этот выход не зависит от буферов трех состояний. Последовательность правого сдвига для S1 S0 = 10:

SR> Q A > Q B > Q C > Q D > Q E > Q F > Q G > Q H (Q H ‘)

Данные левого сдвига из пакета вправо сдвигаются на входе SL . Любые данные, сдвинутые влево от этапа Q A, каскадируются влево через Q A ‘, также не зависящие от буферов трех состояний. Последовательность сдвига влево для S1 S0 = 01:

(Q A ‘) Q A <Q B <Q C <Q D <Q E <Q F <Q G <Q H (Q SL ‘)

Сдвиг может происходить при отключении буферов трех состояний одним из OE2 ‘ или OE1′ = 1 . Хотя, выходы содержимого регистра не будут доступны. См. Таблицу.

«Чистый» символ ANSI для 8-разрядного универсального сдвигового регистра SN74ALS299 с выводом трех состояний показан для справки выше.

Показано, что аннотированная версия символа ANSI разъясняет содержащуюся в нем терминологию. Обратите внимание, что режим ANSI (S0 S1) отменяется из порядка (S1 S0), используемого в предыдущей таблице. Это изменяет номера десятичного режима (1 и 2). В любом случае мы полностью согласны с официальным паспортом, копируя эту несогласованность.

Тревога с блок-схемой удаленной клавиатуры повторяется ниже. Ранее мы построили считыватель клавиатуры и удаленный дисплей в виде отдельных блоков. Теперь мы объединим клавиатуру и дисплей в единое целое с использованием универсального регистра сдвига. Хотя они и разделены на диаграмме, клавиатура и дисплей находятся в одном и том же удаленном корпусе.

Мы будем параллельно загружать данные клавиатуры в регистр сдвига на один тактовый импульс, а затем переставляем его в основной блок. В то же время мы будем переводить светодиодные данные из основного аварийного сигнала в удаленный сдвиговый регистр, чтобы освещать светодиоды. Мы будем одновременно перемещать данные клавиатуры и светодиодные данные в регистр сдвига.

Восемь светодиодов и токоограничивающие резисторы подключены к восьми выводам ввода / вывода универсального сдвигового регистра 74ALS299. Светодиоды могут управляться только в режиме 3 с S1 = 0 S0 = 0 . Разрешения tristate OE1 и OE2 основаны на постоянном включении выходов тристата во время режимов 0, 1, 2 . Это приведет к тому, что светодиоды будут гореть (мерцать) во время переключения. Если бы это было проблемой, EN1 и EN2 могли быть необоснованными и параллельно с S1 и S0 соответственно включать только тристатные буферы и загорать светодиоды во время удержания, режим 3 . Давайте сделаем это простым для этого примера.

При параллельной загрузке S0 = 1 инвертируется на 0, позволяет восьмеричным тристатным буферам заземлять переключатели стеклоочистителей. Верхние, разомкнутые контакты переключателя поднимаются до логического уровня с помощью комбинации резисторов-светодиодов на восьми входах. Любое замыкание переключателя будет кратковременным. Параллельно загружаем данные переключателя в «299» в такт t0, когда S0 и S1 высоки. См. Формы сигналов ниже.

После того, как S0 опустится, восемь часов (от t0 до t8 ) сбрасывают данные закрытия переключателя из «299 через штырь Q h » . В то же время новые светодиодные данные сдвигаются на SR 299 теми же восемью часами. Светодиодные данные заменяют данные о закрытии переключателя в процессе переноса.

После 8-го такта переключения t8 S1 выходит на низкую, чтобы получить режим удержания ( S1 S0 = 00 ). Данные в сдвиговом регистре остаются неизменными, даже если есть больше часов, например, T9, t10 и т. Д. Где сигналы формируются из «скрытого-пейджера»>

← Предыдущая страница

Индекс учебников

Следующая страница →

Регистр универсальный Теплодар 7 л d115 G3/4, цена

Описание регистра универсального Теплодар 7 л d115 G3/4:

Регистр универсальный Теплодар 7 л d115 G3/4 предназначен для нагрева воды в выносном баке посредством горячих дымовых газов.

Производитель оставляет за собой право изменять страну производства, характеристики товара, его внешний вид и комплектность без предварительного уведомления продавца. Уточняйте информацию у менеджеров!

1. Способы доставки

| до 100 кг | до 300 кг | до 500 кг** | Постаматы и ПВЗ PickPoint | |

| Москва | 390 руб | 500 руб | 900 руб | 200 руб |

| МО, область | 390 руб* | 500 руб* | 900 руб* | 200 руб |

| Регионы, РФ | 450 руб | |||

| Самовывоз |

Выдача товара до 20:00, Раменский район, Михайловская слобода, Старорязанская улица, д.4. (при оплате — резерв товара) Пункт выдачи по адресу: Москва, Рязанский проспект, д.79 (пн-вс с 09:00 до 20:00) |

|||

* каждый 1 км за МКАД дополнительно 30 руб

** полная информация по доставке крупногабаритных грузов смотрите в разделе Доставка и оплата

2. Способы оплаты

Банковской картой онлайн на сайте ЮMoney (Я.Деньги)

Наличными курьеру QIWI кошелек

Сбербанк-онлайн WebMoney

Безналичный расчет

Вы можете вернуть товар, если был обнаружен производственный брак, дефекты и прочие повреждения. Срок возврата осуществляется в течение 14 дней с даты покупки товара.

Возврат товара осуществляется в полном соответствии с законодательством РФ, включая Закон о Правах Потребителя.

Подробная информация о возратах и обмене

Cк — тактирование Cl — асинхронный сброс S0 — управление режимами S1 — управление режимами последовательные входы Rx — для сдвига вправо Lx — для сдвига влево Регистр может осуществлять функции

параллельной загрузки, сдвига вправо (от Qa к Qd) и сдвига влево (от Qd

к Qa) и хранения.

| ||||||||

| Параметры для 1564 | E=2 В | E=4.5 В | E=6 В |

| Выходной ток логического 0, мА | -0.02 | -4 | -5.2 |

| Выходной ток логической 1, мА | -0.02 | -4 | -5.2 |

| Входное напряжение логического 0, В | -0.5 | -1.4 | -1.8 |

| Входное напряжение логической 1, В | 1.5- | 3.2- | 4.2- |

| Выходное напряжение логического

0, В при токе 0.02 мА при токе 4 мА при токе 5.2 мА |

— -0.1 — — |

— — -0.4 — |

— — — -0.4 |

| Выходное напряжение логической

1, В при токе 0.02 мА при токе 4 мА при токе 5.2 мА |

— 1.9- — — |

— — 3.7- — |

— — — 5.2- |

| 1564- Задержки (T=+25/T=Tmax) | E=+2 | E=+4.5 | E=+6 |

| От Ck до Qi | -67-145/-220 | -17-29/-44 | -14-25/-37 |

| От Cl до Qi | -67-150/-225 | -17-30/-45 | -14-26/-37 |

| Длительность импульса Ck | 80-/120- | 16-/24- | 14-/20- |

| Длительность импульса Cl=L | 80-/120- | 16-/24- | 14-/20- |

| Время предустановки данных | 100-/150- | 20-/30- | 17-/26- |

| Время удержания данных | 0-/0- | 0-/0- | 0-/0- |

| Максимальная частота, МГц | 6-/4.2- | 31-/21- | 36-/25- |

Универсальный регистр сдвига в цифровой логике

Универсальный регистр сдвига — это регистр, который имеет как правый сдвиг, так и левый сдвиг с возможностью параллельной загрузки. Универсальные регистры сдвига используются в качестве элементов памяти в компьютерах. Однонаправленный сдвиговый регистр может выполнять сдвиг только в одном направлении. Двунаправленный сдвиговый регистр может выполнять сдвиг в обоих направлениях. Универсальный сдвиговый регистр представляет собой комбинацию двунаправленного сдвигового регистра и однонаправленного сдвигового регистра с возможностью параллельной загрузки.

Универсальный n-разрядный регистр сдвига —

Универсальный n-разрядный регистр сдвига состоит из n триггеров и n мультиплексоров 4 × 1. Все n мультиплексоров используют одни и те же линии выбора (S1 и S0) для выбора режима, в котором работает сдвиговый регистр. Выбор входов выбирает подходящий вход для триггеров.

Вниманию читателя! Не прекращайте учиться сейчас. Получите все важные концепции теории CS для собеседований SDE с помощью курса CS Theory Course по приемлемой для студентов цене и станьте готовым к работе в отрасли.

Основные соединения —

- Первый вход (нулевой вывод мультиплексора) подключен к выходному выводу соответствующего триггера.

- Второй вход (первый вывод мультиплексора) подключен к выходу самого предыдущего триггера, что облегчает сдвиг вправо.

- Третий вход (второй вывод мультиплексора) подключен к выходу ближайшего триггера, что облегчает сдвиг влево.

- Четвертый вход (третий вывод мультиплексора) подключен к отдельным битам входных данных, что облегчает параллельную загрузку.

Работа универсального регистра сдвига зависит от входов, заданных для выбранных строк.

Операции регистрации, выполняемые для различных входов строк выбора, следующие:

| S1 | s0 | Операция регистра |

|---|---|---|

| 0 | 0 | Без изменений |

| 0 | 1 | Сдвиг вправо |

| 1 | 0 | Сдвиг влево |

| 1 | 1 | Параллельная нагрузка |

Артикул:

Digital Electronics — Atul P.Годсе, г-жа Дипали А. Годсе

Универсальные регистры сдвига: параллельный вход, параллельный выход | Регистры сдвига

Назначение регистра сдвига с параллельным входом / параллельным выходом — принимать параллельные данные, сдвигать их и затем выводить, как показано ниже.

Универсальный регистр сдвига — это универсальное устройство в дополнение к функции параллельного ввода / вывода.

Выше мы применяем четыре бита данных к регистру сдвига с параллельным входом / параллельным выходом по адресу D A D B D C D D .Управление режимом, которым может быть несколько входов, контролирует параллельную загрузку и смещение.

Управление режимом может также управлять направлением сдвига в некоторых реальных устройствах. Данные будут сдвинуты на одну битовую позицию для каждого тактового импульса.

Сдвинутые данные доступны на выходах Q A Q B Q C Q D . Входящие и исходящие данные предназначены для каскадирования нескольких этапов.

Хотя, выше, мы можем только каскадировать данные для сдвига вправо.Мы могли бы приспособить каскадирование данных сдвига влево, добавив пару сигналов, указывающих влево, «данные на входе» и «данные на выходе», как указано выше.

Внутренние детали сдвигового регистра с параллельным входом и выходом правого сдвига показаны ниже.

Буферы с тремя состояниями не являются строго обязательными для сдвигового регистра параллельного ввода / параллельного вывода, но являются частью реального устройства, показанного ниже.

74LS395 настолько близко соответствует нашей концепции гипотетического сдвигового регистра сдвига вправо с параллельным входом / параллельным выходом, что мы используем чрезмерно упрощенную версию данных, приведенных выше.

Подробнее см. Ссылку на полный лист технических данных далее в этой главе.

LD / SH ’ управляет мультиплексором И-ИЛИ на входе данных в FF. Если LD / SH ’= 1 , активированы четыре верхних логических элемента AND, что позволяет применять параллельные входы D A D B D C D D к четырем входам данных FF.

Обратите внимание на пузырек инвертора на тактовом входе четырех FF. Это указывает на то, что 74LS395 синхронизирует данные по отрицательной тактовой частоте, которая является переходом от высокого уровня к низкому.

Четыре бита данных будут синхронизироваться параллельно от D A D B D C D D до Q A Q B Q C Q D при следующие отрицательные часы. В этой «реальной части» OC ’ должно быть низким, если данные должны быть доступны на фактических выходных контактах, а не только на внутренних FF.

Ранее загруженные данные могут быть сдвинуты вправо на одну битовую позицию, если LD / SH ’= 0 для последующих отрицательных фронтов тактовой частоты.

Четыре такта полностью сдвигают данные из нашего 4-битного регистра сдвига. Данные будут потеряны, если наше устройство не будет подключено каскадом от Q D ’ к SER другого устройства.

Выше образец данных представлен входам D A D B D C D D . Шаблон загружается в Q A Q B Q C Q D .Затем он сдвигается на один бит вправо.

Входящие данные обозначаются как X , что означает, что мы не знаем, что это такое. Если бы вход ( SER ) был заземлен, например, мы бы знали, какие данные ( 0 ) были сдвинуты.

Также показан сдвиг вправо на две позиции, требующий двух часов.

Приведенный выше рисунок служит ссылкой для оборудования, задействованного в сдвиге данных вправо.

С этой цифрой слишком просто возиться, если не считать сравнения с более сложными цифрами.

Правый сдвиг данных приведен выше для ссылки на предыдущий правый сдвиг.

Если нам нужно сдвинуть влево, FF должны быть перемонтированы. Сравните с предыдущим правым переключателем. Также были поменяны местами SI и SO . SI переходит на Q C . Q C переходит на Q B . Q B переходит на Q A . Q A выходит на соединение SO , где он может каскадно подключаться к другому переключателю SI . Эта последовательность сдвига влево является обратной от последовательности сдвига вправо.

Выше мы сдвигаем тот же образец данных влево на один бит.

Есть одна проблема с цифрой «сдвиг влево» выше. Для этого нет рынка. Деталь с левым переключателем никто не производит.

«Настоящее устройство», которое смещает одно направление, может быть подключено снаружи для смещения другого направления.Или, если мы скажем, что нет левого или правого в контексте устройства, которое сдвигается только в одном направлении.

Однако есть рынок устройств, которые могут переключаться влево или вправо по команде с помощью линии управления. Конечно, в этом контексте допустимы «лево» и «право».

То, что мы имеем выше, является гипотетическим регистром сдвига, способным сдвигать в любом направлении под управлением L ’/ R .

Для смещения нормального направления вправо установлено значение L ’/ R = 1 . L ’/ R = 1 включает логические элементы И мультиплексора с меткой R .

Это позволяет данным следовать по пути, показанному стрелками, когда применяются часы. Путь подключения такой же, как на приведенном выше рисунке «слишком простой» «сдвиг вправо».

Данные смещаются на SR , на Q A , на Q B , на Q C , откуда они уходят на SR каскад . Этот вывод может переместить SR другого устройства вправо.

Что если мы изменим L ’/ R на L’ / R = 0 ?

При L ’/ R = 0 , включены логические элементы И мультиплексора, обозначенные L , что дает путь, показанный стрелками, такой же, как на приведенном выше рисунке со сдвигом влево.

Данные смещаются на SL , на Q C , на Q B , на Q A , откуда они уходят на SL каскад .Этот вывод может переместить SL другого устройства влево.

Главное достоинство двух приведенных выше рисунков, иллюстрирующих «регистр сдвига влево / вправо», — это простота.

За работой левого и правого регулятора L ’/ R = 0 легко проследить. Коммерческая часть требует параллельной загрузки данных, подразумеваемой заголовком раздела. Это показано на рисунке ниже.

Теперь, когда мы можем сдвигать как влево, так и вправо через L ‘/ R , давайте добавим SH / LD’ , сдвиг / нагрузка и логические элементы И, помеченные как «загрузка», чтобы обеспечить параллельную загрузку данных со входов D A D B D C .

Когда SH / LD ‘= 0 , И вентили R и L отключены, И вентили «загрузка» разрешены для передачи данных D A D B D C в FF ввод данных. следующие часы CLK синхронизируют данные с Q A Q B Q C .

Пока присутствуют одни и те же данные, они будут повторно загружаться на следующих часах. Однако данные, представленные только для одного тактового сигнала, будут потеряны с выходов, когда они больше не будут присутствовать на входах данных.

Одно из решений — загрузить данные на одном такте, а затем перейти к переходу на следующие четыре такта. Эта проблема устранена в 74ALS299 путем добавления еще одного логического элемента И к мультиплексору.

Если SH / LD ‘ изменяется на SH / LD’ = 1 , вентили И, помеченные как «нагрузка», отключаются, позволяя левому / правому регулятору L ‘/ R устанавливать направление сдвига на L или R И ворота. Сдвиг такой же, как на предыдущих рисунках.

Единственное, что необходимо для создания жизнеспособного интегрированного устройства, — это добавить четвертый логический элемент И к мультиплексору, как упоминалось для 74ALS299.

Это показано в следующем разделе для этой части.

Устройства параллельного ввода / вывода и универсальные

Давайте подробнее рассмотрим регистры сдвига с последовательным входом / параллельным выходом, доступные в виде интегральных схем, любезно предоставленные Texas Instruments.

Чтобы просмотреть полные спецификации устройства, перейдите по ссылкам.

Мы уже рассмотрели внутренние детали SN74LS395A, см. Предыдущий рисунок выше, регистр сдвига 74LS395 с параллельным входом / параллельным выходом и выходом с тремя состояниями.

Непосредственно выше находится символ ANSI для 74LS395.

Почему только 4 бита, как указано выше в SRG4 ? Наличие как параллельных входов, так и параллельных выходов, в дополнение к выводам управления и питания, не позволяет использовать больше битов ввода / вывода (ввод / вывод) в 16-контактном DIP (Dual Inline Package).

R указывает, что каскады регистра сдвига сбрасываются входом CLR ’ (активная нижняя инвертирующая половина стрелки на входе) секции управления в верхней части символа. OC ’, при низком уровне (снова переверните стрелку) включит ( EN4 ) четыре выходных буфера с тремя состояниями ( Q A Q B Q C Q D ) в разделе данных.

Load / shift ’( LD / SH’ ) на штифте (7) соответствует внутренним компонентам M1 (нагрузка) и M2 (сдвиг). Ищите префиксы 1 и 2 в остальной части символа, чтобы выяснить, что ими управляется.

Часы, чувствительные к отрицательному фронту (обозначены перевернутой стрелкой на выводе 10) C3 / 2 выполняет две функции.

Во-первых, 3 из C3 / 2 влияет на любой ввод с префиксом 3 , скажем, 2,3D или 1,3D в разделе данных.

Это будет параллельная нагрузка на A, B, C, D , относящаяся к M1 и C3 для 1,3D . Во-вторых, 2 из C3 / 2 — стрелка вправо указывает на синхронизацию данных везде, где 2 появляется в префиксе ( 2,3D на контакте 2).

Таким образом, мы имеем синхронизацию данных на SER в Q A с режимом 2 .Стрелка вправо после C3 / 2 учитывает сдвиг на ступенях внутреннего регистра сдвига Q A Q B Q C Q D .

Правые указывающие треугольники указывают на буферизацию; перевернутый треугольник указывает на три состояния, контролируемые EN4 .

Обратите внимание, что все 4 в символе, связанном с EN , часто опускаются. Считается, что этапы Q B Q C имеют те же атрибуты, что и Q D . Q D ’ каскадно переходят к SER следующего пакета справа.

В приведенной выше таблице, взятой из таблицы данных «299», резюмируется работа универсального регистра сдвига / хранения 74ALS299.

Чтобы получить полную информацию, перейдите по ссылке «299» выше. Логические элементы мультиплексора R , L , load работают как на предыдущих рисунках «сдвиг влево / вправо регистр».

Разница в том, что входы режима S1 и S0 выбирают сдвиг влево, сдвиг вправо и загрузку с режимом, установленным на S1 S0 = от до 01 , 10 и 11 соответственно, как показано на таблица, включающая шлюзы мультиплексора L , R и загружают соответственно.

См. Таблицу. Незначительное отличие — это параллельный путь нагрузки от выходов с тремя состояниями. Фактически буферы с тремя состояниями отключены (должны быть) отключены с помощью S1 S0 = 11 , чтобы освободить шину ввода / вывода для использования в качестве входов.

Шина — это набор похожих сигналов. Входы применяются к A , B — H (те же контакты, что и Q A , Q B , через Q H ) и направляются к шлюзу нагрузки . в мультиплексорах и на входах D FF.Данные — это параллельная нагрузка на тактовый импульс.

Один новый вентиль мультиплексора — логический элемент И, помеченный как , удержание , разрешено S1 S0 = 00 . Створ удержания обеспечивает путь от выхода Q FF обратно к затвору удержания к входу D того же FF. В результате в режиме S1 S0 = 00 выход постоянно перезагружается с каждым новым тактовым импульсом. Таким образом, данные сохранены. Это кратко изложено в таблице.

Для чтения данных с выходов Q A , Q B , по Q H , буферы с тремя состояниями должны быть включены с помощью OE2 ‘, OE1’ = 00 и mode = S1 S0 = 00, 01 или 10 .

То есть режим любой, кроме , загрузка . См. Вторую таблицу.

Сдвиг вправо данных из пакета влево, сдвиг на входе SR . Любые данные, сдвинутые вправо от каскада каскада Q H вправо через Q H ’.

Буферы с тремя состояниями не влияют на этот вывод. Последовательность сдвига вправо для S1 S0 = 10 :

SR> Q A > Q B > Q C > Q D > Q E > Q F > Q G > Q H (Q H ’)

Данные сдвига влево из пакета вправо сдвигаются на входе SL .Любые данные, сдвинутые влево от этапа Q A , каскадируются влево через Q A ’, также на них не влияют буферы с тремя состояниями. Последовательность сдвига влево для S1 S0 = 01 :

(Q A ‘) Q A B

C

D

E

F

G

H (Q SL ‘)

Сдвиг может происходить с буферами с тремя состояниями, отключенными одним из OE2 ’ или OE1’ = 1 .Однако выходы содержимого регистров будут недоступны. См. Таблицу.

«Чистый» символ ANSI для 8-битного универсального сдвигового регистра SN74ALS299 с параллельным входом / параллельным выходом и выходом с тремя состояниями показан для справки выше.

Аннотированная версия символа ANSI показана для пояснения содержащейся в нем терминологии.

Обратите внимание, что режим ANSI (S0 S1) отличается от порядка (S1 S0), использованного в предыдущей таблице.

Это меняет местами десятичные числа режима (1 и 2). В любом случае мы полностью согласны с официальной таблицей данных, копируя это несоответствие.

Практическое применение

Блок-схема сигнализации с удаленной клавиатурой повторяется ниже. Раньше считыватель клавиатуры и выносной дисплей мы строили как отдельные блоки.

Теперь объединим клавиатуру и дисплей в единый блок, используя универсальный регистр сдвига.

Клавиатура и дисплей разделены на схеме, но находятся в одном удаленном корпусе.

Мы будем параллельно загружать данные клавиатуры в регистр сдвига по одному тактовому импульсу, а затем перемещать их в основной блок аварийной сигнализации.

В то же время мы переместим данные светодиодов из основного аварийного сигнала в удаленный регистр сдвига, чтобы светодиоды загорелись.

Мы будем одновременно переносить данные клавиатуры и данные светодиодов в регистр сдвига.

Восемь светодиодов и токоограничивающие резисторы подключены к восьми контактам ввода-вывода универсального сдвигового регистра 74ALS299.

Светодиоды могут работать только в режиме 3 с S1 = 0 S0 = 0 . Включение трех состояний OE1 ’ и OE2’ заземлено для постоянного включения трехсторонних выходов в режимах 0, 1, 2 .

Это приведет к тому, что светодиоды загорятся (мерцают) во время переключения. Если бы это было проблемой, то EN1 ’и EN2’ можно было бы отключить и подключить параллельно к S1 и S0 соответственно, чтобы активировать только трехсторонние буферы и загорать светодиоды во время удержания, режим 3 .Давайте рассмотрим этот пример проще.

Во время параллельной нагрузки S0 = 1 , инвертированное в 0, позволяет восьмицилиндровым буферам с тремя состояниями заземлять дворники переключателя.

Верхние разомкнутые контакты переключателя подтягиваются до высокого логического уровня комбинацией резистора и светодиода на восьми входах.

Любое замыкание переключателя закоротит входной низкий уровень. Мы параллельно загружаем данные коммутатора в ‘299 на часах t0 , когда оба S0 и S1 имеют высокий уровень.См. Кривые ниже.

Когда S0 переходит в низкий уровень, восемь тактов (от t0 до t8 ) переключают данные о замыкании переключателя из ‘299 через вывод Q h ’ .

В то же время новые данные светодиода сдвигаются в SR из 299 на те же восемь тактов. Данные светодиода заменяют данные о замыкании переключателя в процессе переключения.

После тактовой частоты 8-й смены t8 , S1 переходит в низкий уровень в режим удержания выхода ( S1 S0 = 00 ).Данные в регистре сдвига остаются прежними, даже если тактов больше, например, T9 , t10 и т. Д.

Откуда берутся осциллограммы? Они могли бы быть сгенерированы микропроцессором, если бы тактовая частота не превышала 100 кГц, и в этом случае было бы неудобно генерировать какие-либо тактовые импульсы после t8 .

Если бы часы находились в мегагерцовом диапазоне, они бы работали непрерывно. Часы S1 и S0 будут генерироваться цифровой логикой, не показанной здесь.

СВЯЗАННЫЕ РАБОЧИЕ ЛИСТЫ:

Дизайн, работа и применение

В цифровой электронике регистры сдвига — это последовательные логические схемы, которые могут временно хранить данные и обеспечивать передачу данных к своему выходному устройству для каждого тактового импульса. Они могут передавать / сдвигать данные вправо или влево в последовательном и параллельном режимах. В зависимости от режима операций ввода / вывода, регистры сдвига могут использоваться как регистр сдвига с последовательным вводом и параллельным выводом, регистр сдвига с последовательным вводом и выводом, регистр сдвига с параллельным выводом, параллельный ввод -параллельный сдвиговый регистр.На основе сдвига данных существуют универсальные регистры сдвига и регистры двунаправленного сдвига. Вот полное описание универсального регистра сдвига.

Что такое универсальный регистр сдвига?

Определение: Регистр, который может хранить данные и / сдвигать данные вправо и влево вместе с возможностью параллельной загрузки, известен как универсальный регистр сдвига. Его можно использовать для выполнения операций ввода / вывода как в последовательном, так и в параллельном режимах.Однонаправленные регистры сдвига и двунаправленные регистры сдвига объединяются вместе, чтобы получить структуру универсального регистра сдвига. Он также известен как сдвиговый регистр с параллельным выходом или сдвиговый регистр с параллельной загрузкой.

Универсальные регистры сдвига могут выполнять 3 операции, перечисленные ниже.

- Параллельная загрузка — хранит данные параллельно, а также данные параллельно

- Сдвиг влево — сохраняет данные и передает данные со смещением влево по последовательному пути

- Сдвиг вправо — сохраняет данные и передает данные путем смещения вправо в последовательном пути.

Следовательно, универсальные регистры сдвига могут выполнять операции ввода / вывода как с последовательной, так и с параллельной нагрузкой.

Схема универсального регистра сдвига

Схема4-битного универсального регистра сдвига показана ниже.

Схема универсального регистра сдвига- Последовательный вход для управления сдвигом вправо позволяет передавать данные вправо, и все линии последовательного ввода и вывода подключены к режиму сдвига вправо. Вход подается на логический элемент И-1 триггера -1, как показано на рисунке, через последовательный входной контакт.

- Последовательный ввод для сдвига влево позволяет передавать данные влево, а все линии последовательного ввода и вывода подключаются к режиму сдвига влево.

- При параллельной передаче данных все параллельные входные и выходные линии связаны с параллельной нагрузкой.

- Штифт очистки очищает регистр и устанавливается на 0. Вывод

- CLK обеспечивает тактовые импульсы для синхронизации всех операций.

- В состоянии управления информация или данные в регистре не изменяются даже при подаче тактового импульса.

- Если регистр работает с параллельной загрузкой и сдвигает данные вправо и влево, то он действует как универсальный сдвиговый регистр.

Конструкция универсального регистра сдвига

Схема 4-битного универсального регистра сдвига с использованием мультиплексоров и триггеров показана ниже.

Конструкция универсального сдвигового регистра- S0 и S1 — это выбранные выводы, которые используются для выбора режима работы этого регистра. Это может быть операция сдвига влево или вправо, или параллельный режим.

- Вывод 0 первого мультиплексора 4 × 1 подается на выходной вывод первого триггера. Обратите внимание на соединения, как показано на рисунке.

- Контакт-1 первого мультиплексора 4X1 подключен к последовательному входу для сдвига вправо. В этом режиме регистр сдвигает данные вправо.

- Точно так же контакт 2 мультиплексора 4X1 подключен к последовательному входу для сдвига влево. В этом режиме универсальный регистр сдвига сдвигает данные влево.

- M1 — это данные параллельного ввода, подаваемые на контакт 3 первого мультиплексора 4 × 1 для обеспечения работы в параллельном режиме и сохранения данных в регистре.

- Аналогичным образом, оставшиеся отдельные биты данных параллельного ввода передаются на контакт 3 соответствующего 4X1MUX для обеспечения параллельной загрузки.

- F1, F2, F3 и F4 — это параллельные выходы триггеров, которые связаны с мультиплексором 4 × 1.

Универсальный регистр сдвига рабочий

- Из вышеприведенного рисунка выбраны выводы режима работы универсального регистра сдвига. Последовательный ввод сдвигает данные вправо и влево и сохраняет данные в регистре.

- Чистый штырь и штырь CLK подключены к триггеру.

- M0, M1, M2, M3 — параллельные входы, а F0, F1, F2, F3 — параллельные выходы триггеров

- Когда входной вывод активен HIGH, универсальный регистр сдвига загружает / извлекает данные параллельно. В этом случае входной контакт напрямую подключен к 4 × 1 MUX .

- Когда входной вывод (режим) активен LOW, то универсальный регистр сдвига сдвигает данные. В этом случае входной вывод подключается к мультиплексору 4 × 1 через вентиль НЕ.

- Когда входной вывод (режим) подключен к GND (земле), то универсальный регистр сдвига действует как двунаправленный регистр сдвига.

- Чтобы выполнить операцию сдвига вправо, входной вывод подается на 1-й вентиль И 1-го триггера через последовательный вход для «дерьмо-вправо».

- Для выполнения операции сдвига влево входной вывод подается на 8-й логический элемент И последнего триггера через вход M.

- Если выбранные выводы S0 = 0 и S1 = 0, то этот регистр не работает ни в каком режиме.Это означает, что он будет в заблокированном состоянии или в состоянии без изменений, даже если тактовые импульсы применяются.

- Если выбранные выводы S0 = 0 и S1 = 1, то этот регистр передает или сдвигает данные влево и сохраняет данные.

- Если выбранные выводы S0 = 1 и S1 = 0, то этот регистр сдвигает данные вправо и, следовательно, выполняет операцию сдвига вправо.

- Если выбранные выводы S0 = 1 и S1 = 1, то этот регистр загружает данные параллельно. Следовательно, он выполняет операцию параллельной загрузки и сохраняет данные.

|

S0 |

S1 |

Режим работы |

|

0 |

0 | Состояние блокировки (без изменений) |

|

0 |

1 | Shift-влево |

| 1 | 0 |

Shift-вправо |

| 1 | 1 |

Параллельная загрузка |

Из приведенной выше таблицы мы можем заметить, что этот регистр работает во всех режимах с последовательными / параллельными входами с использованием мультиплексоров 4 × 1 и триггеров.

Преимущества

К преимуществам универсального сдвигового регистра относятся следующие.

- Этот регистр может выполнять 3 операции, такие как сдвиг влево, сдвиг вправо и параллельная загрузка.

- Временно хранит данные в регистре.

- Он может выполнять последовательно-параллельные, параллельные с последовательными, параллельные с параллельными и последовательно-последовательные операции.

- Он может выполнять операции ввода-вывода как в последовательном, так и в параллельном режимах.

- Комбинация однонаправленного сдвигового регистра и двунаправленного сдвигового регистра дает универсальный сдвиговый регистр.

- Этот регистр действует как интерфейс между одним устройством и другим устройством для передачи данных.

Приложения

Применение универсального сдвигового регистра включает следующее.

- Используется в микроконтроллерах для расширения ввода / вывода

- Используется как преобразователь последовательного интерфейса в последовательный

- Используется как параллельный преобразователь данных

- Используется как преобразователь последовательно-параллельных данных.

- Используется для последовательной передачи данных

- Используется при параллельной передаче данных.

- Используется как элемент памяти в цифровой электронике, например, в компьютерах.

- Используется в приложениях с выдержкой времени

- Используется как счетчики частоты, двоичные счетчики и цифровые часы

- Используется в приложениях для обработки данных.

Итак, это все об универсальном регистре сдвига — определение, схема, конструкция, работа, преимущества и недостатки.Существуют различные типы 4-битных регистров, доступные в виде IC 74291, IC 74395 и многих других. Вот вам вопрос: «Как работает двунаправленный универсальный сдвиговый регистр?»

Универсальная регистрация избирателей — FairVote

- Ресурсы

- Библиотека реформ

- Универсальная регистрация избирателей

Универсальная регистрация избирателей модернизирует регистрацию избирателей в Соединенных Штатах.Правительство будет нести ответственность за поддержание точных и полных списков избирателей, переведя нашу систему с ее нынешней структуры согласия на структуру отказа. Автоматическая универсальная регистрация избирателей значительно уменьшит дублирование и пропуски в списках избирателей, что приведет к созданию системы, уравновешивающей две цели: доступность выборов и безопасность.

FairVote гордится тем, что является давним сторонником всеобщей регистрации избирателей и первой общенациональной избирательной организацией, которая изначально поддержала реформу.Другие продемократические организации взяли на себя роль всеобъемлющего законодательства о регистрации избирателей, и FairVote больше не играет активной роли в продвижении этого вопроса. Тем не менее, мы с гордостью поддерживаем набор полезных ресурсов для тех, кто хочет узнать больше и продвигать всеобщую регистрацию избирателей в штатах по всей стране.

Зачем нужна всеобщая регистрация избирателей

Полные и точные списки избирателей необходимы для честности избирательного процесса и легитимности результатов.Тем не менее, как свидетельствуют недавние выборы, списки избирателей завалены повторяющимися регистраторами и ошибками. Около трети имеющих право голоса американских избирателей не зарегистрированы для голосования, и кампании по регистрации избирателей приводят к всплеску регистраций, близких к выборам, которые трудно поддаются обработке и которые создают непредвиденный спрос на избирательные участки. В результате миллионы избирателей, имеющих право голоса, фактически исключены из политического процесса.

Хотя ни один процесс регистрации избирателей не идеален, наш процесс полон недостатков.Соединенные Штаты — одна из немногих демократических стран в мире, где правительство не берет на себя ответственность за регистрацию избирателей. Вместо этого наше правительство предоставляет создание списков избирателей партийным и беспристрастным организациям по регистрации избирателей, политическим партиям, сотрудникам избирательных комиссий и активным гражданам. К сожалению, такой подход подразумевает мошенничество при регистрации избирателей. Неудивительно, что списки избирателей не являются ни полными, ни точными.

Напротив, международная норма — это упорядоченный процесс автоматической регистрации каждого гражданина, достигшего избирательного возраста, и каждого человека, который становится гражданином.Граждане автоматически включаются в списки избирателей по достижении избирательного возраста и / или государственные чиновники активно работают над регистрацией всех граждан. Например, на первых демократических выборах в Ираке должностные лица, ответственные за выборы, автоматически перенесли имена иракцев из продовольственных списков в списки избирателей.

Регистрация избирателей должна быть взаимной ответственностью граждан и их правительства. Правительство должно не только способствовать регистрации; он должен активно регистрировать взрослых, имеющих право голоса, в рамках своей обязанности по составлению точных списков.Целью должна быть 100% регистрация избирателей. Более того, всеобщая регистрация избирателей может объединить консерваторов, обеспокоенных мошенничеством при регистрации избирателей, и либералов, обеспокоенных анемичным участием в политической жизни.

Самый полный способ перейти к всеобщей регистрации избирателей — это установить федеральные стандарты, которым штаты должны следовать, чтобы гарантировать, что все правомочные избиратели включены в списки избирателей своего штата. Эти стандарты также должны быть связаны с отказоустойчивостью, чтобы граждане, не внесенные в списки, могли зарегистрироваться и проголосовать в день выборов.Федеральные стандарты должны также установить единый национальный возраст регистрации избирателей — 16 лет, при котором молодежь систематически регистрируется для голосования и автоматически добавляется в списки избирателей по достижении избирательного возраста.

Даже до того, как у нас появится национальный стандарт, государства могут принять немедленные меры. В таких штатах, как Флорида и Гавайи, уже установлен единый возраст для регистрации избирателей — 16 лет. Орегон принял первый в своем роде закон об автоматической регистрации избирателей в 2015 году, гарантирующий, что любой имеющий право житель штата Орегон с водительскими правами будет автоматически зарегистрирован для голосования и получит бюллетень по почте за несколько недель до дня выборов.Несколько штатов также работают над политикой автоматической регистрации избирателей, при которой граждане, подающие государственные налоговые декларации, систематически регистрируются для голосования. Штаты также могут привязать формы изменения адреса почтового отделения к базе данных регистрации избирателей и использовать существующие государственные базы данных для перехода к системе всеобщей регистрации избирателей.

Какими бы лучшими ни были результаты, мы считаем, что такие изменения позволят зарегистрировать гораздо больше граждан упорядоченным образом, будут способствовать большему пониманию ценности 100% регистрации и предоставят средства для систематического ознакомления молодых людей с важностью политического участия.Мы видим естественное дополнение к этому предложению — «программу голосования» для старшеклассников.

Ресурсы

Руководство по политике FairVote: универсальная регистрация избирателей

Канадская модель

Massachusetts Health Care Model

Международная перспектива

Центр правосудия Бреннана по модернизации регистрации избирателей

Руководство по регистрации избирателей

В этой таблице представлены крайние сроки регистрации избирателей по штатам.Информация предоставляется в последний возможный день для регистрации в каждом штате, а также различные крайние сроки для личной, почтовой, онлайн-регистрации или регистрации третьей стороной в каждом штате по мере необходимости. infogram_0_voter_registration_deadlines Сроки регистрации избирателя // e.infogr.am / js / embed.js? QyWtext / javascript

infogram_0_voter_registration_deadlines_table Таблица сроков регистрации избирателей // e.infogr.am / js / embed.js? UsQtext / javascript

Последнее обновление: январь 2016 г.

Шаг 1: Получите номер DUNS

Шаг 1. Получите номер DUNS

Получение номера Универсальной системы нумерации данных (DUNS) — это первый шаг к регистрации в качестве организации-заявителя в программе Grants.губ. Приведенные ниже инструкции описывают DUNS и проходят через процесс получения бесплатного номера DUNS.

Назначение ДУНС

A DUNS номер — это уникальный девятизначный номер, используемый для идентификации вашей организации. Федеральное правительство использует номер DUNS, чтобы отслеживать, как распределяются федеральные деньги.

Перед регистрацией на номер DUNS

Есть ли у моей организации номер DUNS? Большинство крупных организаций, библиотек, колледжей и исследовательских университетов уже имеют номер DUNS.Вам следует связаться с администратором гранта, финансовым отделом, финансовым директором или уполномоченным должностным лицом, чтобы узнать номер DUNS вашей организации.

Как зарегистрироваться для получения номера DUNS

Если у вашей организации еще нет номера DUNS или его никто не знает, посетите веб-сайт Dun & Bradstreet (D&B) или позвоните по телефону 1-866-705-5711, чтобы зарегистрироваться или выполнить поиск номера DUNS.

Регистрация номера DUNS осуществляется бесплатно, поэтому, если вы столкнетесь с какими-либо организациями или веб-сайтами, требующими плату или плату за получение номера DUNS, это, скорее всего, мошенничество или мошенничество.

Для получения номера DUNS вам понадобится вся информация, указанная ниже:

- Название организации

- Адрес организации

- Имя главного исполнительного директора (CEO) или владельца организации

- Юридическая структура организации (например, корпорация, товарищество, собственность)

- Год начала организации

- Основной вид деятельности

- Общее количество сотрудников (полное и неполное рабочее время)

ПРИМЕЧАНИЕ: В какой-то момент номер DUNS будет заменен «новым непатентованным идентификатором», запрошенным и назначенным Системой управления наградами (SAM.gov). Этот новый идентификатор называется уникальным идентификатором объекта (UEI) или идентификатором объекта. Grants.gov начал подготовку к этому переходу, информируя пользователей о предстоящих изменениях и обновляя метки полей и ссылки на номер DUNS (текущий идентификатор) в системе Grants.gov. Пользователи должны продолжать использовать номер DUNS в полях UEI до дальнейшего уведомления. Чтобы узнать больше о развертывании UEI в SAM, посетите gsa.gov/entityid.

Сколько времени нужно, чтобы получить номер DUNS?

Получение номера DUNS может занять до двух рабочих дней, но это может произойти и за один рабочий день.

Информация для иностранных абитуриентов

Если ваша организация находится за пределами США, вы можете зарегистрироваться для получения номера DUNS онлайн. Для регистрации в D&B вам не требуется получать федеральный налоговый идентификационный номер (TIN), также известный как идентификационный номер работодателя (EIN). При регистрации просто оставьте поле ИНН / EIN пустым. Однако любой, кто ведет дела с федеральным правительством, обычно должен получить TIN / EIN, чтобы соответствовать требованиям налоговой отчетности IRS.

Дополнительная информация для иностранных заявителей доступна в разделе «Право на получение гранта» программы «Гранты на обучение». Для получения информации о налогах и ИНН посетите веб-сайт IRS и найдите их самые последние инструкции для иностранцев и международных налогоплательщиков. Вы также можете связаться с контактным лицом агентства, указанным для возможности предоставления гранта, чтобы получить дополнительную информацию о конкретной возможности предоставления гранта.

Перейти к шагу 2: Зарегистрируйтесь в SAM

Регистр Modbus и цифровой ввод / вывод

Регистр Modbus и цифровой ввод / вывод

Пример действителен для: Все версии

CB3 Версия ПО: 3.1.17779 и выше

Версия программного обеспечения серии e: 5.1

Обратите внимание, что старые или новые версии программного обеспечения могут вести себя по-разному.

Это пример использования регистров Modbus для чтения с цифровых входов и записи в цифровые выходы блока управления.

Введение

Все универсальные роботы оснащены внутренним сервером Modbus. Это руководство по настройке клиента Modbus для чтения и записи во внутренние регистры сервера Modbus.

Адреса Modbus

Регистры цифровых входов и выходов расположены по адресам, указанным ниже. Полный список 16-битных регистров карты портов находится здесь Modbus server -16377.

|

Адрес |

до 3.0 |

3,0 |

3,1 |

R |

Вт |

|

|

0 |

Х |

Х |

Х |

Х |

|

Входы, биты 0-15 [BBBBBBBTTxxxxxx] x = undef, T = инструмент, B = поле |

|

1 |

Х |

Х |

Х |

Х |

Х |

Выходы, биты 0-15 [BBBBBBBBTTxxxxxx] x = undef, T = инструмент, B = поле |

Настройка ввода-вывода клиента Modbus Доступ к регистрам

Modbus может быть получен роботом изнутри с помощью клиента Modbus.

1. Клиент Modbus находится на вкладке установки.

2. Внутренний IP-адрес для сервера Modbus — 127.0.0.1.

3. Входные и выходные регистры добавляются нажатием кнопки «+» в правой части графического интерфейса пользователя

.

4. Установите для сигнала адреса Modbus значение 0 для входа в регистр. Пример ниже показывает, что когда цифровые входы 4 и 5 активированы, регистр Modbus преобразует двоичное число в целое число

.

5.Установите для сигнала адреса Modbus значение 1 для выходного регистра. Когда в регистре Modbus заданы целочисленные значения, значения цифрового выхода отражаются соответствующим образом.

Преобразование целого числа в двоичный список

Данные с сервера Modbus являются целыми числами. Данные могут быть преобразованы в список двоичных файлов с использованием функций ниже. После преобразования можно получить доступ к индивидуальному каналу ввода-вывода.

binary_list_to_integer ()

- Функция преобразования двоичного списка в целое число

integer_to_binary_list ()

- Функция преобразования целого числа в список двоичных файлов

Пример кода

Чтение входных регистров и преобразование в двоичную информацию

Программа для роботов

ASSIGN List_A = integer_to_binary (цифровые_входы)

ASSIGN Input_4 = List_A [4]

ASSIGN Input_5 = List_A [5]

Преобразование списка двоичных значений и установка выходного регистра.

Программа для роботов

ASSIGN List_B = [Истина, Ложь, Ложь, Ложь, Ложь, Ложь, Ложь, Ложь, Ложь, Ложь, Ложь, Ложь, Ложь, Ложь, Ложь, Ложь]

SET digital_outputs = binary_list_to_integer (List_B)

Последовательность перед запуском

ASSIGN List_A = [True]

ASSIGN List_B = [Ложь, Истина, Ложь, Истина, Истина, Истина]

Программа для роботов

ASSIGN List_A = integer_to_binary (цифровые_входы)

ПОДОЖДИТЕ 0.5

НАБОР digital_outputs = binary_list_to_integer (List_B)

ПОДОЖДИТЕ 0,5

Настроить универсальную печать | Документы Microsoft

- 3 минуты на чтение

В этой статье

В этом кратком руководстве объясняется, как включить универсальную печать и настроить принтер.

Назначить лицензии пользователям

Доступ к универсальной печати теперь включен в соответствующие подписки, перечисленные на странице лицензии на универсальную печать . Universal Print является частью этих подписок и указана в разделе «Детали плана обслуживания». Чтобы предоставить пользователям доступ к Universal Print, назначьте пользователю одну из соответствующих лицензий на подписку.

Чтобы просмотреть сведения о плане обслуживания, перейдите в Azure Active Directory — Лицензии — Все продукты и щелкните лицензию M365 или Windows 10.Выберите «Сведения о плане обслуживания». Вы должны увидеть «Универсальный принтер» в списке как часть лицензии.

Если вы приобрели автономную подписку на универсальную печать, назначьте лицензию на универсальную печать своим пользователям.

Предварительные требования

- Лицензия на универсальную печать назначается пользователю глобальным администратором

- Для настройки и управления универсальной печатью соответствующему администратору должна быть назначена соответствующая лицензия на универсальную печать.

- Для настройки и управления универсальной печатью администратору должна быть назначена одна из следующих двух ролей Azure Active Directory (Azure AD):

Администратор принтераилиГлобальный администратор. - Клиентское устройство (для установки и печати из Universal Print) под управлением клиентской ОС Windows версии 1903 или более поздней. Использование последней версии ОС обеспечит наилучшее взаимодействие с пользователем.

- Подключение к Интернету.

Шаг 1. Настройка универсального коннектора печати

Существующие на рынке принтеры не могут напрямую взаимодействовать с Universal Print и требуют прокси-коннектора Universal Print.Для получения дополнительной информации см .:

Что такое универсальный коннектор для печати?

Настройка универсальных разъемов печати

Шаг 2. Зарегистрируйте принтеры с помощью универсального коннектора печати

Принтеры, установленные на разъемах Universal Print, необходимо зарегистрировать в Universal Print. Для получения дополнительной информации см .:

Зарегистрируйте принтеры в Universal Print

Шаг 3. Назначьте разрешения и предоставьте общий доступ к принтеру

Зарегистрированные принтеры должны иметь разрешения, назначенные пользователям и группам безопасности Azure AD.После настройки разрешений к принтеру необходимо предоставить общий доступ, чтобы пользователи могли добавить его на свое устройство для печати.

Назначьте права доступа к принтеру и предоставьте общий доступ к принтеру

После предоставления общего доступа к принтеру пользователи могут начать на нем печать!

Шаг 4. Добавьте принтер универсальной печати на устройство Windows

Прежде чем пытаться добавить принтер Universal Print к устройству пользователя, убедитесь, что:

-

Устройство пользователя подключено к Интернету.

-

Устройство пользователя:

-

Принтер Universal Print предоставлен в общий доступ.

-

Пользователь был добавлен в права доступа к принтеру Universal Print, который должен быть добавлен на устройство.

-

Пользователю назначена лицензия на использование Universal Print. Дополнительные сведения о назначении лицензий см. В разделе Назначение или удаление лицензий на портале Azure Active Directory.

Примечание

После добавления лицензии для пользователя или добавления их в разрешения принтера может пройти до 30 минут, прежде чем принтер можно будет добавить на их устройство.

Чтобы добавить принтер универсальной печати на клиентское устройство Windows:

-

Выберите Настройки > Устройства > Принтеры и сканеры .

-

Выберите Добавить принтер или сканер .

Если нужный принтер не отображается в списке, выберите Искать принтеры в моей организации или Искать универсальный принтер для принтеров . Одна из этих ссылок появится внизу списка результатов поиска принтера и сканера и откроет страницу поиска, где вы можете найти принтер Universal Print, введя часть общего имени принтера.

-

Выберите нужный принтер, а затем выберите Добавить устройство .

-

После добавления принтера он появится в списке Printers & scanners в Settings .

Для принтеров Universal Print драйвером, выбранным на устройстве пользователя с Windows, является «Драйвер универсального класса печати».