Справочник «Цифровые Интегральные Микросхемы»

Справочник «Цифровые Интегральные Микросхемы» [ Содержание ]

Увлекаетесь электроникой?

Приглашаем Вас принять участие

в бета-тестировании онлайн-редактора

электрических схем.

sapr.asvcorp.ru

Работайте со схемами прямо из браузера.

2.1. Основы схемотехники элементов ТТЛ

Основную логическую операцию в элементе ТТЛ выполняет многоэмиттерный транзистор (рис. 2.1). Для удобства рассмотрения переключения логического элемента ко входу подключим управляющий переключатель S1, движок которого может занимать два положения — В и Н, а к выходу подключим резистор Rн. В положении В на вход поступит напряжение высокого уровня, т. е. питающее напряжение Uи.п., а в положении Н — напряжение низкого уровня, соответствующее нулю (вход заземляем). Если на вход (рис. 2.1,0) подано низкое напряжение (переключатель S1 поставлен в положение Н), то появится входной ток низкого уровня , который будет протекать от источника питания Uип = 5 В через резистор

Величина этого

тока определяется сопротивлением резистора RБ:

Величина этого

тока определяется сопротивлением резистора RБ:

В быстродействующих и экономичных ИС ТТЛ сопротивления резисторов

RБ отличаются примерно на порядок.

Переход база — коллектор транзистора VT1 открыться не может,

так как на нем нет избыточного напряжения более чем

0,7 В = UБЭ. Напряжение на выходе

близко к нулю Uвых=О. Таким образом, переход база — эмиттер

транзистора VT1 открыт, а переход база — коллектор VT1

закрыт, т. е. многоэмиттерный транзистор VT1 находится в

активном режиме, напряжение на выходе равно нулю Uвых=О.

Если число входов транзистора VT1 более одного

(рис. 2,1,б (два из них не присоединены), то величина тока

не изменится. Если все три эмиттера VT1

соединить вместе, ток

практически не изменится.

Следовательно, неиспользуемые входы можно оставлять разомкнутыми.

Если заземлен хотя бы один из входов транзистора

VT1 (рис. 2.1,б),

смена логических уровней на остальных входах не влияет на выходное

напряжение Uвых.

2.1,б),

смена логических уровней на остальных входах не влияет на выходное

напряжение Uвых.

Переведем движок переключателя S1 в положение В (рис. 2.1,в) (подано на вход напряжение высокого уровня), тогда переход база — эмиттер транзистора VT1 будет закрыт, так как напряжение между базой и эмиттером меньше или равно нулю UБЭ=<0. Оба электрода (база и эмиттер) подключены к источнику питания Uи.п=5 В. Большой ток базы IБ течет от источника питания Uи.п. через резистор RБ, открытый переход база — коллектор, а затем через резистор нагрузки Rн к нулевому потенциалу (рис. 2.1,в). На коллекторе VT1 появляется напряжение высокого уровня:

На вход 1 поступает лишь входной ток утечки высокого уровня , не превышающий при нормальной температуре нескольких наноампер (направление тока показано на рис. 2.1,в)

Рис. 2.1. Простейшие логические элементы ТТЛ:

а — путь входного тока Iвх0; б — токи в танзисторе VT1 при низком входном уровне;

в — токи в транзисторе VT1 при высоком входном уровне;

г — токи в простейшем инверторе при высоком входном уровне

Таким образом, переход база — эмиттер транзистора VT1 закрыт, а переход

база — коллектор VT1 открыт, т. е. многоэмиттерный транзистор

VT1 находится в инверсном активном режиме, напряжение на выходе

больше нуля: Uвых>0 (имеет высокий уровень).

е. многоэмиттерный транзистор

VT1 находится в инверсном активном режиме, напряжение на выходе

больше нуля: Uвых>0 (имеет высокий уровень).

Следовательно, на рис. 2.1,в приведен одновходовый элемент ТТЛ, реализующий логическую операцию И и не изменяющий фазу входного сигнала. Такой элемент назовем неинвертирующнм. В такой схеме активным включающим является напряжение низкого уровня и через переключатель S1 на корпус стекает большой входной ток (для стандартных элементов ТТЛ, серия К155, ток одного входа ~=1,6 мА) [1. 4].

Для получения инвертирующего логического элемента, реализующего логическую операцию И-НЕ, необходимо к многоэмиттерному транзистору VT1 добавить инвертор, выполненный на транзисторе VT2 (рис. 2.1.г).

Если на вход 1 логического элемента поступает напряжение высокого

уровня (переключатель S1 в положении В), то

многоэмиттсрный транзистор VT1 находится в

инверсном активном режиме, а транзистор VT2

насыщается базовым током IБ и выходное

напряжение, снимаемое с коллектора  Это напряжение

является напряжением насыщения коллектор — эмиттер

Uкэ.нас для кремниевого транзистора

VT2.

Это напряжение

является напряжением насыщения коллектор — эмиттер

Uкэ.нас для кремниевого транзистора

VT2.

Если на вход 1 логического элемента подать напряжение низкого уровня (переключатель S1 в положении Н), то транзистор VT2 практически закрыт, а во входной цепи течет большой ток . Выходное напряжение, снимаемое с коллектора VT2, близко к напряжению источника питания Uи.п., т. е. имеет высокий уровень, что соответствует логической единице .

Рассмотренный инвертор, выполненный на транзисторе VT2, является простым инвертором. Он используется лишь в микросхемах, выходы у которых имеют открытые коллекторы. Недостатком простого инвертора является низкая нагрузочная способность в закрытом состоянии (выходное сопротивление определяется сопротивлением резистора, стоящего в коллекторной цепи транзистора VT2).

Для повышения нагрузочной способности логического элемента вместо

простого инвертора большинство элементов ТТЛ имеют сложный инвертор

(рис. 2.2,а). Он состоит из фазоразделительного каскада, выполненного

на транзисторе VT2, и двухтактного выходного каскада,

состоящего из выходных транзисторов: насыщаемого VT5

и составного эмиттерного повторителя VT3 и

VT4.

2.2,а). Он состоит из фазоразделительного каскада, выполненного

на транзисторе VT2, и двухтактного выходного каскада,

состоящего из выходных транзисторов: насыщаемого VT5

и составного эмиттерного повторителя VT3 и

VT4.

Рис. 2.2.а. схема элемента со сложным инвертором

Рассмотрим функционирование логического элемента со сложным инвертором.

Подадим на вход напряжение низкого уровня, соответствующее логическому нулю

(переключатель  п.=5 В. Поэтому выходное напряжение,

снимаемое с нагрузки, расположенной в эмиттерной цепи

VT4, будет иметь высокий уровень, что соответствует

логической единице Uвых1.

п.=5 В. Поэтому выходное напряжение,

снимаемое с нагрузки, расположенной в эмиттерной цепи

VT4, будет иметь высокий уровень, что соответствует

логической единице Uвых1.

Рис. 2.2.б. распределение токов и напряжений при низком входном уровне

Статическое выходное напряжение высокого уровня для логического элемента равно: =Uи.п.-Iвых·R4-Uкэ-2·Uб.э.

Так как на транзисторах VT3, VT4 выполнен эмиттерный повторитель, то он не может перейти в состояние насыщения, и напряжение Uкэ VT4 не уменьшается меньше (0.7 .. 1) В, а напряжение Uбэ примерно равно 0,7 В для транзисторов без переходов Шотки. Падением напряжения на резисторе R4, ограничивающем ток в выходном каскаде, когда VT4 и VT5 открыты, можно пренебречь. Тогда получаем >=2,6 В.

Для транзисторов с переходами Шотки напряжение Uбэ

составляет (0. 2 … 0.3) В. Следовательно, для перспективных элементов

ТТЛ напряжение высокого уровня

2 … 0.3) В. Следовательно, для перспективных элементов

ТТЛ напряжение высокого уровня

Рис. 2.2.в. распределение токов и напряжений при высоком входном уровне

Подадим на вход 1 напряжение высокого уровня (переключатель

S1 поставлен в положение В) (рис. 2.2,в),

соответствующего логической единице, тогда многоэмиттерный транзистор

VT1 будет находиться в инверсном активном режиме

(переход база — эмиттер закрыт, а переход база — коллектор

открыт), течет большой ток IБ

в базу транзистора VT2, который откроется.

Часть эмиттерного тока транзистора VT2 поступает

в базу транзистора VT5, этот транзистор открывается и входит

в режим насыщения. Транзисторы VT3, VT4 будут закрыты.

Выходной сигнал, снимаемый с открытого и насыщенного транзистора

VT5 (rкэ~=30…50 Ом), имеет

низкий уровень Uвых0~=0. 3 В, что соответствует

логическому нулю.

3 В, что соответствует

логическому нулю.

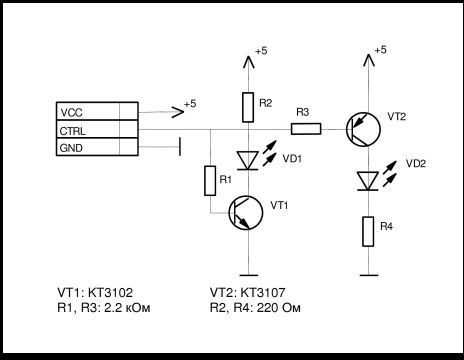

Диод VD1 предназначен для защиты входа транзистора VTl от пробоя и называется демпфирующим.

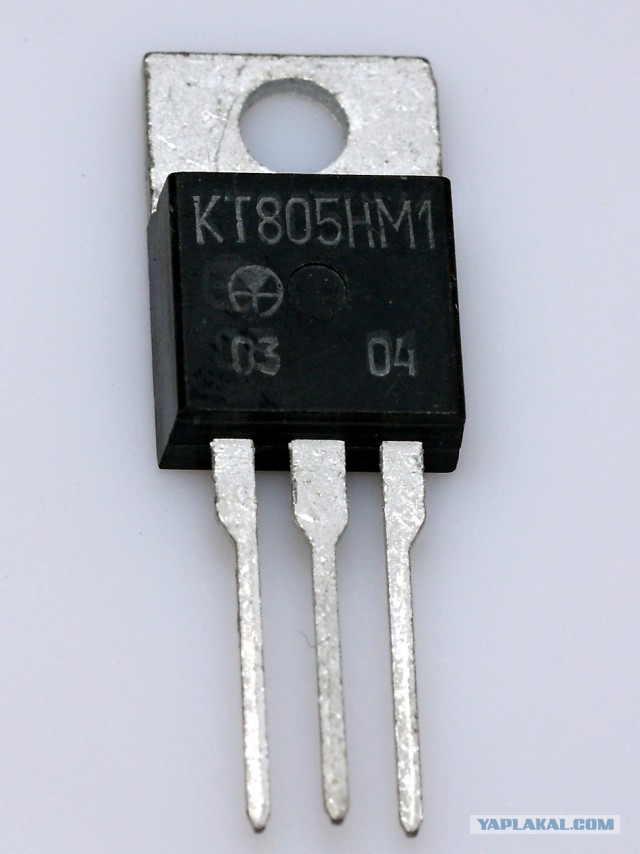

Vt1 транзистор

Транзисторы — это полупроводниковые приборы, которые предназначены для усиления, генерации и преобразования электрических сигналов. Это главный компонент в любой электрической схеме. Транзисторы бывают полевые и биполярные. Отличие их в том, что в биполярном транзисторе в переносе заряда участвуют электроны носители отрицательных зарядов и дырки носители положительных зарядов , а в полевом — один из носителей зарядов электроны или дырки.

Поиск данных по Вашему запросу:

Схемы, справочники, даташиты:

Прайс-листы, цены:

Обсуждения, статьи, мануалы:

Дождитесь окончания поиска во всех базах.

По завершению появится ссылка для доступа к найденным материалам.

Содержание:

- 19) Составной транзистор

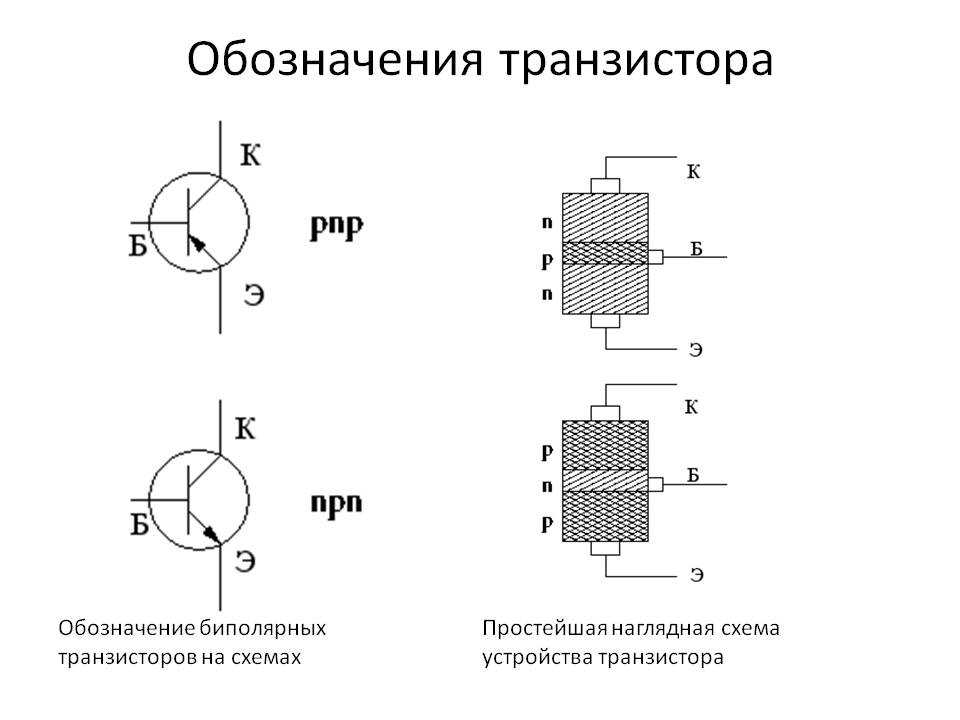

- Условное обозначение транзисторов на схемах

- Триггер на транзисторах

- Составной транзистор (схема Дарлингтона)

- Составные транзисторы. Схемы включения.

- ЗАМЕНА ТРАНЗИСТОРА ДАРЛИНГТОНА ПОЛЕВЫМИ ТРАНЗИСТОРАМИ – СДЕЛАЙ САМ

- Составной транзистор дарлингтона работа и устройство

ПОСМОТРИТЕ ВИДЕО ПО ТЕМЕ: Diode Transistor Logic Gates

19) Составной транзистор

Регистрация Вход. Ответы Mail. Вопросы — лидеры Квадрокоптер летит токо в верх модель YH 1 ставка. Не взлетает квадрокоптер 1 ставка. Перестал работать Mi band 4 1 ставка. А разве понятие «эфир» можно всерьёз рассматривать в электронике? Задача по физике 1 ставка. Лидеры категории Антон Владимирович Искусственный Интеллект.

Ответы Mail. Вопросы — лидеры Квадрокоптер летит токо в верх модель YH 1 ставка. Не взлетает квадрокоптер 1 ставка. Перестал работать Mi band 4 1 ставка. А разве понятие «эфир» можно всерьёз рассматривать в электронике? Задача по физике 1 ставка. Лидеры категории Антон Владимирович Искусственный Интеллект.

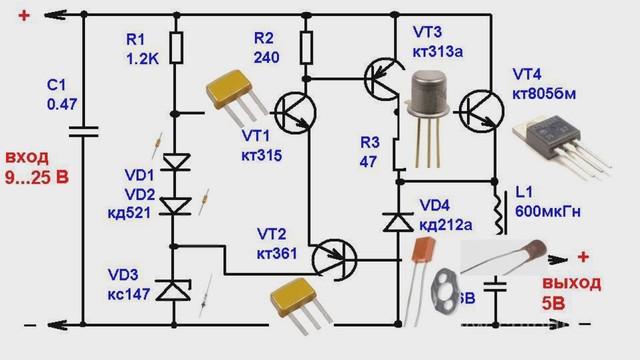

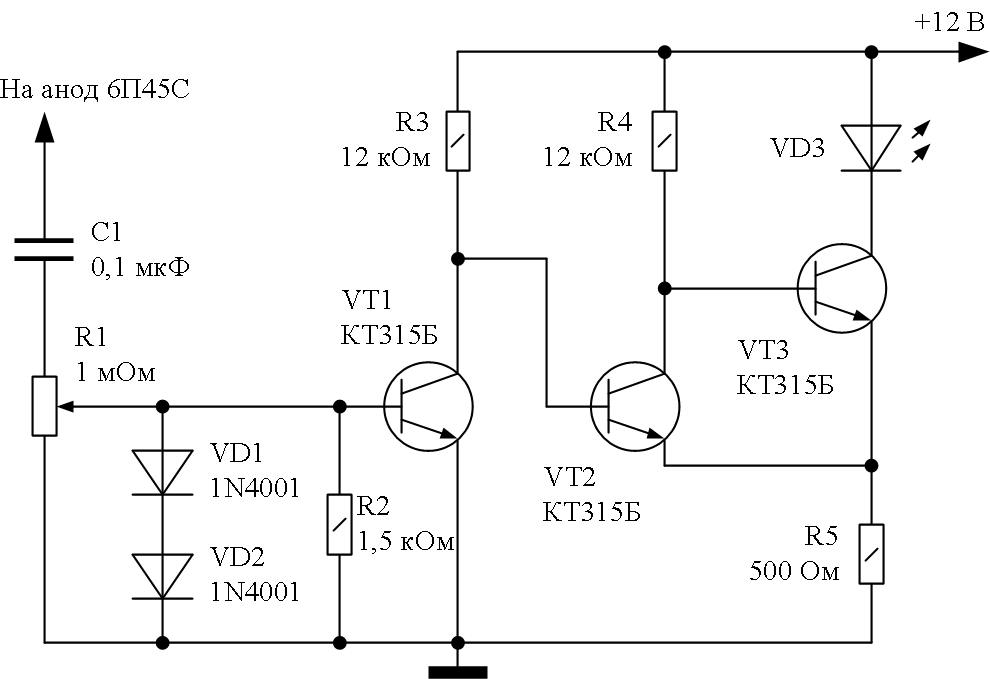

Кислый Высший разум. Голосование за лучший ответ. Nik Vas Искусственный Интеллект 2 года назад Все три транзистора являются усилителями низкой частоты. Комментарий удален IF Мастер помогите пожалуйста найти эту схему в журнале радио в каком выпуске какого года содержится эта схема. Комментарий удален happy case Мудрец сзр. Юрий Ладога Просветленный 2 года назад все три усилители, можно сказать vt1 — входящий, vt2 и vt3 — оконечный.

Вольный ветер Искусственный Интеллект 2 года назад Схема слишком много потребляет питания, батарейки на час не хватит, найди более экономичную Комментарий удален Вольный ветер Искусственный Интеллект Громкоговорящее устройство автобуса, схема простая довольно мощная и экономичная Похожие вопросы. Также спрашивают.

Также спрашивают.

Условное обозначение транзисторов на схемах

Транзистор от английских слов transfer — переносить и re sistor — сопротивление — полупроводниковый прибор, предназначенный для усиления, генерирования и преобразования электрических колебаний. Наиболее распространены так называемые биполярные транзисторы. Электропроводность эмиттера и коллектора всегда одинаковая p или n , базы — противоположная n или p. Иными словами, биполярный транзистор содержит два р-n-перехода: один из них соединяет базу с эмиттером эмиттерный переход , другой — с коллектором коллекторный переход. Буквенный код транзисторов — латинские буквы VT.

Транзисторы — это полупроводниковые приборы, которые предназначены для усиления, генерации и преобразования электрических сигналов.

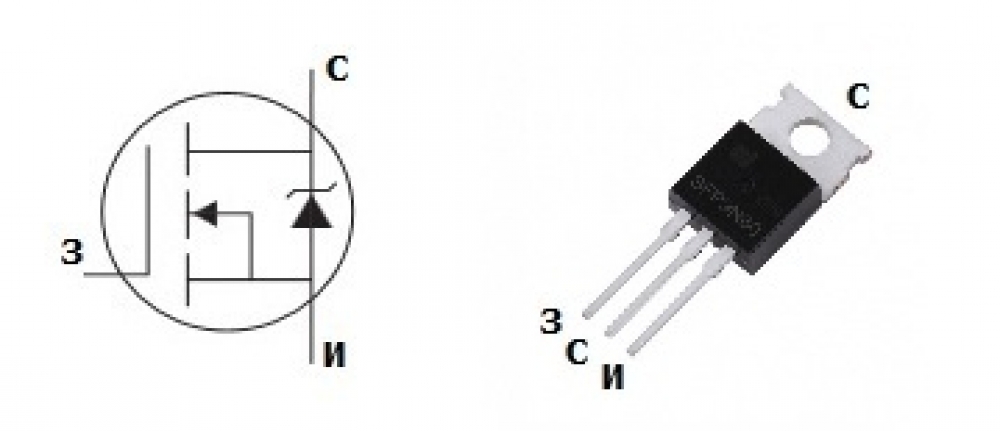

Триггер на транзисторах

На фото справа вы видите первый работающий транзистор, который был создан в году тремя учёными — Уолтером Браттейном, Джоном Бардином и Уильямом Шокли. Несмотря на то, что первый транзистор имел не очень презентабельный вид, это не помешало ему произвести революцию в радиоэлектронике. Транзистор является первым твёрдотельным устройством, способным усиливать, генерировать и преобразовывать электрический сигнал. Он не имеет подверженных вибрации частей, обладает компактными размерами. Это делает его очень привлекательным для применения в электронике. Это было маленькое вступление, а теперь давайте разберёмся более подробно в том, что же представляет собой транзистор. Сперва стоит напомнить о том, что транзисторы делятся на два больших класса. К первому относятся так называемые биполярные, а ко второму — полевые они же униполярные.

Транзистор является первым твёрдотельным устройством, способным усиливать, генерировать и преобразовывать электрический сигнал. Он не имеет подверженных вибрации частей, обладает компактными размерами. Это делает его очень привлекательным для применения в электронике. Это было маленькое вступление, а теперь давайте разберёмся более подробно в том, что же представляет собой транзистор. Сперва стоит напомнить о том, что транзисторы делятся на два больших класса. К первому относятся так называемые биполярные, а ко второму — полевые они же униполярные.

Составной транзистор (схема Дарлингтона)

Составной транзистор транзистор Дарлингтона — объединение двух или более биполярных транзисторовс целью увеличения коэффициента усиления по току. Составной транзистор являетсякаскадным соединениемнескольких транзисторов, включенных по схеме с общим коллектором. Нагрузкой предыдущего каскада является переход база-эмиттер транзистора следующего каскада, то есть транзисторы соединяются коллекторами, а эмиттер входного транзистора соединяется с базой выходного. Кроме того, может использоваться нагрузка в виде резистора. Такое соединение рассматривают как один транзистор, коэффициент усиления по току которого при работе транзисторов в активном режиме приблизительно равен произведению коэффициентов усиления первого и второго транзисторов: Составной транзистор имеет три вывода база, эмиттер и коллектор , которые эквивалентны выводам обычного одиночного транзистора.

Кроме того, может использоваться нагрузка в виде резистора. Такое соединение рассматривают как один транзистор, коэффициент усиления по току которого при работе транзисторов в активном режиме приблизительно равен произведению коэффициентов усиления первого и второго транзисторов: Составной транзистор имеет три вывода база, эмиттер и коллектор , которые эквивалентны выводам обычного одиночного транзистора.

Составной транзистор транзистор Дарлингтона — объединение двух или более биполярных транзисторов с целью увеличения коэффициента усиления по току.

Составные транзисторы. Схемы включения.

Войдите , пожалуйста. Хабр Geektimes Тостер Мой круг Фрилансим. Мегапосты: Криминальный квест HR-истории Путешествия гика. Войти Регистрация. Биполярные транзисторы. For dummies Электроника для начинающих Предисловие Поскольку тема транзисторов весьма и весьма обширна, то посвященных им статей будет две: отдельно о биполярных и отдельно о полевых транзисторах.

ЗАМЕНА ТРАНЗИСТОРА ДАРЛИНГТОНА ПОЛЕВЫМИ ТРАНЗИСТОРАМИ – СДЕЛАЙ САМ

При проектировании схем радиоэлектронных устройств часто желательно иметь транзисторы с параметрами лучше тех моделей, которые предлагают фирмы производители радиоэлектронных компонентов или лучше чем позволяет реализовать доступная технология изготовления транзисторов. Эта ситуация чаще всего встречается при проектировании интегральных микросхем. Нам обычно требуются больший коэффициент усиления по току h 21 , большее значение входного сопротивления h 11 или меньшее значение выходной проводимости h Улучшить параметры транзисторов позволяют различные схемы составных транзисторов. Существует много возможностей реализовать составной транзистор из полевых или биполярных транзисторов различной проводимости, улучшая при этом его параметры. Наибольшее распространение получила схема Дарлингтона. В простейшем случае это соединение двух транзисторов одинаковой полярности.

Эта ситуация чаще всего встречается при проектировании интегральных микросхем. Нам обычно требуются больший коэффициент усиления по току h 21 , большее значение входного сопротивления h 11 или меньшее значение выходной проводимости h Улучшить параметры транзисторов позволяют различные схемы составных транзисторов. Существует много возможностей реализовать составной транзистор из полевых или биполярных транзисторов различной проводимости, улучшая при этом его параметры. Наибольшее распространение получила схема Дарлингтона. В простейшем случае это соединение двух транзисторов одинаковой полярности.

В рассматриваемой конструкции, представляющей собой двухкаскадное радиопередающее устройство, на транзисторе VT1 выполнен микро-.

Составной транзистор дарлингтона работа и устройство

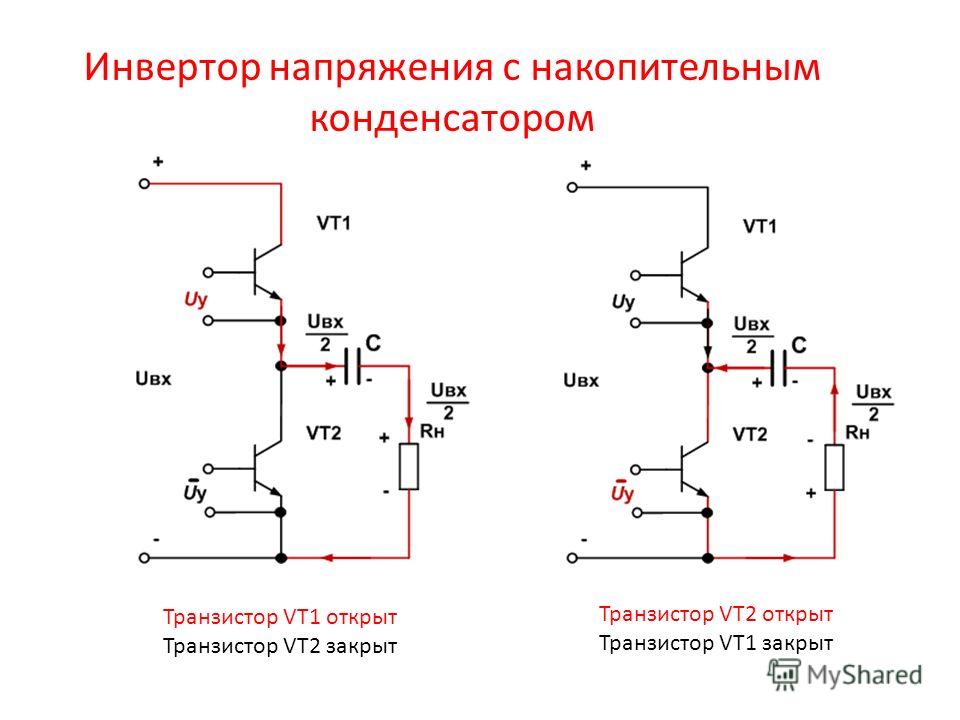

Исследование статических и динамических характеристик КМОП-инвертора. Инвертор реализует функцию НЕ и является простейшим базовым логическим элементом. В качестве инверторов используют ключи на биполярных или полевых транзисторах. Передаточная характеристика инвертора показана на рис.

Передаточная характеристика инвертора показана на рис.

Составным транзистором называется соединение двух и более транзисторов, эквивалентное одному транзистору, но с большим коэффициентом усиления или другими отличительными свойствами. Известно несколько схем составного транзистора. Схема Дарлингтона. Она характеризуется тем, что входные цепи всех входящих в нее транзисторов соединены последовательно, а выходные цепи — параллельно рис.

Познакомиться с работой различных электронных устройств лучше всего на примере простых транзисторных схем.

Регистрация Вход. Ответы Mail. Вопросы — лидеры Квадрокоптер летит токо в верх модель YH 1 ставка. Не взлетает квадрокоптер 1 ставка. Перестал работать Mi band 4 1 ставка.

В схеме усилительного каскада на рис. Для создания смещения здесь используется делитель напряжения -. В соответствии с выбранным положением начальной рабочей точки, определяемой напряжением смещения, в коллекторной цепи транзистора протекает начальный коллекторный ток. Этот ток создает на эмиттерном сопротивлении падение напряжения:.

Этот ток создает на эмиттерном сопротивлении падение напряжения:.

vt1%20транзистор техпаспорт и примечания по применению

Недоступно

Резюме: нет абстрактного текста

Текст: ток коллектора и глубина модуляции SFH601 -4 VCEsat=f (lc) (TA=25°C) Рисунок 20. Транзистор

OCR-сканирование

Недоступно

Резюме: нет абстрактного текста

Текст: ) Рис. 20. Емкость транзистора C -f(V o ) (Ta=25°C, f=1 МГц) 0 ,1 [· 0 i-i- — L I 10

OCR-сканирование

lc приборная панель 2 b-5

Резюме: нет абстрактного текста

Текст: ) Рис. 20. Емкость транзистора C=f(VQ) (Ta=25°C, f=1 МГц) ≥ SFH600 5-212

OCR-сканирование

РЛ2010-54.1К-138-Д1

Резюме: thermonics YD80SM-12 12V ВЕНТИЛЯТОР УПРАВЛЕНИЕ С ИСПОЛЬЗОВАНИЕМ ТЕРМИСТОРА 47k термистор ntc PN2222A to-92 PWM IC 8-PIN DIP pwm термистор 80-vt1 2N2222A

Текст: Нет доступного текста файла

Оригинал

2014 — MIC502YM

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2003 — YD80SM-12

Резюме: 12 В — управление скоростью вращения вентилятора с помощью термистора 2003 ATX ШИМ-управление PN2222A ЭКВИВАЛЕНТ RL201054

Текст: Нет доступного текста файла

Оригинал

1998 — mic502 ic

Резюме: YD80SM-12 2N2222A MIC502 MIC502BM MIC502BN 240 термистор ntc 100k Линейный драйвер вентилятора

Текст: Нет доступного текста файла

Оригинал

2002 — транзистор vt1

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2001 — транзистор vt1

Реферат: УПРАВЛЕНИЕ ВЕНТИЛЯТОРОМ 24 В С ПОМОЩЬЮ ТЕРМИСТОРА thermonics 2N2222A MIC502 MIC502BM MIC502BN УПРАВЛЕНИЕ ВЕНТИЛЯТОРОМ 12 В С ИСПОЛЬЗОВАНИЕМ ТЕРМИСТОРА Термистор-резистор ШИМ-термистор

Текст: Нет доступного текста файла

Оригинал

2001 — YD80SM-12

Реферат: УПРАВЛЕНИЕ ВЕНТИЛЯТОРОМ 12 В С ИСПОЛЬЗОВАНИЕМ ТЕРМИСТОРА MIC502 PWM IC 8-PIN DIP vt1 транзистор 2N2222A MIC502BM MIC502BN thermonics RL201054

Текст: Нет доступного текста файла

Оригинал

1999 г. — нет в наличии

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

термистор 502 на

Резюме: IC502 24V ВЕНТИЛЯТОР УПРАВЛЕНИЕ С ИСПОЛЬЗОВАНИЕМ ТЕРМИСТОРА IC 502 термистор 502

Текст: Нет доступного текста файла

OCR-сканирование

Недоступно

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

OCR-сканирование

2010 — Недоступно

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2003 — 112206

Резюме: mic502 ic 12V FAN CONTROL BY USING THERMISTOR datasheet драйвер бесколлекторный охлаждающий вентилятор постоянного тока mic502 MIC502BM MIC502BN MIC502YM

Текст: Нет доступного текста файла

Оригинал

IC502

Реферат: УПРАВЛЕНИЕ ВЕНТИЛЯТОРОМ 24В С ПОМОЩЬЮ ТЕРМИСТОРА K138

Текст: Нет доступного текста файла

OCR-сканирование

Недоступно

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2003 — Недоступно

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2011 — HMC1000LP5E

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2002 — ВСК9182

Реферат: Транзистор vt1 GR-253-CORE VSC9187 VSC9188

Текст: Нет доступного текста файла

Оригинал

2009 — Калибровка гироскопа

Аннотация: автожир Ан-1049

Текст: Нет доступного текста файла

Оригинал

2002 — ГР-1400-ЯДЕР

Резюме: GR-253-CORE VSC9182 VSC9186 VSC9187 VSC9188 cdr 03a

Текст: Нет доступного текста файла

Оригинал

2012 — LTC2995IUD

Реферат: ИМС уд 1803 маркировка T01 SOT 1332V UV диод LTC2997

Текст: Нет доступного текста файла

Оригинал

2012 — Недоступно

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

ЛМ56

Реферат: СХЕМА ТЕРМОСТАТА HVAC lm568 LM56BIM LM56BIMM LM56BIMMX LM56BIMX LM56CIM LM56CIMX M08A

Текст: Нет доступного текста файла

Оригинал

Предыдущий 1 2 3 … 23 24 25 Далее

Время попрощаться с ggNMOS Snapback для защиты от электростатического разряда – SOFICS – Решения для интегральных схем

RIP Зажим ggNMOS ESD – спасибо за годы самоотверженной работы и обслуживанияSnapback ggNMOS уже много лет является нашим супергеройским антистатическим устройством.

Благодаря правильному анализу, пониманию и некоторым хитростям инженеры ESD по всему миру полагались на него и завоевали уважение своих коллег. Инженеры могли произвести впечатление на своих коллег, которые считали, что это чистая магия. ggNMOS был нашей опорой и источником силы.

Однако в последние годы ggNMOS было трудно следить и адаптироваться ко всем новейшим инновациям и масштабированию процессов. Мы все еще могли полагаться на него в особых случаях, но стало ясно, что конец близок.

С уходом из жизни ggNMOS оставляет после себя множество надежных ИС-продуктов.

Инженеры по ИС, разрабатывающие зажимы для защиты от электростатического разряда для чипов в зрелых низковольтных (5 В или ниже) технологиях CMOS (0,18 мкм или старше), избалованы. В этих процессах диоды ESD могут проводить большой ток ESD, типичные расчетные окна ESD очень широки, а NMOS-транзистор является идеальным фиксатором защиты от ESD для большинства комбинаций нагрузок.

Snapback Защита от электростатического разряда на основе NMOS

В этих зрелых технологических узлах NMOS-транзистор сочетает в себе несколько хороших характеристик во время событий электростатического разряда

- Операция Snapback, когда активируется паразитный биполярный NPN-транзистор .

- Небольшого устройства достаточно для стандартной устойчивости к электростатическим разрядам (It2) благодаря высокой производительности NPN .

- Эффективная защита для большинства функциональных цепей благодаря низкому напряжению срабатывания (Vt1), определяемому пробоем перехода сток-подложка, ниже типичного напряжения отказа цепей оксида затвора и сердечника.

- Низкий риск защелкивания , поскольку напряжение фиксации/удержания (Vh), определяемое бета-вариантом NPN, выше напряжения питания.

Клемма имеет пусковое напряжение (Vt1), напряжение фиксации/удержания (Vh), сопротивление в открытом состоянии (Ron) и уровень тока отказа (It2).

Клемма имеет пусковое напряжение (Vt1), напряжение фиксации/удержания (Vh), сопротивление в открытом состоянии (Ron) и уровень тока отказа (It2). Благодаря этим характеристикам NMOS-транзистор используется в качестве фиксатора электростатического разряда в различных местах микросхемы в зрелых процессах.

- ggNMOS можно использовать как силовой зажим устройство

- Конструкторы используют это устройство также в качестве локальной защиты для защиты входных затворов

- Выходные драйверы могут быть легко изготовлены зажим

- Подход вторичной защиты может быть использован для расширения окна проектирования ESD для более чувствительных цепей

«NMOST с заземленным затвором (ggNMOST) —

одна из рабочих лошадок в области ESD».

Постоянно обновляется и совершенствуется

Благодаря такому приятному универсальному подходу многие инженеры по электростатическим разрядам и инженеры-технологи по всему миру придумали приемы , чтобы максимально повысить удобство использования при внесении изменений в технологический процесс. Во многих публикациях содержится подробная информация о добавлении фиктивных пальцев, масках блокировки nLDD, блокировке силицида, балластировке на заднем конце, методах срабатывания нескольких пальцев и масках имплантатов ESD.

Во многих публикациях содержится подробная информация о добавлении фиктивных пальцев, масках блокировки nLDD, блокировке силицида, балластировке на заднем конце, методах срабатывания нескольких пальцев и масках имплантатов ESD.

К сожалению, все хорошие истории когда-нибудь заканчиваются . Основываясь на хорошем опыте работы со зрелыми узлами, инженеры задались вопросом, можно ли использовать Snapback NMOS также в более продвинутых процессах CMOS, FinFET, высокого напряжения, BCD или SOI. Литейные заводы продвигали использование NMOS-транзистора snapback для защиты от электростатического разряда в каждом из этих процессов, но это привело к большому количеству отказов продукта.

Передовая технология CMOS

Например, в более продвинутом техпроцессе совсем не мрачно. Существует ряд тенденций , которые играют роль в упадке защиты от электростатического разряда на основе ggNMOS для наиболее чувствительных интерфейсов.

- Соединения стали более мелкими, а размеры — меньшими в каждом последующем узле процесса. Этот уменьшенный объем вызвал падение надежности паразитного устройства NPN . С более чем 10 мА/мкм в 0,25 мкм производительность упала до менее половины в 28-нм CMOS. Таким образом, для той же устойчивости к электростатическому разряду периметр необходимо удвоить.

- Напряжение срабатывания Vt1 упало на каждом узле с ~6 В для 180-нм до ~4 В для 28-нм КМОП. Однако напряжение пробоя оксида с тонким затвором падало быстрее (>8 В до менее чем 3,5 В). С 90 нм, напряжение пробоя сток-подложка примерно такое же, как напряжение пробоя (тонкого) оксида. Это означает, что, например.

зажим ggNMOS ESD 40 нм больше не может защитить тонкий оксидный интерфейс , не говоря уже о себе.

зажим ggNMOS ESD 40 нм больше не может защитить тонкий оксидный интерфейс , не говоря уже о себе. - Инженеры по защите от электростатических разрядов придумали хитрые методы снижения напряжения срабатывания до напряжения удержания, например, с помощью объем или корпус или уклон ворот. Это отложило проблему.

- Напряжение ограничения также снижается на более продвинутых узлах CMOS (> 4 В до 3,5 В), но это снижение происходит медленнее. В узле 28 нм напряжение фиксации выше напряжения пробоя тонкого оксида . Конец…

Отчетливо видна сниженная маржа и отсутствие эффективной защиты от 90 нм.

Отчетливо видна сниженная маржа и отсутствие эффективной защиты от 90 нм. Люди успешно использовали зажимы ggNMOS в 28-нм CMOS, например, в качестве зажимов CDM (вторичных). Благодаря короткой длительности импульса пробой оксида затвора в переходном режиме немного выше. Для основной или первичной защиты от электростатического разряда лучше полагаться на другие концепции защиты от электростатического разряда. Для интерфейсов на основе толстых оксидных транзисторов окно проектирования ESD по-прежнему достаточно велико. Большинство ячеек ввода-вывода общего назначения основаны на транзисторах с толстым оксидом.

Технология FinFET

Как и в случае с усовершенствованной КМОП, подход NMOS мгновенного возврата больше не является предпочтительным вариантом в процессах FinFET. Часто NMOS-транзистор не выдерживает обратного хода для импульсов TLP длительностью 100 нс, даже если стоки заблокированы силицидом. Транзистор FinFET NMOS не может защитить себя во время стресса от электростатического разряда. Пробой (тонкого) оксида затвора дополнительно снижается до 3 В или менее.

Пробой (тонкого) оксида затвора дополнительно снижается до 3 В или менее.

Проблемы возникают даже у интерфейсов на основе толстых оксидных транзисторов. Транзисторы NMOS FinFET с толстым оксидом также часто выходят из строя при возврате. К счастью, можно использовать и другие защитные устройства. Узнайте больше в другой статье нашего блога (защита от электростатического разряда для FinFET).

Высоковольтные и BCD-процессы

В высоковольтных и BCD-процессах разработчикам обязательно следует искать альтернативы. Крупные литейные заводы (по-прежнему) продвигают NLDMOS-транзисторы для защиты от электростатических разрядов в качестве ограничителя мощности, самозащитных драйверов и локальной защиты ввода-вывода. Конечно, разработчики интегральных схем, создающие сложные аналоговые схемы, часто полагаются на эти руководства и рекомендации.

. седых волос. Единственная польза от этих литейных рекомендаций — это больше отладки/консалтинга для Sofics. Мы часто встречаем разработчиков микросхем, которые следовали рекомендациям производителя, но впоследствии сталкивались с проблемами электростатического разряда или защелкивания. Они протягивают руку и ожидают быстрого решения в течение 2 недель для повторного запуска своего следующего продукта.

Но отладка продуктов, связанных с электростатическим разрядом, не является нашей страстью. Наши инженеры предпочитают активно решать проблемы электростатического разряда . При каждой возможности тестирования чипа они ищут улучшенные концепции защиты, которые никто раньше не пробовал. Мы изобретаем, разрабатываем и оптимизируем решения для защиты от электростатического разряда, которые могут быть повторно использованы многими без необходимости повторного запуска продукта.

Кто прав?

Так что же происходит? Кто прав? Эксперты литейного производства по электростатическому разряду протестировали предлагаемые зажимы для защиты от электростатического разряда и с готовностью делятся результатами анализа TLP и HBM, чтобы продемонстрировать, что зажимам для защиты от электростатического разряда на основе NLDMOS можно доверять.

С другой стороны, компания Sofics смогла охарактеризовать свойства электростатического разряда транзисторов NLDMOS во многих процессах BCD на различных литейных заводах и собственных фабриках. Наш вывод состоит в том, что разработчики микросхем должны воздерживаться от использования NLDMOS-транзисторов snapback для защиты от электростатических разрядов .

Разработка через тестирование

В мире программного обеспечения разработчики используют «разработку через тестирование». Сначала они определяют все условия испытаний и ограничения, которые должен пройти новый программный модуль. Сначала они создают тестовую процедуру, прежде чем приступают к кодированию функции.

Сначала они создают тестовую процедуру, прежде чем приступают к кодированию функции.

В поисках новых концепций защиты мы использовали аналогичный подход. Основываясь на нашем опыте работы со многими клиентами и технологических процессах, мы определяем минимальные условия, которым должны соответствовать зажимы ESD.

Деградация после многократного воздействия электростатического разряда?

Конечно, когда клещи ESD проходят испытания на заводе и проходят испытания HBM 2 кВ, или анализ TLP показывает хорошие характеристики обратного хода (пример выше), а ток утечки остается ниже уровня 1 мкА до 1,3 А, все должно быть в порядке, верно. ? Это зависит. Одного тестового условия недостаточно.

Одним из условий испытаний , в которое мы твердо верим, является «отсутствие деградации» . Мы рекомендуем использовать устройства защиты от электростатического разряда, которые не разрушаются после повторяющихся (слаботочных) импульсов нагрузки от электростатического разряда. Еще в 2001 году такие условия испытания на отсутствие деградации были фактически предложены в рецензируемой публикации Imec в Бельгии (ссылка).

Еще в 2001 году такие условия испытания на отсутствие деградации были фактически предложены в рецензируемой публикации Imec в Бельгии (ссылка).

Предположим, зажим рассчитан на 2 кВ HBM, пиковый ток примерно 1,3 А. Когда этот зажим подвергается нагрузке 1000 раз, скажем, 1 А (~ 1,5 кВ HBM), он должен вести себя точно так же, как и для первого импульса.

Всякий раз, когда мы запускаем этот тест на высоковольтных транзисторах NLDMOS, мы замечаем изменение утечки . Каждый раз, когда устройство запускается в обратном направлении, некоторые заряды захватываются оксидом рядом с каналом NMOS. Захваченный заряд влияет на поведение устройства. Устройства

HV NLDMOS подвергались нагрузке несколькими (<50) импульсами при разных уровнях тока для исследования деградации. Выше включения NPN деградация видна в увеличении тока утечки. Захват заряда в полевом оксиде на клюве птицы локально снижает напряжение пробоя, представленное черным пятном на стоке. Из-за пониженного напряжения пробоя следующий ток нагрузки от электростатического разряда (2,3) будет локализован в черной точке, препятствуя равномерной проводимости по всему пальцу.

Иногда сдвиг утечки виден даже во время стандартного теста TLP. Изменение количества ступеней может повлиять на ток отказа. На рисунке ниже показано постепенное увеличение тока утечки при повышении уровня нагрузки TLP. Более того, это показывает, что утечка увеличивается быстрее, если плотность импульсов TLP выше.

2 идентичных высоковольтных устройства ggNMOS на одной (тестовой микросхеме) пластине. ВАХ такая же, при Vt1 выше 70В и удерживающем напряжении около 10В. Но ток отказа разный. Синий индикатор показывает сбой около 700 мА. Красное измерение показывает сбой при 1,3 А, почти в два раза. Единственная разница между обоими измерениями заключается в плотности импульса.В документе Sofics 2004 г. об антистатических клещах для высоковольтных процессов приводится больше данных специально для устройств NLDMOS (ссылка). В статье также содержится дополнительная информация о том, что происходит внутри устройства.

Другие проблемы

Существуют и другие проблемы с Snapback NLDMOS для защиты от электростатического разряда. Существует большая разница между напряжением запуска Vt1 и напряжением фиксации Vh. Это может привести к неравномерному запуску между различными отводами устройства и даже в пределах одного отвода устройства.

Существует большая разница между напряжением запуска Vt1 и напряжением фиксации Vh. Это может привести к неравномерному запуску между различными отводами устройства и даже в пределах одного отвода устройства.

Напряжение срабатывания (Vt1) высокое, но обычно напряжение фиксации/удержания довольно низкое (10 В или ниже). Это может привести к проблемам фиксации , когда NPN срабатывает в условиях питания. Лучше полагаться на зажимы для защиты от электростатического разряда с напряжением зажима выше напряжения сигнала/питания. Компания Sofics разработала широкий спектр таких устройств для высоковольтных процессов с 2008 года. Они доступны под торговой маркой PowerQubic.

Другой типичной проблемой является так называемый эффект окна . Устройство выдерживает высокое (2 кВ HBM) воздействие электростатического разряда, но выходит из строя при низком (например, 500 В HBM) уровне. Это поведение иногда можно проверить с помощью тестов TLP с разным временем нарастания. Когда устройства ggNMOS подвергаются нагрузке с разным временем нарастания, поведение меняется. Для быстрых времен нарастания можно увеличить общее (и затворное) напряжение, понизив триггерное напряжение Vt1.

Это поведение иногда можно проверить с помощью тестов TLP с разным временем нарастания. Когда устройства ggNMOS подвергаются нагрузке с разным временем нарастания, поведение меняется. Для быстрых времен нарастания можно увеличить общее (и затворное) напряжение, понизив триггерное напряжение Vt1.

Заключение

В течение многих лет мы полагались на устройство snapback ggNMOS. Это было идеальное устройство ESD с отличными внутренними свойствами и способами оптимизации для более требовательных приложений. К сожалению, в передовых технологиях, таких как 28-нм CMOS, процессы FinFET и, конечно, для процессов высокого напряжения, устройство необходимо заменить альтернативными концепциями защиты от электростатического разряда.