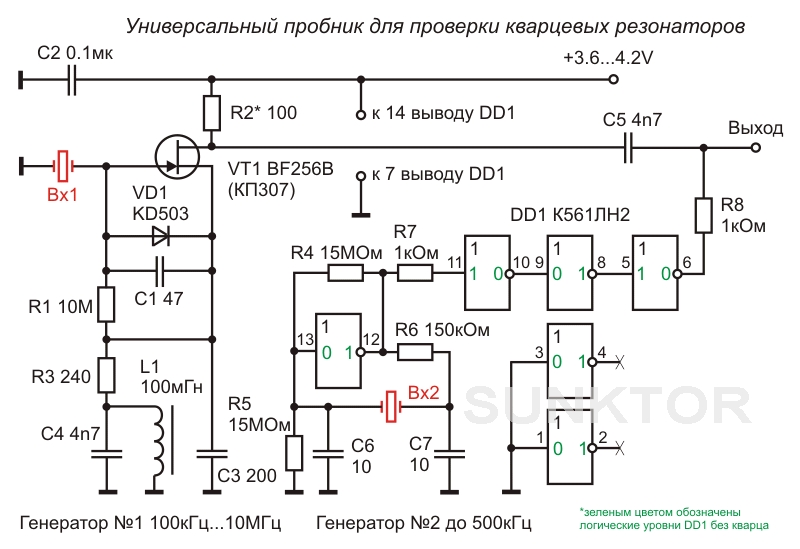

Как работает генератор на 500 кГц. Какие элементы входят в его схему. Почему используется последовательный резонансный контур. На каких транзисторах можно собрать генератор. Как настроить частоту генерации.

Принцип работы генератора на 500 кГц

Генератор на 500 кГц представляет собой высокостабильный источник синусоидального сигнала, используемый в качестве опорного в различных радиотехнических устройствах. Его основу составляет последовательный резонансный LC-контур, обеспечивающий высокую стабильность частоты генерации.

Ключевые особенности такого генератора:

- Использование последовательного резонансного контура

- Применение биполярного транзистора в качестве активного элемента

- Наличие цепи положительной обратной связи

- Высокая стабильность частоты (нестабильность менее 0,1%)

- Синусоидальная форма выходного сигнала

Схема генератора на 500 кГц

Типовая схема высокостабильного генератора на 500 кГц включает следующие основные элементы:

- Биполярный транзистор (например, КТ209)

- Последовательный резонансный LC-контур

- Конденсаторы и резисторы для задания режима работы

- Катушку связи для снятия выходного сигнала

Рассмотрим подробнее назначение основных элементов схемы:

Транзистор

В качестве активного элемента используется биполярный транзистор структуры p-n-p (например, КТ209) или n-p-n (КТ630). Он обеспечивает усиление сигнала и компенсацию потерь в контуре для поддержания незатухающих колебаний.

Резонансный контур

Последовательный LC-контур является ключевым элементом, определяющим частоту генерации. Он состоит из катушки индуктивности и конденсатора, включенных последовательно. На резонансной частоте контур имеет минимальное сопротивление.

Цепь обратной связи

Положительная обратная связь организуется путем подключения контура между коллектором и базой транзистора. Это обеспечивает самовозбуждение генератора на резонансной частоте контура.

Преимущества последовательного резонансного контура

Использование последовательного резонансного контура в генераторе имеет ряд важных преимуществ:

- Высокая стабильность частоты генерации

- Меньшая зависимость от параметров транзистора

- Близкая к синусоидальной форма выходного сигнала

- Возможность точной настройки на заданную частоту

Благодаря этим особенностям генератор на последовательном контуре позволяет получить более качественный и стабильный сигнал по сравнению с генераторами на параллельном контуре.

Настройка частоты генератора

Точная настройка частоты генерации на 500 кГц осуществляется следующими способами:

- Изменение индуктивности катушки контура

- Подстройка емкости конденсатора контура

- Регулировка напряжения питания генератора

Для достижения максимальной стабильности следует использовать катушки с высокой добротностью и конденсаторы с малым температурным коэффициентом емкости.

Применение генератора на 500 кГц

Высокостабильный генератор на 500 кГц находит широкое применение в различных областях радиотехники:

- В качестве опорного генератора в радиоприемной аппаратуре

- Как источник сигнала промежуточной частоты в супергетеродинных приемниках

- В измерительной технике в качестве калибровочного генератора

- В системах радиосвязи как задающий генератор

Благодаря высокой стабильности частоты такой генератор позволяет обеспечить точную настройку и калибровку радиотехнических устройств.

Как собрать генератор на 500 кГц своими руками

Для самостоятельной сборки генератора на 500 кГц потребуются следующие компоненты:

- Транзистор КТ209 или аналогичный

- Катушка индуктивности ~100-120 мкГн

- Конденсатор ~860 пФ

- Резисторы для задания режима

- Источник питания 1,5-2 В

Порядок сборки и настройки:

- Намотать катушку контура на каркасе диаметром 5-7 мм

- Собрать схему генератора на макетной плате

- Подключить источник питания

- Измерить частоту генерации частотомером

- Подстроить частоту изменением числа витков катушки

При правильной сборке и настройке генератор должен выдавать стабильный синусоидальный сигнал частотой 500 кГц.

Особенности настройки генератора на 500 кГц

При настройке высокостабильного генератора на 500 кГц следует учитывать ряд важных моментов:

- Напряжение питания должно быть стабилизировано

- Необходимо обеспечить хороший теплоотвод от транзистора

- Катушка контура должна быть жестко закреплена

- Следует использовать высококачественные конденсаторы

- Важно минимизировать паразитные емкости монтажа

Соблюдение этих рекомендаций позволит добиться максимальной стабильности частоты генерации. При необходимости можно применить термокомпенсацию для дальнейшего повышения стабильности.

Измерение параметров генератора 500 кГц

Для оценки качества работы собранного генератора следует измерить его основные параметры:

- Частота генерации (должна быть 500 кГц ± 0,1%)

- Форма выходного сигнала (близкая к синусоиде)

- Уровень выходного напряжения (обычно 0,5-1 В)

- Кратковременная нестабильность частоты

- Температурный коэффициент частоты

Измерения проводятся с помощью частотомера, осциллографа и анализатора спектра. Полученные результаты позволяют оценить стабильность и качество работы генератора.

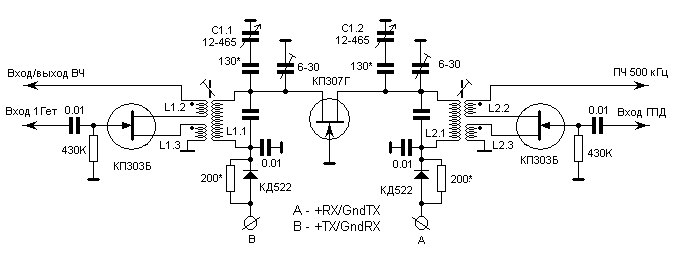

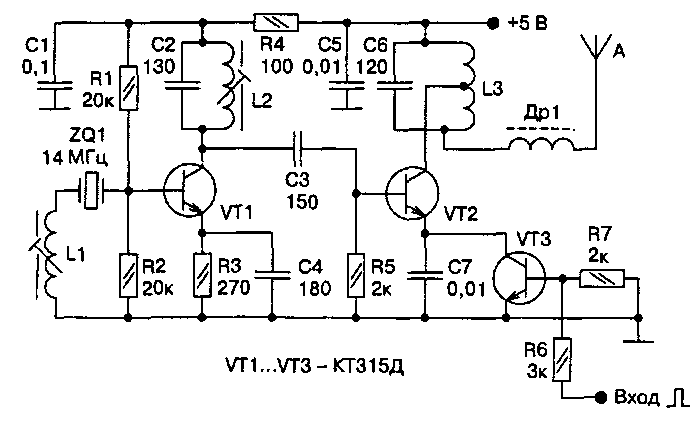

Схема тракта КВ-Трансивера 500 кГц » Паятель.Ру

Категория: Трансиверы

Тракт предназначен для работы в качестве основной платы простого KB-трансивера с однократным преобразованием частоты и промежуточной частотой 500 кГц. Основным селективным элементом схемы является электромеханический фильтр типа ЭМФ-9Д-500-ЗВ. Он используется для выделения промежуточной частоты при приеме и для формирования SSB-сигнала при передаче.Схема тракта однонаправленная, то есть, направление прохождения сигнала по каскадам при смене режимов приема (RX) и передачи (ТХ) не изменяется. Переключение режимов RX/TX производится посредством двух электромагнитных реле (на схеме показаны только их контакты) и коммутацией внешних узлов, таких как антенная система, фильтры, генераторы плавного диапазона и опорной частоты, а так же, низкочастотные усилители.

Коэффициент передачи тракта при приеме регулируется вручную посредством переменного резистора, а коэффициент передачи при передаче устанавливается посредством подстроечного резистора фиксированным, при налаживании трансивера в целом. Автоматического регулятора усиления нет. Смесители частот, выполняющие роль модуляторов, демодуляторов и преобразователей частоты выполнены на высокочастотных трансформаторах по схемам балансных кольцевых смесителей на диодах.

Автоматического регулятора усиления нет. Смесители частот, выполняющие роль модуляторов, демодуляторов и преобразователей частоты выполнены на высокочастотных трансформаторах по схемам балансных кольцевых смесителей на диодах.

Положения контактов реле на схеме показано при приеме. При приеме сигнал от входной системы (от ФСС RX), которая может представлять собой антенную систему и контуры (ФСС), УРЧ или без УРЧ, поступает на вход смесителя на VD1-VD4. При передаче сюда же поступает сигнал НЧ с выхода микрофонного усилителя (дроссель L1 разделяет ВЧ и НЧ цепи).

Сигнал от генератора плавного диапазона (ГПД) поступает на смеситель через контакты реле К1.1. Результат преобразования, — промежуточная частота 500 кГц выделяется в контуре L3-C3. Далее следует каскадный усилительный каскад на транзисторах VT1 и VT2, нагруженный первичной обмоткой электромеханического фильтра Z1. Фильтр выделяет верхнюю боковую полосу.

Затем следует еще один каскад по схеме с общим эмиттером на VT3, нагруженный контуром L4-С16, с выхода которого сигнал поступает на кольцевой смеситель VD5-VD8, работающий сейчас как демодулятор. Напряжение опорной частоты 500 кГц поступает на него через контакты реле К2.1. Низкочастотный (демодулированный) сигнал снимается с R13.

Напряжение опорной частоты 500 кГц поступает на него через контакты реле К2.1. Низкочастотный (демодулированный) сигнал снимается с R13.

При передаче функции смесителей меняются на противоположные. Низкочастотное напряжение с микрофонного усилителя поступает на смеситель на диодах VD1-VD4 (через разделительный конденсатор С1 и заградительный дроссель L1). Через контакты реле К1.1 на смеситель поступает напряжение частотой 500 кГц от опорного генератора (при приеме это напряжение поступало на смеситель на диодах VD5-VD8).

Смеситель работает балансным модулятором. Подстроенный резистор R2 необходим для выполнения процедуры балансировки модулятора, чтобы максимально подавить несущую частоту.

В контуре L3-C3 выделяется сигнал, содержащий частоты двух боковых полос. Далее происходит усиление в каскаде на VT1 и VT2 и подавление нижней и выделение верхней боковой полосы в электромеханическом фильтре Z1. Затем, еще усиление каскадом на VT3 и далее сигнал поступает на преобразователь частоты на диодах VD5-VD8.

Теперь напряжение от ГПД поступает на этот преобразователь. На выходе выделяется продукт преобразования, из которого полезный сигнал должен быть выделен контурами ФСС рабочего КВ диапазона, и подан далее на усилитель мощности передатчика.

Коэффициент усиления всего тракта при передаче устанавливается подстроенным резистором R11. При приеме установка производится переменным резистором R12. Предварительные установки соотношений коэффициентов передачи, и их зависимости изменения от регулировки данными резисторами, осуществляются подбором сопротивлений R3 и R7.

Все трансформаторы одинаковы. Сердечник каждого из них состоит из двух склеенных вместе ферритовых колец размера 7x4x3 мм из феррита 400НН. Все обмотки содержат по 12 витков провода ПЭЛШО 0,24. Наматывают трансформаторы проводом, сложенным втрое, а затем с помощью прозвонки мультиметра определяют назначение концов обмоток.

Контурные катушки намотаны на четырехсекционных каркасах от модулей ПЧЗ радиоканалов телевизоров типа УСЦТ (с экранами). Контурные катушки имеют по 72 витка (по 18 витков в секцию). Катушки связи — по 12 витков. Катушка L3 имеет отвод от 18-го витка. Провод — ПЭВ 0,12.

Контурные катушки имеют по 72 витка (по 18 витков в секцию). Катушки связи — по 12 витков. Катушка L3 имеет отвод от 18-го витка. Провод — ПЭВ 0,12.

Дроссели L1 и L6 намотаны на кольцах К7х4хЗ из феррита 400НН, содержат по 30 витков ПЭВ 0,12.

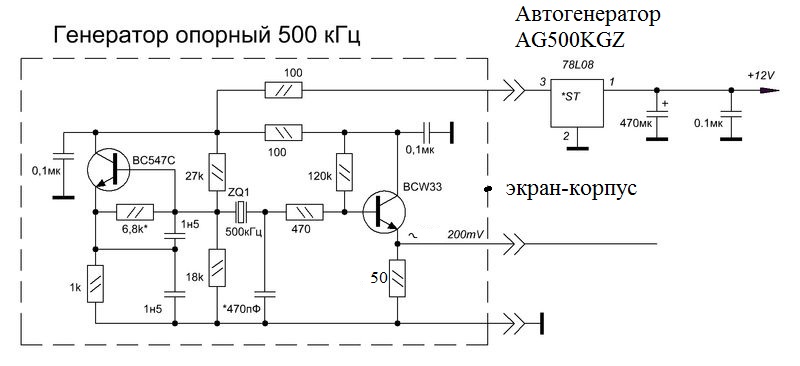

Высокостабильный генератор сигнала на транзисторе

12.12.2018

Генераторы

2741

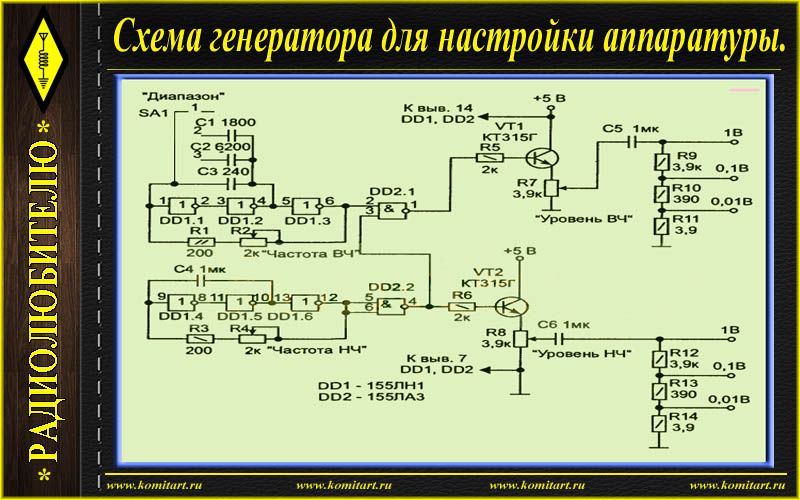

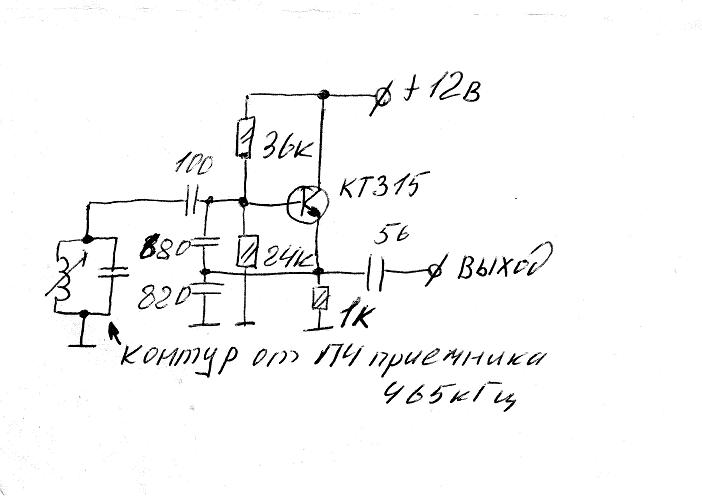

Схема высокостабильного генератора сигнала на 465 кГц (500 кГц), построенного на последовательном резонансном LC-контуре. Суточная (24 часа) нестабильность генератора не превышает 0,3 кГц. Это составляет меньше 0,1 %.

В одно время я изучал свойства параллельного и последовательного резонансных контуров. Подавая сигнал от генератора на контур с помощью осциллографа, я наблюдал сигнал на вторичной катушке индуктивности, входящей в контур. Так, на параллельном контуре присутствует как сигнал собственных колебаний контура, так и сигнал генератора. Это показывает, что параллельный контур удобно использовать в фильтрах сосредоточенной селекции, в нагрузках смесителей (преобразователей) частоты, в умножителях частоты.

В то время как на катушке последовательного контура выделяется гармонический или близкий к нему сигнал резонансной частоты контура, это не смотря на то, что на контур подавался сигнал разной формы и частоты. Поэтому я утверждаю, что последовательный контур выгодно использовать в генераторах частоты сигнала При этом частота генерации будет в большей степени зависеть от, параметров контура, и в меньшей — от характеристик транзистора.

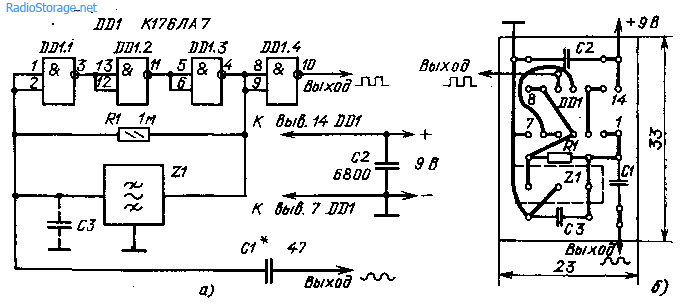

Схема электрическая принципиальная генератора приведена на рис. 1.

Схема генератора ВЧОснову генератора составляет биполярный транзистор типа КТ209И (М, Б, Д).

Конденсатор С2 — типа КТ, С1, С4 — типа КМ.

Катушка индуктивности L9, L10 — это трансформатор промежуточной частоты от радиоприемника «Селга-404». Схема выводов катушек указана на рис. 2. L9 намотана проводом ПЭВ-2 диаметром 0,10 мм и содержит 24 витка, L10 состоит из 81 витка высокочастотного провода 3×0,08 мм. Индуктивность L10 составляет 117 мкГн. Добротность катушки на частоте 465 кГц равна 90.

Индуктивность L10 составляет 117 мкГн. Добротность катушки на частоте 465 кГц равна 90.

Настройка генератора происходит следующим образом. При отключенном резисторе R4 на транзистор подается напряжение -1,50 В и с помощью R1 на коллекторе VT1 устанавливается напряжение -0,95 В. Это напряжение устанавливается из расчета: напряжение питания -1,50 В минус напряжение насыщения Ura нас, равное у КТ209 0,4 V В, и деленное на 2. Затем к коллектору VT1 подключаем частотомер. Я использовал частотомер с чувствительностью 0,5 В амплитудного напряжения сигнала.

Вместо R4 подключается потенциометр на 2,2 кОм и, постепенно уменьшая его сопротивления, добиваются появления устойчивой генерации частоты. Затем измеряют сопротивление R4 и заменяют его на постоянный резистор. После этого подключают частотомер к С5, подобрав R3. Частоту генерации сигнала 465,0 кГц подстраивают с помощью изменения индуктивности, катушки L10 и емкости конденсатоpa СЗ.

Снимать сигнал следует с катушки L9, так как из-за нелинейности входных и выходных характеристик транзистора при малом напряжении на коллекторе Ura, на R2 выделяется сигнал искаженной синусоиды.

Величина сопротивления R2 влияет на добротность LC-контура и его сопротивление можно уменьшить, увеличив добротность, однако при этом возрастает энергия, рассеиваемая на L и С контура и на коллекторе VT1. Если кого не устраивает полярность напряжения питания -1,50 В, то можно использовать транзистор КТ630Б (Д, Е) с проводимостью п-р-п.

Источник питания на 1,50 В должен быть высокостабильным для получения высокбстабильной частоты сигнала. Так, уменьшение и увеличение напряжение питания от -1,30 В и до -1,70 В приводит к изменению частоты генерации от -0,4 кГц и до +0,4 кГц от среднего значения 465,0 кГц. Напряжение питания можно выбрать 2,0 В для данной схемы (или любое в этом диапазоне напряжений).

Нестабильность частоты генератора составила за 12 часов непрерывной работы с 465,0 кГц до 465,1 кГц (+0,1 кГц). А за 24 часа непрерывной работы до 465,3 кГц, т.

Настроить генератор на частоту 500,0 кГц можно, изменив номинал С2 до 860 пФ. Предполагаю, что увеличить стабильность последовательного контура можно, подобрав С2 по температурному коэффициенту емкости. Этот генератор частоты сигнала может работать и от электрической батарейки на 1,5 В типа («R14»), но при этом высокая Стабильность частоты сигнала не гарантируется.

Этот схемой я показал принцип построения высокостабильного LC-генератора на последовательном контуре. А опытный радиолюбитель сам додумает практическую схему генератора на свою, нужную ему частоту. С катушки L9 снимается сигнал -0,70 В действующего переменного напряжения, а с R2 -0,25 В. За счет резонанса, напряжение на С2 и L10 в 10 раз превышает напряжения на контуре.

- Генератор ВЧ

Электроника | Бесплатный полнотекстовый | Генератор тактовых импульсов с несколькими выходами от 500 кГц до 150 МГц, использующий аналоговую ФАПЧ и дробный делитель без обратной связи с 0,13 мкм CMOS

1. Введение

В современных коммуникационных, сетевых и видеоустройствах используется широкий спектр процессоров, FPGA и памяти для выполнения задач и процессов, требуемых конечными приложениями [1,2]. Архитектура синхронизации в этих приложениях становится все более сложной из-за растущего уровня интеграции, необходимой в новых проектах. Чтобы удовлетворить уникальные требования для каждой аппаратной конструкции, предлагается генератор тактовых импульсов с несколькими выходами. Обеспечивая хорошую частотную гибкость, его можно применять для замены тактовых генераторов с фиксированной частотой и дискретных кварцевых генераторов.

Обычно контур фазовой автоподстройки частоты с дробным коэффициентом деления также может использоваться для удовлетворения различных требований к тактовой частоте благодаря возможности вывода на любой частоте [3,4,5]. Однако полоса пропускания PLL ограничивает максимальную скорость переключения частоты. В то время как процессору может потребоваться возможность быстрого переключения частоты для поддержки методов энергосбережения, таких как динамическое масштабирование частоты (DFS), современным многоядерным процессорам также требуются динамически регулируемые генераторы тактовой частоты для каждого ядра, которые должны обеспечивать быстрое переключение частоты без выброса частоты. и жесткие ограничения по времени установления [6,7]. Для решения этой проблемы была предложена модуляция без обратной связи. Для достижения этой цели было реализовано несколько методов, таких как многофазное переключение, линии задержки с цифровым управлением (DCDL) и преобразователь цифро-времени (DTC). Многофазная коммутация и DCDL имеют точную глубину модуляции и отличную скорость переключения, но страдают от большого детерминированного джиттера. Используя DTC с высоким разрешением, можно добиться низкого джиттера. Однако для устранения джиттера, вызванного шумом квантования, необходима дополнительная калибровочная ячейка для калибровки коэффициента усиления ДТК, что увеличивает сложность схемы [8,9].

Однако полоса пропускания PLL ограничивает максимальную скорость переключения частоты. В то время как процессору может потребоваться возможность быстрого переключения частоты для поддержки методов энергосбережения, таких как динамическое масштабирование частоты (DFS), современным многоядерным процессорам также требуются динамически регулируемые генераторы тактовой частоты для каждого ядра, которые должны обеспечивать быстрое переключение частоты без выброса частоты. и жесткие ограничения по времени установления [6,7]. Для решения этой проблемы была предложена модуляция без обратной связи. Для достижения этой цели было реализовано несколько методов, таких как многофазное переключение, линии задержки с цифровым управлением (DCDL) и преобразователь цифро-времени (DTC). Многофазная коммутация и DCDL имеют точную глубину модуляции и отличную скорость переключения, но страдают от большого детерминированного джиттера. Используя DTC с высоким разрешением, можно добиться низкого джиттера. Однако для устранения джиттера, вызванного шумом квантования, необходима дополнительная калибровочная ячейка для калибровки коэффициента усиления ДТК, что увеличивает сложность схемы [8,9]. ].

].

Без ограничения полосы пропускания делители без обратной связи имеют более быстрое переключение частоты, и можно избежать выброса частоты. Ввиду преимуществ модуляции без обратной связи предлагается новая архитектура делителя без обратной связи. Он содержит дельта-сигма модулятор первого порядка (DSM), многомодульный делитель (MMD), вычислитель фазовой ошибки и ячейку регулировки фазы. В отличие от всех вышеперечисленных цифровых методов, ячейка регулировки фазы вызывает фазовую задержку, изменяя зарядный ток конденсатора для устранения фазовой ошибки. Для сравнения, этот метод проще. Он может одновременно достигать превосходных характеристик джиттера и скорости переключения.

Остальная часть этого документа организована следующим образом. Детали дизайна этой работы представлены в Разделе 2. Результаты моделирования схем показаны и проанализированы в Разделе 3. Результаты проиллюстрированы и обсуждены в Разделе 4. Наконец, выводы сделаны в Разделе 5.

2.

Материалы и Методы

Материалы и МетодыВся архитектура генератора тактовых импульсов показана на рисунке 1. Выходной сигнал PLL может подаваться на несколько дробных делителей для получения различных выходных частот.

2.1. PLL Design

Блок-схема PLL показана на рис. 2. Поскольку PLL широко изучалась [10,11,12], здесь дано лишь краткое описание схемотехники.

Во-первых, фазово-частотный детектор (PFD) использует два D-переключателя для сравнения входных тактовых импульсов и отправляет сигналы UP и DOWN для управления ячейкой зарядового насоса. Когда оба выхода UP и DOWN становятся высокими, выход логического элемента AND одновременно будет высоким, сбрасывая оба переключателя [11]. Что касается зарядового насоса (CP) и пассивного фильтра нижних частот (LPF), они применяются для преобразования разности фаз в напряжение настройки. В то же время высокочастотный шум, возникающий от блоков перед ФНЧ, будет отфильтрован. Посредством повышающих и понижающих токов, подаваемых CP, происходит постепенное изменение напряжения настройки. Пока частота обратной связи и опорная частота не сравняются, напряжение настройки становится постоянным. В это время ГУН будет генерировать стабильные высокочастотные часы. Частота может быть задана как:

Пока частота обратной связи и опорная частота не сравняются, напряжение настройки становится постоянным. В это время ГУН будет генерировать стабильные высокочастотные часы. Частота может быть задана как:Что касается экономии средств, к PLL применяется кольцевой VCO, площадь которого меньше. На рис. 3 показана схема трехкаскадного кольцевого ГУН. Здесь, когда собственное усиление NM1 достаточно велико, входное напряжение Vc может линейно преобразовываться в ток. Тогда ток стока NM1 будет обеспечивать ток смещения для ячейки задержки через структуру токового зеркала. Кривая настройки ГУН выбирается с помощью массивов конденсаторов. Автоматическая регулировка частоты (AFC) осуществляется с помощью кода Verilog.

2.2. Конструкция дробного делителя с разомкнутым контуром

Блок-схема делителя с разомкнутым контуром, который мы использовали, показана на рисунке 4. Чтобы устранить ошибки квантования, вызванные DSM, относительная разность фаз в MMD вычисляется путем сравнения сгенерированных дроби и целого числа. DSM, и управляющий сигнал передается в ячейку регулировки фазы. Затем фаза желаемого выходного тактового сигнала будет динамически регулироваться, чтобы соответствовать идеальной форме тактового сигнала. Основываясь на этой архитектуре, каждый выходной тактовый сигнал может быть выбран для генерации любой частоты от 500 кГц до 150 МГц.

DSM, и управляющий сигнал передается в ячейку регулировки фазы. Затем фаза желаемого выходного тактового сигнала будет динамически регулироваться, чтобы соответствовать идеальной форме тактового сигнала. Основываясь на этой архитектуре, каждый выходной тактовый сигнал может быть выбран для генерации любой частоты от 500 кГц до 150 МГц.

2.2.1. Многомодульный делитель

Схема MMD показана на рис. 5. Она основана на ячейке деления на 2/3 и счетчике P [13]. P [9:0] получается из блока DSM. Выходная частота ГУН (fvco) сначала отправляется в ячейку с делением на 2/3. Если P[0] равно 0, то функция деления на 3 не работает. В противном случае, когда счетчик P уменьшается до нуля, генерируется сигнал высокого уровня Ld, который сбрасывает счетчик P и активирует функцию деления на 3. В то же время счетчик P посылает выходной сигнал деления в ячейку деления на 2. Он используется для подтверждения рабочего цикла 50%. Таким образом, коэффициент деления всегда является четным целым числом. Наконец, коэффициент деления выходной частоты можно описать как:

Наконец, коэффициент деления выходной частоты можно описать как:2.2.2. Цепи регулировки фазы

На рис. 6 показано, как добиться коэффициента деления 4,25 с помощью двухрежимного делителя 4/5. Это можно реализовать, разделив ввод на 4 для трех циклов и на 5 для одного цикла повторяющимся образом [9]. Мы обнаружили, что детерминированный джиттер был почти таким же большим, как у T IN . Для лучшего применения он должен быть как можно меньше. В результате для его улучшения были добавлены схемы регулировки фазы.

Как показано на рис. 5, схемы регулировки фазы изменяют время, когда поступает передний фронт сигнала деления счетчика P. Таким образом, фаза окончательных выходных часов может быть согласована с идеальными часами.

Конкретную реализацию можно увидеть на рис. 7. Что касается источников хвостового тока (NM1 и NM2), то имеется восемь групп, у которых коэффициенты умножения транзисторов уменьшаются кратно 2. RC-фильтр (R1, C1) был добавлен для уменьшения шум тока смещения и стабилизация напряжения затвора. Таким образом, текущие источники могут быть более точными. Переключение PM1 и NM1 управляется цифровыми схемами. Мы видим, что если PM1 включен, а NM1 выключен, то напряжение Va увеличится до VDD. После этого, если NM1 включен, напряжение Va уменьшится до прежнего значения. Время изменения Va влияет на выход счетчика P через схему логического преобразования.

Таким образом, текущие источники могут быть более точными. Переключение PM1 и NM1 управляется цифровыми схемами. Мы видим, что если PM1 включен, а NM1 выключен, то напряжение Va увеличится до VDD. После этого, если NM1 включен, напряжение Va уменьшится до прежнего значения. Время изменения Va влияет на выход счетчика P через схему логического преобразования.

Более того, чтобы лучше компенсировать детерминированный джиттер, время отключения источников тока устанавливается равным T в . В этом идеальном случае время задержки может быть выражено как:

Более того, чтобы лучше компенсировать детерминированный джиттер, время отключения источников тока устанавливается равным T в . В этом идеальном случае время задержки может быть выражено как:При расчете времени задержки, когда отключается только один ток, они могут быть перечислены как T в /2, T в /2 2 , Т в /2 3 , Т в /2 4 , Т в /2 5 , T в /2 6 , T в /2 7 и T в /2 8 90 058 по размеру. В результате лучшим фазовым разрешением можно считать T в /2 8 . Это частично определяется входной частотой. Таким образом, лучше выбрать более высокочастотный вход.

NM1 не идеальный переключатель. Это вызывает ошибки для компенсации детерминированного джиттера.

2.2.3. Калькулятор DSM и фазовой ошибки

Этот расчет также выполняется с использованием кода Verilog. В соответствии с разработанными схемами регулировки фазы выше был выбран DSM первого порядка, чтобы детерминированный джиттер не превышал T в [14]. Входной сигнал коэффициента деления состоит из 11-битного целого числа и 20-битной дроби. Коэффициент целочисленного деления (N) находится в диапазоне от 6 до 1800 с добавлением дробной части α, что дает коэффициент деления N + α. Кроме того, включен разрешенный управляющий сигнал fn_en. Это сигнал, который контролирует, включена ли функция дробного деления. Когда сигнал установлен на ноль, включается функция дробного деления. Наконец, входной тактовый сигнал генерируется из блока MMD, что обеспечивает синхронное изменение коэффициента деления.

В соответствии с разработанными схемами регулировки фазы выше был выбран DSM первого порядка, чтобы детерминированный джиттер не превышал T в [14]. Входной сигнал коэффициента деления состоит из 11-битного целого числа и 20-битной дроби. Коэффициент целочисленного деления (N) находится в диапазоне от 6 до 1800 с добавлением дробной части α, что дает коэффициент деления N + α. Кроме того, включен разрешенный управляющий сигнал fn_en. Это сигнал, который контролирует, включена ли функция дробного деления. Когда сигнал установлен на ноль, включается функция дробного деления. Наконец, входной тактовый сигнал генерируется из блока MMD, что обеспечивает синхронное изменение коэффициента деления.

Выход DSM представляет собой динамическое число, которое переключается между двумя последовательными целочисленными значениями. Он отправляется в MMD и ячейку вычислителя фазовой ошибки. Как видно, поскольку коэффициент деления переключается только между N и N + 1, детерминированный джиттер можно легко рассчитать как αT IN и (1-α)T IN . Чтобы компенсировать джиттер, необходимо было заставить схемы регулировки фазы генерировать соответственно противоположные времена задержки. Например, если числа деления меняются на N, N и N + 1, соответствующие времена задержки будут равны αT IN , αT IN и -(1-α)T IN. Для этого вычислитель динамически управляет переключателями источников тока в цепях коррекции фазовой ошибки. Здесь применяется простой алгоритм.

Чтобы компенсировать джиттер, необходимо было заставить схемы регулировки фазы генерировать соответственно противоположные времена задержки. Например, если числа деления меняются на N, N и N + 1, соответствующие времена задержки будут равны αT IN , αT IN и -(1-α)T IN. Для этого вычислитель динамически управляет переключателями источников тока в цепях коррекции фазовой ошибки. Здесь применяется простой алгоритм.

3. Результаты

3.1. Результаты моделирования

3.1.1. Диапазон настройки ГУН

Диапазон настройки и анализ фазового шума трехкаскадного кольцевого ГУН показаны на рис. 8. Целевая частота 600–900 МГц достигается за счет управления массивами переключающих конденсаторов. Комбинированные значения конденсатора и контролируемого напряжения определяют значение выходной частоты.

3.1.2. Whole Performance

На рис. 9 показаны выходные результаты тактового генератора. Для части PLL мы предоставили входную частоту 25 МГц и коэффициент деления 32. Затем, используя алгоритм AFC и процесс блокировки PLL, его выходная частота составляет 800 МГц. Для делителя без обратной связи мы устанавливаем дробное отношение равным 30,375. Затем P [9:0], который является выходом DSM, переключается между 0000001101 и 0000001110, соответствующий коэффициент деления переключается между 30 и 32, а управляющий сигнал S [7:0] и выход P счетчик меняется синхронно. Подобно рисунку 6, когда выход DSM равен 0000001101, детерминированный джиттер составляет -0,375T 9Появится 0035 в , и для его компенсации будет сгенерирована эквивалентная задержка T . Точно так же детерминированный джиттер 0,625T в будет смещен, когда на выходе DSM будет 0000001110. Наконец, можно получить выходную частоту 26,337 МГц.

Для части PLL мы предоставили входную частоту 25 МГц и коэффициент деления 32. Затем, используя алгоритм AFC и процесс блокировки PLL, его выходная частота составляет 800 МГц. Для делителя без обратной связи мы устанавливаем дробное отношение равным 30,375. Затем P [9:0], который является выходом DSM, переключается между 0000001101 и 0000001110, соответствующий коэффициент деления переключается между 30 и 32, а управляющий сигнал S [7:0] и выход P счетчик меняется синхронно. Подобно рисунку 6, когда выход DSM равен 0000001101, детерминированный джиттер составляет -0,375T 9Появится 0035 в , и для его компенсации будет сгенерирована эквивалентная задержка T . Точно так же детерминированный джиттер 0,625T в будет смещен, когда на выходе DSM будет 0000001110. Наконец, можно получить выходную частоту 26,337 МГц.

3.1.3. Скорость переключения частоты дробного делителя без обратной связи

Для проверки возможности быстрого переключения мы изменили значение N + α с 30,375 до 190,875. Результаты представлены на рис. 10. Время переключения составило менее 50 нс при частотном шаге около 28 МГц. Как только фиксированная входная частота готова, делитель может генерировать выходной сигнал и мгновенно переключаться.

Результаты представлены на рис. 10. Время переключения составило менее 50 нс при частотном шаге около 28 МГц. Как только фиксированная входная частота готова, делитель может генерировать выходной сигнал и мгновенно переключаться.

3.2. Результаты испытаний

3.2.1. Output Clock

Кварцевый генератор с частотой 27 МГц использовался в качестве эталонного входного тактового сигнала аналоговой PLL для теста. Коэффициент целочисленного деления был установлен равным 24, поэтому выходная частота PLL составляла 648 МГц. Коэффициент деления дробного делителя без обратной связи составил 15,75. В итоге были получены часы с частотой 41,14 МГц. Мы использовали осциллограф для наблюдения за формой волны, которая представлена на рисунке 11. Марка осциллографа была TEXTRONIX, а модель продукта — TBS2000B.

3.2.2. Среднеквадратичное дрожание

Как упоминалось выше, мы получили дальнейшее измерение среднеквадратичного джиттера с помощью анализатора спектра. Результат теста представлен на рисунке 12. Результаты теста среднеквадратичного джиттера. Мы видим, что несущая частота выходного тактового сигнала была около 41,14 МГц, а среднеквадратичное дрожание 5,189 пс. Кроме того, фазовый шум при отстройке 1 МГц составлял около −133 дБн/Гц. Торговая марка анализатора спектра — Agilent, а модель продукта — N9020A. Схему измерения можно увидеть в Приложении А.

Результат теста представлен на рисунке 12. Результаты теста среднеквадратичного джиттера. Мы видим, что несущая частота выходного тактового сигнала была около 41,14 МГц, а среднеквадратичное дрожание 5,189 пс. Кроме того, фазовый шум при отстройке 1 МГц составлял около −133 дБн/Гц. Торговая марка анализатора спектра — Agilent, а модель продукта — N9020A. Схему измерения можно увидеть в Приложении А.

4. Обсуждение

На рис. 13 показана фотография кристалла, на которой изображены PLL и открытый дробный делитель. Мы видим, что площадь открытого фракционного делителя составляет около 0,032 мм 2 (245 мкм × 130 мкм).

Конструкция ФАПЧ основана на трехкаскадном кольцевом ГУН. Он использует опорную частоту 27 МГц и обеспечивает выходную частоту 600–900 МГц. Затем, используя дробный делитель без обратной связи, можно получить тактовый сигнал с частотным диапазоном 500 кГц–150 МГц. Благодаря схемам регулировки фазы детерминированный джиттер DSM значительно подавляется. В таблице 1 показано сравнение этой архитектуры с другими.

В таблице 1 показано сравнение этой архитектуры с другими.

Видно, что все конструкции могут обеспечить любую выходную частоту в широком диапазоне. Однако архитектура дробного делителя без обратной связи имеет возможность мгновенного переключения. Для сравнения, архитектура Ref. [9] в целом имеет отличную производительность, и в тесте использовался внешний источник тактового сигнала со среднеквадратичным дрожанием 200 фс. Однако был добавлен блок цифровой калибровки для подавления влияния изменений процесса, напряжения и температуры, что упростило конструкцию схемы. Архитектуры Ref. [17] и ссылка. [18] используют инверторы и массивы переключающих конденсаторов в качестве ячеек задержки и потребляют большой ток. Измеренное среднеквадратичное значение джиттера в нашей работе составило около 5,2 пс, а потребляемая мощность — 7,7 мВт. Однако характеристики фазового шума PLL были плохими из-за конструктивных ограничений. В некоторой степени производительность прямого входного тактового сигнала ограничивает наилучшую производительность, которую может достичь дробный делитель без обратной связи. Кроме того, благодаря архитектуре без обратной связи полоса пропускания модуляции не ограничена. Он идеально подходит для приложений с часами с расширенным спектром (SSC). Кроме того, могут быть достигнуты превосходные электромагнитные помехи (EMI) [18]. Таким образом, мы заменим кольцевые генераторы на LC-генераторы для улучшения характеристик джиттера и добавим в будущем функцию SSC.

Кроме того, благодаря архитектуре без обратной связи полоса пропускания модуляции не ограничена. Он идеально подходит для приложений с часами с расширенным спектром (SSC). Кроме того, могут быть достигнуты превосходные электромагнитные помехи (EMI) [18]. Таким образом, мы заменим кольцевые генераторы на LC-генераторы для улучшения характеристик джиттера и добавим в будущем функцию SSC.

5. Выводы

В заключение, предлагается генератор тактовых импульсов с несколькими выходами для удовлетворения различных требований к тактовым частотам в SoC. Используя группу источников тока для зарядки конденсатора, ошибка квантования, вызванная DSM, была успешно подавлена. Эта новая архитектура делителя без обратной связи обеспечивает превосходные характеристики джиттера и мгновенное переключение частоты.

Вклады авторов

Концептуализация, JJ, YJ и YG; методология, JJ, YJ и YG; программное обеспечение, JJ; проверка, Дж.Дж. и Ю.Г.; формальный анализ, JJ; расследование, JJ; ресурсы, JJ; курирование данных, J. J. и Ю.Г.; написание — подготовка первоначального проекта, JJ; написание — обзор и редактирование, JJ; визуализация, JJ; надзор, Ю.Г. и Ю.Дж.; администрация проекта, JJ, YJ и YG; приобретение финансирования, Ю.Г. Все авторы прочитали и согласились с опубликованной версией рукописи.

J. и Ю.Г.; написание — подготовка первоначального проекта, JJ; написание — обзор и редактирование, JJ; визуализация, JJ; надзор, Ю.Г. и Ю.Дж.; администрация проекта, JJ, YJ и YG; приобретение финансирования, Ю.Г. Все авторы прочитали и согласились с опубликованной версией рукописи.

Финансирование

Это исследование не получило внешнего финансирования.

Заявление Институционального контрольного совета

Неприменимо.

Заявление об информированном согласии

Неприменимо.

Заявление о доступности данных

Неприменимо.

Конфликт интересов

Авторы заявляют об отсутствии конфликта интересов.

Приложение A

На Рисунке A1 и Рисунке A2 показана измерительная установка тактового генератора во время тестирования.

Рисунок A1. Измерение выходного тактового сигнала с помощью осциллографа.

Рисунок A1. Измерение выходного тактового сигнала с помощью осциллографа.

Рисунок A2. Измерение среднеквадратичного джиттера с помощью анализатора спектра.

Рисунок A2. Измерение среднеквадратичного джиттера с помощью анализатора спектра.

Ссылки

- Ким, Дж. Х.; Квак, Ю.Х.; Ким, М .; Ким, SW; Ким, К. КМОП-генератор тактовых импульсов на основе DLL с частотой 120–1,8 ГГц для динамического масштабирования частоты. IEEE J. Твердотельные схемы 2006 , 41, 2077–2082. [Google Scholar] [CrossRef]

- Хван, Дж.; Чон, GS; Чу, С.Х.; Ким, В .; Чон, Д.К. Программируемый генератор тактовых импульсов без кристалла с гибридным генератором RC-LC для приложений ГГц в 14-нм FinFET CMOS. В Proceedings of the BCICTS, Сан-Диего, Калифорния, США, 15–17 октября 2018 г. [Google Scholar]

- Fan, Y.; Го, Х .; Ван Р.; Чжан, З .; Ляо, Х. Маломощный цифровой PLL с дробным коэффициентом деления без калибровки и мощным линейным фазовым интерполятором. В материалах Азиатской конференции по твердотельным схемам IEEE 2016 г.

(A-SSCC), Тояма, Япония, 7–9.Ноябрь 2016 г. [Google Scholar]

(A-SSCC), Тояма, Япония, 7–9.Ноябрь 2016 г. [Google Scholar] - Джамали М.; Эбрахими, Э. Новый синтезатор частоты Fractional-N с использованием архитектуры Nested-PLL. В Proceedings of the Electrical Engineering, Тегеран, Иран, 2–4 мая 2017 г. [Google Scholar]

- Mahmoud, A.; Андреани, П .; Пинг, Л. 65-нанометровая КМОП-система цифровой ФАПЧ фракции N с формованным внутриполосным фазовым шумом. В Proceedings of the Nordic Circuits and Systems Conference (NORCAS): NORCHIP & International Symposium on System-on-Chip (SoC), 2015 г., Осло, Норвегия, 26–28 октября 2015 г. [Google Scholar]

- Аллен, А.; Десаи, Дж.; Вердико, Ф.; Андерсон, Ф.; Малвихилл, Д.; Дэн, К. Динамическая система синхронизации с переключением частоты на четырехъядерном процессоре Itanium®. В материалах конференции IEEE International Solid-State Circuits Conference-Digest of Technical Papers, Сан-Франциско, Калифорния, США, 8–12 февраля 2009 г.

[Google Scholar]

[Google Scholar] - Tierno, J.; Рыляков, А.; Фридман, Д.; Чен, А .; Stawiasz, K. Генератор тактовых импульсов с переменной частотой для каждого ядра на основе DPLL для восьмиядерного микропроцессора POWER7. In Proceedings of the VLSI Circuits (VLSIC), 2010 IEEE Symposium on, Гонолулу, Гавайи, США, 16–18 июня 2010 г. [Google Scholar]

- Де Каро, Д.; Тесситоре, Ф.; Вай, Г.; Императо, Н.; Петра, Н.; Неаполь, Э.; Паррелла, К.; Стролло, А.Г.М. Генератор тактовых импульсов с расширенным спектром 3,3 ГГц, поддерживающий прерывистую частотную модуляцию в 28-нм КМОП. IEEE J. Твердотельные схемы 2015 , 50, 2074–2089. [Google Scholar] [CrossRef]

- Эльхолы А.; Саксена, С.; Шу, Г.; Эльшазлы, А .; Ханумолу, П.К. Многоканальный полностью цифровой генератор тактовых импульсов с малым джиттером, использующий дробные делители разомкнутого контура на основе DTC. IEEE J. Твердотельные схемы 2018 , 53, 1806–1817.

[Google Scholar] [CrossRef]

[Google Scholar] [CrossRef] - Суман, С.; Шарма, К.Г.; Гош, П.К. Анализ и проектирование кольцевого ГУН с недостаточным током. В материалах Международной конференции по электротехнике, электронике и методам оптимизации (ICEEOT)-2016, Майсуру, Индия, 9–10 декабря 2016 г. [Google Scholar]

- Мишра, А.; Шарма, Г.К.; Булчандани, Д. Анализ производительности конструкции системы ФАПЧ с оптимальной мощностью с использованием пятикаскадного CS-VCO на длине волны 180 нм. В материалах Международной конференции по распространению сигналов и компьютерным технологиям, Аджмер, Индия, 12–13 июля 2014 г. [Google Scholar]

- Бласко, Г.; Изерн, Э.; Мартин, Э. Разработка стабильной системы генератора импульсов на основе кольцевого ГУН с фазовой автоподстройкой частоты с использованием 180-нм КМОП-технологии. В Proceedings of the Design of Circuits & Integrated Systems, Estoril, Portugal, 25–27 ноября 2016 г. [Google Scholar]

- «> Elkholy, A.; Саксена, С.; Нандвана, Р.К.; Эльшазлы, А .; Ханумолу, П.К. Широкополосная кольцевая цифровая система ФАПЧ с дробным коэффициентом деления 2,0–5,5 ГГц с многомодульным делителем расширенного диапазона. IEEE J. Твердотельные схемы 2016 , 51, 1771–1784. [Google Scholar] [CrossRef]

- Райли, T.A.D.; Коупленд, М.А. Дельта-сигма модуляция в синтезе частот с дробным коэффициентом деления. IEEE J. Твердотельные схемы 1993 , 28, 553–559. [Google Scholar] [CrossRef][Green Version]

- Xu, X.; Ри, В .; Ван, З. Гибридная система ФАПЧ с дробным коэффициентом деления и без смещения по току с малым числом побочных импульсов для генерации тактовых импульсов низкого напряжения. В материалах Международного симпозиума IEEE по схемам и системам (ISCAS) 2020 г., Севилья, Испания, 12–14 октября 2020 г. [Google Scholar]

- Де Каро, Д.; Романи, Калифорния; Петра, Н.; Стролло, AGM; Паррелла, К. 1,27 ГГц, полностью цифровой генератор/синтезатор тактовых импульсов с расширенным спектром на 65-нм CMOS.

IEEE J. Твердотельные схемы 2010 , 45, 1048–1060. [Google Scholar] [CrossRef]

IEEE J. Твердотельные схемы 2010 , 45, 1048–1060. [Google Scholar] [CrossRef] - Хо, Ю.-Х.; Яо, С.-Ю. Полностью цифровой цикл с задержкой быстрого сбора данных, использующий алгоритм предсказания начального бита для регистра последовательного приближения. IEEE транс. Интеграл очень большого масштаба. (СБИС) Сист. 2016 , 24, 759–763. [Google Scholar] [CrossRef]

- Эльхолы А.; Эльшазлы, А .; Саксена, С.; Шу, Г.; Ханумолу, П.К. Полностью цифровой генератор тактовых импульсов с реконфигурируемым многовыходным тактовым генератором с частотой от 20 до 1000 МГц ± 14 пс с размахом джиттера, использующий дробные делители с разомкнутым контуром в 65-нм CMOS. В Proceedings of the Solid-State Circuits Conference Digest of Technical Papers (ISSCC), IEEE International 2014, Сан-Франциско, Калифорния, США, 9–13 февраля 2014 г. [Google Scholar]

Рисунок 1. Вся архитектура тактового генератора.

Рисунок 1. Вся архитектура тактового генератора.

Вся архитектура тактового генератора.

Рисунок 2. Блок-схема PLL.

Рисунок 2. Блок-схема PLL.

Рисунок 3. Схема VCO.

Рисунок 3. Схема VCO.

Рисунок 4. Блок-схема делителя без обратной связи.

Рисунок 4. Блок-схема делителя без обратной связи.

Рисунок 5. Схема ММД.

Рисунок 5. Схема ММД.

Рисунок 6. Блок-схемы и временные диаграммы дробного делителя.

Рисунок 6. Блок-схемы и временные диаграммы дробного делителя.

Рисунок 7. Схема фазорегулирующей цепи.

Рисунок 7. Схема фазорегулирующей цепи.

Рисунок 8. Диапазон перестройки ГУН.

Рисунок 8. Диапазон перестройки ГУН.

Рисунок 9. Вывод результатов тактового генератора.

Рисунок 9. Вывод результатов тактового генератора.

Рисунок 10. Результаты моделирования переключения частоты.

Рисунок 10. Результаты моделирования переключения частоты.

Рисунок 11. Схема выходных часов.

Рисунок 11. Схема выходных часов.

Рисунок 12. Результаты тестирования среднеквадратичного джиттера.

Рисунок 12. Результаты тестирования среднеквадратичного джиттера.

Рисунок 13. Умереть фотография.

Рис. 13. Умереть фотография.

Таблица 1. Резюме и сравнение с разными статьями.

Таблица 1. Резюме и сравнение с разными статьями.

| [9] | [15] | [16] | [17] | Эта работа 1 | |

|---|---|---|---|---|---|

| Архитектура | Дробная-N Делитель (DTC) | Дробная-N PLL | Дробная-N Делитель (DCDL) | Задержка — замкнутый цикл (DCDL) | Дробный делитель N (аналоговый фазорегулирующая ячейка) |

| Технология (нм) | 65 | 65 | 65 | 180 | 130 | 90 381

| Питание (В) | 0,9 | 0,65 | 1,2 | 1,8 | 1,2 |

| Входная частота (МГц) | 5000 | 60 | 1270 | NA 903 86 | 600–900 |

| Выходная частота (МГц) | 20–1000 | 1000–1500 | 180–1270 | 60–1100 | 0,5–150 |

| Среднеквадратичное дрожание (пс) | 1,44 | 14,0 | 12,8 | 1,4 | 5,2 |

| Мгновенное переключение | Да | Нет | Да | Нет | Да |

| Потребляемая мощность | 3,2 мВт | 1 0,85 мВт | 19,8 мВт | 23 мВт | 7,7 мВт |

| Площадь (мм 2 ) | 0,017 | 0,23 | 0,044 | 0,066 | 0,032 |

1 При сравнении питания, потребляемой мощности и площади учитывался только делитель без обратной связи.

Примечание издателя: MDPI остается нейтральным в отношении юрисдикционных претензий в опубликованных картах и институциональной принадлежности. |

© 2022 авторами. Лицензиат MDPI, Базель, Швейцария. Эта статья находится в открытом доступе и распространяется на условиях лицензии Creative Commons Attribution (CC BY) (https://creativecommons.org/licenses/by/4.0/).

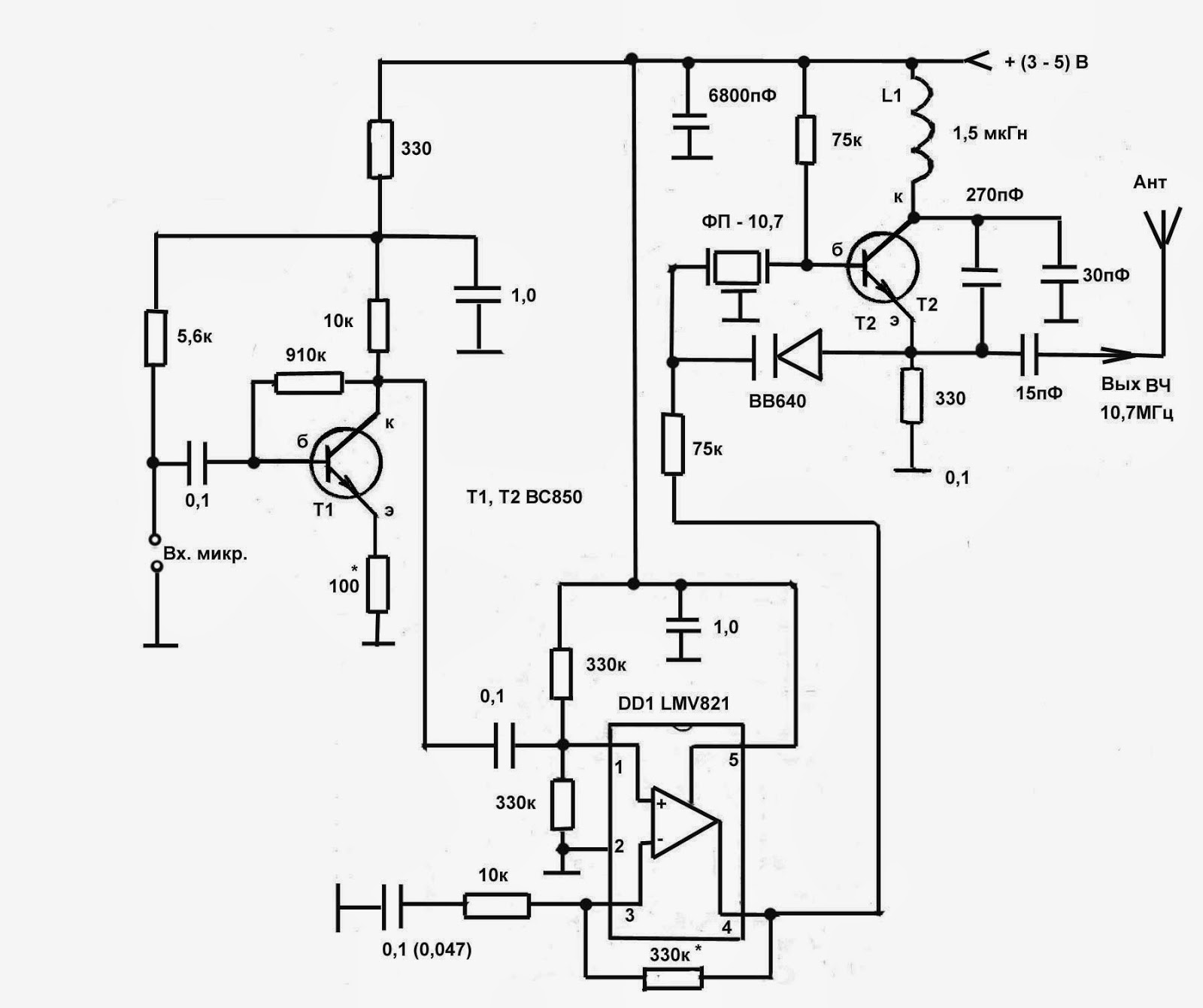

Цепь генератора опорной частоты от 1 Гц до 1 МГц

Вы здесь: Главная / Мини-проекты / Схема генератора опорной частоты от 1 Гц до 1 МГц

Искать на этом веб-сайте вы можете использовать в многочисленных приложениях для тестирования частоты и периода времени. В первую очередь он хорошо подходит для генератора стробирующих импульсов в счетчиках частоты.

Схема способна генерировать весь диапазон опорных частот, таких как 1 Гц, 5 Гц, 10 Гц, 50 Гц, 100 Гц, 500 Гц, 1 кГц, 5 кГц, 10 кГц, 50 кГц, 100 кГц, 500 Гц. кГц, 1 МГц

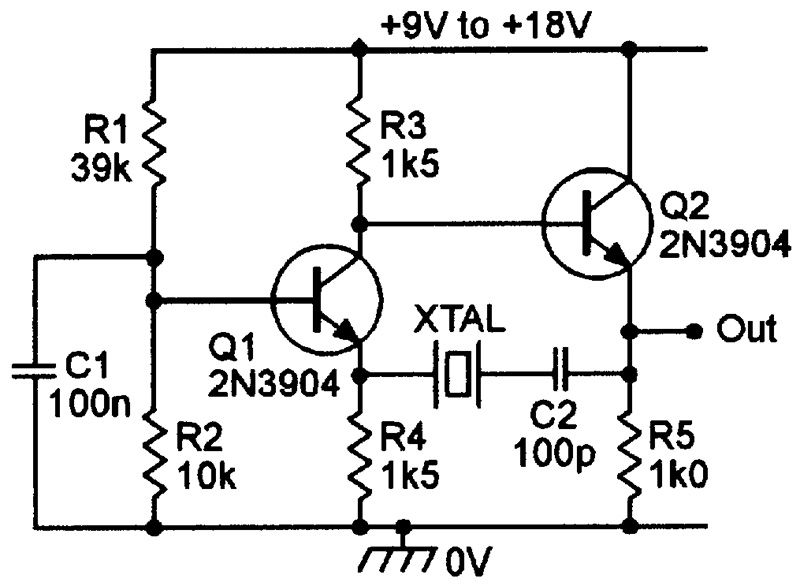

В основе схемы лежит кварцевый генератор с частотой 1 МГц, сконфигурированный с использованием пары вентилей И-НЕ.

Третий логический элемент И-НЕ действует как буфер на выходе этого генератора, выходной сигнал которого делится вниз на число 7490 декадных счетчиков.

Они включают в себя этап деления на 2, сопровождаемый этапом деления на 5, который предполагает, что наряду с делением опорной частоты до 1 Гц в декадах сигналы 500 кГц и более низкие значения до 5 Гц также доступный.

Все эти сигналы особенно полезны, когда необходимы стробирующие импульсы для подсчета частоты. Например, выход 5 Гц даст вам положительные импульсы шириной 100 мс, таким образом, когда проверяется частота сигнала 10 МГц, стробирующий импульс такой длины может позволить передать 11 500 000 циклов сигнала на счетчик, представляя дисплей 10,00000.

В качестве альтернативы, для расчета времени более выгодны выходы от 1 Гц до 1 МГц. Например, при вычислении интервала в одну секунду можно измерить 1 000 000 циклов выходного сигнала с частотой 1 МГц, что дает отображение 10001300.

Дизайн печатной платы

Дизайн и структура печатной платы очень обтекаемы и эффектно представлены. Выходы доступны через нижний край схемы компоновки платы. В комплекте, предназначенном для генератора, имеется один дополнительный вентиль И-НЕ, который можно использовать в качестве вентиля в приложениях для измерения частоты.

Выходы доступны через нижний край схемы компоновки платы. В комплекте, предназначенном для генератора, имеется один дополнительный вентиль И-НЕ, который можно использовать в качестве вентиля в приложениях для измерения частоты.

Контакты проводки к этому вводятся в правом верхнем углу платы. Частоту генератора можно было настроить точно до 1 МГц с помощью подстроечного конденсатора.

Идеальный способ сделать это — использовать осциллограф для проверки выхода 100 кГц с приемом Дройтвича 200 кГц и применить фигуру Лиссажу. Триммер, естественно, нужно подстраивать до тех пор, пока число Лиссажу не перестанет вращаться.

Эта прецизионная схема развертки, управляемая кварцевым генератором, построена с использованием общедоступных КМОП-ИС и недорогого кварцевого резонатора. Эта схема предоставляет пользователю конфигурации для получения 50 Гц, 100 Гц или 200 Гц. Эталонная частота 50 Гц обычно может применяться в качестве базы времени для калибровки электронных часов, частотомеров и многих других устройств. IC1 состоит из генератора и делителя на 20.

IC1 состоит из генератора и делителя на 20.

Если предположить, что контур генератора точно откалиброван с помощью C2, выходной сигнал на контакте 3 (Q14) будет генерировать прямоугольный сигнал частотой 200 Гц. При использовании двух триггеров от IC2 rge результирующее напряжение прямоугольной формы последовательно делится на 2, а затем на 4, что дает пару дополнительных выходных сигналов 100 Гц и 50 Гц.

Как откалибровать

50 Гц, генерируемые контактом 1. Любители, имеющие измеритель частоты, могут легко откалибровать эту схему генератора временной развертки с кварцевым управлением, просто подключив измеритель к контакту 7 IC1 (Q4) и подстроив C2. до тех пор, пока на счетчике не появится индикация 204,800 Гц. Любопытно, что любой пользователь, у которого нет частотомера, вероятно, не должен падать духом, потому что регулировки триммера C2 примерно в центральной точке может быть достаточно, чтобы получить достаточную точность для большинства приложений.

Выход 100 Гц удобен для разработки цифровых счетчиков.