Как устроен инвертор сигнала на транзисторе. Какие типы транзисторов используются для создания инверторов. Каковы основные схемы инверторов на биполярных и полевых транзисторах. В чем преимущества и недостатки различных схем инверторов.

Принцип работы инвертора сигнала на транзисторе

Инвертор — это базовый логический элемент, выполняющий операцию логического отрицания (инверсии). Его выходной сигнал всегда противоположен входному. Простейший инвертор можно реализовать на одном транзисторе.

Принцип работы транзисторного инвертора основан на использовании ключевого режима работы транзистора. В этом режиме транзистор может находиться в двух состояниях:

- Закрытом — сопротивление между коллектором и эмиттером очень велико

- Открытом — сопротивление между коллектором и эмиттером мало

Переключение между этими состояниями осуществляется подачей управляющего сигнала на базу (для биполярного транзистора) или затвор (для полевого транзистора).

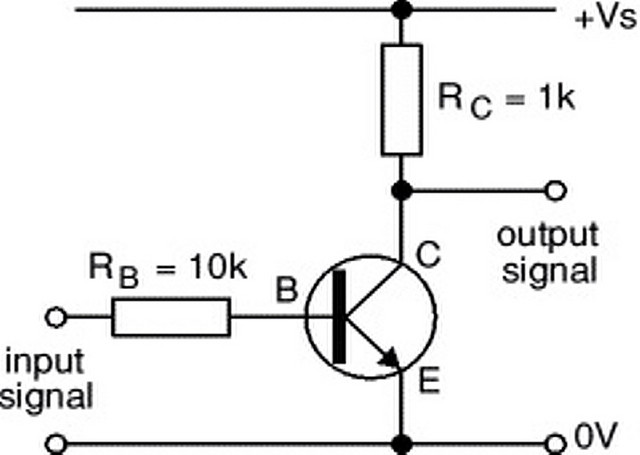

Простейшая схема инвертора на биполярном транзисторе

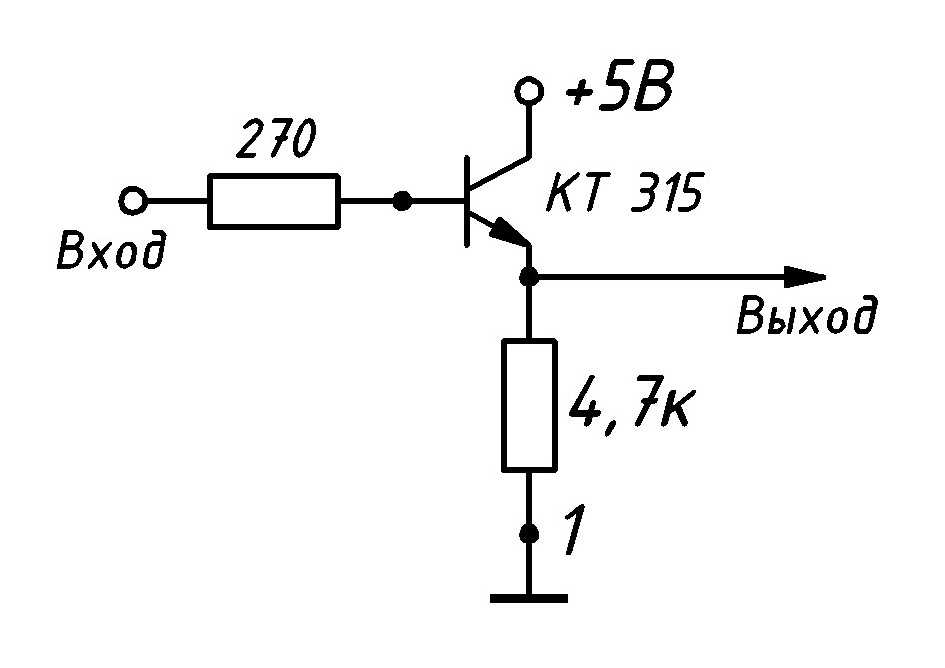

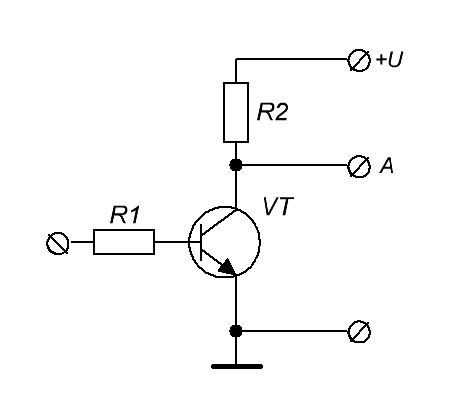

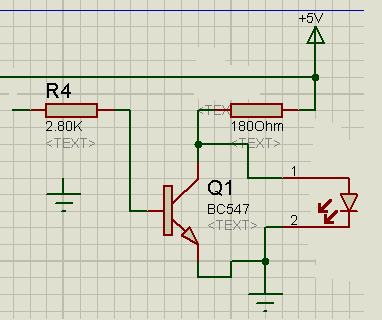

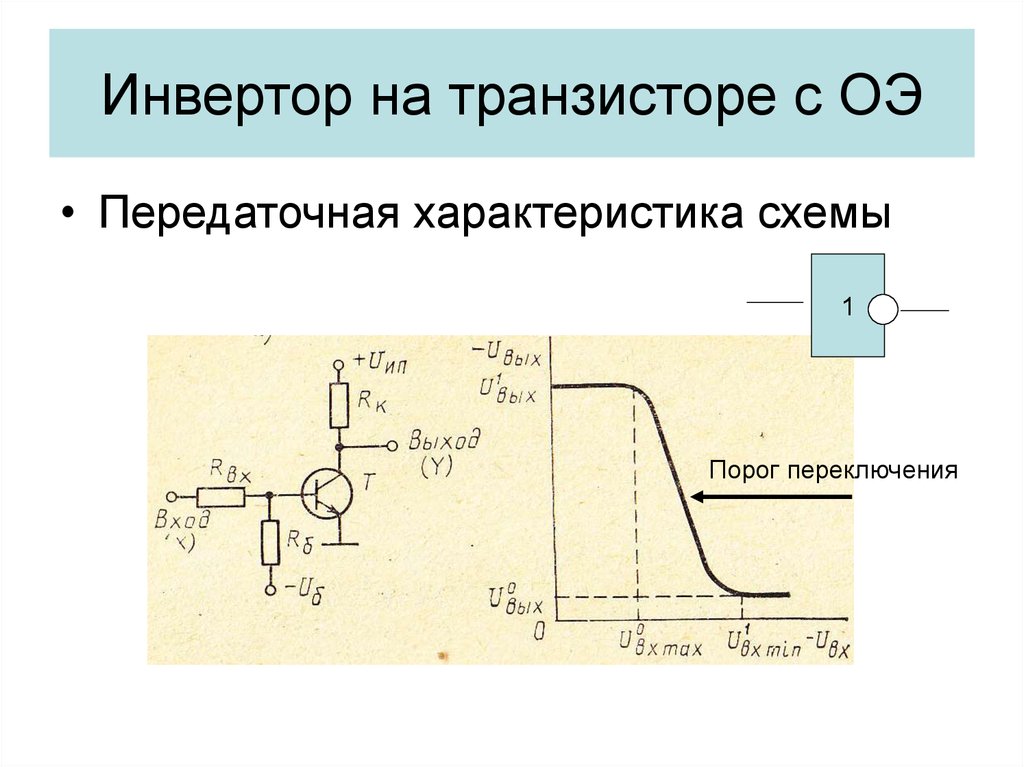

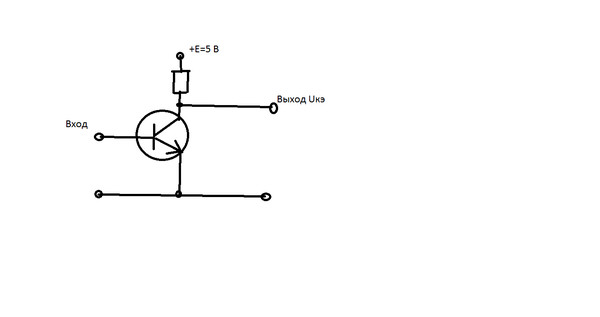

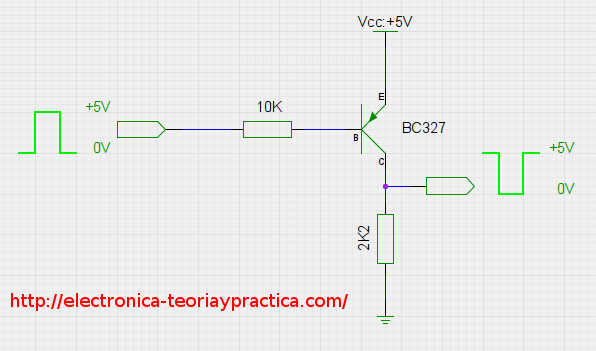

Рассмотрим принципиальную схему простейшего инвертора на биполярном n-p-n транзисторе:

«` «`Принцип работы этой схемы:

- Когда на входе низкий уровень (логический 0), транзистор закрыт. Ток через него не течет, напряжение на выходе близко к напряжению питания Vcc (логическая 1).

- При подаче на вход высокого уровня (логическая 1) транзистор открывается. Через него протекает ток, создавая падение напряжения на резисторе R. Напряжение на выходе становится близким к нулю (логический 0).

Таким образом, выходной сигнал всегда инвертирован относительно входного.

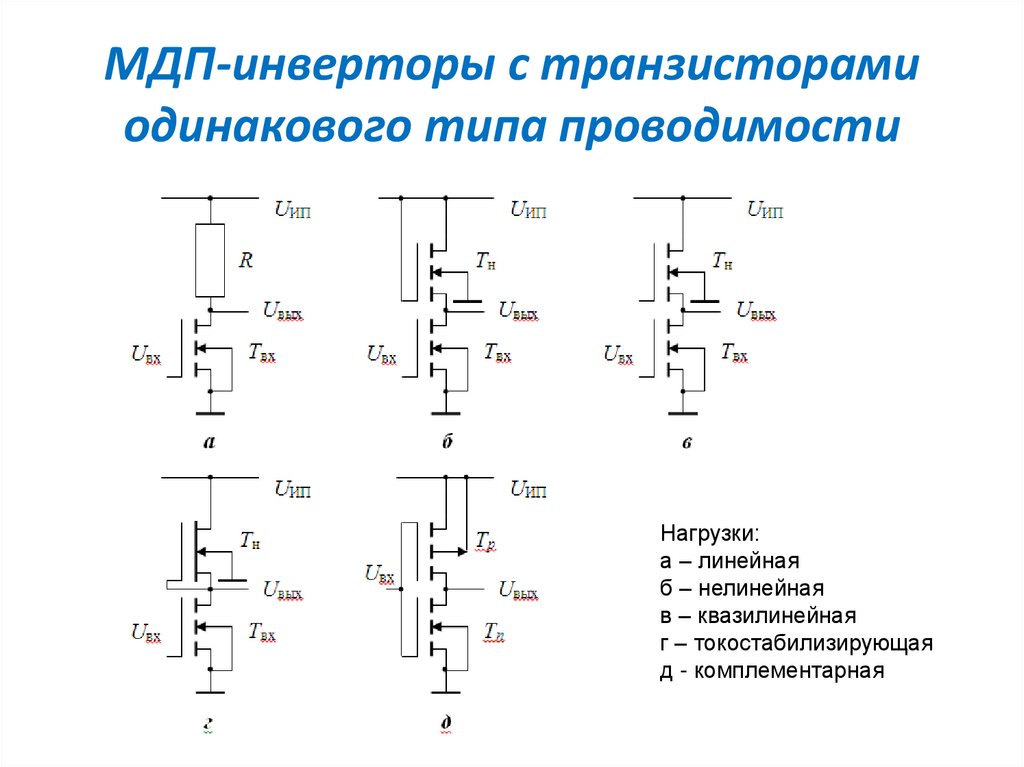

Инверторы на полевых транзисторах

Более эффективными являются инверторы на полевых МОП-транзисторах (MOSFET). Они обладают меньшим энергопотреблением, особенно в статическом режиме. Рассмотрим схему КМОП-инвертора:

Принцип работы КМОП-инвертора:

- При низком входном уровне p-канальный транзистор открыт, а n-канальный закрыт. Выход соединяется с шиной питания, формируя высокий уровень.

- При высоком входном уровне p-канальный транзистор закрыт, а n-канальный открыт. Выход соединяется с общим проводом, формируя низкий уровень.

Преимущества КМОП-инвертора:

- Очень низкое энергопотребление в статическом режиме

- Высокая помехоустойчивость

- Широкий диапазон напряжений питания

Применение инверторов в цифровых схемах

Инверторы являются базовыми элементами цифровой электроники и широко применяются в различных устройствах:

- Формирование логических сигналов

- Усиление и восстановление формы импульсных сигналов

- Построение более сложных логических элементов (И-НЕ, ИЛИ-НЕ и др.)

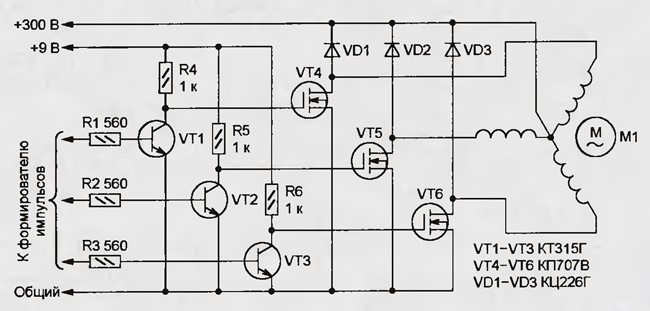

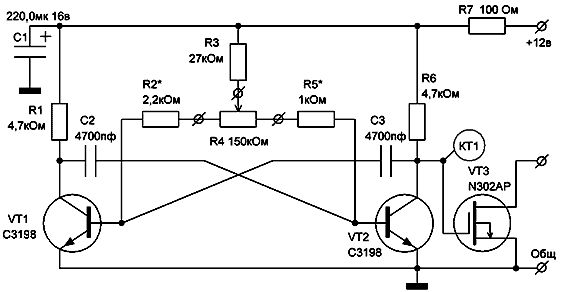

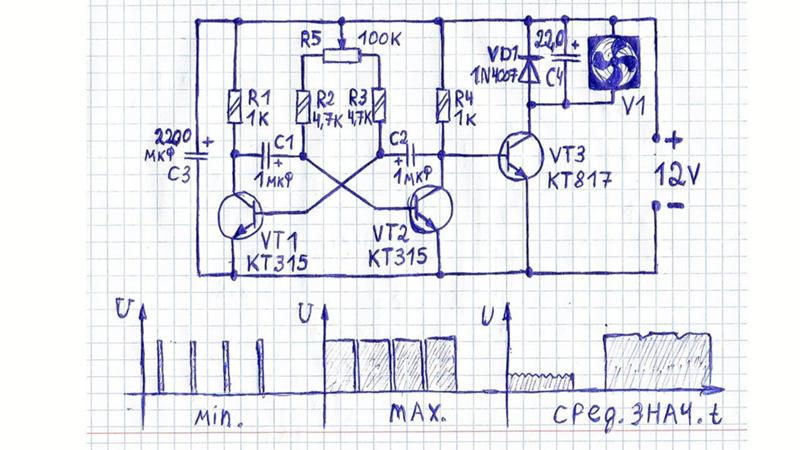

- Создание генераторов и мультивибраторов

- Реализация запоминающих элементов (триггеров)

На основе инверторов строятся практически все цифровые устройства — от простейших логических схем до сложных микропроцессоров.

Характеристики реальных инверторов

Реальные инверторы отличаются от идеальных рядом параметров:

- Задержка распространения сигнала

- Пороговое напряжение переключения

- Выходное сопротивление

- Помехоустойчивость

- Быстродействие

- Энергопотребление

Эти параметры необходимо учитывать при проектировании цифровых устройств. Выбор конкретного типа инвертора зависит от требований к разрабатываемой схеме.

Особенности инверторов в интегральном исполнении

В современной электронике инверторы обычно используются в составе интегральных микросхем. Это позволяет значительно улучшить их характеристики:

- Уменьшить размеры

- Снизить энергопотребление

- Повысить быстродействие

- Улучшить согласование параметров

- Увеличить надежность

Интегральные инверторы входят в состав различных логических серий микросхем, например:

- ТТЛ (транзисторно-транзисторная логика)

- КМОП (комплементарная МОП-структура)

- ЭСЛ (эмиттерно-связанная логика)

Каждая серия имеет свои особенности и область применения.

Моделирование работы инвертора

Для анализа работы инвертора удобно использовать компьютерное моделирование. Рассмотрим простую модель КМОП-инвертора в программе симуляции электронных схем:

«`

import React, { useState } from ‘react’;

const InverterModel = () => {

const [input, setInput] = useState(false);

const toggleInput = () =>

«`

import React, { useState } from ‘react’;

const InverterModel = () => {

const [input, setInput] = useState(false);

const toggleInput = () =>Модель КМОП-инвертора

Эта модель наглядно демонстрирует основной принцип работы инвертора — инверсию входного сигнала. При нажатии на кнопку входа выходной сигнал всегда меняется на противоположный.

Перспективы развития инверторов

Развитие технологий микроэлектроники приводит к постоянному совершенствованию инверторов:- Уменьшение размеров транзисторов позволяет повысить плотность интеграции и быстродействие

- Новые материалы (например, графен) могут значительно улучшить характеристики

- Квантовые эффекты открывают возможности для создания принципиально новых типов инверторов

- Оптические и спиновые инверторы могут стать основой для создания сверхбыстродействующих вычислительных устройств

Несмотря на свою простоту, инверторы остаются ключевыми элементами цифровой электроники и продолжают развиваться вместе с ней.

Логическая схема НЕ

В реальных инверторах присутствует несколько транзисторов, благодаря которым коэффициент усиления по напряжению может быть увеличен в максимальной степени. Это необходимо для обеспечения достаточного напряжения на выходном транзисторе, чтобы он гарантированно находится либо в режиме отсечки, либо в режиме насыщения.

Кроме того в реальных инверторах присутствуют дополнительные элементы, предотвращающие возможный выход схемы из строя. Показанный в этой статье инвертор на одном транзисторе слишком примитивен, чтобы его можно было использовать в практических целях. Ниже показана принципиальная схема инвертора со всеми компонентами, необходимыми для обеспечения его стабильной и надёжной работы:

Схема состоит из резисторов и биполярных транзисторов. Следует отметить, что выполнять функцию логической схемы НЕ могут и другие схемы, включая и такие, в которых вместо биполярных транзисторов используются полевые транзисторы.

Давайте проанализируем работу этой схемы при сигнале высокого логического уровня на её входе. Мы можем смоделировать эту ситуацию, если изобразим на входе схемы переключатель, через который схема соединена с линией питания V cc:

В этом случае диод D1 будет прямосмещён, а следовательно не будет проводить ток. В действительности, единственная причина, по которой в схеме используется D1 — это необходимость защиты транзистора в том случае, если на вход будет подано отрицательное напряжение (по отношению к земле). При отсутствии напряжения между базой и эмиттером транзистора Q1, ток на нём будет также отсутствовать. Однако в приведённой схеме транзистор Q1 используется в необычной функции. В действительности, транзистор Q1 используется в качестве пары встречно-включённых диодов. На следующей схеме показана реальная функция транзистора Q1:

Назначение этих диодов заключается в том, чтобы подавать ток на базу транзистора Q2 или же отводить его от базы этого транзистора в зависимости от логического уровня на входе.

Допустим, что у нас имеется следующая диодно-резисторная схема, представляющая переходы база-эмиттер транзисторов Q2 и Q4 в виде отдельных диодов (все остальные элементы схемы можно опустить и сконцентрировать внимание на способе «направления» тока двумя встречно-включёнными диодами):

Когда переключатель переведён в «верхнее» положение (соединён с линией Vcc), должно быть очевидно, что на левом диоде транзистора Q1 ток будет отсутствовать, поскольку отсутствует напряжение в цепи переключатель-диод-R1-переключатель. Однако, ток будет на правом диоде транзистора Q1, а также на переходе база-эмиттер Q2 и переходе база-эмиттер Q4:

Таким образом, мы можем сделать вывод, что в реальной логической схеме, на транзисторах Q2 и Q4будет ток базы, в связи с чем на них будет также присутствовать ток коллектора. Общее падение напряжения между базой Q1 (узлом, соединяющим два встречно-включённых диода) и землёй будет примерно равно 2,1 В, что соответствует падению напряжения трёх pn-переходов: правый диод, диод база-эмиттер Q2 и диод база-эмиттер Q4.

Общее падение напряжения между базой Q1 (узлом, соединяющим два встречно-включённых диода) и землёй будет примерно равно 2,1 В, что соответствует падению напряжения трёх pn-переходов: правый диод, диод база-эмиттер Q2 и диод база-эмиттер Q4.

Теперь давайте посмотрим, что произойдёт, если перевести переключатель в «нижнее» положение:

Если бы мы измерили ток этой схемы, то мы бы обнаружили, что весь ток проходит через левый диод Q1, а на правом диоде ток отсутствует. Почему же в этой цепи будет отсутствовать ток, несмотря на то, что все ещё существует полный путь для тока через диод Q4, диод Q2, правый диод пары и R1?

Вы конечно помните, что pn-переходы плоскостных диодов не проявляют линейных характеристик: они не проводят до тех пор, пока приложенное прямое напряжение не достигнет определённого минимального уровня, примерно 0,7 В для кремниевых и 0,3 В для германиевых диодов. А затем, когда они начинают проводить, падение напряжения на них не превышает 0,7 В. Когда переключатель нашей схемы переведён в «нижнее» положение, левый диод проводит и падение напряжения на нём составляет 0,7 В.

А затем, когда они начинают проводить, падение напряжения на них не превышает 0,7 В. Когда переключатель нашей схемы переведён в «нижнее» положение, левый диод проводит и падение напряжения на нём составляет 0,7 В.

Вспомним, что при переключателе в «верхнем» положении (транзисторы Q2 и Q4 проводят), падение напряжения между двумя этими точками (база Q1 и земля) составляет 2,1 В, что является минимальным напряжением, необходимым для прямого смещения трёх последовательно включённых кремниевых pn-переходов. Напряжение 0,7 В, обеспечиваемое прямым падением напряжения на левом диоде, просто недостаточно для того, чтобы ток протекал по последовательной цепи правого диода, диода Q2, и параллельной части схемы R3//Q4, поэтому в этой части схемы ток будет отсутствовать. При отсутствии тока на базах транзисторов Q2 или Q4, на них также будет отсутствовать ток коллектора: транзисторы Q2 и Q4 будут находиться в состоянии отсечки.

Таким образом, приведённая конфигурация позволяет на 100 процентов переключать ток базы транзистора Q2 (а следовательно и управлять всей схемой, включая напряжение на выходе) посредством управления направлением движения тока на левом диоде.

Если вернуться к нашей изначальной схеме, то мы увидим, что высокий логический уровень на входе поддерживается переключателем (соединённым с линией Vcc), при этом левый диод не проводит (падение напряжения 0 В.) Тем не менее, правый диод проводит ток на базу Q2 через резистор R1:

При наличии тока базы, транзистор Q2 будет включён. Более того, он будет находиться в режиме насыщения, поскольку резистор R1 будет обеспечивать более чем достаточный ток на его базе. Если транзистор Q2 находится в режиме насыщения, падение напряжения на резисторе R3 будет достаточным, чтобы обеспечить прямое смещение перехода база-эмиттер транзистора Q4, что также приведёт к его насыщению:

Если транзистор Q4 находится в состоянии насыщения, то его выход будет практически напрямую соединён с землёй, то есть напряжение на его выходе будет (по отношению к земле) равно почти 0 вольт, что соответствует уровню логического нуля. Благодаря диоду D2, между базой и эмиттером Q3 будет недостаточное напряжение для того, чтобы он был открыт, а следовательно он будет находиться в режиме отсечки.

Благодаря диоду D2, между базой и эмиттером Q3 будет недостаточное напряжение для того, чтобы он был открыт, а следовательно он будет находиться в режиме отсечки.

Давайте теперь посмотрим, что произойдёт, если мы поменяем логический уровень на ноль, путём перевода переключателя в другое положение:

Теперь будет ток на левом диоде транзистора Q1 и отсутствовать ток на правом диоде: Это устраняет ток базы Q2, вследствие чего этот транзистор будет отключён. Когда отключён транзистор Q2, отсутствует путь для тока базы транзистора Q4, и следовательно транзистор Q4 также перейдёт в состояние отсечки. Транзистор Q3, с другой стороны, будет иметь достаточное напряжение между базой и землёй для прямого смещения перехода база-эмиттер и перехода в состояние насыщения, следовательно на его выходе будет напряжение, соответствующее высокому логическому уровню. В действительности, выходное напряжение будет лежать приблизительно на уровне 4 В в зависимости от степени насыщения и тока нагрузки, однако этого достаточно для обеспечения высокого логического уровня.

Теперь работа схемы рассмотрена полностью: логическая единица даёт на выходе ноль и наоборот.

Проницательный наблюдатель обратит внимание на то, что состояние с плавающим входом (когда он не соединён ни с Vcc, ни с землёй), будет восприниматься схемой как высокий логический уровень на входе. Когда вход не соединён ни с линией питания, ни с общей линией, на левом диоде Q1 ток будет отсутствовать, при этом весь ток R1 будет поступать на базу Q2, что приведёт к насыщению транзистора Q2, а следовательно на выходе будет напряжение низкого логического уровня:

Такая ситуация свойственна для всех логических схем подобного типа, называемых Транзисторно Транзисторными Логическими, схемами или ТТЛ-схемами. Вместе с тем, из этой ситуации можно извлечь выгоду и упростить выход схемы, поскольку очень часто сигналы с выходов логических схем обычно подаются на другие схемы. Если плавающий вход воспринимается ТТЛ-схемой как состояние высокого логического уровень, то выход любой логической схемы, сигнал с которого поступает на вход ТТЛ-схемы, должен лишь обеспечивать путь к земле для низкого логического уровня и быть плавающим для получения высокого логического уровня. Эту концепцию стоит объяснить подробнее.

Эту концепцию стоит объяснить подробнее.

Логическая схема, как мы уже проанализировали, может пропускать ток в двух направлениях. Технически, это называется вытекающим и втекающим током. Когда на выходе схемы высокий логический уровень, ток протекает с выхода на Vcc через верхний выходной транзистор (Q3), что позволяет току протекать от земли через нагрузку к выходу схемы, через эмиттер Q3, и наконец, наверх к Vcc (плюс источника питания):

Чтобы упростить эту концепцию, мы можем изобразить выход схемы в виде переключателя на два направления, который может соединять выход либо с линией Vcc, либо с землёй, в зависимости от своего состояния. Если на выходе схемы высокий логический уровень, то комбинация транзисторов Q3 в насыщении и Q4 в режиме отсечки аналогична переключателю на два направления в положении «Vcc», что открывает току путь через заземлённую нагрузку:

Имейте ввиду, что переключатель на два направления, показанный внутри условного обозначения схемы представлен транзисторами Q3 и Q4, попеременно соединяющими выход схемы с линией Vcc или землёй, а не показанным ранее переключателем, подающим входной сигнал.

И наоборот, когда на выходе схемы низкий логический уровень, подаваемый на нагрузку, схема подобна переключателю на два направления установленному в положение «земля». Когда нагрузка соединена с Vcc , ток будет течь в другом направлении: с земли, через эмиттер транзистора Q4, через выход схемы, нагрузку и обратно на линию Vcc. В этом состоянии ток будет втекающим:

Комбинация из транзисторов Q3 и Q4, работающих по двутактной схеме (так называемый выходной двухтранзисторный каскад) может либо проводить ток к линии Vcc, либо проводить его с общей линии к нагрузке. Тем не менее, на вход стандартной ТТЛ-схемы поступает только втекающий ток. То есть, мы знаем, что при плавающем входе, ТТЛ-схема воспринимает это состояние как высокий логический уровень, а следовательно любой сигнал должен лишь обеспечивать логический ноль (втекающий ток):

Следовательно мы можем упростить выходной каскад логической схемы и полностью устранить транзистор Q3. В результате мы получим выход с открытым коллектором:

В результате мы получим выход с открытым коллектором:

Для обозначения выхода с открытым коллектором используется оособый знак внутри стандартного условного обозначения. Здесь показано условное обозначение инвертора с выходом с открытым коллектором:

Следует помнить, что высокий логический уровень по умолчанию при плавающем входе верен только в случае ТТЛ-схем, и не обязателен для схем других типов, особенно для логических схем на полевых транзисторах.

· РЕЗЮМЕ:

· Инвертор, или логическая схема НЕ инвертирует логический уровень входного сигнала. То есть, сигнал логического нуля на входе инвертируется в сигнал логической единицы на выходе, и наоборот.

· Схемы, подобные приведённой в этой статье, и состоящие из резисторов и биполярных транзисторов называются ТТЛ-схемами. ТТЛ — сокращение от транзисторно-транзисторная логика. Существуют также логические схемы на полевых транзисторах.

· Ток логической схемы называется вытекающим, когда он течёт между выходом схемы и положительной линией питания (Vcc). Другими словами, в таком варианте выход схемы соединён с источником питания (+V).

Другими словами, в таком варианте выход схемы соединён с источником питания (+V).

· Ток логической схемы называется втекающим, когда он течёт между выходом схемы и общей линией питания. Другими словами, выход схемы соединён с землёй.

· Если в логической схеме используется каскадный выход, то она может включаться как в разрыв положительной, так и общей линии питания. Логические схемы с выходом с открытым коллектором могут быть включены только в разрыв общей линии питания. Схемы с открытым коллектором применяются в тех случаях, когда выходной сигнал подаётся на вход другой ТТЛ-схемы, поскольку ТТЛ-схемам не требуется вытекающий ток.

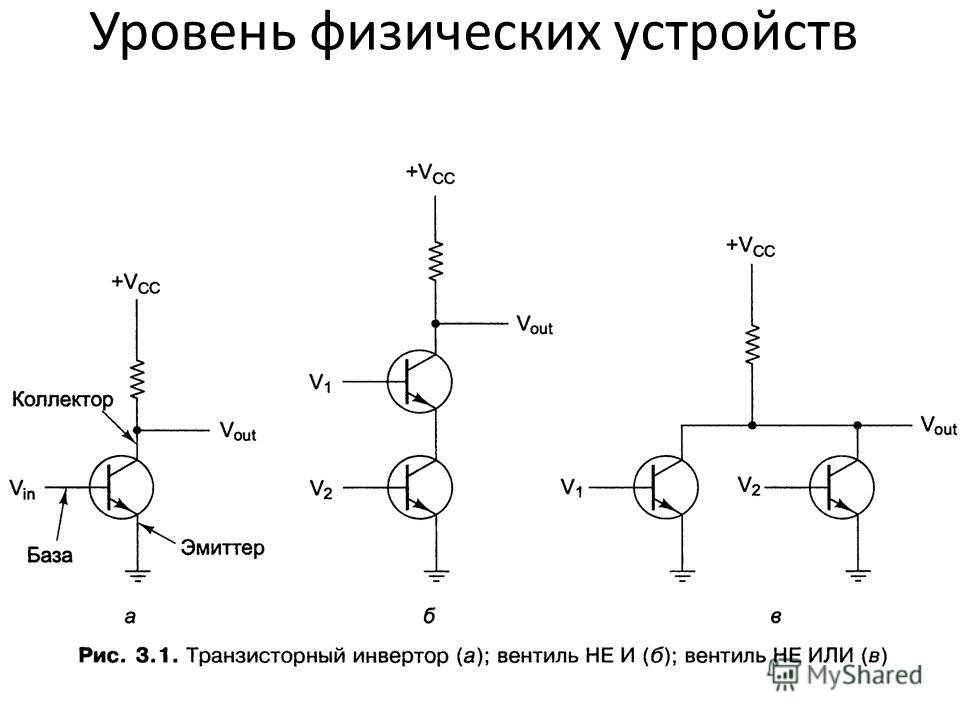

1. Схемотехника цифровых устройств

1. Схемотехника цифровых устройствВ основе цифровой электроники лежит использование ключевых режимов работы полупроводниковых приборов. В таком режиме полупроводниковый транзистор может рассматриваться как устройство, сопротивление между двумя электродами которого управляется третьим электродом, причем в одном из состояний сопротивление близко к нулю (ключ замкнут), а в другом – бесконечно велико (ключ разомкнут). Механическая модель транзистора показана на рис.1.1.

Механическая модель транзистора показана на рис.1.1.

Рис.1.1. Механическая модель транзистора.

Из подобных элементов может быть построена схема, состояние которой может быть описано двумя уровнями напряжения – низким и высоким. С целью увеличения помехоустойчивости для каждого уровня выбирается некоторый диапазон значений напряжения, обеспечивающий устойчивое считывание состояния цифрового выхода входами других цифровых узлов (рис.1.2)

Рис.1.2. Логические уровни в цифровых устройствах.

Напряжения, меньшие некоторого минимального значения U0, трактуются как логическая величина «ноль», а большие некоторого U1 – как «логическая единица». Напряжение питания естественным образом ограничивает диапазон возможных значений напряжения – нижним пределом логического нуля является нулевое напряжение, а верхним пределом логической единицы – напряжение питания. Таким образом, с помощью значений напряжения можно представить простейшие сигналы, принимающие только два значения. Однако кроме передачи логического уровня, требуется и преобразование сигналов, что также обеспечивается полупроводниковыми устройствами.

Однако кроме передачи логического уровня, требуется и преобразование сигналов, что также обеспечивается полупроводниковыми устройствами.

Рис. 1.3. Простейший инвертор на биполярном транзисторе.

На рис.1.3. изображена упрощенная схема инвертора на биполярном транзисторе. Принцип работы данной схемы можно понять, если учесть, что при наличии тока базы транзистор уменьшает сопротивление между выводами эмиттера и коллектора («открывается»), а при отсутствии – увеличивает («закрывается»). Резисторы R1 и R2 служат для ограничения тока базы, а R3 ограничивает максимальный ток коллектора. Теперь, если на вход данной схемы будет подано напряжение, соответствующее логической единице, управляющий ток базы откроет транзистор, и сопротивление между эмиттером и коллектором резко уменьшится. Следовательно, напряжение на коллекторе будет близко к нулю. Если же напряжение на входе будет близко к нулю, ток базы будет слишком мал для открывания транзистора, и напряжение на коллекторе будет определяться током, протекающим от источника питания через резистор R3. Таким образом, логический уровень на выходе данной схемы всегда противоположен логическому уровню на ее входе. Такое устройство и называется инвертором.

Таким образом, логический уровень на выходе данной схемы всегда противоположен логическому уровню на ее входе. Такое устройство и называется инвертором.

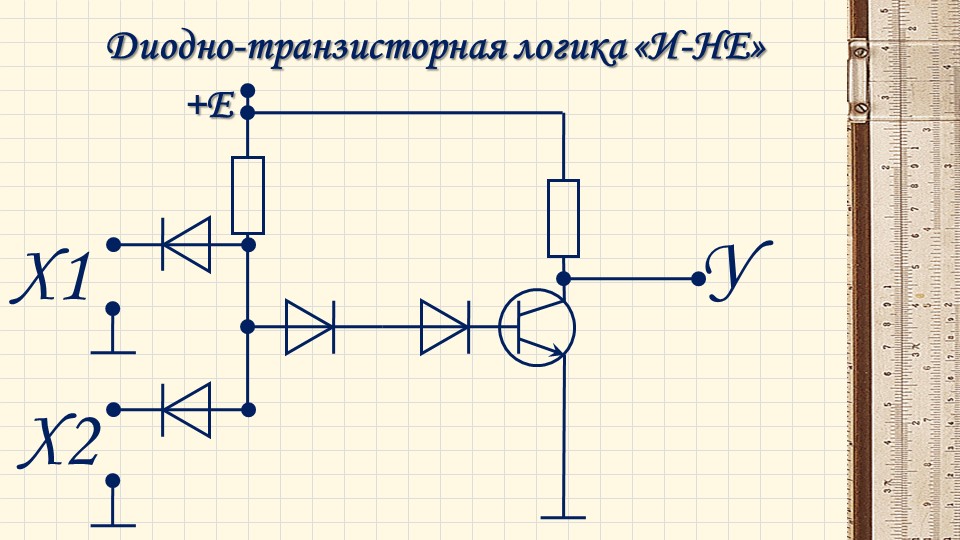

Показанная на рис.1.3. схема является сильно упрощенной и не соответствует схемотехнике промышленных цифровых микросхем. Тем не менее, она позволяет ознакомиться с принципом использования биполярных транзисторов для создания цифровых схем. В реальных устройствах используется первичное преобразование электрических сигналов, которое обычно также выполняется с помощью транзисторов. Вследствие этого одна из наиболее распространенных архитектур цифровых систем носит название «транзисторно-транзисторная логика», или ТТЛ. Такое название отражает тот факт, что транзисторы используются как для первичного преобразования сигналов, так и для формирования выходного напряжения. Предшественниками такой архитектуры являются резисторно-транзисторная (показанная на рис.1.3) и диодно-транзисторная логика.

Существенным недостатком микросхем ТТЛ является наличие статического потребления – для удержания биполярного транзистора в открытом состоянии требуется протекание постоянного тока базы, поэтому использование биполярных транзисторов в цифровых устройствах ограничено максимальной рассеиваемой мощностью.

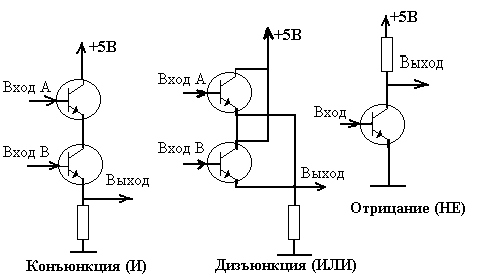

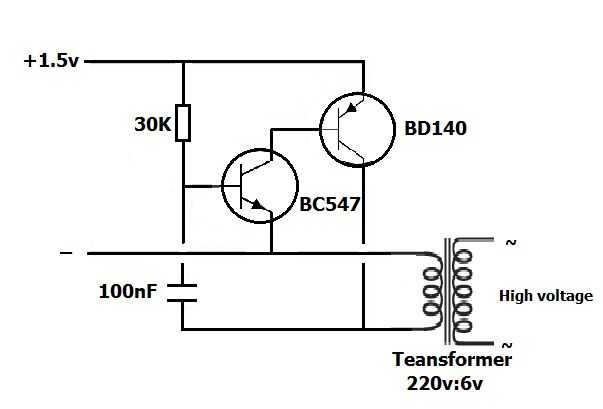

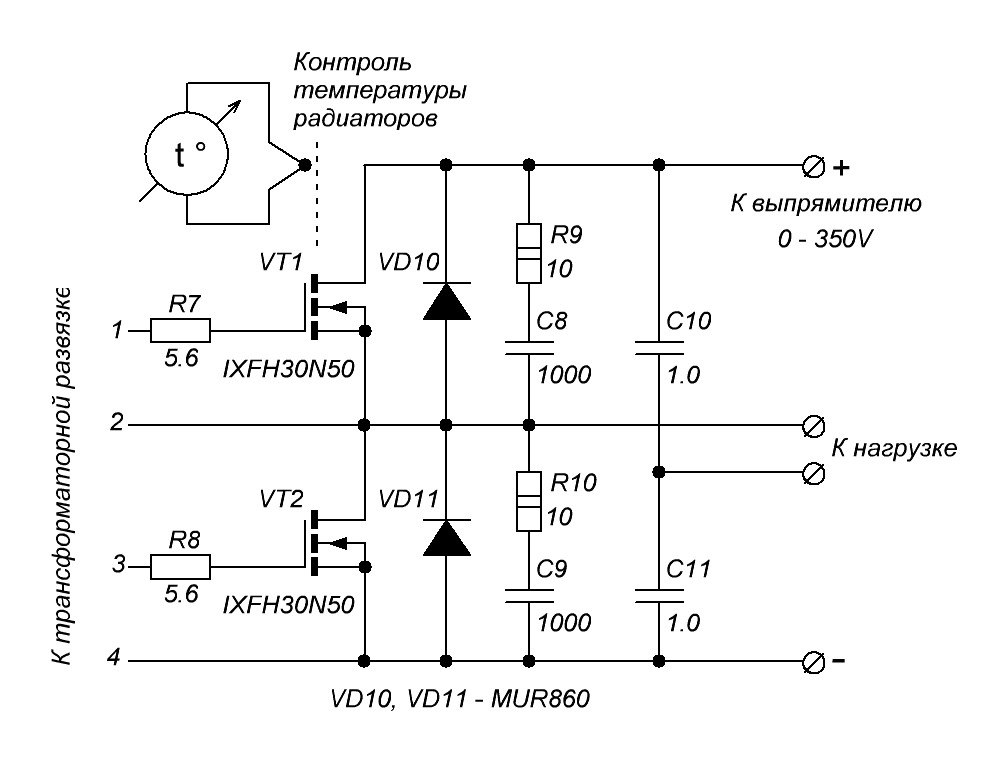

Альтернативным вариантом является построение цифровых устройств на полевых транзисторах, которые управляются потенциалом затвора и не требуют постоянного протекания управляющего тока. Удобнее использовать полевые транзисторы, выполненные по технологии «металл-окисел-полупроводник», МОП. В зависимости от типа проводимости канала такие транзисторы могут открываться либо низким логическим уровнем (транзисторы с p-каналом), либо высоким (транзисторы с n-каналом). Использование транзисторов, аналогичных по характеристикам, но имеющих разный тип проводимости канала (комплементарных, т.е. «дополняющих») позволяет реализовать эффективный инвертор (рис.1.4.).

Рис.1.4. Принципиальная электрическая схема инвертора КМОП.

На схеме рис.1.4. верхний транзистор открывается при низком логическом уровне, подключая к выходу напряжение питания (т.е. обеспечивая высокий уровень выходного напряжения). При высоком входном уровне верхний транзистор закрывается, а нижний – открывается и подключает к выходу уровень нуля. Статическое потребление такой схемы определяется утечками тока через слой диэлектрика между затвором и каналом, т.е. весьма мало. Большую роль играет так называемое динамическое потребление: в процессе переключения входного напряжения существует период времени, в течение которого оба транзистора обладают конечным сопротивлением, и наблюдается протекание тока через оба канала (в статическом состоянии один из транзисторов почти полностью открыт, а другой – почти полностью закрыт). При этом мощность, потребляемая схемами КМОП, оказывается приблизительно пропорциональной частоте переключения внутренних сигналов.

Статическое потребление такой схемы определяется утечками тока через слой диэлектрика между затвором и каналом, т.е. весьма мало. Большую роль играет так называемое динамическое потребление: в процессе переключения входного напряжения существует период времени, в течение которого оба транзистора обладают конечным сопротивлением, и наблюдается протекание тока через оба канала (в статическом состоянии один из транзисторов почти полностью открыт, а другой – почти полностью закрыт). При этом мощность, потребляемая схемами КМОП, оказывается приблизительно пропорциональной частоте переключения внутренних сигналов.

Приведенные выше сведения о схемотехнике цифровых устройств являются сильно упрощенными и не отражают целый ряд вопросов. Например, уменьшение норм технологического процесса и размеров транзисторов приводит к тому, что сопротивление диэлектрика между затвором и каналом также уменьшается, что приводит к резкому росту утечек тока. Не рассмотрено также поведение транзисторных ключей в динамическом режиме, подключение нагрузки к выходам, особенности технологических процессов изготовления цифровых устройств и многое другое. Для подробного изучения схемотехники цифровых элементов следует обратиться к специальной литературе.

Для подробного изучения схемотехники цифровых элементов следует обратиться к специальной литературе.

Инвертор не является единственным устройством для преобразования логических сигналов. Более того, интерес представляют как раз не одновходовые, а многовходовые устройства, позволяющие сформировать сигнал, представляющий собой сложную функцию от состояния входов. Набор базовых логических элементов представлен на рис. 1.5.

Рис. 1.5. Базовые логические элементы: логическое НЕ (инвертор), логическое И, логическое ИЛИ. Верхний ряд – изображение по IEEE, нижний ряд – по ЕСКД.

Логические элементы называются также вентилями (в англоязычной литературе gate). Необходимо обратить внимание, что таким же термином обозначается затвор полевого транзистора, хотя смысловая нагрузка в этих случаях различна.

Удобным способом описания работы логических вентилей является составление таблиц истинности. В такую таблицу записывается состояние выхода в зависимости от комбинации входных сигналов. Для элементов, показанных на рис. 1.5., таблицы истинности будут выглядеть следующим образом.

Для элементов, показанных на рис. 1.5., таблицы истинности будут выглядеть следующим образом.

Таблица 1.1.

Таблицы истинности для базовых логических элементов

|

Элемент НЕ | |

|

A |

Q |

|

0 |

1 |

|

1 |

0 |

|

Элемент И |

|

Элемент ИЛИ |

||||

|

A |

B |

Q |

A |

B |

Q |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

|

|

0 |

1 |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

0 |

1 |

0 |

1 |

|

|

1 |

1 |

1 |

1 |

1 |

1 |

|

Число входов для логических элементов Ии ИЛИ может быть больше двух. При этом сохраняется принцип работы, показанный в таблице 1.1: на выходе элемента И логическая 1 появляется только в том случае, если все входы находятся в состоянии логической 1 («И на первом, И на втором, И на третьем…»), а для появления логической 1 на выходе элемента ИЛИ достаточно наличия логической 1 хотя бы на одном из его входов. Имея двухвходовые логические элементы, можно создать такой же элемент с числом входов больше двух, соединяя одинаковые элементы последовательно, как это показано на рис.1.6.

При этом сохраняется принцип работы, показанный в таблице 1.1: на выходе элемента И логическая 1 появляется только в том случае, если все входы находятся в состоянии логической 1 («И на первом, И на втором, И на третьем…»), а для появления логической 1 на выходе элемента ИЛИ достаточно наличия логической 1 хотя бы на одном из его входов. Имея двухвходовые логические элементы, можно создать такой же элемент с числом входов больше двух, соединяя одинаковые элементы последовательно, как это показано на рис.1.6.

С помощью базовых логических элементов можно формировать и более сложные схемы, которые будут описываться сложными таблицами истинности. Для упрощения построения таких схем вводятся вспомогательные логические элементы. Основными их разновидностями являются: вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ, схемы И-НЕ, ИЛИ-НЕ. Графические обозначения этих вентилей показаны на рис. 1.7., а таблицы истинности приведены в табл.1.2.

Рис. 1.7. Вспомогательные логические элементы: ИСКЛЮЧАЩЕЕ ИЛИ, И-НЕ, ИЛИ-НЕ. Верхний ряд – изображение по IEEE, нижний ряд – по ЕСКД.

Верхний ряд – изображение по IEEE, нижний ряд – по ЕСКД.

Таблица 1.2.

Таблицы истинности для вспомогательных логических элементов

|

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ | ||

|

A |

B |

Q |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

|

Элемент И-НЕ |

|

Элемент ИЛИ-НЕ |

||||

|

A |

B |

Q |

A |

B |

Q |

|

|

0 |

0 |

1 |

0 |

0 |

1 |

|

|

0 |

1 |

1 |

0 |

1 |

0 |

|

|

1 |

0 |

1 |

1 |

0 |

0 |

|

|

1 |

1 |

0 |

1 |

1 |

0 |

|

Из табл. 1.2. видно, что элемент ИСКЛЮЧАЩЕЕ ИЛИ формирует на выходе логическую 1, когда логические уровни на его входах различны. Его можно также рассматривать как элемент ИЛИ, за исключением состояния «оба входа равны 1».

1.2. видно, что элемент ИСКЛЮЧАЩЕЕ ИЛИ формирует на выходе логическую 1, когда логические уровни на его входах различны. Его можно также рассматривать как элемент ИЛИ, за исключением состояния «оба входа равны 1».

Элементы И-НЕ и ИЛИ-НЕ могут быть получены путем последовательного соединения элементов И, НЕ и ИЛИ, НЕ соответственно. Для упрощения графического изображения символ инверсии (небольшой кружок) размещают непосредственно на выходе такого элемента. Часто в обозначении элемента указывается и число его входов. Например, 3ИЛИ соответствует трехвходовому элементу ИЛИ.

Символы инверсии могут быть размещены и на входах логических элементов. В этом случае их работу необходимо анализировать так, как если бы сигнал на этот вход подавался через элемент НЕ.

Рассмотрим двухвходовой элемент И-НЕ (2И-НЕ). Если объединить его входы, то таблицу истинности можно представить следующим образом.

Таблица 1.3.

Таблицы истинности для элемента 2И-НЕ с объединенными входами

|

A |

B |

Q |

|

0 |

0 |

1 |

|

1 |

1 |

0 |

Из этой таблицы следует, что элемент 2И-НЕ в данном случае выполняет функцию инвертора.

Соединив элементы 2И-НЕ и инвертор, созданный из такого же элемента с объединенными входами, получаем элемент 2И. Обращаясь к рис.1.6., убеждаемся, что теперь можно получить элемент И с произвольным числом входов.

Наконец, вводя инверторы для входных сигналов, получаем следующую таблицу истинности (в скобках показаны значения инвертированных сигналов, которые в действительно воспринимаются элементом 2И-НЕ).

Таблица 1.4.

Таблицы истинности для элемента 2И-НЕ с инвертированными входами

|

Элемент 2И-НЕ с инвертированными входами | ||

|

A |

B |

Q |

|

0 (1) |

0 (1) |

0 |

|

0 (1) |

1 (0) |

1 |

|

1 (0) |

0 (1) |

1 |

|

1 (0) |

1 (0) |

1 |

Итак, для элемента 2И логическая единица на выходе должна появиться только в том случае, если оба сигнала, стоящие в скобках, равны 1. В остальных случаях на выходе присутствует логический ноль. С учетом инвертора, стоящего на выходе, получаем результаты, показанные в табл.1.4. Нетрудно убедиться, что они соответствуют логике работы элемента 2ИЛИ.

В остальных случаях на выходе присутствует логический ноль. С учетом инвертора, стоящего на выходе, получаем результаты, показанные в табл.1.4. Нетрудно убедиться, что они соответствуют логике работы элемента 2ИЛИ.

Таким образом, имея достаточное количество элементов 2И-НЕ, можно реализовать любой из элементов И, ИЛИ, НЕ. Поэтому элемент 2И-НЕ может выступать в роли некоторого эквивалента сложности комбинаторной схемы. Аналогичные рассуждения можно провести и для элемента 2ИЛИ-НЕ, с помощью которого также реализуются любые схемы комбинаторной логики. Элементы 2И-НЕ (называемый также базисом Шеффера) и 2ИЛИ-НЕ (базис Пирса) являются так называемыми эквивалентными логическими вентилями (equivalentlogicgates), с помощью которых можно оценить сложность того или иного цифрового устройства.

Особенностью работы представленных логических элементов является то, что соответствующий таблице истинности сигнал на их выходе появляется с незначительной задержкой относительно смены состояний на входе. Эта задержка обусловлена только процессами переключения элементов схемы и при рассмотрении идеальных элементов считается, что она равна нулю. Таким образом, изменение уровня выходного сигнала может произойти в любой момент времени, поэтому такие схемы относят к классу асинхронных. Однако более точным названием, отражающим использование логических вентилей, состояние которых определяется только уровнем входного сигнала, является термин «комбинаторная логика» (combinatory). Действительно, для точного определения состояния выхода такой схемы достаточно знать комбинацию состояний ее входов. При этом предыстория их изменений не играет роли. Существуют также устройства, состояние которых может также измениться в любой момент времени, но определяется не только текущим состоянием входов, но и историей изменения этих состояний.

Эта задержка обусловлена только процессами переключения элементов схемы и при рассмотрении идеальных элементов считается, что она равна нулю. Таким образом, изменение уровня выходного сигнала может произойти в любой момент времени, поэтому такие схемы относят к классу асинхронных. Однако более точным названием, отражающим использование логических вентилей, состояние которых определяется только уровнем входного сигнала, является термин «комбинаторная логика» (combinatory). Действительно, для точного определения состояния выхода такой схемы достаточно знать комбинацию состояний ее входов. При этом предыстория их изменений не играет роли. Существуют также устройства, состояние которых может также измениться в любой момент времени, но определяется не только текущим состоянием входов, но и историей изменения этих состояний.

На базе устройств комбинаторной логики возможно решение многих задач вычислительной техники. В частности, с их помощью производится выполнение базовых арифметических операций.

Рассмотрим операцию сложения, выполняемую над числами, представленными в двоичной системе счисления. В этой системе возможны всего четыре варианта: 0 + 0 = 0, 0 + 1 = 1, 1 + 0 = 1, 1+1=10 (210). Для представления числа 2, которое в двоичном виде запишется как 10, требуется уже два разряда.

Запишем таблицу истинности для элемента, устанавливающего выход в соответствии с младшим разрядом результата сложения двух чисел, представленных в двоичной системе.

Таблица 1.5.

Таблица истинности одноразрядного сумматора.

|

Результат сложения чисел A и B | ||

|

A |

B |

Q |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

В последнем случае в таблице записан ноль, поскольку произошел перенос в следующий разряд. Из таблицы видно, что операция сложения реализуется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ.

Из таблицы видно, что операция сложения реализуется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ.

Для представления числа, переносимого в следующий разряд, потребуется еще один выход. Нетрудно убедиться, что значение этого выхода равно 1 только в том случае, когда оба входа равны 1 – сигнал переноса, таким образом, формируется элементом И.

При сложении многоразрядных двоичных чисел необходимо учитывать сигналы переноса, приходящие из предыдущих разрядов, и формировать такие сигналы для последующих разрядов. С учетом сигнала переноса, каждый элемент сумматора, начиная со второго, должен иметь три входа вместо двух. Обозначим вход переноса как Cin, а выход как Cout и составим таблицу истинности для такого блока.

Таблица 1.6.

Таблица истинности одного разряда многоразрядного сумматора.

|

A |

B |

Cin |

Q |

Cout |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

При составлении таблицы истинности использовалось свойство коммутативности сложения: поскольку порядок слагаемых не влияет на результат, можно ориентироваться на то, что нечетное число единиц в трех входных сигналах обуславливает появление единицы на выходе Q, а выход Cout принимает значение 1 в тех случаях, когда два или три входа находятся в состоянии единицы. Можно подобрать несколько вариантов реализации устройства комбинаторной логики, реализующего сложение.

Можно подобрать несколько вариантов реализации устройства комбинаторной логики, реализующего сложение.

Рис. 1.8. Многоразрядный сумматор.

Элементы комбинаторной логики реализуются цифровыми микросхемами малой степени интеграции. Это серии 155, 555, 1533 и др. российского производства и их аналоги 74xx, выполненные по технологии ТТЛ, а также КМОП-устройства серий 176, 561 и 54xx соответственно. В составе этих серий присутствует большое количество элементов рассмотренных выше типов с различным числом входов.

Немаловажным является тот факт, что заданная таблица истинности может быть в общем случае получена более чем одним способом соединения стандартных микросхем комбинаторной логики. Эти способы могут отличаться различным числом используемых вентилей, корпусов микросхем, суммарными задержками распространения сигналов и т.п. Поэтому при использовании дискретных микросхем комбинаторной логики весьма важной является задача получения схемотехнического решения, минимизирующего число использованных корпусов и/или наименований микросхем, для чего используются приемы эквивалентного преобразования логических выражений, подробно описанные в специальной литературе. С развитием технологии изготовления интегральных микросхем, а особенно с учетом возможностей микросхем программируемой логики, рассматриваемых в данном курсе, вопросы минимизации схем комбинаторной логики существенно теряют актуальность, поскольку, как будет подробно рассмотрено в последующих главах, в программируемых микросхемах с архитектурой FPGA занимаемый объем и вносимые задержки зависят только от числа входов комбинаторной схемы, но не от вида реализуемой функции.

С развитием технологии изготовления интегральных микросхем, а особенно с учетом возможностей микросхем программируемой логики, рассматриваемых в данном курсе, вопросы минимизации схем комбинаторной логики существенно теряют актуальность, поскольку, как будет подробно рассмотрено в последующих главах, в программируемых микросхемах с архитектурой FPGA занимаемый объем и вносимые задержки зависят только от числа входов комбинаторной схемы, но не от вида реализуемой функции.

В противоположность асинхронным, синхронные цифровые устройства изменяют состояние выходных сигналов в строго определенные моменты времени. Эти моменты, как правило, соответствуют положительному перепаду специального синхронизирующего сигнала, называемого проще тактовым сигналом. Для описания работы синхронных устройств может использоваться такое представление, как временные диаграммы работы. Они представляют собой графики зависимости логических уровней от времени, на которых показывают типичные комбинации и события (перепады уровня) на входных линиях, а также соответствующие изменения выходных сигналов. Базовым синхронным элементом является D-триггер. Его графическое изображение и временные диаграммы работы показаны на рис. 1.9.

Базовым синхронным элементом является D-триггер. Его графическое изображение и временные диаграммы работы показаны на рис. 1.9.

Рис. 1.9 Графическое изображение и временные диаграммы работы D-триггера.

На рис.1.9. видно, что выход триггера Q принимает то же состояние, что было на входе данных D, в момент положительного перепада (фронта) тактового сигнала. В остальные моменты времени изменения логического уровня на входе D никак не влияют на состояние выхода. Такое поведение позволяет, в частности, использовать D-триггер в качестве устройства хранения данных. После подачи на вход D требуемого уровня сигнала и запоминания его в триггере по фронту тактового сигнала значение с входа данных D может быть убрано. При этом возникает проблема: как добиться того, чтобы последующие фронты тактового сигнала не переписывали запомненное в триггере значение? Одним из способов является формирование вспомогательного тактового сигнала с помощью элемента 2И. На первый из входов этого вентиля подается собственно тактовый сигнал, а на второй – сигнал разрешения. Обращаясь к таблице истинности 2И, нетрудно убедиться, что если на втором входе будет присутствовать сигнал логического нуля, то выход этого элемента будет оставаться в нуле при любом уровне тактового сигнала. Если же на вход разрешения подан сигнал логической единицы, то состояние выхода полностью определяется состоянием входа, на который подан тактовый сигнал. Таким образом, элемент 2И может запрещать прохождение тактового сигнала на вход C триггера в те периоды времени, когда обновление его состояния не требуется.

Обращаясь к таблице истинности 2И, нетрудно убедиться, что если на втором входе будет присутствовать сигнал логического нуля, то выход этого элемента будет оставаться в нуле при любом уровне тактового сигнала. Если же на вход разрешения подан сигнал логической единицы, то состояние выхода полностью определяется состоянием входа, на который подан тактовый сигнал. Таким образом, элемент 2И может запрещать прохождение тактового сигнала на вход C триггера в те периоды времени, когда обновление его состояния не требуется.

В ряде случаев введение в проект вспомогательных вентилей, запрещающих прохождение тактового сигнала, ведет к труднообнаружимым ошибкам. Их источником является тот факт, что тактовый сигнал, прошедший через логический вентиль, оказывается задержанным относительно исходного сигнала на время, требуемое для переключения внутренних схем элемента 2И. Это приводит к тому, что фронт тактового сигнала приходит на разные триггеры в разные моменты времени, и часть триггеров проекта, срабатывая раньше, может исказить логические сигналы, требующие записи в остальные триггеры. Этот неприятный эффект носит название «гонки фронтов», и его следует всячески избегать. Для исключения записи в неподходящие моменты времени в состав триггеров (и других синхронных узлов) вводят специальный вход разрешения записи CE (от ClockEnable – «разрешение тактового сигнала»). Перезапись состояния триггера происходит только в том случае, если в момент прихода фронта тактового сигнала на входе CE присутствовал высокий логический уровень.

Этот неприятный эффект носит название «гонки фронтов», и его следует всячески избегать. Для исключения записи в неподходящие моменты времени в состав триггеров (и других синхронных узлов) вводят специальный вход разрешения записи CE (от ClockEnable – «разрешение тактового сигнала»). Перезапись состояния триггера происходит только в том случае, если в момент прихода фронта тактового сигнала на входе CE присутствовал высокий логический уровень.

Необходимо иметь в виду, что действительный уровень сигнала, разрешающего работу синхронных устройств, может быть как логическим нулем, так и логической единицей. В схемотехнике ТТЛ существует целый ряд соображений, по которым некоторые сигналы считаются активными, если их уровень соответствует логическому нулю. Такие сигналы обозначают символом инверсии (небольшой кружок на входе, аналогично выходу инвертора), чертой над именем сигнала на его графическом изображении, а в текстовых описаниях – символами ~ # n перед именем сигнала (например, ~CE, #CE, nCE). Уровень сигнала, при котором соответствующий вход считается влияющим на работу устройства, называют активным уровнем сигнала. Пример изображения D-триггера с входом разрешения тактового сигнала, имеющим активный низкий уровень, приведен на рис. 1.10.

Уровень сигнала, при котором соответствующий вход считается влияющим на работу устройства, называют активным уровнем сигнала. Пример изображения D-триггера с входом разрешения тактового сигнала, имеющим активный низкий уровень, приведен на рис. 1.10.

На практике в современных цифровых микросхемах управляющие сигналы чаще имеют высокий активный уровень.

Рис. 1.10 Графическое изображение D-триггера с входом разрешения тактового сигнала, имеющим активный низкий уровень.

Аналогично, активный низкий уровень можно назначить и другим входам и выходам цифровых устройств. Например, если инвертировать тактовый вход D-триггера, то перезапись выхода Q будет происходить при переходе тактового сигнала от уровня единицы к уровню нуля («по спаду тактового сигнала»).

С помощью триггеров можно создавать ряд широко используемых цифровых узлов, например, регистры и счетчики. Под регистром в процессорной технике понимают узел для хранения значения переменной состояния. Это может быть как регистр в понимании программиста, так и внутренние сигналы, кодирующие состояние процессора, недоступные программисту. Все эти устройства в своей основе имеют триггер. Если объединить тактовые входы у нескольких триггеров, то запись в них будет происходить одновременно.

Это может быть как регистр в понимании программиста, так и внутренние сигналы, кодирующие состояние процессора, недоступные программисту. Все эти устройства в своей основе имеют триггер. Если объединить тактовые входы у нескольких триггеров, то запись в них будет происходить одновременно.

Рис. 1.11. Соединение D-триггеров для получения 4-разрядного регистра.

В схеме, показанной на рис.1.11, четыре триггера формируют устройство для хранения 4-разрядного двоичного числа. Новое значение в регистр записывается по фронту тактового сигнала. Каждый триггер может иметь также вход разрешения записи, и при объединении этих входов образуется вход разрешения записи в регистр, что позволяет перезаписывать значение регистра только в моменты, предусмотренные разработчиком схемы.

= Перейти к содержанию =

Как работает транзисторный инвертор?

Как работает транзисторный инвертор?

Возможно, это самый важный вопрос в аналоговой электронике именно потому, что эта схема представляет собой простейший транзисторный усилитель. Таким образом, на самом деле возникает вопрос: «Как работает транзисторный усилитель?»

Таким образом, на самом деле возникает вопрос: «Как работает транзисторный усилитель?»

А поскольку усиление на самом деле является регулированием напряжения, на самом деле возникает вопрос: «Как мы можем управлять одним напряжением с помощью другого напряжения?»

И только последний вопрос, почему и как схема инвертирует входное напряжение…

Интересно, эта проблема возникла давно. Где-то в середине 19 века люди почувствовали необходимость снизить электрическое напряжение… и они это сделали. Чтобы понять смысл всего этого, давайте проследим эволюцию этой идеи от простой электрической схемы того времени до современной электронной схемы.

Я сделаю это за шесть последовательных шагов, иллюстрируя их простыми концептуальными диаграммами. Значения величин являются приблизительными для целей этого интуитивного объяснения.

Понижающий делитель напряжения

Представьте, что первые три шага (схемы) происходят в 19 веке.

ШАГ 1: Подключение источника постоянного напряжения. У нас есть источник постоянного напряжения Vcc1, и мы подаем это напряжение на нагрузку истинного напряжения (вольтметр VM1), которая имеет очень высокое сопротивление и поэтому не потребляет никакого тока. Напряжение «чрезмерно» высокое; поэтому наша задача — уменьшить его.

У нас есть источник постоянного напряжения Vcc1, и мы подаем это напряжение на нагрузку истинного напряжения (вольтметр VM1), которая имеет очень высокое сопротивление и поэтому не потребляет никакого тока. Напряжение «чрезмерно» высокое; поэтому наша задача — уменьшить его.

смоделируйте эту схему — Схема создана с помощью CircuitLab

ШАГ 2: Попытка снять некоторое напряжение через сопротивление. Первая идея, которая приходит в голову, это включить резистор R последовательно с источником напряжения Vcc2, чтобы снять с него часть напряжения. Каково же, однако, наше удивление, когда мы видим, что напряжение после резистора не меняется. Проблема в том, что ток не течет через резистор… на резисторе нет падения напряжения… и напряжение не меняется… как будто резистор не резистор.

ЭТАП 3: Пропускание тока. Итак, мы должны вызвать ток в цепи. Для этого включим второй резистор R2 последовательно с первым R1 и параллельно «нагрузке» VM3.

Регулирующий делитель напряжения

Теперь представьте, что следующие три шага (схемы) происходят как в 19-м, так и в 21-м веках.

Для изменения напряжения у нас есть три варианта — изменить сопротивление R1, R2 или оба. Если бы мы были в 19века, мы бы вручную изменяли сопротивление, перемещая движок так называемого «реостата» (схемы слева внизу), но в современных электронных схемах, например. в инверторе OP это должно выполняться автоматически с помощью чего-то вроде «резистора, управляемого напряжением» (схемы справа внизу). Таким устройством может служить транзистор. Это «резистор режима улучшения», что означает, что при увеличении управляющего напряжения его сопротивление уменьшается.

ШАГ 4: Замена R2. Таким образом, при уменьшении R2 (в левой схеме, в 19 веке:-) или увеличении напряжения база-эмиттер Q2 (в правой схеме) выходное напряжение уменьшается… и схема (OP) инвертирует .

смоделируйте эту схему

ШАГ 5: Замена резистора R1. И о.в., при уменьшении R1 (на левой схеме) или увеличении напряжения база-эмиттер Q1 (на правой схеме) выходное напряжение увеличивается… и можно сказать, что в этом смысле схема неинвертирующий .

И о.в., при уменьшении R1 (на левой схеме) или увеличении напряжения база-эмиттер Q1 (на правой схеме) выходное напряжение увеличивается… и можно сказать, что в этом смысле схема неинвертирующий .

смоделируйте эту схему

ШАГ 6: Изменение R1 и R2. Наконец нам пришла в голову гениальная идея — одновременно поменять R1 и R2 (слева) и V1 и V2 (справа) в обратном направлении. Получается так называемая «комплементарная цепь» без резисторов, которая в обоих состояниях не потребляет ток.

смоделировать эту схему

Что такое решение схемы OP?

Это конфигурация, которую мы обсуждали на шаге 4. Регулятор (Q2) подключен к нижней части «делителя напряжения», так что по мере увеличения входного напряжения его «сопротивление» уменьшается, а выходное напряжение соответственно уменьшается. В крайних двух случаях при высоком входном напряжении выход низкий, и, наоборот, при низком входном напряжении выход высокий, т. е. схема инвертируется.

е. схема инвертируется.

Сопротивление транзистора нелинейно, но это не важно для понимания принципа.

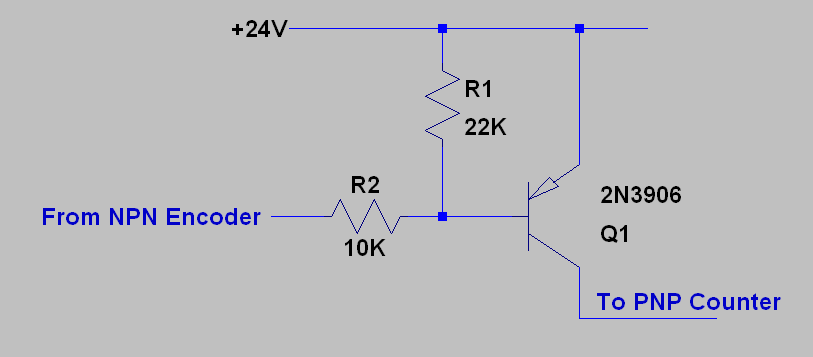

не ворота — Как я могу «инвертировать» сигнал 24 В постоянного тока

\$\начало группы\$

У меня есть «сигнал» 24 В постоянного тока, поступающий из той же линии, из которой питается соленоид. Этот сигнал поступает от ПЛК.

Мне нужно взять этот сигнал и «инвертировать» его, чтобы его можно было использовать для управления другим соленоидом триггерным способом, т.е. когда первый соленоид выключен, второй (дочерний) соленоид должен быть включен, и наоборот.

Я рассматривал возможность использования простого NPN-транзистора, но немного запутался, как мне «подавать» в него исходные 24 В постоянного тока и нужен ли мне еще один мощный транзистор для фактического питания второго соленоида.

Я также пробовал использовать оптопару и подавать на нее исходный сигнал, но мне все равно нужно было бы инвертировать сигнал с помощью микросхемы «инвертора» логического уровня, плюс мне также понадобится какая-то схема драйвера для питания. второй соленоид.

второй соленоид.

Все это кажется довольно сложным, нужно всего лишь инвертировать сигнал 24 В пост. тока для использования на другом соленоиде, поэтому любые советы будут очень признательны.

Я добавил макет псевдосхемы, в котором я мог бы добавить базовый цифровой инвертор.

Другой очевидный способ, который я мог бы сделать, это просто использовать реле для монтажа на печатной плате, но опять же, это кажется ненужным для того, что оно делает, и может выйти из строя.

- сигнал

- без ворот

\$\конечная группа\$

10

\$\начало группы\$

Если этот сигнал не может управлять соленоидом напрямую, вы можете инвертировать его с помощью NPN или мощного полевого МОП-транзистора. Убедитесь, что вы выбрали NPN с достаточной текущей способностью.

По сути, вам нужно подать на базу NPN достаточный базовый ток, чтобы насытить ее — рассчитайте это как ток соленоида, деленный на 20. Базовый ток будет (приблизительно) 24 В/RBASE.

Базовый ток будет (приблизительно) 24 В/RBASE.

Подключите эмиттер NPN к GND и подключите соленоид между 24 В и коллектором.

Если вы используете МОП-транзистор, вам все равно понадобится диод, и вы можете управлять затвором с 1 кОм от сигнала и дополнительными 470 Ом между затвором и землей. Это ограничит напряжение затвора до ~ 8 В.

Вам понадобится диод для защиты NPN от индуктивных пиков, когда соленоид выключается. Самый простой способ — подключить диод «назад» к соленоиду.

Если на самом деле сигнал 24 В постоянного тока может напрямую управлять соленоидом, то просто подключите соленоид между этим сигналом и землей.

\$\конечная группа\$

6

\$\начало группы\$

Одним из простых решений может быть использование резистивного делителя для понижения напряжения до более низкого логического уровня, а затем использование упомянутого вами цифрового инвертора. Вот тема по теме:

Как инвертировать цифровой сигнал.

И предлагаемое решение с транзистором NPN для инвертирования:

Вот тема по теме:

Как инвертировать цифровой сигнал.

И предлагаемое решение с транзистором NPN для инвертирования:

Затем инвертированный сигнал может управлять транзистором в качестве переключателя нижнего плеча соленоида.

Вы упомянули ПЛК, поэтому я предполагаю, что промышленная среда может иметь переходные процессы в сигналах. Либо базовый резистор NPN, либо резисторный делитель обеспечат некоторую защиту. Использование полевого транзистора было бы рискованным.

\$\конечная группа\$

13

\$\начало группы\$

Вариант 1: реле NC параллельно оригинальному соленоиду.

Вариант 2: Реле SPDT вместо оригинального соленоида.

имитация этой схемы – Схема создана с помощью CircuitLab

\$\конечная группа\$

\$\начало группы\$

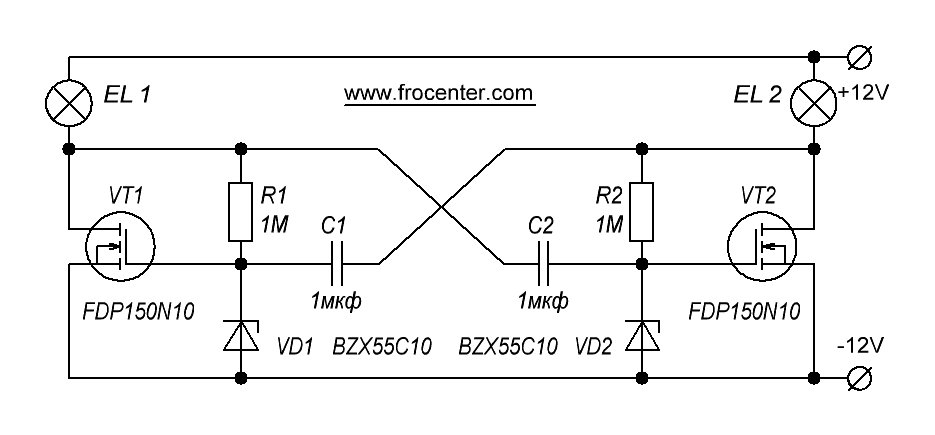

Если первый соленоид заземлен и питается от сигнала 24 В, вы можете использовать транзистор PNP для управления вторым соленоидом от источника питания 24 В. Устройство PMOS также будет работать, если вы отрегулируете R1 и R2, чтобы обеспечить правильное напряжение затвора.

Устройство PMOS также будет работать, если вы отрегулируете R1 и R2, чтобы обеспечить правильное напряжение затвора.

Если управляющее напряжение для соленоида двухтактное, два соленоида могут быть соединены последовательно, как было предложено выше. Но если сигнал с открытым коллектором, двухтактный драйвер можно сконструировать следующим образом:

Добавлен диод Шоттки D3 для имитации привода с открытым коллектором.

Вы также можете переместить соленоид L1 вместо R1 и исключить Q1:

\$\конечная группа\$

3

\$\начало группы\$

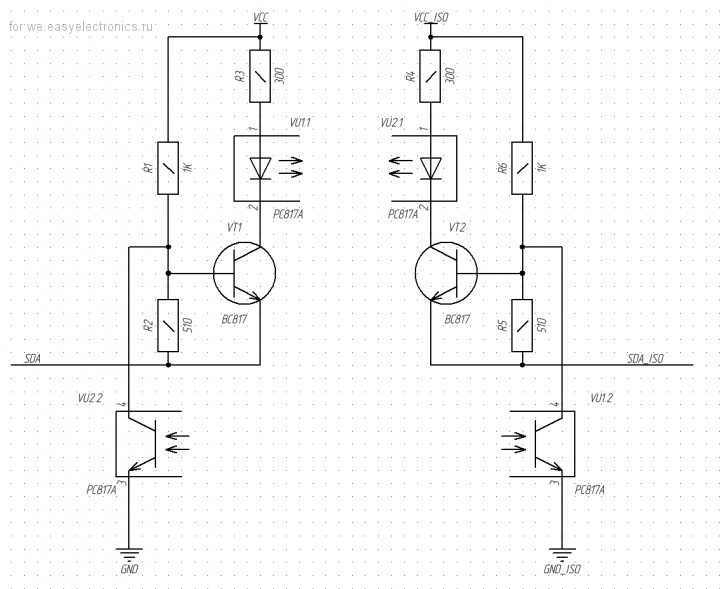

Подниму вашу идею с использованием модуля промышленной оптопары.

Если и только если входной ток соединителя намного ниже тока удержания первого реле (RLY1), вы можете добиться инверсии сигнала, соединив вход соединителя между +24 В и выходом ПЛК. В этом случае ответвитель получает входной сигнал, если выход ПЛК выключен, но ток слишком мал для активации или удержания RLY1.

В этом случае ответвитель получает входной сигнал, если выход ПЛК выключен, но ток слишком мал для активации или удержания RLY1.

Другим ограничением является то, что выход ответвителя рассчитан на требуемый ток RLY2.

Имея защелку в соединительном модуле, это можно сделать быстро.

имитация этой схемы – Схема создана с помощью CircuitLab

\$\конечная группа\$

\$\начало группы\$

Из вопроса я понимаю, что «сигнал 24 В» на самом деле управляет соленоидом. Но вы не говорите, является ли этот сигнал активным высоким или активным низким.

Если активен высокий уровень, то соленоид включен при наличии 24 В, и вы хотите включить другой соленоид при отсутствии 24 В. Если он активен на низком уровне (а ведомый соленоид находится между +24 В и этим сигналом), то все наоборот.

В случае активного высокого уровня можно использовать схему справа: транзистор для инвертирования сигнала, затем МОП-транзистор для включения второго соленоида.