Что такое логические схемы и как их создавать онлайн. Какие инструменты используются для проектирования логических схем. Как анализировать работу логических схем с помощью современных средств. На какие аспекты обратить внимание при разработке логических схем.

Что такое логические схемы и зачем они нужны

Логические схемы представляют собой графическое изображение логических функций и операций. Они широко используются в цифровой электронике для проектирования различных устройств — от простых логических вентилей до сложных микропроцессоров.

Основные преимущества использования логических схем:

- Наглядное представление логики работы устройства

- Возможность анализа и оптимизации схемы

- Удобство проектирования сложных цифровых систем

- Автоматизация процесса разработки электронных устройств

Логические схемы позволяют инженерам-электронщикам и разработчикам цифровых систем эффективно создавать, тестировать и оптимизировать логику работы электронных устройств перед их физической реализацией.

Основные элементы логических схем

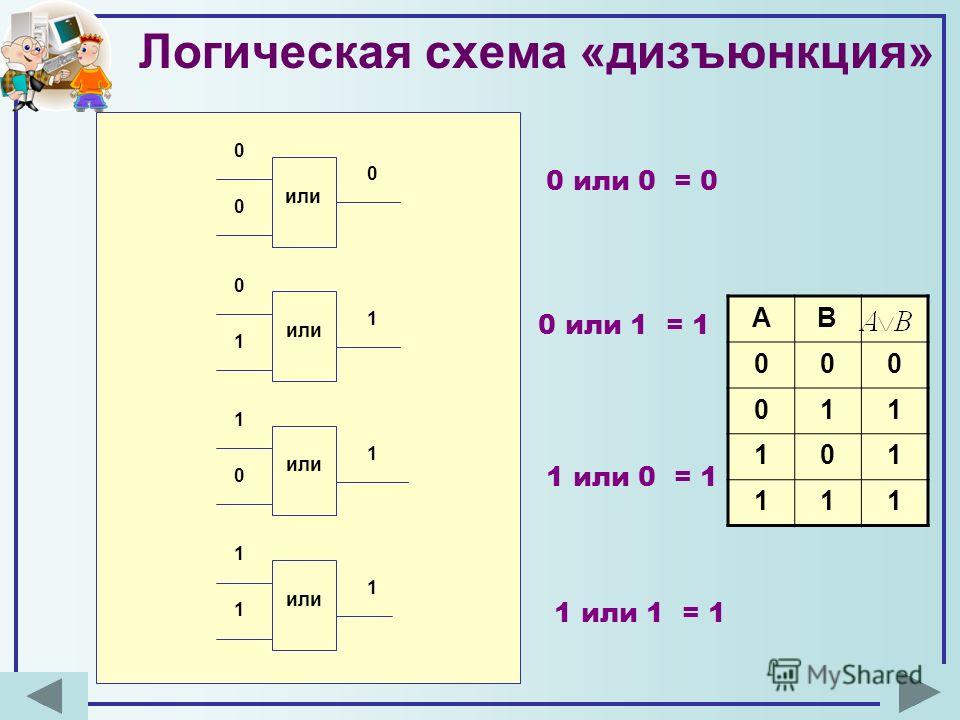

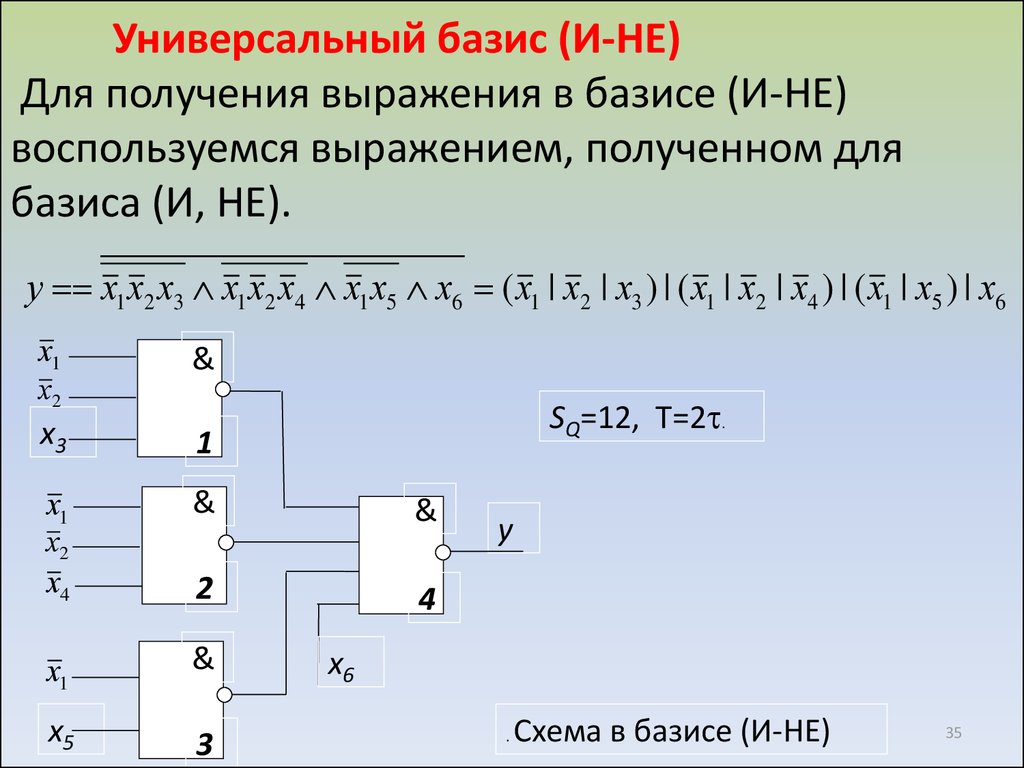

Логические схемы состоят из нескольких базовых элементов:

- Логические вентили (И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и др.)

- Триггеры и регистры для хранения состояний

- Мультиплексоры и демультиплексоры

- Сумматоры, счетчики, компараторы

- Линии связи между элементами

Комбинируя эти базовые элементы, можно создавать логические схемы любой сложности — от простых комбинационных до сложных последовательностных схем с памятью.

Современные инструменты для создания логических схем онлайн

В настоящее время существует множество онлайн-инструментов для проектирования и моделирования логических схем:

1. CircuitLab

CircuitLab — мощный онлайн-редактор схем с возможностью моделирования. Позволяет создавать как аналоговые, так и цифровые схемы. Имеет обширную библиотеку компонентов.

2. Logic.ly

Logic.ly — инструмент для создания и симуляции цифровых логических схем. Имеет интуитивно понятный интерфейс, подходит для обучения основам цифровой логики.

3. Digital Logic Design Simulator

Бесплатный онлайн-симулятор логических схем с возможностью создания комбинационных и последовательностных схем. Поддерживает экспорт в VHDL.

Этапы проектирования логических схем

Процесс создания логической схемы обычно включает следующие этапы:

- Определение требований и спецификаций схемы

- Разработка логических выражений

- Минимизация логических функций

- Выбор элементной базы

- Создание принципиальной схемы

- Моделирование и верификация работы схемы

- Оптимизация схемы (при необходимости)

Современные САПР позволяют автоматизировать многие из этих этапов, что существенно ускоряет процесс проектирования.

Анализ работы логических схем

- Построение таблиц истинности

- Временные диаграммы сигналов

- Функциональное моделирование

- Формальная верификация

Многие онлайн-инструменты предоставляют встроенные средства для такого анализа, что позволяет быстро выявлять и исправлять ошибки в логике работы схемы.

Преимущества онлайн-инструментов для создания логических схем

Использование онлайн-инструментов для проектирования логических схем имеет ряд преимуществ:

- Доступность из любого места с выходом в интернет

- Отсутствие необходимости установки ПО

- Автоматические обновления

- Возможность совместной работы над проектами

- Интеграция с облачными хранилищами

Это делает онлайн-инструменты особенно привлекательными для студентов, небольших команд разработчиков и энтузиастов электроники.

Оптимизация логических схем

Оптимизация логических схем — важный этап проектирования, позволяющий улучшить характеристики устройства. Основные направления оптимизации:

- Минимизация количества логических элементов

- Уменьшение задержек распространения сигналов

- Снижение энергопотребления

- Повышение надежности схемы

Многие современные САПР предоставляют автоматические средства оптимизации логических схем, что позволяет существенно улучшить их характеристики.

Перспективы развития онлайн-инструментов для проектирования логических схем

Онлайн-инструменты для создания логических схем активно развиваются. Основные тенденции:

- Интеграция с системами машинного обучения для автоматической оптимизации схем

- Улучшение средств совместной работы и управления версиями проектов

- Расширение библиотек компонентов и поддержка новых технологий

- Повышение производительности и улучшение пользовательского интерфейса

Это делает онлайн-инструменты все более привлекательными для профессиональных разработчиков электронных устройств.

Логические схемы — презентация онлайн

1. ЛОГИЧЕСКИЕ СХЕМЫ

ТихомировАлександр Николаевич

учитель информатики

гимназия № 528

Санкт-Петербург

2. ЛОГИЧЕСКИЕ СХЕМЫ

Алгебра логики лежит в основеанализа и проектирования

логических схем.

Логические схемы состоят из

логических элементов,

осуществляющих

логические операции.

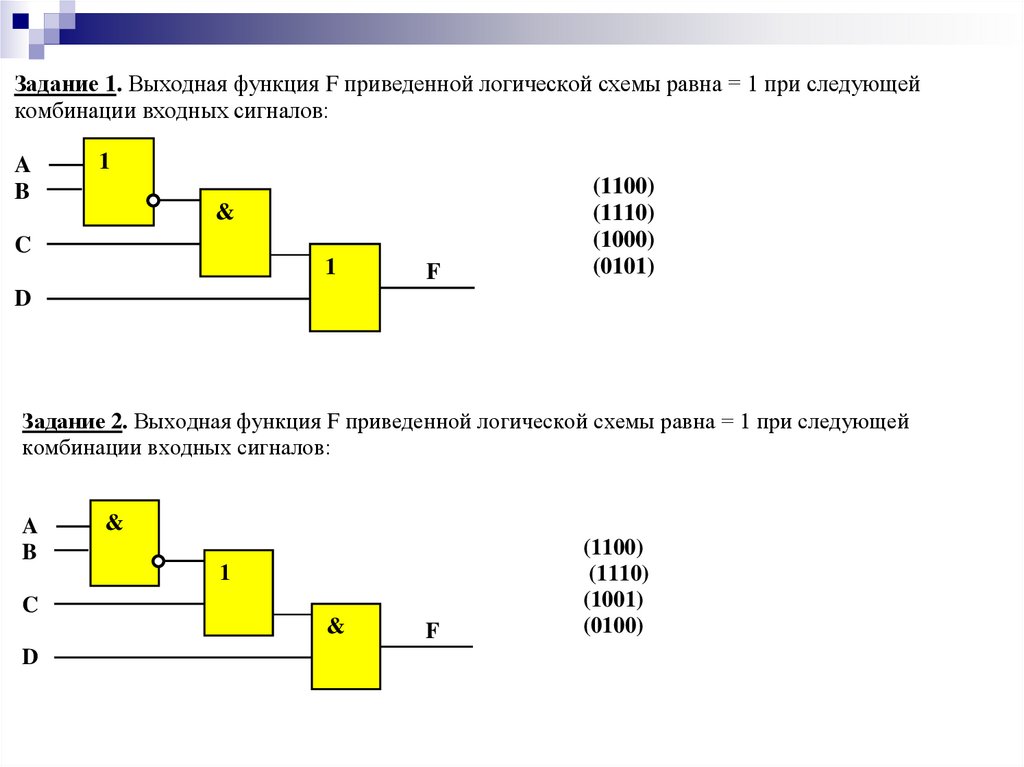

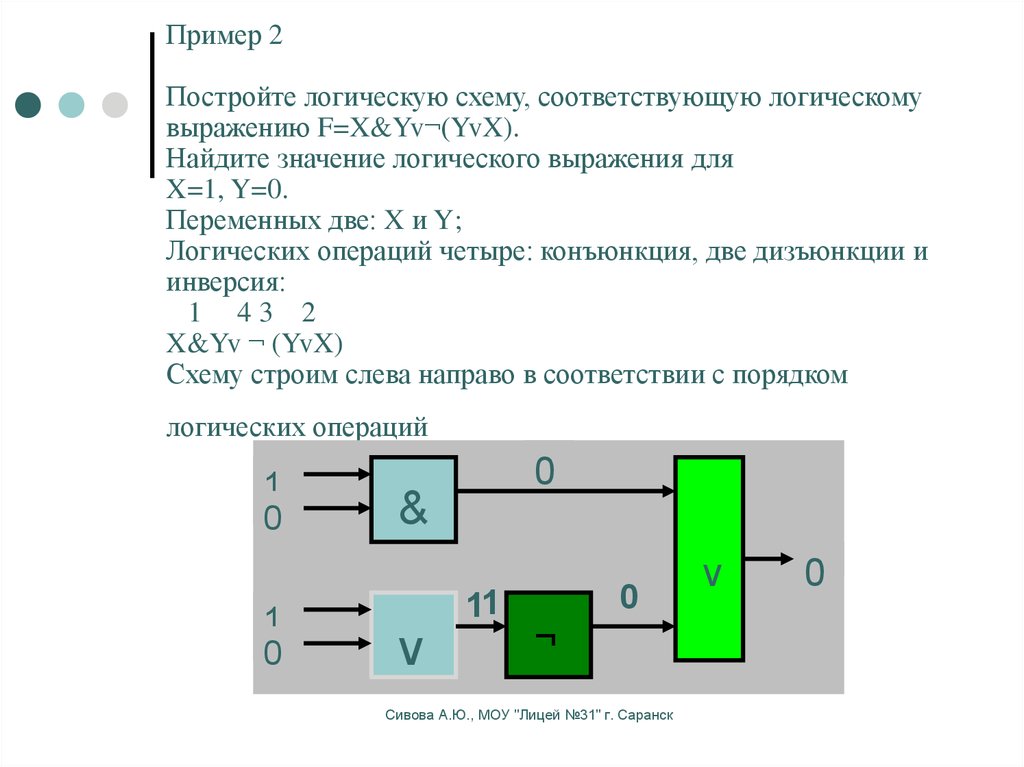

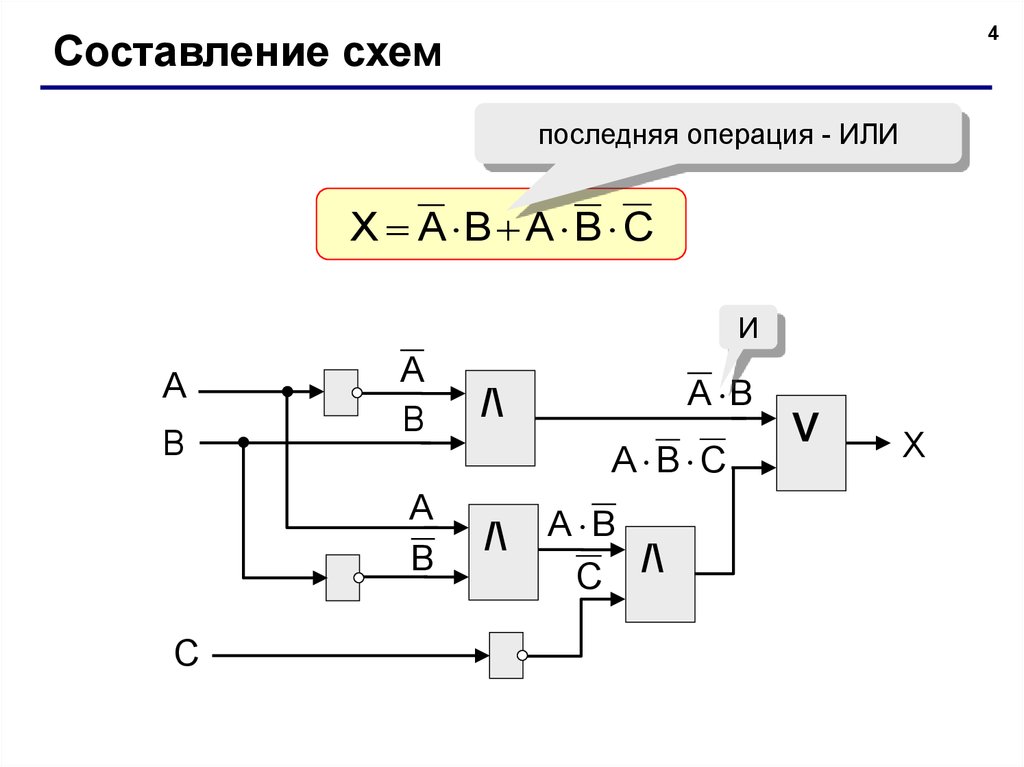

3. ЛОГИЧЕСКИЕ СХЕМЫ

Проектирование логических схем –это реализация

заданных логических функций с

помощью логических элементов.

Анализ логических схем выяснение того, какие логические

сигналы появятся на выходе схемы

после подачи определенных

входных сигналов.

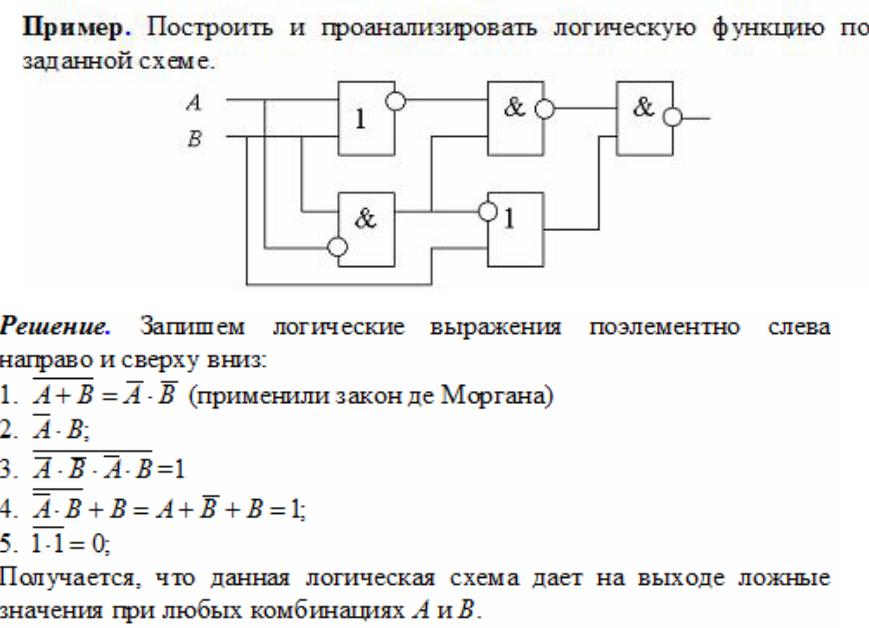

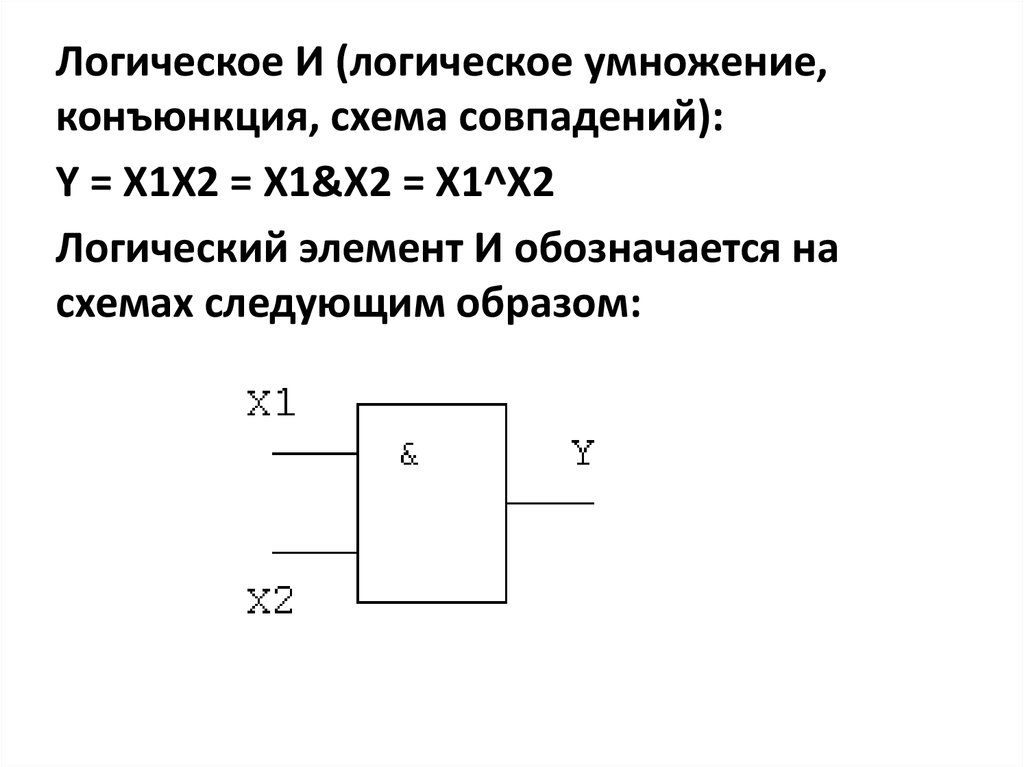

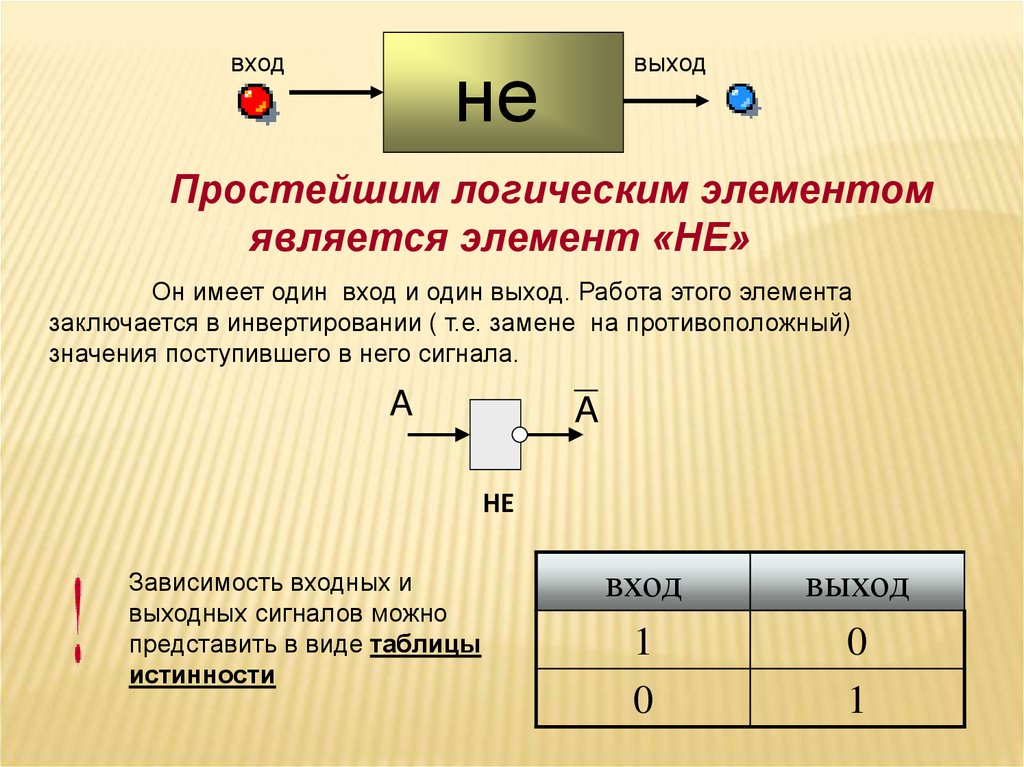

4. ЛОГИЧЕСКИЕ СХЕМЫ

Логические элементы реализуютлогические функции.

A

A

&

A

f (A,B)

1

f (A,B)

B

B

f (A,B) = A * B

f (A,B) = A + B

f (A)

A

f (A)

A

f (A,B)

B

f (A) = A

f (A,B) = A B

5. ЛОГИЧЕСКИЕ СХЕМЫ

Логические схемы реализуют логическиевыражения.

Дана логическая функция

от логических переменных X,Y,Z:

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)

Построить логическую схему (диаграмму),

реализующую данную логическую функцию.

6. ЛОГИЧЕСКИЕ СХЕМЫ

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)X

&

Y

&

Y

Z

1

X

Z

f (X,Y,Z)

7. ЛОГИЧЕСКИЕ СХЕМЫ

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)&

8. ЛОГИЧЕСКИЕ СХЕМЫ

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)&

X

Z

9. ЛОГИЧЕСКИЕ СХЕМЫ

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)&

Y

1

X

Z

Z

10. ЛОГИЧЕСКИЕ СХЕМЫ

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)X

&

Y

Y

&

1

X

Z

Z

11. ЛОГИЧЕСКИЕ СХЕМЫ

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)X

&

Y

&

Y

Z

1

X

Z

f (X,Y,Z)

12. ЛОГИЧЕСКИЕ СХЕМЫ

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)X

&

Y

&

Y

Z

1

X

Z

f (X,Y,Z)

13.

ЛОГИЧЕСКИЕ СХЕМЫf (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)

ЛОГИЧЕСКИЕ СХЕМЫf (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)X

&

Y

&

Y

Z

1

X

Z

f (X,Y,Z)

14. ЛОГИЧЕСКИЕ СХЕМЫ

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)X

&

Y

&

Y

Z

1

X

Z

f (X,Y,Z)

15. ЛОГИЧЕСКИЕ СХЕМЫ

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)X

&

Y

&

Y

Z

1

X

Z

f (X,Y,Z)

16. ЛОГИЧЕСКИЕ СХЕМЫ

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)Инверсия

значения

элемента

X

&

Инверсия

значения

функции

Y

&

Y

1

X

Z

Инверсия

значения

функции

Z

f (X,Y,Z)

17. ЛОГИЧЕСКИЕ СХЕМЫ

Анализ логических схем — выяснение того, какие логические сигналыпоявятся на выходе схемы после подачи определенных входных сигналов.

f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)

X

&

Y

&

Y

Z

1

X

Z

f (X,Y,Z)

18.

ЛОГИЧЕСКИЕ СХЕМЫНайти значение f (X,Y,Z) при X=1, Y=0, Z=1.

ЛОГИЧЕСКИЕ СХЕМЫНайти значение f (X,Y,Z) при X=1, Y=0, Z=1.f (X,Y,Z) = ( (X * Y) (Y + Z) ) * (X Z)

X

&

Y

&

Y

Z

1

X

Z

f (X,Y,Z)

19. ЛОГИЧЕСКИЕ СХЕМЫ

Найти значение f (X,Y,Z) при X=1, Y=0, Z=1.f (X,Y,Z) = ( (1 * 0) (0 + 1) ) * (1 1)

1

&

0

&

0

1

1

1

1

f (X,Y,Z)

20. ЛОГИЧЕСКИЕ СХЕМЫ

Найти значение f (X,Y,Z) при X=1, Y=0, Z=1.f (X,Y,Z) = ( (1 * 0) (0 + 1) ) * (1 1)

1

&

1

1

0

1

&

0

1

1

1

0

1

0

1

1

0

f (X,Y,Z)

21. ЛОГИЧЕСКИЕ СХЕМЫ

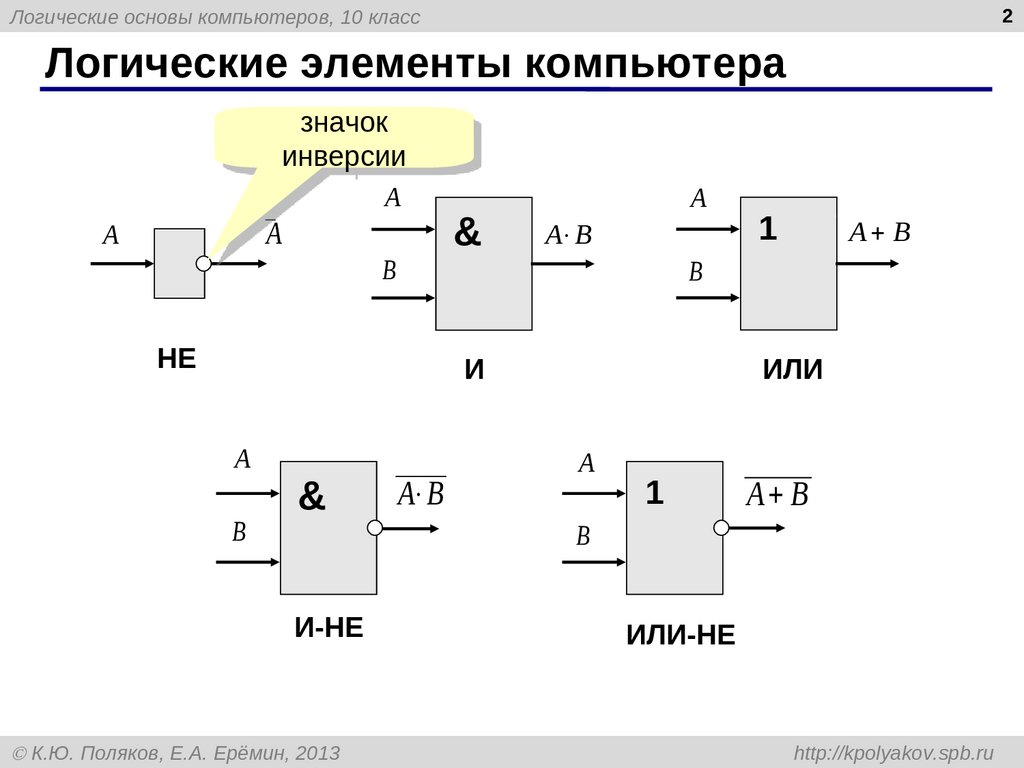

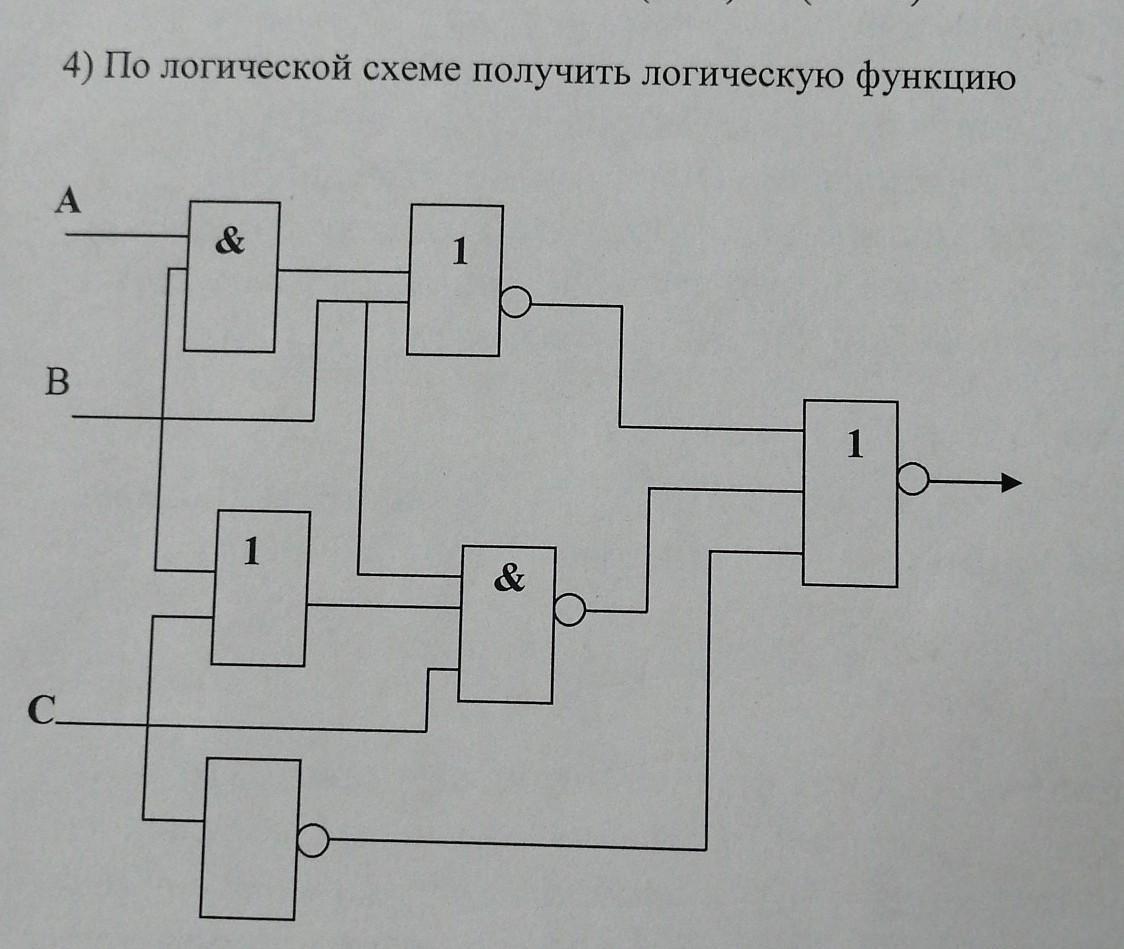

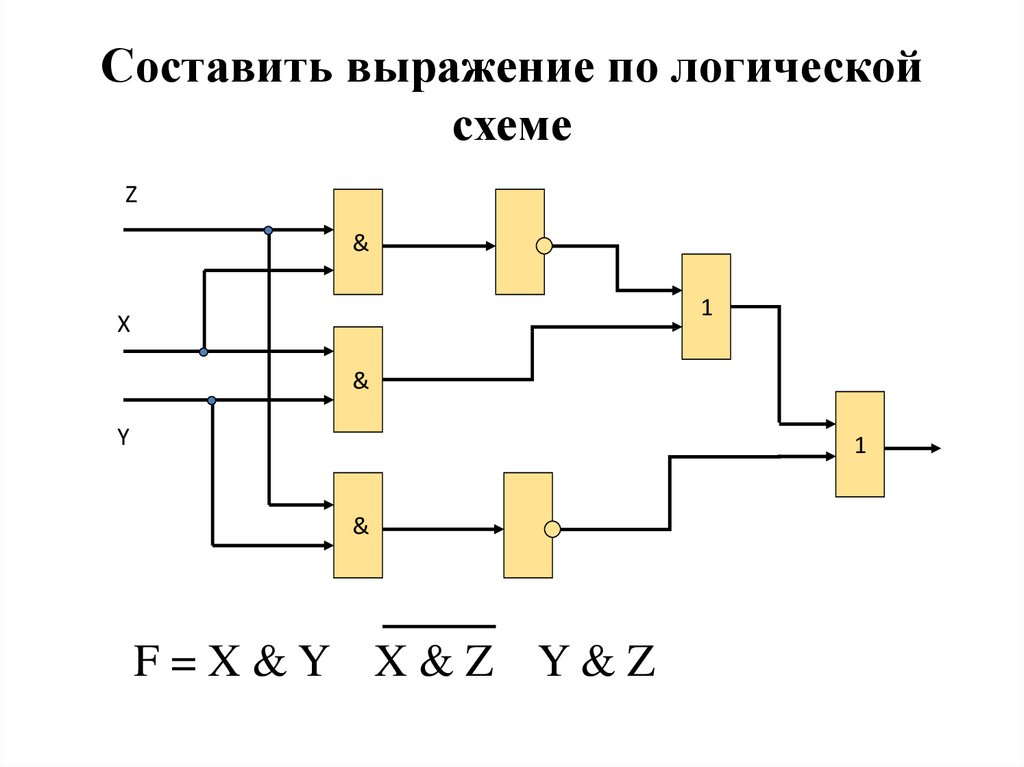

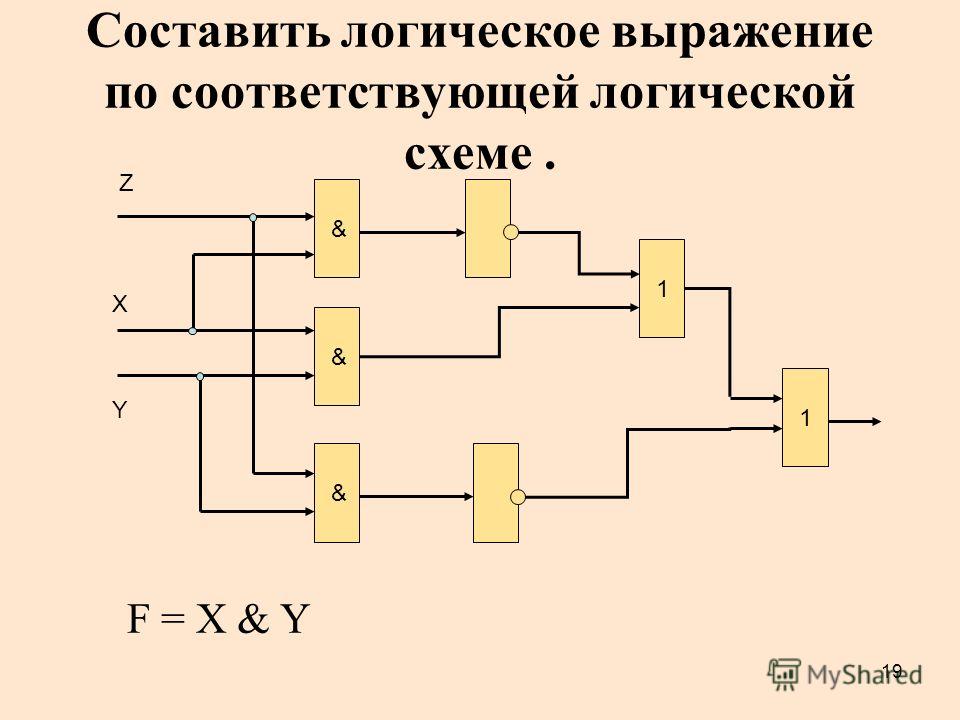

Дана логическая схема (диаграмма).X

Y

&

&

f (X,Y,Z)

Z

Z

Y

1

X

Построить логическую функцию f (X,Y,Z),

реализованную данной логической схемой.

22. ЛОГИЧЕСКИЕ СХЕМЫ

XY

&

&

f (X,Y,Z)

Z

Z

Y

1

X

f (X,Y,Z) = ( ( ( X Y ) * Z ) * ( Z + Y ) ) X

23.

ЛОГИЧЕСКИЕ СХЕМЫДана логическая схема (диаграмма).

ЛОГИЧЕСКИЕ СХЕМЫДана логическая схема (диаграмма).1

1

1

0

&

0

1

&

0

0

0

1

1

1

0

1

1

f (X,Y,Z)

0

X

Построить логическую функцию f (X,Y,Z),

реализованную данной логической схемой.

Логическая оптимизация многоуровневых представлений систем булевых функций на основе блочного разбиения и разложения Шеннона | Бибило

1. Брейтон, Р. К. Синтез многоуровневых комбинационных логических схем / Р. К. Брейтон, Г. Д. Хэчтел, А. Л. Санджованни-Винчентелли // ТИИЭР. – 1990. – Т. 78, № 2. – С. 38–83.

2. Поляков, А. К. Языки VHDL и VERILOG в проектировании цифровой аппаратуры / А. К. Поляков. – М. : СОЛОН-Пресс, 2003. – 320 с.

3. Закревский, А. Д. Логические основы проектирования дискретных устройств / А. Д. Закревский, Ю. В. Поттосин, Л. Д. Черемисинова. – М. : Физматлит, 2007. – 592 с.

4. Закревский, А. Д. Логический синтез каскадных схем / А. Д. Закревский. – М. : Наука, 1981. – 416 c.

– 416 c.

5. Sasao, T. FPGA design by generalized functional decomposition / T. Sasao // Representations of Discrete Functions ; ed. by T. Sasao, M. Fujita. – Kluwer Academic Publishers, 1996. – P. 233–258.

6. Scholl, C. Functional Decomposition with Applications to FPGA Synthesis / C. Scholl. – Kluwer Academic Publishers, 2001. – 288 p.

7. Бибило, П. Н. Применение диаграмм двоичного выбора при синтезе логических схем / П. Н. Бибило. – Минск : Беларус. навука, 2014. – 231 с.

8. Bryant, R. E. Graph-based algorithms for Boolean function manipulation / R. E. Bryant // IEEE Transactions on Computers. – 1986. – Vol. 35, no. 8. – P. 677–691.

9. Bryant, R. E. Ordered binary decision diagrams / R. E. Bryant, C. Meinel // Logic Synthesis and Verification ; ed. by S. Hassoun, T. Sasao, R. K. Brayton. – Kluwer Academic Publishers, 2002. – P. 285–307.

10. Meinel, C. Algorithms and Data Structures in VLSI Design: OBDD – Foundations and Applications / C. Meinel, T. Theobald. – Berlin, Heidelberg : Springer-Verlag, 1998. – 267 p.

Theobald. – Berlin, Heidelberg : Springer-Verlag, 1998. – 267 p.

11. Amaru, L. G. New Data Structures and Algorithms for Logic Synthesis and Verification / L. G. Amaru. – Springer, 2017. – 156 p.

12. Валидация на системном уровне. Высокоуровневое моделирование и управление тестированием / М. Чэнь [и др.]. – М. : Техносфера, 2014. – 296 с.

13. Бибило, П. Н. Использование полиномов Жегалкина при минимизации многоуровневых представлений систем булевых функций на основе разложения Шеннона / П. Н. Бибило, Ю. Ю. Ланкевич // Программная инженерия. – 2017. – № 3. – С. 369–384.

14. Бибило, П. Н. Cистемы проектирования интегральных схем на основе языка VHDL. StateCAD, ModelSim, LeonardoSpectrum / П. Н. Бибило. – М. : СОЛОН-Пресс, 2005. – 384 с.

15. Бибило, П. Н. Логическое проектирование дискретных устройств с использованием продукционнофреймовой модели представления знаний / П. Н. Бибило, В. И. Романов. – Минск : Беларус. навука, 2011. – 279 с.

16. Григорьян, С. Г. Конструирование электронных устройств систем автоматизации и вычислительной техники / С. Г. Григорьян. – Ростов н/Д : Феникс, 2007. – 303 с.

Г. Конструирование электронных устройств систем автоматизации и вычислительной техники / С. Г. Григорьян. – Ростов н/Д : Феникс, 2007. – 303 с.

17. Кузовлев, В. И. Выявление высокоуровневых иерархических структур сверхбольших интегральных схем через сильно связанные логические группы / В. И. Кузовлев, Н. А. Иванова // Вестник МГТУ им. Н. Э. Баумана. Сер. Приборостроение. – 2016. – № 4. – С. 4–18.

18. Netlist and system partitioning / A. B. Kahng [et al.] // VLSI Physical Design: From Graph Partitioning to Timing Closure. – Springer, 2011. – Chap. 2. – P. 31–54.

19. Бибило, П. Н. Оптимизационные преобразования логической схемы на основе блочного разбиения / П. Н. Бибило, Н. А. Кириенко // Информатика. – 2009. – № 3(23). – С. 5–15.

20. Jeong, C. Computer-Aided Design of Digital Systems / C. Jeong // Department of Computer Science [Electronic resource]. – Mode of access: http://www1.cs.columbia.edu/~cs6861/sis/espresso-examples/ex. – Date of access: 20.03.2018.

Makerchip

Самая мощная среда разработки Verilog — для всех!

от Redwood EDA, LLC

от Redwood EDA, LLC

Запуск Makerchip IDE

Наша миссия

Проектирование схем слишком долго было игрой для крупной промышленности! Makerchip предоставляет бесплатно

и мгновенный доступ к новейшим инструментам прямо из браузера и с рабочего стола. Это включает в себя инструменты с открытым исходным кодом и проприетарные.

Переворачивая столы для сообщества открытого исходного кода, Redwood EDA, LLC

коммерческие возможности часто доступны для разработки с открытым исходным кодом здесь в первую очередь— до они

доступны в продаже!

Это включает в себя инструменты с открытым исходным кодом и проприетарные.

Переворачивая столы для сообщества открытого исходного кода, Redwood EDA, LLC

коммерческие возможности часто доступны для разработки с открытым исходным кодом здесь в первую очередь— до они

доступны в продаже!

Разработка Verilog в вашем браузере

Вы можете кодировать, компилировать, моделировать и отлаживать проекты Verilog, все из вашего браузера. Ваш код, блок-схемы, сигналы и новые возможности визуализации тесно интегрированы для беспроблемный дизайн.

Пока Makerchip представляет новаторские возможности для расширенного проектирования Verilog, он также упрощает и упрощает проектирование схем. веселье! Учебники помогут вам начать работу.

Beyond Verilog

Мы сказали «легко» и «Verilog» на одном дыхании? Это просто противоречиво!

Вот почему так важно, чтобы Makerchip поддерживал новый стандарт Transaction-Level Verilog. Transaction-Level Verilog, или TL-Verilog, представляет собой огромный шаг вперед. вперед, устраняя необходимость в устаревших языковых функциях Verilog и вводя

более простой синтаксис. В то же время TL-Verilog добавляет мощные конструкции для конвейеров и

транзакции. Мы поможем вам научиться этому, и вы никогда не повернете назад!

Это самый простой способ написать и отредактировать ваш Verilog с меньшим количеством ошибок.

вперед, устраняя необходимость в устаревших языковых функциях Verilog и вводя

более простой синтаксис. В то же время TL-Verilog добавляет мощные конструкции для конвейеров и

транзакции. Мы поможем вам научиться этому, и вы никогда не повернете назад!

Это самый простой способ написать и отредактировать ваш Verilog с меньшим количеством ошибок.

Easy Pipelining

Вместо записи на Verilog always_ff @(posedge clk) begin ... для создания триггеров… ничего не пишите!

Организуйте свои логические операторы Verilog в конвейеры и позвольте TL-Verilog

подразумевают необходимые триггеры.

Приведенный ниже код предоставляет конвейер с именем |incr , содержащий

ступени трубопровода @1 , @2 и @3 . Каждый этап увеличивает значение от

предыдущего этапа на один в последующем такте.

Триггеры (обозначены серыми квадратами на диаграмме)

переносить ценности с одного этапа на другой.

Если вам интересно, вот соответствующий код Verilog:

логика [2:0] INCR_one_a1, INCR_one_a2; логика [2:0] INCR_two_a2, INCR_two_a3; логика [2:0] INCR_three_a3; присвоить INCR_one_a1[2:0] = 1; always_ff @(posedge clk) INCR_one_a2 <= INCR_one_a1; назначить INCR_two_a2 = INCR_one_a2 + 1; always_ff @(posedge clk) INCR_two_a3 <= INCR_two_a2; назначить INCR_three_a3 = INCR_two_a3 + 1;

Контекст конвейера снижает количество ошибок и упрощает поддержку вашего проекта в условиях изменения времени.

Узнайте больше о конвейерах TL-Verilog, а также о других мощных конструкциях, включая иерархия, состояние, достоверность и транзакции в руководствах по TL-Verilog внутри Makerchip IDE.

Организованные сигналы

Сигналы организованы в соответствии с иерархией проекта TL-Verilog. Осциллограммы четко показывают когда сигналы несут значимые данные.

Организованные диаграммы

Ваши проекты представлены в виде логических схем. Иерархия дизайна TL-Verilog,

включая конвейеры и этапы трубопроводов, обеспечивает организацию

Ваши логические схемы. Ниже путь через

Ниже путь через $ANY

Связанное проектирование и отладка

Конструкции TL-Verilog в редакторе кода, диаграмме и средстве просмотра сигналов связаны друг с другом. Щелчок по элементу, такому как канал, в одном представлении выделит этот элемент. во всех представлениях.

Интеграция инструментов

Makerchip можно легко запустить как редактор Verilog/TL-Verilog из других приложений. Например, Мейкерчип обеспечивает цифровую сторону среды eSim со смешанным сигналом FOSSEE, а SandPiper-SaaS обеспечивает компиляцию eSim TL-Verilog.

Запуск Makerchip IDE

Stateflow — MATLAB и Simulink

Моделирование и имитация логики принятия решений с использованием конечных автоматов и блок-схем

Получить бесплатную пробную версию

Посмотреть цены

Stateflow ® предоставляет графический язык, который включает диаграммы переходов состояний, блок-схемы, таблицы переходов состояний и таблицы истинности. Вы можете использовать Stateflow для описания того, как алгоритмы MATLAB

® и модели Simulink ® реагируют на входные сигналы, события и временные условия.

Вы можете использовать Stateflow для описания того, как алгоритмы MATLAB

® и модели Simulink ® реагируют на входные сигналы, события и временные условия.

Stateflow позволяет проектировать и разрабатывать диспетчерское управление, планирование задач, устранение неисправностей, протоколы связи, пользовательские интерфейсы и гибридные системы.

С помощью Stateflow вы моделируете комбинаторную и последовательную логику принятия решений, которую можно смоделировать как блок в модели Simulink или выполнить как объект в MATLAB. Графическая анимация позволяет анализировать и отлаживать логику во время ее выполнения. Проверки во время редактирования и во время выполнения обеспечивают согласованность и полноту дизайна перед реализацией.

Начало работы:

- Логика управления дизайном

- Графики выполнения и отладки

- Разработайте повторно используемую логику для приложений MATLAB

- Проверка проектов и создание кода

2:06

Продолжительность видео 2:06.

Что такое Stateflow?

Логика управления проектированием

Моделирование системной логики с использованием конечных автоматов, блок-схем и таблиц истинности.

Графическое проектирование конечных автоматов

Графическое построение конечных автоматов путем рисования состояний и соединений, соединенных переходами. Вы также можете создавать функции, используя нотацию блок-схемы, подсистемы Simulink, код MATLAB и таблицы истинности.

Представление режимов работы с использованием состояний

Подсистемы Simulink как состояния

Повторное использование кода MATLAB путем определения функций MATLAB

Начало работы с Stateflow (12:48)

Диаграмма Stateflow, определяющая логику системы контроля температуры котла. На схеме используются графические функции (правая сторона) для реализации вспомогательных алгоритмов, вызываемых системой обогрева (левая сторона).

Разработка блок-схем

Создание блок-схем путем рисования переходов, соединенных в местах соединения. Мастер шаблонов позволяет создавать часто используемые шаблоны логических потоков. Вы можете использовать блок-схемы для разработки логики перехода между состояниями.

Мастер шаблонов позволяет создавать часто используемые шаблоны логических потоков. Вы можете использовать блок-схемы для разработки логики перехода между состояниями.

Блок-схемы в Stateflow

Создание блок-схем с помощью мастера шаблонов

Графически представлять комбинаторную логику, такую как деревья решений и итерационные циклы, с помощью блок-схем.

Разработка логики с помощью таблиц

Таблицы истинности в Stateflow позволяют моделировать логику в Simulink, когда вывод зависит исключительно от текущего ввода. Таблицы перехода состояний обеспечивают структурированную среду для моделирования конечных автоматов в Simulink.

Повторное использование комбинаторной логики путем определения таблиц истинности

Таблицы переходов состояний в Stateflow

Таблицы переходов состояний (4:53)

Таблица истинности, реализующая логику выбора действительного показания датчика в алгоритме обнаружения неисправностей.

Графики выполнения и отладки

Визуализируйте поведение вашей системы для анализа и отладки.

Выполнение диаграмм Stateflow

Визуализируйте поведение системы, используя анимацию диаграмм состояний, чтобы выделить активные состояния и переходы на диаграммах.

Выполнение диаграммы Stateflow

Типы исполнения графиков

Понимание сложной логики с помощью Stateflow.2:59 Продолжительность видео 2:59.

Понимание сложной логики с помощью Stateflow

Отладка диаграмм Stateflow

Возможности отладки Stateflow позволяют детально выполнять выполнение диаграммы. Вы можете устанавливать точки останова, отслеживать значения данных и выполнять различные функции на диаграммах состояний.

Установите точки останова для отладки диаграмм

Обнаружение ошибок моделирования во время редактирования

Анализ и отладка логики с помощью Stateflow (4:00)

Параметры визуализации данных моделирования в Stateflow. Вверху слева: Simulink Data Inspector для сравнения определенных сигналов; внизу слева: настраиваемый интерфейс MATLAB для анализа данных; справа: Simulink Signal Selector для сравнения конкретных состояний.

Вверху слева: Simulink Data Inspector для сравнения определенных сигналов; внизу слева: настраиваемый интерфейс MATLAB для анализа данных; справа: Simulink Signal Selector для сравнения конкретных состояний.

Разработайте повторно используемую логику для приложений MATLAB

Используйте объекты диаграммы Stateflow для разработки повторно используемой логики для приложений MATLAB. Разработайте конечный автомат и логику синхронизации для широкого спектра приложений, включая испытания и измерения, автономные системы, обработку сигналов и связь.

Повторно используемые объекты диаграммы

Создавайте автономные диаграммы Stateflow, которые используют все возможности языка MATLAB в действиях состояний и переходов. Используйте эти диаграммы как объекты MATLAB в своих приложениях, требующих конечного автомата и логики синхронизации.

Создайте диаграммы Stateflow для выполнения как объекты MATLAB

Выполнение и модульное тестирование объектов диаграммы Stateflow

Отладка автономной диаграммы Stateflow

Конечный автомат и логика синхронизации

Ускорьте разработку приложений MATLAB, используя Stateflow для графического проектирования конечного автомата и логики синхронизации, которые было бы трудно реализовать в текстовом виде.

Проектирование логики человеко-машинного интерфейса с использованием диаграмм Stateflow

Смоделируйте протокол связи с помощью объектов диаграммы

Приложение Analog Trigger с использованием диаграмм Stateflow

Использование Stateflow для предоставления логики для приложения MATLAB.2:07 Продолжительность видео 2:07.

Использование Stateflow для предоставления логики для приложения MATLAB

Развертывание приложений Stateflow

Создавайте приложения MATLAB, которые включают объекты диаграмм Stateflow, и делитесь ими, не требуя Stateflow.

Совместно используйте приложения MATLAB, которые включают объекты диаграмм Stateflow, с пользователями, у которых нет Stateflow.

Алгоритмы расписания Simulink

Алгоритмы расписания, смоделированные в Simulink.

Периодическое и непрерывное планирование

Вы можете моделировать условную, событийную и временную логику в Stateflow для периодического или непрерывного вызова алгоритмов Simulink. Оркестрируйте выполнение компонентов, чтобы имитировать планирование вашей среды реального времени.

Оркестрируйте выполнение компонентов, чтобы имитировать планирование вашей среды реального времени.

Переход между режимами работы

Непрерывное моделирование в Stateflow

Синхронизация компонентов модели с помощью широковещательных событий

Вы можете моделировать логику в Stateflow для вызова алгоритмов Simulink и MATLAB периодическим или непрерывным образом.

Временные операторы

Используйте операторы, основанные на событиях и времени (например, после и продолжительности), чтобы задать логику перехода состояний на основе количества событий, прошедшего времени и сигналов без шума без необходимости создавать и поддерживать собственные таймеры и счетчики. .

Выполнение контрольной диаграммы с использованием временной логики

Управление колебаниями с помощью оператора Duration

Темпоральные логические операторы.0:53 Продолжительность видео 0:53.

Операторы темпоральной логики

Проверка проектов и создание кода

Проверка проекта на соответствие требованиям и создание кода для реализации во встроенной системе.

Проверка проектов

Используйте Stateflow с другими продуктами Simulink для проверки соответствия вашего проекта требованиям.

- Связывайте требования непосредственно с объектами Stateflow, используя перетаскивание с помощью Requirements Toolbox™.

- Убедитесь, что ваши диаграммы состояний соответствуют стандартам, используя Simulink Check™.

- Собирайте показатели покрытия модели и сгенерированного кода с помощью Simulink Coverage™.

- Обнаружение ошибок проектирования и создание тестовых векторов с помощью Simulink Design Verifier™.

- Разрабатывайте, управляйте и выполняйте тесты на основе моделирования с помощью Simulink Test™.

Выделите активную логику с помощью слайсера моделей.

Генерация кода

Генерация кода для реализации вашей логики Stateflow во встроенных системах.

- Создавайте код C и C++ из моделей Simulink и Stateflow с помощью Simulink Coder™.