Что представляет собой микросхема 7400. Какие логические элементы она содержит. Как работают элементы И-НЕ. Для чего применяется микросхема 7400 в электронных схемах. Какие существуют разновидности этой микросхемы.

Общее описание и структура микросхемы 7400

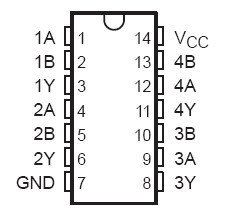

Микросхема 7400 является одной из базовых логических микросхем семейства ТТЛ (транзисторно-транзисторная логика). Она содержит четыре независимых логических элемента И-НЕ с двумя входами каждый.

Основные характеристики микросхемы 7400:

- Напряжение питания: 5В

- Количество элементов: 4

- Тип элементов: И-НЕ

- Число входов каждого элемента: 2

- Число выходов каждого элемента: 1

Принцип работы логических элементов И-НЕ

Как работает логический элемент И-НЕ в микросхеме 7400? Его функционирование основано на следующих принципах:

- Если хотя бы на один вход подается низкий уровень напряжения (логический 0), на выходе устанавливается высокий уровень (логическая 1).

- Только когда на оба входа подается высокий уровень напряжения (логическая 1), на выходе формируется низкий уровень (логический 0).

Данная логика работы может быть представлена в виде таблицы истинности:

| Вход A | Вход B | Выход Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Области применения микросхемы 7400

Для чего используется микросхема 7400 в электронных устройствах? Основные области её применения включают:

- Реализация базовых логических функций И, И-НЕ

- Инвертирование сигналов

- Построение более сложных логических схем

- Создание триггеров и счетчиков

- Формирование импульсных сигналов

Благодаря своей универсальности, микросхема 7400 находит широкое применение в различных цифровых устройствах, от простых логических схем до сложных вычислительных систем.

Разновидности микросхемы 7400

Существует ряд модификаций базовой микросхемы 7400, отличающихся технологией изготовления и электрическими характеристиками. Наиболее распространенные варианты включают:

- 7400 — стандартная ТТЛ-версия

- 74LS00 — версия с пониженным энергопотреблением

- 74ALS00 — усовершенствованная версия с пониженным энергопотреблением

- 74F00 — быстродействующая версия

- 74S00 — версия с улучшенным быстродействием

Каковы основные отличия этих модификаций? Они различаются по следующим параметрам:

- Время задержки распространения сигнала

- Ток потребления

- Нагрузочная способность выходов

- Помехоустойчивость

Технические характеристики различных версий микросхемы 7400

Рассмотрим ключевые параметры наиболее распространенных модификаций микросхемы 7400:

| Время задержки, нс | Ток потребления, мА | |

|---|---|---|

| 7400 | 10 | 8 |

| 74LS00 | 9.5 | 2 |

| 74ALS00 | 6 | 1 |

| 74F00 | 3.4 | 4.4 |

| 74S00 | 3 | 15 |

Как видно из таблицы, версии с пониженным энергопотреблением (LS, ALS) имеют меньший ток потребления, но несколько большее время задержки. Быстродействующие версии (F, S) обеспечивают минимальное время задержки, но потребляют больше тока.

Особенности применения микросхемы 7400 в современной электронике

Несмотря на то, что микросхема 7400 была разработана несколько десятилетий назад, она до сих пор находит применение в современной электронике. Чем обусловлена её популярность?

- Простота использования

- Низкая стоимость

- Высокая надежность

- Совместимость с другими ТТЛ-микросхемами

- Широкая доступность

В каких областях современной электроники чаще всего используется микросхема 7400? Основные сферы применения включают:

- Учебные и экспериментальные проекты

- Прототипирование электронных устройств

- Ремонт и обслуживание устаревшего оборудования

- Создание простых логических схем в любительских проектах

Альтернативы микросхеме 7400 в современных разработках

Хотя микросхема 7400 остается популярной, в современной электронике существуют более совершенные альтернативы. Какие микросхемы могут заменить 7400 в новых разработках?

- Программируемые логические интегральные схемы (ПЛИС)

- Микроконтроллеры со встроенными логическими элементами

- Специализированные цифровые микросхемы с расширенной функциональностью

Чем обусловлен переход к этим альтернативам? Основные преимущества современных решений включают:

- Большую гибкость и возможность перепрограммирования

- Меньшее энергопотребление

- Более высокое быстродействие

- Интеграцию множества функций в одном корпусе

- Уменьшение габаритов электронных устройств

Заключение: роль микросхемы 7400 в развитии цифровой электроники

Микросхема 7400, являясь одним из первых представителей семейства ТТЛ-логики, сыграла важную роль в развитии цифровой электроники. Какой вклад она внесла в эволюцию электронных устройств?

- Стандартизация логических уровней и интерфейсов

- Упрощение проектирования цифровых схем

- Повышение надежности электронных устройств

- Снижение стоимости производства цифровой техники

- Создание базы для развития более сложных интегральных схем

Хотя современная электроника во многом ушла вперед, принципы, заложенные в микросхеме 7400, продолжают использоваться при разработке новых цифровых устройств. Понимание работы этой базовой логической микросхемы остается важным для всех, кто изучает основы цифровой электроники.

Микросхема 7400

7400

Описание

Микросхема 7400 содержит четыре отдельных логических элемента И-НЕ с двумя входами на каждом.

Работа схемы

Все четыре логических элемента микросхемы 7400 И-НЕ можно использовать независимо друг от друга.

При подаче напряжения низкого уровня на один или оба входа каждого элемента на выходе устанавливается напряжение высокого уровня.

Если на оба входа подается напряжение высокого уровня, то на выходе формируется напряжение низкого уровня.

Логическая микросхема 74LS00-S6 по расположению контактов совместима с микросхемой 7400, однако в отличие от неё выдерживает входное напряжение до +15 В.

Применение

Реализация логических функций И, И-НЕ, инвертирование сигналов.

Производится следующая номенклатура микросхем: 7400, 74ALS00, 74AS00, 74F00, 74H00, 74L00, 74LS00, 74S00.

| Тип микросхемы | 7400 | 74ALS00 | 74AS00 | 74F00 | 74LS00 | 74S00 | 74LS00-S6 |

|---|---|---|---|---|---|---|---|

| Время задержки прохождения сигнала, нс | 10 | 6 | 2,6 | 3,4 | 9,5 | 3 | 10 |

| Ток потребления, мА | 8 | 1 | 4 | 4,4 | 2 | 15 | 2 |

| Входы | Выход | |

|---|---|---|

| A | B | Y |

| 0 | X | 1 |

| X | 0 | 1 |

| 1 | 1 | 0 |

| НОМЕР | ОПИСАНИЕ |

| 7400 | 4е элемента 2НЕ-И |

| 741G00 | 1 элемент 2НЕ-И |

| 7401 | 4е элемента 2НЕ-И с открытыми коллекторами на выходах |

| 741G01 | 1 элемент 2НЕ-И с открытым стоком на выходе |

| 7402 | 4е элемента 2НЕ-ИЛИ |

| 741G02 | 1 элемент 2НЕ-ИЛИ |

| 7403 | 4е элемента 2НЕ-И с открытыми коллекторами на выходах |

| 741G03 | 1 элемент 2НЕ-И с открытым стоком на выходе |

| 6 эелементов НЕ | |

| 741G04 | 1 элемент НЕ |

| 7405 | 6 эелементов НЕ с открытыми коллекторами на выходах |

| 741G05 | 1 элемент НЕ с открытым стоком на выходе |

| 7406 | 6 элементов НЕ буффер/драйвер с 30 v открытыми коллекторами на выходах |

| 741G06 | 1 элемент inverting с буффером/drive |

| 7407 | 6 элементов буффер/драйвер с 30 v открытыми коллекторами на выходах |

| 741G07 | 1 элемент буффер/драйвер с открытым стоком на выходе |

| 7408 | 4е элемента 2И |

| 741G08 | 1 элемент 2И |

| 7409 | 4е элемента 2И с открытыми коллекторами на выходах |

| 741G09 | 1 элемент 2И с открытым стоком на выходе |

| 7410 | 3 элемента 3НЕ-И |

| 7411 | 3 элемента 3И |

| 7412 | 3 элемента 3НЕ-И с открытыми коллекторами на выходах |

| 7413 | 2 триггера Шмитта и 4НЕ-И |

| 7414 | 6 триггеров Шмитта с выходами НЕ |

| 741G14 | 1 триггер Шмитта с выходом НЕ |

| 7415 | 3 элемента 3И с открытыми коллекторами на выходах |

| 7416 | 6 элементов НЕ буффер/драйвер с 15 v открытыми коллекторами на выходах |

| 7417 | 6 элементов буффер/драйвер с 15 v открытыми коллекторами на выходах |

| 741G17 | 1 триггер Шмитта |

| 7418 | 2 элемента 4НЕ-И с триггерами Шмитта на входах |

| 7419 | 6 элементов НЕ с триггерами Шмитта |

| 7420 | 2 элемента 4НЕ-И |

| 7421 | 2 элемента 4И |

| 7422 | 2 элемента 4НЕ-И с открытыми коллекторами на выходах |

| 7423 | Расширяемые 2 элемента 4НЕ-ИЛИ со стробирующим входом |

| 7424 | 4е элемента 2НЕ-И с триггерами Шмитта на входе. |

| 7425 | 2 элемента 4НЕ-ИЛИ со стробирующим входом |

| 7426 | 4е элемента 2НЕ-И with 15 v открытыми коллекторами на выходах |

| 7427 | 3 элемента 3НЕ-ИЛИ |

| 741G27 | 1 элемент 3НЕ-ИЛИ |

| 7428 | 4е элемента 2НЕ-ИЛИ с буффером |

| 7430 | 8НЕ-И |

| 7431 | 6 элементов задержки |

| 7432 | 4е элемента 2ИЛИ |

| 741G32 | 1 элемент 2ИЛИ |

| 7433 | 4е элемента 2НЕ-ИЛИ с буффером с открытыми коллекторами на выходах |

| 7436 | 4е элемента 2НЕ-ИЛИ (с другими выводами, чем 7402) |

| 7437 | 4е элемента 2НЕ-И с буффером |

| 7438 | 4е элемента 2НЕ-И с буффером с открытыми коллекторами на выходах |

| 7439 | 4е элемента 2НЕ-И с буффером |

| 7440 | 2 элемента 4НЕ-И с буффером |

| 7441 | Двоично-десяти |

| 7442 | Двоично-десяти |

| 7443 | excess-3 to decimal decoder |

| 7444 | excess-3-Gray code to decimal decoder |

| 7445 | Двоично-десяти |

| 7446 | Двоично-десяти |

| 7447 | Двоично-десяти |

| 7448 | Двоично-десяти |

| 7449 | Двоично-десяти |

| 7450 | 2 элемента 2-расширенных 2И-ИЛИ-НЕ (один расширяемый) |

| 7451 | 2 элемента 2-расширенных 2И-ИЛИ-НЕ |

| 7452 | Расширяемые 4-расширенных 2И-ИЛИ |

| 7453 | Расширяемые 4-расширенных 2И-ИЛИ-НЕ |

| 7454 | 4-расширенных 2И-ИЛИ-НЕ |

| 7455 | 2-расширенных 4И-ИЛИ-НЕ (74H версия расширяемая) |

| 7456 | Делитель частоты 50 к 1 |

| 7457 | Делитель частоты 60 к 1 |

| 7458 | 2И-ИЛИ & 3И-ИЛИ |

| 7459 | 2И-ИЛИ-НЕ & 3И-ИЛИ-НЕ |

| 7460 | 2 элемента 4х входной расширитель |

| 7461 | 3 элемента 3х входной расширитель |

| 7462 | 3-2-2-3-И-ИЛИ расширитель |

| 7463 | 6 элементов детекторов тока |

| 7464 | 4-2-3-2И-ИЛИ-Н |

| 7465 | 4-2-3-2И-ИЛИ-Н |

| 7468 | 2 элемента 4х разрядный десятичный счетчик |

| 7469 | 2 элемента 4х разрядный двоичный счетчик |

| 7470 | AND-gated positive edge triggered J-K flip-flop with preset and clear |

| 74H71 | AND-or-gated J-K master-slave flip-flop with preset |

| 74L71 | AND-gated R-S master-slave flip-flop with preset and clear |

| 7472 | AND gated J-K master-slave flip-flop with preset and clear |

| 7473 | 2 элемента J-K flip-flop with clear |

| 7474 | 2 элемента D positive edge triggered flip-flop with preset and clear |

| 7475 | 4-bit bistable latch |

| 7476 | 2 элемента J-K flip-flop with preset and clear |

| 7477 | 4-bit bistable latch |

| 74H78 | 2 элемента positive pulse triggered J-K flip-flop with preset, common clock, and common clear (different pinout than 74L78 / 74Ls78) |

| 74L78 | 2 элемента positive pulse triggered J-K flip-flop with preset, common clock, and common clear |

| 74Ls78 | 2 элемента negative edge triggered J-K flip-flop with preset, common clock, and common clear |

| 7479 | 2 элемента D flip-flop |

| 741G79 | 1 элемент D-type flip-flop positive edge trigger non-inverting output |

| 7480 | gated full adder |

| 741G80 | 1 элемент D-type flip-flop positive edge trigger inverting output |

| 7481 | 1 элемент 6-bit random access memory |

| 7482 | 2-bit binary full adder |

| 7483 | 4-bit binary full adder |

| 7484 | 1 элемент6-bit random access memory |

| 7485 | 4-bit magnitude comparator |

| 7486 | 4е элемента 2-input XOR gate |

| 741G86 | 1 элемент 2 input exclusive-OR gate |

| 7487 | 4-bit true/complemen |

| 7488 | 256-bit read-only memory |

| 7489 | 64-bit random access memory |

| 7490 | decade counter (separate divide-by-2 and divide-by-5 sections) |

| 7491 | 8-bit shift register, serial In, serial out, gated input |

| 7492 | divide-by-12 counter (separate divide-by-2 and divide-by-6 sections) |

| 7493 | 4-bit binary counter (separate divide-by-2 and divide-by-8 sections) |

| 7494 | 4-bit shift register, 2 элемента asynchronous presets |

| 7495 | 4-bit shift register, parallel In, parallel out, serial input |

| 7496 | 5-bit parallel-In/pa |

| 7497 | synchronous 6-bit binary rate multiplier |

| 741G97 | configurable multiple-funct |

| 7498 | 4-bit data selector/stora |

| 7499 | 4-bit bidirectional universal shift register |

| 74100 | 2 элемента 4-bit bistable latch |

| 74101 | AND-or-gated J-K negative-edge- |

| 74102 | AND-gated J-K negative-edge- |

| 74103 | 2 элемента J-K negative-edge- |

| 74104 | J-K master-slave flip-flop |

| 74105 | J-K master-slave flip-flop |

| 74106 | 2 элемента J-K negative-edge- |

| 74107 | 2 элемента J-K flip-flop with clear |

| 74107a | 2 элемента J-K negative-edge- |

| 74108 | 2 элемента J-K negative-edge- |

| 74109 | 2 элемента J-Not-K positive-edge- |

| 74110 | AND-gated J-K master-slave flip-flop with data lockout |

| 74111 | 2 элемента J-K master-slave flip-flop with data lockout |

| 74112 | 2 элемента J-K negative-edge- |

| 74113 | 2 элемента J-K negative-edge- |

| 74114 | 2 элемента J-K negative-edge- |

| 74116 | 2 элемента 4-bit latch with clear |

| 74118 | 6 элементов set/reset latch |

| 74119 | 6 элементов set/reset latch |

| 74120 | 2 элемента pulse synchronizer/d |

| 74121 | monostable multivibrator |

| 74122 | retriggerable monostable multivibrator with clear |

| 74123 | 2 элемента retriggerable monostable multivibrator with clear |

| 741G123 | 1 элемент retriggerable monostable multivibrator with clear |

| 74124 | 2 элемента voltage-contro |

| 74125 | 4е элемента bus с буффером with three-state outputs, negative enable |

| 741G125 | с буффером/Line driver, three-state output with active low output enable |

| 74126 | 4е элемента bus с буффером with three-state outputs, positive enable |

| 74128 | 4е элемента 2НЕ-ИЛИ Line driver |

| 741G126 | с буффером/line driver, three-state output with active high output enable |

| 74130 | 4е элемента 2И с буффером with 30 v открытыми коллекторами на выходах |

| 74131 | 4е элемента 2И с буффером with 15 v открытыми коллекторами на выходах |

| 74132 | 4е элемента 2НЕ-И schmitt trigger |

| 74133 | 1 элемент3НЕ-И |

| 74134 | 1 элемент2НЕ-И with three-state output |

| 74135 | 4е элемента exclusive-or/N |

| 74136 | 4е элемента 2-input XOR gate с открытыми коллекторами на выходах |

| 74137 | 3 to 8-line decoder/demult |

| 74138 | 3 to 8-line decoder/demult |

| 74139 | 2 элемента 2 to 4-line decoder/demult |

| 74140 | 2 элемента 4НЕ-И line driver |

| 74141 | Двоично-десяти |

| 74142 | decade counter/latch/ |

| 74143 | decade counter/latch/ |

| 74144 | decade counter/latch/ |

| 74145 | Двоично-десяти |

| 74147 | 1 элемент0-line to 4-line priority encoder |

| 74148 | 8-line to 3-line priority encoder |

| 74150 | 1 элемент6-line to 1-line data selector/multi |

| 74151 | 8-line to 1-line data selector/multi |

| 74152 | 8-line to 1-line data selector/multi |

| 74153 | 2 элемента 4-line to 1-line data selector/multi |

| 74154 | 4-line to 16-line decoder/demult |

| 74155 | 2 элемента 2-line to 4-line decoder/demult |

| 74156 | 2 элемента 2-line to 4-line decoder/demult |

| 74157 | 4е элемента 2-line to 1-line data selector/multi |

| 74158 | 4е элемента 2-line to 1-line data selector/multi |

| 74159 | 4-line to 16-line decoder/demult |

| 74160 | synchronous 4-bit decade counter with asynchronous clear |

| 74161 | synchronous 4-bit binary counter with asynchronous clear |

| 74162 | synchronous 4-bit decade counter with synchronous clear |

| 74163 | synchronous 4-bit binary counter with synchronous clear |

| 74164 | 8-bit parallel-out serial shift register with asynchronous clear |

| 74165 | 8-bit serial shift register, parallel Load, complementary outputs |

| 74166 | parallel-Load 8-bit shift register |

| 74167 | synchronous decade rate multiplier |

| 74168 | synchronous 4-bit up/down decade counter |

| 74169 | synchronous 4-bit up/down binary counter |

| 74170 | 4 by 4 register file с открытыми коллекторами на выходах |

| 74172 | 1 элемент6-bit multiple port register file with three-state outputs |

| 74173 | 4е элемента d flip-flop with three-state outputs |

| 74174 | 6 элементов d flip-flop with common clear |

| 74175 | 4е элемента d edge-triggered flip-flop with complementary outputs and asynchronous clear |

| 74176 | presettable decade (bi-quinary) counter/latch |

| 74177 | presettable binary counter/latch |

| 74178 | 4-bit parallel-acces |

| 74179 | 4-bit parallel-acces |

| 74180 | 9-bit odd/even parity bit generator and checker |

| 74181 | 4-bit arithmetic logic unit and function generator |

| 74182 | lookahead carry generator |

| 74183 | 2 элемента carry-save full adder |

| 74184 | BCD to binary converter |

| 74185 | binary to BCD converter |

| 74186 | 512-bit (64×8) read-only memory с открытыми коллекторами на выходах |

| 74187 | 1 элемент024-bit (256×4) read only memory с открытыми коллекторами на выходах |

| 74188 | 256-bit (32×8) programmable read-only memory с открытыми коллекторами на выходах |

| 74189 | 64-bit (16×4) ram with inverting three-state outputs |

| 74190 | synchronous up/down decade counter |

| 74191 | synchronous up/down binary counter |

| 74192 | synchronous up/down decade counter with clear |

| 74193 | synchronous up/down binary counter with clear |

| 74194 | 4-bit bidirectional universal shift register |

| 74195 | 4-bit parallel-acces |

| 74196 | presettable decade counter/latch |

| 74197 | presettable binary counter/latch |

| 74198 | 8-bit bidirectional universal shift register |

| 74199 | 8-bit bidirectional universal shift register with J-Not-K serial inputs |

| 74200 | 256-bit ram with three-state outputs |

| 74201 | 256-bit (256×1) ram with three-state outputs |

| 74206 | 256-bit ram с открытыми коллекторами на выходах |

| 74209 | 1 элемент024-bit (1024×1) ram with three-state output |

| 74210 | octal с буффером |

| 74219 | 64-bit (16×4) ram with noninverting three-state outputs |

| 74221 | 2 элемента monostable multivibrator with schmitt trigger input |

| 74222 | 1 элемент6 by 4 synchronous FIFO memory with three-state outputs |

| 74224 | 1 элемент6 by 4 synchronous FIFO memory with three-state outputs |

| 74225 | asynchronous 16×5 FIFO memory |

| 74226 | 4-bit parallel latched bus transceiver with three-state outputs |

| 74230 | octal буффер/драйвер с three-state outputs |

| 74232 | 4е элемента NOR Schmitt trigger |

| 74237 | 1 элемент-of-8 decoder/demult |

| 74238 | 1 элемент-of-8 decoder/demult |

| 74239 | 2 элемента 2-of-4 decoder/demult |

| 74240 | octal с буффером with Inverted three-state outputs |

| 74241 | octal с буффером with noninverted three-state outputs |

| 74242 | 4е элемента bus transceiver with Inverted three-state outputs |

| 74243 | 4е элемента bus transceiver with noninverted three-state outputs |

| 74244 | octal с буффером with noninverted three-state outputs |

| 74245 | octal bus transceiver with noninverted three-state outputs |

| 74246 | Двоично-десяти |

| 74247 | Двоично-десяти |

| 74248 | Двоично-десяти |

| 74249 | Двоично-десяти |

| 74251 | 8-line to 1-line data selector/multi |

| 74253 | 2 элемента 4-line to 1-line data selector/multi |

| 74255 | 2 элемента 4-bit addressable latch |

| 74256 | 2 элемента 4-bit addressable latch |

| 74257 | 4е элемента 2-line to 1-line data selector/multi |

| 74258 | 4е элемента 2-line to 1-line data selector/mulit |

| 74259 | 8-bit addressable latch |

| 74260 | 2 элемента 5-input NOR gate |

| 74261 | 2-bit by 4-bit parallel binary multiplier |

| 74265 | 4е элемента complementary output elements |

| 74266 | 4е элемента 2-input XNOR gate with open collectoroutpu |

| 74270 | 2048-bit (512×4) read only memory с открытыми коллекторами на выходах |

| 74271 | 2048-bit (256×8) read only memory с открытыми коллекторами на выходах |

| 74273 | 8-bit register with reset |

| 74274 | 4-bit by 4-bit binary multiplier |

| 74275 | 7-bit slice Wallace tree |

| 74276 | 4е элемента J-Not-K edge-triggered Flip-Flops with separate clocks, common preset and clear |

| 74278 | 4-bit cascadeable priority registers with latched data inputs |

| 74279 | 4е элемента set-reset latch |

| 74280 | 9-bit odd/even Parity bit Generator/chec |

| 74281 | 4-bit parallel binary accumulator |

| 74283 | 4-bit binary Full adder |

| 74284 | 4-bit by 4-bit parallel binary multiplier (low order 4 bits of product) |

| 74285 | 4-bit by 4-bit parallel binary multiplier (high order 4 bits of product) |

| 74287 | 1 элемент024-bit (256×4) programmable read-only memory with three-state outputs |

| 74288 | 256-bit (32×8) programmable read-only memory with three-state outputs |

| 74289 | 64-bit (16×4) RAM с открытыми коллекторами на выходах |

| 74290 | decade counter (separate divide-by-2 and divide-by-5 sections) |

| 74291 | 4-bit universal shift register, binary up/down counter, synchronous |

| 74292 | programmable frequency divider/digita |

| 74293 | 4-bit binary counter (separate divide-by-2 and divide-by-8 sections) |

| 74294 | programmable frequency divider/digita |

| 74295 | 4-bit bidirectional register with three-state outputs |

| 74297 | digital phase-locked-l |

| 74298 | 4е элемента 2-input multiplexer with storage |

| 74299 | 8-bit bidirectional universal shift/storage register with three-state outputs |

| 74301 | 256-bit (256×1) random access memory с выходами с открытыми коллекторами |

| 74309 | 1 элемент024-bit (1024×1) random access memory с выходами с открытыми коллекторами |

| 74310 | octal с буффером с триггерами Шмитта на входах |

| 74314 | 1 элемент024-bit random access memory |

| 74320 | crystal controlled oscillator |

| 74322 | 8-bit shift register with sign extend, three-state outputs |

| 74323 | 8-bit bidirectional universal shift/storage register with three-state outputs |

| 74324 | voltage controlled oscillator (or crystal controlled) |

| 74340 | octal с буффером с триггерами Шмитта на входах and three-state inverted outputs |

| 74341 | octal с буффером с триггерами Шмитта на входах and three-state noninverted outputs |

| 74344 | octal с буффером с триггерами Шмитта на входах and three-state noninverted outputs |

| 74348 | 8 to 3-line priority encoder with three-state outputs |

| 74350 | 4-bit shifter with three-state outputs |

| 74351 | 2 элемента 8-line to 1-line data selectors/mult |

| 74352 | 2 элемента 4-line to 1-line data selectors/mult |

| 74353 | 2 элемента 4-line to 1-line data selectors/mult |

| 74354 | 8 to 1-line data selector/multi |

| 74356 | 8 to 1-line data selector/multi |

| 74361 | bubble memory function timing generator |

| 74362 | four-phase clock generator/driv |

| 74365 | 6 элементов с буффером with noninverted three-state outputs |

| 74366 | 6 элементов с буффером with Inverted three-state outputs |

| 74367 | 6 элементов с буффером with noninverted three-state outputs |

| 74368 | 6 элементов с буффером with Inverted three-state outputs |

| 74370 | 2048-bit (512×4) read-only memory with three-state outputs |

| 74371 | 2048-bit (256×8) read-only memory with three-state outputs |

| 74373 | octal transparent latch with three-state outputs |

| 741G373 | 1 элемент transparent latch with three-state output |

| 74374 | octal register with three-state outputs |

| 741G374 | 1 элемент d-type flip-flop with three-state output |

| 74375 | 4е элемента bistable latch |

| 74376 | 4е элемента J-Not-K flip-flop with common clock and common clear |

| 74377 | 8-bit register with clock enable |

| 74378 | 6-bit register with clock enable |

| 74379 | 4-bit register with clock enable and complementary outputs |

| 74380 | 8-bit multifunction register |

| 74381 | 4-bit arithmetic logic unit/function generator with generate and propagate outputs |

| 74382 | 4-bit arithmetic logic unit/function generator with ripple carry and overflow outputs |

| 74385 | 4е элемента 4-bit adder/subtract |

| 74386 | 4е элемента 2-input XOR gate |

| 74387 | 1 элемент024-bit (256×4) programmable read-only memory с открытыми коллекторами на выходах |

| 74388 | 4-bit register with standard and three-state outputs |

| 74390 | 2 элемента 4-bit decade counter |

| 74393 | 2 элемента 4-bit binary counter |

| 74395 | 4-bit universal shift register with three-state outputs |

| 74398 | 4е элемента 2-input mulitplexers with storage and complementary outputs |

| 74399 | 4е элемента 2-input mulitplexer with storage |

| 74405 | 1 элемент to 8 decoder, equivalent to Intel 8205, only found as UCY74S405 so might be non-TI number |

| 74408 | 8-bit parity tree |

| 74412 | multi-mode с буфферомed 8-bit latches with three-state outputs and clear |

| 74423 | 2 элемента retriggerable monostable multivibrator |

| 74424 | two-phase clock generator/driv |

| 74425 | 4е элемента gates with three-state outputs and active low enables |

| 74426 | 4е элемента gates with three-state outputs and active high enables |

| 74428 | system controller for 8080a |

| 74438 | system controller for 8080a |

| 74440 | 4е элемента tridirectional bus transceiver with noninverted открытыми коллекторами на выходах |

| 74441 | 4е элемента tridirectional bus transceiver with Inverted открытыми коллекторами на выходах |

| 74442 | 4е элемента tridirectional bus transceiver with noninverted three-state outputs |

| 74443 | 4е элемента tridirectional bus transceiver with Inverted three-state outputs |

| 74444 | 4е элемента tridirectional bus transceiver with Inverted and noninverted three-state outputs |

| 74448 | 4е элемента tridirectional bus transceiver with Inverted and noninverted открытыми коллекторами на выходах |

| 74450 | 1 элемент6-to-1 multiplexer with complementary outputs |

| 74451 | 2 элемента 8-to-1 multiplexer |

| 74452 | 2 элемента decade counter, synchronous |

| 74453 | 2 элемента binary counter, synchronous |

| 74453 | 4е элемента 4-to-1 multiplexer |

| 74454 | 2 элемента decade up/down counter, synchronous, preset input |

| 74455 | 2 элемента binary up/down counter, synchronous, preset input |

| 74456 | NBCD (Natural binary coded decimal) adder |

| 74460 | bus transfer switch |

| 74461 | 8-bit presettable binary counter with three-state outputs |

| 74462 | fiber-optic link transmitter |

| 74463 | fiber-optic link receiver |

| 74465 | octal с буффером with three-state outputs |

| 74468 | 2 элемента mos-to-ttL level converter |

| 74470 | 2048-bit (256×8) programmable read-only memory с открытыми коллекторами на выходах |

| 74471 | 2048-bit (256×8) programmable read-only memory with three-state outputs |

| 74472 | programmable read-only memory с открытыми коллекторами на выходах |

| 74473 | programmable read-only memory with three-state outputs |

| 74474 | programmable read-only memory с открытыми коллекторами на выходах |

| 74475 | programmable read-only memory with three-state outputs |

| 74481 | 4-bit slice processor elements |

| 74482 | 4-bit slice expandable control elements |

| 74484 | BCD-to-binary converter |

| 74485 | binary-to-BCD converter |

| 74490 | 2 элемента decade counter |

| 74491 | 1 элемент0-bit binary up/down counter with limited preset and three-state outputs |

| 74498 | 8-bit bidirectional shift register with parallel inputs and three-state outputs |

| 74508 | 8-bit multiplier/div |

| 74520 | 8-bit comparator |

| 74521 | 8-bit comparator |

| 74526 | fuse programmable identity comparator, 16 bit |

| 74527 | fuse programmable identity comparator, 8 bit + 4 bit conventional Identity comparator |

| 74528 | fuse programmable Identity comparator, 12 bit |

| 74531 | octal transparent latch with 32 ma three-state outputs |

| 74532 | octal register with 32 ma three-state outputs |

| 74533 | octal transparent latch with inverting three-state Logic outputs |

| 74534 | octal register with inverting three-state outputs |

| 74535 | octal transparent latch with inverting three-state outputs |

| 74536 | octal register with inverting 32 ma three-state outputs |

| 74537 | Двоично-десяти |

| 74538 | 1 элемент of 8 decoder with three-state outputs |

| 74539 | 2 элемента 1 of 4 decoder with three-state outputs |

| 74540 | inverting octal с буффером with three-state outputs |

| 74541 | non-inverting octal с буффером with three-state outputs |

| 74544 | non-inverting octal registered transceiver with three-state outputs |

| 74558 | 8-bit by 8-bit multiplier with three-state outputs |

| 74560 | 4-bit decade counter with three-state outputs |

| 74561 | 4-bit binary counter with three-state outputs |

| 74563 | 8-bit d-type transparent latch with inverting three-state outputs |

| 74564 | 8-bit d-type edge-triggered register with inverting three-state outputs |

| 74568 | decade up/down counter with three-state outputs |

| 74569 | binary up/down counter with three-state outputs |

| 74573 | octal D-type transparent latchwith three-state outputs |

| 74574 | octal D-type edge-triggered flip-flop with three-state outputs |

| 74575 | octal D-type flip-flop with synchronous clear, three-state outputs |

| 74576 | octal D-type flip-flop with inverting three-state outputs |

| 74577 | octal D-type flip-flop with synchronous clear, inverting three-state outputs |

| 74580 | octal transceiver/la |

| 74589 | 8-bit shift register with input latch, three-state outputs |

| 74590 | 8-bit binary counter with output registers and three-state outputs |

| 74592 | 8-bit binary counter with input registers |

| 74593 | 8-bit binary counter with input registers and three-state outputs |

| 74594 | serial-in shift register with output registers |

| 74595 | serial-in shift register with output latches |

| 74596 | serial-in shift register with output registers and открытыми коллекторами на выходах |

| 74597 | serial-out shift register with input latches |

| 74598 | shift register with input latches |

| 74600 | dynamic memory refresh controller, transparent and burst modes, for 4K or 16K drams |

| 74601 | dynamic memory refresh controller, transparent and burst modes, for 64K drams |

| 74602 | dynamic memory refresh controller, cycle steal and burst modes, for 4K or 16K drams |

| 74603 | dynamic memory refresh controller, cycle steal and burst modes, for 64K drams |

| 74604 | octal 2-input multiplexer with latch, high-speed, with three-state outputs |

| 74605 | latch, high-speed, с открытыми коллекторами на выходах |

| 74606 | octal 2-input mulitplexer with latch, glitch-free, with three-state outputs |

| 74607 | octal 2-input mulitplexer with latch, glitch-free, с открытыми коллекторами на выходах |

| 74608 | memory cycle controller |

| 74610 | memory mapper, latched, three-state outputs |

| 74611 | memory mapper, latched, открытыми коллекторами на выходах |

| 74612 | memory mapper, three-state outputs |

| 74613 | memory mapper, открытыми коллекторами на выходах |

| 74620 | octal bus transceiver, inverting, three-state outputs |

| 74621 | octal bus transceiver, noninverting, открытыми коллекторами на выходах |

| 74622 | octal bus transceiver, inverting, открытыми коллекторами на выходах |

| 74623 | octal bus transceiver, noninverting, three-state outputs |

| 74624 | voltage-contro |

| 74625 | 2 элемента voltage-contro |

| 74626 | 2 элемента voltage-contro |

| 74627 | 2 элемента voltage-contro |

| 74628 | voltage-contro |

| 74629 | 2 элемента voltage-contro |

| 74630 | 1 элемент6-bit error detection and correction (EDAC) with three-state outputs |

| 74631 | 1 элемент6-bit error detection and correction с открытыми коллекторами на выходах |

| 74632 | 32-bit error detection and correction |

| 74638 | octal bus transceiver with inverting three-state outputs |

| 74639 | octal bus transceiver with noninverting three-state outputs |

| 74640 | octal bus transceiver with inverting three-state outputs |

| 74641 | octal bus transceiver with noninverting открытыми коллекторами на выходах |

| 74642 | octal bus transceiver with inverting открытыми коллекторами на выходах |

| 74643 | octal bus transceiver with mix of inverting and noninverting three-state outputs |

| 74644 | octal bus transceiver with mix of inverting and noninverting открытыми коллекторами на выходах |

| 74645 | octal bus transceiver |

| 74646 | octal bus transceiver/la |

| 74647 | octal bus transceiver/la |

| 74648 | octal bus transceiver/la |

| 74649 | octal bus transceiver/la |

| 74651 | octal bus transceiver/re |

| 74652 | octal bus transceiver/re |

| 74653 | octal bus transceiver/re |

| 74654 | octal bus transceiver/re |

| 74658 | octal bus transceiver with Parity, inverting |

| 74659 | octal bus transceiver with Parity, noninverting |

| 74664 | octal bus transceiver with Parity, inverting |

| 74665 | octal bus transceiver with Parity, noninverting |

| 74668 | synchronous 4-bit decade Up/down counter |

| 74669 | synchronous 4-bit binary Up/down counter |

| 74670 | 4 by 4 register File with three-state outputs |

| 74671 | 4-bit bidirectional shift register/latch /multiplexer with three-state outputs |

| 74672 | 4-bit bidirectional shift register/latch |

| 74673 | 1 элемент6-bit serial-in serial-out shift register with output storage registers, three-state outputs |

| 74674 | 1 элемент6-bit parallel-in serial-out shift register with three-state outputs |

| 74677 | 1 элемент6-bit address comparator with enable |

| 74678 | 1 элемент6-bit address comparator with latch |

| 74679 | 1 элемент2-bit address comparator with latch |

| 74680 | 1 элемент2-bit address comparator with enable |

| 74681 | 4-bit parallel binary accumulator |

| 74682 | 8-bit magnitude comparator |

| 74683 | 8-bit magnitude comparator с открытыми коллекторами на выходах |

| 74684 | 8-bit magnitude comparator |

| 74685 | 8-bit magnitude comparator с открытыми коллекторами на выходах |

| 74686 | 8-bit magnitude comparator with enable |

| 74687 | 8-bit magnitude comparator with enable |

| 74688 | 8-bit equality comparator |

| 74689 | 8-bit magnitude comparator с открытыми коллекторами на выходах |

| 74690 | three state outputs |

| 74691 | 4-bit binary counter/latch/ |

| 74692 | 4-bit decimal counter/latch/ |

| 74693 | 4-bit binary counter/latch/ |

| 74694 | 4-bit decimal counter/latch/ |

| 74695 | 4-bit binary counter/latch/ |

| 74696 | 4-bit decimal counter/regist |

| 74697 | 4-bit binary counter/regist |

| 74698 | 4-bit decimal counter/regist |

| 74699 | 4-bit binary counter/regist |

| 74716 | programmable decade counter |

| 74718 | programmable binary counter |

| 74724 | voltage controlled multivibrator |

| 74740 | octal с буффером/Line driver, inverting, three-state outputs |

| 74741 | octal с буффером/Line driver, noninverting, three-state outputs, mixed enable polarity |

| 74744 | octal с буффером/Line driver, noninverting, three-state outputs |

| 74748 | 8 to 3-line priority encoder |

| 74779 | 8-bit bidirectional binary counter (3-state) |

| 74783 | synchronous address mulitplexer |

| 74790 | error detection and correction (EDAC) |

| 74794 | 8-bit register with readback |

| 74795 | octal с буффером with three-state outputs |

| 74796 | octal с буффером with three-state outputs |

| 74797 | octal с буффером with three-state outputs |

| 74798 | octal с буффером with three-state outputs |

| 74804 | 6 элементов 2НЕ-И drivers |

| 74805 | 6 элементов 2НЕ-ИЛИ drivers |

| 74808 | 6 элементов 2-input AND drivers |

| 74832 | 6 элементов 2-input OR drivers |

| 74848 | 8 to 3-line priority encoder with three-state outputs |

| 74873 | octal transparent latch |

| 74874 | octal d-type flip-flop |

| 74876 | octal d-type flip-flop with inverting outputs |

| 74878 | 2 элемента 4-bit d-type flip-flop with synchronous clear, noninverting three-state outputs |

| 74879 | 2 элемента 4-bit d-type flip-flop with synchronous clear, inverting three-state outputs |

| 74880 | octal transparent latchwith inverting outputs |

| 74881 | arithmetic logic unit |

| 74882 | 32-bit lookahead carry generator |

| 74888 | 8-bit slice processor |

| 74901 | 6 элементов inverting TTL с буффером |

| 74902 | 6 элементов non-inverting TTL с буффером |

| 74903 | 6 элементов inverting CMOS с буффером |

| 74904 | 6 элементов non-inverting CMOS с буффером |

| 74905 | 1 элемент2-Bit successive approximation register |

| 74906 | 6 элементов open drain n-channel с буфферомs |

| 74907 | 6 элементов open drain p-channel с буфферомs |

| 74908 | 2 элемента CMOS 30V relay driver |

| 74909 | 4е элемента voltage comparator |

| 74910 | 256×1 CMOS static RAM |

| 74911 | 4 digit expandable display controller |

| 74912 | 6 digit BCD display controller and driver |

| 74914 | 6 элементов schmitt trigger with extended input voltage |

| 74915 | seven segment to BCD decoder |

| 74917 | 6 digit Hex display controller and driver |

| 74918 | 2 элемента CMOS 30V relay driver |

| 74920 | 256×4 CMOS static RAM |

| 74921 | 256×4 CMOS static RAM |

| 74922 | 1 элемент6-key encoder |

| 74923 | 20-key encoder |

| 74925 | 4-digit counter/displa |

| 74926 | 4-digit counter/displa |

| 74927 | 4-digit counter/displa |

| 74928 | 4-digit counter/displa |

| 74929 | 1 элемент024×1 CMOS static RAM |

| 74930 | 1 элемент024×1 CMOS static RAM |

| 74932 | phase comparator |

| 74933 | address bus comparator |

| 74934 | =ADC0829 ADC, see corresponding NSC datasheet |

| 74935 | 3.5-digit digital voltmeter (DVM) support chip for multiplexed 7-segment displays |

| 74936 | 3.75-digit digital voltmeter (DVM) support chip for multiplexed 7-segment displays |

| 74937 | =ADC3511 ADC, see corresponding NSC datasheet |

| 74938 | =ADC3711 ADC, see corresponding NSC datasheet |

| 74941 | octal bus/line drivers/line receivers |

| 74945 | 4 digit up/down counter with decoder and driver |

| 74947 | 4 digit up/down counter with decoder and driver |

| 74948 | =ADC0816 ADC, see corresponding NSC datasheet |

| 74949 | =ADC0808 ADC, see corresponding NSC datasheet |

| 74949 | =ADC0808 ADC, see corresponding NSC datasheet |

| 741005 | 6 элементов inverting с буффером with open-collector output |

| 741035 | 6 элементов noninverting с буфферомs with open-collector outputs |

| 742960 | error detection and correction (EDAC) |

| 742961 | edac bus с буффером, inverting |

| 742962 | edac bus с буффером, noninverting |

| 742968 | dynamic memory controller |

| 742969 | memory timing controller for use with EDAC |

| 742970 | memory timing controller for use without EDAC |

| 741G3208 | 1 элемент 3 input OR-AND Gate; |

| 744002 | 2 элемента 4НЕ-ИЛИ |

| 744015 | 2 элемента 4-bit shift registers |

| 744017 | 5-stage ÷10 Johnson counter |

| 744020 | 1 элемент4-stage binary counter |

| 744024 | 7 stage ripple carry binary counter |

| 744028 | Двоично-десяти |

| 744040 | 1 элемент2-stage binary ripple counter |

| 744046 | phase-locked loop and voltage-contro |

| 744049 | 6 элементов inverting с буффером |

| 744050 | 6 элементов с буффером/conve |

| 744051 | high-speed CMOS 8-channel analog mulitplexer/de |

| 744052 | 2 элемента 4-channel analog multiplexer/de |

| 744053 | 3 элемента 2-channel analog multiplexer/de |

| 744059 | programmable divide-by-N counter |

| 744060 | 1 элемент4-stage binary ripple counter with oscillator |

| 744066 | 4е элемента bilateral switches |

| 744067 | 1 элемент6-chann |

| 744075 | 3 элемента 3-input OR gate |

| 744078 | 8-input OR/NOR gate |

| 744094 | 8-bit three-state shift register/latch |

| 744316 | 4е элемента analog switch |

| 744511 | Двоично-десяти |

| 744520 | 2 элемента 4-bit synchronous binary counter |

| 744538 | 2 элемента retriggerable precision monostable multivibrator |

| 747007 | 6 элементов с буффером |

| 747266 | 4е элемента 2-input XNOR gate |

| 7429841 | 1 элемент0-bit bus-interface D-type latch with 3-state outputs |

| 7440103 | presettable 8-bit synchronous down counter |

| 7440105 | 4-bit by 16-word FIFO register |

На склад поступили логические микросхемы фирмы Texas Instruments

Texas Instruments —американская компания, производитель полупроводниковых элементов, микросхем, электроники и изделий на их основе. Является четвертым в мире по размеру производителем полупроводниковых приборов. Занимает первое место по производству микросхем для мобильных устройств, а также первое место по производству цифровых сигнальных процессоров и аналоговых полупроводников.

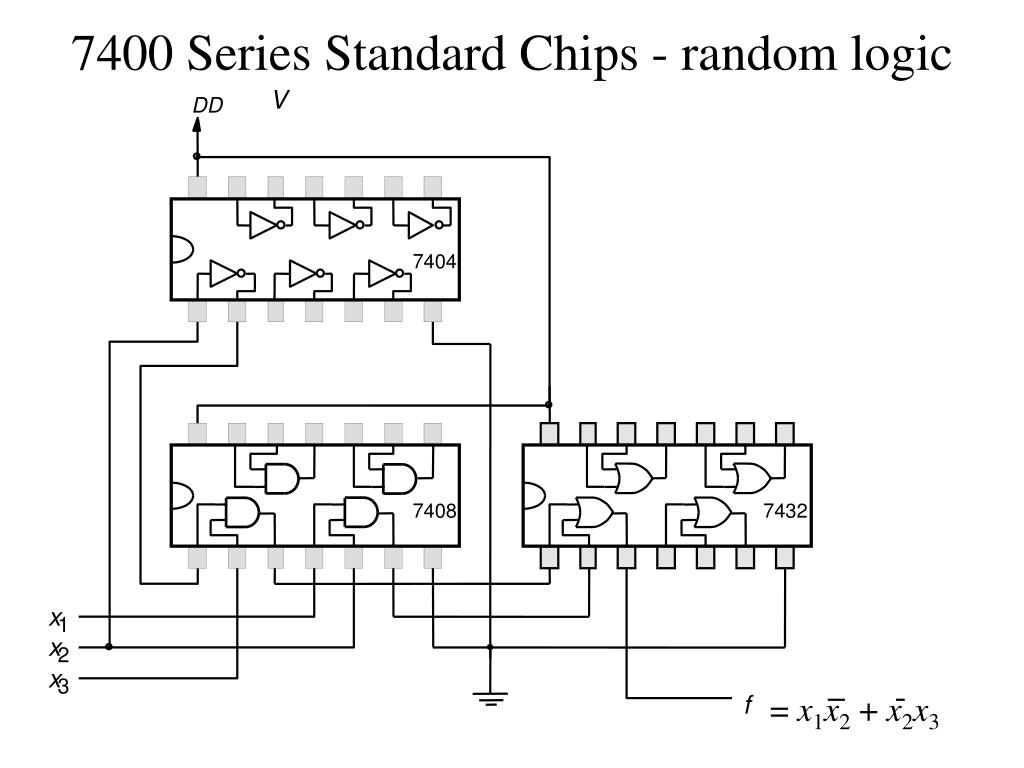

Состоялось существенное пополнение склада логическими микросхемами 74 и 40 серии производства компании Texas Instruments.

74 серия содержит несколько сотен типов микросхем с функциями от базовых логических операций, триггеров, счётчиков, до шинных формирователей, передатчиков сигнала и арифметико-логических устройств.

Изначально семейство разрабатывалось для цифровой логики, но сегодня в нём можно встретить и аналоговые устройства, например, триггеры Шмитта. Новые КМОП версии 74 серии также пригодны для использования в качестве аналоговых усилителей с отрицательной обратной связью, если применить их подобно операционным усилителям только с одним инвертирующим входом.

Микросхемы 74 серии ранних разработок строились на биполярных транзисторах. Новые подсерии, в той или иной степени совместимые функционально и по логическим уровням, используют КМОП-технологию или комбинацию из биполярных и КМОП транзисторов. Биполярные транзисторы обеспечивали большую скорость, но потребляли больше энергии, чем 40 серия, базирующаяся на КМОП-технологиях. Биполярные устройства, ко всему прочему, более требовательны к уровню питающего напряжения, обычно 5 В, в то время как КМОП поддерживают широкий диапазон напряжений.

Микросхемы 74 серии создавались на разных технологиях, но совместимость сохранялась с оригинальными уровнями логики TTL и напряжением питания. Несмотря на то, что элементы построены на КМОП-логике, а не ТТЛ, они сохраняют одинаковые номера для определения идентичных логических функций в различных подсериях.

Микросхемы 74 серии у Texas Instruments используют следующую схему обозначения:

- Первые две или три буквы обозначают назначение и технологию ИС:

- AC — биполярные ИС улучшенные

- SBP — биполярные микропроцессоры

- SMJ — МОП-ИС памяти и микропроцессоры

- SN — стандартные ИС

- TAC — КМОП-логические матрицы

- TAL — ТТЛШ-логические матрицы с пониженной потребляемой мощностью

- TAT — ТТЛШ-логические матрицы

- TBP — биполярные ИС памяти

- TC — формирователи видеосигналов для ПЗС

- TCM — ИС для телекоммуникации

- TIBPAL — биполярные ПЛМ

- TIED — детекторы инфракрасного излучения

- TIL — оптоэлектронные ИС

- TL — аналоговые ИС

- TLC — аналоговые КМОП-ИС

- TMS — МОП-ИС памяти и микропроцессоры

- TM — модули микроЭВМ

- VM — ИС памяти речевого синтеза

- Две цифры префикса температурного диапазона:

- 54, 55 — −55…+125 °C для военного варианта

- 74, 75, 76 — 0…+70 °C для коммерческого варианта

- при обозначении в суффиксе:

- отсутствие знака — 0…+70 °C

- C — 0….+70 °C

- E — −40….+85 °C

- I — −25….+85 °C

- L — 0….+70 °C

- M — −55…+125 °C

- S — специальный диапазон

- или применяемую технологию:

- 54, 74 — стандартная ТТЛ

- 54H, 74H (High) — быстродействующая

- 74F (Fast) — сверхбыстродействующая

- 54L (Low-power) — с пониженной потребляемой мощностью

- 54LS, 74LS (Low-power Schottky) — ТТЛШ с пониженной потребляемой мощностью

- 54S, 74S (Schottky) — ТТЛШ

- 55, 75 — стандартные интерфейсы

- 54AS, 74AS (Advanced Schottky) — улучшенная ТТЛШ

- 54HC, 54HCT, 74HC, 74HCT (High-speed CMOS) — быстродействующие на основе КМОП-структур

- 54ALS, 74ALS (Advanced Low-power Schottky) — улучшенная ТТЛШ с пониженной потребляемой мощностью

- 76 — улучшенные ИС

- при обозначении в суффиксе:

- До четырёх символов, означающих подсерию, обозначающей тип используемой логики.

- Две или более цифры, присвоенные устройству.

- Дополнительные буквы и цифры могут обозначать тип корпуса, категорию качества или иную информацию.

Например, SN74ALS245 означает микросхему, произведённую Texas Instruments, выполненную в коммерческой версии на основе логики ТТЛ, из семейства улучшенных Шоттки с низким энергопотреблением, функция — двунаправленный 8-битный буфер.

40 серия интегральных микросхем реализует различные логические функции, используя КМОП технологию. Она была представлена в 1968 году как малопотребляющая и более гибкая альтернатива 74 серии с ТТЛ логикой.

Изначально 40 серия была медленнее ТТЛ микросхем 74 серии, но имела намного меньшее энергопотребление, была способна работать с намного большим диапазоном питающего напряжения (от 3В до 15В) и имела большую нагрузочную способность. Но её на порядок меньшая скорость (изначально была возможность работы на частотах до 1 МГц, в сравнении с 10 МГц у ТТЛ) ограничивала область применения статичными и низкоскоростными устройствами. Позже новые технологии производства решили проблемы быстродействия, сохранив при этом обратную совместимость с большинством типов микросхем. Недостатком этой серии является высокая вероятность повреждения статическим разрядом из-за высокого сопротивления входов. Но со временем преимущества КМОП (особенно в поздних сериях, например, 74HC) вытеснили старые ТТЛ микросхемы. Микросхемы серии 40 до сих пор широко доступны, но их значимость уже не так велика, как раньше.

В 1990-х годах Texas Instruments перенесла 40 серию на новую HCMOS технологию, из подобных микросхем можно рассмотреть 74HCT4060, предоставляющую функциональность 4060 ИМС, но имеющую большую скорость.

Оригинальная 40 серия была представлена в двух версиях: серия A была небуферизированная, тогда как B обладала буферизированными входами и выходами (в виде дополнительных простых логических вентилей). Буферизированные выходы могут отдавать больший ток, чем вариант без буфера, что в некоторых случаях позволяет не использовать дискретные транзисторные ключи. Версии с буфером также обладают большей скоростью переключения, т.к. нарастание сигнала происходит быстрее, но тем не менее общая задержка на прохождение сигнала больше из-за дополнительных элементов. Буферизированные версии менее чувствительны к электростатическому разряду. Разработчик должен взвешивать плюсы и минусы обоих версий в соответствии с особенностями схемы, используемой в устройстве.

Сегодня логические микросхемы 74 и 40 серии используются в потребительской и промышленной электронике в корпусах для поверхностного монтажа. Устройства в DIP-корпусах также доступны для большинства типов микросхем, они много лет широко использовались повсеместно, однако теперь их применяют только для быстрого макетирования при разработке устройств и обучения.

Новое поступление:

Микросхема 74HCT373D

Модель: Микросхема 74HCT373D

Краткое описание

Микросхемы 74HCT373N / 74HCT373D производства Philips представляют собой восьмиразрядные регистры хранения информации, тактируемые импульсом, с возможностью перевода выходов в высокоимпедансное состояние. Отечественный аналог — ИР22.

Запись информации в триггеры регистра происходит при подаче лог. 1 на вход LE, в этом случае сигналы на выходах регистра повторяют входные, регистр «прозрачен» для сигналов на входах D1 — D8. При подаче лог. 0 на вход LE регистр переходит в режим хранения информации.

Выходы микросхемы находятся в активном состоянии, если на вход OE подан лог. 0. Если же на вход ОE подать лог. 1,выходы регистра переходят в высокоимпедансное состояние. Сигнал на входе OE не влияет на запись в триггеры, запись может производиться как при лог. 0, так и при лог. 1 на этом входе.

Основные характеристики 74HCT373:

|

Напряжение питания (Vdd) |

+4,5..+5,5V |

|

Выходной ток (0/1) макс. |

35mA |

|

Нагруз. способность |

15 входов серии 74LS (К555) |

|

Ток потребления (статический) |

40uA |

|

Входной ток |

<1uA |

|

Типовая задержка |

18nS |

|

Рабочий диапазон температур |

-40oC..+125oC |

|

Корпус |

DIP-20 SO-20w |

|

Отечественный аналог |

ИР22 |

|

Корпус: DIP-14

Корпус: SO-14 |

Микросхема 74HC00N / 74HC00D представляет собой 4 логических элемента 2И-НЕ. Микросхема 74HC00 предназначена для работы при напряжении питания от 2V до 6V, по входным и выходным уровням совместима с другими микросхемами серий КМОП.

Таблица истинности 2И-НЕ:

|

Расположение выводов 74HC00:

Более подробные характеристики микросхемы SN74HC00N(D) с временными параметрами и диаграммами работы Вы можете получить скачав файл документации ниже (на английском языке). |

Технические характеристики 74HC00:

|

| Импортная серия | Серия ГОСТ | Напряжение питания Vcc±10% | Совместимость | Входной ток mkA, при Vccmax | Ток нагрузки mA, при Vccmax | Ток потребления Icc, mkA | Быстродействие | |||

| по входам | по выходам | I IL | I IH | I OL | I OH | |||||

| 74AC | КР1554 | 3,3/5 | CMOS | TTL,CMOS | -1 | 1 | 24 | -24 | 80 | 7,5 |

| 74ACT | КР1594 | 5 | TTL,CMOS | TTL,CMOS | -1 | 1 | 24 | -24 | 80 | 10 |

| 74HC | КР1564 | 2/4,5/6 | CMOS | TTL,CMOS | -1 | 1 | 6 | -6 | 80 | 25 |

| 74AS | КР1530 | 5 | TTL | TTL | -1,6mA | 5 | 64 | -15 | 90 мА | 6,5 |

| 74F | КР1531 | 5 | TTL | TTL | -1,0mA | 20 | 64 | -15 | 90 mA | 6,2 |

| 74ALS | КР1533 | 5 | TTL | TTL | -0,1mA | 20 | 24 | -15 | 27 мА | 10 |

| 74LS | КР555 | 5 | TTL | TTL | -200 | 20 | 24 | -15 | 54 мА | 18 |

| 74S | КР531 | 5 | TTL | TTL | -400 | 50 | 64 | -15 | 120 мА | 9 |

| 74 | КР155 | 5 | TTL | TTL | -1,6mA | 40 | 40 | -250мкА | 41 мА | 30 |

| 74 серия | ГОСТ | Назначение | 74 серия | ГОСТ | Назначение | 74 серия | ГОСТ | Назначение | ||

| 00 | ЛА3 | Четыре логических элемента 2И-НЕ | 136 | ЛП12 | 4 логических элемента «исключающее ИЛИ» с открытым коллектором | 301 | РУ6 | статическое ОЗУ 1024×1 | ||

| 01 | ЛА8 | Четыре логических элемента 2И-НЕ с открытым коллектором | 138 | ИД7 | демультиплексор 3 в 8 со стробом и логикой | 322 | ИР28 | 8-разрядный последовательно-параллельный регистр | ||

| 02 | ЛЕ1 | Четыре логических элемента 2ИЛИ-НЕ | 129 | ИД14 | 2 демультиплексора со 1 в 4 стробом | 323 | ИР29 | 8-разрядный универсальный регистр с тремя состояниями | ||

| 03 | ЛА9 | Четыре логических элемента 2И-НЕ с открытым коллектором | 140 | ЛА16 | Два логических элемента 4И-НЕ работающих на 50 Ом (I(0)=60 мА, I(1)= 40 мА) | 348 | ИВ2 | Каскадируемый приоритетный кодер 8-3 с тремя состояниями | ||

| 04 | ЛН1 | Шесть логических элементов НЕ | 141 | ИД1 | Высоковольтный дешифратор управления газоразрядным индикатором | 350 | ИР42 | 4-разрядный сдвигатель на 0,1,2,3 разряда с тремя состояниями | ||

| 05 | ЛН2 | Шесть логических элементов НЕ с открытым коллектором | 145 | ИД10 | Полный дешифратор 2-10 кода в десятичный с открытым коллектором (15 В) | 352 | КП19 | Сдвоенный мультиплексор 4 в 1, инвертирующий | ||

| 06 | ЛН3 | Шесть мощных (40 мА) инверторов с высоковольтным открытым коллектором (30 В) | 147 | ИВ3 | Приоритетный кодер 10 в 4 | 353 | КП17 | Сдвоенный инверсный мультиплексор 4 в 1 с 3 состояниями | ||

| 07 | ЛП9 | Шесть мощных (40 мА) неинверторов с высоковольтным открытым коллектором (30 В) | 148 | ИВ1 | Каскадируемый приоритетный кодер 8-3 | 365 | ЛП10 | Шесть мощных (32 мА) драйверов-неинверторов с общим стробированием выхода (3 состояния) | ||

| 08 | ЛИ1 | Четыре логических элемента 2И | 150 | КП1 | Мультиплексор 16 в 1 со стробом и инверсией | 366 | ЛН6 | Шесть мощных (32 мА) драйверов-инверторов с общим стробированием выходов (3 состояния) | ||

| 09 | ЛИ2 | Четыре логических элемента 2И с открытым коллектором | 151 | КП7 | Мультиплексор 8 в 1 с инверсией (со стробом) | 367 | ЛП11 | Шесть мощных (32 мА) драйверов-неинверторов со стробированием 2-х и 4-х линий (3 состояния) | ||

| 10 | ЛА4 | Три логических элемента 3И-НЕ | 152 | КП5 | Мультиплексор 8 в 1 с инверсией (со стробом) | 368 | ЛН8 | Шесть мощных инверторов | ||

| 11 | ЛИ3 | Три логических элемента 3И | 153 | КП2 | Сдвоенный мультиплексор 2 в 1 со стробом | 373 | ИР22 | 8-разрядный буферный регистр с тремя состояниями | ||

| 12 | ЛА10 | Три логических элемента 3И-НЕ с открытым коллектором | 154 | ИД3 | Демультиплексор 4 в 16 | 374 | ИР23 | 8 триггеров с тремя состояниями | ||

| 13 | ТЛ1 | Два логических элемента 4И-НЕ с триггером Шмитта | 155 | ИД4 | Сдвоенный демультиплексор 2 в 4 со стробом | 377 | ИР27 | 8-разрядный регистр с разрешением записи | ||

| 14 | ТЛ2 | Шесть логических элементов НЕ с триггером Шмитта | 156 | ИД5 | Сдвоенный демультиплексор 2 в 4 со стробом | 379 | ТМ10 | четыре D-триггера с прямыми и инверсными выходами | ||

| 15 | ЛИ4 | Три логических элемента 3И с открытым коллектором | 157 | КП16 | 4 мультиплексора 2 в 1 со стробом | 381 | ИК2 | АЛУ | ||

| 16 | ЛН5 | Шесть мощных (40 мА) инверторов с высоковольтным открытым коллектором (15 В) | 158 | КП18 | 4 мультиплексора 2 в 1 со стробом и инверсией | 384 | ИП9 | 8-разрядный последовательный умножитель | ||

| 17 | ЛП4 | Шесть мощных (40 мА) неинверторов с высоковольтным открытым коллектором (15 В) | 159 | ИД19 | Дешифратор 3х8 | 385 | ИМ7 | 4 последовательных сумматора/вычитателя | ||

| 20 | ЛА1 | Два логических элемента 4И-НЕ | 160 | ИЕ9 | 4-разрядный десятичный синхронный счетчик | 390 | ИЕ20 | Два 4-разрядных десятичных счетчика | ||

| 21 | ЛИ6 | Два логических элемента 4И | 161 | ИЕ10 | 4-разрядный двоичный синхронный счетчик | 393 | ИЕ19 | Два 4-разрядных двоичных счетчика | ||

| 22 | ЛА7 | Два логических элемента 4И-НЕ с открытым коллектором | 162 | ИЕ11 | 4-разрядный десятичный синхронный счетчик | 395 | ИР25 | 4-разрядный каскадируемый сдвигающий регистр с 3 состояниями | ||

| 23 | ЛЕ2 | Два логических элемента 4ИЛИ-НЕ со стробированием одного элемента и возможностью расширения по ИЛИ на другом | 163 | ИЕ18 | 4-разрядный двоичный синхронный счетчик | 396 | ИР43 | 8-разрядный регистр | ||

| 25 | ЛЕ3 | Два логических элемента 4ИЛИ-НЕ со стробированием | 164 | ИР8 | 8-разрядный сдвигающий регистр со сбросом с параллельным выходом | 399 | КП20 | 4 мультиплексора 2 в 1 с памятью (триггер) | ||

| 26 | ЛА11 | Четыре логических элемента 2И-НЕ с высоковольтным (до 15 В) открытым коллектором | 165 | ИР9 | 8-разрядный сдвигающий регистр с параллельными входами | 450 | ЛП7 | 2 логических элемента 2И-НЕ с общим входом и двумя мощными транзисторами | ||

| 27 | ЛЕ4 | Три логических элемента 3ИЛИ-НЕ | 166 | ИР10 | 8-разрядный сдвигающий регистр со сбросом с параллельной загрузкой и последовательным выходом | 451 | ЛИ5 | Два логических элемента 2И с мощным открытым коллектором | ||

| 28 | ЛЕ5 | Четыре логических элемента 2ИЛИ-НЕ (драйвер линии 75 Ом) I(0)=48 мА, I(1)=2.4 мА | 168 | ИЕ16 | Двоично-десятичный синхронный счетчик | 452 | ЛА18 | Два логических элемента 2И-НЕ с мощным открытым коллектором | ||

| 30 | ЛА2 | Логический элемент 8И-НЕ | 169 | ИЕ17 | Десятичный синхронный счетчик | 453 | ЛЛ2 | Два логических элемента 2ИЛИ с мощным открытым коллектором | ||

| 32 | ЛЛ1 | Четыре логических элемента 2ИЛИ | 170 | ИР32 | 4×4 регистровый файл | 465 | АП14 | 8 неинверсных драйверов с 3 состояниями | ||

| 33 | ЛЕ11 | Четыре логических элемента 2ИЛИ-НЕ с открытым коллектором | 172 | РП3 | 16-битовый регистровый файл с 3 состояниями | 466 | АП15 | 8 инверсных драйверов с 3 состояниями | ||

| 34 | ЛИ9 | Шесть повторителей | 173 | ИР15 | 4-разрядный параллельный регистр с общим сбросом и выходом с тремя состояниями | 482 | ВГ1 | Контроллер адреса | ||

| 37 | ЛА12 | Четыре логических элемента 2И-НЕ с мощным выходом (до 48 мА) | 174 | ТМ9 | Шесть D-триггеров с общим сбросом и тактированием | 533 | ИР40 | 8-разрядный инверсный лэтч с 3 состояниями | ||

| 38 | ЛА13 | Четыре логических элемента 2И-НЕ с мощным (до 48 мА) открытым коллектором | 175 | ТМ8 | Четыре D-триггеров с общим сбросом и тактированием | 534 | ИР41 | 8-разрядный инверсный регистр с 3 состояниями | ||

| 40 | ЛА6 | Два логических элемента 4И-НЕ с повышенной нагрузочной способностью | 180 | ИП2 | 8-разрядная схема контроля по четности | 537 | ИД22 | Дешифратор 4 в 10 с тремя состояниями и изменяемой полярностью выходов | ||

| 42 | ИД6 | Демультиплексор 4 в 10 | 181 | ИП3 | Четырехразрядное АЛУ | 540 | АП12 | 8 инверсных драйверов с 3 состояниями | ||

| 45 | ИД24 | Полный дешифратор 2-10 в десятичный с открытым коллектором (30В) | 182 | ИП4 | Схема быстрого переноса для АЛУ | 541 | АП13 | 8 неинверсных драйверов с 3 состояниями | ||

| 49 | ПП4 | Преобразователь двоичного кода в семисегментный | 183 | ИМ5 | Два одноразрядных полных сумматора | 573 | ИР33 | 8 лэтчей с тремя состояниями | ||

| 50 | ЛР1 | Два логических элемента 2И-2ИЛИ-НЕ, один расширяемый по ИЛИ | 184 | ПР6 | Преобразователь двоично-десятичного кода в двоичный | 574 | ИР37 | 8 триггеров с тремя состояниями | ||

| 51 | ЛР11 | Логический элемент 4-2-3-2И-4ИЛИ-НЕ | 185 | ПР7 | Преобразователь двоичного кода в двоично- десятичный | 593 | ИЕ21 | 8-разрядный двоичный счетчик с входным регистром и двунаправленной шиной ввода/вывода | ||

| 53 | ЛР3 | Логический элемент 2-2-2-3И-4ИЛИ-НЕ расширяемый по ИЛИ | 187 | РЕ2 | ПЗУ | 620 | АП25 | Восьмиканальный двунаправленный приемопередатчик с тремя состояниями и инверсией на выходе | ||

| 54 | ЛР13 | Логический элемент 2-3-3-2И-4ИЛИ-НЕ | 189 | РУ8 | ОЗУ на 64 бит с произвольной выборкой | 623 | АП26 | Восьмиканальный двунаправленный приемопередатчик с тремя состояниями на выходе | ||

| 55 | ЛР4 | Логический элемент 4-4И-2ИЛИ-НЕ расширяемый по ИЛИ | 190 | ИЕ12 | Двоично-десятичный счетчик | 624 | ГГ6 | Генератор | ||

| 60 | ЛД1 | Два 4-входовых расширителя по ИЛИ | 191 | ИЕ13 | Десятичный счетчик | 626 | ГГ2 | Два генератора, управляемых напряжением | ||

| 64 | ЛР9 | Логический элемент 4-2-3-2И-4ИЛИ-НЕ | 192 | ИЕ6 | Двоично-десятичный счетчик | 630 | ВЖ1 | 16-разрядная схема контроля по коду Хэмминга | ||

| 65 | ЛР10 | Логический элемент 4-2-3-2И-4ИЛИ-НЕ с открытым коллектором | 193 | ИЕ7 | Десятичный счетчик | 640 | АП9 | 8-разрядный двунаправленный драйвер с 3 состояниями | ||

| 72 | ТВ1 | J-K триггер с логикой 3И на входе | 194 | ИР11 | 4-разрядный универсальный регистр | 641 | АП7 | 8-разрядный двунаправленный неинверсный драйвер с открытым коллектором | ||

| 74 | ТМ2 | Два D-триггера | 195 | ИР12 | 4-разрядный двунаправленный приемопередатчик без инверсии и выходом с 3 состояниями | 643 | АП16 | 8 двунаправленных драйверов с 3 состояниями | ||

| 75 | ТМ7 | Два сдвоенных лэтча | 196 | ИЕ14 | Двоично-десятичный счетчик | 645 | АП8 | 8-разрядный двунаправленный неинверсный драйвер с тремя состояниями | ||

| 76 | ТК3 | Два JK-триггера | 197 | ИЕ15 | Десятичный счетчик | 646 | ВА1 | 4-разрядный двунаправленный приемо-передатчик с лэтчами на обоих шинах | ||

| 77 | ТМ5 | Два сдвоенных лэтча | 198 | ИР13 | 8-разрядный универсальный регистр | 648 | ВА2 | 8-разрядный двунаправленный приемо-передатчик с тремя состояниями | ||

| 78 | ТВ14 | Триггер | 214 | — | SRAM 4k | 651 | АП17 | 8-разрядный двунаправленный приемо-передатчик с регистрами на обоих шинах | ||

| 80 | ИМ1 | Одноразрядный полный сумматор | 216 | АП2 | Четырехразрядный драйвер с открытым коллектором | 652 | АП24 | 8-разрядный двунаправленный неинверсный приемо-передатчик с тремя состояниями | ||

| 81 | РУ1 | Статическое ОЗУ со схемой управления (16×1) | 221 | АГ4 | Два одновибратора с триггером Шмитта на входе | 670 | ИР26 | 4×4 регистровый файл с тремя состояниями | ||

| 82 | ИМ2 | Двухразрядный полный сумматор | 224 | РУ12 | — | 804 | ЛА20 | 6 мощных логических элемента 2И-НЕ | ||

| 83 | ИМ3 | Четырехразрядный полный сумматор | 225 | РУ10 | FIFO 16×5 бит | 805 | ЛЕ8 | 6 мощных логических элемента 2ИЛИ | ||

| 84 | РУ3 | Статическое ОЗУ (4×4) | 238 | ИД19 | 8-разрядный универсальный регистр сдвига с 3 состояниями | 808 | ЛИ7 | 6 мощных логических элемента 2И | ||

| 85 | СП1 | 4-разрядный цифровой компаратор | 240 | АП3 | Два четырехразрядных драйвера с тремя состояниями | 832 | ЛЛ3 | Шесть логических элементов 2ИЛИ | ||

| 86 | ЛП5 | 4 логических элемента «исключающее ИЛИ» | 241 | АП4 | Два четырехразрядных драйвера с тремя состояниями | 873 | ИР34 | Два 4-разрядных лэтча с тремя состояниями и сбросом | ||

| 89 | РУ2 | ОЗУ на 64 бит с произвольной выборкой | 242 | ИП6 | Четырехразрядные двунаправленные драйвера | 874 | ИР38 | Два 4-разрядных триггера с тремя состояниями и сбросом | ||

| 90 | ИЕ2 | 4-разрядный двоично-десятичный счетчик | 243 | ИП7 | Четырехразрядные двунаправленные драйвера | 881 | ИП14 | Четырехразрядное АЛУ | ||

| 91 | ИР2 | 8-разрядный сдвиговый регистр | 244 | АП5 | Два четырехразрядных драйвера с тремя состояниями | 882 | ИП16 | 32-разрядный генератор с предварительным просмотром и схемой ускоренного переноса | ||

| 92 | ИЕ4 | Счетчик-делитель на 12 | 245 | АП6 | 8-разрядный двунаправленный шинный транслятор | 1000 | ЛА21 | Четыре логических элемента 2И-НЕ | ||

| 93 | ИЕ5 | 4-разрядный двоичный счетчик | 247 | ИД18 | Декодер двоичного кода в семисегментный | 1002 | ЛЕ10 | Четыре логических элемента 2ИЛИ-НЕ | ||

| 95 | ИР1 | 4-разрядный универсальный регистр | 251 | КП15 | Мультиплексор 8 в 1 с 3 состояниями, прямым и инверсным выходами | 1003 | ЛА23 | Четыре логических элемента 2И-НЕ с открытым коллектором | ||

| 97 | ИЕ8 | 6-разрядный делитель частоты с переменным коэффициентом деления | 253 | КП12 | Сдвоенный мультиплексор 4 в 1 с 3 состояниями | 1004 | ЛН8 | Шесть мощных инверторов | ||

| 98 | ИР5 | — | 257 | КП11 | 4 мультиплексора 2 в 1 с 3 состояниями | 1005 | ЛН10 | Шесть мощных инверторов с открытым коллектором | ||

| 100 | ТК7 | JK-триггер | 258 | КП14 | 4 мультиплексора 2 в 1 с 3 состояниями и инверсией | 1008 | ЛИ8 | Четыре логических элемента 2И | ||

| 107 | ТВ6 | Два J-K триггера со сбросом | 259 | ИР30 | 8-разрядный адресуемый лэтч | 1010 | ЛА24 | Три логических элемента 3И-НЕ | ||

| 109 | ТВ15 | Два J-K триггера | 260 | ЛЕ7 | Два логических элемента 5ИЛИ-НЕ | 1011 | ЛИ10 | Три логических элемента 3И | ||

| 112 | ТВ9 | Два J-K триггера | 261 | ИП8 | Умножитель 2×4 | 1020 | ЛА22 | Два логических элемента 4И-НЕ | ||

| 113 | ТВ10 | Два J-K триггера | 237 | ИР35 | 8 D-триггеров с общим тактированием и сбросом | 1032 | ЛЛ4 | Четыре логических элемента 2ИЛИ | ||

| 114 | ТВ11 | Два J-K триггера | 297 | ТР2 | Четыре R-S-триггера | 1034 | ЛП16 | Шесть неинверторов | ||

| 121 | АГ1 | Одновибратор | 280 | ИП5 | 9-разрядная схема контроля по четности | 1035 | ЛП17 | Шесть неинверторов с открытым коллектором | ||

| 123 | АГ3 | Два одновибратора | 281 | ИК4 | 4-разрядный аккумулятор | 4002 | ЛЕ9 | Два счетверенных логических элемента НЕ-ИЛИ | ||

| 124 | ГГ1 | Два генератора, управляемых напряжением | 283 | ИМ6 | 4-разрядный полный сумматор с ускоренным переносом | 4006 | ИР47 | Сдвиговый регистр | ||

| 125 | ЛП8 | 4 неинвертора (3 состояния) | 289 | РУ9 | ОЗУ на 64 бит с произвольной выборкой | 4015 | ИР46 | 4-разрядный регистр с последовательным вводом и Reset | ||

| 126 | ЛП14 | 4 неинвертора (3 состояния) | 292 | ПЦ1 | Программируемый делитель частоты/таймер | 4035 | ИР51 | 4-разрядный последовательно-параллельный регистр | ||

| 128 | ЛЕ6 | Четыре логических элемента 2ИЛИ-НЕ | 295 | ИР16 | 4-разрядный универсальный регистр с тремя состояниями | 4511 | ИД23 | Лэтч, декодер, драйвер семисегментный | ||

| 132 | ТЛ3 | Четыре триггера Шмитта | 298 | КП13 | 4 мультиплексора 2 в 1 с памятью (триггер) | 4520 | ИЕ23 | Два четырехразрядных двоичных счетчика | ||

| 134 | ЛА19 | Элемент 12И-НЕ с тремя состояниями | 299 | ИР24 | 8-разрядный универсальный сдвиговый регистр с объединенными входами/выходами | — | ИР50 | Универсальный двухпортовый регистр | ||

| Название | Назначение | Серия 155 |

Серия 555 |

Серия 531 |

Серия 1531 |

Серия 1530 |

Серия 1533 |

Серия 1554 |

Серия 1564 |

Серия 5564 |

| АГ1 | Одноканальный ждущий мультивибратор | 74121 | 74LS121 | 74S121 | 74F121 | 74AS121 | 74ALS121 | 74AC121 | 74HC121 | 74HCT121 |

| АГ3 | 2 ждущих мультивибратора | 74123 | 74LS123 | 74S123 | 74F123 | 74AS123 | 74ALS123 | 74AC123 | 74HC123 | 74HCT123 |

| АП3 | Буферный усилитель без инверсии | 74240 | 74LS240 | 74S240 | 74F240 | 74AS240 | 74ALS240 | 74AC240 | 74HC240 | 74HCT240 |

| АП4 | Буферный усилитель без инверсии | 74241 | 74LS241 | 74S241 | 74F241 | 74AS241 | 74ALS241 | 74AC241 | 74HC241 | 74HCT241 |

| АП6 | 8 ДНШУ с тремя постоянными выходами | 74245 | 74LS245 | 74S245 | 74F245 | 74AS245 | 74ALS245 | 74AC245 | 74HC245 | 74HCT245 |

| ВГ1 | 74482 | 74LS482 | 74S482 | 74F482 | 74AS482 | 74ALS482 | 74AC482 | 74HC482 | 74HCT482 | |

| ВЖ1 | 74360 | 74LS360 | 74S360 | 74F360 | 74AS360 | 74ALS360 | 74AC360 | 74HC360 | 74HCT360 | |

| ГТ1 | Генератор | 74124 | 74LS124 | 74S124 | 74F124 | 74AS124 | 74ALS124 | 74AC124 | 74HC124 | 74HCT124 |

| ИВ1 | Приоритетный шифратор | 74148 | 74LS148 | 74S148 | 74F148 | 74AS148 | 74ALS148 | 74AC148 | 74HC148 | 74HCT148 |

| ИД1 | Дешифратор для управления газоразрядными индикаторами |

74141 | 74LS141 | 74S141 | 74F141 | 74AS141 | 74ALS141 | 74AC141 | 74HC141 | 74HCT141 |

| ИД10 | Двоично-десятичный дешифратор | 74145 | 74LS145 | 74S145 | 74F145 | 74AS145 | 74ALS145 | 74AC145 | 74HC145 | 74HCT145 |

| ИД14 | Двойной высокоскоростной дешифратор | 74139 | 74LS139 | 74S139 | 74F139 | 74AS139 | 74ALS139 | 74AC139 | 74HC139 | 74HCT139 |

| ИД3 | Дешифратор | 74154 | 74LS154 | 74S154 | 74F154 | 74AS154 | 74ALS154 | 74AC154 | 74HC154 | 74HCT154 |

| ИД4 | 2 дешифратора | 74155 | 74LS155 | 74S155 | 74F155 | 74AS155 | 74ALS155 | 74AC155 | 74HC155 | 74HCT155 |

| ИД6 | Двоично-десятичный дешифратор | 7442 | 74LS42 | 74S42 | 74F42 | 74AS42 | 74ALS42 | 74AC42 | 74HC42 | 74HCT42 |

| ИД7 | Высокоскоростной дешифратор-демультиплексор |

74138 | 74LS138 | 74S138 | 74F138 | 74AS138 | 74ALS138 | 74AC138 | 74HC138 | 74HCT138 |

| ИЕ10 | Декадный двоичный счетчик | 74161 | 74LS161 | 74S161 | 74F161 | 74AS161 | 74ALS161 | 74AC161 | 74HC161 | 74HCT161 |

| ИЕ14 | Декадный асинхронный счетчик | 74196 | 74LS196 | 74S196 | 74F196 | 74AS196 | 74ALS196 | 74AC196 | 74HC196 | 74HCT196 |

| ИЕ15 | Декадный асинхронный счетчик | 74197 | 74LS197 | 74S197 | 74F197 | 74AS197 | 74ALS197 | 74AC197 | 74HC197 | 74HCT197 |

| ИЕ16 | Синхронный реверсивный счетчик | 74168 | 74LS168 | 74S168 | 74F168 | 74AS168 | 74ALS168 | 74AC168 | 74HC168 | 74HCT168 |

| ИЕ17 | Синхронный реверсивный счетчик | 74169 | 74LS169 | 74S169 | 74F169 | 74AS169 | 74ALS169 | 74AC169 | 74HC169 | 74HCT169 |

| ИЕ18 | 4-разрядный двоичный синхронный счетчик |

74163 | 74LS163 | 74S163 | 74F163 | 74AS163 | 74ALS163 | 74AC163 | 74HC163 | 74HCT163 |

| ИЕ2 | 4-разрядный десятичный асинхронный счетчик |

7490 | 74LS90 | 74S90 | 74F90 | 74AS90 | 74ALS90 | 74AC90 | 74HC90 | 74HCT90 |

| ИЕ4 | 4-разрядный двоичный счетчик | 7492 | 74LS92 | 74S92 | 74F92 | 74AS92 | 74ALS92 | 74AC92 | 74HC92 | 74HCT92 |

| ИЕ5 | 4-разрядный асинхронный счетчик | 7493 | 74LS93 | 74S93 | 74F93 | 74AS93 | 74ALS93 | 74AC93 | 74HC93 | 74HCT93 |

| ИЕ6 | 4-разрядный реверсивный счетчик | 74192 | 74LS192 | 74S192 | 74F192 | 74AS192 | 74ALS192 | 74AC192 | 74HC192 | 74HCT192 |

| ИЕ7 | 4-разрядный реверсивный счетчик | 74193 | 74LS193 | 74S193 | 74F193 | 74AS193 | 74ALS193 | 74AC193 | 74HC193 | 74HCT193 |

| ИЕ8 | Программируемый счетчик | 7497 | 74LS97 | 74S97 | 74F97 | 74AS97 | 74ALS97 | 74AC97 | 74HC97 | 74HCT97 |

| ИЕ9 | Декадный двоично-десятичный счетчик |

74160 | 74LS160 | 74S160 | 74F160 | 74AS160 | 74ALS160 | 74AC160 | 74HC160 | 74HCT160 |

| ИК2 | 74381 | 74LS381 | 74S381 | 74F381 | 74AS381 | 74ALS381 | 74AC381 | 74HC381 | 74HCT381 | |

| ИМ1 | Полный сумматор | 7480 | 74LS80 | 74S80 | 74F80 | 74AS80 | 74ALS80 | 74AC80 | 74HC80 | 74HCT80 |

| ИМ2 | cумматор без дополнительных инверсных и управляющих входов |

7482 | 74LS82 | 74S82 | 74F82 | 74AS82 | 74ALS82 | 74AC82 | 74HC82 | 74HCT82 |

| ИМ3 | Быстродействующий полный сумматор |

7483 | 74LS83 | 74S83 | 74F83 | 74AS83 | 74ALS83 | 74AC83 | 74HC83 | 74HCT83 |

| ИМ6 | Сумматор | 74283 | 74LS283 | 74S283 | 74F283 | 74AS283 | 74ALS283 | 74AC283 | 74HC283 | 74HCT283 |

| ИМ7 | 4 последовательных сумматора-вычитателя |

74358 | 74LS358 | 74S358 | 74F358 | 74AS358 | 74ALS358 | 74AC358 | 74HC358 | 74HCT358 |

| ИМ7 | 4 последовательных сумматора-вычитателя |

74385 | 74LS385 | 74S385 | 74F385 | 74AS385 | 74ALS385 | 74AC385 | 74HC385 | 74HCT385 |

| ИП2 | 8-разрядная схема для проверки на четность или нечетность |

74180 | 74LS180 | 74S180 | 74F180 | 74AS180 | 74ALS180 | 74AC180 | 74HC180 | 74HCT180 |

| ИП3 | 4-разрядное скоростное АЛУ | 74181 | 74LS181 | 74S181 | 74F181 | 74AS181 | 74ALS181 | 74AC181 | 74HC181 | 74HCT181 |

| ИП4 | Высокоскоростная схема ускоренного переноса | 74182 | 74LS182 | 74S182 | 74F182 | 74AS182 | 74ALS182 | 74AC182 | 74HC182 | 74HCT182 |

| ИП6 | 4 ДНШУ с инверсией | 74242 | 74LS242 | 74S242 | 74F242 | 74AS242 | 74ALS242 | 74AC242 | 74HC242 | 74HCT242 |

| ИП7 | 4 ДНШУ без инверсии | 74243 | 74LS243 | 74S243 | 74F243 | 74AS243 | 74ALS243 | 74AC243 | 74HC243 | 74HCT243 |

| ИП8 | ДНШУ | 74261 | 74LS261 | 74S261 | 74F261 | 74AS261 | 74ALS261 | 74AC261 | 74HC261 | 74HCT261 |

| ИП9 | Перемножитель | 74384 | 74LS384 | 74S384 | 74F384 | 74AS384 | 74ALS384 | 74AC384 | 74HC384 | 74HCT384 |

| ИР1 | 4-разрядный сдвиговой регистр | 7495 | 74LS95 | 74S95 | 74F95 | 74AS95 | 74ALS95 | 74AC95 | 74HC95 | 74HCT95 |

| ИР11 | Универсальный 4-разрядный сдвиговый регистр |

74194 | 74LS194 | 74S194 | 74F194 | 74AS194 | 74ALS194 | 74AC194 | 74HC194 | 74HCT194 |

| ИР12 | Регистр для скоростных операций: сдвиг, счт, накопление |

74195 | 74LS195 | 74S195 | 74F195 | 74AS195 | 74ALS195 | 74AC195 | 74HC195 | 74HCT195 |

| ИР13 | Универсальный, 8-разрядный, синхронный регистр сдвига |

74198 | 74LS198 | 74S198 | 74F198 | 74AS198 | 74ALS198 | 74AC198 | 74HC198 | 74HCT198 |

| ИР15 | 4-разрядный регистр | 74173 | 74LS173 | 74S173 | 74F173 | 74AS173 | 74ALS173 | 74AC173 | 74HC173 | 74HCT173 |

| ИР16 | 4-разрядный сдвиговой регистр с тремя состояниями вых. |

74295 | 74LS295 | 74S295 | 74F295 | 74AS295 | 74ALS295 | 74AC295 | 74HC295 | 74HCT295 |

| ИР22 | 8-разрядный регистр-защелка | 74373 | 74LS373 | 74S373 | 74F373 | 74AS373 | 74ALS373 | 74AC373 | 74HC373 | 74HCT373 |

| ИР23 | 8-разрядный регистр-зашелка с 8-ю тактируемыми триггерами |

74374 | 74LS374 | 74S374 | 74F374 | 74AS374 | 74ALS374 | 74AC374 | 74HC374 | 74HCT374 |

| ИР24 | Универсальный 8-разрядный регистр | 74299 | 74LS299 | 74S299 | 74F299 | 74AS299 | 74ALS299 | 74AC299 | 74HC299 | 74HCT299 |

| ИР25 | 4-разрядный сдвиговой регистр | 74395 | 74LS395 | 74S395 | 74F395 | 74AS395 | 74ALS395 | 74AC395 | 74HC395 | 74HCT395 |

| ИР26 | Регистр | 74670 | 74LS670 | 74S670 | 74F670 | 74AS670 | 74ALS670 | 74AC670 | 74HC670 | 74HCT670 |

| ИР27 | Содержит 8 D-триггеров | 74377 | 74LS377 | 74S377 | 74F377 | 74AS377 | 74ALS377 | 74AC377 | 74HC377 | 74HCT377 |

| ИР28 | Регистр | 74322 | 74LS322 | 74S322 | 74F322 | 74AS322 | 74ALS322 | 74AC322 | 74HC322 | 74HCT322 |

| ИР8 | 8-разрядный сдвиговый регистр с последовательным входом и параллельным выходом |

74164 | 74LS164 | 74S164 | 74F164 | 74AS164 | 74ALS164 | 74AC164 | 74HC164 | 74HCT164 |

| ИР9 | 8-разрядный сдвиговый регистр, имеющий параллельные и последовательный входы |

74165 | 74LS165 | 74S165 | 74F165 | 74AS165 | 74ALS165 | 74AC165 | 74HC165 | 74HCT165 |

| КП1 | 16-входовый мультиплексор | 74150 | 74LS150 | 74S150 | 74F150 | 74AS150 | 74ALS150 | 74AC150 | 74HC150 | 74HCT150 |

| КП11 | 4 2-входовых мультиплексора | 74257 | 74LS257 | 74S257 | 74F257 | 74AS257 | 74ALS257 | 74AC257 | 74HC257 | 74HCT257 |

| КП12 | Двухканальный мультиплексор | 74253 | 74LS253 | 74S253 | 74F253 | 74AS253 | 74ALS253 | 74AC253 | 74HC253 | 74HCT253 |

| КП13 | Двухканальный мультиплексор и 4-разрядный регистр |

74298 | 74LS298 | 74S298 | 74F298 | 74AS298 | 74ALS298 | 74AC298 | 74HC298 | 74HCT298 |

| КП14 | 4 2-входовых мультиплексора | 74258 | 74LS258 | 74S258 | 74F258 | 74AS258 | 74ALS258 | 74AC258 | 74HC258 | 74HCT258 |

| КП15 | Мультиплексор | 74251 | 74LS251 | 74S251 | 74F251 | 74AS251 | 74ALS251 | 74AC251 | 74HC251 | 74HCT251 |

| Название | Назначение | Серия 155 |

Серия 555 |

Серия 531 |

Серия 1531 |

Серия 1530 |

Серия 1533 |

Серия 1554 |

Серия 1564 |

Серия 5564 |

| КП2 | 2 4-входовых мультиплексора | 74153 | 74LS153 | 74S153 | 74F153 | 74AS153 | 74ALS153 | 74AC153 | 74HC153 | 74HCT153 |

| КП5 | Селектор-мультиплексор | 74152 | 74LS152 | 74S152 | 74F152 | 74AS152 | 74ALS152 | 74AC152 | 74HC152 | 74HCT152 |

| КП7 | Селектор-мультиплексор | 74151 | 74LS151 | 74S151 | 74F151 | 74AS151 | 74ALS151 | 74AC151 | 74HC151 | 74HCT151 |

| ЛА1 | 2 элемента 4И-НЕ | 7420 | 74LS20 | 74S20 | 74F20 | 74AS20 | 74ALS20 | 74AC20 | 74HC20 | 74HCT20 |

| ЛА10 | 3 элемента 3И-НЕ | 7412 | 74LS12 | 74S12 | 74F12 | 74AS12 | 74ALS12 | 74AC12 | 74HC12 | 74HCT12 |

| ЛА11 | 2 элемента 4И-НЕ | 7426 | 74LS26 | 74S26 | 74F26 | 74AS26 | 74ALS26 | 74AC26 | 74HC26 | 74HCT26 |

| ЛА12 | 4 элемента 2И-НЕ | 7437 | 74LS37 | 74S37 | 74F37 | 74AS37 | 74ALS37 | 74AC37 | 74HC37 | 74HCT37 |

| ЛА13 | 4 элемента 2И-НЕ | 7438 | 74LS38 | 74S38 | 74F38 | 74AS38 | 74ALS38 | 74AC38 | 74HC38 | 74HCT38 |

| ЛА19 | 1 элемент 12И с разрешением по вх. |

74134 | 74LS134 | 74S134 | 74F134 | 74AS134 | 74ALS134 | 74AC134 | 74HC134 | 74HCT134 |

| ЛА2 | 1 элемент 8И-НЕ | 7430 | 74LS30 | 74S30 | 74F30 | 74AS30 | 74ALS30 | 74AC30 | 74HC30 | 74HCT30 |

| ЛА3 | 4 элемента 2И-НЕ | 7400 | 74LS00 | 74S00 | 74F00 | 74AS00 | 74ALS00 | 74AC00 | 74HC00 | 74HCT00 |

| ЛА4 | 3 элемента 3И-НЕ | 7410 | 74LS10 | 74S10 | 74F10 | 74AS10 | 74ALS10 | 74AC10 | 74HC10 | 74HCT10 |

| ЛА6 | 2 элемента 4И-НЕ | 74140 | 74LS140 | 74S140 | 74F140 | 74AS140 | 74ALS140 | 74AC140 | 74HC140 | 74HCT140 |

| ЛА6 | 2 элемента 4И-НЕ | 7440 | 74LS40 | 74S40 | 74F40 | 74AS40 | 74ALS40 | 74AC40 | 74HC40 | 74HCT40 |

| ЛА7 | 2 элемента 4И-НЕ | 7422 | 74LS22 | 74S22 | 74F22 | 74AS22 | 74ALS22 | 74AC22 | 74HC22 | 74HCT22 |

| ЛА8 | 4 элемента 2И-НЕ | 7401 | 74LS01 | 74S01 | 74F01 | 74AS01 | 74ALS01 | 74AC01 | 74HC01 | 74HCT01 |

| ЛА9 | 4 элемента 2И-НЕ | 7403 | 74LS03 | 74S03 | 74F03 | 74AS03 | 74ALS03 | 74AC03 | 74HC03 | 74HCT03 |

| ЛД1 | 2 элемента 4И с вых. от коллектора и эмиттера |

7460 | 74LS60 | 74S60 | 74F60 | 74AS60 | 74ALS60 | 74AC60 | 74HC60 | 74HCT60 |

| ЛЕ1 | 4 элемента 2ИЛИ-НЕ | 7402 | 74LS02 | 74S02 | 74F02 | 74AS02 | 74ALS02 | 74AC02 | 74HC02 | 74HCT02 |

| ЛЕ2 | 2 элемента 4ИЛИ-НЕ с разрешением по входу |

7423 | 74LS23 | 74S23 | 74F23 | 74AS23 | 74ALS23 | 74AC23 | 74HC23 | 74HCT23 |

| ЛЕ3 | 2 элемента 4ИЛИ-НЕ с разрешением по входу |

7425 | 74LS25 | 74S25 | 74F25 | 74AS25 | 74ALS25 | 74AC25 | 74HC25 | 74HCT25 |

| ЛЕ4 | 3 элемента 3ИЛИ-НЕ | 7427 | 74LS27 | 74S27 | 74F27 | 74AS27 | 74ALS27 | 74AC27 | 74HC27 | 74HCT27 |

| ЛЕ5 | 4 элемента 2ИЛИ-НЕ | 7428 | 74LS28 | 74S28 | 74F28 | 74AS28 | 74ALS28 | 74AC28 | 74HC28 | 74HCT28 |

| ЛЕ6 | 2 элемента 4ИЛИ-НЕ | 74128 | 74LS128 | 74S128 | 74F128 | 74AS128 | 74ALS128 | 74AC128 | 74HC128 | 74HCT128 |

| ЛЕ7 | 2 элемента 5ИЛИ-НЕ | 74260 | 74LS260 | 74S260 | 74F260 | 74AS260 | 74ALS260 | 74AC260 | 74HC260 | 74HCT260 |

| ЛИ1 | 4 элемента 2И | 7408 | 74LS08 | 74S08 | 74F08 | 74AS08 | 74ALS08 | 74AC08 | 74HC08 | 74HCT08 |

| ЛИ3 | 3 элемента 3ИЛИ | 7411 | 74LS11 | 74S11 | 74F11 | 74AS11 | 74ALS11 | 74AC11 | 74HC11 | 74HCT11 |

| ЛИ4 | 3 элемента 3И | 7415 | 74LS15 | 74S15 | 74F15 | 74AS15 | 74ALS15 | 74AC15 | 74HC15 | 74HCT15 |

| ЛИ6 | 2 элемента 4И | 7421 | 74LS21 | 74S21 | 74F21 | 74AS21 | 74ALS21 | 74AC21 | 74HC21 | 74HCT21 |