Как правильно обозначать микросхемы на принципиальных схемах. Какие существуют условные графические обозначения элементов цифровой техники. Какие правила маркировки выводов микросхем применяются в схемотехнике.

Основные правила обозначения микросхем на электрических схемах

При разработке и изготовлении электронных устройств важно правильно обозначать компоненты на принципиальных схемах. Это позволяет однозначно идентифицировать элементы и понимать их функциональное назначение. Рассмотрим основные правила обозначения микросхем и других элементов цифровой техники на электрических схемах:

- Микросхемы обозначаются прямоугольником, который может содержать основное и дополнительные поля

- Ширина основного поля — не менее 10 мм, дополнительных — не менее 5 мм

- Расстояние между выводами — не менее 5 мм

- Входы изображаются слева, выходы — справа

- Функциональное назначение указывается в верхней части основного поля

- Для обозначения функций используются латинские буквы, цифры и специальные символы

Соблюдение этих базовых правил позволяет создавать понятные и информативные электрические схемы.

Условные графические обозначения элементов цифровой техники

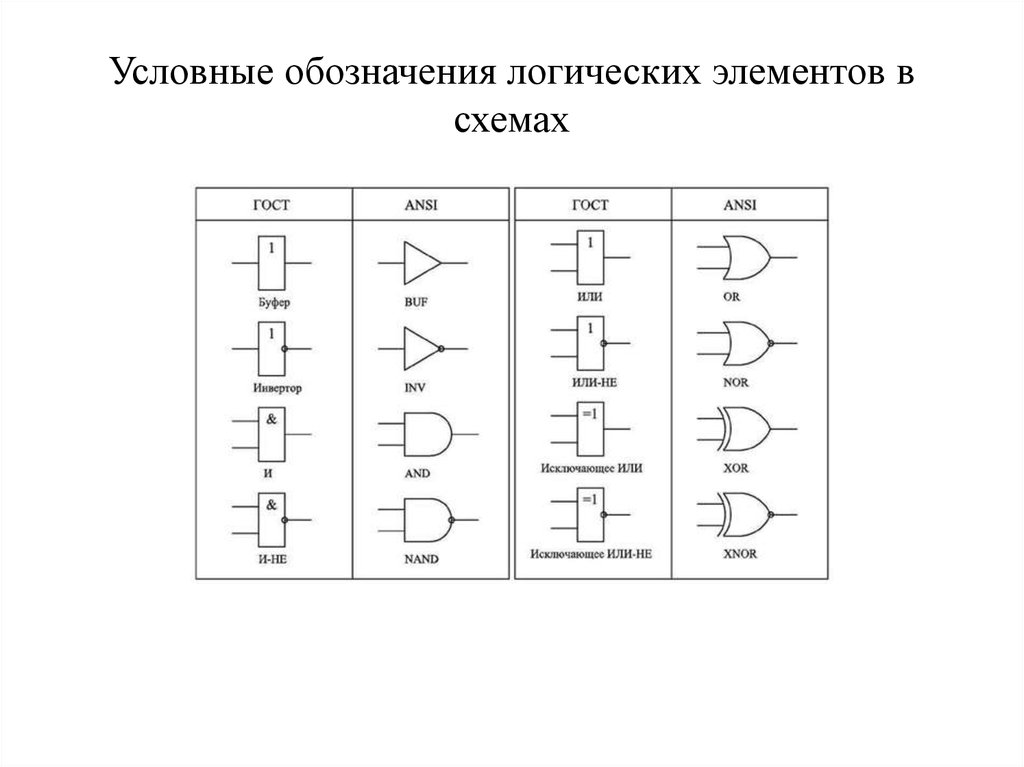

Для элементов цифровой техники используются специальные условные графические обозначения (УГО), которые стандартизированы ГОСТом. Основные виды УГО:

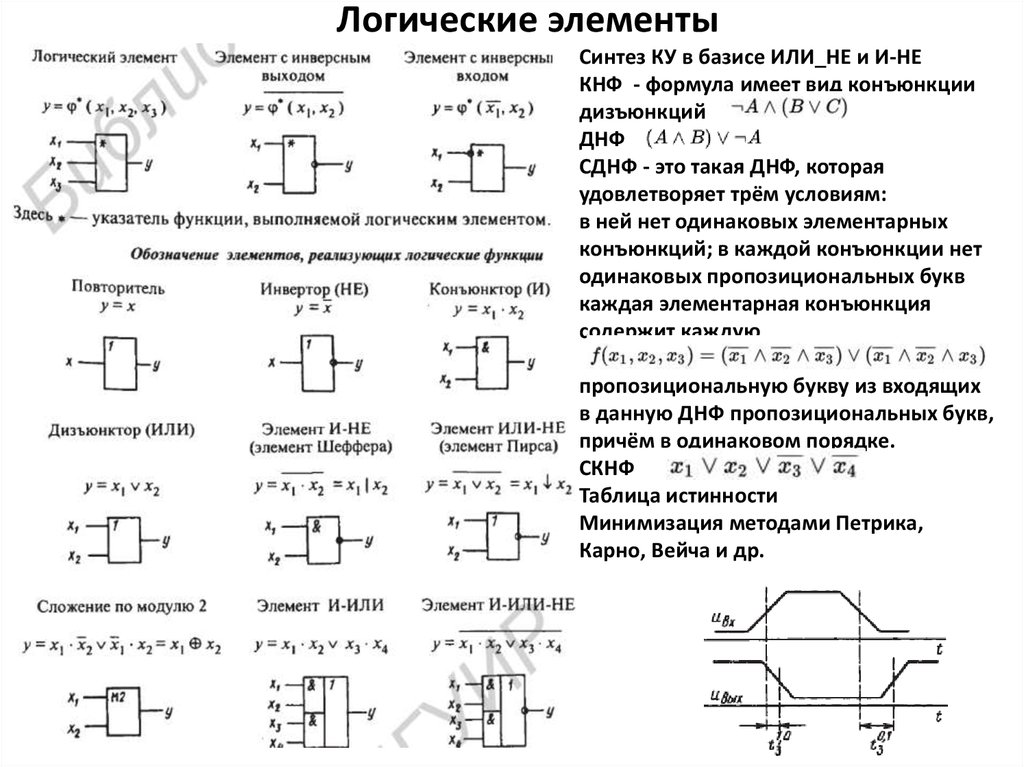

- Логические элементы (И, ИЛИ, НЕ и др.)

- Триггеры

- Регистры

- Счетчики

- Дешифраторы

- Мультиплексоры

- Сумматоры

- Процессоры

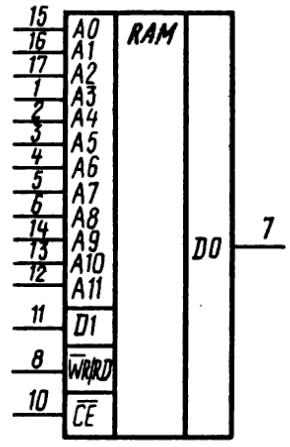

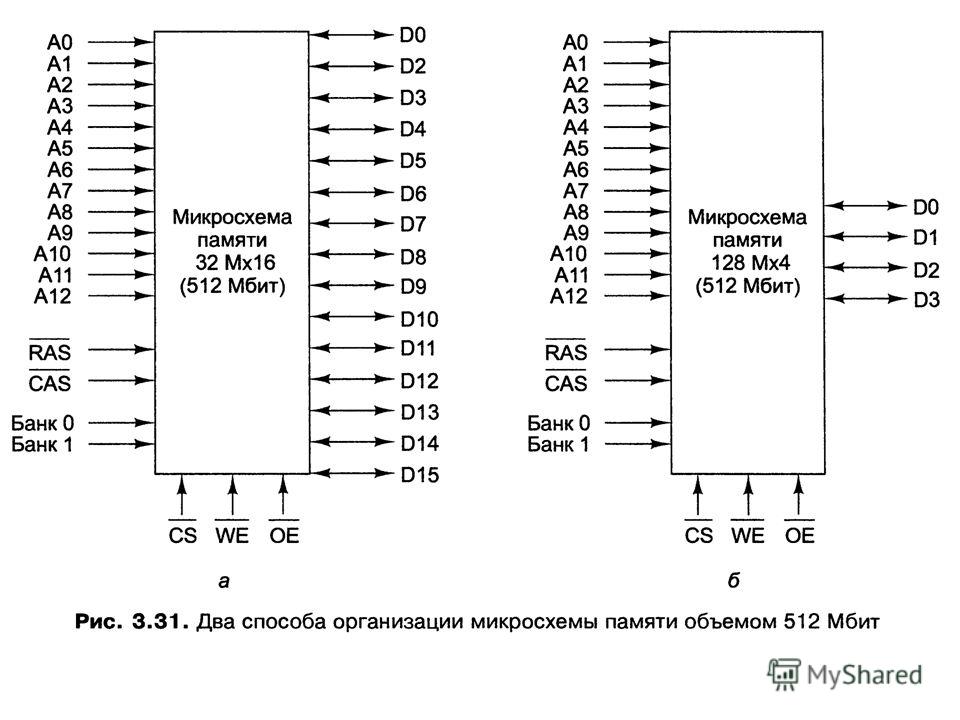

- Память

Каждый тип элемента имеет свое уникальное УГО, что позволяет быстро идентифицировать его на схеме. При этом сохраняется общий принцип изображения в виде прямоугольника с входами слева и выходами справа.

Маркировка выводов микросхем

Правильная маркировка выводов микросхем играет важную роль для понимания их назначения. Основные правила маркировки:

- Прямые статические выводы обозначаются линиями без дополнительных символов

- Инверсные выводы отмечаются кружком

- Динамические выводы обозначаются косой чертой, стрелкой или треугольником

- Неинформационные выводы отмечаются крестиком

- Назначение выводов указывается метками из латинских букв и цифр

Такая система маркировки позволяет однозначно определить функцию каждого вывода микросхемы на принципиальной схеме.

Особенности обозначения сложных микросхем

При обозначении сложных микросхем и микропроцессоров используются дополнительные приемы:

- Сложные функции показываются сочетанием простых (например, CT2DC — двоичный счетчик с дешифратором)

- Для микропроцессоров указывается их тип (например, CPU — центральный процессор)

- Память обозначается как RAM (оперативная) или ROM (постоянная)

- Для нумерации разрядов к обозначениям добавляются цифры (D0, D1, D2 и т.д.)

Это позволяет отразить всю функциональность сложных микросхем в компактном виде на электрической схеме.

Обозначение статических и динамических выводов

Выводы микросхем могут быть статическими и динамическими. Их различное обозначение на схеме важно для понимания принципа работы:

- Статические выводы реагируют на уровень сигнала (0 или 1)

- Динамические выводы реагируют на изменение сигнала (фронт или спад)

- Прямые статические выводы обозначаются линией

- Инверсные статические — линией с кружком

- Прямые динамические — косой чертой или стрелкой

- Инверсные динамические — косой чертой или стрелкой с кружком

Такое разделение позволяет сразу определить тип реакции вывода на входной сигнал.

Применение международных стандартов обозначений

При работе с зарубежной электроникой важно учитывать международные стандарты обозначений:

- Российские ГОСТы наиболее близки к европейским стандартам (например, BS3939)

- Американский стандарт ANSI сильно отличается от российского и европейского

- При работе с импортными компонентами нужно обращать внимание на систему обозначений

- Некоторые обозначения являются универсальными (например, & для элемента И)

- Для сложных микросхем часто используются фирменные обозначения

Знание международных стандартов позволяет правильно читать и составлять схемы с импортными компонентами.

Маркировка специальных выводов микросхем

Некоторые выводы микросхем имеют специальное назначение и маркируются особым образом:

- Открытый коллектор обозначается ромбиком

- Открытый эмиттер — кружком с лучами

- Выводы с высоким импедансом (Z-состояние) — ромбиком с чертой или буквой Z

- Выводы питания часто не обозначаются на схеме

- Тактовые входы обозначаются буквой C или символом треугольника

Такая маркировка позволяет определить особенности подключения и функционирования специальных выводов микросхем.

Упрощение обозначений для типовых микросхем

Для часто используемых стандартных микросхем применяются упрощенные обозначения:

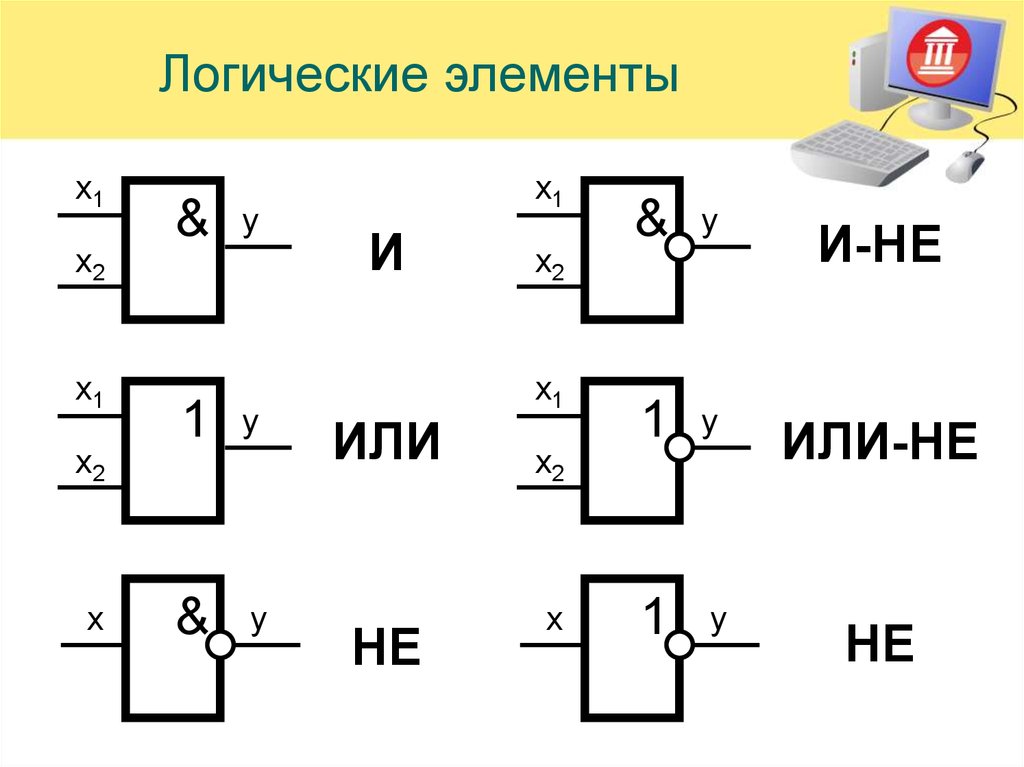

- Логические элементы обозначаются символами (&, 1, =1 и т.д.)

- Триггеры — прямоугольником с буквой T внутри

- Счетчики — прямоугольником с буквой CT

- Регистры — прямоугольником с RG

- Дешифраторы — DC

- Мультиплексоры — MUX

Это позволяет сделать схемы более компактными и читаемыми при использовании стандартных компонентов.

Основные обозначения на схемах

Микросхемы и их функционирование

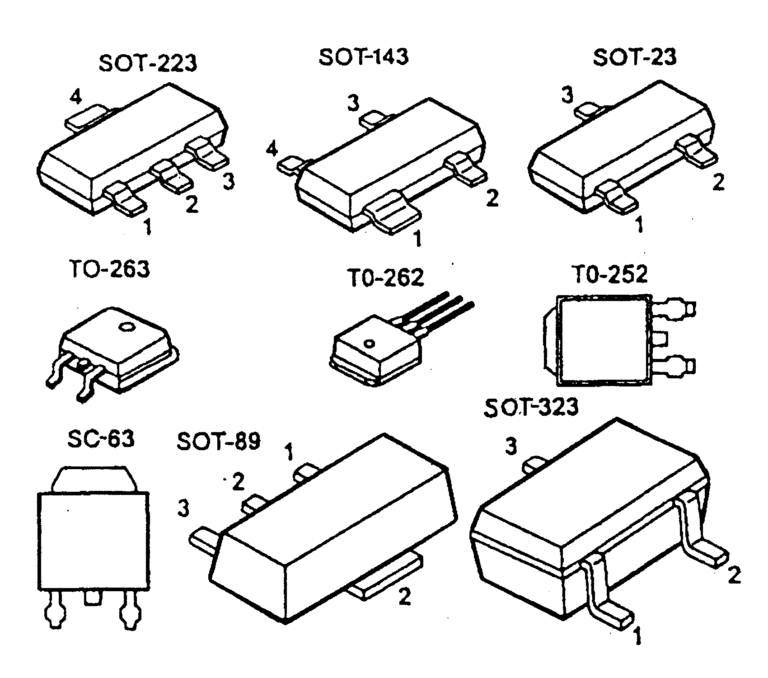

Рассматриваются обозначения цифровых микросхем, их выводов и сигналов на принципиальных схемах, особенности основных серий простейших цифровых микросхем, базовые типы корпусов микросхем, а также принципы двоичного кодирования и принципы работы цифровых устройств.

Основные обозначения на схемах

Для изображения электронных устройств и их узлов применяется три основных типа схем:

- принципиальная схема;

- структурная схема;

- функциональная схема.

Различаются они своим назначением и, самое главное, степенью детализации изображения устройств.

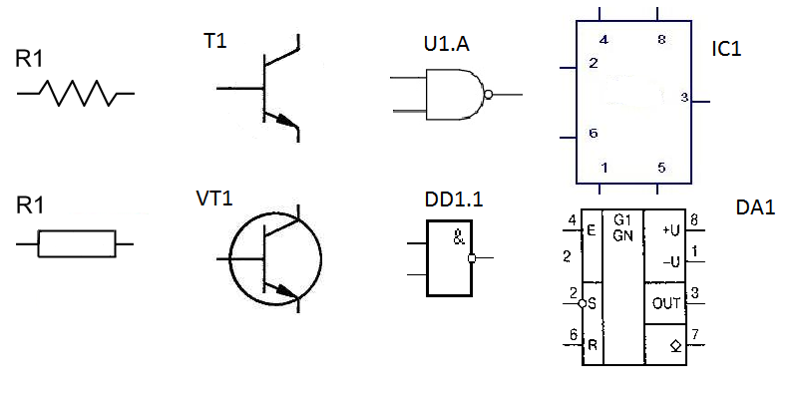

Принципиальная схема — наиболее подробная. Она обязательно показывает все использованные в устройстве элементы и все связи между ними. Если схема строится на основе микросхем, то должны быть показаны номера выводов всех входов и выходов этих микросхем. Принципиальная схема должна позволять полностью воспроизвести устройство. Обозначения принципиальной схемы наиболее жестко стандартизованы, отклонения от стандартов не рекомендуются.

Принципиальная схема должна позволять полностью воспроизвести устройство. Обозначения принципиальной схемы наиболее жестко стандартизованы, отклонения от стандартов не рекомендуются.

Структурная схема — наименее подробная. Она предназначена для отображения общей структуры устройства, то есть его основных блоков, узлов, частей и главных связей между ними. Из структурной схемы должно быть понятно, зачем нужно данное устройство и что оно делает в основных режимах работы, как взаимодействуют его части. Обозначения структурной схемы могут быть довольно произвольными, хотя некоторые общепринятые правила все-таки лучше выполнять.

Функциональная схема представляет собой гибрид структурной и принципиальной. Некоторые наиболее простые блоки, узлы, части устройства отображаются на ней, как на структурной схеме, а остальные — как на принципиальной схеме. Функциональная схема дает возможность понять всю логику работы устройства, все его отличия от других подобных устройств, но не позволяет без дополнительной самостоятельной работы воспроизвести это устройство.

В технической документации обязательно приводятся структурная или функциональная схема, а также обязательно принципиальная схема. В научных статьях и книгах чаще всего ограничиваются структурной или функциональной схемой, приводя принципиальные схемы только некоторых узлов.

А теперь рассмотрим основные обозначения, используемые на схемах.

Все узлы, блоки, части, элементы, микросхемы показываются в виде прямоугольников с соответствующими надписями. Все связи между ними, все передаваемые сигналы изображаются в виде линий, соединяющих эти прямоугольники. Входы и входы/выходы должны быть расположены на левой стороне прямоугольника, выходы — на правой стороне, хотя это правило часто нарушают, когда необходимо упростить рисунок схемы. Выводы и связи питания, как правило, не прорисовывают, если, конечно, не используются нестандартные включения элементов схемы.

Прежде чем перейти к более частным правилам, дадим несколько определений.

Положительный сигнал (сигнал положительной полярности) — это сигнал, активный уровень которого — логическая единица. То есть нуль — это отсутствие сигнала, единица — сигнал пришел (рис. 2.1).

Рис. 2.1. Элементы цифрового сигнала

Отрицательный сигнал (сигнал отрицательной полярности) — это сигнал, активный уровень которого — логический нуль. То есть единица — это отсутствие сигнала, нуль — сигнал пришел (рис. 2.1).

Активный уровень сигнала — это уровень, соответствующий приходу сигнала, то есть выполнению этим сигналом соответствующей ему функции.

Пассивный уровень сигнала — это уровень, в котором сигнал не выполняет никакой функции.

Инвертирование или инверсия сигнала — это изменение его полярности.

Инверсный выход — это выход, выдающий сигнал инверсной полярности по сравнению с входным сигналом.

Прямой выход — это выход, выдающий сигнал такой же полярности, какую имеет входной сигнал.

Положительный фронт сигнала — это переход сигнала из нуля в единицу.

Отрицательный фронт сигнала (спад) — это переход сигнала из единицы в нуль.

Передний фронт сигнала — это переход сигнала из пассивного уровня в активный.

Задний фронт сигнала — это переход сигнала из активного уровня в пассивный.

Тактовый сигнал (или строб) — управляющий сигнал, который определяет момент выполнения элементом или узлом его функции.

Шина — группа сигналов, объединенных по какому-то принципу, например, шиной называют сигналы, соответствующие всем разрядам какого-то двоичного кода.

Рис. 2.2. Обозначение входов и выходов

Для обозначения полярности сигнала на схемах используется простое правило: если сигнал отрицательный, то перед его названием ставится знак минус, например, -WR или -OE, или же (реже) над названием сигнала ставится черта. Если таких знаков нет, то сигнал считается положительным. Для названий сигналов обычно используются латинские буквы, представляющие собой сокращения английских слов, например, WR — сигнал записи (от «write» — «писать»).

Если таких знаков нет, то сигнал считается положительным. Для названий сигналов обычно используются латинские буквы, представляющие собой сокращения английских слов, например, WR — сигнал записи (от «write» — «писать»).

Инверсия сигнала обозначается кружочком на месте входа или выхода. Существуют инверсные входы и инверсные выходы (рис. 2.2).

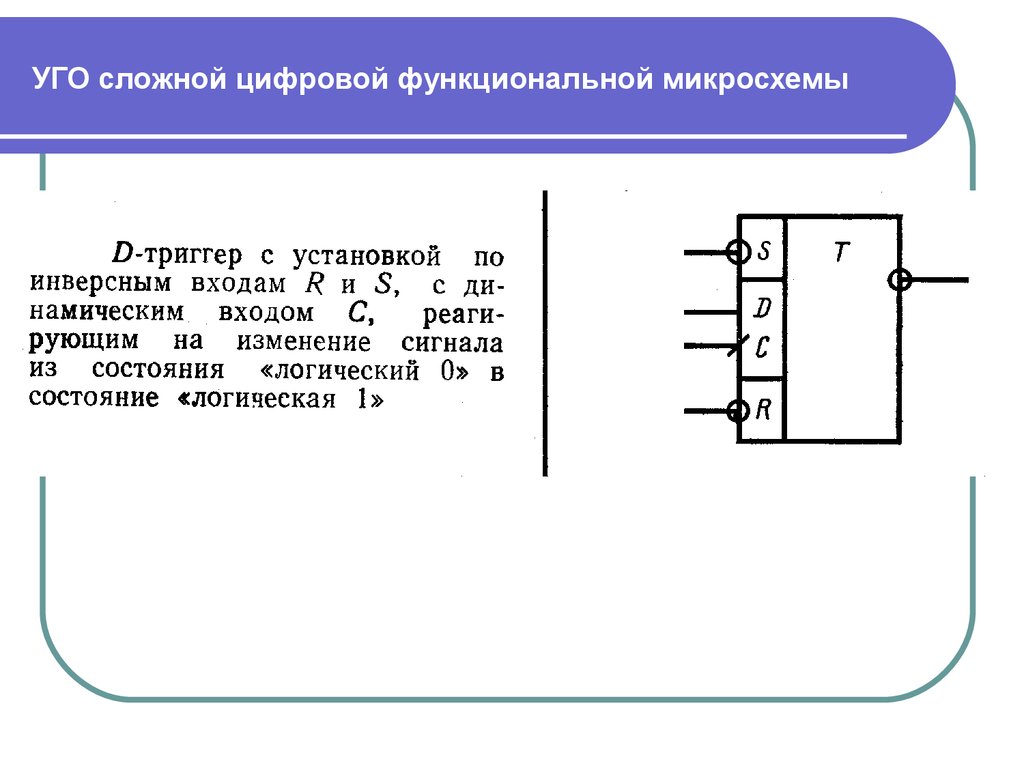

Если какая-то микросхема выполняет функцию по фронту входного сигнала, то на месте входа ставится косая черта (под углом 45°), причем наклон вправо или влево определяется тем, положительный или отрицательный фронт используется в данном случае (рис. 2.2).

Тип выхода микросхемы помечается специальным значком: выход 3С — перечеркнутым ромбом, а выход ОК — подчеркнутым ромбом (рис. 2.2). Стандартный выход (2С) никак не помечается.

Наконец, если у микросхемы необходимо показать неинформационные выводы, то есть выводы, не являющиеся ни логическими входами, ни логическими выходами, то такой вывод помечается косым крестом (две перпендикулярные линии под углом 45°). Это могут быть, например, выводы для подключения внешних элементов (резисторов, конденсаторов) или выводы питания (рис. 2.3).

Это могут быть, например, выводы для подключения внешних элементов (резисторов, конденсаторов) или выводы питания (рис. 2.3).

Рис. 2.3. Обозначение неинформационных выводов

В схемах также предусматриваются специальные обозначения для шин (рис. 2.4). На структурных и функциональных схемах шины обозначаются толстыми линиями или двойными стрелками, причем количество сигналов, входящих в шину, указывается рядом с косой чертой, пересекающей шину. На принципиальных схемах шина тоже обозначается толстой линией, а входящие в шину и выходящие из шины сигналы изображаются в виде перпендикулярных к шине тонких линий с указанием их номера или названия (рис. 2.4). При передаче по шине двоичного кода нумерация начинается с младшего разряда кода.

Рис. 2.4. Обозначение шин

При изображении микросхем используются сокращенные названия входных и выходных сигналов, отражающие их функцию. Эти названия располагаются на рисунке рядом с соответствующим выводом. Также на изображении микросхем указывается выполняемая ими функция (обычно в центре вверху). Изображение микросхемы иногда делят на три вертикальные поля. Левое поле относится к входным сигналам, правое — к выходным сигналам. В центральном поле помещается название микросхемы и символы ее особенностей. Неинформационные выводы могут указываться как на левом, так и на правом поле; иногда их показывают на верхней или нижней стороне прямоугольника, изображающего микросхему.

Также на изображении микросхем указывается выполняемая ими функция (обычно в центре вверху). Изображение микросхемы иногда делят на три вертикальные поля. Левое поле относится к входным сигналам, правое — к выходным сигналам. В центральном поле помещается название микросхемы и символы ее особенностей. Неинформационные выводы могут указываться как на левом, так и на правом поле; иногда их показывают на верхней или нижней стороне прямоугольника, изображающего микросхему.

В табл. 2.1 приведены некоторые наиболее часто встречающиеся обозначения сигналов и функций микросхем. Микросхема в целом обозначается на схемах буквами DD (от английского «digital» — «цифровой») с соответствующим номером, например, DD1, DD20.1, DD38.2 (после точки указывается номер элемента или узла внутри микросхемы).

| Таблица 2.1. Некоторые обозначения сигналов и микросхем | ||

| Обозначение | Название | Назначение |

| & | And | Элемент И |

| =1 | Exclusive Or | Элемент Исключающее ИЛИ |

| Or | Элемент ИЛИ | |

| А | Address | Адресные разряды |

| BF | Buffer | Буфер |

| C | Clock | Тактовый сигнал (строб) |

| CE | Clock Enable | Разрешение тактового сигнала |

| CT | Counter | Счетчик |

| CS | Chip Select | Выбор микросхемы |

| D | Data | Разряды данных, данные |

| DC | Decoder | Дешифратор |

| EZ | Enable Z-state | Разрешение третьего состояния |

| G | Generator | Генератор |

| I | Input | Вход |

| I/O | Input/Output | Вход/Выход |

| OE | Output Enable | Разрешение выхода |

| MS | Multiplexer | Мультиплексор |

| Q | Quit | Выход |

| R | Reset | Сброс (установка в нуль) |

| RG | Register | Регистр |

| S | Set | Установка в единицу |

| SUM | Summator | Сумматор |

| T | Trigger | Тригер |

| TC | Terminal Count | Окончание счета |

| Z | Z-state | Третье состояние выхода |

Более полная таблица обозначений сигналов и микросхем, используемых в принципиальных схемах, приведена в приложении.

Дата добавления: 2017-06-13; просмотров: 3959; ЗАКАЗАТЬ НАПИСАНИЕ РАБОТЫ

УСЛОВНЫЕ ГРАФИЧЕСКИЕ ОБОЗНАЧЕНИЯ ЦИФРОВОЙ И АНАЛОГОВОЙ ТЕХНИКИ…

Привет, Вы узнаете про условные графические обозначения, Разберем основные ее виды и особенности использования. Еще будет много подробных примеров и описаний. Для того чтобы лучше понимать что такое условные графические обозначения, уго , настоятельно рекомендую прочитать все из категории Электроника, Микроэлектроника , Элементная база.

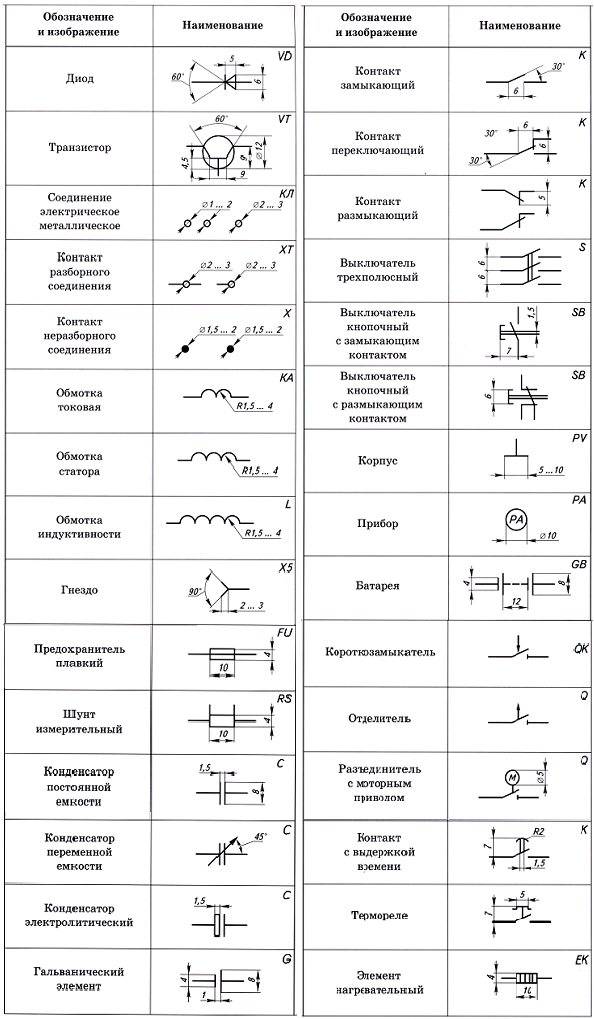

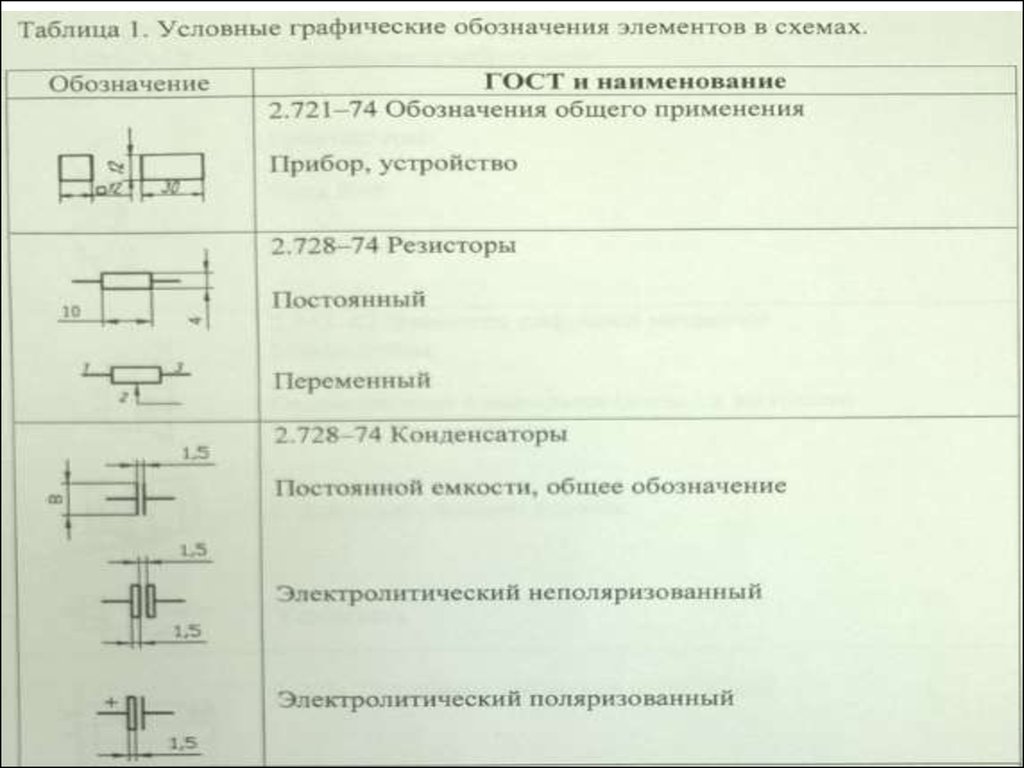

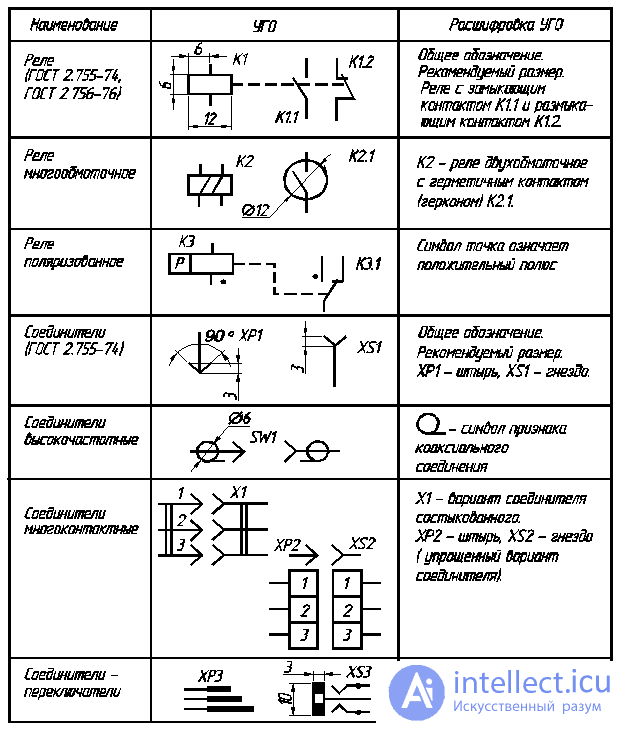

Электрические схемы цифровой и аналоговой техники являются основными документами при разработке, изготовлении, наладке и эксплуатации сложных устройств. При выполнении таких схем, наряду с требованиями ГОСТ 2.701-84 и ГОСТ 2.702-75 (см. разд. 1 пособия), следует учитывать ряд специфических требований, установленных ГОСТ 2.708-81. Правила, установленные этими стандартами, предусматривают выполнение документации ручным или автоматизированным способом. Охватить наиболее часто встречаемые

условные графические обозначения (

уго ) элементов цифровой и аналоговой техники – основная цель данной статьи

Охватить наиболее часто встречаемые

условные графические обозначения (

уго ) элементов цифровой и аналоговой техники – основная цель данной статьи

3.1. Элементы цифровой техники

УГО элементов цифровой техники (ЦТ) построены на основе прямоугольника (ГОСТ 2.743-82). В общем виде УГО может содержать основное поле и одно или два дополнительных, расположенных по обе стороны от основного (рис. 3.1). Следовательно, размер УГО зависит:

- по ширине – от числа полей и меток, расположенных в этих полях;

- по высоте – от числа выводов, интервалов между ними и числа строк в основном и дополнительных полях.

Ширина основного поля должна быть не менее 10 мм, дополнительных – не менее 5 мм, расстояние между выводами – не менее 5 мм, расстояние между выводом и горизонтальной стороной (или границей зоны) УГО – не менее 2,5 мм или кратным ему. Допускается увеличивать ширину полей при нанесении большого числа меток и функций. Выводы можно объединять в группы, которые разделяются интервалом не менее 10 мм или кратным 5 мм.

Допускается увеличивать ширину полей при нанесении большого числа меток и функций. Выводы можно объединять в группы, которые разделяются интервалом не менее 10 мм или кратным 5 мм.

Рис. 3.1. Рекомендуемые размеры и обозначения элемента ЦТ

Выводы элементов подразделяются на входы, выходы, двунаправленные выводы и неинформационные. Входы изображают слева, а выходы – справа. Допускается поворот УГО на 90° по часовой стрелке (рис. 3.2).

Рис. 3.2. Расположение выводов и обозначений при повороте элемента ЦТ

Функциональное назначение элемента цифровой техники указывают в верхней части основного поля УГО (рис. 3.1), которое состоит из прописных букв латинского алфавита, арабских цифр, специальных знаков и символов, вписываемых без пробелов. Обозначение основных функций и их производных сведены в табл. 3.1.

Таблица 3.1 Обозначение основных функций ЦТ и их производных

|

Основная функция |

Код функции |

|

Вычислитель вычислительное устройство (центральный процессор) Процессор Секция процессора Память Оперативное запоминающее устройство с произвольным доступом с последовательным доступом Постоянное запоминающее устройство с одноразовым и многоразовым программированием Управление Перенос Прерывание Передача Прием Ввод/вывод последовательный Ввод/вывод параллельный Арифметика Суммирование Вычитание Умножение Деление Логика Логическое И Логическое ИЛИ Исключающее ИЛИ Повторитель Регистр Регистр со сдвигом слева направо Регистр со сдвигом справа налево Регистр с реверсивным сдвигом Счетчик двоичный десятичный Дешифратор Шифратор Преобразователь Сравнение Мультиплексор Демультиплексор Мультиплексор-селектор |

CP CPU P PS M RAM SAM PROM RPROM CO CR INR TF RC IOS IOP A SM SUB MPL DIV L & или И ³1 =1 1 RG RG® RG¬ RG« CT CT10 DC CD X/Y = = MUX DMX MS |

Окончание табл. 3.1

3.1

|

Основная функция |

Код функции |

|

Селектор Генератор непрерывной последовательности импульсов одиночного импульса (одновибратор) синусоидального сигнала Триггер двуступенчатый Шмитта Формирователь логического 0 логической 1 Ключ Модулятор Демодулятор Нелогические элементы Стабилизатор напряжения тока Наборы (сборки): резисторов диодов транзисторов индикаторов |

SL G GN G1 GSIN T TT TH F FL0 FL1 SW MD DM * ST STU STI *R *D *T *H |

В некоторых элементах ЦТ допускается двоякое обозначение. Например, в обозначении одновибраторов, кроме буквенно-цифрового кода G1, указанного в табл. 3.1, можно использовать символ в виде прямоугольного импульса положительной полярности (П), в обозначении триггеров – символ, схожий с петлей гистерезиса. Нелогические элементы ЦТ – наборы резисторов, диодные и транзисторные матрицы и т. п. помечают звездочкой (*). При необходимости такое обозначение дополняют технической характеристикой. Резисторная сборка, например, может быть обозначена как *R150-8, т. е. восемь резисторов с сопротивлением по 150 Ом.

Например, в обозначении одновибраторов, кроме буквенно-цифрового кода G1, указанного в табл. 3.1, можно использовать символ в виде прямоугольного импульса положительной полярности (П), в обозначении триггеров – символ, схожий с петлей гистерезиса. Нелогические элементы ЦТ – наборы резисторов, диодные и транзисторные матрицы и т. п. помечают звездочкой (*). При необходимости такое обозначение дополняют технической характеристикой. Резисторная сборка, например, может быть обозначена как *R150-8, т. е. восемь резисторов с сопротивлением по 150 Ом.

Сложные функции элемента ЦТ показывают сочетанием из простых. Например, двоичный счетчик с дешифратором обозначается сочетаниемCT2DC, управление записью (WR) – COWR, дешифратор (DC) прерываний(INR) – DCINR и т . Об этом говорит сайт https://intellect.icu . д.

В последнее время все чаще приходится сталкиваться с зарубежной цифровой и аналоговой техникой. Нужно отметить, что в УГО ее элементов стандарты ЕСКД наиболее близки стандартам стран ЕЭС, в частности, BS3939 (Великобритания) и сильно отличаются от американского стандартаANSI. Условные обозначения перечисленных функциональных схем см. в подразд. 3.2.

Условные обозначения перечисленных функциональных схем см. в подразд. 3.2.

3.2. Маркировка выводов элементов цифровой техники

Выводы элементов ЦТ различают статические и динамические.

В свою очередь каждый из них может быть прямым или инверсным.

- На прямом статическом выводе (выходе) двоичная переменная равна 1, если сигнал на выводе (входе) в активном состоянии имеет такое же значение.

- На инверсном статическом выводе (выходе) переменная равна 1, если сигнал на выводе (входе) в активном состоянии имеет уровень 0.

- На прямом динамическом выводе переменная имеет значение 1, если значение на выводе (входе) меняется с 0 на 1.

- На инверсном динамическом выводе переменная имеет значение 1, если значение на выводе (входе) меняется с 1 на 0.

Эти положения отражаются в УГО (рис. 3.3). Прямые статические выводы изображаются линиями, соединенными с основным или дополнительными полями, без дополнительных символов (рис. 3.3, а).

3.3, а).

Прямые инверсные выводы отмечают кружком в месте присоединения с полями (рис. 3.3, б, в, г, д). Предпочтительными считаются обозначения на рис. 3.3, б, в).

Для обозначения динамических выводов используют такие символы, как косая черта, стрелка и треугольник . На рис. 3.3, е, ж, и показаны обозначения прямых динамических выводов, а на рис. 3.3, к, л, м, н – инверсных динамических выводов. Предпочтительными считаются обозначения, показанные на рис. 3.3, е, ж, к, л.

Неинформационный вывод отмечают крестиком, который наносится в месте его присоединения с полем или вблизи поля (рис. 3.3, п, р, с). Если неинформационные выводы сгруппированы, то символ выносится в зону на линию, общую с основным полем (рис. 3.3, с).

Рис. 3.3. Маркировка выводов элемента ЦТ

Назначение выводов показывают метками в дополнительных полях. Метки представляют собой комбинацию из латинских букв, арабских цифр и специальных знаков. Обозначение основных меток приведено в табл. 3.2.

Метки представляют собой комбинацию из латинских букв, арабских цифр и специальных знаков. Обозначение основных меток приведено в табл. 3.2.

Таблица 3.2

Назначение выводов и их кодировка

|

Назначение вывода |

Код метки |

|

Установка в состояние n 1 0 исходное состояние (сброс) Разрешение установки универсального JK-триггера в состояние 1 0 Вход увеличения содержимого элемента на n Вход уменьшения содержимого элемента на n Адрес Адресация по координате X Y Больше Больше или равно Равенство Меньше Меньше или равно Бит Байт Условный бит – «флажок» Блокировка (запрет) Буфер Готовность Данные Заем Запись Считывание Запрос Захват Исполнение (конец) Инструкция (команда) Контроль Маркер Начало |

Sn S R SR J K +n -n « или < > A X Y > ³ = < £ BIT BY EL DE BF RA D BR WR RD RQ TR END INS CH MR BG |

Окончание табл. 3.2

3.2

|

Назначение вывода |

Код метки |

|

Ожидание Ответ Перенос Распространение переноса Генерация переноса Переполнение Повтор Продолжение Приоритет Пуск Разрешение Расширение Регенерация Синхронизация Строб, такт Младший Средний Старший Шина Инверсия |

WI AN CR CRP CPG OF RP CN PR ST E EX REF SYN C LSB ML MSB B IN |

Для обозначения так называемых открытых выводов элементов ЦТ используют специальные символы, такие как ромбик (рис. 3.4, а), кружок с четырьмя лучами (рис. 3.4, б).

3.4, а), кружок с четырьмя лучами (рис. 3.4, б).

Если необходимо уточнить, что данный вывод соединен с коллектором транзистора структуры p–n–p, эмиттером транзистора структуры n–p–n, стоком полевого транзистора с p-каналом или истоком полевого транзистора с n-каналом, то ромбик снабжают черточкой сверху (рис. 3.4, в),

а кружок – уголком с обращенным к нему «раскрывом» (рис. 3.4, г).

В случае, если перечисленные электроды принадлежат транзисторам противоположной структуры или полевым транзисторам с каналами противоположного типа, то черточка у ромбика помещается снизу

(рис. 3.4, д), а вершину уголка направляют в сторону кружка (рис. 3.4, е).

Выводы, имеющие состояние высокого импеданса (Z-состояние), обозначают ромбиком с черточкой внутри (рис. 3.4, ж) или латинской буквой Z(рис. 3.4, и).

Метки сложных функций выводов составляют из простых. Например, чтобы указать разрешение (Е) записи (WR), используют сочетание EWR, а разрешение считывания – чтения (RD) – ERD и т. п. В качестве меток выводов допускается использование обозначений функций и их производных из табл. 3.1.

п. В качестве меток выводов допускается использование обозначений функций и их производных из табл. 3.1.

Рис. 3.4. Маркировка выводов элемента ЦТ с уточнением структуры прибора

Для нумерации разрядов в группах выводов к обозначениям метки добавляются цифры, соответствующие их номерам. Например, информационный вывод нулевого разряда обозначают D0, первого – D1, а второго – D2 и т. д. Допускается обозначение нулевого разряда как D1, первого – D2 и т. д.

Для уменьшения числа знаков в метке допускается вместо весового коэффициента указывать степень его основания. Например, информационный вход с весовым коэффициентом 256 (28) можно обозначить D8 или 8, где стрелка поясняет, что число означает степень.

Если выводы равнозначны и их функции однозначно определяются функцией элемента, то УГО не содержит дополнительных полей. В этом случае расстояния между выводами равны, а сторона УГО, к которой примыкают выводы, делится также на равные части. Например, двухвходовый элемент 2И-НЕ поделит сторону УГО на три равные части (рис. 3.5, а). Метка логики выводов располагается в УГО напротив первого входа сверху. Допускается объединение равнозначных логических выводов в группу с присвоением метки в дополнительном поле. Так, например, метка «&» означает, что все пять выводов элемента объединены логической функцией И, а буква R показывает что каждый вывод (рис. 3.5, б) служит для установки логического элемента в состояние 0. Другие метки и буквы выбираются по назначению (табл. 3.2). Допускается объединение меток выводов элемента в группу, если выполняется однозначная функция (рис. 3.5, в, г).

3.5, а). Метка логики выводов располагается в УГО напротив первого входа сверху. Допускается объединение равнозначных логических выводов в группу с присвоением метки в дополнительном поле. Так, например, метка «&» означает, что все пять выводов элемента объединены логической функцией И, а буква R показывает что каждый вывод (рис. 3.5, б) служит для установки логического элемента в состояние 0. Другие метки и буквы выбираются по назначению (табл. 3.2). Допускается объединение меток выводов элемента в группу, если выполняется однозначная функция (рис. 3.5, в, г).

Двунаправленные выводы обозначают меткой в виде двунаправленной стрелки или двух знаков “< >“. Принято располагать подобные метки над меткой входной функции и под меткой выходной функции, как показано на рис. 3.6, в обозначении входной функции XA и выходной функции YА.

Рис. 3.5. Обозначение выводов с применением меток

Рис. 3.6. Обозначение двунаправленных выводов

Если вывод имеет несколько функциональных назначений и/или взаимосвязей, то их также объединяют в группу, записывая метки одну под другой (рис. 3.7, а). При уточнении выполнения той или иной функции и/или взаимосвязи применяют условные обозначения, показанные на рис. 3.7, б. В данном примере, при сигнале, равном логической 1, выполняется функция Х1, при логическом 0 – функция Х2, при переходе сигнала с уровня 0 до 1 выполняется функция Х3, а наоборот, – функция Х4.

3.7, а). При уточнении выполнения той или иной функции и/или взаимосвязи применяют условные обозначения, показанные на рис. 3.7, б. В данном примере, при сигнале, равном логической 1, выполняется функция Х1, при логическом 0 – функция Х2, при переходе сигнала с уровня 0 до 1 выполняется функция Х3, а наоборот, – функция Х4.

Рис. 3.7. Обозначение выводов, имеющих несколько логических функций

Для выводов, которые не несут логическую информацию (к ним относят выводы питания, электродов полупроводниковых приборов, выводы для подключения резисторов, конденсаторов, кварцевых резонаторов в частотно-задающих цепях), применяют метки буквенно-цифрового кода. Например, на рис. 3.8, а показан фрагмент УГО микросхемы, в которой в одном поле указаны выводы источников двуполярного питания, в другом поле – вывод Kколлектора транзистора типа p–n–p и вывод E эмиттера транзистора типа n–p–n. В третьем поле собраны выводы для подключения резистора, конденсатора, катушки индуктивности и кварцевого резонатора.

Рис. 3.8. Обозначение выводов, не имеющих логических функций

В данном учебном пособии не приводятся типовые УГО элементов цифровых схем, основанных на логике И, И-НЕ, ИЛИ-НЕ, И/ИЛИ-НЕ, триггерныеустройства, счетчики, регистры, дешифраторы и шифраторы, мультиплексоры и т. д. Их можно найти в справочниках по цифровым интегральным микросхемам .

Остановимся на некоторых приемах, используемых при вычерчивании схем цифровых устройств.

Например, рис. 3.9 поясняет, что если устройство содержит несколько одинаковых элементов с числом выводов одного и того же функционального значения, то допускается один из этих элементов начертить полностью, а другие – упрощенно.

Рис. 3.9. Упрощение при повторении одинаковых элементов

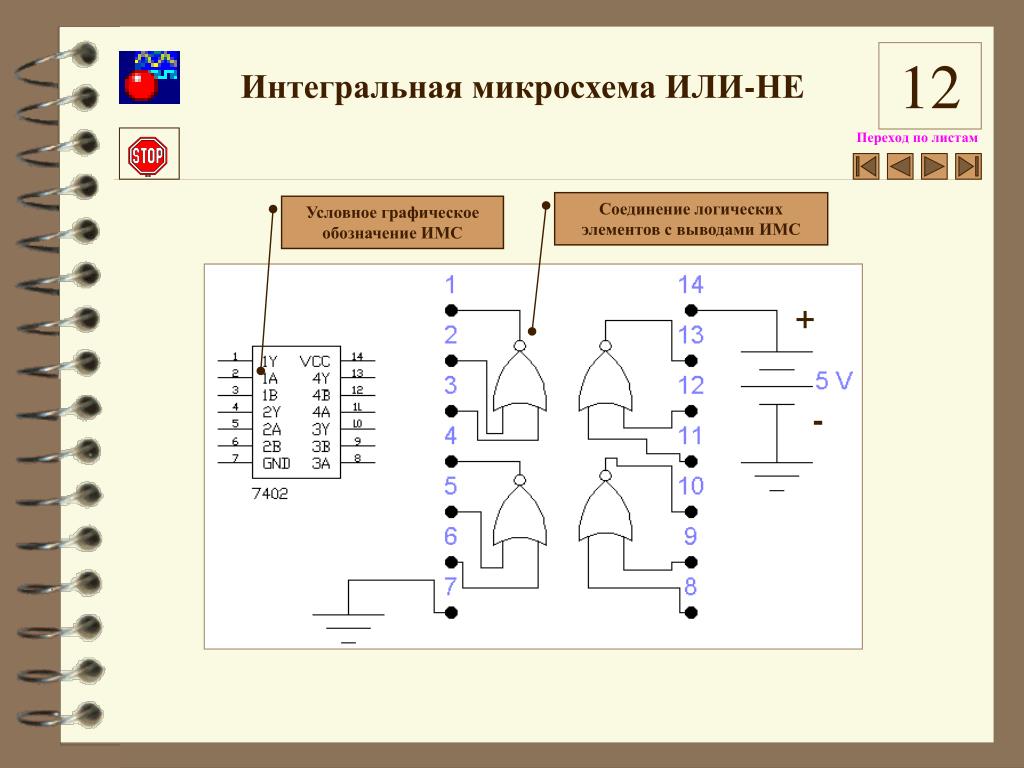

Поскольку цифровые интегральные микросхемы могут содержать по несколько одинаковых логических или иных элементов в одном корпусе, то допускается изображать их схемы как совмещенным, так и разнесенным способом (рис. 3.10).

Рис. 3.10. УГО одинаковых элементов ИМС

3.10. УГО одинаковых элементов ИМС

Одинаковые элементы, образующие столбец или строку, допускается разделять линиями электрической связи (рис. 3.11).

Рис. 3.11. Разделение элементов линиями электрической связи

В этом случае контурные линии УГО вычерчивают не полностью, а с разрывом не менее 1 мм до линии электрической связи.

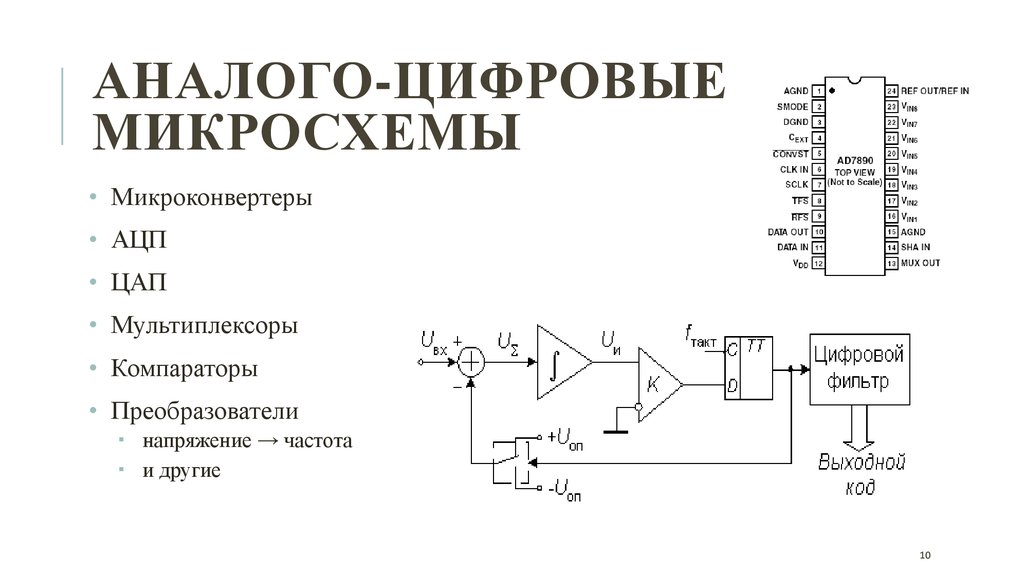

3.3. Элементы аналоговой техники

К элементам аналоговой техники относятся различные усилители

(в том числе суммирующие, дифференцирующие, интегрирующие и др.), функциональные, аналого-цифровые и цифро-аналоговые преобразователи (АЦП и ЦАП), электронные ключи, коммутаторы и т. д. Чаще всего эти устройства выпускаются в виде интегральных схем, поэтому в позиционных обозначениях на схеме применяют код DA.

УГО элементов аналоговой техники устанавливают ГОСТ 2.743-82 и ГОСТ 2.759-82.

УГО изделий этой группы построены аналогично символам элементов цифровой техники. Это значит, что кроме основного поля, они могут содержать дополнительные поля, и их количество и размеры определяются числом выводов, числом знаков в метках, обозначениями функций и т. д.

д.

Входы элементов аналоговой техники располагают слева, а выходы – справа на УГО. Допускается поворот изображения на 90° по часовой стрелке. В этом случае вход элемента будет располагаться внизу, а выход – вверху. Инверсный вход в отличие от прямого обозначается кружком в месте присоединения к контуру УГО элемента (рис. 3.12).

Рис. 3.12. Рекомендуемые размеры и обозначения элемента аналоговой техники

Внешне УГО аналоговой техники почти не отличается от цифровой (сравни рис. 3.1 и 3.12). Различие состоит в функциональном обозначении элементов. Обозначения наиболее часто встречающихся функций в аналоговой технике показаны в табл. 3.3.

Таблица 3.3 Обозначение функций в аналоговой технике

|

Наименование функции |

Код |

|

Детектирование |

DK |

|

Деление |

X:Y или x:y |

|

Деление частоты |

:FR или :fr |

|

Дифференцирование |

D/DT или :d/dt |

|

Интегрирование |

INT или :ò |

|

Логарифмирование |

LOG или :log |

|

Замыкание |

SWM |

|

Размыкание |

SWB |

|

Переключение |

SWT |

|

Преобразование |

X/Y или x/y |

|

Преобразование аналого-цифровое |

Ù / # |

|

Преобразование цифро-аналоговое |

# / Ù |

|

Сравнение |

= = |

|

Суммирование |

SM или S |

|

Тригонометрические функции: синус косинус тангенс котангенс |

SIN или sin COS или cos TG или tg CT или ct |

|

Умножение |

XY или xy |

|

Усиление |

> или |

Символы сложных функций, как и в цифровой технике, составляют из простых. Допускается использовать в случае необходимости обозначения, установленные для цифровой техники (табл. 3.1 и 3.2).

Допускается использовать в случае необходимости обозначения, установленные для цифровой техники (табл. 3.1 и 3.2).

Назначение выводов указывают метками, которые располагают в дополнительных полях. Обозначения основных меток приведены в табл. 3.4.

Таблица 3.4 Обозначение меток в аналоговой технике

|

Метка вывода |

Код |

|

Балансировка (коррекция 0) |

NC |

|

Коррекция частотная |

FC |

|

Начальное значение интегрирования |

1 |

|

Общий вывод |

0V |

|

Поддержание текущего значения сигнала |

H |

|

Питание: от источника напряжения (общее обозначение) от источника напряжения (например, +15 V) |

U + 15 V |

|

Пуск |

ST |

|

Строб, такт |

C |

|

Установка начального значения |

S |

|

Установка в состояние 0 |

R |

Рис. 3.13. УГО операционного усилителя

3.13. УГО операционного усилителя

УГО операционного усилителя изображено на рис. 3.13. У него один выход (правый верхний по рисунку) и два входа: прямой (неинвертирующий), так как фаза выходного сигнала совпадает с фазой сигнала, поданной на вход) и инверсный (инвертирующий) – фаза выходного сигнала сдвинута на 180° относительно сигнала, поступившего на вход. Выводы с метками «+15V» и « –15V» предназначены для подключения двуполярного источника питания ±15V. Выводы с метками FC предназначены для подключения внешней цепи, корректирующей АЧХ операционного усилителя. Заметим, что некоторые виды операционных усилителей имеют внутренние цепи коррекции АЧХ. К выводам NC (коррекция нуля) подключаются элементы установки нулевого напряжения на выходе при отсутствии сигнала на входах. Если операционный усилитель изготовлен в металлическом корпусе и имеет вывод, то последний обозначается в виде перевернутой буквы Т. Этот вывод нельзя путать с выводом общего провода двуполярного питания, которому присваивается метка 0V.

Примеры УГО элементов аналоговой техники сведены в табл. 3.5.

Таблица 3.5 Примеры УГО элементов аналоговой техники по ГОСТ 2.759-82

|

Наименование и выполняемая |

УГО элемента |

|

Усилитель инвертирующий (инвентор) с коэффициентом усиления 1 u = – 1a |

|

|

Усилитель суммирующий u = –50(0,1 + 0,2b + 0,4c + 0,8d) |

|

|

Усилитель интегрирующий Если f = 1; g = 0; h = 0, то

|

|

|

Усилитель дифференцирующий

|

|

Окончание табл. 3.5

3.5

|

Наименование и выполняемая |

УГО элемента |

|

Перемножитель с коэффициентом передачи u = – Kab |

|

|

Делитель |

|

|

Усилитель логарифмирующий u = log(a – 2b) |

|

|

Преобразователь сигналов , общееобозначение |

|

|

Преобразователь полярных координат в прямоугольные u1 = a cos b u2 = a sin b |

|

Вопросы для самопроверки

- 1.

На какие поля делится УГО элемента цифровой техники?

На какие поля делится УГО элемента цифровой техники? - 2. От каких параметров зависят размеры элемента УГО?

- 3. Как маркируется инверсный вывод элемента цифровой техники?

- 4. Какое буквенное обозначение УГО элемента цифровой техники?

- 5. Каким символом обозначают двунаправленный вывод элемента УГО цифровой техники?

- 6. Назовите упрощения УГО при повторении одинаковых элементов.

- 7. Назовите буквенный код УГО элемента аналоговой техники.

- 8. В чем различие УГО элементов аналоговой и цифровой техники?

См. также

- условные графические обозначения , элементов электрических схем , уго ,

К сожалению, в одной статье не просто дать все знания про условные графические обозначения. Но я — старался.

Если ты проявишь интерес к раскрытию подробностей,я обязательно напишу продолжение! Надеюсь, что теперь ты понял что такое условные графические обозначения, уго

и для чего все это нужно, а если не понял, или есть замечания,

то нестесняся пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории

Электроника, Микроэлектроника , Элементная база

Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории

Электроника, Микроэлектроника , Элементная база

Ответы на вопросы для самопроверки пишите в комментариях, мы проверим, или же задавайте свой вопрос по данной теме.

ГОСТ 21.404-85 СПДС. Автоматизация технологических процессов. Обозначения условные приборов и средств автоматизации в схемах

Любые цифровые микросхемы строятся на основе простейших логических элементов.

Это инвертор, логический сумматор “ИЛИ” и логический умножитель “И”

Простейшим логическим элементом является инвертор, который просто изменяет входной сигнал на прямо противоположное значение. Его логическая функция записывается в следующем виде:

где черта над входным значением и обозначает изменение его на противоположное. То же самое действие можно записать при помощи таблицы истинности, приведённой в таблице 1. Так как вход у инвертора только один, то его таблица истинности состоит всего из двух строк.

В качестве логического инвертора можно использовать простейший усилитель с транзистором, включенном по схеме с общим эмиттером (или истоком для полевого транзистора). Принципиальная схема логического элемента инвертора, выполненная на биполярном n-p-n транзисторе, приведена на рисунке 1.

Микросхемы логических инверторов могут обладать различным временем распространения сигнала и могут работать на различные виды нагрузки. Они могут быть выполнены на одном или на нескольких транзисторах. Наиболее распространены логические элементы, выполненные по ТТЛ, ЭСЛ и КМОП технологиям. Но независимо от схемы логического элемента и её параметров все они осуществляют одну и ту же функцию.

Для того, чтобы особенности включения транзисторов не затеняли выполняемую функцию, были введены специальные обозначения для логических элементов — условно-графические обозначения. Условно-графическое обозначение инвертора приведено на рисунке 2.

Инверторы присутствуют практически во всех сериях цифровых микросхем. В отечественных микросхемах инверторы обозначаются буквами ЛН. Например, в микросхеме 1533ЛН1 содержится 6 инверторов. Иностранные микросхемы для обозначения типа микросхемы используется цифровое обозначение. В качестве примера микросхемы, содержащей инверторы, можно назвать 74ALS04. В названии микросхемы отражается, что она совместима с ТТЛ микросхемами (74), произведена по улучшеной малопотребляющей шоттки технологии (ALS), содержит инверторы (04).

В отечественных микросхемах инверторы обозначаются буквами ЛН. Например, в микросхеме 1533ЛН1 содержится 6 инверторов. Иностранные микросхемы для обозначения типа микросхемы используется цифровое обозначение. В качестве примера микросхемы, содержащей инверторы, можно назвать 74ALS04. В названии микросхемы отражается, что она совместима с ТТЛ микросхемами (74), произведена по улучшеной малопотребляющей шоттки технологии (ALS), содержит инверторы (04).

В настоящее время чаще применяются микросхемы поверхностного монтажа (SMD микросхемы), в которых содержится по одному логическому элементу, в частности инвертору. В качестве примера можно назвать микросхему SN74LVC1G04. Микросхема произведена фирмой Texas Instruments (SN), совместима с ТТЛ микросхемами (74) произведена по низковольтовой КМОП технологии (LVC), содержит только один логический элемент (1G), им является инвертор (04).

Для исследования инвертирующего логического элемента можно использовать широкодоступные радиоэлектронные элементы. Так, в качестве генератора входных сигналов можно использовать обычные переключатели или тумблеры. Для исследования таблицы истинности можно даже применить обычный провод, который будем поочередно подключать к источнику питания и ли общему проводу. В качестве логического пробника может быть использована низковольтовая лампочка или светодиод, соединенный последовательно с токоограничивающим резистором. Принципиальная схема исследования логического элемента инвертора, реализованная с помощью этих простейших радиоэлектронных элементов, приведена на рисунке 3.

Так, в качестве генератора входных сигналов можно использовать обычные переключатели или тумблеры. Для исследования таблицы истинности можно даже применить обычный провод, который будем поочередно подключать к источнику питания и ли общему проводу. В качестве логического пробника может быть использована низковольтовая лампочка или светодиод, соединенный последовательно с токоограничивающим резистором. Принципиальная схема исследования логического элемента инвертора, реализованная с помощью этих простейших радиоэлектронных элементов, приведена на рисунке 3.

Схема исследования цифрового логического элемента, приведенная на рисунке 3, позволяет наглядно получить данные для таблицы истинности. Подобное исследование проводится в лабораторной работе 1 Исследование цифровых устройств на основе программируемых логических интегральных схем (ПЛИС) в среде Quartus II. Более полные характеристики цифрового логического элемента инвертора, такие как время задержки входного сигнала, скорость нарастания и спадания фронтов сигнала на выходе, можно получить при помощи импульсного генератора и осциллографа (желательно двухканального осциллографа).

Условные графические обозначения

Приводы и исполнительные механизмы имеют условные графические обозначения.

В схемах различных устройств применяют обозначения символами отдельных частей. Ими могут являться группы элементов, частотные преобразователи, двигатели и другие. А также могут быть воспроизводящие устройства, источники питания.

Функциональные элементы изображают разными фигурами. Чтобы было более понятно внутри обозначений размещены знаки, определяющие мнемоничность режима.

Многие символы изображены квадратами.

Введение

Но начнем немного издалека…

Каждый молодой специалист, который приходит в проектирование, начинает либо со складывания чертежей, либо с чтения нормативной документации, либо нарисуй «вот это» по такому примеру. Вообще, нормативная литература изучается по ходу работы, проектирования.

Невозможно прочитать всю нормативную литературу, относящуюся к твоей специальности или, даже, более узкой специализации. Тем более, что ГОСТ, СНиП и другие нормативы периодически обновляются. И каждому проектировщику приходится отслеживать изменения и новые требования нормативных документов, изменения в линейках производителей электрооборудования, постоянно поддерживать свою квалификацию на должном уровне.

Тем более, что ГОСТ, СНиП и другие нормативы периодически обновляются. И каждому проектировщику приходится отслеживать изменения и новые требования нормативных документов, изменения в линейках производителей электрооборудования, постоянно поддерживать свою квалификацию на должном уровне.

Помните, как Льюиса Кэролла в «Алисе в Стране Чудес»?

«Нужно бежать со всех ног, чтобы только оставаться на месте, а чтобы куда-то попасть, надо бежать как минимум вдвое быстрее!»

Это я не к тому, чтобы поплакаться «как тяжела жизнь проектировщика» или похвастаться «смотрите, какая у нас интересная работа». Речь сейчас не об этом. Учитывая такие обстоятельства, проектировщики перенимают практический опыт от более опытных коллег, многие вещи просто знают как делать правильно, но не знают почему. Работают по принципу «Здесь так заведено».

Порой, это достаточно элементарные вещи. Знаешь, как сделать правильно, но, если спросят «Почему так?», ответить сразу не сможешь, сославшись хотя бы на название нормативного документа.

В этой статье я решил структурировать информацию, касающуюся условных обозначений, разложить всё по полочкам, собрать всё в одном месте.

1. УСЛОВНЫЕ ОБОЗНАЧЕНИЯ

1.1. Графические обозначения

1.1.1. Графические обозначения приборов, средств автоматизации и линий связи должны соответствовать приведенным в табл. 1.

Таблица 1

1.1.2. Отборное устройство для всех постоянно подключенных приборов изображают сплошной тонкой линией, соединяющей технологический трубопровод или аппарат с прибором (черт. 1). При необходимости указания конкретного места расположения отборного устройства (внутри контура технологического аппарата) его обозначают кружком диаметром 2 мм (черт. 2).

1.2. Буквенные обозначения

1.2.1. Основные буквенные обозначения измеряемых величин и функциональных признаков приборов должны соответствовать приведенным в табл. 2.

Таблица 2

| Измеряемая величина | Функциональный признак прибора | ||||

| Обозначение | Основное обозначение измеряемой величины | Дополнительное обозначение, уточняющее измеряемую величину |

Отображение информации |

Формирование выходного сигнала | Дополнительное значение |

| А | + | – | Сигнализация | – | – |

| В | + | – | – | – | – |

| С | + | Автоматическое регулирование, управление |

|||

| D | Плотность | Разность, перепад | – | – | – |

| E | Электрическая величина (см. п. 2.13) п. 2.13) |

– | + | – | – |

| F | Расход | Соотношение, доля, дробь | – | – | – |

| G | Размер, положение, перемещение |

+ | |||

| H | Ручное воздействие |

Верхний предел измеряемой величины |

|||

| I | + | – | Показание | – | – |

| J | + | Автоматическое переключение, обегание |

|||

| К | Время, временная программа | – | – | + | – |

| L | Уровень | Нижний предел измеряемой величины |

|||

| M | Влажность | – | – | – | – |

| N | + | – | – | – | – |

| O | + | – | – | – | – |

| P | Давление, вакуум | – | – | – | – |

| Q | Величина, характеризующая качество: состав, концентрация и т. п. (см. п. 2.13) п. (см. п. 2.13) |

Интегрирование, суммирование по времени | + | ||

| R | Радиоактивность (см. п. 2.13) | – | Регистрация | – | – |

| S | Скорость, частота | Включение, отключение, переключение, блокировка |

|||

| T | Температура | – | – | + | – |

| U | Несколько разнородных измеряемых величин | ||||

| V | Вязкость | – | + | – | – |

| W | Масса | – | – | – | – |

| X | Нерекомендуемая резервная буква | – | – | – | – |

| Y | + | – | – | + | – |

| Z | + | – | – | + | – |

Примечание. Буквенные обозначения, отмеченные знаком «+», являются резервными, знаком «-» – не используются.

1.2.2. Дополнительные буквенные обозначения, применяемые для указания дополнительных функциональных признаков приборов, преобразователей сигналов и вычислительных устройств, приведены в приложении 1.

1.3. Размеры условных обозначений

1.3.1. Размеры условных графических обозначений приборов и средств автоматизации в схемах приведены в табл. 3.

1.3.2. Условные графические обозначения на схемах выполняют сплошной толстой основной линией, а горизонтальную разделительную черту внутри графического обозначения и линии связи – сплошной тонкой линией по ГОСТ 2.303.

1.3.3. Шрифт буквенных обозначений принимают по ГОСТ 2.304 равным 2,5 мм.

Таблица 3

С чего начать чтение схем?

Для того, чтобы научиться читать схемы, первым делом, мы должны изучить как выглядит тот или иной радиоэлемент в схеме. В принципе ничего сложного в этом нет. Вся соль в том, что если в русской азбуке 33 буквы, то для того, чтобы выучить обозначения радиоэлементов, придется неплохо постараться.

До сих пор весь мир не может договориться, как обозначать тот или иной радиоэлемент либо устройство. Поэтому, имейте это ввиду, когда будете собирать буржуйские схемы. В нашей статье мы будем рассматривать наш российский ГОСТ-вариант обозначения радиоэлементов

Принцип работы инвертора напряженияПредставим, что у нас имеется источник электрической энергии постоянного тока такой, как аккумулятор или гальванический элемент и потребитель (нагрузка), который работает только от переменного напряжения. Как преобразовать один вид энергии в другой? Решение было найдено довольно просто. Достаточно подключить аккумулятор к потребителю сначала одной полярностью, а затем через короткий промежуток отключить аккумулятор, а потом снова подключить, но уже обратной полярностью. И такие переключения повторять все время через равные промежутки времени. Если выполнять таких переключений 50 раз за секунду, то на потребитель будет подаваться переменное напряжение частотой 50 Гц. Роль переключателей чаще всего выполняют транзисторы или тиристоры, работающие в ключевом режиме.

Роль переключателей чаще всего выполняют транзисторы или тиристоры, работающие в ключевом режиме.

На схеме, приведенной ниже, изображен источника питания Uип с клеммами 1-2 и потребитель RнLн, обладающий активно-индуктивным характером, с клеммами 3-4. В один момент времени потребитель клеммами 3-4 подключается к клеммам 1-2 Uип, при этом I от Uип протекает в направлении LнRн, а в следующий момент клеммы 3-4 изменяют свое положение и I протекает в противоположном направлении относительно потребителя электрической энергии.

Виды и типы электрических схем

Прежде, чем говорить об условных обозначения на схемах, нужно разобраться, какие виды и типы схем бывают. С 01.07.2009 на территории РФ введен в действие ГОСТ 2.701-2008 «ЕСКД. Схемы. Виды и типы. Общие требования к выполнению».

В соответствии с этим ГОСТ, схемы разделяются на 10 видов:

- Схема электрическая

- Схема гидравлическая

- Схема пневматическая

- Схема газовая

- Схема кинематическая

- Схема вакуумная

- Схема оптическая

- Схема энергетическая

- Схема деления

- Схема комбинированная

Виды схем подразделяются на восемь типов:

- Схема структурная

- Схема функциональная

- Схема принципиальная (полная)

- Схема соединений (монтажная)

- Схема подключения

- Схема общая

- Схема расположения

- Схема объединенная

Меня, как электрика, интересуют схемы вида «Схема электрическая». Вообще, описание и требования к схемам приведены в ГОСТ 2.701-2008 на примере электрических схем, но с 01 января 2012 действует ГОСТ 2.702-2011 «ЕСКД. Правила выполнения электрических схем». Большей частью текст этого ГОСТ дублирует текст ГОСТ 2.701-2008, ссылается на него и другие ГОСТ.

ГОСТ 2.702-2011 подробно описывает требования к каждому виду электрической схемы. При выполнении электрических схем следует руководствоваться именно этим ГОСТ.

ГОСТ 2.702-2011 дает следующее определение понятия электрической схемы: «Схема электрическая — документ, содержащий в виде условных изображений или обозначений составные части изделия, действующие при помощи электрической энергии, и их взаимосвязи». Далее ГОСТ ссылается на документы, регламентирующие правила выполнения условных графических изображения, буквенных обозначений и обозначений проводов и контактных соединений электрических элементов. Рассмотрим каждый отдельно.

Искусство создания схем

Правильно составленных схем осталось совсем немного. Хорошую схему составлять трудно, долго. При создании схемы нельзя забывать, что схема необходима для человека, а не для простого описания какого-либо прибора, выходного двигателя. Многие схемы, созданные по ЕСКД, составлены неграмотно инженерами. Чтобы составить нормальную схему, необходимо изучить искусство для их составления. Когда схема создана на профессиональном уровне, то становится легко работать с ней и с устройством. Рекомендуется перерисовывать схему оборудования, с которым вы работаете или обслуживаете часто.

Когда схема создана на профессиональном уровне, то становится легко работать с ней и с устройством. Рекомендуется перерисовывать схему оборудования, с которым вы работаете или обслуживаете часто.

Главные принципы создания схем

- Схема создается для человека, обслуживающего устройство, а не для машины.

- Схема должна читаться и быть подробной, между ними должен быть баланс.

- Выделяют графическими способами важность необходимых участков и обратная суть устройства.

- При взгляде должно быть понятно, куда идет путь основных режимов и функций.

Графические обозначения в электрических схемах

В части графических обозначений в электрических схемах ГОСТ 2.702-2011 ссылается на три других ГОСТ:

- ГОСТ 2.709-89 «ЕСКД. Обозначения условные проводов и контактных соединений электрических элементов, оборудования и участков цепей в электрических схемах».

- ГОСТ 2.721-74 «ЕСКД. Обозначения условные графические в схемах. Обозначения общего применения»

- ГОСТ 2.

755-87 «ЕСКД. Обозначения условные графические в электрических схемах. Устройства коммутационные и контактные соединения».

755-87 «ЕСКД. Обозначения условные графические в электрических схемах. Устройства коммутационные и контактные соединения».

Условные графические обозначения (УГО) автоматов, рубильников, контакторов, тепловых реле и прочего коммутационного оборудования, которое используется в однолинейных схемах электрических щитов, определены в ГОСТ 2.755-87.

Однако, обозначение УЗО и дифавтоматов в ГОСТ отсутствует. Думаю, в скором времени он будет перевыпущен и обозначение УЗО будет добавлено. А пока, каждый проектировщик изображает УЗО по собственному вкусу, тем более, что ГОСТ 2.702-2011 это предусматривает. Достаточно привести обозначение УГО и его расшифровку в пояснениях к схеме.

Дополнительно к ГОСТ 2.755-87 для полноты схемы понадобится использование изображений из ГОСТ 2.721-74 (в основном для вторичных цепей).

Все обозначения коммутационных аппаратов построены на четырех базовых изображениях:

с использованием девяти функциональных признаков:

Основные условные графические обозначения, используемые в однолинейных схемах электрических щитов:

| Наименование | Изображение |

| Автоматический выключатель (автомат) | |

| Выключатель нагрузки (рубильник) | |

| Контакт контактора | |

| Тепловое реле | |

| УЗО | |

| Дифференциальный автомат | |

| Предохранитель | |

| Автоматический выключатель для защиты двигателя (автомат со встроенным тепловым реле) | |

| Выключатель нагрузки с предохранителем (рубильник с предохранителем) | |

| Трансформатор тока | |

| Трансформатор напряжения | |

| Счетчик электрической энергии | |

| Частотный преобразователь | |

| Замыкающий контакт нажимного кнопочного выключателя без самовозврата с размыканием и возвратом элемента управления автоматически | |

| Замыкающий контакт нажимного кнопочного выключателя без самовозврата с размыканием и возвратом элемента управления посредством вторичного нажатия кнопки | |

| Замыкающий контакт нажимного кнопочного выключателя без самовозврата с размыканием и возвратом элемента управления посредством вытягивания кнопки | |

| Замыкающий контакт нажимного кнопочного выключателя без самовозврата с размыканием и возвратом элемента управления посредством отдельного привода (например, нажатия кнопки-сброс) | |

| Контакт замыкающий с замедлением, действующим при срабатывании | |

| Контакт замыкающий с замедлением, действующим при возврате | |

| Контакт замыкающий с замедлением, действующим при срабатывании и возврате | |

| Контакт размыкающий с замедлением, действующим при срабатывании | |

| Контакт размыкающий с замедлением, действующим при возврате | |

| Контакт замыкающий с замедлением, действующим при срабатывании и возврате | |

| Катушка контактора, общее обозначение катушки реле | |

| Катушка импульсного реле | |

| Катушка фотореле | |

| Катушка реле времени | |

| Мотор-привод | |

| Лампа осветительная, световая индикация (лампочка) | |

| Нагревательный элемент | |

| Разъемное соединение (розетка): гнездо штырь |

|

| Разрядник | |

| Ограничитель перенапряжения (ОПН), варистор | |

| Разборное соединение (клемма) | |

| Амперметр | |

| Вольтметр | |

| Ваттметр | |

| Частотометр |

Обозначения проводов, шин в электрических щитах определяется ГОСТ 2. 721-74.

721-74.

Линии соединения

Каждый проводник имеет наименование. Если у проводов одно название, то их считают за один провод.

Графическое обозначение электроэнергетических объектов на схемах

|

Наименование |

Обозначение объекта |

||

|

существующего |

проектируемого |

намечаемого |

|

|

Электростанция. Общее обозначение |

|||

|

Электростанция тепловая ТЭС. Общее обозначение, ГРЭС |

|||

|

Электростанция тепловая с выдачей тепловой энергии потребителю ТЭЦ |

|||

|

Электростанция гидравлическая. Общее обозначение |

|||

|

Электростанция атомная |

|||

|

Подстанция. |

|||

|

Подстанция переменного тока 35 кВ |

|||

|

Подстанция переменного тока 110 кВ |

|||

|

Подстанция переменного тока 220 кВ |

|||

|

Подстанции переменного тока 500 кВ |

|||

|

Подстанции тяговые переменного тока |

|||

|

Подстанция тяговая постоянного тока |

|||

|

Линия электропередач. Общее обозначение |

|||

|

Линия электропередачи до 1 кВ |

|||

|

Линия электропередач свыше 1 кВ |

|||

|

Кабельная линия |

|||

|

Воздушная линия |

|||

|

Линия электропередач постоянного тока |

± 110 |

±110 |

±110 |

|

⇐ ПредыдущаяСтр 5 из 9Следующая ⇒ 22. Шифратор. Назначение, схема построения на логических элементах, принцип работы и таблица переключения. УГО. Применение. Шифратор — это узел, преобразующий унитарный код на входе в некоторый позиционный код на выходе. Если выходной код является двоичным, то шифратор называется двоичным. Рассмотрим принцип построения 8-входового двоичного шифратора. Закон функционирования такого шифратора можно задать таблицей истинности (таб.3.2)

На рис.38 приведена схема шифратора на восемь входов и его условное обозначение. Рис.38.Схема шифратора (а) и его УГО (б)

С помощью шифратора возможно преобразование цифр десятичных чисел в двоичное представление с использованием любого другого двоично-десятичного кода. 23. Дешифратор. Назначение, схема построения на логических элементах, принцип работы и таблица переключения. УГО. Применение. Дешифратор. Дешифратор — комбинационная схема, содержащая п входов и 2П выходов и преобразующая n-разрядное двоичное число в соответствующий управляющий сигнал, который возникает только на одном из его выходов. Дешифратор представляет собой совокупность схем совпадений, формирующих управляющий сигнал на одном из выходов, в то время как на остальных выходах сигналы отсутствуют. Выходы дешифратора имеют нумерацию, совпадающую с десятичным представлением двоичного числа. Число элементов одноступенчатого дешифратора определяется числом выходов. По способу организации дешифрации слова дешифраторы подразделяются на: 1. Одноступенчатые (линейные). 2. Многоступенчатые (прямоугольные, пирамидальные). Дешифратор, имеющий для n-разрядного числа 2П выходных шин, называется полным дешифратором. Дешифраторы используются для преобразования двоичных кодов в управляющие сигналы для различных устройств ЭВМ. Матричные или линейные дешифраторы. Линейный дешифратор является одноступенчатым, т.к. при его построении используют конъюнкторы, число входов которых равно разрядности входного слова. Прямые и инверсные значения переменных обычно поступают на входы дешифратора с прямых и инверсных выходов триггеров, регистра, на котором записывается входная комбинация переменных. Схема, представленная на рис.36, реализует следующие переключательные функции: Y0=X̅2X̅1X̅0 Y4=X2X̅1X̅0 Y1=X̅2X̅1X0 Y5=X2X̅1X0 Y2=X̅2X1X̅0 Y6=X2X1X̅0 Y3=X̅2X1X0 Y7=X2X1X0

В интегральном исполнении матричные дешифраторы строятся на 3-4 входа. На рис.36.37 приведены: функциональная схема матричного 3-х разрядного дешифратора, таблица возможных состояний дешифратора и его условное графическое обозначение. Возможно построение дешифратора, у которого дешифрация входного слова осуществляется синхронизирующими сигналами. Такие дешифраторы принято называть синхронными дешифраторами.

Рис.36. Функциональная схема (а) и таблица переключений (б) линейного дешифратора

24. Мультиплексор. Назначение, схема построения, на логических элементах, принцип работы и таблица переключения. УГО. Применение. Мультиплексором называется функциональный узел, обеспечивающий передачу информации, поступающей по нескольким входным линиям связи на одну выходную линию. Выбор той или иной входной линии Di; осуществляется в соответствии с поступающим адресным кодом A0, А1… . При наличии п адресных входов можно реализовать М = 2П комбинаций адресных сигналов А|, каждая из которых обеспечивает выбор одной из М входных линий.

Рассмотрим синтез 4-разрядного мультиплексора. Составим таблицу истинности: На основании таб.3.3 составим переключательную функцию для его выхода:

Рис.39.Функцианальная схема мультиплексора.

Рис.40.Условное графическое обозначение мультиплексора.

Функциональные схемы мультиплексоров достаточно просты, они выпускаются в виде интегральных микросхем с четырьмя двухвходовыми, двумя четырёхвходовыми и одним восьмивходовым мультиплексорами в одном корпусе. Для передачи на выход многоразрядных входных данных в параллельной форме используется параллельное включение мультиплексоров по числу разрядов передаваемых данных. Такое включение мультиплексоров называется мультиплексорным деревом(рис.41). Например, чтобы передать на выход седьмой разряд следует подать на MS2 XiXq = 11 и на MS5 Х3Х2 = 01 25. Демультиплексор. Назначение, схема построения на логических элементах, принцип работы и таблица переключения. УГО. Применение. Демультиплексором называется функциональный узел, обеспечивающий передачу информации в одну из выходных линий в соответствии с принятым адресом. При этом на остальных выходных линиях поддерживается логический «О». То., демультиплексоры используются для восстановления мультиплексированной информации. Демультиплексор имеет один информационный вход и несколько выходов. В этом случае вход подключается к выходу, имеющему заданный адрес.

Используя таб. 3.4 можно легко записать переключательные функции для выходов приведённой на рис.42 схемы демультиплексора:

Рис.43.УГО демультиплексора При D = 1 демультиплексор выполняет функции полного дешифратора, реализуя на на выходах минтермы адресных переменных А0,…,Аn-1.

Рис.44.Пример коммутирующей схемы.

Рис.45.Функциональная схема 16-ти разрядного демультиплексорного дерева.

⇐ Предыдущая123456789Следующая ⇒ |

Карта сайта — АО «ГРУППА КРЕМНИЙ ЭЛ»

Контакты

Версия для слабовидящих

Войти/Регистрация

- Главная

|

|

| jpg»> |

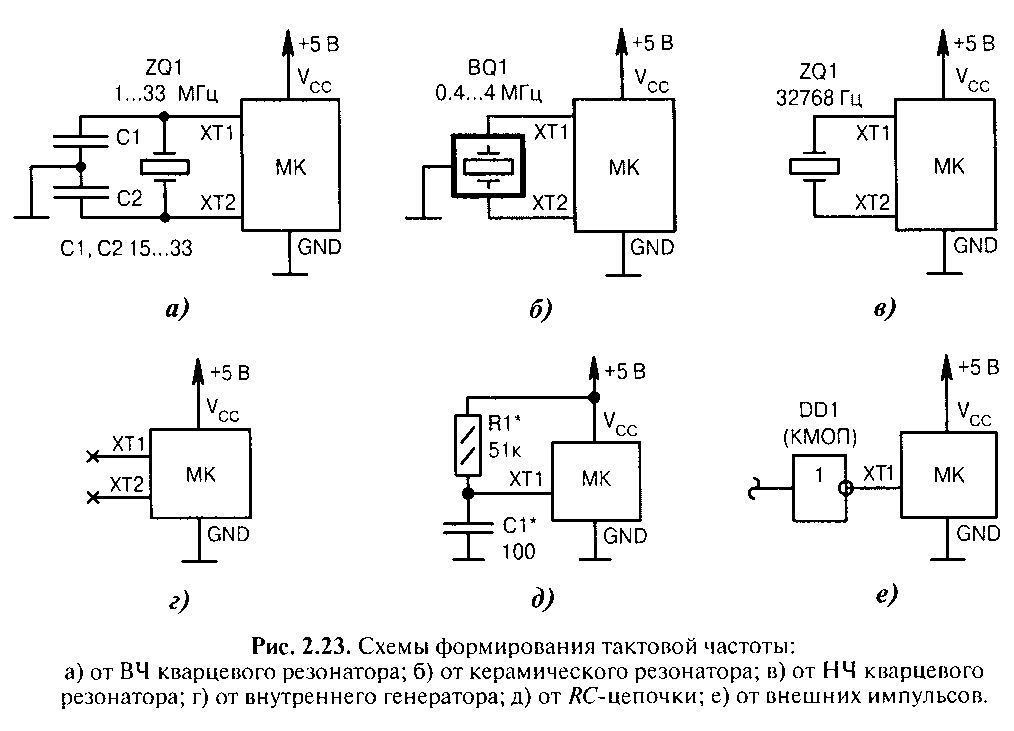

КР580ГФ24 — микросхема генератора тактовых сигналов, используемого для синхронизации работы микропроцессора KP580BM80A.

Таблица 1

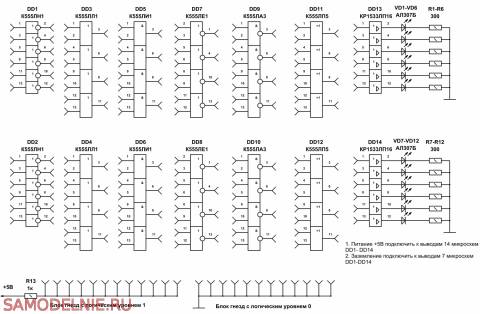

Генератор тактовых сигналов состоит из генератора опорной частоты, счетчика-делителя на 9, формирователя фаз С1 и С2 и логических схем. Для стабилизации тактовых сигналов опорной частоты ко входам XTA1L1 и ХТА1L2 генератора подключается кварцевый резонатор, частота которого должна быть в 9 раз больше частоты выходных сигналов С1 и С2. В радиолюбительской практике чаще всего используются кварцевые резонаторы 15 — 20 МГц. KP580BК38 (прежнее обозначение КР580ИК38) — микросхема системного контроллера и буферного регистра данных. Используется в компьютерах и микропроцессорных системах, собранных на базе микропроцессора KP580BM80A как формирователь управляющих сигналов и как буферный регистр данных. Условное графическое изображение микросхемы и ее структурная схема показаны на рисунках 3 и 4. Назначение выводов — в таблице 2.

Таблица 2

Системный контроллер формирует управляющие сигналы по сигналам состояния микропроцессора при обращении: к запоминающим устройствам RD и WR, при обращении к устройствам ввода/вывода RD10 и WR10, INTA, а также обеспечивает прием и передачу 8-разрядной информации между каналами данных микропроцессора (выводы D7 — D0) и системным каналом по выводам DB7 — DB0. КР580ИР82 — микросхема 8-разрядного адресного регистра, предназначенная для связи микропроцессора с системной шиной; обладает повышенной нагрузочной способностью. Микросхема КР580ИР82 — восьмиразрядный D-регистр с «защелкой» без инверсии и с тремя состояниями на выходе. Условное графическое обозначение и ее структурная схема приведены на рисунках 5 и 6. Назначение выводов — в таблице 3.

Таблица 3

Микросхема состоит из восьми одинаковых функциональных блоков и схемы управления. Микросхема КР580ВВ55А (старое обозначение К580ИК55А) — программируемое устройство ввода/вывода параллельной информации. Применяется в микропроцессорной технике в качестве элемента ввода/вывода общего назначения для подключения интерфейсных устройств (клавиатуры, принтера, накопителя на магнитной ленте и т. д.) к магистралям данных. Условное графическое изображение микросхемы показано на рисунке 7, а ее структурная схема — на рисунке 8. Данные о назначении выводов вы найдете в таблице 4.

Таблица 4

Обмен информацией между магистралью данных системы и микросхемой KР580BB55A осуществляется через 8-разрядный двунаправленный канал данных (D). Таблица 5

Режим работы каждого из каналов ВА, ВВ и ВС определяется содержимым регистра управляющего слова (РУС). Записав в него управляющее слово, микросхему можно перевести в один из трех режимов работы: режим 0 — простой ввод/вывод, режим 1 — стробируемый ввод/вывод, режим 2- двунаправленный канал.

Микросхема К589ИР12 — многорежимный восьмиразрядный универсальный буферный регистр.

Таблица 6

Микросхема состоит из восьми информационных триггеров, восьми выходных буферных устройств с тремя устойчивыми состояниями, отдельного D-триггера для формирования запроса на прерывания и гибкой схемы управления режимами работы регистра. Управляющие выводы микросхемы — CS1, CS2, MD и EW. Эти входы используются для управления выборкой устройств, информацией регистра, состоянием выходных буферных каскадов и триггером запроса на прерывание. Микросхемы К589АП16 и К589АП26 — двунаправленные шинные формирователи, своего рода усилители цифровых сигналов. Отличаются они тем, что, проходя через микросхему К589АП16, сигнал остается неизменным, а через К589АП26 — инвертируется. Используются эти микросхемы для управления шинами (магистралями) в цифровой и микропроцессорной технике. Обе микросхемы представляют собой 4-канальные коммутаторы, имеющие в каждом канале одну шину только для приема информации и одну двунаправленную шину для приема и выдачи информации.

Таблица 7

Для управления режимами работы и направлением выдачи информации используется специальная схема на двух элементах 2И. Таблица 8 |

Патент США на способ и устройство для проверки технологии изготовления микросхем. Патент (Патент № 5,121,335, выдан 9 июня 1992 г.)

ПРЕДПОСЫЛКИ ИЗОБРЕТЕНИЯ

электронные микросхемы и, более конкретно, к способу и устройству для проверки правильности выполнения процедуры изготовления микросхемы.

2. Описание предшествующего уровня техники

Способ защиты аппаратных интегральных схем или микросхем от несанкционированного копирования и/или использования описан в патенте США No. № 4766516, озаглавленный «Способ и устройство для защиты интегральных схем от несанкционированного копирования и использования», выданный 23 августа 1988 г. Ф. Оздемиру и др. и переданный компании Hughes Aircraft Company, правопреемнику настоящего изобретения. Согласно этому методу, по крайней мере один дополнительный элемент схемы, который не способствует функционированию интегральной схемы (ИС), а, скорее, препятствует правильному функционированию ИС в случае попытки копирования, анализа или другого несанкционированного использования. изготавливается вместе с общей ИС. Идентичность дополнительных элементов схемы маскируется за счет того, что они формируют видимый вид кажущихся элементов, но с физическими модификациями, которые не сразу видны переписчику, но заставляют их функционировать по-другому. Такие модификации включают в себя очень узкие разрывы разомкнутой цепи в металлизированных соединительных линиях, предпочтительно выполненные с помощью сфокусированного ионного луча (FIB) или лазерного луча; разупорядочение структуры решетки или изменение уровня легирования полупроводниковой области, предпочтительно с помощью FIB; и введение электрического заряда в полупроводниковую область, предпочтительно с помощью электронного луча.

Такие модификации включают в себя очень узкие разрывы разомкнутой цепи в металлизированных соединительных линиях, предпочтительно выполненные с помощью сфокусированного ионного луча (FIB) или лазерного луча; разупорядочение структуры решетки или изменение уровня легирования полупроводниковой области, предпочтительно с помощью FIB; и введение электрического заряда в полупроводниковую область, предпочтительно с помощью электронного луча.

FIB и другие типы модификаций практически невозможно обнаружить, что желательно для предотвращения несанкционированного копирования и/или использования. Однако необнаруживаемость модификаций также затрудняет определение того, правильно ли была выполнена процедура модификации. Неисправность в аппаратуре или управляющем программном обеспечении, а также несанкционированное изменение или использование могут сделать модификации или саму схему неработоспособной или отличаться от того, что было задумано.

В дополнение к приложениям безопасности, FIB, например, используются в самых разных процессах изготовления микросхем, пример представлен в статье, озаглавленной «Литографический подход для изготовления 100 нм с помощью сфокусированного ионного луча», С. Мацуи и др. al, Journal of Vacuum Science Technology, B4(4), стр. 845-849 (июль/август 1986 г.). Ошибочное выполнение процедуры обработки FIB приведет к созданию дефектных микросхем, при этом источник ошибки будет трудно определить из-за относительной необнаруживаемости модификаций FIB.

Мацуи и др. al, Journal of Vacuum Science Technology, B4(4), стр. 845-849 (июль/август 1986 г.). Ошибочное выполнение процедуры обработки FIB приведет к созданию дефектных микросхем, при этом источник ошибки будет трудно определить из-за относительной необнаруживаемости модификаций FIB.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Настоящее изобретение обеспечивает способ и устройство для выполнения и проверки процедуры изготовления микросхемы или интегральной схемы, что особенно ценно, когда процедура включает в себя внесение модификаций в микросхему, которые относительно незаметны. , включая модификации с использованием FIB, лазерного луча или электронного луча, как описано в упомянутом выше патенте Ozdemir et al. Однако изобретение широко применимо к любой процедуре изготовления микросхем, где требуется проверка надлежащего выполнения процедуры, а управляющие или выходные сигналы от устройства, выполняющего процедуру, могут быть перехвачены и использованы для создания записи процедуры. В дополнение к обеспечению защиты от несанкционированного вмешательства изобретение обеспечивает эффективный способ контроля качества, который ценен сам по себе в приложениях, где защита от вмешательства не требуется.

В дополнение к обеспечению защиты от несанкционированного вмешательства изобретение обеспечивает эффективный способ контроля качества, который ценен сам по себе в приложениях, где защита от вмешательства не требуется.

Более конкретно, устройство используется для выполнения процедуры изготовления микросхемы под контролем данных спецификации. В предпочтительном варианте осуществления изобретения процедура включает выполнение относительно незаметных модификаций микросхемы с использованием сфокусированного ионного пучка или других средств для предотвращения несанкционированного анализа, воспроизведения и/или использования микросхемы. Выход устройства прослушивается для создания записи данных о сигналах, фактически применяемых для управления сфокусированным ионным пучком или другими устройствами для выполнения процедуры. Данные записи записываются по крайней мере в одну область хранения данных проверки микросхемы, желательно с использованием одних и тех же устройств. При тестировании микросхемы данные, записанные в область памяти, считываются и сравниваются с данными спецификации и сгенерированными данными записи. Корректность выполнения процедуры проверяется, если сравниваемые данные соответствуют друг другу.

Корректность выполнения процедуры проверяется, если сравниваемые данные соответствуют друг другу.

Эти и другие особенности и преимущества настоящего изобретения будут очевидны специалистам в данной области техники из следующего подробного описания вместе с прилагаемыми чертежами, на которых одинаковые ссылочные позиции относятся к одинаковым частям.

ОПИСАНИЕ ЧЕРТЕЖЕЙ

РИС. 1а представляет собой блок-схему, иллюстрирующую устройство для выполнения и проверки процедуры изготовления микросхемы в соответствии с настоящим изобретением;

РИС. 1b иллюстрирует устройство по фиг. 1а после уничтожения его области хранения данных проверки;

РИС. 2 аналогичен фиг. 1а, но иллюстрирует второй вариант осуществления изобретения;

РИС. 3 также аналогичен фиг. 1а, но иллюстрирует третий вариант осуществления изобретения;

РИС. 4-7 — схемы, иллюстрирующие альтернативные варианты расположения областей хранения данных проверки на микросхемах в соответствии с изобретением; и

РИС. 8 представляет собой электрическую принципиальную схему, иллюстрирующую примерную единичную ячейку области хранения данных проверки.

8 представляет собой электрическую принципиальную схему, иллюстрирующую примерную единичную ячейку области хранения данных проверки.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Обращаясь теперь к фиг. 1а чертежа устройство для выполнения и проверки процедуры изготовления микросхемы в целом обозначено как 10 и включает в себя блок спецификации 12. Хотя это не показано подробно, блок 12 обычно хранит данные спецификации в форме машиночитаемых данных, которые определяют процедура, выполняемая на микросхеме, и компьютер для запуска программного обеспечения. Данные спецификации, как правило, должны быть на языке высокого уровня, в котором этапы процедуры указаны в удобной для пользователя форме.

Данные спецификации обозначены как D1 и подаются из блока 12 спецификации в блок 14 преобразования, который преобразует или переводит данные спецификации D1 высокого уровня в данные управления D4 низкого уровня в виде числовых кодов. В одном варианте осуществления изобретения блок 14 преобразования реализован в виде программного обеспечения. В другом варианте осуществления изобретения блок 14 преобразования реализован в виде аппаратных средств. Данные управления подаются на блок 16 управления, который подключен для управления работой устройства 18 для выполнения требуемой процедуры на микросхеме. В предпочтительном варианте осуществления изобретения устройство 18 сконструировано для генерирования сфокусированного электронного луча (FIB), лазерного луча, электронного луча и/или других средств для выполнения процедуры относительно необнаруживаемой модификации схемы (RUCM), такой как описанная в патент Ozdemir et al. под контролем спецификации/контрольных данных D1, D4. Однако изобретение не ограничено этим, и устройство в другом варианте осуществления изобретения сконструировано для выполнения любой другой процедуры изготовления микросхемы, которая способна генерировать запись фактически выполненных этапов процесса, таких как фотолитография, осаждение эпитаксиального слоя. и т. д.

В другом варианте осуществления изобретения блок 14 преобразования реализован в виде аппаратных средств. Данные управления подаются на блок 16 управления, который подключен для управления работой устройства 18 для выполнения требуемой процедуры на микросхеме. В предпочтительном варианте осуществления изобретения устройство 18 сконструировано для генерирования сфокусированного электронного луча (FIB), лазерного луча, электронного луча и/или других средств для выполнения процедуры относительно необнаруживаемой модификации схемы (RUCM), такой как описанная в патент Ozdemir et al. под контролем спецификации/контрольных данных D1, D4. Однако изобретение не ограничено этим, и устройство в другом варианте осуществления изобретения сконструировано для выполнения любой другой процедуры изготовления микросхемы, которая способна генерировать запись фактически выполненных этапов процесса, таких как фотолитография, осаждение эпитаксиального слоя. и т. д.

В предпочтительном варианте осуществления изобретения, в котором аппарат 18 выполнен в виде устройства ФИП, управляющие данные D4 включают числовые коды, обозначающие перемещение ФИП к заданному набору прямоугольных координат, выбор типа имплантируемого иона, выполнять облучение микросхемы по заданным координатам в течение заданного промежутка времени при заданном уровне энергии и дозировке и т. д. Следует отметить, что объем изобретения дополнительно включает предоставление данных спецификации в низкоуровневом формате управления D4, в в этом случае блок 14 преобразования не требуется.