Что такое логисторная логика. Как она отличается от традиционной КМОП-логики. Какие преимущества может дать использование логисторов. Как реализуются базовые логические операции на логисторах. Каковы перспективы применения логисторной логики в процессорах.

Что такое логисторная логика и чем она отличается от КМОП

Логисторная логика — это новый подход к построению логических схем и процессоров, разрабатываемый группой российских ученых. Ключевые особенности логисторной логики:

- Использование нового типа транзисторов — логисторов

- Параллельно-последовательное выполнение операций вместо строго последовательного

- Применение нестандартного метода кодирования логических нулей и единиц

- Использование двуполярного питания

- Размещение затворов в виде сетки в вертикальной и горизонтальной плоскостях

В отличие от КМОП-логики, где операции выполняются строго последовательно, в логисторной логике возможно параллельное выполнение операций на уровне логических элементов. Это потенциально позволяет значительно увеличить производительность процессоров.

Устройство и принцип работы логистора

Логистор — это новый тип транзистора, специально разработанный для логисторной логики. Его ключевые особенности:

- Четыре вывода: исток (Source), сток (Drain), затвор (Gate) и база (Base)

- Выходной сигнал между истоком и стоком «изолирован» от управляющего сигнала между затвором и базой

- Канал проводимости между истоком и стоком формируется при подаче положительного напряжения на затвор и отрицательного на базу

Благодаря такой конструкции логисторы могут использоваться не только как переключающие элементы, но и как оптроны, обеспечивая гальваническую развязку в схемах.

Преимущества логисторной логики

Использование логисторной логики потенциально позволяет получить следующие преимущества по сравнению с традиционной КМОП-логикой:

- Увеличение быстродействия за счет параллельного выполнения операций

- Снижение энергопотребления процессоров

- Увеличение плотности размещения транзисторов на кристалле

- Возможность создания более сложных логических элементов

При этом для производства логисторных микросхем может использоваться существующий техпроцесс с минимальными изменениями.

Реализация базовых логических операций

В логисторной логике используется нестандартный метод кодирования логических нулей и единиц. Каждый бит передается по двум проводникам:

- Логический 0: +V на первом проводе, -V на втором

- Логическая 1: -V на первом проводе, +V на втором

Базовые логические операции реализуются путем создания или разрыва пути тока между входами и выходом. Например, операция И выполняется так:

- Входы A и B подаются на затворы двух последовательно соединенных логисторов

- Выход формируется на стоке второго логистора

- Высокий уровень на выходе будет только если оба входа имеют высокий уровень

Аналогичным образом реализуются и другие логические операции. При этом в логисторной логике возможно создание более сложных многовходовых элементов.

Перспективы применения в процессорах

Логисторная логика находится пока на стадии исследований и разработки. Однако она имеет большой потенциал для применения в процессорах следующих поколений. Ключевые преимущества, которые может дать ее использование:

- Увеличение тактовой частоты процессоров за счет параллельного выполнения операций

- Снижение энергопотребления и тепловыделения

- Увеличение количества транзисторов на кристалле без уменьшения техпроцесса

- Возможность создания процессоров с принципиально новой архитектурой

Для практического применения логисторной логики потребуется решить ряд технологических задач, в частности, отработать технологию массового производства логисторов. Однако потенциальные преимущества делают это направление весьма перспективным для дальнейших исследований и разработок.

Текущее состояние разработок

На данный момент логисторная логика находится на ранней стадии исследований. Ключевые достижения:

- Разработана теоретическая база и основные принципы

- Проведено компьютерное моделирование работы логисторов

- Создан прототип логического элемента на дискретных компонентах

- Получены первые экспериментальные образцы логисторов

Дальнейшие работы направлены на создание интегральных схем на основе логисторов и отработку технологии их массового производства. Это позволит перейти к практическому применению логисторной логики в процессорах.

Потенциальные области применения

Помимо создания высокопроизводительных процессоров, логисторная логика может найти применение и в других областях:

- Сверхбыстрые АЦП и ЦАП

- Высокочастотные усилители

- Системы машинного зрения

- Нейроморфные вычислительные устройства

- Квантовые компьютеры

Уникальные свойства логисторов позволяют создавать принципиально новые электронные устройства с улучшенными характеристиками. Это открывает широкие перспективы для развития различных областей электроники и вычислительной техники.

Логисторная логика / Хабр

Логисторная логика это набор концепций, применение которых может позволить ускорить вычисления, сократить затраты энергии на вычисления и увеличить плотность транзисторов на кристалле без существенного изменения техпроцесса. Она находится в разработке и статья ниже является лишь первичным результатом. Мы надеемся что она вызовет интерес в научных кругах и среди энтузиастов и разработка будет продолжена.

Логисторная логика предполагает:

Параллельно — последовательное , а не последовательное как в CMOS, выполнение операций на уровне логических элементов (альтернатива CMOS)

Не стандартный метод кодирования 0 и 1

Использование Логисторов (тип транзисторов)

Использование двуполярного питания

Использование «grid array» расположения гейтов (вертикально и горизонтально на виде сверху)

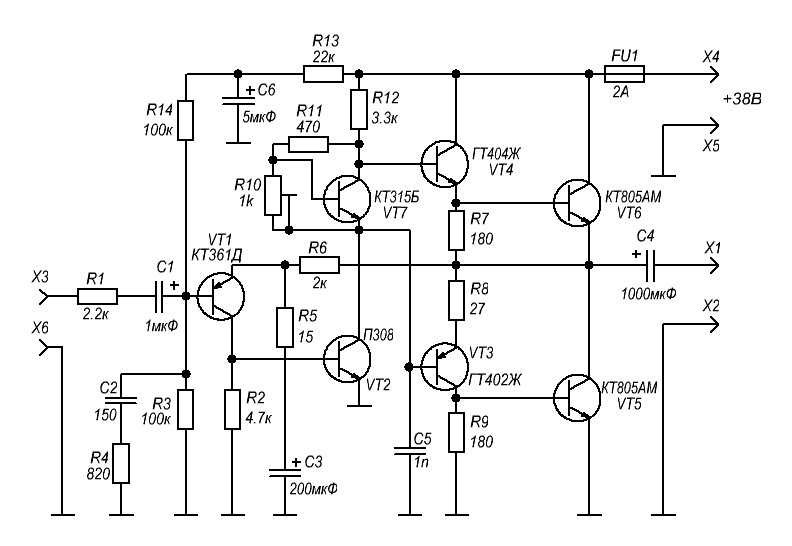

В процессорах математические операции описываются логическими схемами, которые представлены последовательным подключением CMOS транзисторных сборок.

Время выполнения этих операций определяется суммой времен выполнения каждой из последовательно подключенных транзисторных CMOS сборок

Чтобы продемонстрировать задержки, возникающие при последовательном подключении CMOS сборок представим симуляцию, выполненную в LTSpice на основе реальных spice моделей 10нм FinFET:

На графике ниже виден исходный сигнал (зеленый) и задержки, возникающие после двух (синий) и после 4-х инверторов (красный)

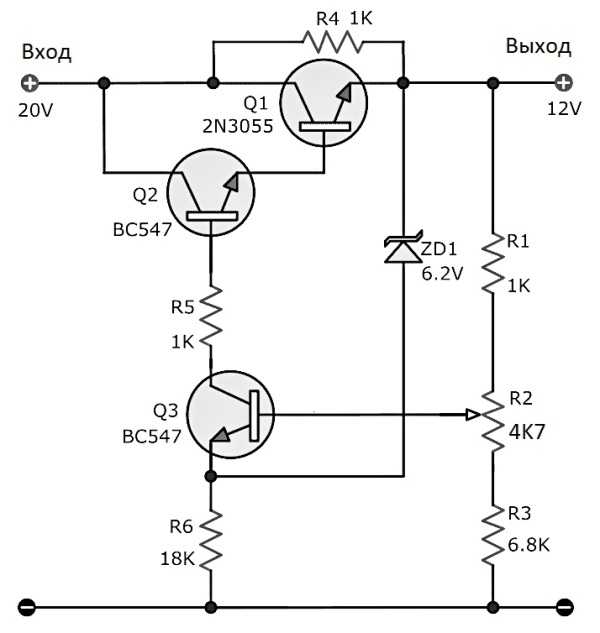

Предлагается новый тип транзистора — логистор:

В логисторе выходной сигнал (между Source и Drain) «изолирован» от управляющего сигнала — между Gate и Base, соответственно логисторы могут также использоваться вместо оптронов

В comsol semiconductor была произведена симуляция логистора, которая показала возникновение канала между Source и Drain при подаче положительного напряжения на Gate и отрицательного на Base. Ниже показан канал при отсутствии и наличии напряжения между Source и Drain:

Расчетная Вольт-Амперная характеристика логистора:

Благодаря двуполярному питанию, которое будет описано ниже, не требуется обеспечивать полное «запирание» логистора при закороченных Gate и Base, благодаря чему возможен подбор профиля допинга при котором логистор «качественнее» запирается и позволяет пропускать втрое большие токи чем NMOS при прочих равных.

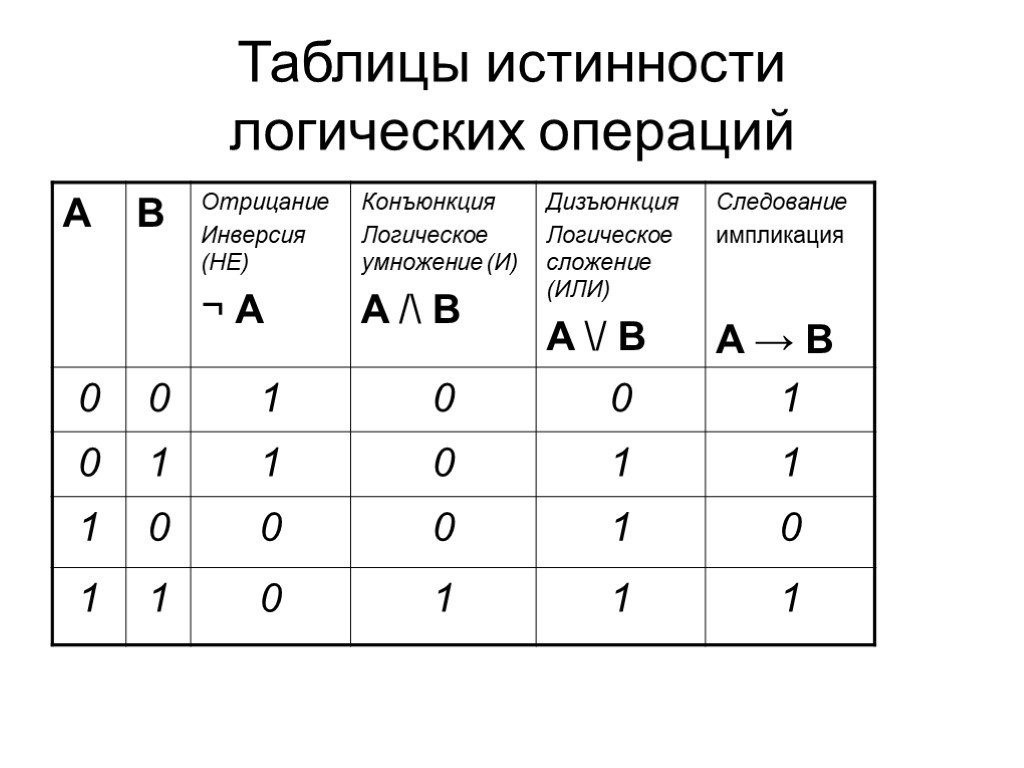

Входные значения в ALU, построенном на базе логисторной логики должны иметь ниже описанный метод кодирования 0 и 1:

Где выходное значение — это напряжение между выходами и землей. Как видно, каждый бит передается по двум проводам.

Единичные логические операции в логисторной логике принципиально описываются следующим образом:

Где «результат» — наличие (1) или отсутствие (0) пути

В логисторной логике логические цепи отличны от CMOS, TTL и других технологий. В случае отсутствия ограничения степени параллельности (в «полной» логисторной логике) цепи строятся таким образом, чтобы при выполнении операции не возникало «to Gate» операций. Другими словами в ALU запрещена подача сигнала с Drain на Gate.

В результате операции выполняются параллельно а не последовательно как у CMOS

Пример построения «полной» логисторной схемы для сумматора двух 4-х битных чисел

A1, A2, A3, A4; B1, B2, B3, B4 — биты первого и второго числа; outputs — результат

Инвертированные входы представлены как проводящие ключи, не инвертированные — не проводящие

В логисторной логике формат выхода не регламентирован и может не совпадать с форматом входа, поэтому правая часть (комплиментарная) не обязательна и приведена для понимания метода составления комплиментарных схем.

В полной логисторной логике каждый выход должен иметь независимую логическую схему.

Ниже представлена симуляция в Logisim без комплиментарной части. справа сверху — стандартная схема сумматора; справа снизу — схема необходимая для построения полных логисторных схем

Далее представлена симуляция логисторного сумматора двух 3-х битных чисел в falstad:

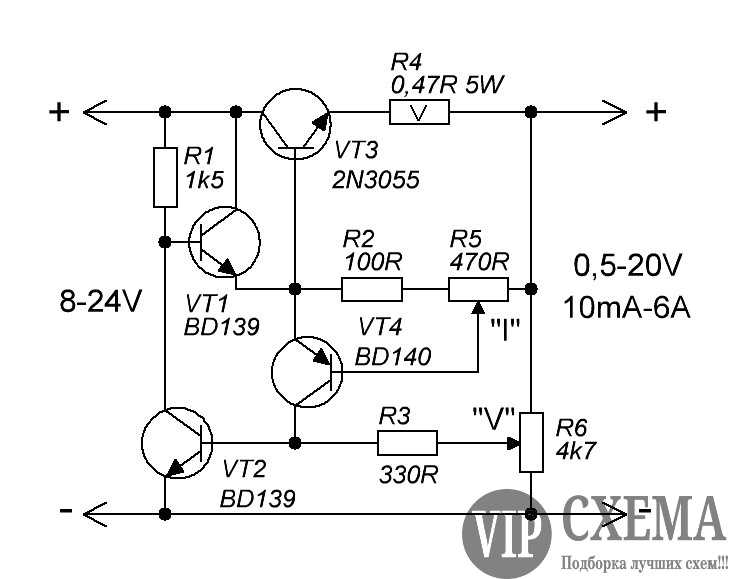

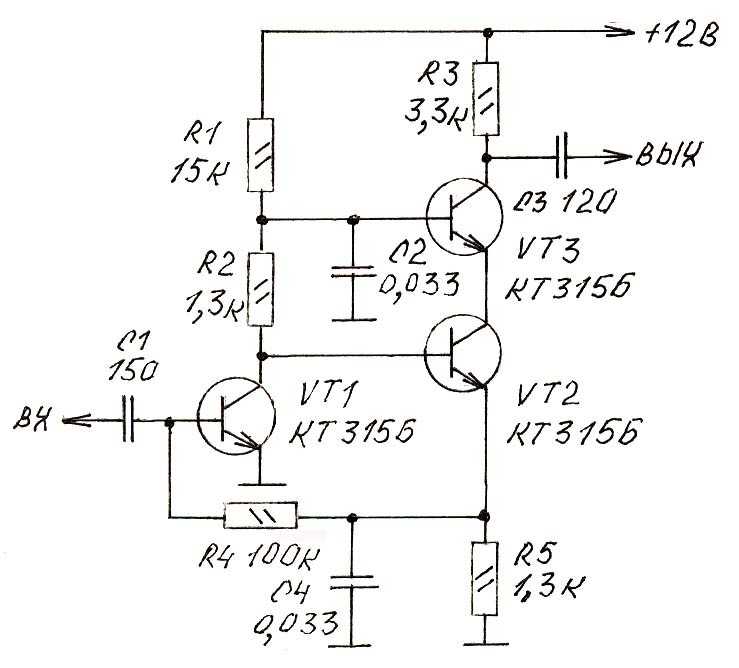

Для подтверждения работоспособности логической части логисторной логики была запроектирована в EasyEDA и изготовлена на JLCPcb плата:

Виду того что логисторы не существуют, были использованы оптроны. Плата работает и выдает ожидаемые значения, что неопровержимо доказывает верность логической части логисторной логики.

Для достижения высокой плотности размещения логисторов рекомендуется объединить Base всех логисторов и разместить Base на обратной стороне Substrate. Gates рекомендуется располагать горизонтально и вертикально. Source и Drain соседних Логисторов необходимо объединять, так что к одному Source / Drain будут присоединяться 4 Gate

Стоит обратить особое внимание на то что в статье описана логисторная логика без ограничения степени параллельности (полная), где степень параллельности — примерное количество Gates которое может запитываться с одного Drain. Для увеличения производительности обязательно использование ограничения степени параллельности. При этом исчезает требование — использовать независимую схему для каждого выходного бита. Использование каскадирования перед логисторной логикой для увеличения токов для насыщения большого количества Gates — является очевидным, но наихудшим решением

Для увеличения производительности обязательно использование ограничения степени параллельности. При этом исчезает требование — использовать независимую схему для каждого выходного бита. Использование каскадирования перед логисторной логикой для увеличения токов для насыщения большого количества Gates — является очевидным, но наихудшим решением

По техническим причинам коллектив далее не может продолжать работу над проектом и описать оптимальное решение внедрения ограничения степени параллельности, а также не обладает ресурсами для реализации чипа на базе логисторной логики, поэтому материал передается в доработку научному сообществу и энтузиастам

Разработано в ЛНМО; Авторы: Артем Родичкин, Анна Евсеева, Полина Маслова, Семен Архипов, Инна Миронова, Чечулин Михаил

Транзисторная логическая схема — Большая Энциклопедия Нефти и Газа, статья, страница 2

Cтраница 2

Принципы построении статических ИМС на МДП-транзисторах р-типа во многом соответствуют принципам построения транзисторных логических схем с непосредственными связями. Так, для построения многовходовой схемы ИЛИ — НЕ к одному нагрузочному МДП-транзистору подключают стоком т логических транзисторов, истоки которых заземляют.

[16]

Так, для построения многовходовой схемы ИЛИ — НЕ к одному нагрузочному МДП-транзистору подключают стоком т логических транзисторов, истоки которых заземляют.

[16]

| Схемы инверторов на МДП транзисторах. бозначения МДП-транзисторов — и ц типов. б — — инвертор на. [17] |

Принципы построения статических ИМС на МДП-транзисторах р-типа во многом соответствуют принципам построения транзисторных логических схем с непосредственными связями. [18]

| Схемы базовых логических элементов на МДП-транзисторах р-типа. [19] |

Основные принципы построения статических микросхем на МДП-транзисторах р-типа во многом соответствуют принципам построения транзисторных логических схем с непосредственными связями. Так, для построения многовходной схемы ИЛИ-НЕ к одному нагрузочному МДП-травзиетору подключаются стоком m логических транзисторов, истоки которых заземляются.

Построение логических схем в виде ИС с инжекционным питанием производится по методике, аналогичной транзисторным логическим схемам с непосредственными связями. Одна из схем 3 ИЛИ-НЕ, нагруженная на четыре выходных каскада, приведена на рис. 3 — 66, а. Генераторы тока / г учитывают ток инжекции эмиттера при обратных ( или нулевых) смещениях переходов эмиттер — база. [21]

Инвертор относится к основным элементам транзисторной логики ( а следовательно, и цифровых управляющих систем), так как можно строить транзисторные логические схемы, состоящие из одних инверторов. Поэтому инвертор подробно анализируется в гл. [22]

Транзисторные логические схемы с непосредственными связями — схемы, в которых отсутствуют компоненты цепей связи и связь между элементами осуществляется непосредственно проводниками. Такие транзисторные логические схемы имеют в качестве компонентов только транзисторы и сопротивления коллекторных нагрузок.

| Схема И-НЕ на базе транзисторно-транзисторной логики ( ТТЛ. [24] |

Их называют логическими схемами или логикой. На рис. 24 показаны транзисторные логические схемы с непосредственными связями. По упомянутым выше причинам такие схемы уже не применяют. [25]

Пульверса представляет собой краткий справочник для проектировщиков электронного оборудования, в котором используются транзисторные переключательные схемы. Разумеется, авторы включили в свой справочник не весь материал, относящийся к [26]

[26]

| Логические элементы ИС на КМДП-транзисторах ( а и инжекционной логике. [27] |

Эти транзисторы подают инжекторный ток в базу п-р-п-транзисторов VT3 и VT4, поэтому такие схемы называются инжекторными. Области базы и коллектора соответственно р-я-р-транзисторов являются также областями эмиттера и базы и-р-и-транзисторов, поэтому эти элементы называют совмещенными транзисторными логическими схемами. [28]

| Логические элементы ИС на КМДП-транзисторах ( а и инжекционной логике. [29] |

Эти транзисторы подают инжекторный ток в базу п-р — п — транзисторов VT3 и VT4, поэтому такие схемы называются инжекторными. Области базы и коллектора соответственно р-л-р-транзисторов являются также областями эмиттера и базы п-р — п — транзисторов, поэтому эти элементы называют совмещенными транзисторными логическими схемами. [30]

[30]

Страницы: 1 2 3

Проектирование вентиля И с использованием транзисторов

Как многие из нас знают, интегральная схема или ИС представляет собой комбинацию множества небольших схем в небольшом корпусе, которые вместе выполняют общую задачу. Подобно операционному усилителю или таймеру 555, микросхема состоит из множества транзисторов, триггеров, логических вентилей и других комбинационных цифровых схем. Точно так же триггер может быть построен с использованием комбинации логических элементов, а сами логические элементы могут быть построены с использованием нескольких транзисторов.

Логические элементы являются основой многих цифровых электронных схем. От базовых триггеров до микроконтроллеров Логические элементы формируют основной принцип хранения и обработки битов. Они устанавливают связь между каждым входом и выходом системы, используя арметическую логику. Существует множество различных типов логических вентилей, и каждый из них имеет разную логику, которая используется для разных целей. Но в этой статье основное внимание будет уделено И Воротам , потому что позже нам будет построение вентиля И с использованием схемы BJT-транзистора . Увлекательно, верно? Давайте начнем.

Но в этой статье основное внимание будет уделено И Воротам , потому что позже нам будет построение вентиля И с использованием схемы BJT-транзистора . Увлекательно, верно? Давайте начнем.

Логический элемент И

Логический элемент И представляет собой D-образный логический элемент с двумя входами и одним единственным выходом, где D-форма между входом и выходом представляет собой логическую схему. Соотношение между входными и выходными значениями можно объяснить с помощью таблицы истинности вентиля И , показанной ниже.

Вывод уравнений можно легко объяснить с помощью И Логическое уравнение вентиля , которое равно Q = A x B или Q = AB . Следовательно, для логического элемента И выход равен HIGH только тогда, когда оба входа равны HIGH .

Транзистор

Транзистор — это полупроводниковый прибор с тремя выводами, который можно подключить к внешней цепи. Устройство можно использовать как переключатель, а также как усилитель для изменения значений или управления прохождением электрического сигнала.

Устройство можно использовать как переключатель, а также как усилитель для изменения значений или управления прохождением электрического сигнала.

Для построения логического элемента И с использованием транзистора мы будем использовать транзисторы BJT, которые можно разделить на два типа: PNP и NPN – Транзисторы с биполярным переходом . Символ схемы для каждого из них можно увидеть ниже.

Эта статья объяснит вам, как построить схему затвора И с использованием транзистора. Логика логического элемента И уже объяснена выше, и для построения логического элемента И с использованием транзистора мы будем следовать той же таблице истинности, показанной выше.

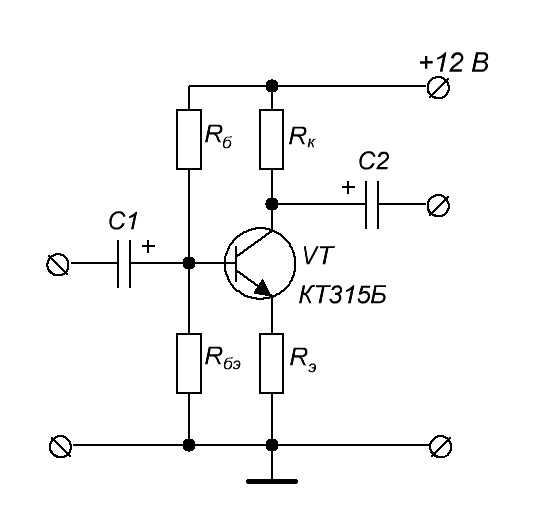

Принципиальная схема и необходимые компоненты

Список компонентов, необходимых для построения логического элемента И с использованием NPN-транзистора

- Два NPN-транзистора.

(Вы также можете использовать транзистор PNP, если он доступен)

(Вы также можете использовать транзистор PNP, если он доступен) - Два резистора 10 кОм и один резистор 4-5 кОм.

- Один светодиод (светоизлучающий диод) для проверки выхода.

- Макет.

- Источник питания +5 В.

- Две кнопки PUSH.

- Соединительные провода.

Схема представляет как входы A и B для вентиля И, так и выход, Q, который также имеет питание +5 В на коллектор первого транзистора, который последовательно соединен со вторым транзистором, а светодиод подключен к эмиттеру. вывод второго транзистора. Входы A и B подключены к базовой клемме транзистора 1 и транзистора 2 соответственно, а выход Q подключается к светодиоду положительной клеммы. На приведенной ниже диаграмме представлена описанная выше схема для построения логического элемента И с использованием NPN-транзистора.

В этом руководстве используются транзисторы BC547 NPN Transistor , которые были добавлены в схему со всеми вышеупомянутыми компонентами, как показано ниже.

Если у вас нет с собой кнопок, вы также можете использовать провода в качестве переключателей, добавляя или удаляя их по мере необходимости (вместо нажатия на переключатель). То же самое можно увидеть на видео, где я использовал провода в качестве переключателя, подключенного к базовой клемме для обоих транзисторов.

Та же схема, построенная с использованием вышеупомянутых аппаратных компонентов, будет выглядеть примерно так, как показано на изображении ниже.

Работа затвора И с использованием транзистора

Здесь мы будем использовать транзистор в качестве переключателя, поэтому, когда напряжение подается через коллекторный вывод NPN-транзистора, напряжение достигает только эмиттерного перехода. когда на базовый переход подается напряжение между 0 В и напряжением коллектора.

Аналогично, приведенная выше схема заставит светодиод светиться, т. е. выход равен 1 (высокий уровень), только когда оба входа равны 1 (высокий уровень), т. е. когда на базовые клеммы обоих транзисторов подается напряжение. Это означает, что будет прямолинейный путь тока от VCC (питание +5 В) к светодиоду и далее к земле. В остальных случаях выход будет 0 (Низкий), а светодиод будет выключен. Все это можно объяснить более подробно, разбираясь в каждом случае отдельно.

е. когда на базовые клеммы обоих транзисторов подается напряжение. Это означает, что будет прямолинейный путь тока от VCC (питание +5 В) к светодиоду и далее к земле. В остальных случаях выход будет 0 (Низкий), а светодиод будет выключен. Все это можно объяснить более подробно, разбираясь в каждом случае отдельно.

Случай 1: Когда оба входа равны нулю – A = 0 & B = 0 .

Когда оба входа A и B равны 0, в этом случае вам не нужно нажимать никакие кнопки. Если вы не используете кнопки, удалите провода, соединенные с кнопками и клеммой основания обоих транзисторов. Итак, мы получили оба входа A и B как 0, и теперь нам нужно проверить выход, который также должен быть 0 в соответствии с таблицей истинности вентиля AND.

Теперь, когда напряжение подается через клемму коллектора Транзистора 1, эмиттер не получает никаких входных данных, поскольку значение базовой клеммы равно 0. Точно так же эмиттер транзистора 1, который подключен к коллектору Транзистора 2 , не подает ток или напряжение, а также значение базовой клеммы транзистора 2 равно 0. Таким образом, эмиттер транзистора 2 и выводит значение 0, и в результате светодиод будет выключен.

Таким образом, эмиттер транзистора 2 и выводит значение 0, и в результате светодиод будет выключен.

Случай 2: Когда входные данные – A = 0 & B = 1 .

Во втором случае, когда входы A = 0 и B = 1, схема имеет первый вход как 0 (Низкий), а второй вход как 1 (Высокий) к базе транзистора 1 и 2, соответственно. Теперь, когда питание 5 В подается на коллектор первого транзистора, фазовый сдвиг транзистора не изменяется, поскольку на базовом выводе есть вход 0. Который передает значение 0 на эмиттер, а эмиттер первого транзистора последовательно соединен с коллектором второго транзистора, поэтому значение 0 поступает на коллектор второго транзистора.

Теперь у второго транзистора высокое значение в базе, поэтому это позволит тому же значению, полученному в коллекторе, пройти к эмиттеру. Но так как на выводе коллектора второго транзистора значение 0, то и эмиттер тоже будет 0 и светодиод, подключенный к эмиттеру, светиться не будет.

Случай 3: Когда входные данные – A = 1 & B = 0 .

Здесь вход равен 1 (высокий уровень) для базы первого транзистора и низкий уровень для базы второго транзистора. Таким образом, путь тока будет начинаться от источника питания 5 В к коллектору второго транзистора, проходя через коллектор и эмиттер первого транзистора, поскольку значение базового вывода для первого транзистора велико.

Но во втором транзисторе значение базовой клеммы равно 0, и поэтому ток не проходит от коллектора к эмиттеру второго транзистора, и в результате светодиод будет по-прежнему выключен.

Случай 4: Когда оба входа равны единице – A = 1 & B = 1 .

Последний случай и здесь оба входа должны быть высокими, которые подключены к базовым клеммам обоих транзисторов. Это означает, что всякий раз, когда через коллектор обоих транзисторов проходит ток или напряжение, база достигает насыщения и транзистор проводит.

С практической точки зрения, когда на вывод коллектора транзистора 1 подается питание +5 В, а вывод базы насыщен, вывод эмиттера будет получать высокий выходной сигнал, поскольку транзистор смещен в прямом направлении. Этот высокий выходной сигнал на эмиттере поступает непосредственно на коллектор 2 транзисторов и через последовательное соединение. Теперь, аналогично второму транзистору, входной сигнал на коллекторе высокий, и в этом случае на клемме базы также высокий уровень, что означает, что второй транзистор также находится в состоянии насыщения, и высокий входной сигнал будет проходить от коллектора к эмиттеру. Этот высокий уровень выходного сигнала на эмиттере идет на светодиод, который включает светодиод.

Следовательно, все четыре случая имеют те же входы и выходы, что и реальный логический элемент И. Таким образом, мы построили логический вентиль И с использованием транзистора . Надеюсь, вы поняли урок и вам понравилось узнавать что-то новое. Полную работу установки можно найти в видео ниже. В нашем следующем уроке мы также узнаем, как построить вентиль ИЛИ с использованием транзистора и вентиль НЕ с использованием транзистора . Если у вас есть какие-либо вопросы, оставьте их в разделе комментариев ниже или используйте наши форумы для других технических вопросов.

Полную работу установки можно найти в видео ниже. В нашем следующем уроке мы также узнаем, как построить вентиль ИЛИ с использованием транзистора и вентиль НЕ с использованием транзистора . Если у вас есть какие-либо вопросы, оставьте их в разделе комментариев ниже или используйте наши форумы для других технических вопросов.

Транзисторные затворы

Транзисторные затворы

|

Индекс Концепции электроники Цифровая электроника Справочник | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

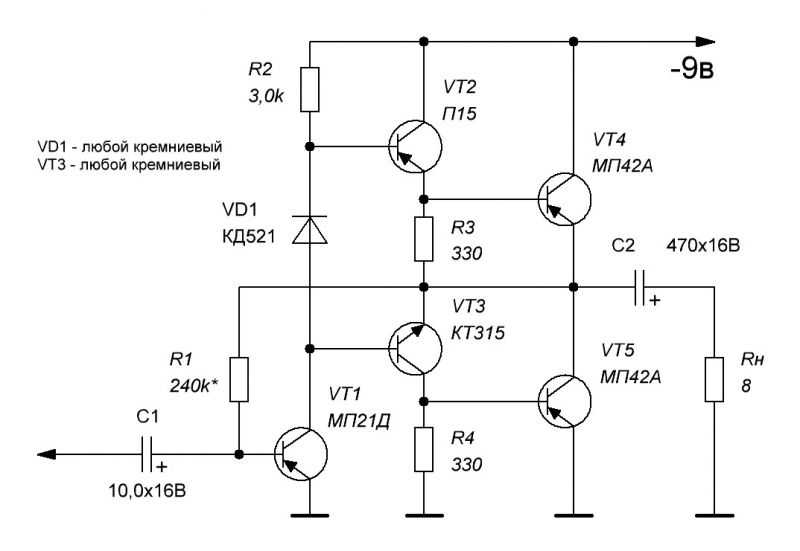

Когда диод база-эмиттер включен достаточно, чтобы войти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики И транзисторы соединены последовательно, и оба транзистора должны быть в проводящем состоянии, чтобы на выходе был высокий уровень.

Когда диод база-эмиттер включен достаточно, чтобы войти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики И транзисторы соединены последовательно, и оба транзистора должны быть в проводящем состоянии, чтобы на выходе был высокий уровень.  Когда диод база-эмиттер включен достаточно, чтобы войти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики ИЛИ транзисторы включены параллельно, и на выходе устанавливается высокий уровень, если какой-либо из транзисторов находится в проводящем состоянии.

Когда диод база-эмиттер включен достаточно, чтобы войти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики ИЛИ транзисторы включены параллельно, и на выходе устанавливается высокий уровень, если какой-либо из транзисторов находится в проводящем состоянии.  Когда диод база-эмиттер включен достаточно, чтобы войти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики И-НЕ транзисторы включены последовательно, но выход находится над ними. Выход высокий, если оба входа A и B не имеют высокого уровня, и в этом случае выход снимается близко к потенциалу земли.

Когда диод база-эмиттер включен достаточно, чтобы войти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики И-НЕ транзисторы включены последовательно, но выход находится над ними. Выход высокий, если оба входа A и B не имеют высокого уровня, и в этом случае выход снимается близко к потенциалу земли.  Когда диод база-эмиттер включен достаточно, чтобы войти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики ИЛИ-НЕ транзисторы подключены параллельно выходу над ними, поэтому, если один или оба входа имеют высокий уровень, на выходе устанавливается низкий уровень.

Когда диод база-эмиттер включен достаточно, чтобы войти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики ИЛИ-НЕ транзисторы подключены параллельно выходу над ними, поэтому, если один или оба входа имеют высокий уровень, на выходе устанавливается низкий уровень.