Как работает схема с общим истоком полевого транзистора. Какие преимущества дает такое включение. Для каких задач подходит схема с общим истоком. Как рассчитать основные параметры усилительного каскада на полевом транзисторе с общим истоком.

Принцип работы схемы с общим истоком полевого транзистора

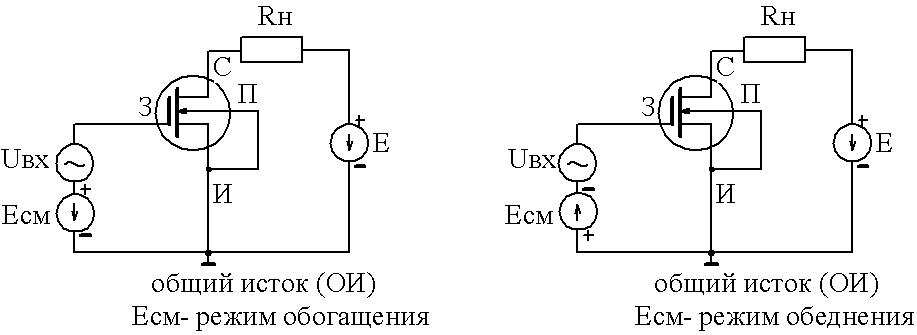

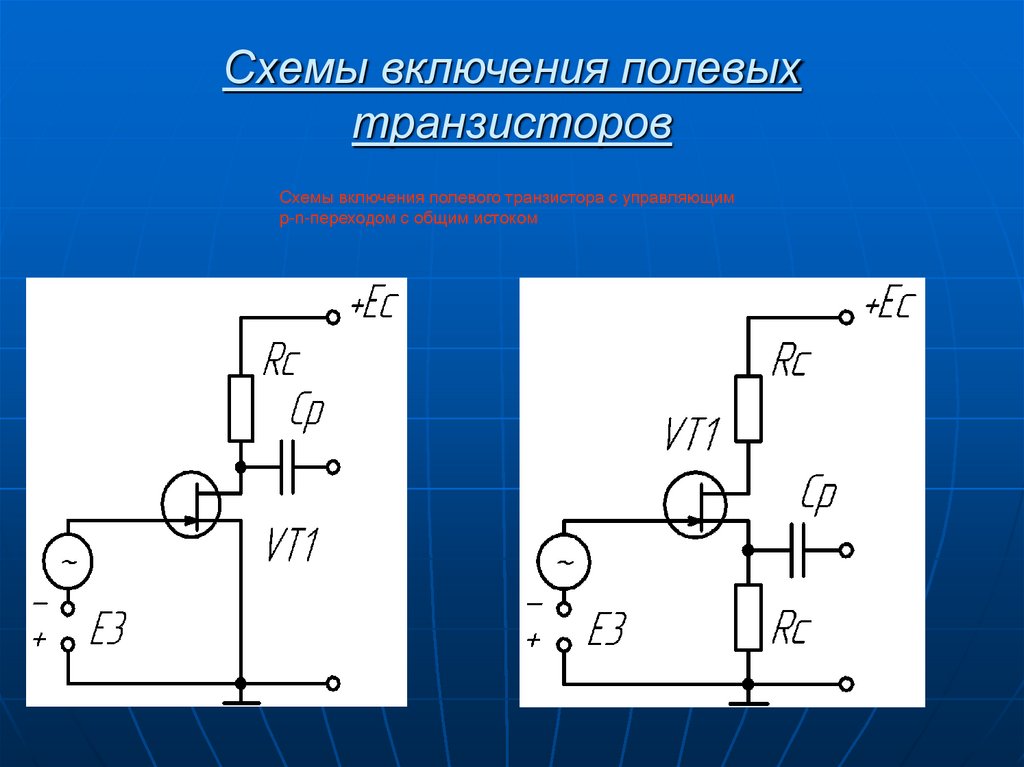

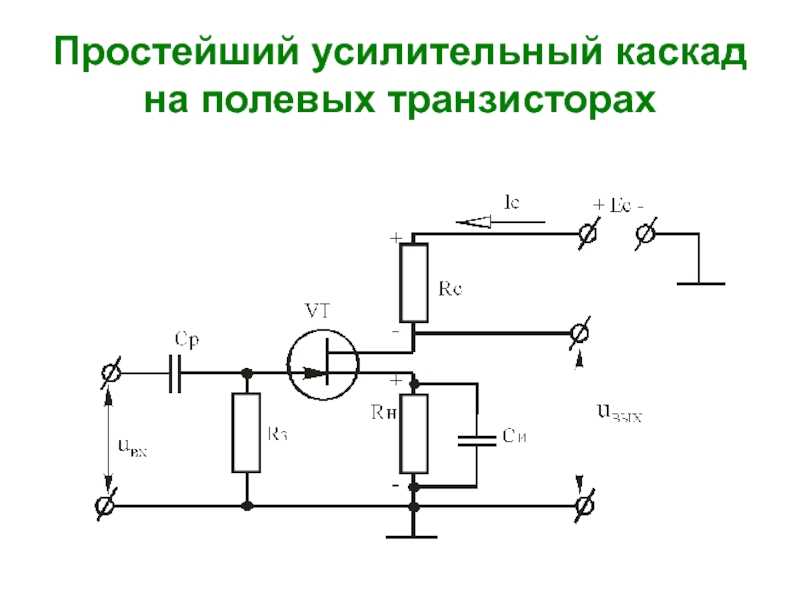

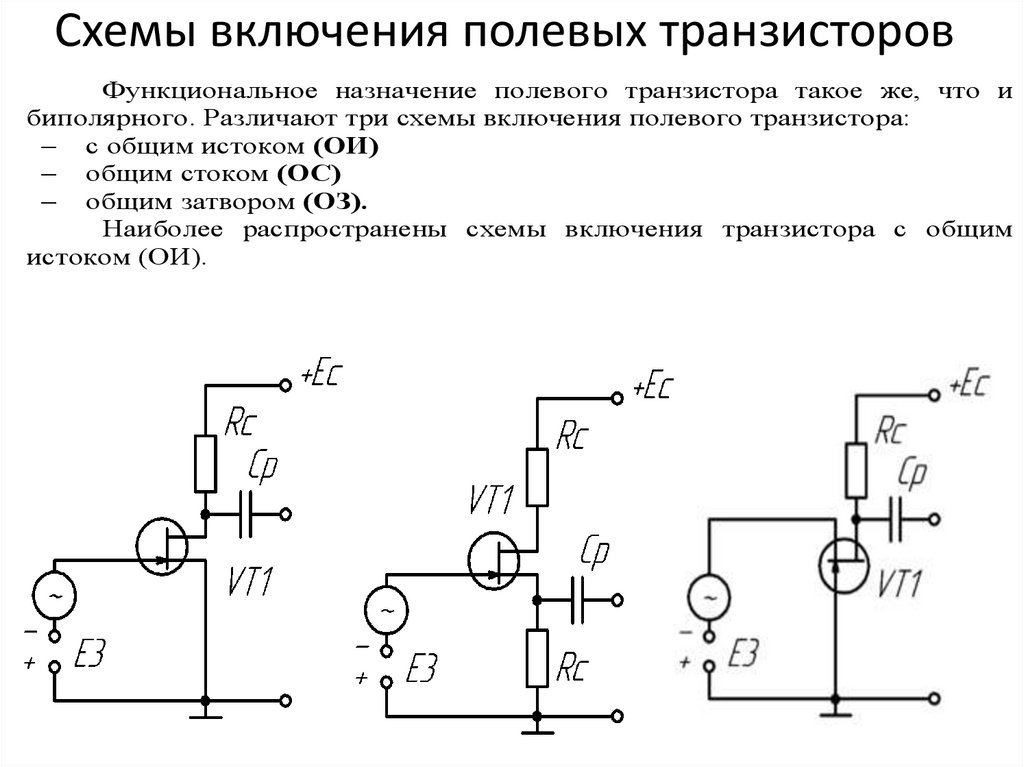

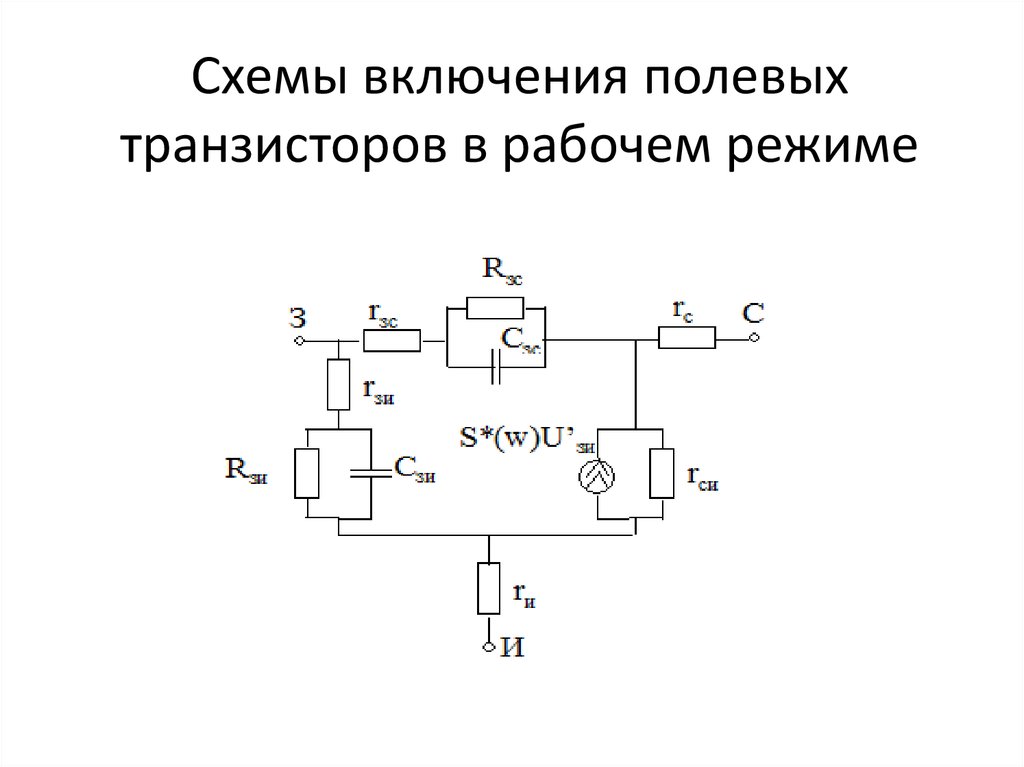

Схема включения с общим истоком является одной из основных схем включения полевых транзисторов. В этой конфигурации:

- Исток транзистора подключен к общей шине (земле)

- Входной сигнал подается на затвор

- Выходной сигнал снимается со стока

Принцип работы схемы с общим истоком следующий:

- Входное напряжение на затворе управляет током канала транзистора

- Изменение тока канала вызывает изменение напряжения на стоковом резисторе

- Это приводит к усилению входного сигнала по напряжению на выходе схемы

Таким образом, схема с общим истоком обеспечивает усиление как по току, так и по напряжению.

Преимущества схемы с общим истоком

Схема включения полевого транзистора с общим истоком обладает рядом важных преимуществ:

- Высокое входное сопротивление (до сотен МОм)

- Хорошее усиление по напряжению (до 10-30)

- Возможность работы в широком диапазоне частот

- Низкий уровень собственных шумов

- Простота реализации

Эти преимущества делают схему с общим истоком востребованной во многих применениях, особенно на высоких частотах.

Основные параметры схемы с общим истоком

Ключевыми параметрами усилительного каскада на полевом транзисторе с общим истоком являются:

- Коэффициент усиления по напряжению (Ku)

- Входное сопротивление (Rвх)

- Выходное сопротивление (Rвых)

- Верхняя граничная частота (fв)

Рассмотрим, как рассчитываются эти параметры.

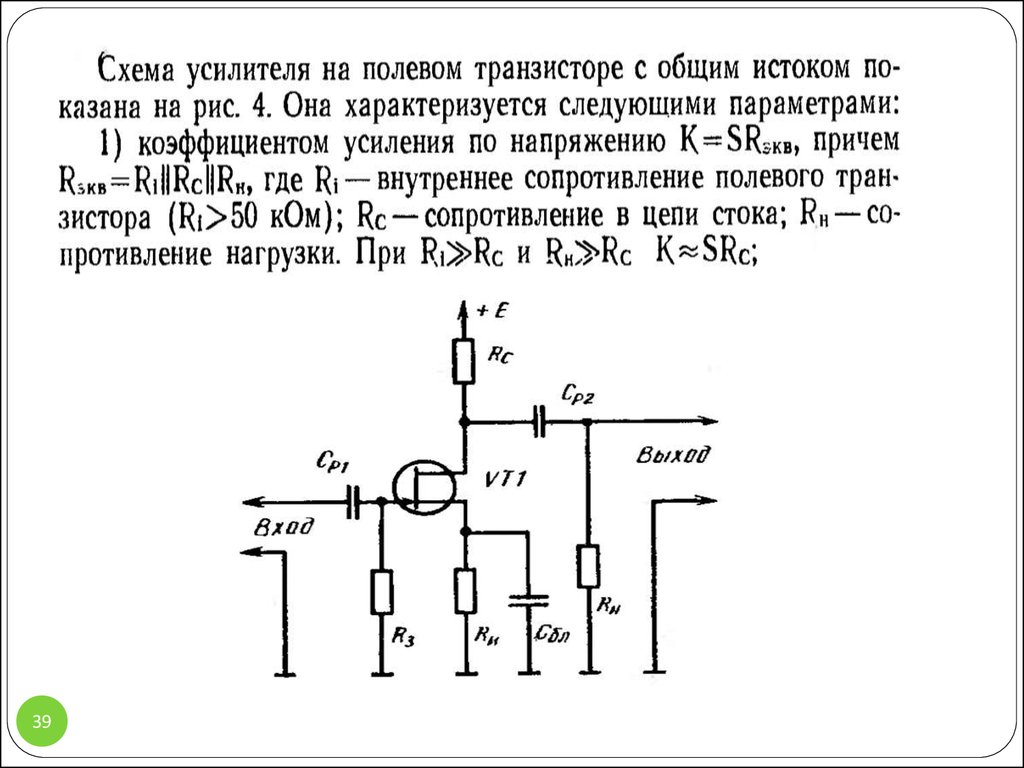

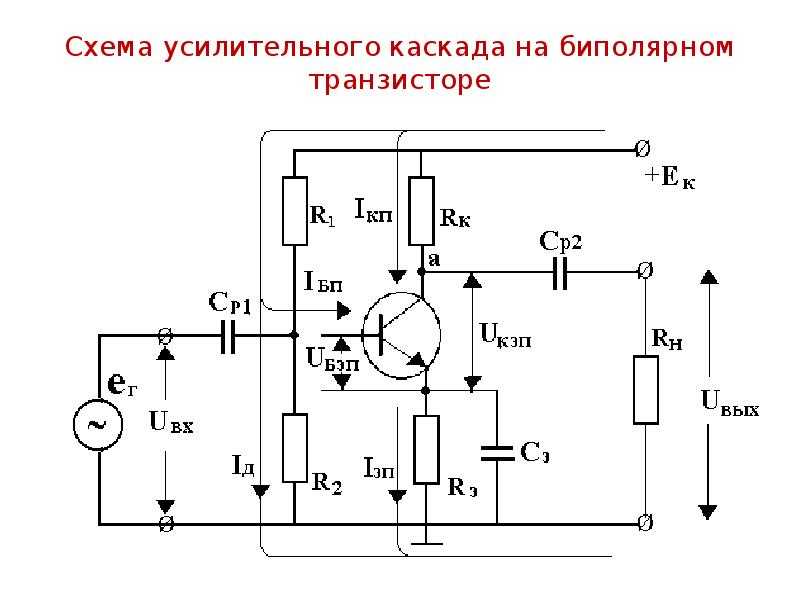

Расчет коэффициента усиления

Коэффициент усиления по напряжению для схемы с общим истоком определяется формулой:

Ku = -S * Rс

где S — крутизна характеристики транзистора, Rс — сопротивление в цепи стока.

Входное сопротивление

Входное сопротивление схемы с общим истоком очень велико и определяется сопротивлением цепи затвор-исток:

Rвх ≈ Rзи

Для полевых транзисторов Rзи может достигать сотен МОм.

Выходное сопротивление

Выходное сопротивление схемы с общим истоком рассчитывается как:

Rвых = Rс || rси

где rси — выходное сопротивление транзистора.

Верхняя граничная частота

Верхняя граничная частота определяется емкостью затвор-сток:

fв = 1 / (2π * Rвых * Cзс)

Для высокочастотных транзисторов fв может достигать сотен МГц.

Применение схемы с общим истоком

Благодаря своим преимуществам, схема с общим истоком нашла широкое применение в различных областях электроники:

- Высокочастотные усилители

- Малошумящие предусилители

- Входные каскады измерительных приборов

- Усилители для датчиков с высоким выходным сопротивлением

- Преобразователи импеданса

Особенно эффективно использование схемы с общим истоком в радиочастотных и СВЧ-устройствах благодаря хорошим высокочастотным свойствам полевых транзисторов.

Особенности расчета схемы с общим истоком

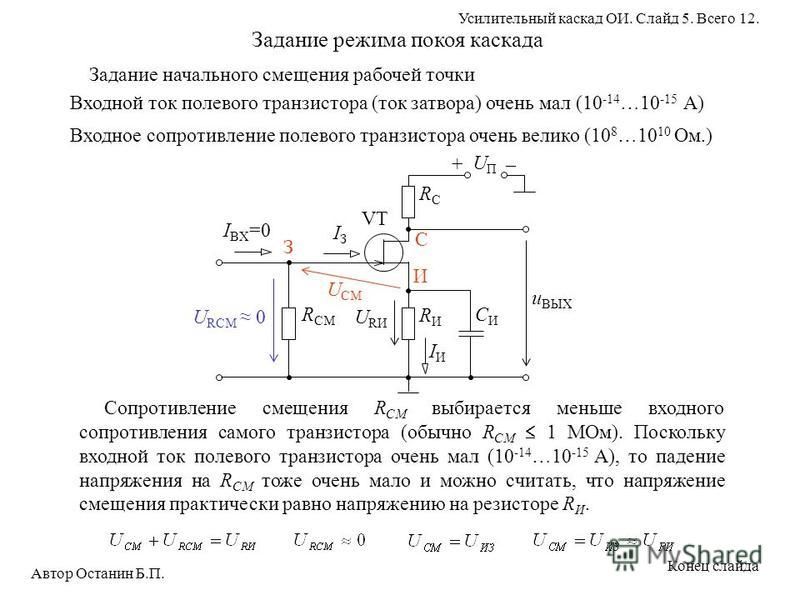

При проектировании усилительного каскада на полевом транзисторе с общим истоком необходимо учитывать следующие особенности:

- Выбор рабочей точки транзистора для обеспечения линейного режима

- Расчет цепи автоматического смещения

- Учет частотных свойств транзистора

- Обеспечение температурной стабилизации

Правильный расчет этих параметров позволяет реализовать все преимущества схемы с общим истоком и получить качественный усилитель.

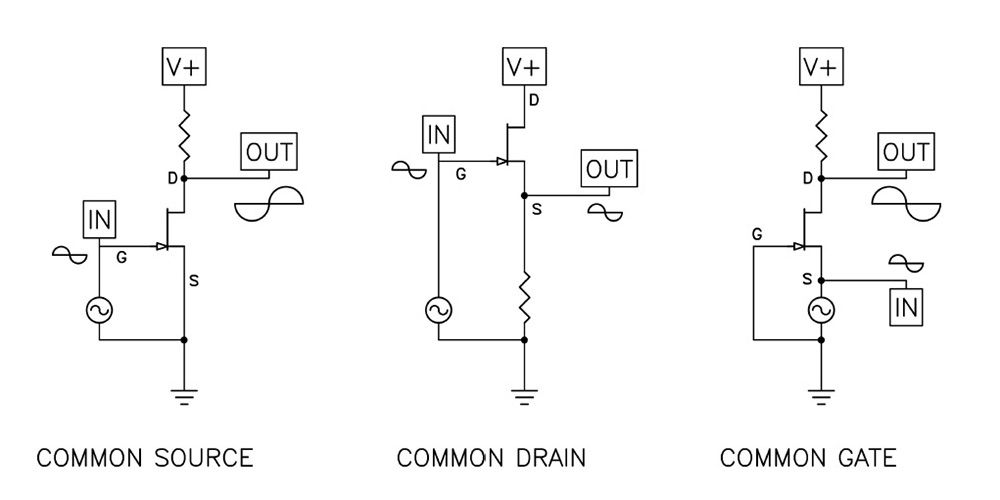

Сравнение с другими схемами включения

Рассмотрим, как схема с общим истоком соотносится с другими базовыми схемами включения полевых транзисторов:

| Параметр | Общий исток | Общий затвор | Общий сток |

|---|---|---|---|

| Усиление по напряжению | Высокое | Среднее | < 1 |

| Входное сопротивление | Очень высокое | Низкое | Высокое |

| Выходное сопротивление | Среднее | Высокое | Низкое |

Как видно, схема с общим истоком обеспечивает наилучшее сочетание усиления и входного сопротивления.

Практические рекомендации по реализации

При практической реализации усилителя на полевом транзисторе с общим истоком следует учитывать ряд моментов:

- Использовать качественные высокочастотные транзисторы

- Применять экранирование для снижения паразитных связей

- Минимизировать длину выводов элементов

- Использовать развязывающие RC-цепочки в цепях питания

- Обеспечить хороший теплоотвод от транзистора

Соблюдение этих рекомендаций позволит реализовать все преимущества схемы с общим истоком и получить качественный усилитель.

Полупроводниковая схемотехника

Полупроводниковая схемотехника

ОглавлениеПредисловие редактора переводаЧасть I. Основные положения 1. Пояснение применяемых величин 2.  Пассивные RC- и LRC- цепи Пассивные RC- и LRC- цепи2.1. ФИЛЬТР НИЖНИХ ЧАСТОТ 2.1.3. ДЛИТЕЛЬНОСТЬ ФРОНТА ИМПУЛЬСА И ЧАСТОТА СРЕЗА ФИЛЬТРА 2.2. ФИЛЬТР ВЕРХНИХ ЧАСТОТ 2.3. КОМПЕНСИРОВАННЫЙ ДЕЛИТЕЛЬ НАПРЯЖЕНИЯ 2.4. ПАССИВНЫЙ ПОЛОСОВОЙ RC-ФИЛЬТР 2.5. МОСТ ВИНА-РОБИНСОНА 2.6. ДВОЙНОЙ Т-ОБРАЗНЫЙ ФИЛЬТР 2.7. КОЛЕБАТЕЛЬНЫЙ КОНТУР 3. Диоды 3.2. СТАБИЛИТРОНЫ 3.3. ВАРИКАПЫ 4. Транзистор и схемы на его основе 4.2. СХЕМА С ОБЩИМ ЭМИТТЕРОМ 4.2.2. НЕЛИНЕЙНЫЕ ИСКАЖЕНИЯ 4.2.3. СХЕМА С ОБЩИМ ЭМИТТЕРОМ И ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО ТОКУ 4.2.5. УСТАНОВКА РАБОЧЕЙ ТОЧКИ 4.3. СХЕМА С ОБЩЕЙ БАЗОЙ 4.4. СХЕМА С ОБЩИМ КОЛЛЕКТОРОМ, ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 4.5. ТРАНЗИСТОР КАК ИСТОЧНИК СТАБИЛЬНОГО ТОКА 4.5.2. БИПОЛЯРНЫЙ ИСТОЧНИК ПИТАНИЯ 4.5.3. СХЕМА «ТОКОВОГО ЗЕРКАЛА» 4.6. СХЕМА ДАРЛИНГТОНА 4.7. ДИФФЕРЕНЦИАЛЬНЫЕ УСИЛИТЕЛИ 4.7.2. РЕЖИМ БОЛЬШОГО СИГНАЛА 4.7.3. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО ТОКУ 4.  7.4. НАПРЯЖЕНИЕ РАЗБАЛАНСА 7.4. НАПРЯЖЕНИЕ РАЗБАЛАНСА4.8. ИЗМЕРЕНИЕ НЕКОТОРЫХ ПАРАМЕТРОВ ПРИ МАЛОМ СИГНАЛЕ 4.9. ШУМЫ ТРАНЗИСТОРА 4.10. ПРЕДЕЛЬНЫЕ ПАРАМЕТРЫ 5. Полевые транзисторы 5.2. ХАРАКТЕРИСТИКИ И ПАРАМЕТРЫ МАЛЫХ СИГНАЛОВ 5.3. ПРЕДЕЛЬНЫЕ ЭЛЕКТРИЧЕСКИЕ ПАРАМЕТРЫ 5.4. ОСНОВНЫЕ СХЕМЫ ВКЛЮЧЕНИЯ 5.4.1. СХЕМА С ОБЩИМ ИСТОКОМ 5.4.2. СХЕМА С ОБЩИМ ЗАТВОРОМ 5.4.3. СХЕМА С ОБЩИМ СТОКОМ, ИСТОКОВЫЙ ПОВТОРИТЕЛЬ 5.5. ПОЛЕВОЙ ТРАНЗИСТОР КАК СТАБИЛИЗАТОР ТОКА 5.6. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ 5.7. ПОЛЕВОЙ ТРАНЗИСТОР В КАЧЕСТВЕ УПРАВЛЯЕМОГО СОПРОТИВЛЕНИЯ 6. Операционный усилитель 6.1. СВОЙСТВА ОПЕРАЦИОННОГО УСИЛИТЕЛЯ 6.2. ПРИНЦИП ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗИ 6.3. НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ 6.4. ИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ 7. Внутренняя структура операционных усилителей 7.2. ПРОСТЕЙШИЕ СХЕМЫ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 7.3. СТАНДАРТНАЯ СХЕМА ИНТЕГРАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ 7.4. КОРРЕКЦИЯ ЧАСТОТНОЙ ХАРАКТЕРИСТИКИ 7.4.  2. ПОЛНАЯ ЧАСТОТНАЯ КОРРЕКЦИЯ 2. ПОЛНАЯ ЧАСТОТНАЯ КОРРЕКЦИЯ7.4.3. ПОДСТРАИВАЕМАЯ ЧАСТОТНАЯ КОРРЕКЦИЯ 7.4.4. СКОРОСТЬ НАРАСТАНИЯ 7.4.5. КОМПЕНСАЦИЯ ЕМКОСТНОЙ НАГРУЗКИ 7.5. ИЗМЕРЕНИЕ ПАРАМЕТРОВ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 8. Простейшие переключающие схемы 8.2. БИСТАБИЛЬНЫЕ РЕЛАКСАЦИОННЫЕ СХЕМЫ 8.2.2. ТРИГГЕР ШМИТТА 8.3. МОНОСТАБИЛЬНАЯ РЕЛАКСАЦИОННАЯ СХЕМА 8.4. НЕСТАБИЛЬНАЯ РЕЛАКСАЦИОННАЯ СХЕМА 9. Базовые логические схемы 9.1. ОСНОВНЫЕ ЛОГИЧЕСКИЕ ФУНКЦИИ 9.2. СОСТАВЛЕНИЕ ЛОГИЧЕСКИХ ФУНКЦИЙ 9.2.1. ТАБЛИЦА КАРНО 9.3. ПРОИЗВОДНЫЕ ОСНОВНЫХ ЛОГИЧЕСКИХ ФУНКЦИЙ 9.4. СХЕМОТЕХНИЧЕСКАЯ РЕАЛИЗАЦИЯ ОСНОВНЫХ ЛОГИЧЕСКИХ ФУНКЦИЙ 9.4.1. РЕЗИСТИВНО-ТРАНЗИСТОРНАЯ ЛОГИКА (РТЛ) 9.4.2. ДИОДНО-ТРАНЗИСТОРНАЯ ЛОГИКА (ДТЛ) 9.4.3. ТРАНЗИСТОРНО-ТРАНЗИСТОРНАЯ ЛОГИКА (ТТЛ) 9.4.4. ИНТЕГРАЛЬНАЯ ИНЖЕКЦИОННАЯ ЛОГИКА 9.4.5. ЭМИТТЕРНО-СВЯЗАННАЯ ЛОГИКА (ЭСЛ) 9.4.6. n-КАНАЛЬНАЯ МОП-ЛОГИКА 9.4.7. КОМПЛЕМЕНТАРНАЯ МОП-ЛОГИКА (КМОП) 9.4.8. ОБЗОР 9.  4.9. СПЕЦИАЛЬНЫЕ СХЕМЫ ВЫХОДНЫХ КАСКАДОВ 4.9. СПЕЦИАЛЬНЫЕ СХЕМЫ ВЫХОДНЫХ КАСКАДОВ9.5. ИНТЕГРАЛЬНЫЕ ТРИГГЕРЫ 9.5.2. ТРИГГЕРЫ ТИПА M-S (MASTER-SLAVE) 9.5.3. ДИНАМИЧЕСКИЙ ТРИГГЕР 9.6. ПОЛУПРОВОДНИКОВЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА 9.6.2. ПОСТОЯННЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА (ПЗУ) 9.6.3. ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ МАТРИЦЫ (ПЛМ) 10. Оптоэлектронные приборы 10.1. ОСНОВНЫЕ ПОНЯТИЯ ФОТОМЕТРИИ 10.2. ФОТОРЕЗИСТОР 10.3. ФОТОДИОДЫ 10.4. ФОТОТРАНЗИСТОРЫ 10.5. СВЕТОДИОДЫ 10.6. ОПТРОНЫ Часть II. Применения 11. Линейные и нелинейные аналоговые вычислительные схемы 11.1. СХЕМА СУММИРОВАНИЯ 11.2. СХЕМЫ ВЫЧИТАНИЯ 11.2.2. СХЕМА ВЫЧИТАНИЯ НА ОПЕРАЦИОННОМ УСИЛИТЕЛЕ 11.3. БИПОЛЯРНОЕ УСИЛИТЕЛЬНОЕ ЗВЕНО 11.4. СХЕМЫ ИНТЕГРИРОВАНИЯ 11.4.1. ИНВЕРТИРУЮЩИЙ ИНТЕГРАТОР 11.4.2. ЗАДАНИЕ НАЧАЛЬНЫХ УСЛОВИЙ 11.4.3. СУММИРУЮЩИЙ ИНТЕГРАТОР 11.4.4. НЕИНВЕРТИРУЮЩИЙ ИНТЕГРАТОР 11.5. СХЕМЫ ДИФФЕРЕНЦИРОВАНИЯ 11.5.3. СХЕМА ДИФФЕРЕНЦИРОВАНИЯ С ВЫСОКИМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ 11.  11.7. ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ 11.7.2. ЭКСПОНЕНТА 11.7.3. ВЫЧИСЛЕНИЕ СТЕПЕННЫХ ФУНКЦИЙ С ПОМОЩЬЮ ЛОГАРИФМОВ 11.7.4. ФУНКЦИИ SIN X И COS X 11.7.5. ПЕРЕСТРАИВАЕМЫЕ ФУНКЦИОНАЛЬНЫЕ СХЕМЫ 11.8. АНАЛОГОВЫЕ СХЕМЫ УМНОЖЕНИЯ 11.8.2. УМНОЖЕНИЕ С ПОМОЩЬЮ ЛОГАРИФМИЧЕСКИХ ФУНКЦИОНАЛЬНЫХ ГЕНЕРАТОРОВ 11.8.3. СХЕМА УМНОЖЕНИЯ, ИСПОЛЬЗУЮЩАЯ ИЗМЕНЕНИЕ КРУТИЗНЫ ХАРАКТЕРИСТИКИ ТРАНЗИСТОРОВ 11.8.4. СХЕМА УМНОЖЕНИЯ С ИЗОЛИРОВАННЫМИ ЗВЕНЬЯМИ 11.8.5. БАЛАНСИРОВКА СХЕМ УМНОЖЕНИЯ 11.8.6. СХЕМЫ ЧЕТЫРЕХКВАДРАНТНОГО УМНОЖЕНИЯ 11.8.7. ПРИМЕНЕНИЕ СХЕМЫ УМНОЖЕНИЯ ДЛЯ ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНЫХ КОРНЕЙ 11.9. ПРЕОБРАЗОВАНИЕ КООРДИНАТ 11.9.2. ПРЕОБРАЗОВАНИЕ ДЕКАРТОВЫХ КООРДИНАТ В ПОЛЯРНЫЕ 12. Управляемые источники и схемы преобразования полного сопротивления 12.1. ИСТОЧНИКИ НАПРЯЖЕНИЯ, УПРАВЛЯЕМЫЕ НАПРЯЖЕНИЕМ 12.2. ИСТОЧНИКИ НАПРЯЖЕНИЯ, УПРАВЛЯЕМЫЕ ТОКОМ 12.3. ИСТОЧНИКИ ТОКА, УПРАВЛЯЕМЫЕ НАПРЯЖЕНИЕМ 12.  3.2. ИСТОЧНИКИ ТОКА С ЗАЗЕМЛЕННОЙ НАГРУЗКОЙ 3.2. ИСТОЧНИКИ ТОКА С ЗАЗЕМЛЕННОЙ НАГРУЗКОЙ12.3.3. ЭТАЛОННЫЕ ИСТОЧНИКИ ТОКА НА ТРАНЗИСТОРАХ 12.3.4. ПЛАВАЮЩИЕ ИСТОЧНИКИ ТОКА 12.4. ИСТОЧНИКИ ТОКА, УПРАВЛЯЕМЫЕ ТОКОМ 12.5. ПРЕОБРАЗОВАТЕЛЬ ОТРИЦАТЕЛЬНОГО СОПРОТИВЛЕНИЯ (NIC) 12.6. ГИРАТОР 12.7. ЦИРКУЛЯТОР 13. Активные фильтры 13.1. ТЕОРЕТИЧЕСКОЕ ОПИСАНИЕ ФИЛЬТРОВ НИЖНИХ ЧАСТОТ 13.1.1. ФИЛЬТР БАТТЕРВОРТА 13.1.2. ФИЛЬТР ЧЕБЫШЕВА 13.1.3. ФИЛЬТРЫ БЕССЕЛЯ 13.1.4. ОБОБЩЕННОЕ ОПИСАНИЕ ФИЛЬТРОВ 13.2. ПРЕОБРАЗОВАНИЕ НИЖНИХ ЧАСТОТ В ВЕРХНИЕ 13.3. РЕАЛИЗАЦИЯ ФИЛЬТРОВ НИЖНИХ И ВЕРХНИХ ЧАСТОТ ПЕРВОГО ПОРЯДКА 13.4. РЕАЛИЗАЦИЯ ФИЛЬТРОВ НИЖНИХ И ВЕРХНИХ ЧАСТОТ ВТОРОГО ПОРЯДКА 13.4.2. ФИЛЬТР СО СЛОЖНОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.4.3. ФИЛЬТР С ПОЛОЖИТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.4.4. ФИЛЬТР НИЖНИХ ЧАСТОТ С ОМИЧЕСКОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.5. РЕАЛИЗАЦИЯ ФИЛЬТРОВ ВЕРХНИХ И НИЖНИХ ЧАСТОТ БОЛЕЕ ВЫСОКОГО ПОРЯДКА 13.6. ПРЕОБРАЗОВАНИЕ ФИЛЬТРА НИЖНИХ ЧАСТОТ В ПОЛОСОВОЙ ФИЛЬТР 13.  6.1. ПОЛОСОВОЙ ФИЛЬТР ВТОРОГО ПОРЯДКА 6.1. ПОЛОСОВОЙ ФИЛЬТР ВТОРОГО ПОРЯДКА13.6.2. ПОЛОСОВОЙ ФИЛЬТР ЧЕТВЕРТОГО ПОРЯДКА 13.7. РЕАЛИЗАЦИЯ ПОЛОСОВЫХ ФИЛЬТРОВ ВТОРОГО ПОРЯДКА 13.7.2. ПОЛОСОВОЙ ФИЛЬТР СО СЛОЖНОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.7.3. ПОЛОСОВОЙ ФИЛЬТР С ПОЛОЖИТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.7.4. ПОЛОСОВОЙ ФИЛЬТР С ОМИЧЕСКОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ 13.8. ПРЕОБРАЗОВАНИЕ ФИЛЬТРОВ НИЖНИХ ЧАСТОТ В ЗАГРАЖДАЮЩИЕ ПОЛОСОВЫЕ ФИЛЬТРЫ 13.9. РЕАЛИЗАЦИЯ ЗАГРАЖДАЮЩИХ ФИЛЬТРОВ ВТОРОГО ПОРЯДКА 13.9.1. ЗАГРАЖДАЮЩИЙ LRC-ФИЛЬТР 13.9.2. АКТИВНЫЙ ЗАГРАЖДАЮЩИЙ ФИЛЬТР С ДВОЙНЫМ Т-ОБРАЗНЫМ МОСТОМ 13.9.3. АКТИВНЫЙ ЗАГРАЖДАЮЩИЙ ФИЛЬТР С МОСТОМ ВИНА-РОБИНСОНА 13.10. ФАЗОВЫЙ ФИЛЬТР 13.10.2. РЕАЛИЗАЦИЯ ФАЗОВОГО ФИЛЬТРА ПЕРВОГО ПОРЯДКА 13.10.3. РЕАЛИЗАЦИЯ ФАЗОВОГО ФИЛЬТРА ВТОРОГО ПОРЯДКА 13.11. ПЕРЕСТРАИВАЕМЫЙ УНИВЕРСАЛЬНЫЙ ФИЛЬТР 14. Широкополосные усилители 14.1. ЗАВИСИМОСТЬ КОЭФФИЦИЕНТА УСИЛЕНИЯ ПО ТОКУ ОТ ЧАСТОТЫ 14.2. ВЛИЯНИЕ ВНУТРЕННИХ ЕМКОСТЕЙ ТРАНЗИСТОРА И ЕМКОСТЕЙ МОНТАЖА 14.  3. КАСКОДНАЯ СХЕМА 3. КАСКОДНАЯ СХЕМА14.4. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КАК ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ 14.5. СИММЕТРИЧНЫЙ ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ 14.5.2. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ИНВЕРТОРОМ 14.5.3. ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С КОМПЛЕМЕНТАРНОЙ КАСКОДНОЙ СХЕМОЙ 14.5.4. ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ 14.6. ШИРОКОПОЛОСНЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ 14.6.2. ДВУХТАКТНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 14.7. ШИРОКОПОЛОСНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ 15. Усилители мощности 15.1. ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ КАК УСИЛИТЕЛЬ МОЩНОСТИ 15.2. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ 15.2.2. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ В РЕЖИМЕ AB 15.2.3. СПОСОБЫ ЗАДАНИЯ НАПРЯЖЕНИЯ СМЕЩЕНИЯ 15.3. СХЕМЫ ОГРАНИЧЕНИЯ ТОКА 15.4. КОМПЛЕМЕНТАРНЫЙ ЭМИТТЕРНЫЙ ПОВТОРИТЕЛЬ ПО СХЕМЕ ДАРЛИНГТОНА 15.5. РАСЧЕТ МОЩНОГО ОКОНЕЧНОГО КАСКАДА 15.6. СХЕМЫ ПРЕДВАРИТЕЛЬНЫХ УСИЛИТЕЛЕЙ НАПРЯЖЕНИЯ 15.7. ПОВЫШЕНИЕ НАГРУЗОЧНОЙ СПОСОБНОСТИ ИНТЕГРАЛЬНЫХ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 16. Источники питания 16.  1. СВОЙСТВА СЕТЕВЫХ ТРАНСФОРМАТОРОВ 1. СВОЙСТВА СЕТЕВЫХ ТРАНСФОРМАТОРОВ16.2. ВЫПРЯМИТЕЛИ 16.2.1. ОДНОПОЛУПЕРИОДНЫЙ ВЫПРЯМИТЕЛЬ 16.2.2. МОСТОВОЙ ВЫПРЯМИТЕЛЬ 16.2.3. МОСТОВОЙ ВЫПРЯМИТЕЛЬ ДЛЯ ДВУХ СИММЕТРИЧНЫХ ОТНОСИТЕЛЬНО ЗЕМЛИ ВЫХОДНЫХ НАПРЯЖЕНИЙ 16.3. ПОСЛЕДОВАТЕЛЬНАЯ СТАБИЛИЗАЦИЯ НАПРЯЖЕНИЯ 16.3.2. СХЕМА С РЕГУЛИРУЮЩИМ УСИЛИТЕЛЕМ 16.3.3. ИНТЕГРАЛЬНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ 16.3.4. СТАБИЛИЗАТОР С МАЛЫМ НАПРЯЖЕНИЕМ ПОТЕРЬ 16.3.5. СТАБИЛИЗАЦИЯ НАПРЯЖЕНИЙ, СИММЕТРИЧНЫХ ОТНОСИТЕЛЬНО ЗЕМЛИ 16.3.6. СТАБИЛИЗАТОР НАПРЯЖЕНИЯ С ИЗМЕРИТЕЛЬНЫМИ ВЫВОДАМИ 16.3.7. ЛАБОРАТОРНЫЕ ИСТОЧНИКИ ПИТАНИЯ 16.3.8. ОКОНЕЧНЫЙ КАСКАД ЛАБОРАТОРНОГО ИСТОЧНИКА ПИТАНИЯ С БОЛЬШОЙ ВЫХОДНОЙ МОЩНОСТЬЮ 16.4. ПОЛУЧЕНИЕ ОПОРНОГО НАПРЯЖЕНИЯ 16.4.2. ПОЛУЧЕНИЕ МАЛЫХ ОПОРНЫХ НАПРЯЖЕНИЙ 16.5. ИМПУЛЬСНЫЕ РЕГУЛЯТОРЫ НАПРЯЖЕНИЯ 16.5.2. ПЕРВИЧНЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ 17. Аналоговые коммутаторы и компараторы 17.2. ЭЛЕКТРОННЫЕ КОММУТАТОРЫ 17.2.2. ДИОДНЫЙ КОММУТАТОР 17.2.3. КОММУТАТОР НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ 17.  3. АНАЛОГОВЫЕ КОММУТАТОРЫ НА БАЗЕ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ 3. АНАЛОГОВЫЕ КОММУТАТОРЫ НА БАЗЕ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ17.3.2. КОММУТАТОР НА ПОЛЕВОМ ТРАНЗИСТОРЕ С ПЕРЕМЕНОЙ ЗНАКА ВЫХОДНОГО НАПРЯЖЕНИЯ 17.3.3. КОММУТАТОР НА БАЗЕ ДИФФЕРЕНЦИАЛЬНОГО УСИЛИТЕЛЯ 17.4. АНАЛОГОВЫЕ КОММУТАТОРЫ С ПАМЯТЬЮ 17.5. КОМПАРАТОРЫ 17.5.2. КОМПАРАТОР С ПРЕЦИЗИОННЫМ ВЫХОДНЫМ НАПРЯЖЕНИЕМ 17.5.3. ДВУХПОРОГОВЫЙ КОМПАРАТОР 17.6. ТРИГГЕР ШМИТТА 17.6.1. ИНВЕРТИРУЮЩИЙ ТРИГГЕР ШМИТТА 17.6.2. НЕИНВЕРТИРУЮЩИЙ ТРИГГЕР ШМИТТА 17.6.3. ПРЕЦИЗИОННЫЙ ТРИГГЕР ШМИТТА 18. Генераторы сигналов 18.1. LC-ГЕНЕРАТОРЫ 18.1.2. ГЕНЕРАТОР С ТРАНСФОРМАТОРНОЙ СВЯЗЬЮ (СХЕМА МАЙССНЕРА) 18.1.3. ТРЕХТОЧЕЧНАЯ СХЕМА С ИНДУKТИВНОЙ ОБРАТНОЙ СВЯЗЬЮ (СХЕМА ХАРТЛИ) 18.1.4. ТРЕХТОЧЕЧНАЯ СХЕМА С ЕМКОСТНОЙ ОБРАТНОЙ СВЯЗЬЮ (СХЕМА КОЛПИТЦА) 18.1.5. LC-ГЕНЕРАТОР С ЭМИТТЕРНОЙ СВЯЗЬЮ 18.1.6. ДВУХТАКТНЫЕ ГЕНЕРАТОРЫ 18.2. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ 18.2.1. ЭЛЕКТРИЧЕСКИЕ СВОЙСТВА КВАРЦЕВОГО РЕЗОНАТОРА 18.2.2. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ С LC-КОЛЕБАТЕЛЬНЫМ КОНТУРОМ 18.  2.3. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ БЕЗ LC-КОНТУРА 2.3. КВАРЦЕВЫЕ ГЕНЕРАТОРЫ БЕЗ LC-КОНТУРА18.3. СИНУСОИДАЛЬНЫЕ RC-ГЕНЕРАТОРЫ 18.3.2. МОДЕЛИРОВАНИЕ ДИФФЕРЕНЦИАЛЬНОГО УРАВНЕНИЯ СИНУСОИДАЛЬНЫХ КОЛЕБАНИЙ 18.4. ГЕНЕРАТОРЫ СИГНАЛОВ СПЕЦИАЛЬНОЙ ФОРМЫ (ФУНКЦИОНАЛЬНЫЕ ГЕНЕРАТОРЫ) 18.4.2. ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР С УПРАВЛЯЕМОЙ ЧАСТОТОЙ ВЫХОДНОГО СИГНАЛА 18.4.3. ВЫСОКОЧАСТОТНЫЙ ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР 18.5. МУЛЬТИВИБРАТОРЫ 18.5.1. НИЗКОЧАСТОТНЫЕ МУЛЬТИВИБРАТОРЫ 18.5.2. ВЫСОКОЧАСТОТНЫЕ МУЛЬТИВИБРАТОРЫ 19. Комбинационные логические схемы 19.1. ПРЕОБРАЗОВАТЕЛИ КОДОВ 19.1.2. ДВОИЧНО-ДЕСЯТИЧНЫЕ КОДЫ 19.1.3. КОД ГРЕЯ 19.2. МУЛЬТИПЛЕКСОР И ДЕМУЛЬТИПЛЕКСОР 19.3. КОМБИНАЦИОННОЕ УСТРОЙСТВО СДВИГА 19.4. КОМПАРАТОРЫ 19.5. СУММАТОРЫ 19.5.1. ПОЛУСУММАТОР 19.5.2. ПОЛНЫЙ СУММАТОР 19.5.3. СУММАТОРЫ С ПАРАЛЛЕЛЬНЫМ ПЕРЕНОСОМ 19.5.4. СЛОЖЕНИЕ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ 19.5.5. ВЫЧИТАНИЕ 19.5.6. СЛОЖЕНИЕ ЧИСЕЛ С ЛЮБЫМИ ЗНАКАМИ 19.6. УМНОЖИТЕЛИ 19.7. ЦИФРОВЫЕ ФУНКЦИОНАЛЬНЫЕ ПРЕОБРАЗОВАТЕЛИ 20.  Интегральные схемы со структурами последовательностного типа Интегральные схемы со структурами последовательностного типа20.1. ДВОИЧНЫЕ СЧЕТЧИКИ 20.1.1. АСИНХРОННЫЙ (ПОСЛЕДОВАТЕЛЬНЫЙ) СЧЕТЧИК 20.1.2. СИНХРОННЫЙ (ПАРАЛЛЕЛЬНЫЙ) СЧЕТЧИК 20.2. ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК В КОДЕ 8421 20.2.1. АСИНХРОННЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК 20.2.2. СИНХРОННЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК 20.3. СЧЕТЧИК С ПРЕДВАРИТЕЛЬНОЙ УСТАНОВКОЙ 20.4. РЕГИСТРЫ СДВИГА 20.4.2. КОЛЬЦЕВОЙ РЕГИСТР 20.4.3. РЕГИСТР СДВИГА С ПАРАЛЛЕЛЬНЫМ ВВОДОМ 20.4.4. РЕГИСТР СДВИГА С ПЕРЕКЛЮЧАЕМЫМ НАПРАВЛЕНИЕМ СДВИГА 20.5. ПОЛУЧЕНИЕ ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ 20.6. ПЕРВОНАЧАЛЬНАЯ ОБРАБОТКА АСИНХРОННОГО СИГНАЛА 20.6.2. СИНХРОНИЗАЦИЯ ИМПУЛЬСОВ 20.6.3. СИНХРОННЫЙ ОДНОВИБРАТОР 20.6.4. СИНХРОННЫЙ ДЕТЕКТОР ИЗМЕНЕНИЙ 20.6.5. СИНХРОННЫЙ ТАКТОВЫЙ ПЕРЕКЛЮЧАТЕЛЬ 20.7. СИСТЕМАТИЧЕСКИЙ СИНТЕЗ ПОСЛЕДОВАТЕЛЬНОСТНЫХ СХЕМ 20.7.2. ПРИМЕР СИНТЕЗА ПЕРЕКЛЮЧАЕМОГО СЧЕТЧИКА 20.7.3. СОКРАЩЕНИЕ ЕМКОСТИ ПАМЯТИ 21. Микро-ЭВМ 21.1. ОСНОВНАЯ СТРУКТУРА МИКРО-ЭВМ 21.  2. ПРИНЦИП ДЕЙСТВИЯ МИКРОПРОЦЕССОРА 2. ПРИНЦИП ДЕЙСТВИЯ МИКРОПРОЦЕССОРА21.3. НАБОР КОМАНД 21.4. ОТЛАДОЧНЫЕ СРЕДСТВА 21.5. ОБЗОР МИКРОПРОЦЕССОРОВ РАЗЛИЧНОГО ТИПА 21.6. МОДУЛЬНОЕ ПОСТРОЕНИЕ МИКРО-ЭВМ 21.7. ПЕРИФЕРИЙНЫЕ УСТРОЙСТВА 21.7.1. ПАРАЛЛЕЛЬНЫЙ ИНТЕРФЕЙС 21.7.2. ПОСЛЕДОВАТЕЛЬНЫЙ ИНТЕРФЕЙС 21.7.3. ИНТЕРФЕЙС МАГИСТРАЛИ «ОБЩАЯ ШИНА» 21.7.4. ПРОГРАММИРУЕМЫЙ СЧЕТЧИК 21.7.5. ПОДКЛЮЧЕНИЕ ПЕРИФЕРИЙНЫХ МОДУЛЕЙ СЕМЕЙСТВА 8080 К МАГИСТРАЛЯМ СЕМЕЙСТВА 6800 21.7.6. ОБЗОР ПЕРИФЕРИЙНЫХ УСТРОЙСТВ 21.8. МИНИМАЛЬНЫЕ СИСТЕМЫ 21.8.2. ОДНОКРИСТАЛЬНАЯ МИКРО-ЭВМ 22. Цифровые фильтры 22.1. ТЕОРЕМА О ДИСКРЕТИЗАЦИИ (ТЕОРЕМА О ВЫБОРКАХ) 22.1.2. ПРАКТИЧЕСКИЕ СООБРАЖЕНИЯ 22.2. ЦИФРОВАЯ ФУНКЦИЯ ПЕРЕДАЧИ ФИЛЬТРА 22.3. БИЛИНЕЙНОЕ ПРЕОБРАЗОВАНИЕ 22.4. РЕАЛИЗАЦИЯ ЦИФРОВЫХ ФИЛЬТРОВ 22.4.2. СТРУКТУРА ЦИФРОВЫХ ФИЛЬТРОВ ВТОРОГО ПОРЯДКА 22.4.3. ПРАКТИЧЕСКИЕ СООБРАЖЕНИЯ 23. Передача данных и индикация 23.1. СОЕДИНИТЕЛЬНЫЕ ЛИНИИ 23.2. ЗАЩИТА ДАННЫХ 23.2.2. КОД ХЕММИНГА 23.  3. СТАТИЧЕСКИЕ ЦИФРОВЫЕ ИНДИКАТОРЫ 3. СТАТИЧЕСКИЕ ЦИФРОВЫЕ ИНДИКАТОРЫ23.3.1. ДВОИЧНЫЕ ИНДИКАТОРЫ НА СВЕТОДИОДАХ 23.3.2. ДЕКАДНЫЕ ИНДИКАТОРЫ 23.3.3. ИНДИКАЦИЯ В ШЕСТНАДЦАТЕРИЧНОМ КОДЕ 23.4. МУЛЬТИПЛЕКСНЫЕ ИНДИКАТОРЫ 23.4.1. МНОГОРАЗРЯДНЫЕ 7-СЕГМЕНТНЫЕ ИНДИКАТОРЫ 23.4.2. МАТРИЦА ТОЧЕК 24. Цифро-аналоговые и аналого-цифровые преобразователи 24.1. СХЕМОТЕХНИЧЕСКИЕ ПРИНЦИПЫ ЦА-ПРЕОБРАЗОВАТЕЛЕЙ 24.1.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ С ПЕРЕКИДНЫМИ КЛЮЧАМИ 24.1.3. РЕЗИСТИВНАЯ МАТРИЦА ПОСТОЯННОГО ИМПЕДАНСА (МАТРИЦА ТИПА R-2R) 24.1.4. РЕЗИСТИВНАЯ МАТРИЦА ДЛЯ ДЕКАДНЫХ ПРЕОБРАЗОВАТЕЛЕЙ 24.2. ПОСТРОЕНИЕ ЦА-ПРЕОБРАЗОВАТЕЛЕЙ С ЭЛЕКТРОННЫМИ КЛЮЧАМИ 24.2.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ С ТОКОВЫМИ КЛЮЧАМИ 24.3. ЦА-ПРЕОБРАЮВАТЕЛИ ДЛЯ СПЕЦИАЛЬНЫХ ПРИМЕНЕНИЙ 24.3.2. ЦА-ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ДЕЛЕНИЯ 24.3.3. ЦА-ПРЕОБРАЗОВАТЕЛЬ КАК ГЕНЕРАТОР ФУНКЦИЙ 24.4. ОСНОВНЫЕ ПРИНЦИПЫ АЦ-ПРЕОБРАЗОВАНИЯ 24.5. ТОЧНОСТЬ АЦ-ПРЕОБРАЗОВАТЕЛЕЙ 24.6. ПОСТРОЕНИЕ АЦ-ПРЕОБРАЗОВАТЕЛЕЙ 25. Измерительные схемы 25.  1. ИЗМЕРЕНИЕ НАПРЯЖЕНИЙ 1. ИЗМЕРЕНИЕ НАПРЯЖЕНИЙ25.1.2. ИЗМЕРЕНИЕ РАЗНОСТИ ПОТЕНЦИАЛОВ 25.1.3. ИЗОЛИРОВАННЫЙ УСИЛИТЕЛЬ 25.2. ИЗМЕРЕНИЕ ТОКА 25.2.1. ИЗОЛИРОВАННЫЕ ОТ ЗЕМЛИ АМПЕРМЕТРЫ С МАЛЫМ ПАДЕНИЕМ НАПРЯЖЕНИЯ 25.2.2. ИЗМЕРЕНИЕ ТОКА ПРИ ВЫСОКОМ ПОТЕНЦИАЛЕ 25.3. ИЗМЕРИТЕЛЬНЫЙ ВЫПРЯМИТЕЛЬ 25.3.2. ИЗМЕРЕНИЕ ЭФФЕКТИВНОГО ЗНАЧЕНИЯ 25.3.3. ИЗМЕРЕНИЕ АМПЛИТУДНЫХ ЗНАЧЕНИЙ 25.3.4. СИНХРОННЫЙ ДЕТЕКТОР 26. Электронные регуляторы 26.2. ТИПЫ РЕГУЛЯТОРОВ 26.2.1. П-РЕГУЛЯТОР 26.2.2. ПИ-РЕГУЛЯТОР 26.2.3. ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР 26.2.4. НАСТРАИВАЕМЫЕ ПИД-РЕГУЛЯТОРЫ 26.3. УПРАВЛЕНИЕ НЕЛИНЕЙНЫМИ ОБЪЕКТАМИ 26.4. ОТСЛЕЖИВАЮЩАЯ СИНХРОНИЗАЦИЯ (АВТОПОДСТРОЙКА) 26.4.1. ЭЛЕМЕНТЫ ВЫБОРКИ-ХРАНЕНИЯ В КАЧЕСТВЕ ФАЗОВОГО ДЕТЕКТОРА 26.4.2. СИНХРОННЫЙ ВЫПРЯМИТЕЛЬ В КАЧЕСТВЕ ФАЗОВОГО ДЕТЕКТОРА 26.4.3. ЧАСТОТНО-ЧУВСТВИТЕЛЬНЫЙ ФАЗОВЫЙ ДЕТЕКТОР 26.4.4. ФАЗОВЫЙ ДЕТЕКТОР С ПРОИЗВОЛЬНО УВЕЛИЧИВАЕМЫМ ДИАПАЗОНОМ ИЗМЕРЕНИЙ 26.4.5. ФАЗОРЕГУЛЯТОР В КАЧЕСТВЕ ПЕРЕМНОЖИТЕЛЯ ЧАСТОТ |

5.

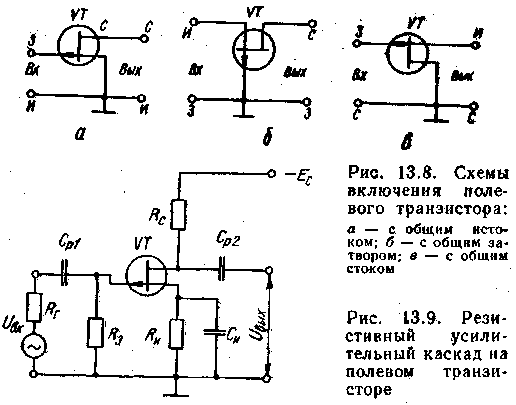

4.2. Схема с общим затвором

4.2. Схема с общим затвором Как правило, для полевых транзисторов схемы с общим затвором почти не применяются, так как при этом включении не используется свойство высокоомности цепи затвор-исток транзистора.

5.4.3. Схема с общим стоком, истоковый повторитель

Схема с общим стоком обладает значительно большим входным сопротивлением, чем схема с общим истоком. В большинстве случаев, однако, это не имеет особого значения, поскольку оно достаточно велико и для схем с общим истоком. Преимуществом такой схемы является то, что она существенно уменьшает входную емкость каскада. В отличие от эмиттерного повторителя выходное сопротивление истокового повторителя не зависит от внутреннего сопротивления Rg источника сигнала.

Рис 5.8 Истоковый повторитель

Типовые значения

коэффициента усиления и выходного

сопротивления истокового повторителя

можно проиллюстрировать числовым

примером. При крутизне характеристики

транзистора 5 мА/В и сопротивлении в

цепи истока Rs = 1 кОм

При крутизне характеристики

транзистора 5 мА/В и сопротивлении в

цепи истока Rs = 1 кОм

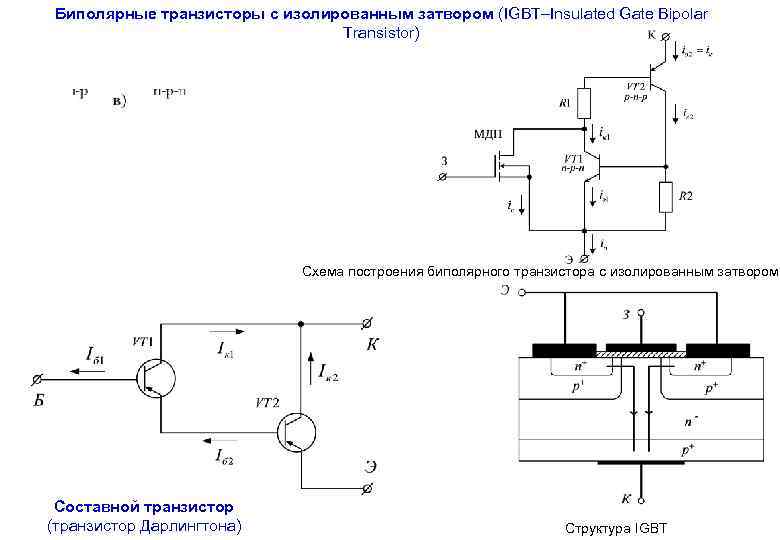

Из примера следует, что истоковый повторитель не позволяет достичь таких низких величин выходных сопротивлений, как эмиттерный повторитель. Причина этого состоит в том, что полевые транзисторы имеют меньшую крутизну, чем биполярные. Поэтому часто полевой и биполярный транзисторы включают совместно по так называемой схеме Дарлингтона изображенной на рис. 5.9.

Рис 5.9 Схема Дарлингтона на полевом и биполярном транзисторах.

5.5. Полевой транзистор как стабилизатор тока

Рис 5.10 Полевой транзистор в качестве источника стабильного тока

Схема,

представленная на рис. 5.10, работает

аналогично транзисторному стабилизатору

тока, изображенному рис. 4.25. У нормально

открытого полевого транзистора

ток стока течет даже тогда, когда

вспомогательное напряжение UH

равно нулю. Этот режим работы транстора

представляет особый интерес, так как

схема стабилизатора тока может бы

выполнена в виде двухполюсника, как

показано на рис. 5.11.

Этот режим работы транстора

представляет особый интерес, так как

схема стабилизатора тока может бы

выполнена в виде двухполюсника, как

показано на рис. 5.11.

Рис 5.11 Стабилизатор тока на полевом транзисторе, выполненный по схеме без вспомогательного напряжения.

Благодаря этой особенности схема может быть включена вместо любого омического сопротивления. Чтобы найти сопротивление обратной связи Rs, следует определить величину UGS для заданного тока стабилизации I передаточной характеристике транзистора. В соответствии с формулой (5.10) получаем

Для определения внутреннего сопротивления стабилизатора тока можно использовать выражение (4.29) для биполярного транзистора, положив и rBE стремящимися к бесконечности и заменив остальные параметры согласно таблице соответствия (5.6):

На

числовом примере можно проиллюстрировать

порядок получаемых величин. Для полевого

транзистора, имеющего при токе стока

ID

= 1 мА следующие параметры: rDS

= 80 кОм и S = 2 мА/В, получим при Rs = 2 кОм

внутреннее сопротивление источника

тока ri

= 400 кОм Эта величина заметно ниже, чем

у аналогичной схемы стабилизатора тока

на биполярном транзисторе.

Для полевого

транзистора, имеющего при токе стока

ID

= 1 мА следующие параметры: rDS

= 80 кОм и S = 2 мА/В, получим при Rs = 2 кОм

внутреннее сопротивление источника

тока ri

= 400 кОм Эта величина заметно ниже, чем

у аналогичной схемы стабилизатора тока

на биполярном транзисторе.

Сравнив выражения (5.12) и (4.29), можно заметить принципиальное различие между стабилизаторами тока на полевом и биполярном транзисторах, а именно: если беспредельно увеличивать сопротивление RE или соответственно RS, то внутреннее сопротивление стабилизатора тока, выполненного на полевом транзисторе, будет стремиться к бесконечности, а на биполярном -к предельному значению, равному rCE. Типовые зависимости ri от RE для биполярного или от Rs для полевого транзисторов изображены на рис. 5.12.

Рис 5.12

Сравнение внутренних сопротивлений

стабилизаторов тока, выполненных на

полевом и биполярном транзисторах. Представлены типовые зависимости

внутреннего сопротивления от параметров

схемы при токе стабилизации, равном 1

мА

Представлены типовые зависимости

внутреннего сопротивления от параметров

схемы при токе стабилизации, равном 1

мА

Следует отметить, что при больших значениях сопротивления обратной связи лучшие характеристики достигаются для стабилизаторов на полевых транзисторах.

Для улучшения параметров стабилизаторов тока сопротивление обратной связи стабилизатора можно выполнить в виде отдельного стабилизатора тока. Если для этого использовать стабилизатор тока на биполярном транзисторе, как изображено на рис 5.13, то, согласно числовому примеру, рассмотренному в разд. 4.5.1, при токе стабилизации 1 мА дифференциальное сопротивление такого стабилизатора Гу, применяемого как сопротивление обратной связи, составит приблизительно 7 МОм. Внутреннее сопротивление стабилизатора с подключенным верхним в схеме полевым транзистором составит около 1,1 ГОм.

Рис 5.13 Каскадирование стабилизаторов тока.

Анализ выхода с общим источником MOSFET

спросил

Изменено 5 лет, 10 месяцев назад

Просмотрено 2к раз

\$\начало группы\$

В чем разница между этими двумя схемами, когда меняется только выходной узел?

Есть ли изменения в выходном сопротивлении, коэффициенте усиления по напряжению или где-то еще?

Симуляция этой схемы-схема, созданная с использованием CircuitLab

Симуляция этой цепи

- MOSFET

- CURED-Analysis

- 70030

4

\$\начало группы\$

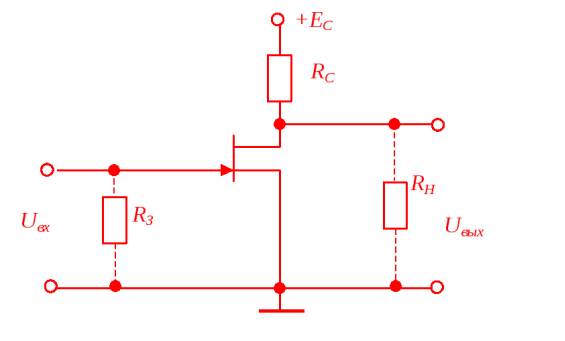

Да, между этими двумя схемами огромная разница. Когда выходное напряжение снимается с клеммы истока, у нас есть повторитель истока (усилитель с общим стоком). Выходное напряжение на Vgs ниже, чем напряжение на затворе MOSFET. Коэффициент усиления по напряжению меньше единицы (\$A_V = \frac{R_4}{\frac{1}{gm} + R_4}\$), а Rout равен 1/gm (низкий).

Когда выходное напряжение снимается с клеммы истока, у нас есть повторитель истока (усилитель с общим стоком). Выходное напряжение на Vgs ниже, чем напряжение на затворе MOSFET. Коэффициент усиления по напряжению меньше единицы (\$A_V = \frac{R_4}{\frac{1}{gm} + R_4}\$), а Rout равен 1/gm (низкий).

Вторая схема представляет собой классический общий исток с резистором вырождения истока (R4). Коэффициент усиления по напряжению равен \$A_V = -\frac{R3}{R4+ \frac{1}{gm}}\$

Коэффициент усиления по напряжению отрицательный, но обычно мы игнорируем этот знак «минус». Потому что это информирует нас только о фазовом сдвиге на 180 градусов между Vin и Vout. Когда напряжение на затворе MOSFET увеличивается, ток стока также увеличивается. Ток в резисторе стока (R3) увеличивается (ID = IR3), что увеличивает падение напряжения на нем (на R3, VR3 = Id R3), поэтому напряжение стока уменьшается (Vd = Vdd — Id R3), что составляет 180 градусов. к изменению напряжения на затворе. А выходное сопротивление Rвых = R3.

А выходное сопротивление Rвых = R3.

\$\конечная группа\$

2

\$\начало группы\$

Это классический 0/180 балансный выходной усилитель с обращенной фазой. Вы используете его в некоторых усилителях звука. Если активное устройство смещено для высокого gm (крутизна), нижнее колебание напряжения почти идентично верхнему колебанию напряжения.

смоделируйте эту схему — Схема создана с помощью CircuitLab

\$\конечная группа\$

2

\$\начало группы\$

Есть ли изменения в выходном сопротивлении, коэффициенте усиления по напряжению или еще где-то?

так как нет входного сигнала, на эти вопросы нет ответа.

после этого вам нужно будет знать о характеристиках входного сигнала, чтобы уверенно отвечать на ваши вопросы.

\$\конечная группа\$

1

Зарегистрируйтесь или войдите в систему

Зарегистрируйтесь с помощью Google

Зарегистрироваться через Facebook

Зарегистрируйтесь, используя электронную почту и пароль

Опубликовать как гость

Электронная почта

Требуется, но никогда не отображается

Опубликовать как гость

Электронная почта

Требуется, но не отображается

Нажимая «Опубликовать свой ответ», вы соглашаетесь с нашими условиями обслуживания, политикой конфиденциальности и политикой использования файлов cookie

.

rf — Может ли N-канальный JFET-переключатель иметь положительный общий исток?

спросил

Изменено 4 года, 8 месяцев назад

Просмотрено 200 раз

\$\начало группы\$

Рассматриваю варианты коммутации для сети тюнеров ВЧ (3-15 МГц). Pin-диоды интересны, но окружающая их схема управления несколько неудобна, и для их работы требуется относительно большая мощность.

Я читаю о RF JFET. Как общие руководства по JFET, так и спецификации для RF JFET, таких как J211, предполагают, что Vgs должно быть отрицательным, что потребует добавления отрицательного источника питания.

Можно ли обойти это, подключив N-канальный JFET так же, как P-канальный MOSFET с общим истоком? Исток к Vdd, вентиль к линии управления уровня TTL и сток к нагрузке. Это не потребует дополнительного отрицательного источника питания.

Это не потребует дополнительного отрицательного источника питания.

Судя по диалогу, мне нужно отойти от этого (пожалуйста, представьте, что MOSFET — это JFET):

К этому:

- RF

- коммутация

- jfet

\$\конечная группа\$

2

\$\начало группы\$

В определенной степени вы можете использовать N-канальный JFET с истоком в V+ и контролировать проводимость канала с напряжением затвора от 0 вольт до V+. Проблема в том, что у вас не может быть значительного уровня постоянного тока (или сигнала с пиковыми уровнями) намного ниже положительной шины стока. Возьми 2Н59.51 характеристика: —

Как вы можете видеть, для различных уровней VGS вы можете получить приемлемую 4-квадрантную характеристику тока стока по отношению к напряжению стока, но это станет проблематичным в третьем квадранте, поскольку VDS становится более отрицательным.