Калейдоскоп схем на операционных усилителях

Операционные усилители

Калейдоскоп схем на операционных усилителях

Подразделы: 4.09 4.10

Мы предоставляем читателю право самостоятельно проанализировать работу приведенных ниже схем.

Схема с инвертированием по выбору. Схемы, представленные на рис. 4.14, позволяют инвертировать входной сигнал или пропускать его без инвертирования в зависимости от положения переключателя. Положение переключателя определяет также коэффициент усиления по напряжению — он может быть равен или +1, или -1.

Рис. 4.14.

Упражнение 4.5. Покажите, что схемы, представленные на рис. 4.14, работают так, как сказано выше.

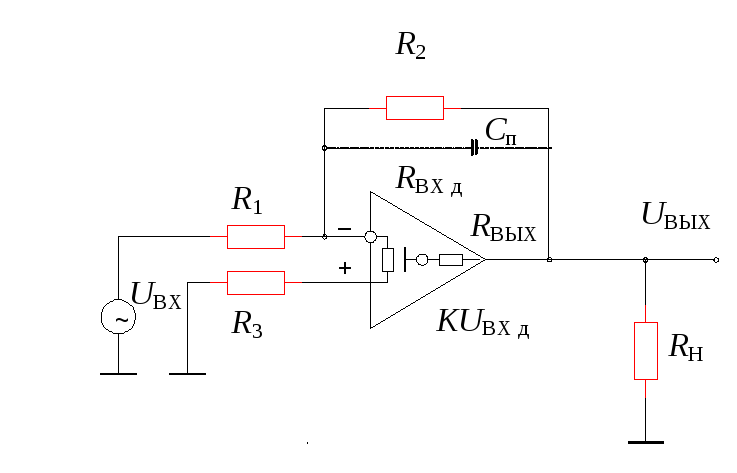

Повторитель со следящей связью. В транзисторных усилителях на величину входного импеданса могут влиять цепи смешения; такая же проблема возникает при использовании ОУ, особенно с межкаскадными связями по переменному току, когда ко входу обязательно должен быть подключен заземленный резистор. Схема со следящей связью, представленная на рис. 4.15. позволяет решить эту проблему. Как и в транзисторной схеме со следящей связью (разд. 2.17), конденсатор емкостью 0,1 мкФ вместе с верхним резистором с сопротивлением 1 МОм образует для входных сигналов высокоомную входную цепь. Низкочастотный спад усиления для этой схемы начинается на частоте 10 Гц, на более низких частотах на спаде усиления начинает сказываться влияние обоих конденсаторов и ослабление оценивается величиной 12дБ/октава. Замечание: у вас может появиться искушение уменьшить величину входного конденсатора связи, так как его нагрузка привязана к высокому импедансу. Однако, это может привести к появлению пика в частотной характеристике, как в характеристике схемы активного фильтра (см. разд. 5.06).

Схема со следящей связью, представленная на рис. 4.15. позволяет решить эту проблему. Как и в транзисторной схеме со следящей связью (разд. 2.17), конденсатор емкостью 0,1 мкФ вместе с верхним резистором с сопротивлением 1 МОм образует для входных сигналов высокоомную входную цепь. Низкочастотный спад усиления для этой схемы начинается на частоте 10 Гц, на более низких частотах на спаде усиления начинает сказываться влияние обоих конденсаторов и ослабление оценивается величиной 12дБ/октава. Замечание: у вас может появиться искушение уменьшить величину входного конденсатора связи, так как его нагрузка привязана к высокому импедансу. Однако, это может привести к появлению пика в частотной характеристике, как в характеристике схемы активного фильтра (см. разд. 5.06).

Рис. 4.15.

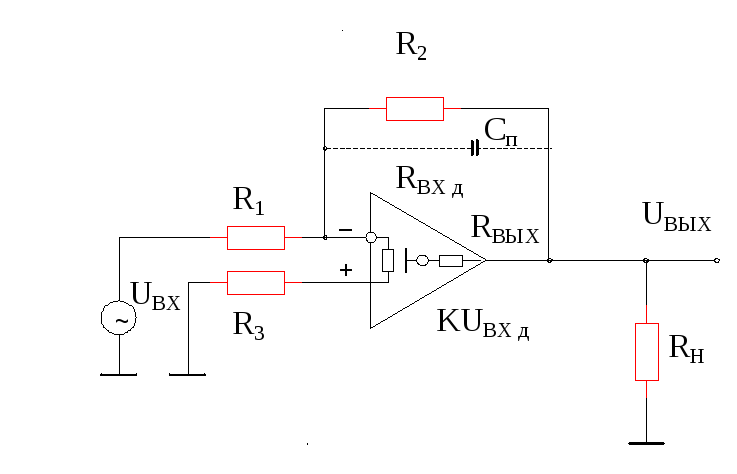

Идеальный преобразователь тока в напряжение. Напомним, что простейшим преобразователь тока в напряжение — это всего — навсего резистор. Однако у него есть недостаток, который состоит в том, что для источника входного сигнала входное сопротивление такого преобразователя не равно нулю; этот недостаток может оказаться очень серьезным, если устройство, обеспечивающее входной ток, имеет очень малый выходной рабочий диапазон или не может обеспечить постоянство тока при изменении выходного напряжения. Примером может служить диодный фотоэлемент (фотодиод), или солнечная батарея. Небольшой светочувствительностью обладают даже обычные диоды в прозрачных корпусах, которые используются почти в любой схеме (известно немало историй о загадочном поведении схем которое в конце концов было объяснено этим эффектом). На рис. 4.16 представлена хорошая схема для преобразования тока в напряжение, в которой потенциал входа поддерживается строго равным потенциалу земли. Инвертирующий вход имеет квазинуль потенциала; это очень хорошо, так как фотодиод может создавать потенциал, равный всего нескольким десятым долям вольта. Представленная схема обеспечивает преобразование тока в напряжение в отношении 1 В на 1 мкА входного тока. (В ОУ с биполярными плоскостными транзисторами на входах иногда между неинвертирующим входом и землей включают резистор: его функции мы определим, когда будем обсуждать недостатки операционных усилителей).

Примером может служить диодный фотоэлемент (фотодиод), или солнечная батарея. Небольшой светочувствительностью обладают даже обычные диоды в прозрачных корпусах, которые используются почти в любой схеме (известно немало историй о загадочном поведении схем которое в конце концов было объяснено этим эффектом). На рис. 4.16 представлена хорошая схема для преобразования тока в напряжение, в которой потенциал входа поддерживается строго равным потенциалу земли. Инвертирующий вход имеет квазинуль потенциала; это очень хорошо, так как фотодиод может создавать потенциал, равный всего нескольким десятым долям вольта. Представленная схема обеспечивает преобразование тока в напряжение в отношении 1 В на 1 мкА входного тока. (В ОУ с биполярными плоскостными транзисторами на входах иногда между неинвертирующим входом и землей включают резистор: его функции мы определим, когда будем обсуждать недостатки операционных усилителей).

Рис. 4.16.

Безусловно, этот преобразователь тока в напряжение можно с таким же успехом использовать с элементами, через которые протекает ток при наличии положительного напряжения возбуждения, например Uкк. В такую схему часто включают фотоумножители и фототранзисторы (оба элемента под воздействием света начинают потреблять ток от положительно источника питания (рис. 4.17).

В такую схему часто включают фотоумножители и фототранзисторы (оба элемента под воздействием света начинают потреблять ток от положительно источника питания (рис. 4.17).

Упражнение 4.4. Используя ОУ типа 411 и измерительный прибор на 1 мА (полный размах шкалы), разработайте схему «идеального» измерителя тока (т.е. с нулевым входным импедансом) с полным размахом шкалы, рассчитанным на 5 мА. Разработайте схему так, чтобы входной сигнал никогда не превышал ±150% полного размаха шкалы. Предположите, что диапазон выходного сигнала для ОУ типа 411 составляет ±13 В (источники питания ±15 В), а внутреннее сопротивление измерительного прибора равно 500 Ом.

Рис. 4.17.

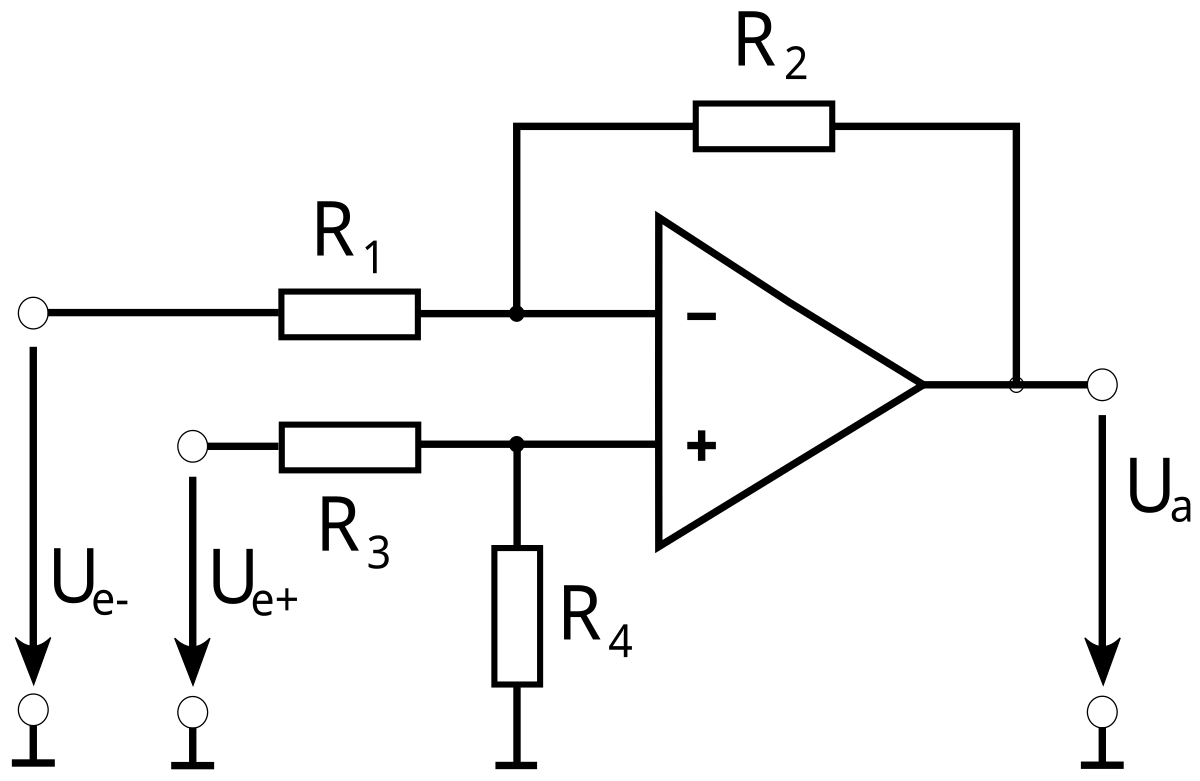

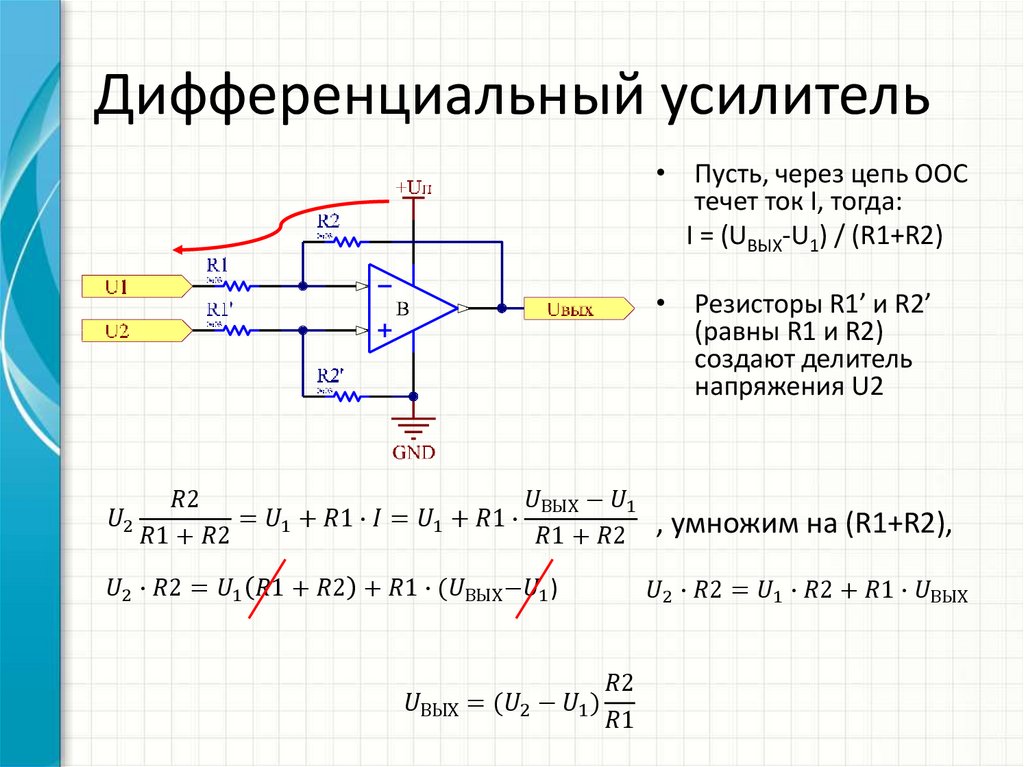

Дифференциальный усилитель. На рис. 4.18 представлена схема дифференциального усилителя, коэффициент усиления которого равен R2/R1. В этой схеме, как и в схеме источника тока с согласованными резисторами, для получения высокого значения КОСС необходимо обеспечить точное согласование резисторов. Для этого лучше всего при первом удобном случае создать запас резисторов с сопротивлением 100 кОм и точностью 0,01%. Коэффициент усиления дифференциального усилителя будет равен единице, но этот недостаток легко устранить за счет последующих усилительных каскадов (с несимметричным входом). Более подробно дифференциальные усилители рассмотрены в гл. 7.

Для этого лучше всего при первом удобном случае создать запас резисторов с сопротивлением 100 кОм и точностью 0,01%. Коэффициент усиления дифференциального усилителя будет равен единице, но этот недостаток легко устранить за счет последующих усилительных каскадов (с несимметричным входом). Более подробно дифференциальные усилители рассмотрены в гл. 7.

Рис. 4.18.

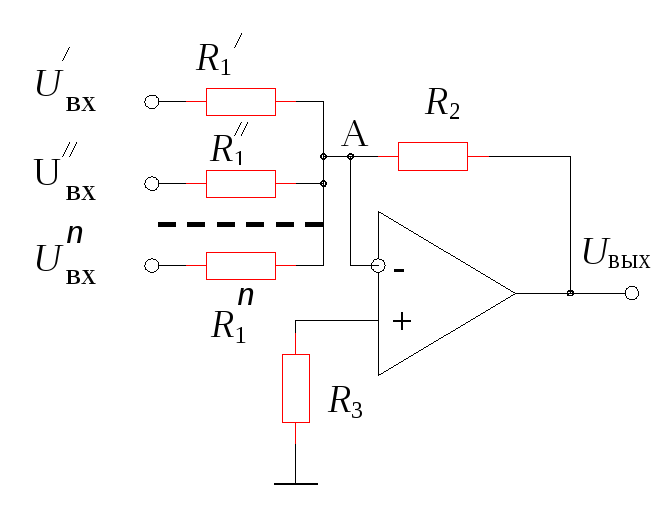

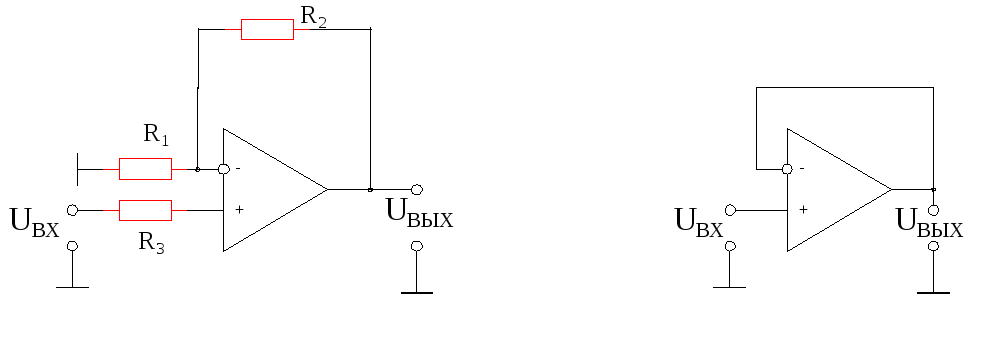

Суммирующий усилитель. Схема, показанная на рис. 4.19, представляет собой один из вариантов инвертирующего усилителя. Точка X имеет потенциальный нуль, поэтому входной ток равен U1/R + U2/R + U3/R, отсюда Uвых = — (Ul + U2 + U3). Обратите внимание, что входные сигналы могут быть как положительными, так и отрицательными. Кроме того, входные резисторы не обязательно должны быть одинаковыми; если они неодинаковы, то получим взвешенную сумму. Например, схема может иметь 4 входа, на каждом из которых напряжение равно + 1 В или О В; входы представляют двоичные значения: 1, 2, 4 и 8. Если использовать резисторы с сопротивлением 10, 5, 2,5 и 1,25 кОм. то снимаемое с выхода напряжение (в вольтах) будет пропорционально двоичному числу, которое задано на входе. Эту схему нетрудно расширить до нескольких цифр. Описанный метод представления чисел лежит в основе цифро-аналогового преобразования, правда, на входе преобразователя обычно используют другую схему (резистивную сетку R — 2R).

Если использовать резисторы с сопротивлением 10, 5, 2,5 и 1,25 кОм. то снимаемое с выхода напряжение (в вольтах) будет пропорционально двоичному числу, которое задано на входе. Эту схему нетрудно расширить до нескольких цифр. Описанный метод представления чисел лежит в основе цифро-аналогового преобразования, правда, на входе преобразователя обычно используют другую схему (резистивную сетку R — 2R).

Рис. 4.19.

Упражнение 4.5. Постройте схему цифро-аналогового преобразователя на две десятичные цифры, подобрав соответствующим образом входные резисторы для суммирующего усилителя. Цифровой вход должен представлять собой две цифры; каждый вход должен состоять из четырех шин, соответствующих значениям 1, 2, 4 и 8, из которых формируется десятичная цифра. Потенциал входной шины может быть равен потенциалу земли или +1 В, т. е. восемь входных шин соответствуют числам 1, 2, 4. 8. 10. 20, 40 и 80. В связи с тем, что диапазон выходного сигнала ограничен значениями ±13 В, нужно сделать так, чтобы выходное напряжение (в вольтах) составляло одну десятую часть числа на входе.

Предусилитель для электромагнитного звукоснимателя. Предусилитель для звукоснимателя по стандарту RIAA представляет собой пример усилителя с частотной характеристикой особого вида. При записи звука на пластинку амплитудная характеристика имеет почти плоский вид, с другой стороны, электромагнитный звукосниматель реагирует на скорость движения иглы в бороздке диска, следовательно, усилитель воспроизведения должен иметь подъем частотной характеристики на низких частотах. Такую характеристику обеспечивает схема, показанная на рис. 4.20. График представляет собой частотную характеристику усилителя воспроизведения (построенную относительно значения коэффициента усиления 0 дБ при частоте 1 кГц), точки перегиба графика отмечены в единицах времени. Заземленный конденсатор емкостью 47 мкФ уменьшает коэффициент усиления по постоянному току до единицы, в противном случае он был бы равен 1000; как упоминалось выше, это делается для того, чтобы устранить усиление входного сдвига по постоянному току Использованная в примере интегральная схема типа LM833 представляет собой сдвоенный ОУ, предназначенный для использования в звуковом диапазоне («золотой» для данного примера является схема типа LM1028, которая в 13 дБ раз тише ив 10 дБ раз дороже, чем схема типа 833!).

Рис. 4.20. Операционный усилитель в схеме предусилителя звуковых частот для электрофонов с электромагнитной головкой и коррекцией частотной характеристики по стандарту RIAA.

Усилитель мощности (бустер). Для получения больших выходных токов к выходу ОУ можно подключить мощный транзисторный повторитель (рис. 4.21). В примере использован неинвертирующий усилитель, но повторитель можно подключать к любом операционному усилителю. Обратите внимание, что сигнал обратной связи снимается с эмиттера; следовательно, обратная связь определяет нужное выходное напряжение независимо от падения напряжения Uбэ. При использовании этой схемы возникает обычная проблема, связанная с тем, что повторитель может только отдавать ток (для n-p-n — транзистора). Как и в случае транзисторного повторителя, проблема решается применением двухтактного варианта схемы (рис. 4.22). В дальнейшем мы покажем, что ограниченная скорость, с которой может изменяться напряжение на выходе (скорость нарастания), накладывает серьезные ограничения на быстродействие усилителя в переходной области и вызывает переходные искажения. Если усилитель будет использоваться в системе с малым быстродействием, то смешать двухтактную пару в состоянии покоя не нужно, так как переходные искажения будут в основном устранены за счет обратной связи. Промышленность выпускает несколько типов интегральных схем усилителей мощности для операционных усилителей, например LT1010, ОРА633 и 3553. Эти двухтактные усилители с единичным коэффициентом усиления работают на частотах до 100 МГц и выше, их выходной ток равен 200 мА. Их смело можно охватывать петлей обратной связи.

Если усилитель будет использоваться в системе с малым быстродействием, то смешать двухтактную пару в состоянии покоя не нужно, так как переходные искажения будут в основном устранены за счет обратной связи. Промышленность выпускает несколько типов интегральных схем усилителей мощности для операционных усилителей, например LT1010, ОРА633 и 3553. Эти двухтактные усилители с единичным коэффициентом усиления работают на частотах до 100 МГц и выше, их выходной ток равен 200 мА. Их смело можно охватывать петлей обратной связи.

Рис. 4.21.

Рис. 4.22.

Источник питания. Операционный усилитель может работать как усилитель в стабилизаторе напряжения с обратной связью (рис. 4.23). Операционный усилитель сравнивает выходное напряжение с эталонным напряжением стабилитрона и соответственно управляет составным транзистором Дарлингтона, выполняющим функции «проходного транзистора». Эта схема обеспечивает стабилизированное напряжение 10 В при протекании через нагрузку тока до 1 А. Некоторые замечания по этой схеме:

Некоторые замечания по этой схеме:

1. Делитель, с которого снимается выходное напряжение, может быть выполнен в виде потенциометра, тогда выходное напряжение можно будет регулировать.

2. Для ослабления пульсаций на зенеровском диоде (стабилитроне) резистор с сопротивлением 10 кОм полезно заменить источником тока. Другой вариант состоит в том, чтобы смещение зенеровского диода задавать от выходного сигнала; в этом случае вы с пользой применяете стабилизатор, который построили. Замечание: если вы захотите воспользоваться этим трюком, то внимательно проанализируйте вашу схему и убедитесь в том, что она запускается, когда на нее подается питание.

3. Схема, подобная рассмотренной, может быть повреждена при возникновении короткого замыкания на выходе. Это связано с тем, что при этом ОУ стремится обеспечить протекание через составной транзистор очень большого тока. В стабилизированном источнике питания всегда следует предусматривать схему для ограничения «аварийного» тока (более подробно вы познакомитесь с этим вопросом в разд. 6.05).

6.05).

4. Промышленность выпускает разнообразные стабилизаторы напряжения в интегральном исполнении, начиная от освященных временем интегральных схем типа 723 до недавно появившихся 3-выводных регулируемых стабилизаторов с внутренними средствами ограничения тока и ограничения по перегреву (см. табл. 6.8-6.10). Эти устройства, в которых имеются встроенные температурно-компенсированный источник эталонного напряжения и проходной транзистор, Так удобны в работе, что операционные усилители общего назначения теперь почти никогда не используются в стабилизатоpax напряжения. Исключением являются случаи, когда стабильное напряжение нужно сформировать внутри схемы. уже имеющей стабилизированный источник напряжения.

Рис. 4.23.

В гл. 6 мы подробно поговорим о стабилизаторах напряжения и источниках питания и рассмотрим специальные интегральные схемы, предназначенные для использования в качестве стабилизаторов напряжения.

Подразделы: 4.09 4.10

Подробный анализ работы операционных усилителей

1.

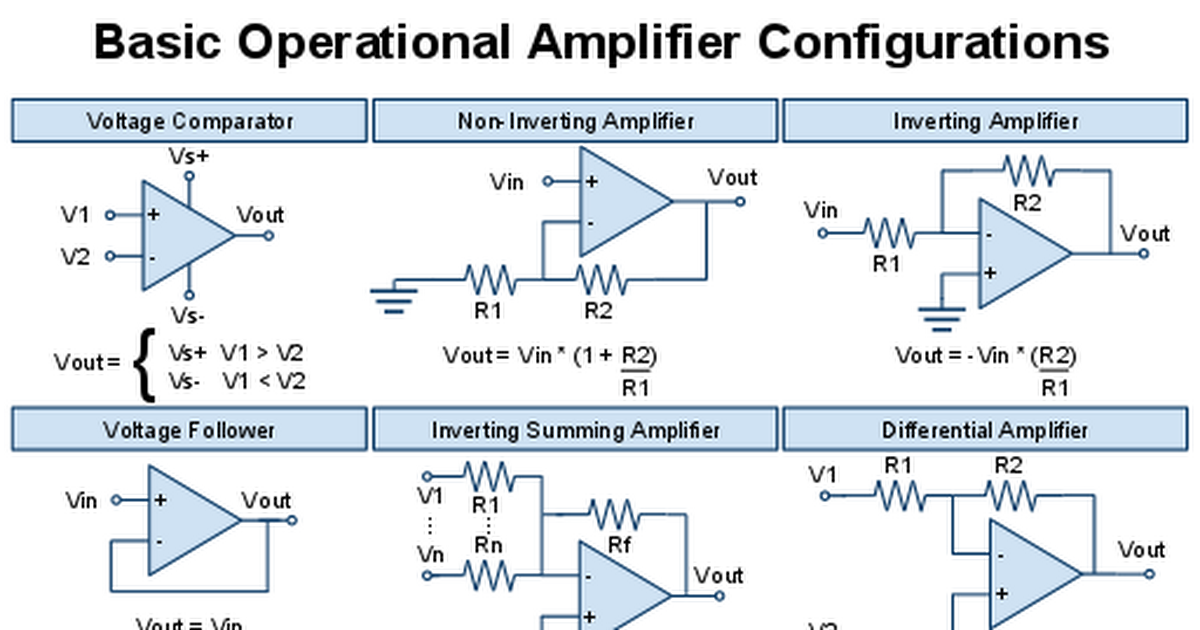

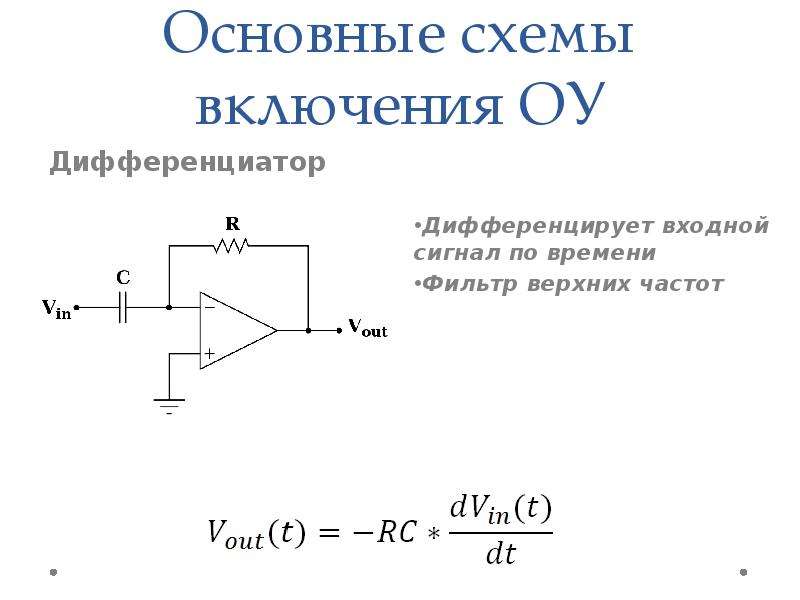

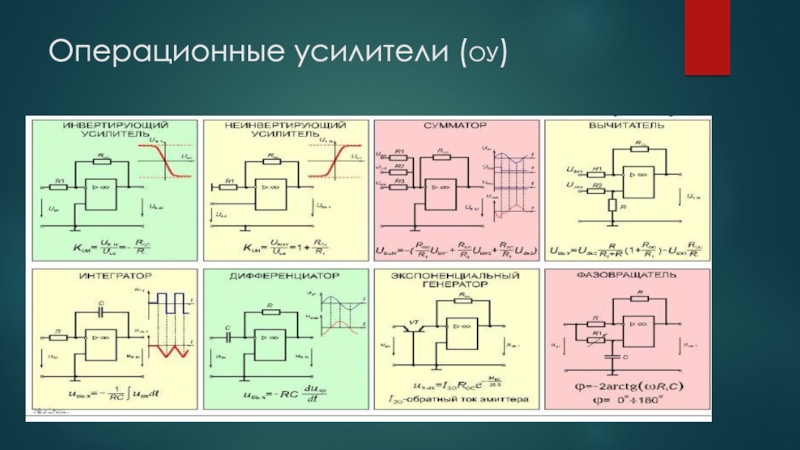

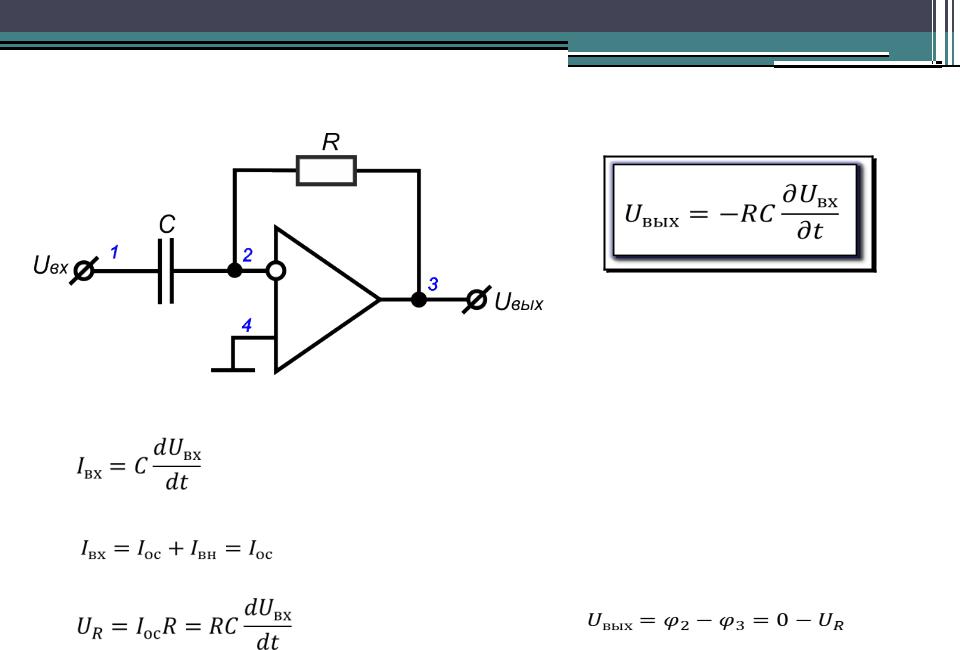

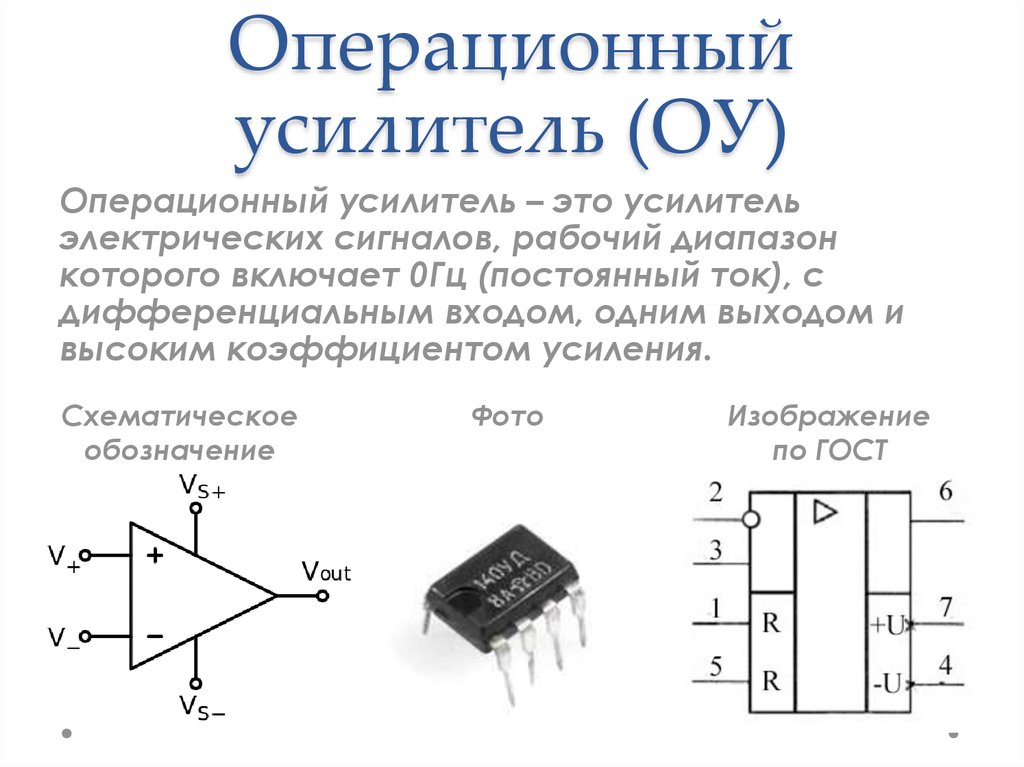

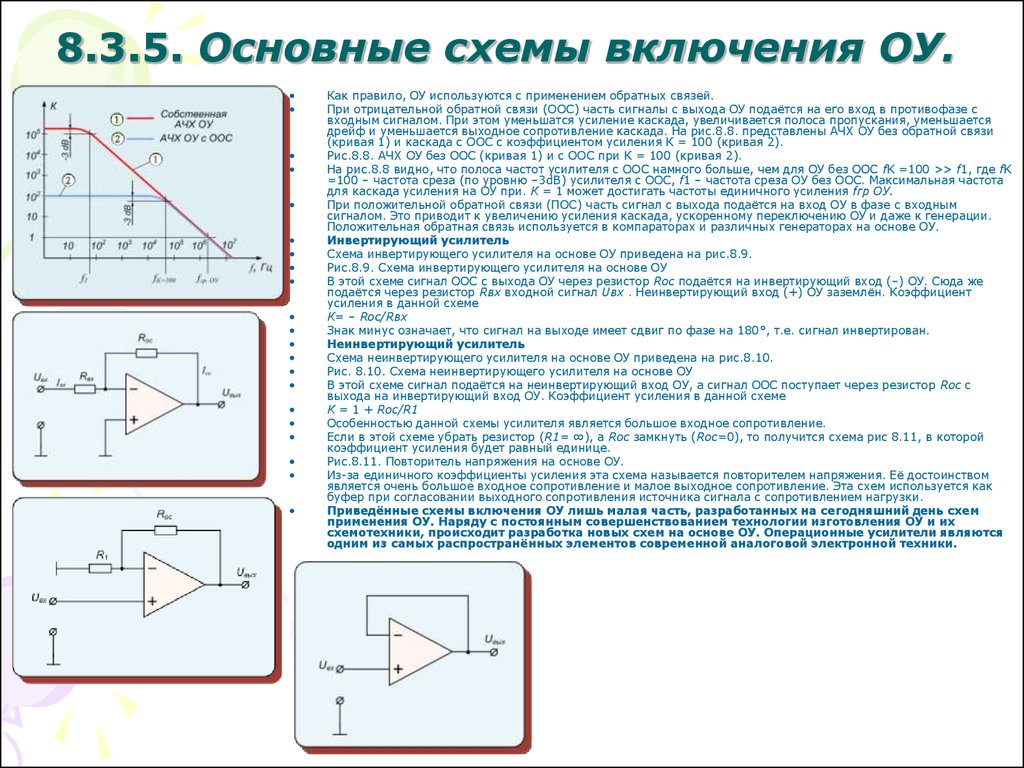

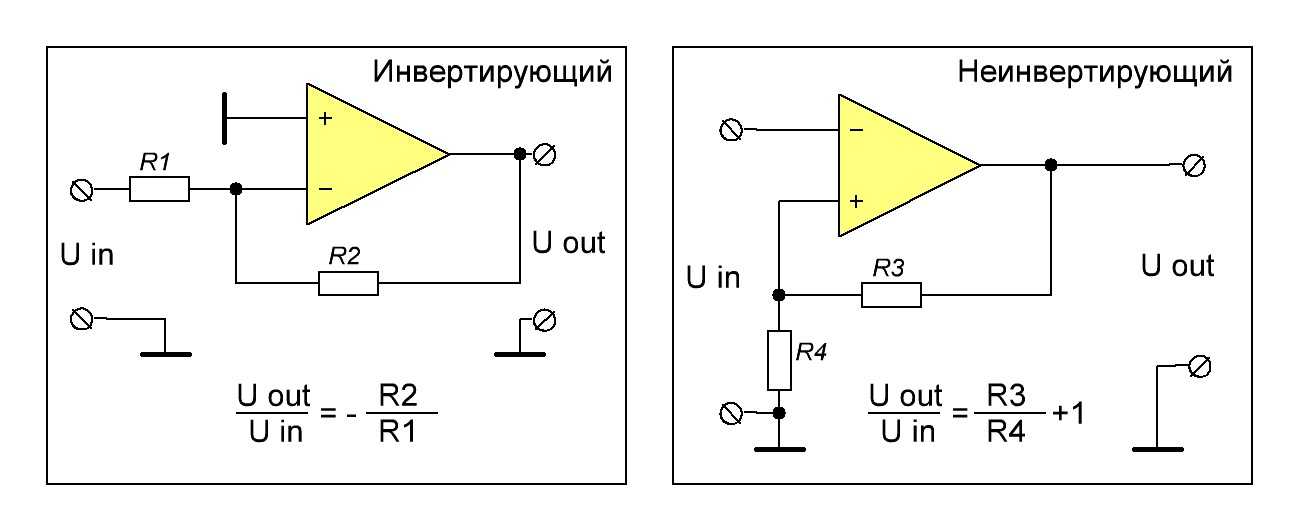

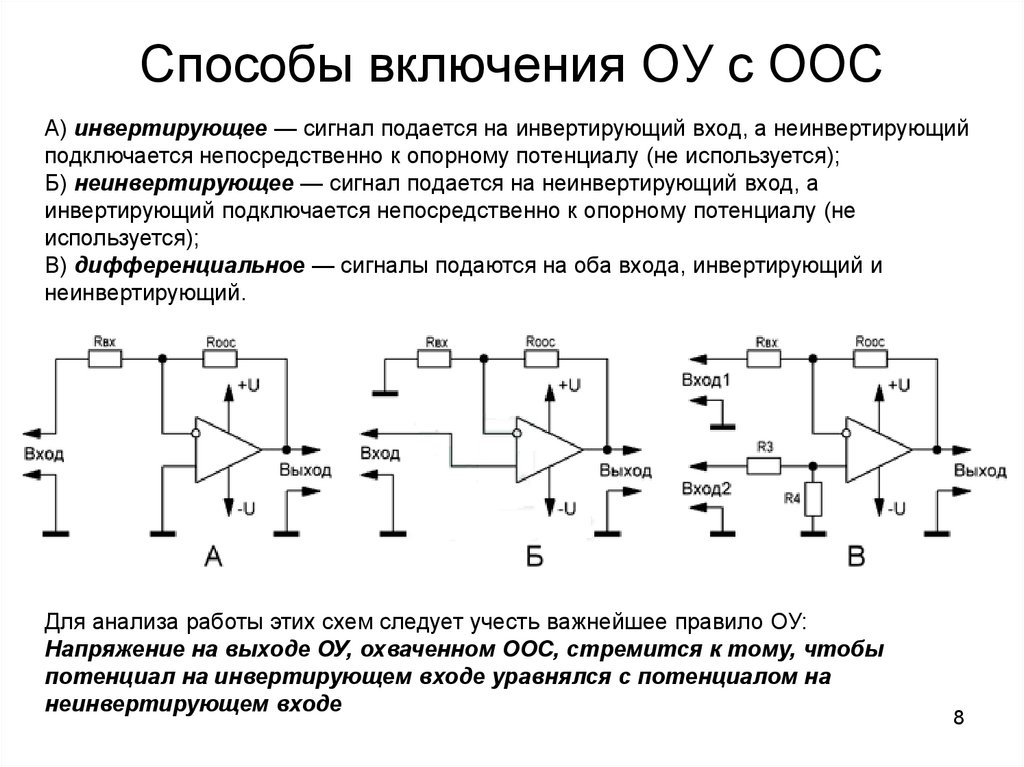

6 Основные схемы включения оу

6 Основные схемы включения оу В основе анализа схем на операционных усилителях лежат два следующих предположения.

Основываясь на этих предположениях, проведём анализ простейших усилительных схем на ОУ.

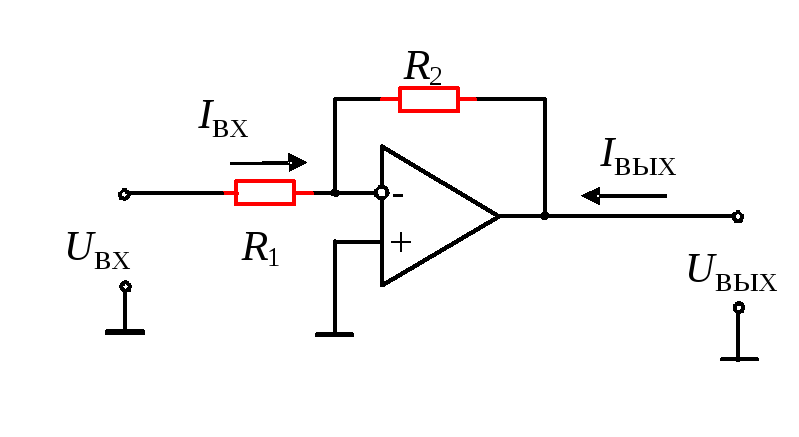

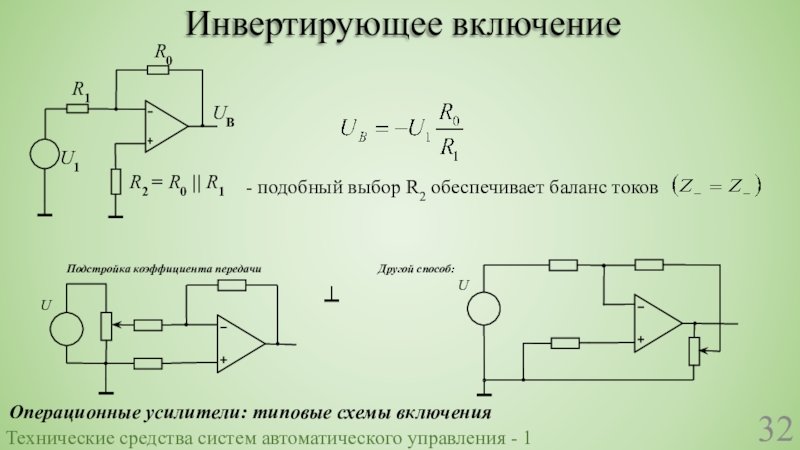

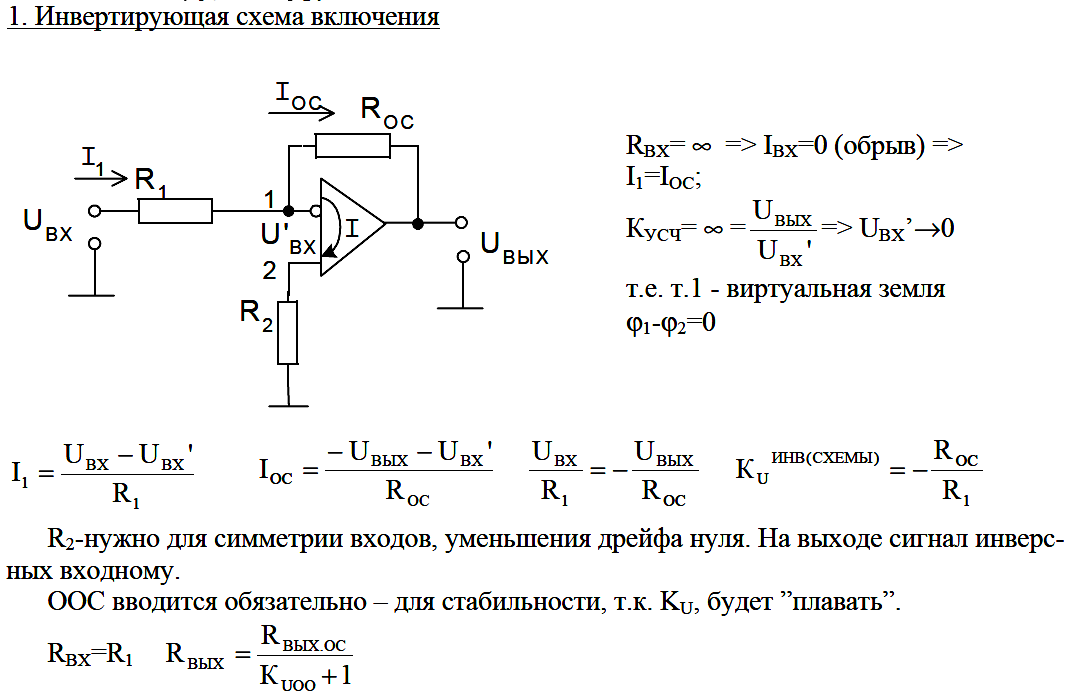

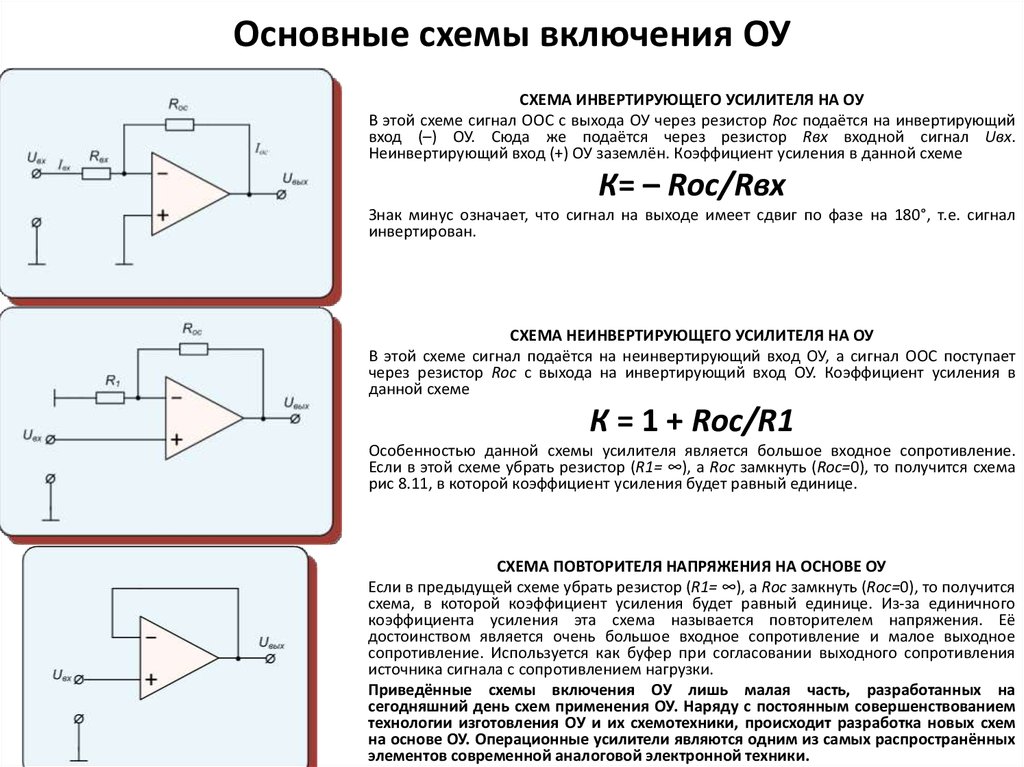

1.6.1 Инвертирующий усилитель

Схема инвертирующего усилителя показана на рисунке 8. Используя два указанных выше предположения, определим коэффициент усиления по напряжению инвертирующего усилителя.

Рисунок 8 – Инвертирующий усилитель

Резисторы R1 и R2 образуют цепь параллельной отрицательной обратной связи по напряжению. Поэтому в соответствии с принципом виртуального замыкания разность потенциалов между входами ОУ становится очень малой. Поскольку неинвертирующий вход заземлен, то и на инвертирующем входе появляется потенциал близкий к нулю. При этом входной ток I1, протекающий по резистору R1, составит I1=U1/R1

Поскольку вход ОУ имеет очень большое

сопротивление, то весь этот ток будет

протекать по резистору R2,

создавая падение

напряжения U2 = U1

۰R2/R1.

Здесь U1 = Uвх

, U2 = Uвых.

Поэтому

коэффициент усиления по напряжению K

оказывается равным К = –U2/U1.

Таким образом К

= –R2/R1.Знак

минус учитывает инверсию сигнала на

выходе усилителя. Входное сопротивление

усилителя Rвх = R1.

Выходное сопротивление очень мало.

Поскольку вход ОУ имеет очень большое

сопротивление, то весь этот ток будет

протекать по резистору R2,

создавая падение

напряжения U2 = U1

۰R2/R1.

Здесь U1 = Uвх

, U2 = Uвых.

Поэтому

коэффициент усиления по напряжению K

оказывается равным К = –U2/U1.

Таким образом К

= –R2/R1.Знак

минус учитывает инверсию сигнала на

выходе усилителя. Входное сопротивление

усилителя Rвх = R1.

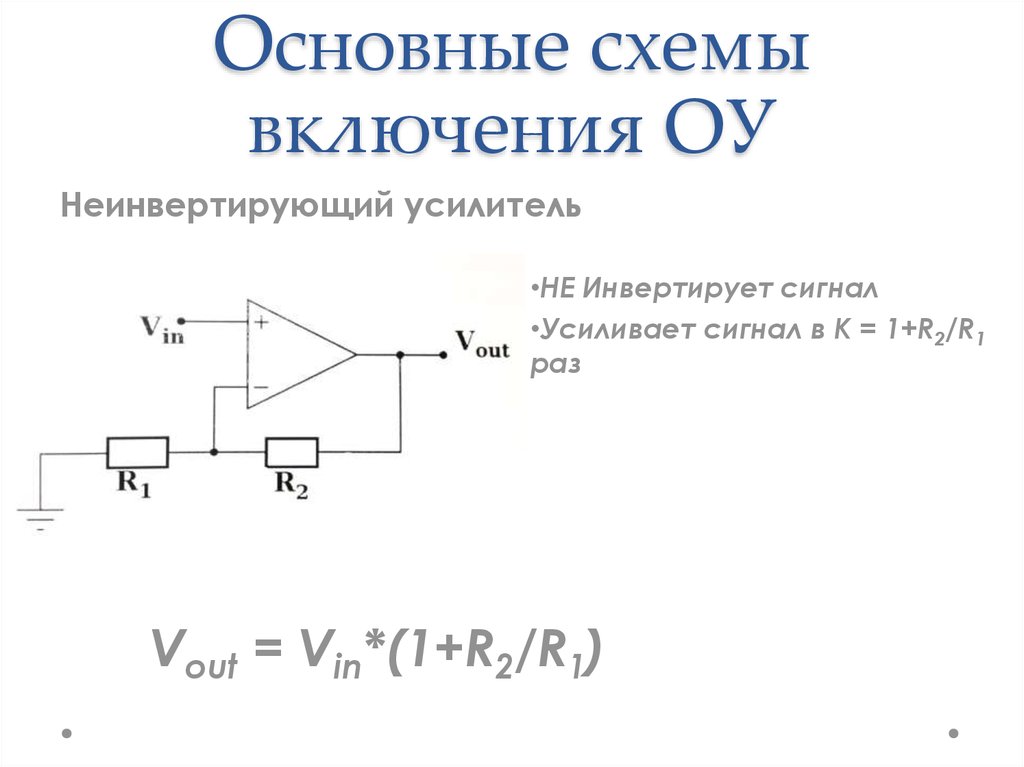

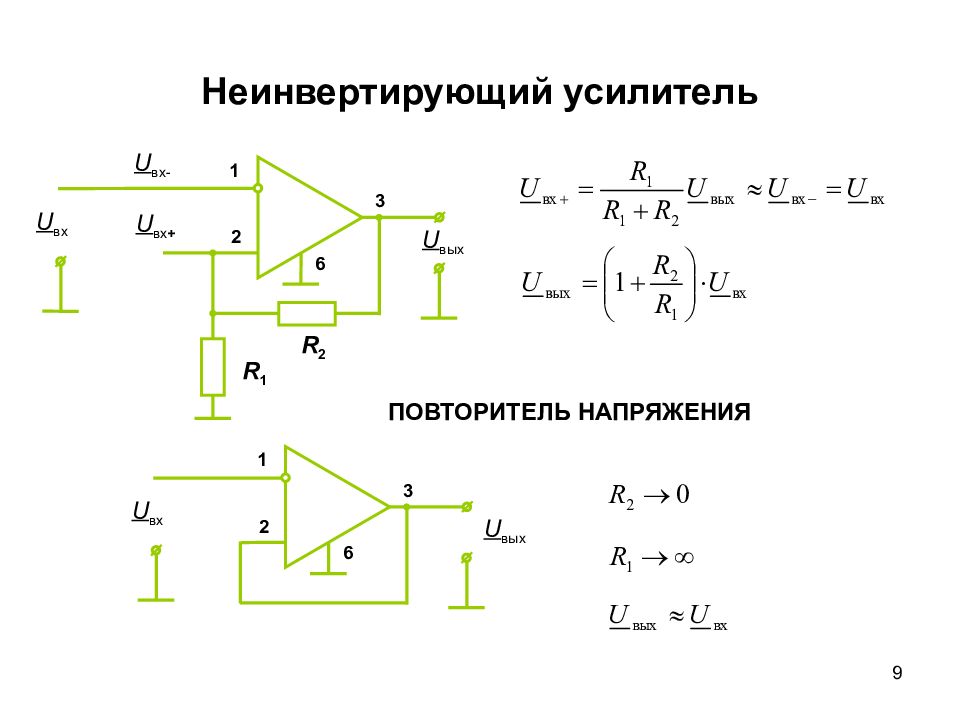

Выходное сопротивление очень мало. 1.6.2 Неинвертирующий усилитель

Схема неинвертирующего усилителя показана на рисунке 9.

Рисунок 9 – Схема неинвертирующего усилителя

Резисторы

R

1

и

R2

образуют

цепь последовательной отрицательной

обратной связи по напряжению, поэтому

в соответствии с принципом виртуального

замыкания разность потенциалов между

двумя входами очень мала, то есть на

инвертирующем входе будет такое же

напряжение, как и на неинвертирующем. Следовательно, через резистор R1

будет протекать ток I1 = U1 / R1.

В силу высокого входного сопротивления

такой же ток будет протекать по резистору

R2

и падение напряжения на нем составит

U2 = U1۰R2 / R1.

Выходное напряжение будет равно сумме

напряжений на инвертирующем входе и

падения напряжения на резисторе R2

, то

есть U2=U1(1+R2/R1).

Поэтому коэффициент усиления по

напряжению K

окажется равным

K=1+R

Следовательно, через резистор R1

будет протекать ток I1 = U1 / R1.

В силу высокого входного сопротивления

такой же ток будет протекать по резистору

R2

и падение напряжения на нем составит

U2 = U1۰R2 / R1.

Выходное напряжение будет равно сумме

напряжений на инвертирующем входе и

падения напряжения на резисторе R2

, то

есть U2=U1(1+R2/R1).

Поэтому коэффициент усиления по

напряжению K

окажется равным

K=1+R

Влияние напряжения смещения может быть исследовано по схеме замещения, представленной на рисунке 10. Напряжение смещения оказывается приложенным последовательно с входным напряжением. Таким образом, на выходе, как и входное напряжение, напряжение смещения будет увеличиваться в K раз.

Рисунок 10 – Схема замещения ОУ с отрицательной обратной связью с учетом влияния напряжения смещения

1.

7 Коррекция частотной характеристики оу

7 Коррекция частотной характеристики оу Вследствие наличия паразитных емкостей и многокаскадной структуры операционный усилитель по своим частотным свойствам аналогичен фильтру нижних частот высокого порядка. Типичная частотная характеристика коэффициента усиления Ko операционного усилителя без частотной коррекции изображена на рисунке 11. Выше частоты flчастотная характеристика определяется первым фильтром нижних частот с минимальной граничной частотой. Коэффициент усиления в этой области частот падает с ростом частоты (наклон составляет 20 дБ/декада), а фазовый сдвиг выходного напряжения U вых относительно входного Uд достигает φ = — 90°. Это значит, что выходное напряжение отстает по фазе от входного на 90°.

Рисунок 11 – Амплитудно-частотная и фазочастотная характеристики операционного усилителя (диаграмма Боде).

Выше

частоты f2

начинает действовать второй фильтр

нижних частот и коэффициент усиления

уменьшается сильнее (наклон 40 дБ/декада),

а фазовый сдвиг между Uд

и Uвых

достигает

φ = –180°. Это означает, что

отрицательная обратная связь, которая

осуществлялась подачей части выходного

напряжения на инвертирующий вход

усилителя, в этой частотной области

становится положительной. Как известно,

если имеется такая частота, для которой

фазовый сдвиг по цепи обратной связи

становится равным нулю (условие баланса

фаз), а коэффициент петлевого усиления

| K | >

1 (условие баланса амплитуд), в такой

усилительной системе могут возникнуть

автоколебания. Усилитель прекращает

выполнять свои функции, превратившись

в генератор. Коэффициент

Это означает, что

отрицательная обратная связь, которая

осуществлялась подачей части выходного

напряжения на инвертирующий вход

усилителя, в этой частотной области

становится положительной. Как известно,

если имеется такая частота, для которой

фазовый сдвиг по цепи обратной связи

становится равным нулю (условие баланса

фаз), а коэффициент петлевого усиления

| K | >

1 (условие баланса амплитуд), в такой

усилительной системе могут возникнуть

автоколебания. Усилитель прекращает

выполнять свои функции, превратившись

в генератор. Коэффициент

Для

предотвращения самовозбуждения при

наличии отрицательной обратной связи

в усилитель вводятся частотно-корректирующие

цепь. Для этого соединяют через конденсатор

выход и вход (коллектор и базу – для

биполярного транзистора) одного из

транзисторов, входящих в состав ОУ. Как

правило, такая цепь изменяет

амплитудно-частотную и фазочастотную

характеристики операционного усилителя

таким образом, что при

фазовый сдвиг не достигает 180

0..

Разность между 1800

и фазовым сдвигом на данной частоте

является запасом по фазе и от него

существенно зависит получаемый результат.

На рисунке 12 наглядно показано влияние

запаса по фазе на усилительные свойства

усилителя.

Как

правило, такая цепь изменяет

амплитудно-частотную и фазочастотную

характеристики операционного усилителя

таким образом, что при

фазовый сдвиг не достигает 180

0..

Разность между 1800

и фазовым сдвигом на данной частоте

является запасом по фазе и от него

существенно зависит получаемый результат.

На рисунке 12 наглядно показано влияние

запаса по фазе на усилительные свойства

усилителя.

Рисунок 12 – Импульсные переходные характеристики операционного усилителя, охваченного обратной связью, при различных значениях запаса по фазе

Наряду

со снижением полосы пропускания усилителя

частотная коррекция дает еще один

нежелательный эффект: скорость нарастания

выходного напряжения становится при

этом довольно малой величиной. Вследствие

ограниченного значения этой величины

при быстрых изменениях входного

напряжения возникают характерные

искажения сигнала, которые не могут

быть устранены путем введения отрицательной

обратной связи.

Базовый цифровой ввод/вывод: ползунковый переключатель, кнопка и светодиод

Базовые устройства ввода: ползунковый переключатель и кнопка

Схемы часто требуют входных данных, поступающих непосредственно от пользователей (в отличие от входных данных, поступающих от других устройств). Устройства пользовательского ввода могут иметь различные формы, в том числе клавиатуры (как на ПК), кнопки (как на калькуляторе или телефоне), поворотные диски, переключатели и рычаги и т. д. Платы Digilent® включают в себя несколько устройств ввода, обычно включая кнопки. и ползунковые переключатели.

Ползунковые переключатели также известны как однопозиционные двухполюсные переключатели (STDP), поскольку существует только один переключатель (или положение), но доступны два положения (или полюса) (полюс — это электрический контакт, к которому может быть подключен переключатель). установить контакт). Эти переключатели могут быть настроены на вывод либо Vdd (когда исполнительный механизм находится ближе всего к краю платы), либо ЗЕМЛЯ . Кнопочные переключатели также известны как «мгновенные» контактные кнопки, потому что они контактируют только при активном нажатии — они выводят

Основные устройства вывода: светодиод

Схемы часто требуют, чтобы устройства вывода сообщали пользователю о своем состоянии. Примеры электронных устройств вывода включают компьютерные мониторы, LCD буквенно-цифровые панели (как на калькуляторе), небольшие лампы или светодиоды ( LED ) и т. д. Платы Digilent включают в себя различные устройства вывода, но все они включают некоторое количество отдельных LED , и семисегментные дисплеи LED , которые могут отображать цифры 0-9 в каждой позиции цифры (каждый сегмент семисегментного дисплея

содержит один светодиод ). Светодиоды представляют собой полупроводниковые приборы с двумя выводами, проводящие ток только в одном направлении (от анода к катоду). Маленький 9Чипы 0025 LED закреплены внутри пластикового корпуса и излучают свет заданной частоты (КРАСНЫЙ, ЖЕЛТЫЙ и т. д.), когда через них проходит небольшой электрический ток (обычно от 10 мА до 25 мА).

Маленький 9Чипы 0025 LED закреплены внутри пластикового корпуса и излучают свет заданной частоты (КРАСНЫЙ, ЖЕЛТЫЙ и т. д.), когда через них проходит небольшой электрический ток (обычно от 10 мА до 25 мА).

Отдельные светодиоды обозначаются ссылочным обозначением «LD__» на платах Digilent, а семисегментные дисплеи обозначаются ссылочным обозначением «DSP». Отдельные светодиоды обычно управляются напрямую от чипа Xilinx® на платах Digilent, но для дисплеев

Светодиоды не включатся, если их аноды не имеют минимального напряжения выше их катодов — обычно около двух вольт. Если к светодиоду приложено меньше минимального порогового напряжения, он останется темным. В приведенном ниже примере для включения светодиода требуется падение напряжения 2 В, при этом на резисторе остается падение напряжения 1,3 В. Таким образом, резистор на 130 Ом требуется, чтобы в цепи протекал ток 10 мА ($3,3 В — 2 В = 1,3 В$ и 1,3 В / 130 Ом = 10 мА).

В приведенном ниже примере для включения светодиода требуется падение напряжения 2 В, при этом на резисторе остается падение напряжения 1,3 В. Таким образом, резистор на 130 Ом требуется, чтобы в цепи протекал ток 10 мА ($3,3 В — 2 В = 1,3 В$ и 1,3 В / 130 Ом = 10 мА).

Важные идеи:

-

Переключатели и кнопки обычно используются в качестве устройств ввода для цифровых систем. Выход схемы можно изменить между Vdd и Gnd, нажав/отпустив кнопку или сдвинув переключатель. Однако соответствие между выходным напряжением и нажатием/отпусканием кнопки или скольжением переключателя определяется фактической конфигурацией схемы.

-

Светодиод обычно используется как простое цифровое устройство вывода. Обычно на плате Digilent высокое напряжение загорается, а низкое выключает.

узнать, основы, схемы, базовый цифровой-io, ползунковый переключатель, нажать кнопку, светодиод

Схемы переключения со сверхмалым энергопотреблением на основе генератора бинарных последовательностей с импульсными нейронами схемы с инженерной точки зрения.

Интерес не ограничивается исследованиями в области алгоритмов, но также распространяется на исследования в области аппаратного обеспечения, целью которых является внедрение схем и систем, основанных на нейронных технологиях, с более низким энергопотреблением и малой задержкой 9.0076 1,2,3,4,5,6,7,8 . Тем не менее, большая часть текущих исследований в области аппаратного обеспечения нацелена на понимание биологических процессов или реализацию алгоритма машинного обучения и может не полностью использовать огромный потенциал биологических нейронных цепей.

Интерес не ограничивается исследованиями в области алгоритмов, но также распространяется на исследования в области аппаратного обеспечения, целью которых является внедрение схем и систем, основанных на нейронных технологиях, с более низким энергопотреблением и малой задержкой 9.0076 1,2,3,4,5,6,7,8 . Тем не менее, большая часть текущих исследований в области аппаратного обеспечения нацелена на понимание биологических процессов или реализацию алгоритма машинного обучения и может не полностью использовать огромный потенциал биологических нейронных цепей. С инженерной точки зрения биологические нейронные цепи представляют собой превосходные системы управления, которые контролируют движения тела с низким энергопотреблением и малой задержкой. Он компрометирует компромисс между энергопотреблением и временем отклика за счет автоматизации и децентрализации индивидуального управления двигателем, а не быстрого централизованного контроля движений тела с обратной связью. Существует два типа такого децентрализованного управления моторикой: один с использованием рефлексов, которые демонстрируют фиксированную реакцию на конкретный сенсорный вход, а другой с использованием центрального генератора паттернов, который приводит в действие двигательные органы в соответствии с запрограммированным временным паттерном 9,10 . В то время как рефлекторная цепь представляет собой относительно простую систему ввода-вывода, центральный генератор паттернов представляет собой нейронную сеть, которая автономно генерирует временные паттерны без ввода (рис. 1а) и отвечает за сложный и ритмичный двигательный контроль, такой как ходьба, жевание, дыхание. , и глотание 11,12 . Генератор центрального шаблона обычно использует пиковые сигналы, неоднородные по времени. Это существенно отличается от тактового сигнала в цифровых схемах, который тикает с фиксированным периодом, не зависящим от окружающей среды. По сравнению с однородным во времени тактовым сигналом всплески с разновременными синхронизациями могут сохранить избыточность и, следовательно, больше подходят для работы в реальном времени.

В то время как рефлекторная цепь представляет собой относительно простую систему ввода-вывода, центральный генератор паттернов представляет собой нейронную сеть, которая автономно генерирует временные паттерны без ввода (рис. 1а) и отвечает за сложный и ритмичный двигательный контроль, такой как ходьба, жевание, дыхание. , и глотание 11,12 . Генератор центрального шаблона обычно использует пиковые сигналы, неоднородные по времени. Это существенно отличается от тактового сигнала в цифровых схемах, который тикает с фиксированным периодом, не зависящим от окружающей среды. По сравнению с однородным во времени тактовым сигналом всплески с разновременными синхронизациями могут сохранить избыточность и, следовательно, больше подходят для работы в реальном времени.

Генератор бинарных шаблонов. ( a ) Центральный генератор паттернов в нейронной сети человека, который управляет биологическими моторами. ( b ) Концепция генератора искусственных шаблонов, который управляет переключающими цепями для преобразования напряжения постоянного тока в постоянный. ( c ) Генератор двоичных последовательностей, специально разработанный генератор последовательностей для управления коммутационными цепями. Он состоит из цепочки генераторов времени ожидания с широким диапазоном предварительно запрограммированных значений времени ожидания. ( d ) Пиковые или битовые выходные сигналы от генератора двоичных последовательностей. Длина битового сигнала соответствует предварительно запрограммированному времени ожидания каждого генератора времени ожидания. Этот битовый сигнал непосредственно используется для управления затвором в схемах переключения.

( c ) Генератор двоичных последовательностей, специально разработанный генератор последовательностей для управления коммутационными цепями. Он состоит из цепочки генераторов времени ожидания с широким диапазоном предварительно запрограммированных значений времени ожидания. ( d ) Пиковые или битовые выходные сигналы от генератора двоичных последовательностей. Длина битового сигнала соответствует предварительно запрограммированному времени ожидания каждого генератора времени ожидания. Этот битовый сигнал непосредственно используется для управления затвором в схемах переключения.

Изображение полного размера

К настоящему времени искусственно изготовлено несколько центральных генераторов паттернов в виде электронных схем для управления приводами роботов 13,14,15,16,17 , биологические мышцы 18 и физиологические системы 19 . Однако есть несколько примеров их применения для управления более общими электронными схемами, такими как схемы переключения (рис. 1b). Схема переключения состоит из нескольких транзисторных переключателей, которые быстро включаются и выключаются, чтобы обеспечить точную усредненную функцию. Они являются важными строительными блоками в различных областях электроники, включая устройства Интернета вещей (IoT). Параллельно с искусственными центральными генераторами шаблонов для исполнительных механизмов и биологических систем генераторы шаблонов для коммутационных цепей могут обеспечить энергосберегающую схему управления в реальном времени в будущих устройствах IoT.

1b). Схема переключения состоит из нескольких транзисторных переключателей, которые быстро включаются и выключаются, чтобы обеспечить точную усредненную функцию. Они являются важными строительными блоками в различных областях электроники, включая устройства Интернета вещей (IoT). Параллельно с искусственными центральными генераторами шаблонов для исполнительных механизмов и биологических систем генераторы шаблонов для коммутационных цепей могут обеспечить энергосберегающую схему управления в реальном времени в будущих устройствах IoT.

В этом исследовании мы сконструировали генератор искусственных образов, оптимизированный для коммутационных цепей, а не для приводов или биологических систем. Генераторы паттернов в предыдущих исследованиях часто использовали кодирование с частотой всплесков, которое передает аналоговую информацию с помощью всплесков частоты. С другой стороны, переключающим схемам требуется только временная информация о событии переключения, и поэтому более удобно использовать временное кодирование, которое передает информацию в виде временной привязки каждого выброса. Одним из основных компонентов временного кодирования является генератор времени ожидания, который генерирует пиковый сигнал по истечении предварительно запрограммированного времени ожидания с момента появления входного напряжения. Кроме того, необходим широкий диапазон времени ожидания, поскольку схемы переключения иногда меняются быстро, порядка наносекунд, в то время как большую часть времени ожидания требуется для экономии энергии. В этом исследовании мы экспериментально продемонстрировали этот широкий диапазон времени ожидания от 100 нс до 100 мс на шести порядках. Чтобы сгенерировать произвольное время ожидания и выходной импульсный сигнал, была принята методика импульсных нейронных цепей с функцией интегрирования и активации 9.0076 20,21,22,23,24 . Схемы импульсных нейронов были оптимизированы исключительно с целью генерации времени ожидания на основе технологии комплементарных оксидов металлов и полупроводников (CMOS), и никакие другие биологические функции не были реализованы намеренно.

Одним из основных компонентов временного кодирования является генератор времени ожидания, который генерирует пиковый сигнал по истечении предварительно запрограммированного времени ожидания с момента появления входного напряжения. Кроме того, необходим широкий диапазон времени ожидания, поскольку схемы переключения иногда меняются быстро, порядка наносекунд, в то время как большую часть времени ожидания требуется для экономии энергии. В этом исследовании мы экспериментально продемонстрировали этот широкий диапазон времени ожидания от 100 нс до 100 мс на шести порядках. Чтобы сгенерировать произвольное время ожидания и выходной импульсный сигнал, была принята методика импульсных нейронных цепей с функцией интегрирования и активации 9.0076 20,21,22,23,24 . Схемы импульсных нейронов были оптимизированы исключительно с целью генерации времени ожидания на основе технологии комплементарных оксидов металлов и полупроводников (CMOS), и никакие другие биологические функции не были реализованы намеренно. В результате они достигли чрезвычайно низкого энергопотребления порядка 100 фДж на всплеск, что соответствует минимальному среднему энергопотреблению 1,2 пВт, что является самым низким показателем среди прошлых экспериментальных демонстраций 20,21,22,23,24 . Для управления схемой переключения вход и выход вышеуказанной схемы импульсных нейронов CMOS были подключены к схеме защелки установки-сброса для генерации двоичной формы волны с длиной предварительно запрограммированного времени ожидания, как показано на рис. 1c,d. Затем эта бинарная форма волны просто подавалась на затворы транзисторов для асинхронного управления схемами переключения. Эта простая схема «генератора двоичных последовательностей» может быть применена к универсальным коммутационным схемам и может обеспечить управление в реальном времени при чрезвычайно малой мощности. Для демонстрации мы использовали этот генератор бинарных шаблонов для управления схемой преобразования напряжения постоянного тока, которая необходима для устройств IoT, и показали с помощью моделирования, что он может генерировать широкий диапазон выходной мощности от 8,36 нВт до 1,16 мВт примерно при 9КПД 0%, с незначительным энергопотреблением управления примерно на три порядка меньше, чем выходная мощность.

В результате они достигли чрезвычайно низкого энергопотребления порядка 100 фДж на всплеск, что соответствует минимальному среднему энергопотреблению 1,2 пВт, что является самым низким показателем среди прошлых экспериментальных демонстраций 20,21,22,23,24 . Для управления схемой переключения вход и выход вышеуказанной схемы импульсных нейронов CMOS были подключены к схеме защелки установки-сброса для генерации двоичной формы волны с длиной предварительно запрограммированного времени ожидания, как показано на рис. 1c,d. Затем эта бинарная форма волны просто подавалась на затворы транзисторов для асинхронного управления схемами переключения. Эта простая схема «генератора двоичных последовательностей» может быть применена к универсальным коммутационным схемам и может обеспечить управление в реальном времени при чрезвычайно малой мощности. Для демонстрации мы использовали этот генератор бинарных шаблонов для управления схемой преобразования напряжения постоянного тока, которая необходима для устройств IoT, и показали с помощью моделирования, что он может генерировать широкий диапазон выходной мощности от 8,36 нВт до 1,16 мВт примерно при 9КПД 0%, с незначительным энергопотреблением управления примерно на три порядка меньше, чем выходная мощность. Таким образом, управление коммутационными цепями с помощью генератора двоичных последовательностей обеспечивает мощное средство для смягчения ограничений по мощности и реализации различных функций в оконечных устройствах IoT с автономным питанием.

Таким образом, управление коммутационными цепями с помощью генератора двоичных последовательностей обеспечивает мощное средство для смягчения ограничений по мощности и реализации различных функций в оконечных устройствах IoT с автономным питанием.

В этой статье мы сначала подробно объясним концепцию генератора двоичных последовательностей, который представляет собой специально разработанный генератор последовательностей для управления коммутационными схемами. Затем мы визуализируем, как это работает, демонстрируя схему переключения для преобразования напряжения постоянного тока в постоянный. Наконец, моделирование и эксперименты показаны для нейронных цепей КМОП, которые являются важными строительными блоками для генератора бинарных последовательностей.

Генератор бинарных шаблонов

Искусственные центральные генераторы шаблонов ранее изучались в области робототехники 13,14,15,16,17 . Там информация передается в виде аналогового значения частоты всплесков (кодирование скорости всплесков), которое можно использовать для управления исполнительными механизмами роботов. Потребляемая мощность зависит от приводной мощности исполнительных механизмов, и нет необходимости снижать до предела потребляемую мощность управления. Масштаб времени управления также определяется скоростью движения робота, поэтому нет необходимости в большом диапазоне времени управления вплоть до наносекунд. С другой стороны, если для коммутационных цепей должен использоваться генератор искусственных последовательностей, требуется чрезвычайно низкое энергопотребление и широкий диапазон масштабов времени вплоть до наносекунд. Следовательно, для управления коммутационными схемами необходим новый генератор искусственных последовательностей, отвечающий всем этим требованиям.

Потребляемая мощность зависит от приводной мощности исполнительных механизмов, и нет необходимости снижать до предела потребляемую мощность управления. Масштаб времени управления также определяется скоростью движения робота, поэтому нет необходимости в большом диапазоне времени управления вплоть до наносекунд. С другой стороны, если для коммутационных цепей должен использоваться генератор искусственных последовательностей, требуется чрезвычайно низкое энергопотребление и широкий диапазон масштабов времени вплоть до наносекунд. Следовательно, для управления коммутационными схемами необходим новый генератор искусственных последовательностей, отвечающий всем этим требованиям.

Для решения этой проблемы был построен генератор двоичных образов на основе схемы управления временным кодированием. Ранее аналогичные бинарные сигналы также использовались в некоторых исследованиях по управлению роботами 13,14 . Чтобы сконструировать генератор бинарных сигналов, мы использовали схемы импульсных нейронов CMOS с функцией интегрирования и активации, которые могут генерировать импульс после запрограммированного времени ожидания от начала входного ступенчатого напряжения. Подробности будут обсуждаться в последующих разделах. Каждая цепь импульсных нейронов объединена со схемой защелки установки-сброса, простейшей схемой памяти, как показано на рис. 1c, d. Когда схема защелки включается входным импульсным сигналом, схема защелки генерирует выходное напряжение 1 В. Затем это выходное напряжение подается на последующую схему импульсного нейрона, что приводит к выходу импульсного сигнала после предварительно запрограммированного ожидания. время. Этот выходной выброс из цепи импульсного нейрона сбрасывает начальную схему защелки и одновременно включает схему защелки следующего этапа. Повторяя эту операцию, импульсные сигналы генерируются через произвольные интервалы времени ( V A , V C и V E на рис. 1c,d), а двоичный шаблон может быть сгенерирован на выходе схем защелок ( V B и В Д ). Затем этот двоичный код можно использовать для управления транзисторными затворами в схемах переключения.

Подробности будут обсуждаться в последующих разделах. Каждая цепь импульсных нейронов объединена со схемой защелки установки-сброса, простейшей схемой памяти, как показано на рис. 1c, d. Когда схема защелки включается входным импульсным сигналом, схема защелки генерирует выходное напряжение 1 В. Затем это выходное напряжение подается на последующую схему импульсного нейрона, что приводит к выходу импульсного сигнала после предварительно запрограммированного ожидания. время. Этот выходной выброс из цепи импульсного нейрона сбрасывает начальную схему защелки и одновременно включает схему защелки следующего этапа. Повторяя эту операцию, импульсные сигналы генерируются через произвольные интервалы времени ( V A , V C и V E на рис. 1c,d), а двоичный шаблон может быть сгенерирован на выходе схем защелок ( V B и В Д ). Затем этот двоичный код можно использовать для управления транзисторными затворами в схемах переключения. Здесь комбинация схемы защелки и цепи импульсного нейрона называется генератором времени ожидания (пунктирный квадрат на рис. 1c). Следует отметить, что цепь импульсных нейронов в генераторе двоичных последовательностей напрямую связана со схемой защелки установки-сброса и, следовательно, должна быть совместима с логическими схемами КМОП. В частности, он должен работать при том же напряжении питания 1 В, что и логические схемы, и должен выдавать всплески с достаточно коротким временем нарастания и временем спада в масштабе наносекунд. Все эти требования удовлетворяются специальной конструкцией КМОП-нейронных цепей, как показано ниже.

Здесь комбинация схемы защелки и цепи импульсного нейрона называется генератором времени ожидания (пунктирный квадрат на рис. 1c). Следует отметить, что цепь импульсных нейронов в генераторе двоичных последовательностей напрямую связана со схемой защелки установки-сброса и, следовательно, должна быть совместима с логическими схемами КМОП. В частности, он должен работать при том же напряжении питания 1 В, что и логические схемы, и должен выдавать всплески с достаточно коротким временем нарастания и временем спада в масштабе наносекунд. Все эти требования удовлетворяются специальной конструкцией КМОП-нейронных цепей, как показано ниже.

Применение к схеме преобразователя напряжения

Чтобы наглядно представить, как генератор двоичных последовательностей работает в практической системе, на рис. 2 показано моделирование схемы переключения для преобразования напряжения постоянного тока в постоянный. Преобразование напряжения постоянного тока в постоянный ток важный компонент для цепей электропитания, особенно для устройства сбора энергии IoT 25 , где изменяющаяся во времени генерируемая мощность преобразуется в повышающе-понижающее преобразование с помощью катушки индуктивности и сохраняется в конденсаторе при определенном уровне напряжения (рис. 2a). Работа схемы состоит из двух периодов: первый период, когда включены переключатели S1 и S3 (красная стрелка), и второй период, когда включен только переключатель S2 (зеленая стрелка). В первый период заряд, накопленный в первичном конденсаторе ( C 1 ) течет на землю через S1 и S3, а электростатическая энергия C 1 преобразуется в энергию магнитного потока индуктора. Во втором периоде ток течет от земли к вторичному конденсатору ( C 2 ) через S2, и энергия магнитного потока преобразуется в электростатическую энергию C 2 .

2a). Работа схемы состоит из двух периодов: первый период, когда включены переключатели S1 и S3 (красная стрелка), и второй период, когда включен только переключатель S2 (зеленая стрелка). В первый период заряд, накопленный в первичном конденсаторе ( C 1 ) течет на землю через S1 и S3, а электростатическая энергия C 1 преобразуется в энергию магнитного потока индуктора. Во втором периоде ток течет от земли к вторичному конденсатору ( C 2 ) через S2, и энергия магнитного потока преобразуется в электростатическую энергию C 2 .

Пример применения генератора бинарных шаблонов. ( а ) Блок-схема схемы преобразователя напряжения постоянного тока, состоящего из катушки индуктивности и нескольких переключателей. ( b ) Принципиальная схема смоделированной схемы преобразователя напряжения постоянного тока, где операция переключения управляется генератором двоичных последовательностей. Генератор бинарных паттернов состоит из цепи импульсных нейронов, определяющей период переключения, и двух генераторов времени ожидания для последовательностей переключения. Топология схемы преобразователя напряжения постоянного тока представляет собой типичный повышающе-понижающий преобразователь с дросселем 200 мГн. ( c ) Форма волны напряжения или тока генератора двоичных последовательностей и схемы преобразователя напряжения постоянного тока. ( d ) Формы сигналов генератора двоичных последовательностей и напряжения вокруг переключателя S 1 . Промежуток времени соответствует синей заштрихованной области на (c). ( e ) Моделируемая выходная мощность и мощность управления как функция входной мощности, когда В C1 составляет около 3 В, а В C2 составляет около 5 В. Входная мощность изменяется путем изменения период В СПК1 от 3 с до 50 мкс. Мощность управления пренебрежимо мала, на несколько порядков меньше входной или выходной мощности.

Генератор бинарных паттернов состоит из цепи импульсных нейронов, определяющей период переключения, и двух генераторов времени ожидания для последовательностей переключения. Топология схемы преобразователя напряжения постоянного тока представляет собой типичный повышающе-понижающий преобразователь с дросселем 200 мГн. ( c ) Форма волны напряжения или тока генератора двоичных последовательностей и схемы преобразователя напряжения постоянного тока. ( d ) Формы сигналов генератора двоичных последовательностей и напряжения вокруг переключателя S 1 . Промежуток времени соответствует синей заштрихованной области на (c). ( e ) Моделируемая выходная мощность и мощность управления как функция входной мощности, когда В C1 составляет около 3 В, а В C2 составляет около 5 В. Входная мощность изменяется путем изменения период В СПК1 от 3 с до 50 мкс. Мощность управления пренебрежимо мала, на несколько порядков меньше входной или выходной мощности. ( f ) Смоделированная эффективность преобразования мощности (отношение выходной мощности к входной мощности) как функция выходной мощности, которая остается относительно высокой до чрезвычайно низкого уровня выходной мощности. ( г ) Классификация управляющей мощности (2,23 нВт) при входной мощности 84 мкВт, что соответствует точке со сплошным кружком на ( и ). Потребляемая мощность генератора бинарных образов («Нейронов») достаточно мала, даже меньше, чем логическая схема.

( f ) Смоделированная эффективность преобразования мощности (отношение выходной мощности к входной мощности) как функция выходной мощности, которая остается относительно высокой до чрезвычайно низкого уровня выходной мощности. ( г ) Классификация управляющей мощности (2,23 нВт) при входной мощности 84 мкВт, что соответствует точке со сплошным кружком на ( и ). Потребляемая мощность генератора бинарных образов («Нейронов») достаточно мала, даже меньше, чем логическая схема.

Изображение с полным размером

Для управления этой операцией переключения двоичные напряжения от генератора двоичных последовательностей подавались на электроды затворов полевых транзисторов металл-оксид-полупроводник (МОП-транзисторы), как показано на рис. 2b. Двоичный шаблон ( V BIT2 ) был сгенерирован из пиковых сигналов V SPK1 и V SPK2 , как показано на рис. 2c, и использовался для управления воротами S1, S2 и S3. Во-первых, В SPK1 генерируется в определенный период, например 300 мкс, схемой пикового нейрона первой ступени, а В SPK2 генерируется через 30 мкс после В SPK1 9012 SPK1. генератор времени ожидания. Затем созданный двоичный код V BIT2 инвертировался инвертором и использовался для управления воротами S2. При этом уровень напряжения V BIT2 был повышен с 1 до 2 В с помощью переключателя уровня и использовался для управления затвором S3. Для управления напряжением затвора ( В S1 ) S1, который подключен к стороне высокого напряжения в схеме, был сгенерирован бинарный шаблон ( В BIT3 ) из В SPK2 и дополнительный пиковый сигнал ( В СПК3 ). Когда V BIT3 включен, V OFF опущен, V S1 подтянут, а S1 выключен (рис. 2г). С другой стороны, когда V BIT2 включен, V S1 опущен, а S1 включен.

Во-первых, В SPK1 генерируется в определенный период, например 300 мкс, схемой пикового нейрона первой ступени, а В SPK2 генерируется через 30 мкс после В SPK1 9012 SPK1. генератор времени ожидания. Затем созданный двоичный код V BIT2 инвертировался инвертором и использовался для управления воротами S2. При этом уровень напряжения V BIT2 был повышен с 1 до 2 В с помощью переключателя уровня и использовался для управления затвором S3. Для управления напряжением затвора ( В S1 ) S1, который подключен к стороне высокого напряжения в схеме, был сгенерирован бинарный шаблон ( В BIT3 ) из В SPK2 и дополнительный пиковый сигнал ( В СПК3 ). Когда V BIT3 включен, V OFF опущен, V S1 подтянут, а S1 выключен (рис. 2г). С другой стороны, когда V BIT2 включен, V S1 опущен, а S1 включен. Таким образом, уровень напряжения двоичной комбинации правильно преобразуется и используется для управления затвором, что делает схему переключения чрезвычайно простой и маломощной.

Таким образом, уровень напряжения двоичной комбинации правильно преобразуется и используется для управления затвором, что делает схему переключения чрезвычайно простой и маломощной.

При изменении входной мощности этой схемы от 9,28 нВт до 1,33 мВт путем изменения периода В SPK1 от 3 с до 50 мкс, выходная мощность изменялась почти пропорционально от 8,36 нВт до 1,16 мВт (рис. 2д), а общий КПД составлял около 90% (рис. 2е). Сравнение с предыдущими исследованиями в дополнительном примечании 1 показывает, что преобразователь с генератором двоичных последовательностей поддерживает более высокую эффективность, чем предыдущие, без ухудшения выходной мощности до 8,36 нВт. Высокий КПД при малой выходной мощности обусловлен главным образом тем, что потребляемая мощность схемы управления была на 2–4 порядка меньше выходной мощности во всем диапазоне, например, 17,5 пВт при выходной мощности 8,36 нВт и 114 нВт при выходная мощность 1,16 мВт (рис. 2д). В реальных IoT-устройствах необходимо реализовать различные схемы управления, но пока ими можно управлять с помощью генератора двоичных шаблонов, можно не беспокоиться о накладных расходах управляющей мощности даже при чрезвычайно низкой выходной мощности.

Чтобы выяснить причину низкого энергопотребления управления, мы исследовали происхождение общей мощности управления 2,23 нВт при входной мощности 84,4 мкВт (точка, закрашенная кружком на рис. 2e). Результаты на рис. 2g показывают, что генератор двоичных последовательностей работает даже с меньшим энергопотреблением, чем логическая схема, и это позволяет схеме управления в целом достичь очень низкого энергопотребления. Следует отметить, что мощность управления соответствует всей схеме переключения, но не содержит мощности для обнаружения напряжения ни на входе, ни на выходе. Этот результат свидетельствует о возможности создания электроники сверхмалого энергопотребления следующего поколения, в которой различные функции могут быть реализованы даже при очень ограниченной мощности менее 1 мкВт, если управление базируется на генераторе двоичных последовательностей.

Моделирование цепи импульсных нейронов

Наиболее важными строительными блоками для генератора бинарных паттернов являются генераторы времени ожидания, которые состоят из нейронных цепей импульсных помех. До сих пор были созданы различные нейронные цепи с разными целями в отношении биологических нейронов. В биологических нейронах мембранный потенциал увеличивается с каждым входом, и когда достигается пороговый потенциал, приток ионов Na и отток ионов K чередуются 26 , создавая импульсный потенциал (рис. 3a). Это точно описывается уравнением Ходжкина–Хаксли 27 , но при проектировании нейронных цепей используется более упрощенная модель 28 . В предыдущих исследованиях были изготовлены относительно точные аналоговые схемы нейронов, реализующие экспоненциальное поведение ионных каналов в подпороговой области транзистора 29,30 . С другой стороны, было выполнено дальнейшее упрощение функций для создания крупномасштабных систем, включающих ряд нейронных цепей. Такие упрощенные модели включают интеграционно-активный нейрон, который представляет собой простейшую версию 9.0076 31 , нейрон дырявого интегрирования-возгорания, который игнорирует изменение динамики нейрона 32 , нейрон Ижикевича, который алгоритмически обрабатывает процесс возбуждения 33 , и нейрон фазового перехода, который реализует функции с материальными свойствами 34,35 .

До сих пор были созданы различные нейронные цепи с разными целями в отношении биологических нейронов. В биологических нейронах мембранный потенциал увеличивается с каждым входом, и когда достигается пороговый потенциал, приток ионов Na и отток ионов K чередуются 26 , создавая импульсный потенциал (рис. 3a). Это точно описывается уравнением Ходжкина–Хаксли 27 , но при проектировании нейронных цепей используется более упрощенная модель 28 . В предыдущих исследованиях были изготовлены относительно точные аналоговые схемы нейронов, реализующие экспоненциальное поведение ионных каналов в подпороговой области транзистора 29,30 . С другой стороны, было выполнено дальнейшее упрощение функций для создания крупномасштабных систем, включающих ряд нейронных цепей. Такие упрощенные модели включают интеграционно-активный нейрон, который представляет собой простейшую версию 9.0076 31 , нейрон дырявого интегрирования-возгорания, который игнорирует изменение динамики нейрона 32 , нейрон Ижикевича, который алгоритмически обрабатывает процесс возбуждения 33 , и нейрон фазового перехода, который реализует функции с материальными свойствами 34,35 . В этих аналоговых нейронных схемах существует компромисс между точностью и простотой, но, сосредоточив внимание на математической структуре нелинейной динамики нейронов, была разработана схема, которая уравновешивает оба эти фактора.0076 36,37 . Недавно также были предложены схемы, которые максимально снижают энергопотребление за счет снижения напряжения питания до нескольких сотен мВ или использования чрезвычайно малого туннельного тока 23,24,38 . Эти нейронные схемы использовались для приложений машинного обучения 3 , а также для обработки оптических, слуховых или других сенсорных сигналов 39,40,41 .

В этих аналоговых нейронных схемах существует компромисс между точностью и простотой, но, сосредоточив внимание на математической структуре нелинейной динамики нейронов, была разработана схема, которая уравновешивает оба эти фактора.0076 36,37 . Недавно также были предложены схемы, которые максимально снижают энергопотребление за счет снижения напряжения питания до нескольких сотен мВ или использования чрезвычайно малого туннельного тока 23,24,38 . Эти нейронные схемы использовались для приложений машинного обучения 3 , а также для обработки оптических, слуховых или других сенсорных сигналов 39,40,41 .

Цепь импульсных нейронов CMOS. ( a ) Схематическое изображение биологического нейрона. ( b ) Цепь импульсных нейронов CMOS с функцией интеграции-срабатывания, которая используется для генератора времени ожидания. ( c ) Схематическое изображение V IN , V 1 и V OUT in ( b ) в зависимости от времени. Время ожидания соответствует периоду между появлением V IN и выходом V OUT . Подробная информация обо всех цепях импульсных нейронов с разным временем ожидания представлена в дополнительном примечании 3.

Время ожидания соответствует периоду между появлением V IN и выходом V OUT . Подробная информация обо всех цепях импульсных нейронов с разным временем ожидания представлена в дополнительном примечании 3.

Изображение в натуральную величину

В этом исследовании мы изготовили импульсную нейронную схему, специально разработанную для генерации времени ожидания при сверхнизком энергопотреблении. С целью генерации времени ожидания схема импульсных нейронов реализует функцию интеграции-срабатывания, в то время как все другие биологические функции были намеренно исключены. Он также предназначен для генерации прямоугольной импульсной волны шириной наносекунды в качестве выходного импульса для бесшовного соединения с логическими схемами CMOS с общим источником питания 1 В. Сфабрикованная нейронная схема спайка состоит из двух частей: одна часть генерирует время ожидания, а другая часть генерирует спайк (рис. 3b). В первой части входной ток создается током включения или подпороговым током транзистора при приложении 1 В и заряжает конденсатор приблизительно постоянным током. Затем, после времени ожидания, определяемого отношением емкости к току, потенциал конденсатора ( В 1 ) достигает порогового напряжения инвертора (около 0,5 В) и активирует часть генерации пиков, как показано на рис. 3c. Емкость была рассчитана как можно меньше для снижения энергопотребления, и использовались конденсаторы металл-оксид-полупроводник (МОП) с емкостью в несколько десятков фФ или даже меньшей, которая паразитирует на транзисторах и проводке. Часть генерации шипа состоит из схемы CMOS. Когда V 1 достигает порогового значения, поочередно активируются положительная обратная связь и обратная связь с задержкой, чтобы генерировать пиковый выходной сигнал. Вообще говоря, для снижения энергопотребления схем интегрирования-срабатывания нейронов использовались такие методы, как снижение напряжения питания или использование емкостной обратной связи 9.0076 23,24,42 , но здесь, чтобы использовать питание 1 В и максимально сократить использование конденсаторов, мы использовали только схемы CMOS.

Затем, после времени ожидания, определяемого отношением емкости к току, потенциал конденсатора ( В 1 ) достигает порогового напряжения инвертора (около 0,5 В) и активирует часть генерации пиков, как показано на рис. 3c. Емкость была рассчитана как можно меньше для снижения энергопотребления, и использовались конденсаторы металл-оксид-полупроводник (МОП) с емкостью в несколько десятков фФ или даже меньшей, которая паразитирует на транзисторах и проводке. Часть генерации шипа состоит из схемы CMOS. Когда V 1 достигает порогового значения, поочередно активируются положительная обратная связь и обратная связь с задержкой, чтобы генерировать пиковый выходной сигнал. Вообще говоря, для снижения энергопотребления схем интегрирования-срабатывания нейронов использовались такие методы, как снижение напряжения питания или использование емкостной обратной связи 9.0076 23,24,42 , но здесь, чтобы использовать питание 1 В и максимально сократить использование конденсаторов, мы использовали только схемы CMOS.

Чтобы детально прояснить работу схемы импульсных нейронов, показано моделирование схемы импульсных нейронов, которая генерирует время ожидания примерно 100 мс, как показано на рис. 4a. Был использован транзистор с выдерживаемым напряжением 5 В в процессе TSMC 0,18 мкм (более подробную информацию см. В дополнительных примечаниях 2 и 3), поскольку транзистор на 5 В при напряжении питания 1 В приводит к почти пороговым вычислениям и значительно снижает энергопотребление. Как показано на рис. 4b, когда 1 В подается на В в (входное напряжение показано серым цветом), В 1 постепенно увеличивается (красный цвет), а пиковое напряжение выводится как В из (синий цвет). Здесь после достижения В 1 порогового потенциала положительная обратная связь поднимает В 1 близко к 1 В (красный цвет), что способствует резкому нарастанию В из . Затем, сбросив V 1 на 0 В с обратной связью с задержкой, V из резко падает, и пиковый сигнал завершается. Увеличенный вид процесса зажигания (рис. 4c) показывает, что подъем или спад формы волны становится круче с каждым последующим инвертором, в порядке 3 , В 4 , и В из . Таким образом, соединяя КМОП-инверторы в несколько каскадов, можно получить крутую форму сигнала на выходе на цифровом уровне, независимо от времени ожидания на входе. Энергозатраты на серию операций достаточно малы, всего 0,16 пДж на операцию спайка (рис. 4d). Это соответствует средней потребляемой мощности 1,7 пВт, что более чем на порядок ниже, чем в предыдущих экспериментальных демонстрациях 20,21,22,23,24 . Здесь для подавления энергопотребления сверху и снизу инвертора первого каскада были вставлены диоды (рис. 4а), в противном случае сквозной ток течет длительное время по мере приближения В 1 к порогу инвертора и увеличивается потребление энергии. Моделирование цепи импульсных нейронов с более коротким временем ожидания (примерно 1 мкс) также представлено в дополнительном примечании 4, а моделирование для всех других схем нейронных импульсов также обобщено в дополнительном примечании 5.

Увеличенный вид процесса зажигания (рис. 4c) показывает, что подъем или спад формы волны становится круче с каждым последующим инвертором, в порядке 3 , В 4 , и В из . Таким образом, соединяя КМОП-инверторы в несколько каскадов, можно получить крутую форму сигнала на выходе на цифровом уровне, независимо от времени ожидания на входе. Энергозатраты на серию операций достаточно малы, всего 0,16 пДж на операцию спайка (рис. 4d). Это соответствует средней потребляемой мощности 1,7 пВт, что более чем на порядок ниже, чем в предыдущих экспериментальных демонстрациях 20,21,22,23,24 . Здесь для подавления энергопотребления сверху и снизу инвертора первого каскада были вставлены диоды (рис. 4а), в противном случае сквозной ток течет длительное время по мере приближения В 1 к порогу инвертора и увеличивается потребление энергии. Моделирование цепи импульсных нейронов с более коротким временем ожидания (примерно 1 мкс) также представлено в дополнительном примечании 4, а моделирование для всех других схем нейронных импульсов также обобщено в дополнительном примечании 5.

Моделирование цепи импульсного нейрона. ( a ) Смоделированная схема импульсного нейрона для времени ожидания 100 мс. ( b ) Волна напряжения формируется в нескольких разных узлах в ( a ). Красная заштрихованная область указывает время ожидания этой нейронной цепи. ( c ) Увеличение ( b ) вблизи события генерации спайка, которое обозначено серой тенью. ( d ) Смоделированное энергопотребление цепи нейрона с выбросом, которое быстро увеличивается по мере приближения к событию выброса из-за увеличения сквозного тока в инверторе первой ступени. Подробная работа цепи импульсных нейронов 1 мкс также представлена в дополнительном примечании 4, а моделирование всех схем нейронных импульсов с разным временем ожидания представлено в дополнительном примечании 5.

Изображение в натуральную величину

Эксперименты с импульсными нейронными схемами

На основе моделирования экспериментально были изготовлены импульсные нейронные схемы с использованием процесса TSMC 180 нм BCD, как показано на рис. 5a,b. Управляя входным током цепи импульсных нейронов (дополнительное примечание 3), можно генерировать различную продолжительность времени ожидания из входного напряжения 1 В, которое было измерено на основе экспериментальных настроек, как показано на рис. 5c. На рис. 5d, e мы использовали ток включения PMOS-транзистора для создания времени ожидания порядка 100 нс. Здесь, поскольку ток включения PMOS может быть настроен до 10 нА с длиной и шириной канала, время ожидания может составлять всего 100 нс с паразитной емкостью в несколько фФ. На рис. 5f,g вместо этого ток выключения ниже pA низкопорогового PMOS-транзистора с выдерживаемым напряжением 2 В использовался для создания времени ожидания порядка 100 мс. В этом случае также использовался дополнительный МОП-конденсатор емкостью 33 фФ для увеличения времени ожидания. Таким образом, нам удалось экспериментально сгенерировать на чипе произвольное время ожидания, охватывающее шесть порядков величины от 100 нс до 100 мс. Схемы и параметры устройства для всех других периодов ожидания также приведены в дополнительном примечании 3.

5a,b. Управляя входным током цепи импульсных нейронов (дополнительное примечание 3), можно генерировать различную продолжительность времени ожидания из входного напряжения 1 В, которое было измерено на основе экспериментальных настроек, как показано на рис. 5c. На рис. 5d, e мы использовали ток включения PMOS-транзистора для создания времени ожидания порядка 100 нс. Здесь, поскольку ток включения PMOS может быть настроен до 10 нА с длиной и шириной канала, время ожидания может составлять всего 100 нс с паразитной емкостью в несколько фФ. На рис. 5f,g вместо этого ток выключения ниже pA низкопорогового PMOS-транзистора с выдерживаемым напряжением 2 В использовался для создания времени ожидания порядка 100 мс. В этом случае также использовался дополнительный МОП-конденсатор емкостью 33 фФ для увеличения времени ожидания. Таким образом, нам удалось экспериментально сгенерировать на чипе произвольное время ожидания, охватывающее шесть порядков величины от 100 нс до 100 мс. Схемы и параметры устройства для всех других периодов ожидания также приведены в дополнительном примечании 3.

Эксперименты с импульсным нейронным контуром. ( a ) Оптическая микрофотография изготовленного чипа для включения нейронных цепей с различным временем ожидания от 100 нс до 100 мс. ( b ) Увеличение области чипа для импульсной нейронной цепи с временем ожидания 100 мс. Красный пунктирный квадрат указывает на всю нейронную цепь спайка, в то время как красный сплошной квадрат соответствует части генерации спайка и мембранному конденсатору. ( c ) Экспериментальная установка для измерения импульсных нейронных цепей. В IN и В OUT — напряжения внутри буферов ввода/вывода, а V IN-EX и V OUT-EX — напряжения вне буферов ввода/вывода , которые были измерены осциллографом. ( d ) Принципиальная схема изготовленной схемы импульсного нейрона для времени ожидания 100 нс (подробности см. в Дополнительном примечании 3). ( e ) Экспериментально измеренные формы сигналов V IN-EX и V OUT-EX для 100 нс пикового нейронного контура в ( d ). Интервал между пиками составляет примерно 100 нс. ( f ) Принципиальная схема изготовленной схемы импульсного нейрона для времени ожидания 100 мс (подробности см. в Дополнительном примечании 3). ( г ) Экспериментально измеренные формы сигналов В IN-EX и В OUT-EX для 100 мс импульсной цепи нейрона в ( f ). Интервал между пиками составляет примерно 100 мс. Эксперименты со всеми цепями импульсных нейронов с разным временем ожидания представлены в дополнительном примечании 5.

Интервал между пиками составляет примерно 100 нс. ( f ) Принципиальная схема изготовленной схемы импульсного нейрона для времени ожидания 100 мс (подробности см. в Дополнительном примечании 3). ( г ) Экспериментально измеренные формы сигналов В IN-EX и В OUT-EX для 100 мс импульсной цепи нейрона в ( f ). Интервал между пиками составляет примерно 100 мс. Эксперименты со всеми цепями импульсных нейронов с разным временем ожидания представлены в дополнительном примечании 5.

Изображение в натуральную величину время ожидания (рис. 6а и дополнительное примечание 5). Как показано на рис. 6b, ширина выходного пика составляла примерно 40 нс для времени ожидания до 100 мкс и примерно 400 нс для более длительного времени ожидания из-за вставки диодов в инвертор первой ступени, как упоминалось ранее на рис. 4а. Эта ширина пика может быть преобразована примерно до 40 нс с помощью схемы преобразования ширины пика, как показано в дополнительном примечании 6. Крутой подъем и спад выходного пика гарантирует совместимость пика с логическими схемами CMOS. Было обнаружено, что экспериментально измеренное потребление энергии на операцию спайка составляет от 60 до 120 фДж для всех времен ожидания (рис. 6с). Интересно отметить, что прошлые примеры нейронной схемы с длинным интервалом импульса порядка 100 мс ограничены, а наша нейронная схема на 100 мс имеет самую низкую потребляемую мощность 1,2 пВт среди всех экспериментальных демонстраций (Таблица 1). . Сравнение в таблице 1 ясно показывает, что изготовленные нейронные схемы со спайками обладают уникальным свойством совместимости с цифровыми схемами в смысле ширины спайка и напряжения питания, и в то же время достаточно низким энергопотреблением и широким диапазоном регулирования. время ожидания. Следует подчеркнуть, что все эти функции оптимизированы для генерации времени ожидания внутри цифровой схемы и асинхронного управления коммутационными цепями, а не для реализации биологических функций или простого снижения энергопотребления в одиночной нейронной схеме как в случае предыдущих исследований 21,23,24 .

Крутой подъем и спад выходного пика гарантирует совместимость пика с логическими схемами CMOS. Было обнаружено, что экспериментально измеренное потребление энергии на операцию спайка составляет от 60 до 120 фДж для всех времен ожидания (рис. 6с). Интересно отметить, что прошлые примеры нейронной схемы с длинным интервалом импульса порядка 100 мс ограничены, а наша нейронная схема на 100 мс имеет самую низкую потребляемую мощность 1,2 пВт среди всех экспериментальных демонстраций (Таблица 1). . Сравнение в таблице 1 ясно показывает, что изготовленные нейронные схемы со спайками обладают уникальным свойством совместимости с цифровыми схемами в смысле ширины спайка и напряжения питания, и в то же время достаточно низким энергопотреблением и широким диапазоном регулирования. время ожидания. Следует подчеркнуть, что все эти функции оптимизированы для генерации времени ожидания внутри цифровой схемы и асинхронного управления коммутационными цепями, а не для реализации биологических функций или простого снижения энергопотребления в одиночной нейронной схеме как в случае предыдущих исследований 21,23,24 .