Что такое EPM240T100C5N. Какие особенности имеет эта ПЛИС. Для каких задач подходит EPM240T100C5N. Как программировать и использовать эту микросхему. Каковы технические характеристики EPM240T100C5N.

Общее описание и ключевые особенности EPM240T100C5N

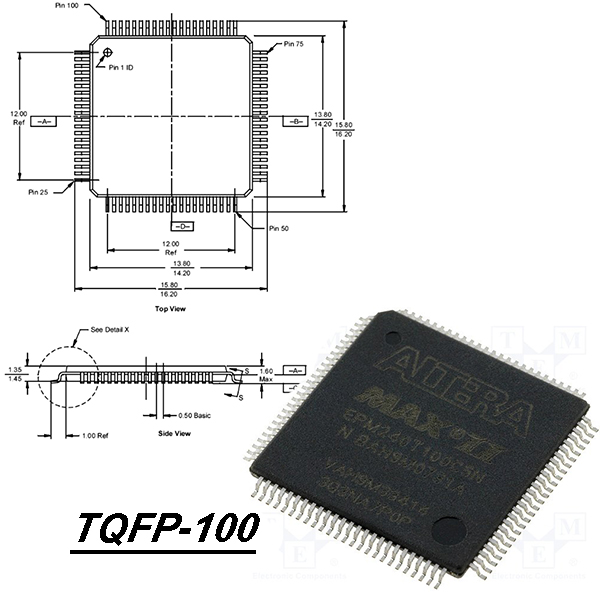

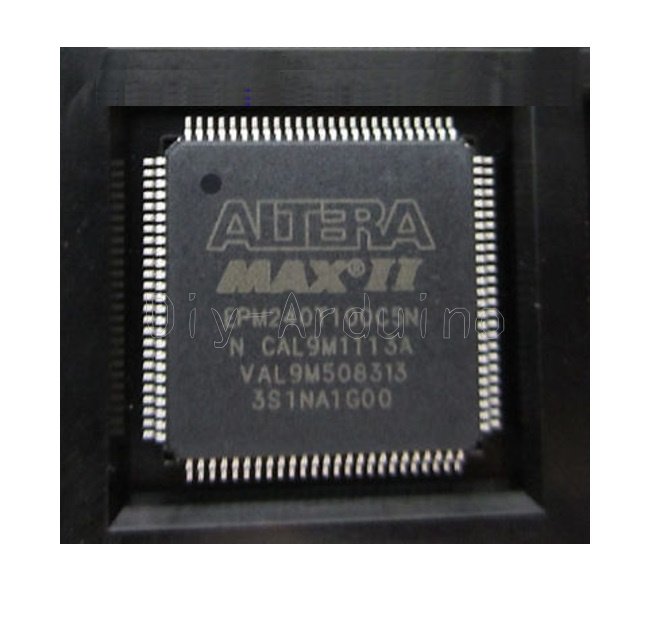

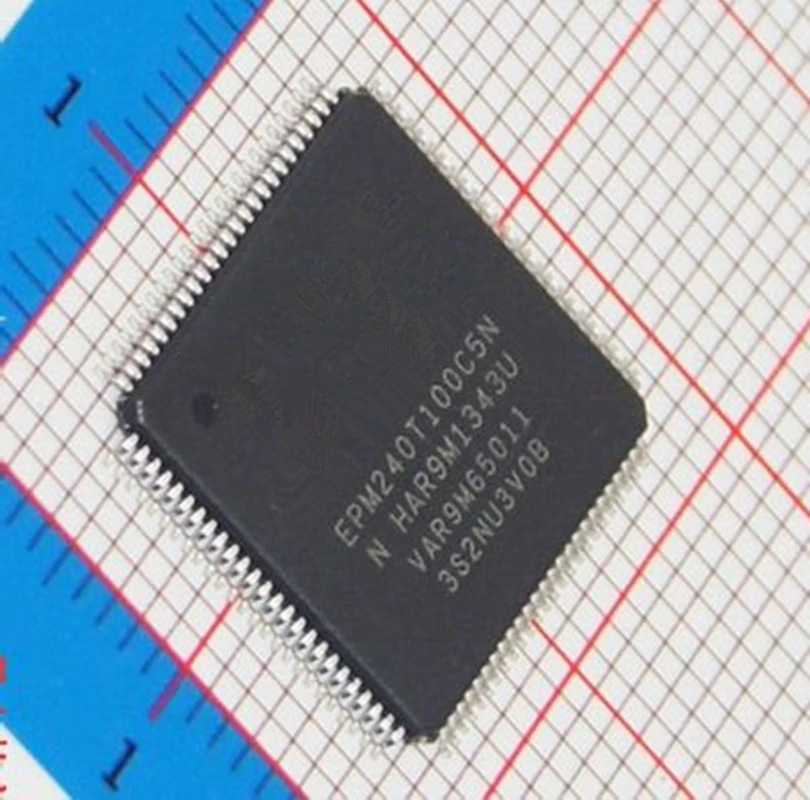

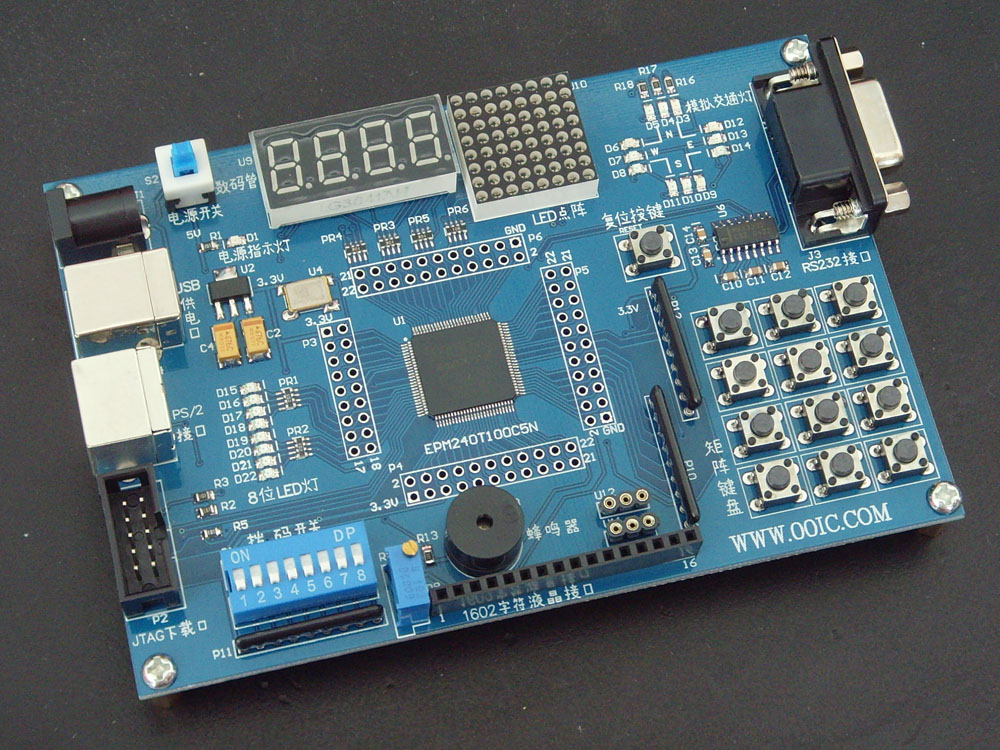

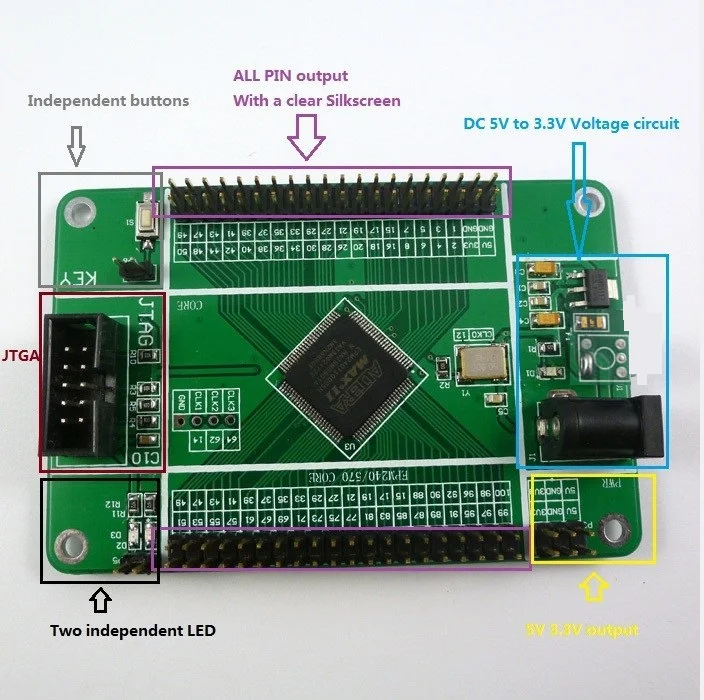

EPM240T100C5N — это программируемая логическая интегральная схема (ПЛИС) семейства MAX II производства компании Altera (сейчас часть Intel). Данная микросхема относится к классу CPLD (Complex Programmable Logic Device) и обладает следующими ключевыми характеристиками:

- 192 макроячейки для реализации логических функций

- 80 программируемых входов/выходов

- Максимальная рабочая частота 201.1 МГц

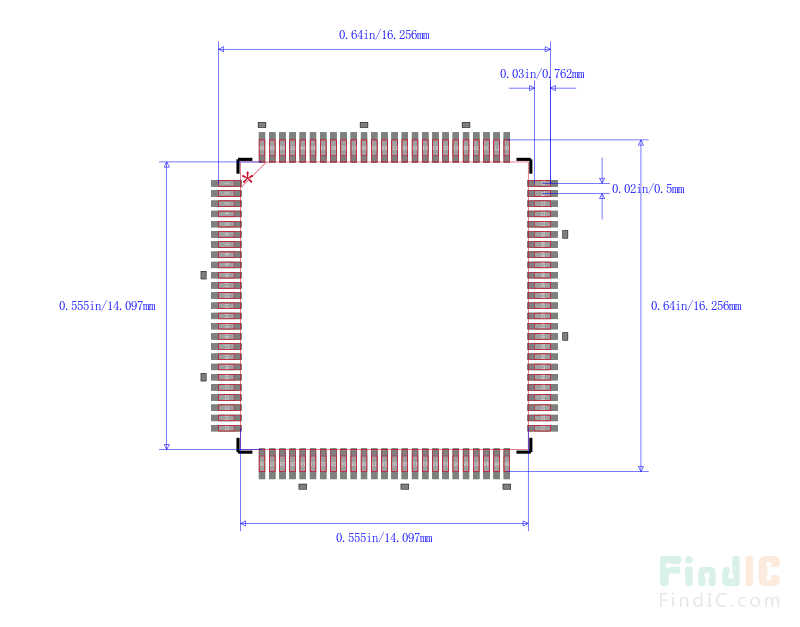

- Корпус TQFP-100

- Напряжение питания 2.375-3.6 В

- Технологический процесс 0.18 мкм

- Энергонезависимая флеш-память для хранения конфигурации

EPM240T100C5N предназначена для реализации сложных цифровых устройств и систем управления. Встроенная флеш-память позволяет сохранять конфигурацию даже при отключении питания.

Архитектура и внутренняя структура EPM240T100C5N

Микросхема EPM240T100C5N имеет следующую внутреннюю архитектуру:

- Матрица программируемых логических блоков (Logic Array Blocks, LABs)

- Глобальная коммутационная матрица для соединения LABs

- Блоки ввода/вывода с программируемыми буферами

- Встроенный генератор тактовой частоты

- Блок пользовательской флеш-памяти (User Flash Memory, UFM) объемом 8 Кбит

Такая архитектура обеспечивает высокую гибкость при проектировании цифровых устройств. Программируемые логические блоки позволяют реализовать произвольные комбинационные и последовательностные схемы.

Области применения и типовые задачи для EPM240T100C5N

EPM240T100C5N находит применение в следующих областях:

- Промышленная автоматика и управление

- Телекоммуникационное оборудование

- Автомобильная электроника

- Потребительская электроника

- Медицинское оборудование

Типовые задачи, решаемые с помощью EPM240T100C5N:

- Расширение интерфейсов ввода/вывода микроконтроллеров

- Реализация быстродействующих конечных автоматов

- Создание заказных интерфейсов и протоколов обмена данными

- Реализация специализированных вычислителей

- Построение схем управления питанием и синхронизацией

Программирование и отладка проектов на EPM240T100C5N

Для разработки проектов на базе EPM240T100C5N используется САПР Quartus Prime от компании Intel (ранее Altera). Процесс создания проекта включает следующие этапы:

- Описание логики на языках Verilog или VHDL

- Синтез проекта

- Размещение и трассировка

- Временной анализ

- Программирование микросхемы через JTAG-интерфейс

Для отладки можно использовать встроенный логический анализатор SignalTap II. Он позволяет захватывать и анализировать внутренние сигналы ПЛИС в реальном времени.

Сравнение EPM240T100C5N с аналогами других производителей

EPM240T100C5N можно сравнить со следующими аналогами:

- XC2C256 от Xilinx: имеет 256 макроячеек, но меньшую частоту (133 МГц)

- LC4064V от Lattice: 64 макроячейки, более низкое энергопотребление

- A3P060 от Microsemi: 60 макроячеек, встроенный криптопроцессор

EPM240T100C5N выигрывает за счет оптимального сочетания логической емкости, быстродействия и стоимости. Это делает ее хорошим выбором для многих проектов.

Особенности проектирования устройств на базе EPM240T100C5N

При разработке устройств с использованием EPM240T100C5N следует учитывать несколько важных моментов:

- Тщательно планировать размещение выводов для оптимальной трассировки печатной платы

- Использовать блокировочные конденсаторы по питанию для минимизации помех

- Применять буферные элементы на высокочастотных линиях ввода/вывода

- Разделять цифровые и аналоговые цепи при наличии АЦП/ЦАП

- Использовать возможности встроенного UFM для хранения параметров и конфигурации

Правильный подход к проектированию позволит максимально эффективно использовать ресурсы EPM240T100C5N и создать надежное устройство.

Рекомендации по выбору EPM240T100C5N для конкретных проектов

При выборе EPM240T100C5N для своего проекта необходимо ответить на следующие вопросы:

- Достаточно ли 192 макроячеек для реализации требуемой логики?

- Хватит ли 80 линий ввода/вывода для подключения всех внешних интерфейсов?

- Соответствует ли быстродействие EPM240T100C5N требованиям проекта?

- Подходят ли электрические параметры микросхемы (напряжения питания, токи потребления)?

- Удовлетворяет ли корпус TQFP-100 требованиям к габаритам устройства?

Если на все вопросы получены положительные ответы, то EPM240T100C5N является хорошим выбором для реализации проекта. В противном случае стоит рассмотреть другие модели семейства MAX II или аналоги других производителей.

Преимущества использования EPM240T100C5N

Применение EPM240T100C5N в проектах дает ряд существенных преимуществ:

- Высокая степень интеграции позволяет уменьшить количество компонентов на плате

- Возможность оперативного изменения логики работы устройства

- Высокое быстродействие для реализации сложных алгоритмов управления

- Энергонезависимость конфигурации благодаря встроенной флеш-памяти

- Широкий выбор готовых IP-ядер от Altera для типовых задач

Эти преимущества делают EPM240T100C5N привлекательным выбором для многих разработчиков цифровых устройств.

EPM240T100C5N от 23034.38 рублей со склада от 7 дней, по запросу производства ALTERA

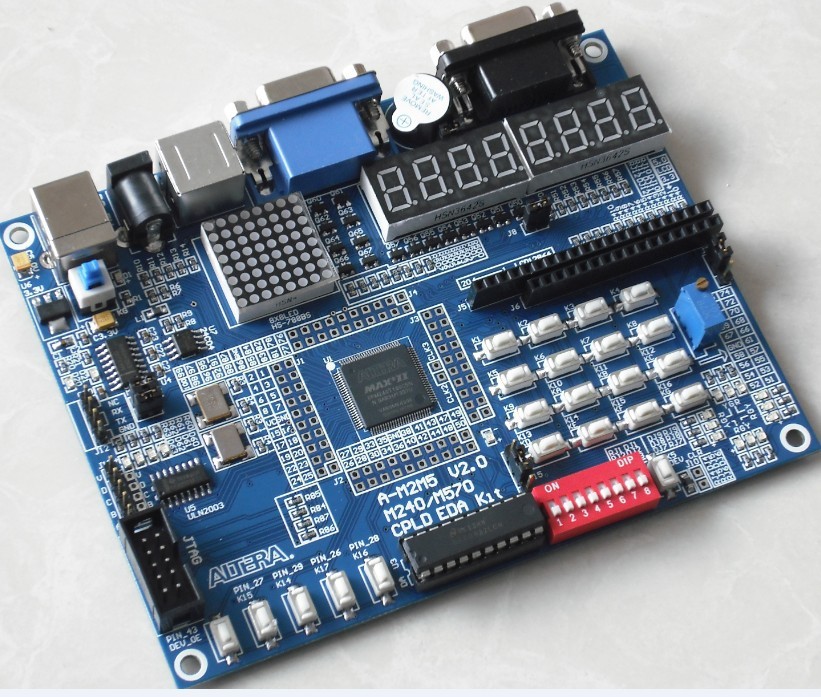

Изображение дано только в качестве иллюстрации.Ознакомьтесь c описанием продукта. Сообщить об ошибке.

Запросить

Бесплатная доставка заказов от 5000 ₽

IC, MAXII SPI CPLD, 201.1MHZ, TQFP-100.

The EPM240T100C5N is a MAX II instant-on non volatile CPLD with speed grade 5 in 100 pin TQFP package. It is based on 0.18µm, 6 layer metal flash process with non volatile storage of 8Kbits. MAX II device offers high I/O counts, fast performance and reliability. It has MultiVolt core, user flash memory (UFM) block and enhanced in-system programmability (ISP). MAX II device is designed to reduce cost and power while providing programmable solutions for applications such as bus bridging, I/O expansion, power-on reset (POR), sequencing control and device configuration control.

подробнее скрыть

| Тип ПЛИС | Флэш-память | Ничего не выбрано | |

| Количество Макроячеек | 192 | ||

| Количество I/O | 80I/O | ||

| Минимальное Напряжение Питания | 2. 375В 375В | ||

| Максимальное Напряжение Питания | 3.6В | ||

| Стиль Корпуса Микросхемы Логики | TQFP | ||

| Количество Выводов | 100вывод(-ов) | ||

| Задержка Распространения | 5. 9нс 9нс | ||

| Время Установки | 2.7нс | ||

| Частота | 201. 1МГц 1МГц | ||

| Минимальная Рабочая Температура | 0°C | ||

| Максимальная Рабочая Температура | 85°C | ||

| Упаковка | Поштучно | ||

| Линия Продукции | MAX II Series | ||

| Уровень Чувствительности к Влажности (MSL) | MSL 3 — 168 часов |

Техническое описание

- EPM240T100C5N скачать

Pdf, 1.

01 MB

01 MB

Вы можете купить EPM240T100C5N от 1 штуки. Работаем с частными лицами и с юридическими лицами по безналичному расчету.

Цену EPM240T100C5N и наличие сообщим по вашему запросу.

- EPM240T100C5N Datasheet

Архив даташитов

Сопутствующие товары

RE471ROTH ELEKTRONIK

Мультиадаптер, SMD, FR4, стеклоэпоксидный композит, 1.5мм, 57.2мм x 57.2мм

PL-BYTEBLASTER2NALTERA

CABLE, PROGRAMMING, PARALLEL PORT

PL-USB-BLASTER-RCNALTERA

CABLE, PROGRAMMING DOWNLOAD, USB

PVX003A0X3-SRZGE CRITICAL POWER

POL DC/DC преобразователь, Analog Pico Dlynx, Регулируемый, DOSA, 16. 5 Вт, 600 мВ, 5.5 В, 3 А

5 Вт, 600 мВ, 5.5 В, 3 А

GE CRITICAL POWER

POL DC/DC преобразователь, Analog Pico Dlynx, Регулируемый, DOSA, 33 Вт, 600 мВ, 5.5 В, 6 А

PVX012A0X3-SRZGE CRITICAL POWER

POL DC/DC преобразователь, Analog Pico Dlynx, Регулируемый, DOSA, 66 Вт, 600 мВ, 5.5 В, 12 А

UVT020A0X3-SRZGE CRITICAL POWER

POL DC/DC преобразователь, Analog Micro Dlynx, Регулируемый, DOSA

PDT003A0X3-SRZGE CRITICAL POWER

POL DC/DC преобразователь, Digital Pico Dlynx, Регулируемый, DOSA, 16.5 Вт, 450 мВ, 5.5 В, 3 А

PDT006A0X3-SRZGE CRITICAL POWER

POL DC/DC преобразователь, Digital Pico Dlynx, Регулируемый, DOSA, 33 Вт, 450 мВ, 5.5 В, 6 А

PDT012A0X3-SRZGE CRITICAL POWER

POL DC/DC преобразователь, Digital Pico Dlynx, Регулируемый, DOSA, 66 Вт, 450 мВ, 5. 5 В, 12 А

5 В, 12 А

xDevs.com | Project VC1 — vacuum-fluorescent table clock design

1. Наименование и основание для проведения работ.

1.1 Наименование изделия – электронный модуль индикатора времени на базе вакуумно-флуоресцентных индикаторов (в дальнейшем Изделие)

2. Цель выполнения работ.

2.1 Целью настоящей работы является разработка образца прибора отображения суточного времени. Отображение выполняется с помощью газоразрядных индикаторов(ламп) ИВ12 в качестве элементов индикации, в соответствии с пунктом 3 настоящего технического задания. Результатом работ по ТЗ является разработка инженерных документов на электронный блок для передачи проекта в серийное изготовление, изготовление прототипа для проведения предпроизводственных испытаний.

Конструкция изделия должна представлять собой моноблок небольших размеров, для настольной установки и применения неквалифицированным персоналом.

Питание устройства осуществляется от внешнего блока питания (в состав разработки не входит), с выходным напряжением постоянного тока от 5 до 15В (+-10%) (оптимально для данной системы), либо от интерфейсного порта (конструктив разъема mini USB Type-B). Продумать целесообразность установки 2х разъемов, тип А и Тип Б

Продумать целесообразность установки 2х разъемов, тип А и Тип Б

В устройстве должна быть предусмотрена возможность установки автономного элемента питания(батареи) для подпитки часов реального времени. Индикация времени при автономном питании не активна.

Батарея обеспечивает автономный ход часов и сохранение пользовательских настроек при отсутствии питания внешней сети.

Программное обеспечение Изделия (далее прошивка) должно обеспечивать:

• Инициализацию аппаратных средств микроконтроллера (МК).

• Включение преобразователя напряжения для питания ламп.

• Вывод цифр на индикаторы.

• Вывод времени на индикаторы в выбранном формате (12ч/24ч, дата/время).

• Работу индикаторов хода часов.

• Функциональную обработку кнопок управления.

• Считывание микроконтроллером данных из микросхемы времени.

• Управление цветом и яркостью подсветки ламп и яркостью свечения ламп .

• {все диоды подсветки включаются и выключаются одной кнопкой, регулировка яркости не требуется}.

Изделие должно эксплуатироваться в нормальных условиях окружающей температуры и влажности.

Изделие должно обладать достаточной устойчивостью к легким вибрациям.

Изделие должно выдерживать падение и\или пропадание напряжения питающего напряжения на любой период времени без каких либо повреждений.

Минимальное (гарантийное) время работы индикаторных ламп в данном Изделии должно совпадать с заявленной заводской наработкой ламп в 10000 часов. (недопустимость режимов работы Изделия приводящих к преждевременному выходу из строя ламп) Все напряжения соблюсти в рамках паспорта на лампы.

Погрешность хода часов не должна превышать 10 с в месяц. При включении устройства текущее время должно отображаться на индикаторах не позже 1 секунды после включения.

Аппаратное оснащение изделия разделено на блоки. Все блоки реализованы физически на монолитной печатной плате из стеклотекстолита марки FR4, с двухсторонней металлизацией, защитной маской и шелкографией с обоих сторон. Плата должна быть выполнена фабричным способом по чертежам разработчика. Прототип изготавливается с помощью возможностей разработчика.

Плата должна быть выполнена фабричным способом по чертежам разработчика. Прототип изготавливается с помощью возможностей разработчика.

В изделии применить современную элементную базу компонентов для SMD-монтажа (surface mounted device), соблюсти размер печатной платы не более 180 х 60 мм. На плате выполнить технологические отверстия для монтажа в корпусе согласно эскизу. Высота элементов не должна превысить 12 мм , без учета габаритных размеров ламп.

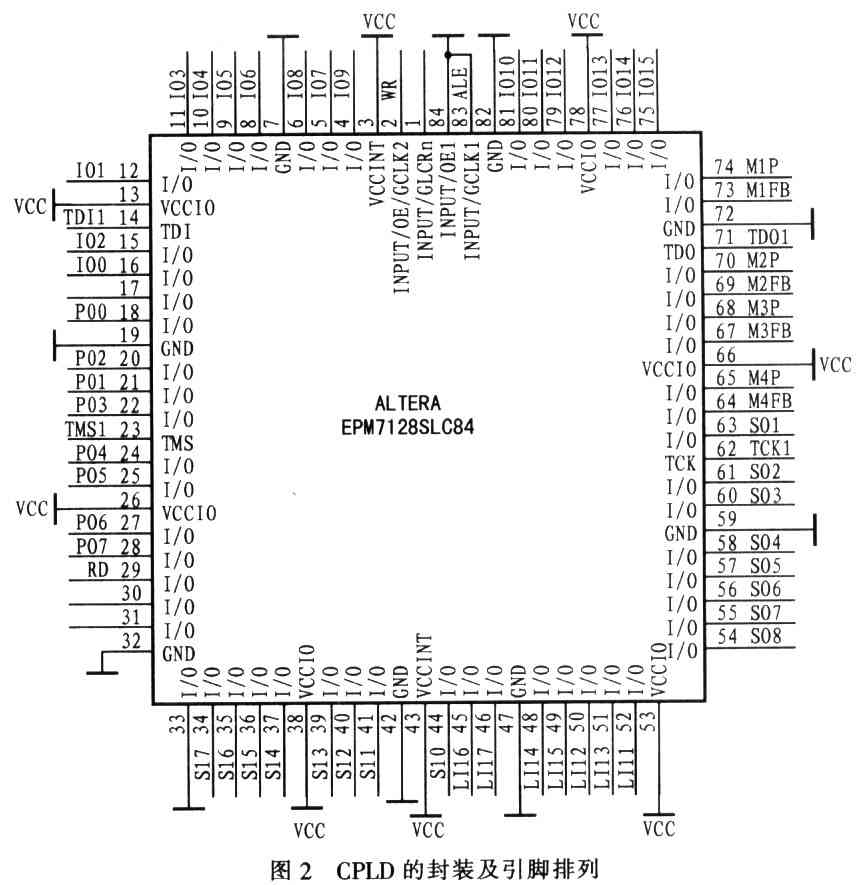

4.2.1. Блок цифровой

В данном блоке реализуется

Микроконтроллер на базе ядра ARM7TDMI

Микросхема часов реального времени DS1340

Микросхема интерфейса ламп EPM240T100C5N

Обвязка необходимая для работы микроконтроллера и часов

Схема управления источником питания ламп

4.2.2. Блок индикации и сигнализации

Посадочные места под пайку для монтажа 6 вакуумных ламп ИВ-12

6 ламп ИВ-12.

Пьезоэлектрический зуммер для режима будильника.

4.2.3. Блок питания

Импульсный DC-DC блок питания для питания анодов и сеток ламп.

В случае необходимости применить компактный трансформатор для SMD (Talema)

Преобразователь питания DC-DC для питания МК и часов

Защитная схемотехника на входе питания (т.е. перепад напряжения ???)

Схема питания от интерфейсного порта USB.

Автономная батарея для питания часов (CR2032) с панелью.

4.3. Разъемы подключения и органы управления

Разъем питания

Кнопки для управления.

Инструкция по прошивке электронных часов xDevs.com VC1

1. Собранные часы подключаются к источнику питания +12В с помощью штатного разъема питания.

2. Часы имеют две программируемые микросхемы – микроконтроллер DD3 и микросхема ПЛИС U1.

3. Программируем микросхему ПЛИС. Для этого нужен программатор ALTERA USB Blaster и персональный ПК (ноутбук) с установленным пакетом ALTERA Quartus II 9.0 (можно скачать бесплатно с официального сайта www.altera.com).

Подключение программатор к часам производится с помощью любого удобного кабеля

Сигналы используемые на данном этапе:

Название сигнала на плате часов Название сигнала разъема программатора

2 – ATDI 9 – TDI

4 – ATDO 3 – TDO

6 – ATCK 1 – TCK

8 – ATMS 5 – TMS

10 – GND 2 – GND

1 – VREF_JTAG 4 – VCC (TRGT)

Инструкция по использованию программатора: http://www. altera.com/literature/ug/ug_usb_blstr.pdf

altera.com/literature/ug/ug_usb_blstr.pdf

Для программирования данной микросхемы ПЛИС следует использовать файл

release\cpld_vc1.pof

4. После программирования следует обесточить часы.

5. Программирование микроконтроллера DD3 осуществляется с помощью отладочного модуля Segger J-Link.

http://www.segger.com/cms/jlink.html

Модуль подключается к интерфейсу USB персонального ПК, а отладочный порт JTAG (20 контактов) подключается к порту на плате часов (20 контактов). После подключения обоих кабелей нужно подать питание на плату часов.

Для программирования используется программа http://www.segger.com/cms/jflash.html и файл прошивки vc1.hex. В настройках проекта следует указать модель процессора NXP LPC2101

После этого следует осуществить подключение (Target / Connect). При этом отладочный модуль должен успешно подключиться к целевому микроконтроллеру (как на скриншоте ниже, Connected successfully).

После этого следует выбрать пункт Program & Verify либо нажать F6. Код программы будет прошит в микроконтроллер.

Код программы будет прошит в микроконтроллер.

6. Теперь часы нужно выключить, а все кабеля отключить. При следующем включении часы будут функционировать в полноценном режиме.

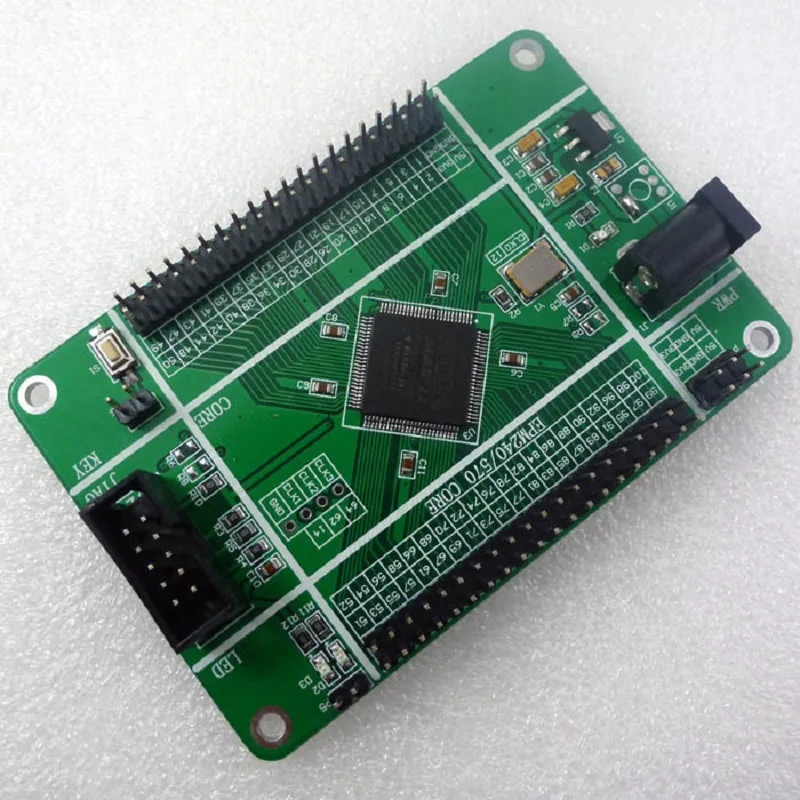

EPM240T100C5N для Altera MAX II CPLDS

Главная > FPGA Familis > MAX II CPLDS > EPM240T100C5N

Изображения приведены только для справки.

Базовая цена FOB: Получить последнюю цену >

$2.471 — $5,515 | 1 шт. (минимальный заказ)

Производитель: Альтера

Упаковка/кейс: TQFP-100

RoHS:

Жизненный цикл: Активный

Ресурс запасов: Заводские излишки запасов / Франчайзинговый дистрибьютор

Категории продуктов: Встраиваемые устройства — CPLD (сложные программируемые логические устройства)

Описание: Семейство CPLD MAX II 192 макроячейки 201,1 МГц, технология 0,18 мкм, 2,5 В/3,3 В, автомобильный 100-контактный лоток TQFP

.

Вы также можете узнать больше…

Вы также можете узнать больше…- Альтера МАКС 9000 EPLD

- Четырехсерийная конфигурация Altera (EPCQ)

- Altera MAX V CPLDS

- Altera MAX 10 ПЛИС

- Altera Stratix II ПЛИС

- Альтера Стратикс III Логик

- Altera FLEX 8000 ПЛИС

- Altera ARRIA II GX ПЛИС

Хотите купить EPM240T100C5N по лучшей цене? Пожалуйста, заполните краткую форму ниже:

ЭПМ240Т100К5М

Альтера QFP

ЭПМ240Т100К5Х

Альтера QFP

ЭПМ240Т100К-5Н

Альтера QFP

ЭПМ240Т100К5НН

Альтера QFP

Другие авторизованные дистрибьюторы (Fpgakey предоставит конкурентоспособную цену со всех франчайзинговых ресурсов.

)

)- ЭПМ240Т100К5Н

- Корпорация Intel

- IC CPLD 192MC 4.7NS 100TQFP

- 0

1+ $10,866

- ЭПМ240Т100К5Н

- Альтера Корпорация

- 80

1+ $11,695

- ЭПМ240Т100К5Н

- Альтера Корпорация

- CPLD — Комплексные программируемые логические устройства CPLD — MAX II 192 Macro 80 IOs

- 2846

1+ $9,3700

Нужна помощь?

Опора

Если у вас есть какие-либо вопросы о продукте и связанных с ним проблемах, пожалуйста, свяжитесь с нами.