Что такое цифровые компараторы. Как работают одноразрядные и многоразрядные компараторы. Для чего используются компараторы в электронных схемах. Какие бывают типы цифровых компараторов.

Что такое цифровой компаратор и как он работает

Цифровой компаратор — это устройство, которое сравнивает два цифровых или двоичных числа и определяет, равны ли они или какое из них больше. Основные функции цифрового компаратора:

- Сравнение двух чисел одинаковой разрядности

- Определение равенства чисел (A = B)

- Определение неравенства чисел (A < B или A > B)

Принцип работы компаратора основан на последовательном сравнении соответствующих разрядов двух чисел, начиная со старшего разряда. Результат сравнения выдается в виде логических сигналов на выходах компаратора.

Виды цифровых компараторов

Существует несколько основных типов цифровых компараторов:

1. Одноразрядный компаратор

Сравнивает два однобитных числа (0 или 1). Имеет 2 входа и 3 выхода для результатов A=B, A<B и A>B. Реализуется на простых логических элементах.

2. Многоразрядный компаратор

Сравнивает многоразрядные двоичные числа. Состоит из каскадно соединенных одноразрядных компараторов. Количество разрядов определяет точность сравнения.

3. Компаратор на сумматоре

Использует схему вычитания для сравнения двух чисел. Если результат вычитания равен нулю, числа равны. Знак результата определяет, какое число больше.

4. Компаратор с гистерезисом

Имеет дополнительную обратную связь, которая создает гистерезис при переключении. Это помогает устранить ложные срабатывания от шумов и помех.

Принцип работы многоразрядного компаратора

Работа многоразрядного компаратора основана на последовательном сравнении разрядов двух чисел:

- Сравниваются старшие разряды чисел A и B.

- Если разряды не равны, определяется результат A>B или A<B.

- Если разряды равны, переходят к сравнению следующих разрядов.

- Процесс продолжается до младших разрядов.

- Если все разряды равны, выдается сигнал A=B.

Такой алгоритм позволяет сравнивать числа любой разрядности.

Применение цифровых компараторов

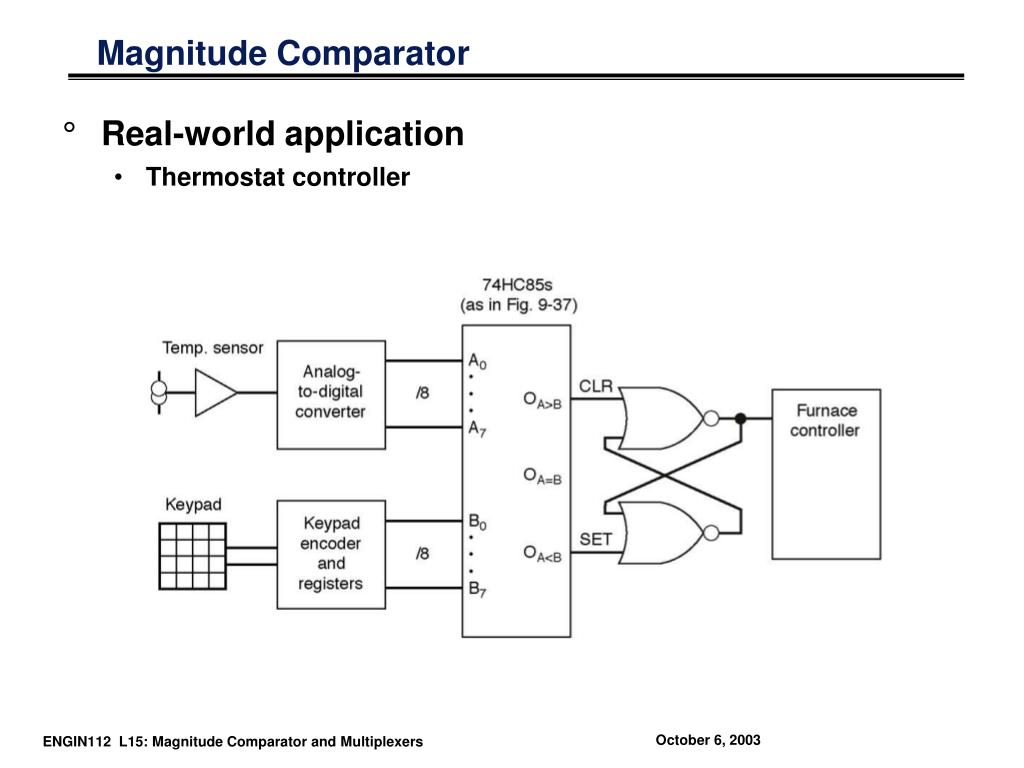

Цифровые компараторы широко используются в различных электронных устройствах и системах:

- В микропроцессорных системах для сравнения кодов и адресов

- В системах автоматического управления для контроля параметров

- В измерительных приборах для сравнения результатов измерений

- В устройствах цифровой обработки сигналов

- В системах защиты информации для проверки паролей и кодов доступа

Преимущества использования цифровых компараторов

Применение цифровых компараторов в электронных схемах дает ряд преимуществ:

- Высокая скорость сравнения чисел

- Простота реализации на логических элементах

- Возможность сравнения многоразрядных чисел

- Низкое энергопотребление

- Высокая помехоустойчивость

- Совместимость с другими цифровыми устройствами

Как выбрать подходящий цифровой компаратор

При выборе цифрового компаратора следует учитывать следующие параметры:

- Разрядность сравниваемых чисел

- Быстродействие (время сравнения)

- Напряжение питания и потребляемая мощность

- Тип выходных сигналов

- Наличие дополнительных функций (например, каскадирование)

- Совместимость с другими элементами схемы

Правильный выбор компаратора позволит оптимизировать работу всего устройства.

Проектирование схем с цифровыми компараторами

При разработке схем с использованием цифровых компараторов важно учитывать следующие аспекты:

- Правильное подключение входных сигналов с учетом их разрядности

- Обеспечение стабильного питания для устранения ложных срабатываний

- Использование фильтров на входах для подавления помех

- Правильная интерпретация выходных сигналов компаратора

- Учет задержек распространения сигналов в компараторе

Соблюдение этих правил поможет создать надежную и эффективную схему с цифровым компаратором.

Перспективы развития цифровых компараторов

Основные направления совершенствования цифровых компараторов включают:

- Увеличение быстродействия и уменьшение времени сравнения

- Снижение энергопотребления

- Повышение разрядности сравниваемых чисел

- Интеграция дополнительных функций (например, программируемые пороги)

- Улучшение помехоустойчивости

- Разработка специализированных компараторов для конкретных применений

Эти усовершенствования позволят расширить области применения цифровых компараторов и повысить эффективность электронных устройств.

Сумматоры и цифровые компараторы: таблицы истинности, принцип работы

Что такое сумматоры?Сумматоры — это комбинационные устройства, предназначенные для сложения чисел. Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значения входных чисел А и В, значение результата суммирования S и значение переноса в старший разряд P (см. рис. 3.48).

Цифровые сумматоры

Работа устройства, реализующего таблицу истинность (рис. 3.48), описывается следующими уравнениями

S = А·В + А·В

Р = А·В

Очевидно, что по отношении: к столбцу S реализуется логическая функция «исключающее ИЛИ», т. е. S = А + В.

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

Устройство, реализующее таблицу (рис. 3.48), называют полусумматором, и оно имеет логическую структуру, изображенную на рис. 3.49.

Поскольку полусумматор имеет только два входа, он может использоваться для суммирования лишь в младшем разряде.

При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса. Такое устройство (рис. 3.50) называют полным сумматором и его можно представить как объединение двух полусумматоров (Рвх — дополнительный вход переноса).

Сумматор обозначают через SM.

Цифровые компараторы

Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел A и B с одинаковым количеством разрядов либо вид неравенства A> B или A < B. Цифровые компараторы имеют три выхода.

Абрамян Евгений Павлович

Доцент кафедры электротехники СПбГПУ

Задать вопрос

Схема одноразрядного компаратора представляет собой структуру логического элемента «исключающее ИЛИ-НЕ» (рис. 3.51).

Из анализа схемы следует, что если A= B, то F = 1, в противном случае, т. е. при А ≠ В, F = 0. Если А > В, т. е. А = 1, В = 0, то С = 1, а если А < В, т. е. А = 0, В = 1, то D = l.

е. при А ≠ В, F = 0. Если А > В, т. е. А = 1, В = 0, то С = 1, а если А < В, т. е. А = 0, В = 1, то D = l.

Если попарно равны между собой все разряды двух n-разрядных двоичных чисел, то равны и эти два числа А и В. Применяя цифровой компаратор для каждого разряда, например, четырехзначных чисел, и определяя значения F1, F2, F3, F4 логических переменных на выходах компараторов, факт равенства А = В установим в случае, когда F = F1 · F2 · F3 · F4 = 1. Если же F = 0, то А ≠ В.

Неравенство А > В обеспечивается (для четырехразрядного числа) в четырех случаях: или А4 > В4, или А4 = В4 и А3 > В3, или А4 = В4, А3 = В3 и А2 > В2, или А4 = В4, А3 = В3, А2 = В2 и A1 > В1 (где А4 и В4 — старшие разряды чисел А и В). Очевидно, что если поменять местами А1 и B1, то будет выполняться неравенство А < В.

Цифровые компараторы выпускают, как правило, в виде самостоятельных микросхем. Так, микросхема К564ИП2 (рис. 3.52) является четырехразрядным компаратором, в котором каждый из одноразрядных компараторов аналогичен рассмотренной ранее схеме. Данная микросхема имеет расширяющие входы А < В, А = В, А > В, что позволяет наращивать разрядность обоих чисел. Для этого компараторы соединяют каскадно или параллельно (пирамидально).

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

Рассмотрим каскадное соединение компараторов К564ИП2 для сравнения двух восьмиразрядных чисел (рис. 3.53). При этом соединении выходы А = В и А В микросхемы младших разрядов подают соответственно потенциалы U0 и U1 (U0 соответствует логическому 0, a U1 — «1»). В последующих микросхемах на входах А > В поддерживают потенциал логической единицы U1.

Двухпороговые компараторы на логических элементах

В некоторых случаях возникает необходимость контроля напряжения в некотором заданном интервале пороговых значений. Для этих целей обычно применяют два ОУ с логическим элементом (рис. 1). Ранее уже публиковались варианты с использованием одного ОУ [1,2].

Рис. 1.

Иногда при разработке электронных устройств некоторые логические элементы оказываются незадействованными. Автор предлагает несколько вариантов реализации двухпороговых компараторов на логических элементах КМОП без использования ОУ для тех случаев, когда значения уровней меньше порога переключения микросхем, что исключает непосредственную подачу сигнала на вход логического элемента.

Первый вариант представлен на рис. 2. Значения контролируемых порогов устанавливают резисторами R3, R4. Если входное напряжение больше верхнего порога, то на входе элементов DD1.1 и DD1.2 будет низкий уровень. Поскольку элемент DD1.1 включён как инвертор, а элемент DD1.2 как повторитель, светиться будет только светодиод HL1. Аналогично, если входное напряжение меньше нижнего порога, светиться будет только светодиод HL2. В случае, когда контролируемое напряжение попадёт в интервал между порогами, светодиоды HL1 и HL2 погаснут и загорится светодиод HL3.

Рис. 2.

Для приведения входного напряжения к логическому уровню использован усилитель на транзисторе, включённом по схеме с общим эмиттером. Резистор R2 необходимо подобрать так, чтобы, во-первых, значение напряжения на нижних по схеме выводах переменных резисторов было не менее 1 В, а на верхних — не более чем напряжение питания минус 1 В. А, во-вторых, это условие должно соблюдаться при любом значении входного напряжения между контролируемыми порогами. Диоды VD1, VD2 и резистор R6 выполняют функцию ИЛИ и могут быть заменены соответствующим логическим элементом. Сопротивление резистора R5 определяется напряжением питания и необходимой яркостью свечения светодиодов. Транзистор VT1 служит для термостабилизации порогов переключения. Транзисторы необходимо подобрать так, чтобы вольт-амперные характеристики эмиттерных переходов были как можно ближе. В случае исключения транзистора VT1 контролируемые пороги напряжения будут существенно меняться при изменении окружающей температуры.

Входное сопротивление устройства определяется резистором R1, минимальный контролируемый уровень соответствует напряжению открывания p-n перехода транзистора VТ2 и приблизительно равен 0,6 В. Интервал допустимого напряжения питания равен соответствующему значению для микросхемы DD1. Разность между порогами может быть не более чем 10 % от напряжения питания. Точность сравнения — 5…50 мВ и зависит от напряжения питания и коэффициента передачи по току транзистора VT2.

Повышение минимального напряжения питания до 7 В позволяет несколько упростить устройство (рис. 3). Здесь функцию логического ИЛИ выполняют светодиоды HL1 и HL2.

Рис. 3.

Рис. 4.

Когда необходимо, чтобы светодиод светил только при нахождении входного уровня в заданном интервале, компаратор можно существенно упростить (рис. 4).

В устройстве, схема которого представлена на рис. 5, устранён недостаток, связанный с ограничением разности между порогами, однако входное сопротивление снижено и определяется параллельным включением резисторов R1 и R2, а подборку коллекторных резисторов R4 и R5 необходимо выполнить для каждого каскада.

Рис. 5.

В случае, если необходимо контролировать переменное напряжение или переменную составляющую постоянного напряжения, можно воспользоваться компаратором, схема которого показана на рис. 6. По сравнению с рис. 2 добавлены разделительный C1 и фильтрующий C2 конденсаторы, а также защитный диод VD1. Минимальные ёмкости конденсаторов определяются частотой сигнала. На схеме они приведены для частоты 1 кГц. Конденсатор C2 необходимо подобрать так, чтобы уровень пульсаций не приводил к паразитному переключению логических элементов. Входное сопротивление также определяется резистором R1.

Рис. 6.

Рис. 7.

Рис. 8.

Для увеличения входного сопротивления устройство необходимо дополнить буферным каскадом на ОУ (рис. 7) или истоковым повторителем (рис. 8). В первом случае входное сопротивление равно сопротивлению резистора R2 и может быть единицы мегом. Резисторами R1 и R2 необходимо установить среднюю точку, чтобы добиться симметричного ограничения вершин синусоиды. Во втором случае входное сопротивление — сотни мегом. Ёмкость конденсаторов C1-C3 указана для частоты входного сигнала 1 кГц.

Во всех вариантах можно применять биполярные транзисторы и диоды — маломощные кремниевые, конденсаторы — керамические или плёночные, ОУ DA1 можно использовать любой без частотной коррекции с подходящим напряжением питания. Полевой транзистор КП303А можно заменить любым маломощным с управляющим p-n переходом и каналом n-типа.

Примечание: В качестве биполярных, транзисторов с близкими параметрами и хорошим тепловым контактом желательно применить транзисторные сборки, содержащие два транзистора — КР159НТ1В, ВС847BDW, а также четыре (КС1НТ251) или пять (КР198НТ1Б) транзисторов структуры n-p-n.

Между затвором транзистора VT1 (рис. 8) и общим проводом необходимо включить резистор сопротивлением несколько десятков килоом.

Литература

1. Двухпороговый компаратор. — Радио, 1985, №7, с. 58.

2. Гричко В. Двухпороговый компаратор. — Радио, 2003, № 4, с. 32.

Автор: А. Староверов, г. Вологда

Компаратор Цифровой компаратор кратко Цифровые устройства. Микропроцессоры…

Сразу хочу сказать, что здесь никакой воды про компаратор, и только нужная информация. Для того чтобы лучше понимать что такое компаратор, цифровой компаратор,компаратор кодов , настоятельно рекомендую прочитать все из категории Цифровые устройства. Микропроцессоры и микроконтроллеры. принципы работы ЭВМ

Цифровой компаратор или компаратор кодов логическое устройство с двумя словарными входами, на которые подаются два разных двоичных слова равной в битах длины и обычно с тремя двоичными выходами, на которые выдается признак сравнения входных слов, — первое слово больше второго, меньше или слова равны. При этом выходы «больше», «меньше» имеют смысл, если входные слова кодируют числа в том или ином машинном представлении.

Часто цифровые компараторы не имеют выходов «больше», «меньше», а только выход «равно».

Может быть построен на логических элементах, работа которых основана на самых различных физических принципах, но современные компараторы обычно представляют собой полупроводниковые электронные устройства работающие в двоичной логике.

Промышленностью компараторы выпускаются в виде законченных компонентов — микросхем с разной длиной сравниваемых слов и других параметров. Примеры микросхем цифровых компараторов: КМОП- логика — 4063 и 4585, ТТЛ — 7485 и 74682-89 и многие другие.

Компараторы широко используются в вычислительной технике, измерительной технике, радио- и проводной связи, бытовых приборах. Например, цифровые часы с будильником содержат цифровой компаратор , при совпадении текущего времени с заданным, подается звуковой сигнал .

Аналоговым эквивалентом цифрового компаратора является аналоговый компаратор напряжений или токов. Некоторые микроконтроллеры имеют входные встроенные аналоговые компараторы, состояние выходов которых может быть считано программой контроллера или вызывать ее прерывание подпрограммой.

Компаратор — устройство, предназначенное для сравнения измеряемого входного сигнала Uвх с опорным напряжением Uоп.

Компараторами напряжения называют ИМС, предназначенные для сравнения двух напряжений и выдачи результата сравнения в логической форме: высокий уровень сигнала, низкий уровень сигнала

Существует три типа компараторов:

• Быстродействующие Δt ≤ 1нсек

• Средние 1нсек ≤ Δt ≤ 10нсек

• Медленные Δt ≥ 10нсек

Цифровые компараторы (от английского compare — сравнивать) выполняют сравнение двух чисел А, В одинаковой разрядности, заданных в двоичном или двоично-десятичном коде. В зависимости от схемного исполнения компараторы могут определять равенство А=В или неравенства А<В, А>В. Результат сравнения отображается в виде логического сигнала на одноименных выходах.

Цифровые компараторы применяются для выявления нужного числа (слова) в цифровых последовательностях, для отметки времени в часовых приборах, для выполнения условных переходов в вычислительных устройствах, а также в адресных селекторах [18].

Схема одноразрядного компаратора приведена на рис. 9.23. Компаратор состоит из двух элементов НЕ, четырех элементов И и одного элемента ИЛИ-НЕ.

Для исследования компаратора к нему подключен логический преобразователь. Подсоединяя его клемму OUT к каждому выходу компаратора, можно получить таблицу истинности и булево выражение для каждого режима работы компаратора. Для случая А=В, показанного на рис. 9.23, результаты моделирования представлены на рис. 9.24, откуда видно, что условию А=В соответствуют две комбинации сигналов на входе: А=В=1 или А=В=0. Этому условию и отвечает булево выражение на дополнительном дисплее.

Логические функции

,

Здесь каждая буква с нижним цифровым индексом представляет один из битов в числах.

Равенство (эквивалентность)

Двоичные числа и будут равны, если все пары соответственных битов обоих чисел равны, то есть:

, , и .

В двоичной записи чисел их цифры это или 0, или 1 . Об этом говорит сайт https://intellect.icu . Булева функция для равенства любых двух цифр и (здесь логическая операция «ИЛИ» обозначена символом , а «И» символом точки) может быть выражена как:

.

При этом равна 1 только если и равны.

Для равенства и , все функции (для i = 0, 1, 2, 3) должны быть равны 1.

Поэтому признак равенства и записывается в виде логической функции как

.

Двоичная функция равна 1 только если все пары цифр двух чисел равны.

Неравенство (неэквивалентность)

Чтобы определить наибольшее из двух двоичных чисел, мы рассмотрим отношение величин пар значащих цифр, начиная со старших битов к младшим битам до нахождения неравенства в некоторой позиции. Когда неравенство найдено, то, если соответствующий бит равен 1 и такой же бит равен 0, то мы считаем, что .

Это последовательное сравнение может быть выражено логическими выражениями как:

,

.

и — выходные двоичные переменные, которые равны 1 когда или соответственно.

Цифровой компаратор с использованием мультиплексоров

Однобитовый двоичный полный компаратор, равенство, неравенство, больше, меньше на уровне логического элемента. Создано с использованием Logisim

alternative comparator without using XNOR (using NOR gate)

Таблицы истинности компаратора

Для примеров приведены таблицы истинности тривиального однобитового и двухбитового компараторов.

Логическая функция однобитового цифрового компаратора описывается таблицей истинности:

Таблица истинности двухбитового компаратора:

Контрольные вопросы и задания

1. Какие функции выполняет цифровой компаратор, в каких устройствах он может быть использован?

2. Используя схему на рис. 9.23, проведите ее исследование в режимах А>В, А<В и проанализируйте полученные результаты

См. также

А как ты думаешь, при улучшении компаратор, будет лучше нам? Надеюсь, что теперь ты понял что такое компаратор, цифровой компаратор,компаратор кодов и для чего все это нужно, а если не понял, или есть замечания, то нестесняся пиши или спрашивай в комментариях, с удовольствием отвечу. Для того чтобы глубже понять настоятельно рекомендую изучить всю информацию из категории Цифровые устройства. Микропроцессоры и микроконтроллеры. принципы работы ЭВМ

Ответы на вопросы для самопроверки пишите в комментариях, мы проверим, или же задавайте свой вопрос по данной теме.

Компаратор — это… Что такое Компаратор?

Проходная характеристика неинвертирующего компаратораКомпаратор (аналоговых сигналов) (англ. comparator — сравнивающее устройство[1]) — электронная схема, принимающая на свои входы два аналоговых сигнала и выдающая логическую «1», если сигнал на прямом входе («+») больше чем на инверсном входе («−»), и логический «0», если сигнал на прямом входе меньше, чем на инверсном входе.

Одно напряжение сравнения двоичного компаратора делит весь диапазон входных напряжений на два поддиапазона. Двоичный логический сигнал (бит) на выходе двоичного компаратора указывает в каком из двух поддиапазонов находится входное напряжение.

Простейший компаратор представляет собой дифференциальный усилитель. Компаратор отличается от линейного операционного усилителя (ОУ) устройством и входного и выходного каскадов:

- Входной каскад компаратора должен выдерживать широкий диапазон входных напряжений между инвертирующим и неинвертирующим входами, вплоть до размаха питающих напряжений, и быстро восстанавливаться при изменении знака этого напряжения.

- Выходной каскад компаратора выполняется совместимым по логическим уровням и токам с конкретным типом входов логических схем (технологий ТТЛ, ЭСЛ и т. п.). Возможны выходные каскады на одиночном транзисторе с открытым коллектором (совместимость с ТТЛ и КМОП логикой).

- Для формирования гистерезисной передаточной характеристики, компараторы часто охватывают положительной обратной связью. Эта мера позволяет избежать быстрых нежелательных переключений состояния выхода, обусловленном шумами во входном сигнале, при медленно изменяющемся входном сигнале.

При подаче эталонного напряжения сравнения на инвертирующий вход, входной сигнал подаётся на неинвертирующий вход и компаратор является неинвертирующим (повторителем, буфером).

При подаче эталонного напряжения сравнения на неинвертирующий вход, входной сигнал подаётся на инвертирующий вход и компаратор является инвертирующим (инвертором).

Несколько реже применяются компараторы на основе логических элементов, охваченных обратной связью (см., например, триггер Шмитта — не компаратор по своей природе, но устройство с очень схожей областью применения).

При математическом моделировании компаратора возникает проблема выходного напряжения компаратора при одинаковых напряжениях на обоих входах компаратора. В этой точке компаратор находится в состоянии неустойчивого равновесия. Проблему можно решить, если принять доопределение, что, в точке неустойчивого равновесия выходное напряжение компаратора остаётся в предыдущем состоянии.

Реализации

В аналоговой схемотехнике компаратор обычно реализуется на базе операционного усилителя, охваченного резистивной положительной обратной связью.

Компараторы с двумя и более напряжениями сравнения

Строятся на двух и более дифференциальных усилителях.

Компараторы, построенные на двух дифференциальных усилителях, можно условно разделить на двухвходовые и трёхвходовые. Двухвходовые компараторы применяются в тех случаях, когда сигнал изменяется достаточно быстро (не вызывает быстрых переключений состояния выхода, и на выходе генерируют один из потенциалов, которыми запитаны опреационные усилители (как правило — +5В или 0В).

Троичный компаратор

Трёхвходовой (троичный) компаратор имеет два напряжения сравнения. Два напряжения сравнения делят весь диапазон входных напряжений на три нечётких поддиапазона в нечёткой (fuzzy) троичной логике, которым присваиваются три чётких значения в чёткой троичной логике. Двухбитный троичный (2B BCT) логический сигнал (трит) на выходе троичного компаратора указывает в каком из трёх поддиапазонов находится входное напряжение. Логическая часть троичного компаратора выполняет унарную троичную логическую функцию — «повторитель» (F1073 = F810). Двухбитный троичный трит (2B BCT) может быть преобразован в трёхбитный трит (3B BCT) или в трёхуровневый трит (3LCT).

Троичный компаратор является простейшим одноразрядным троичным АЦП.

Троичный компаратор является переходником из нечёткой (fuzzy) троичной логики в чёткую троичную логику для решения задач нечёткой троичной логики средствами чёткой троичной логики.

Применяется в прецизионном триггере Шмитта с RS-триггером.

Троичный компаратор низкого качества с двоичными компараторами на цифровых логических элементах применён в троичном индикаторе напряжения источника питания с преобразованием двухбитного трита (2B BCT) в трёхбитный одноединичный трит (3B BCT)[2].

Многовходовые компараторы

Входной каскад параллельных АЦП прямого преобразования является многоуровневым компаратором. В нём применяются напряжений сравнения, где n — количество битов выходного кода.

Промышленные компараторы

Пример широко известных компараторов: LM311 (российский аналог — КР554СА3), LM339 (российский аналог — К1401СА1). Эта микросхема часто встречается, в частности, на системных платах ЭВМ, а также в системах управления ШИМ контроллеров в блоках преобразования напряжения (например в компьютерных блоках питания с системой питания ATX). Подробнее о них можно узнать из книги «Электроника», О. В. Миловзоров, И. Г. Панков — 2004; «Электронные приборы и усилители», Ф. И. Вайсбурд, Г. А. Панаев, Б. Н. Савельев — 2005

Примечания

Ссылки

| Микросхемы, производившиеся в СССР | |||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Технологии | РТЛ • ДТЛ • ТТЛ • ЭСЛ • N-МОП • КМОП • И3Л | ||||||||||||||||||||||||||||||||||||||||

| Система обозначения по ГОСТ 18682-73 |

|

||||||||||||||||||||||||||||||||||||||||

| Тип корпуса (ГОСТ 17467-72) |

Тип 1 • Тип 2 • Тип 3 • Тип 4 • | ||||||||||||||||||||||||||||||||||||||||

| Производители | Ангстрем • Алмаз • ВНИИС • ЕРЗ • ИРЗ • Интеграл • Полёт • МНИИПА • НИИЭТ • МЦСТ | ||||||||||||||||||||||||||||||||||||||||

3.7. Компараторы

Компараторы – это КС, осуществляющие сравнение (от англ. Compare – сравнение) поступающих на их вход двоичных кодов. Результатом такого сравнения могут быть следующие значения выходного сигнала: „А=В” (равенство кодов А и В), „А≠В” (неравенство кодов А и В) и „А<В” (код А меньше кода В) или „А>В” (код А больше кода В), в случае „≠”.

Пусть заданы две совокупности переменных ν′=(xn, …, xp, …, x1) и ν′′=(yn, …, yp, …, y1). Так как xp=0 или 1 и yp=0 или 1, то каждая из совокупностей переменных ν′ и ν′′ имеет 2nкомбинаций значений. Для краткости такие совокупности значений переменных принято называть кодами, а величины xp и yp – разрядами кодов.

КС, реализующая функцию f(ν)=f(ν′, ν′′), где ν=( xn, …, x1, yn, …, y1), которая равна 1 только при xp=yp для всех p=1…n, называется схемой равнозначности кодов. Разряды xpи yp равны только в том случае, если , поэтому функция(здесь знаксоответствует логической функции «И», а– функции «ИЛИ») принимает значение, равное 1, только при по — парном равенстве всех одноименных кодов. На рис. 3.16,а и 3.16,б показаны две схемы, реализующие функциюf(ν), которые построены для n=4 на основании полученного выражения. Схема равнозначности упрощается при использовании ЛЭ «исключающее ИЛИ» с открытым коллектором (рис. 3.16, в)).

Рис. 3.16 Схемы равнозначности кодов

Схемы сравнения двоичных чисел – это устройства, формирующие на своем выходе, помимо сигнала равенства входных кодов (А=В), еще и сигналы, несущие информацию какое из входных кодов больше другого (А<В и А>В).

Пусть заданы два n–разрядных числа A=(xn, …, x1) и B=(yn, …, y1), где xn и yn – старшие разряды этих чисел. Соотношение между числами A и B описываются пятью функциями:

Легко заметить, что можно рассматривать только две функции, к примеру, F(A<B) и F(A=B), т.к. остальные функции можно выразить через них.

Для построения компаратора с тремя выходами (=, > и <) для одноразрядных слов (табл. 3.8) требует реализации функций: FA=B=,FA>B=иFA<B=. Функциональная схема компаратора для одноразрядных слов с тремя выходами представлена на рис. 3.17.

Табл.3.8 Таблица истинности для компаратора

Рис.3.17 Функциональная схема компаратора для одноразрядных слов

Функцию FA>B для многоразрядных слов можно получить на основе рассуждений, например, при сравнении двухразрядных слов. Если старшие разряды xi и yi не равны, то результат известен независимо от младших разрядов: при xi=1 и yi=0 имеем A>B, а при xi=0 и yi=1 имеем A<B. Если старшие разряды равны (xi=yi), результат неизвестен, и требуется анализ следующего разряда по тому же алгоритму. Таким образом, для двухразрядных слов можно записать: .

Аналогичны рассуждения для слов любой разрядности – к анализу следующего разряда нужно переходить только при равенстве предыдущих. Для n-разрядных слов:

(3.12)

Пример реализации компаратора с тремя выходами для двухразрядных слов приведен на рисунке 3.18. Выработка признака A>B в этой схеме производится по соотношению 3.13 (штрихом отмечены соответствующие выходы компаратора младшей группы):

(3.13)

Рис.3.18 Компаратор для двухразрядных слов

В сериях цифровых элементов представлены компараторы с тремя выходами (=, >, <). Условное графическое обозначение такого компаратора приведено на рисунке 3.19.

Рис. 3.19. Условное графическое обозначение четырехразрядного

компаратора с тремя выходами

На рисунке 3.20 представлено каскадное соединение компараторов для сравнения двух восьмиразрядных чисел. При этом соединении выходы А=В, А<В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А=В, А<В и А>В микросхемы младших разрядов подают соответственно сигналы U0, U1, U1 (U0 соответствует уровню лог.”0”, U1 – лог.”1”). В последующих микросхемах на вход А>В подается сигнал U1.

Рис. 3.20. Схема каскадного соединения компараторов

Представленная на рис. 3.20 схема каскадирования компараторов обладает существенным недостатком, состоящим в увеличении задержки распространения сигнала при увеличении разрядности сравниваемых кодов. Если нам важен только факт равенства или неравенства входных кодов, то увеличить быстродействие при объединении компараторов можно, если подавать их выходные сигналы на элемент И (рис. 3.21). В этом случае суммарная задержка схемы превысит задержку одного компаратора всего лишь на задержку элемента И. При применении компараторов с инверсным выходом надо брать элемент ИЛИ с нужным числом входов.

Рис. 3.21. Уменьшение задержки при каскадировании компараторов

| Количество каналов | 4канал(-ов) |

| Минимальная Рабочая Температура | -55 C |

| Максимальная Рабочая Температура | 125 C |

| Максимальное Напряжение Питания | 6В |

| Минимальное Напряжение Питания | 2В |

| Количество Выводов | 16вывод(-ов) |

| Уровень Чувствительности к Влажности (MSL) | MSL 3 — 168 часов |

| Количество Бит | 4бит |

| Тип Компаратора | Величина |

| Стиль Корпуса Микросхемы Логики | SOIC |

| Базовый Номер / Семейство Логики | 74HC85 |

| Базовый Номер Микросхемы Логики | 7485 |

| Семейство Логической Микросхемы | 74HC |

| Максимальный выходной ток высокого уровня | -5.2mA |

| Максимальная рабочая температура | +125 °C |

| Длина | 9.9мм |

| Максимальное время задержки распространения при максимальной CL | 195 ns @ 2 V, 33 ns @ 6 V, 39 ns @ 4.5 V |

| Минимальное рабочее напряжение питания | 2 В |

| Производитель | Texas Instruments |

| Состояние проверки задержки распространения | 50пФ |

| Полярность | Неинвертирующий |

| Тип корпуса | SOIC |

| Тип монтажа | Поверхностный монтаж |

| Минимальная рабочая температура | -55 °C |

| Ширина | 3.91мм |

| Семейство логических элементов | HC |

| Высота | 1.58мм |

| Логическая функция | Компаратор величины |

| Максимальное рабочее напряжение питания | 6 В |

| Число контактов | 16 |

| Размеры | 9.9 x 3.91 x 1.58мм |

| Выходная функция | A<B, A=B, A>B |

| Количество бит | 4бит |

| Максимальный выходной ток низкого уровня | -5.2mA |

| Maximum High Level Output Current | -5.2mA |

| Maximum Operating Temperature | +125 °C |

| Length | 9.9мм |

| Maximum Propagation Delay Time @ Maximum CL | 195 ns @ 2 V, 33 ns @ 6 V, 39 ns @ 4.5 V |

| Minimum Operating Supply Voltage | 2 В |

| Brand | Texas Instruments |

| Состояние проверки задержки распространения | 50пФ |

| Полярность | Неинвертирующий |

| Package Type | SOIC |

| Тип монтажа | Поверхностный монтаж |

| Минимальная рабочая температура | -55 °C |

| Ширина | 3.91мм |

| Logic Family | HC |

| Height | 1.58мм |

| Logic Function | Компаратор величины |

| Maximum Operating Supply Voltage | 6 В |

| Pin Count | 16 |

| Dimensions | 9.9 x 3.91 x 1.58мм |

| Максимальный выходной ток низкого уровня | 5.2mA |

| Количество бит | 4бит |

| Ib — Входной ток смещения | 0.008 mA |

| Вид монтажа | SMD/SMT |

| Время задержки распространения | 195 ns, 39 ns, 33 ns |

| Категория продукта | Логические компараторы |

| Количество цифровых разрядов | 4 bit |

| Логическая функция | A <B, A = B, A >B |

| Максимальная рабочая температура | + 125 C |

| Минимальная рабочая температура | 55 C |

| Напряжение питания — макс. | 8 uA, 6 V |

| Напряжение питания — мин. | 2 V |

| Подкатегория | Logic ICs |

| Полярность | Non-Inverting |

| Продукт | Digital Comparators |

| Рабочее напряжение питания | 2 V to 6 V |

| Размер фабричной упаковки | 2500 |

| Серия | CD74HC85 |

| Тип выхода | CMOS/TTL |

| Тип компаратора | Magnitude |

| Тип продукта | Logic Comparators |

| Торговая марка | Texas Instruments |

| Упаковка / блок | SOP-16 |

| Вес, г | 0.165 |

Компаратор двоичных чисел

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны компараторы двоичных чисел (см., например, патент РФ 2300131, кл. G06F 7/02, 2007 г.), содержащие логические элементы и формирующие признаки соотношений А>В, А=В, где А=а1а0, B=b1b0 — двухразрядные двоичные числа, задаваемые двоичными сигналами а0, а1, b0, b1 ∈ {0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных компараторов двоичных чисел, относится сложность устройства, обусловленная тем, что, в частности, упомянутый аналог состоит из логических элементов четырех типов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип компаратор двоичных чисел (рис. 8.32а на стр. 500 в книге Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Справочник. М.: Радио и связь, 1990 г.), который содержит логические элементы и формирует признаки соотношений А>В, А=В, где А=а1а0, B=b1b0 — двухразрядные двоичные числа, задаваемые двоичными сигналами а0, а1, b0, b1 ∈ {0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится сложность устройства, обусловленная тем, что прототип состоит из логических элементов пяти типов.

Техническим результатом изобретения является упрощение устройства за счет уменьшения числа типов используемых логических элементов.

Указанный технический результат при осуществлении изобретения достигается тем, что в компараторе двоичных чисел, содержащем два элемента И, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четыре элемента НЕ, первый вход первого элемента И, вход j-го и вход, выход (j+2)-го элементов НЕ соединены соответственно с выходом третьего элемента НЕ, первым входом и выходом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, j-ым входом второго элемента И, подсоединенного выходом к выходу «Равно» компаратора двоичных чисел, особенность заключается в том, что в него введены третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и третий, четвертый элементы И, а первый, второй входы (j+2)-го, второй вход и выход первого элементов И соединены соответственно с выходом j-го элемента НЕ, вторым входом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходом четвертого элемента И и вторым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного первым входом и выходом соответственно к выходу третьего элемента И и выходу «Больше» компаратора двоичных чисел, j-й и (j+2)-й входы которого соединены соответственно с первым и вторым входами j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

На чертеже представлена схема предлагаемого компаратора двоичных чисел.

Компаратор двоичных чисел содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11, 12, 13, элементы И 21, 22, 23, 24, элементы НЕ 31, 32, 33, 34, причем первый вход элемента 21, вход элемента 3j и вход, выход элемента 3j+2 соединены соответственно с выходом элемента 33, первым входом и выходом элемента 1j, j-ым входом элемента 22, подсоединенного выходом к выходу «Равно» компаратора двоичных чисел, а первый, второй входы элемента 2j+2, второй вход и выход элемента 21 соединены соответственно с выходом элемента 3j, вторым входом элемента 1j, выходом элемента 24 и вторым входом элемента 13, подсоединенного первым входом и выходом соответственно к выходу элемента 23 и выходу «Больше» компаратора двоичных чисел, j-й и (j+2)-й входы которого соединены соответственно с первым и вторым входами элемента 1j.

Работа предлагаемого компаратора двоичных чисел осуществляется следующим образом. На его первый, второй и третий, четвертый входы подаются соответственно произвольные двоичные сигналы b1, b0 ∈ {0,1} и а1, а0, ∈ {0,1}, которые задают подлежащие сравнению двухразрядные двоичные числа B=b1b0 и А=а1а0 (а1, b1, и a0, b0 определяют значения старших и младших разрядов соответственно). Тогда сигналы на выходах «Больше», «Равно» предлагаемого компаратора будут определяться выражениями

В представленной ниже таблице приведены значения реализуемых выражениями (1) функций на всех возможных наборах значений их аргументов.

С учетом таблицы имеем QA>B=1 если А>В, QA=B=1 если А=В.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый компаратор двоичных чисел формирует признаки соотношений А>В, А=В, где А=а1а0, B=b1b0 — двухразрядные двоичные числа, задаваемые двоичными сигналами а0, а1, b0, b1 ∈ {0,1}, и устроен проще чем прототип, поскольку состоит из логических элементов трех типов.

Компаратор двоичных чисел, содержащий два элемента И, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИИСКЛЮЧАЮЩЕЕ ИЛИ и четыре элемента НЕ, причем первый вход первого элемента И, вход j-го и вход, выход (j+2)-го элементов НЕ соединены соответственно с выходом третьего элемента НЕ, первым входом и выходом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, j-ым входом второго элемента И, подсоединенного выходом к выходу «Равно» компаратора двоичных чисел, отличающийся тем, что в него введены третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и третий, четвертый элементы И, а первый, второй входы (j+2)-го, второй вход и выход первого элементов И соединены соответственно с выходом j-го элемента НЕ, вторым входом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходом четвертого элемента И и вторым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного первым входом и выходом соответственно к выходу третьего элемента И и выходу «Больше» компаратора двоичных чисел, j-й и (j+2)-й входы которого соединены соответственно с первым и вторым входами j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.Двоичные компараторы

- Изучив этот раздел, вы сможете:

- Распознавать использование схем двоичного компаратора.

- Разберитесь в работе двоичных компараторов.

- • Компараторы равенства.

- • Компараторы величин.

- Моделируйте работу многобитовых компараторов с помощью программного обеспечения.

- • 4-битные компараторы величины.

- • 4-битные каскадные компараторы.

- Access Comparator IC Datasheets.

Двоичные компараторы, также называемые цифровыми компараторами или логическими компараторами, представляют собой комбинационные логические схемы, которые используются для проверки того, является ли значение, представленное одним двоичным словом, больше, меньше или равно значению, представленному другим двоичным словом. Можно использовать два основных типа компаратора.

• Компараторы равенства.

• Компараторы величин.

Компараторы равенства

Рис. 4.3.1 Четырехбитный компаратор равенства

Компаратор равенства, такой как показанный на рис. 4.3.1, является простейшим многобитовым логическим компаратором и может использоваться для таких схем, как электронные замки и устройства безопасности, где двоичный пароль, состоящий из нескольких битов, вводится в компаратор для сравнивать с другим заданным словом.

На рис. 4.3.1 логическая 1 будет присутствовать на выходе, если два входных слова совпадают, в противном случае на выходе останется 0.Следовательно, существует только одна правильная входная комбинация, и чем больше битов во входных словах, тем больше возможных неправильных комбинаций. С дополнительной схемой для подсчета может быть обеспечена дополнительная безопасность за счет ограничения количества попыток перед блокировкой ввода.

Схема компаратора равенства состоит из логического элемента исключающее ИЛИ-ИЛИ (XNOR) на пару входных битов. Если два входа идентичны (оба 1 или оба 0), на выходе получается логическая 1.

Затем выходы вентилей XNOR объединяются в логический элемент AND, выход которого будет равен 1, только когда все вентили XNOR указывают совпадающие входы.

Компараторы звездных величин

Рис. 4.3.2 Однобитовый компаратор величины

Компаратор величины также может использоваться для обозначения равенства, но имеет еще два выхода: один — логическая 1, когда слово A больше слова B, и другой — логическая 1, когда слово A меньше слова B. поэтому составляют основу принятия решений в логических схемах. Любая логическая проблема может быть сведена к одному или нескольким (иногда многим) решениям «да / нет» на основе пары сравниваемых значений.

Простой 1-битный компаратор величины показан на рис. 4.3.2. Элемент 1 выдает функцию A> B, элемент 3 дает A Эта базовая схема для компаратора величин может быть расширена для любого количества битов, но чем больше битов должно сравниваться, тем сложнее становится схема. Доступны интегральные схемы сравнения величин, которые можно использовать для сравнения многобитовых слов. Одной из таких ИС является 4-битный КМОП-компаратор 74HC85 от Philips Semiconductors (NXP), показанный на рис.4.3.3. Эта ИС сравнивает два 4-битных слова и выдает выходные данные на контактах 5, 6 и 7, которые указывают, равны ли входные слова или нет, имеют ли A или B более высокое числовое значение. На рис. 4.3.4 показана упрощенная схема типичного четырехразрядного компаратора, основанного на микросхеме 74HC85, без входных и выходных буферов. Если вы изучали предыдущие модули цифровой электроники с помощью learnabout-electronics, вы можете заметить, что уровень сложности на рис.4.3.4 намного больше, чем в предыдущих схемах. В модуле 2.1 было заявлено, что любая цифровая схема полагается всего на несколько типов логических элементов (И, ИЛИ, ИЛИ, ИЛИ, НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ и ИСКЛЮЧИТЕЛЬНОЕ ИЛИ), и даже этот список можно сократить, используя только И ИЛИ и НЕ для получения другие логические функции. Поэтому более сложные логические схемы по-прежнему используют комбинации этих основных функций, но только связи между ними и быстрое увеличение количества используемых вентилей усложняют их. , такие как 74HC85, называются «интегрированными устройствами среднего размера» или устройствами MSI, чтобы отличать их от устройств SSI (маломасштабных интегрированных), таких как базовые ИС логических вентилей, изученные в модулях 2.1 и 2.2. Хотя эти устройства кажутся (и являются!) Сложными, интересно сравнить количество отдельных транзисторов в этой схеме с теми, которые используются в схемах, описанных в более ранних модулях. На рис. 4.3.4 показан 31 вентиль (не считая пропущенных входных и выходных буферных вентилей), и каждый вентиль содержит около 4 транзисторов на вентиль, что дает общее количество транзисторов для этого типичного чипа MSI, состоящего из более чем 124 транзисторов, поэтому неудивительно, что схема выглядит сложной! Таким образом, эта небольшая ИС содержит больше транзисторов, чем, например, во многих аналоговых цветных телевизионных приемниках, однако эта схема делает гораздо меньше, чем требовалось бы от того же количества транзисторов в телевизоре, и ее работу намного проще понять, особенно если вы уже разбираетесь в работе основных логических вентилей. Обратите внимание на выходы на рис. 4.3.3, для A Когда две или более ИС соединены каскадом вместе, как показано на рис. 4.3.5, выходы первой ИС (представляющие 4 младших бита) подключаются к каскадным входам второй ИС и так далее.Окончательный результат сравнения отображается на трех каскадных выходах наиболее значимого 4-битного компаратора. Для обеспечения корректного сравнения каскадные входы первого (наименее значимого) компаратора должны быть подключены следующим образом: A B (контакт 4) = логический 0. A = B (вывод 3) = логика 1. Это также относится к одной ИС, если сравниваются только два 4-битных слова. состоят из стандартных вентилей И, ИЛИ и НЕ, которые сравнивают цифровые сигналы, присутствующие на их входных клеммах, и выдают выходной сигнал в зависимости от состояния этих входов. Например, помимо возможности складывать и вычитать двоичные числа, нам необходимо иметь возможность сравнивать их и определять, больше ли значение на входе A, меньше или равно значению на входе B и т. Д. Цифровой компаратор выполняет следующие функции: это использует несколько логических вентилей, которые работают на принципах булевой алгебры . Доступны два основных типа цифрового компаратора : Целью цифрового компаратора является сравнение набора переменных или неизвестных чисел, например A (A1, A2, A3,…. An и т. Д.), С постоянным или неизвестным значением, например B (B1 , B2, B3,…. Bn и т. Д.) И создают условие вывода или флаг в зависимости от результата сравнения.Например, компаратор величин из двух 1-битных входов (A и B) будет создавать следующие три выходных состояния при сравнении друг с другом. Это означает: A больше B, A равно B или A меньше B Это полезно, если мы хотим сравнить две переменные и хотим получить результат при достижении любого из трех вышеуказанных условий. Например, при достижении определенного числа счетчик выводит данные со счетчика. Рассмотрим простой 1-битный компаратор ниже. Тогда работа 1-битного цифрового компаратора приведена в следующей таблице истинности. Вы можете заметить две отличительные особенности компаратора из приведенной выше таблицы истинности.Во-первых, схема не различает ни два «0», ни две «1», поскольку выход A = B создается, когда они оба равны, либо A = B = «0», либо A = B = «1». . Во-вторых, выходное условие для A = B похоже на состояние обычно доступного логического элемента, функции Exclusive-NOR или Ex-NOR (эквивалентность) для каждого из n битов, что дает: Q = A ⊕ B фактически используют вентили Исключающее ИЛИ-ИЛИ в своей конструкции для сравнения соответствующих пар битов. Когда мы сравниваем два двоичных или двоично-десятичных значения или переменных друг с другом, мы сравниваем «величину» этих значений, логический «0» с логической «1», из которой происходит термин Magnitude Comparator . Помимо сравнения отдельных битов, мы можем разработать более крупные битовые компараторы путем каскадного объединения n из них и создания n-битного компаратора, как мы это делали для n-битного сумматора в предыдущем руководстве. Многобитовые компараторы могут быть сконструированы для сравнения целых двоичных или двоично-десятичных слов для получения вывода, если одно слово больше, равно или меньше другого. Очень хорошим примером этого является 4-битный компаратор величины . Здесь два 4-битных слова («полубайты») сравниваются друг с другом для получения соответствующего вывода, при этом одно слово подключается к входам A, а другое сравнивается со входом B, как показано ниже. Некоторые коммерчески доступные цифровые компараторы, такие как 4-битный компаратор амплитуды TTL 74LS85 или CMOS 4063, имеют дополнительные входные клеммы, которые позволяют «каскадировать» вместе большее количество отдельных компараторов для сравнения слов размером более 4 бит с компараторами амплитуды «n» — биты производятся. Эти каскадные входы подключаются непосредственно к соответствующим выходам предыдущего компаратора, как показано, для сравнения 8, 16 или даже 32-битных слов. При сравнении больших двоичных или двоично-десятичных чисел, как в приведенном выше примере, для экономии времени компаратор сначала сравнивает бит наивысшего порядка (MSB). Если равенство существует, A = B, тогда он сравнивает следующий младший бит и так далее, пока не достигнет бита самого низкого порядка (LSB). Если равенство все еще существует, то два числа считаются равными. Если обнаружено неравенство, либо A> B, либо A Цифровые компараторы — это интегральные схемы (ИС), которые сравнивают величину двух двоичных величин и определяют соотношение этих величин.Существует два основных типа цифровых компараторов: компараторы идентичности и компараторы величины. Компараторы идентичности показывают, равны ли два входа. Компараторы величин показывают, равны ли два входа и, если нет, какой вход больше или меньше. Обычно цифровые компараторы используются для сравнения входного напряжения с опорным напряжением. Логические схемы, включающие несколько отдельных компараторов, могут характеризовать большие группы входных сигналов.Цифровые компараторы могут работать синхронно с часами или асинхронно, включая достаточное усиление, чтобы заставить выходной сигнал перейти в насыщение. Задержка распространения — это временной интервал между подачей входного сигнала и появлением соответствующего выхода. Как и другие микросхемы, цифровые компараторы требуют минимального тока для активной работы и имеют диапазон рабочих температур.Некоторые цифровые компараторы устойчивы к радиации. Другие обеспечивают защиту от электростатического разряда (ESD). Другое логическое семейство, комплементарный металл-оксидный полупроводник (CMOS), использует комбинацию полевых транзисторов металл-оксид-полупроводник (MOSFET) p-типа и n-типа для реализации логических вентилей и других цифровых схем. для цифровых компараторов включают технологию перекрестных переключателей (CBT), арсенид галлия (GaAs), встроенную логику впрыска (I 2 L) и кремний на сапфире (SOS). Также доступны стрельба с логикой приемопередатчика (GTL) и стрельба с логикой приемопередатчика плюс (GTLP). доступны в различных типах корпусов ИС и с разным количеством контактов и триггеров. доступны в керамическом (CDIP) или пластиковом (PDIP) исполнении. Другие типы пакетов IC включают в себя пакет с малым контуром (SOP), пакет с тонким контуром (TSOP) и пакет с маленьким контуром (SSOP). JIS B 7536 — Электрические компараторы. A-A-58089 — Компаратор настольного типа с электронным усилением. DESC-DWG-84151 — Микросхемы, цифровые, маломощный ттл Шоттки, компаратор величин, монолитный кремний. 1-Source Electronic Components, Inc. 0 руб.38000 7,500 — Немедленно 800 2156-HA17393F-EL-E-ND 0 — Немедленно 571 Non-Stock 2156-CD74HCT688M-HC-ND УЛЬТРА-МАЛЫЙ, ОДИНОЧНЫЙ, КОМПАРАТОР $ 0,49000 1,467 — Немедленно 614 2156-MAX9030AXT-ND Навалом БЫСТРЫЙ 8-БИТНЫЙ СРАВНИТЕЛЬ ИДЕНТИЧНОСТИ $ 0.64000 2,383 — Немедленно 466 2156-CD74FCT521DTM-ND $67000 2,147 — Немедленно 451 2156-74AC11521DW-ND $97000 17,440 — Немедленно 311 2156-TL712CPS-ND BEYOND-THE 779 — Немедленно 256 2156-MAX9120EXK-ND 9034 9034 8-битный МАГНИТ19000 6,775 — Немедленно 252 2156-74HC688P-E-ND $ 1.96000 276 — Немедленно 1 2368-NTE4063B-ND Сумка КМОП 4-БИТНЫЙ МАГНИТНЫЙ КОМПАРАТОР $ 3,18000 165 — Immediate 95 2156-CD4585BD-ND Навалом $ 7.71000 7,064 — Немедленно 39 Non-Stock 2156-SN74AS885NT-TI-ND СЕЙЧАС NEXPERIA 74HC688PW — IDENTIT $ 0,24000 5,81312 LLC Inc. 1,236 2156-74HC688PW, 112-ND Bulk SN74HC684 8-БИТНАЯ ИДЕНТИФИКАЦИЯ / МАГНИТУ $ 4.89000 21,728 — Немедленно 9023 629023 74HC Объемный IC COMPARATOR IDENTITY 8B 20DIP $ 1,22000 432 — Немедленно 1 296-8361-5-ND Трубка ИДЕНТИЧНОСТЬ СРАВНИТЕЛЬНОГО КОМПЬЮТЕРА ИС 8B 20SOIC $ 2,60000 188 — Немедленно 1 D 1 D Трубка $ 0,09000 0 — Немедленно 2,671 Объемный 0 руб.19000 0 — Немедленно 1,336 2156-HA17903FP-EL-E-ND 1 доллар.00000 0 — Немедленно 251 2156-QS74FCT521CTS0-ND КВАДРАТНЫЙ ПРИВОД 107000 0 — Немедленно 78 2156-MAX9966BGCCQ-ND 9034 9034 $.87000 0 — Немедленно 134 2156-CA139AM-ND Навалом $ 338000 0 — Немедленно 50 2156-AM25LS2521PCB-ND $ 3.56000 0 — Немедленно 71 2156-LT1016CP-ND Навалом 0 — Немедленно 2 2156-CD4063BF-ND Навалом 9003- IC COMPARATOR 9023 9023 9023 ИДЕНТ. 0 — Немедленно — Non-Stock 74AC521SC-ND Tube IC COMPARATOR IDENTITY 8B 20DIP Устарело 0 — Немедленно — Non-Stock 74ACT521PC-ND Метод замка и ключа зависит от конструкции TSC, который состоит из четырех компонентов. ) контролирует текущий режим TSC; компаратор тестовых ключей используется только тогда, когда TC включен в первый раз, возвращая безопасный или небезопасный результат; LFSR выбирает одну субцепь во время операции сканирования и управляет выходным мультиплексором; и декодер переводит выходной сигнал LFSR в схему однократного включения.На рисунке 9.10 показаны сигналы, передаваемые между каждым из компонентов TSC. Связь между каждым из компонентов сведена к минимуму, чтобы уменьшить маршрутизацию и общий размер TSC. Рисунок 9.10. Схема проектирования ЦТП. Блок конечного автомата состоит из простой логики состояния и двух счетчиков. Логика состояния управляет компаратором тестовых ключей и LFSR. FSM также определяет, в соответствии с ответом компаратора тестовых ключей, следует ли заполнять LFSR вектором из SI, или использовать случайное начальное число, созданное в LFSR при сбросе системы.Случайное начальное число может быть создано множеством различных способов, в том числе с использованием генератора истинных случайных чисел (TRNG). Первым счетчиком, используемым в блоке FSM, был счетчик log2 (q), который используется только для заполнения LFSR, где q — длина LFSR. Второй счетчик — это счетчик log2 (l), используемый для тактирования LFSR после -1 циклов, сдвигающего содержимое LFSR для включения новой подцепи. Компаратор тестового ключа используется один раз, только после того, как система была перезагружена и впервые переведена в тестовый режим.Чтобы компаратор оставался маленьким, и поскольку тестовый ключ из SI считывается последовательно, каждый бит последовательно проверяется на соответствие ключа, хранящегося на микросхеме в защищенной памяти. При сравнении каждого бита в FF сохраняется результат выполнения, который в конечном итоге считывается автоматом. После k циклов конечный результат считывается автоматом, определяющим, будет ли TSC работать в безопасном режиме или продолжит работу в небезопасном режиме. При разработке технологии Lock & Key цель состоит в том, чтобы иметь возможность гарантировать безопасность цепей сканирования, сохраняя при этом простоту и независимость конструкции.Чтобы декодер не стал слишком сложным, LFSR с примитивной полиномиальной конфигурацией позволяет выбрать m = 2q-1 субцепей, где q — размер LFSR в безопасном режиме. Использование примитивного полинома позволяет выбрать все субцепи один раз и только один раз во время цикла тестирования. Если используется непримитивная полиномиальная конфигурация, если не включена дополнительная логика, некоторые субцепи могут выбираться более одного раза или никогда не выбираться вообще. Используя биты q из LFSR, декодер включает один из m выходов, оставляя остальные равными нулю.Поскольку существует по крайней мере один примитивный полином для всех значений q , LFSR гарантированно выберет каждую подцепочку один раз перед повторением для любой длины LFSR [35]. Количество FF в дизайне до вставки отсканированного изображения не обязательно должно делиться без остатка на м . Есть две возможности решить эту проблему. Первый — это включение фиктивных FF (в форме контрольных точек: контрольная контрольная точка и контрольная точка наблюдения), что стало обычной практикой при тестировании задержки [35].Общее количество требуемых FF, n , и общее количество необходимых фиктивных FF, ndFF, записывается следующим образом: (9.1) ndFF = {0when (nmodm) = 0, m− (nmodm) в противном случае. Второй вариант — дополнить части тестового шаблона, относящиеся к более коротким субцепям. Это немедленно сдвинет любые фиктивные значения в начале шаблона и не повлияет на функциональную работу CUT. Этот вариант требует меньше усилий при проектировании, так как он не использует дополнительную логику, но увеличивает накладные расходы на тестовый шаблон.Однако из-за методов тестового сжатия накладные расходы будут минимальными, поскольку фиктивные значения могут быть установлены на значения, которые максимизируют сжатие. Выбор примитивного полинома значительно упрощает конструкцию декодера. Декодер может напрямую преобразовывать вывод LFSR в серию нулей и выбирать один для непосредственного управления каждой подцепочкой. Этот метод не только сокращает время разработки, но также снижает накладные расходы на область TSC в целом, поскольку не требуется дополнительная логика для обеспечения того, чтобы все субцепи были выбраны один раз во время цикла тестирования. Проблема с использованием LFSR с примитивной полиномиальной конфигурацией заключается в предсказуемости его поведения. Если бы LFSR оставался неизменным для работы в небезопасном режиме, определение порядка не заняло бы много времени, поскольку порядок всегда один и тот же, только начальная и конечная точки будут отличаться. Чтобы избежать этой предсказуемости, необходимо изменить конфигурацию LFSR, если он установлен в небезопасный режим. Путем модификации LFSR для включения дополнительных r -битов для работы в небезопасном режиме, примитивный полиномиальный LFSR становится непримитивным полиномиальным LFSR.Как видно на рис. 9.11, дополнительные биты скрыты за мультиплексором и становятся активными только при работе в небезопасном режиме. Интерфейс между LFSR и декодером не изменяется. Поскольку исходный LFSR составляет только меньшую часть LFSR небезопасного режима, становится возможным повторный выбор одной и той же подцепи в течение одного цикла тестирования, что приводит к более сложному выходу. Более короткая периодичность не является проблемой, поскольку это было в безопасном режиме, поскольку не требуется доступ ко всем субцепям, но фасад полностью функциональной цепочки сканирования все еще существует. Рисунок 9.11. Изменяемый LFSR определяется режимом безопасности TSC. Сравнение данных необходимо в цифровых системах при выполнении арифметических или логических операций. Это сравнение определяет, является ли одно число больше, равно или меньше другого числа. Цифровой компаратор широко используется в комбинационных системах и специально разработан для сравнения относительных величин двоичных чисел. Они также доступны в форме ИС с различными конфигурациями сравнения битов, такими как 4-битная, 8-битная и т. Д.Более одного компаратора также могут быть подключены в каскадном порядке для сравнения чисел большей длины. Каждый раз, когда мы хотим сравнить два двоичных числа, сначала мы должны сравнить наиболее значимые биты. Если эти старшие биты равны, то нам нужно сравнить только следующие значащие биты. Но если MSB не равны, тогда будет ясно, что либо A больше, либо меньше B, и процесс сравнения прекращается. Например, два 2-битных числа: A = A1A0 и B = B1B0.Если A1 не равно B1, то ясно, что A больше B для A1 = 1 и B1 = 0, иначе A меньше B для A0 = 0 и B0 = 1. На этом этапе процесс сравнения прекращается. Если старшие биты равны, то есть только A1 = B1, тогда нам нужно сравнить следующие значащие биты A0 и B0 и решить, больше ли число, меньше или равно. Таким образом, компаратор выдает три выхода, поскольку L, E и G соответствуют сравнениям меньше, равно и больше. Цифровые компараторы могут быть двух типов Компаратор идентификации Компараторы, которые имеют только одну выходную клемму и выдают выходной сигнал либо низкий, либо высокий, являются компараторами идентичности. Компаратор амплитуды Компараторы с тремя выходными клеммами и проверяет наличие трех условий, т.е. больше или меньше или равно компаратору величины. В начало Цифровой компаратор величин — это комбинационная схема, которая сравнивает два цифровых или двоичных числа (рассмотрим A и B) и определяет их относительные величины, чтобы выяснить, равно ли одно число, меньше чем или больше, чем другое цифровое число. Три двоичные переменные используются для обозначения результата сравнения: A> B, A Эти компараторы могут сравнивать 2-битные, 4-битные и 8-битные числа в зависимости от требований приложения. Они доступны в виде ИС семейства TTL, а также логики CMOS, и некоторые из этих ИС включают IC 7485 (4-битный компаратор), IC 4585 (4-битный компаратор в семействе CMOS) и IC 74AS885 (8-битный компаратор). В начало Компаратор, используемый для сравнения двух битов, то есть двух чисел, каждое из которых состоит из одного бита, называется однобитовым компаратором. Он состоит из двух входов, позволяющих двум однобитовым числам и трем выходам генерировать меньшие, равные и большие выходы сравнения. На рисунке ниже показана блок-схема однобитового компаратора амплитуды. Этот компаратор сравнивает два бита и выдает один из 3 выходов как L (A Таблица истинности для однобитового компаратора приведена ниже. Когда A0 B0 = 00 и 11, оба входа равны, поэтому выход A = B будет высоким. Когда A0 B0 = 01, B больше, чем A, и, следовательно, AB активен. Из таблицы истинности логические выражения для каждого выхода могут быть выражены как Используя эти логические выражения, мы можем реализовать логическую схему для этого компаратора, используя два элемента И, один элемент НЕ и один элемент Ex-NOR. как показано на рисунке ниже.Логические элементы И используются, чтобы определить, является ли двоичная цифра меньше, чем больше, чем другой бит, тогда как вентиль Экс-ИЛИ используется, чтобы определить, равны ли два двоичных числа или нет. На рисунке один логический элемент И имеет входы A0 (B0) ̅, а другой — входы (A0) ̅ B0. Следовательно, один выход логического элемента И равен 1, если A0> B0 (т. Е. A0 = 1 и B0 = 0), и равен нулю, если A0 Элемент Ex-NOR имеет входы A0 B0, следовательно, выход элемента Ex-NOR будет 1, если A0 = B0, и выход будет 0, если A0 не равно B0. В начало 2-битный компаратор сравнивает два двоичных числа, каждое из двух битов, и определяет их соотношение, например, одно число равно или больше или меньше другого. На рисунке ниже показана блок-схема двухразрядного компаратора с четырьмя входами и тремя выходами. Первое число A обозначено как A = A1A0, а второе число обозначено как B = B1B0. Этот компаратор выдает три выхода: G (G = 1, если A> B), E (E = 1, если A = B) и L (L = 1, если A Упрощение k-карты для приведенной выше таблицы истинности выглядит следующим образом. Из приведенного выше упрощения k-карты каждый выход может быть выражен как Используя полученное выше логическое уравнение для каждого выхода, логическая диаграмма может быть реализована с использованием четырех вентилей НЕ, семи вентилей И, двух вентилей ИЛИ. ворота и два ворот Ex-NOR. На рисунке ниже показана логическая схема 2-битного компаратора, использующего базовые логические элементы. Также возможно построить этот компаратор путем каскадного соединения двух 1-битных компараторов. В начало Может использоваться для сравнения двух 4-битных слов. Два 4-битных числа: A = A3 A2 A1 A0 и B3 B2 B1 B0, где A3 и B3 являются старшими битами. Он сравнивает каждый из этих битов одного числа с битами другого числа и производит один из следующих выходных данных как A = B, A B.Формулировки выходной логики этого преобразователя: Из приведенных выше утверждений вывод A> B логическое выражение может быть записано как Равный вывод получается, когда все отдельные биты одного числа точно совпадают с соответствующими битами другого числа.Тогда логическое выражение для выхода A = B может быть записано как E = (A3 Ex-NOR B3) (A2 Ex-NOR B2) (A1 Ex-NOR B1) (A0 Ex-NOR B0) Из приведенного выше вывести логические выражения, логическая схема для этого компаратора может быть реализована с использованием логических вентилей, как указано ниже. В этом случае четыре выхода вентилей Ex-NOR применяются к вентилю AND, чтобы получить двоичную переменную E или A = B. Два других выхода также используют выходы Ex-NOR для генерации логических функций, как показано на рисунке. 4-битный компаратор в основном доступен в форме ИС, и общий тип этой ИС — 7485.Эту ИС можно использовать для сравнения двух 4-битных двоичных слов путем заземления входов разъема I (A> B), I (A В дополнение к обычному компаратору эта ИС снабжена каскадными входами, чтобы облегчить каскадное соединение нескольких компараторов. Любое количество битов можно сравнить путем каскадного соединения нескольких из этих микросхем компаратора. В начало 8-битный компаратор сравнивает два 8-битных числа путем каскадирования двух 4-битных компараторов.Схема подключения этого компаратора показана ниже, в которой выходы компаратора низшего порядка A Для компаратора низшего порядка каскадный вход A = B должен быть подключен к высокому уровню, а два других каскадных входа A, B должны быть подключены к низкому уровню. Выходы компаратора более высокого порядка становятся выходами этого восьмиразрядного компаратора. В начало В начало Логический компаратор Данный проект направлен на создание современной версии устаревшего HP10529A HP10529 — довольно простое устройство, выпущенное HP в начале семидесятых годов.Несмотря на свою простоту, он довольно эффективен для поиска неисправных ИС TTL. Основная идея HP10529A заключается в том, что у вас есть эталонная ИС на небольшой плате, вставленной в логический компаратор HP10529A. Затем вы вставляете клипон IC в микросхему, которая требует тестирования.

Затем HP10529A сравнит выходы опорного сигнала и тестируемого устройства. Если есть разница, загорится светодиод. HP10529A использует компаратор 74L86, а также драйвер с открытым коллектором для управления светодиодом.На выходе 74L86 есть конденсатор для размытия сигнала по времени.

а также схему фильтрации нижних частот на выходе с открытым коллектором, чтобы светодиод оставался включенным дольше, если есть короткий импульс, который является ошибочным. Когда выход открытого коллектора NOR идет на него, он разряжает конденсатор, а также создает низкий уровень на входе инвертора 74L04. Таким образом, NOR еще какое-то время будет иметь низкий выход. Если сигнал на эталонной плате является входом, то сигнал от DUT si подключен как к эталонной микросхеме, так и к обоим входам 74LS86.Если сигнал является выходным, эталонная микросхема подключается к верхнему входному сигналу 74LS86, а DUt подключается к нижнему входу 74LS86 на схемах выше. Первая проблема с HP10529 заключается в том, что он устарел. Есть такие, которые продаются на Ebay по довольно высоким ценам. Но если вы его получите, в него войдет, возможно, всего несколько плат адаптеров. Также должен быть вариант с разъемом ZIF, но я никогда не видел его на Ebay. Решением было бы сделать меня своим.Это будет дешевле, чем покупать Ebay в США и отправлять их в Швецию. Это топология печатной платы. Идея состоит в том, чтобы поместить эталонную ИС в разъем ZIF, а затем запрограммировать входы, вставив перемычку в исходное положение в двух рядах заголовков контактов. Я изучаю вариант создания небольшой печатной платы, которую можно было бы протолкнуть над заголовками PIN и, таким образом, можно было бы аналогичным тем, которые используются с HP10529: библиотека эталонных плат для общих типов ИС TTL. Схема растяжения импульса менее продвинута в том, что я передал сигнал обратной связи через конденсатор, который растягивал бы сигнал. Это в основном из-за нехватки места и возможности прокладки такого количества проводов на плате. К сожалению, в текущей компоновке есть небольшая неприятная ошибка. Электролитический конденсатор подключается к светодиоду напрямую, а не к выходу драйвера с открытым коллектором. Это должно быть исправлено в макете, но упорядоченные доски неправильные, и их нужно было закрепить с помощью небольших проводов и надрезов… Рис. 4.3.3 Четырехразрядный компаратор величины 74HC85

Среднемасштабные интегрированные устройства (MSI)

Рис.4.3.4 Четырехразрядный компаратор величины

ИС Рис. 4.3.5 Восьмиразрядный компаратор величин с использованием двух микросхем 74HC85

Компараторы в каскаде

Цифровые или двоичные компараторы

Схема 1-битного цифрового компаратора

Таблица истинности цифрового компаратора

Входы

Выходы

В

А

А> В

А = В

А <В

0

0

0

1

0

0

1

1

0

0

1

0

0

0

1

1

1

0

1

0

4-битный компаратор величины

Компаратор 8-битных слов

: типы, характеристики, применение

Важные характеристики

Цифровые компараторы различаются по напряжению питания, количеству битов, задержке распространения, рабочему току и рабочей температуре. Напряжение питания составляет от -5 В до 5 В и включает промежуточные напряжения, такие как -4,5 В, -3,3 В, -3 В, 1,2 В, 1,5 В, 1,8 В, 2.5 В, 3 В, 3,3 В и 3,6 В. Количество битов — это размер двоичных чисел, которые цифровой компаратор может обработать, так что, например, 4-битный компаратор принимает два входных числа, каждое с четырьмя битами . Как выбрать

Выбор цифровых компараторов требует анализа логических семейств. Транзисторно-транзисторная логика (TTL) и связанные технологии, такие как Fairchild Advanced Schottky TTL (FAST), используют транзисторы в качестве цифровых переключателей. Напротив, логика с эмиттерной связью (ECL) использует транзисторы для управления током через вентили, которые вычисляют логические функции. Варианты упаковки

Базовые типы корпусов ИС

Варианты упаковки BGA

QFP Варианты упаковки

Связанные стандарты

Список литературы

Кредит изображения:

Интегральные схемы (ИС) | Логика — Компараторы

125 Rochester Electronics, LLC Renesas Electronics America Inc * Активный — — — — — — — — — — — — 125 — 000 Rochester Electronics, LLC Harris Corporation 74HCT 74HCT Устаревший Identity Comparator 8 Активный низкий A = B 4,5 В ~ 5,5 В 4 мА, 4 мА 34 нс при 4,5 В, 50 пФ 8 µA -55 ° C C 20-SOIC (0.295 дюймов, ширина 7,50 мм) 20-SOIC Поверхностный монтаж Maxim Integrated * Активный — — — — — 9035 — — — — — Rochester Electronics, LLC Harris Corporation * 5

5

5 9023 — — — — — — — — — — Rochester Electronics, LLC Texas Instruments * 5 5

— — — — — — — — — — Rochester Electronics, LLC Texas Instruments * 12 5 * 5 9034 9034 — 9034 9034 — 9034 — — — — — — — — — — 18000 Rochester Electronics, LLC Maxim Integrated * 9034 — — — — — — — — — — Rochester Electronics, LLC Renesas Electronics America Inc 74HC 9033 9033 9023 9033 Identity Comparator 8 Активный низкий A = B 2 В ~ 6 В 5,2 мА, 5,2 мА 29 нс при 6 В, 50 пФ 8 мкА -40 ° C ~ 125 ° C 9036 — — NTE Electronics, Inc NTE Electronics, Inc 4000B Active 4 Активный высокий A 3 В ~ 18 В 2,4 мА, 2,4 мА 350 нс при 15 В, 50 пФ 100 мкА -55 ° C ~ 125 ° C 14-DIP (0.260 дюймов, 6,6 мм) 14-DIP Сквозное отверстие Корпорация * Активный — — — — — 9035 — 9012 — — — — Rochester Electronics, LLC Texas Instruments 74AS Устаревший Компаратор амплитуды 8 Активный высокий A 4,5 В ~ 5,5 В 2 мА, 20 мА 17,5 нс при 5 В, 50 пФ — 0 ° C 70 ° C 24-DIP (0.300 дюймов, 7,62 мм) 24-PDIP Сквозное отверстие 74HC Active Identity Comparator 8 Active Low 5.2 мА, 5,2 мА 29 нс при 6 В, 50 пФ 8 мкА -40 ° C ~ 125 ° C 20-TSSOP (0,173 дюйма, ширина 4,40 мм) 20-TSSOP Крепление на поверхность Rochester Electronics, LLC Texas Instruments Texas Instruments Активный Компаратор величин 8 Активный низкий A = B, A> B 2V ~ 6V 5.2 мА, 5,2 мА 47 нс при 6 В, 50 пФ — -40 ° C ~ 85 ° C 20-DIP (0,300 дюйма, 7,62 мм) 20-PDIP Сквозное отверстие Texas Instruments Texas Instruments Активный Компаратор идентификации 8 Активный низкий A = B 2V ~ 6V 5.2 мА, 5,2 мА 36 нс при 6 В, 50 пФ 8 мкА -40 ° C ~ 85 ° C 20-DIP (0,300 дюйма, 7,62 мм) 20-PDIP Сквозное отверстие Renesas Electronics America Inc Renesas Electronics America Inc Активный Identity Comparator 8 Активный Низкий A = B 4.75 В ~ 5,25 В 15 мА, 48 мА 7,2 нс при 5 В, 50 пФ 10 мкА -40 ° C ~ 85 ° C 20-SOIC (0,295 дюйма, ширина 7,50 мм) 20-SOIC Поверхностный монтаж Rochester Electronics, LLC Texas Instruments 10 22 21P Активный — — — — — — — — — — — — Rochester Electronics, LLC Renesas Electronics America Inc * Активный — — — — — — — — — — — — СЕРИЯ AR Rochester Electronics, LLC Quality Semiconductor * Активный — — — — — — — — — — Rochester Electronics, LLC Maxim Integrated * 9034 — — — — — — — — — — Rochester Electronics, LLC Harris Corporation * 9034 9034 — — — — — — — — — — Rochester Electronics, LLC Advanced Micro Devices — 22 Bulk 8 — — 4,75 В ~ 5,25 В 440 мкА, 12 мА 15 нс при 5 В, 15 пФ 40 мА 0 ° C ~ 70 ° C 20-DIP 20-DIP 20-DIP Сквозное отверстие Rochester Electronics, LLC Texas Instruments * 9034 9034 — — — — — — — — — — ЛОГИЧЕСКАЯ ИНФОРМАЦИЯ94000 Rochester Electronics, LLC Harris Corporation * 9034 — — — — — — — — — — ON Semiconductor ON Semiconductor 74AC Ideity Compsole Активный низкий A = B 2 В ~ 6 В 24 мА, 24 мА 8.5 нс при 5 В, 50 пФ 4 мкА -40 ° C ~ 85 ° C 20-SOIC (0,295 дюйма, ширина 7,50 мм) 20-SOIC Поверхностный монтаж ON Semiconductor ON Semiconductor Устарело Компаратор идентификации 8 Активный Низкий A = B 4.5 В ~ 5,5 В 24 мА, 24 мА 10 нс при 5 В, 50 пФ 4 мкА -40 ° C ~ 85 ° C 20-DIP (0,300 дюйма, 7,62 мм) 20-PDIP Сквозной Отверстие Компараторы — обзор | Темы ScienceDirect

9.2.6.2 Конструкция замка и ключа

Цифровой компаратор и компаратор величин

Цифровой компаратор

Однобитовый компаратор величины

2-битный компаратор

4-битный компаратор

8-битный компаратор

Приложения компараторов

GitHub — MattisLind / логический компаратор: логический компаратор

Компоновка печатной платы