Какие особенности имеет последовательное соединение полевых транзисторов. Каковы преимущества и недостатки такого соединения. Как правильно соединять полевые транзисторы последовательно. Какие схемы используются для последовательного соединения.

Особенности последовательного соединения полевых транзисторов

Последовательное соединение полевых транзисторов имеет ряд важных особенностей:

- Позволяет увеличить рабочее напряжение схемы

- Требует согласования параметров транзисторов

- Усложняет схему управления затворами

- Снижает быстродействие по сравнению с одиночным транзистором

- Увеличивает потери в открытом состоянии

Основная цель последовательного соединения — повышение максимального рабочего напряжения схемы. При этом возникают определенные сложности с управлением и согласованием параметров транзисторов.

Преимущества последовательного соединения полевых транзисторов

Основные преимущества последовательного соединения полевых транзисторов:

- Увеличение максимального рабочего напряжения схемы

- Возможность использования транзисторов с меньшим допустимым напряжением

- Улучшение теплового режима за счет распределения мощности

- Снижение паразитных емкостей

- Повышение надежности за счет резервирования

Главное преимущество — возможность работы при более высоких напряжениях. Это позволяет создавать высоковольтные ключи на основе низковольтных транзисторов.

Недостатки последовательного соединения полевых транзисторов

К основным недостаткам последовательного соединения полевых транзисторов можно отнести:

- Усложнение схемы управления затворами транзисторов

- Необходимость согласования параметров транзисторов

- Увеличение потерь в открытом состоянии

- Снижение быстродействия схемы

- Возможные проблемы с синхронизацией переключения

- Удорожание конструкции

Наиболее существенный недостаток — сложность обеспечения синхронного и согласованного управления всеми транзисторами в цепочке. Это требует специальных схемотехнических решений.

Правила последовательного соединения полевых транзисторов

При последовательном соединении полевых транзисторов необходимо соблюдать следующие основные правила:

- Использовать транзисторы с максимально близкими параметрами

- Обеспечить синхронное управление затворами всех транзисторов

- Выравнивать напряжения на транзисторах с помощью резисторов

- Защищать затворы от перенапряжений стабилитронами

- Использовать снабберные цепи для улучшения коммутации

Соблюдение этих правил позволяет создать надежную схему последовательного соединения полевых транзисторов с предсказуемыми характеристиками.

Схемы последовательного соединения полевых транзисторов

Существует несколько основных схем последовательного соединения полевых транзисторов:

- С разделительными трансформаторами в цепях управления

- С резистивными делителями для смещения затворов

- С емкостными делителями напряжения

- С оптронной развязкой управляющих сигналов

- С интегральными драйверами затворов

Выбор конкретной схемы зависит от требований по быстродействию, рабочему напряжению, мощности и других параметров проектируемого устройства.

Расчет параметров схемы последовательного соединения

При проектировании схемы последовательного соединения полевых транзисторов необходимо выполнить следующие основные расчеты:

- Определить требуемое количество последовательно соединяемых транзисторов

- Рассчитать напряжения на каждом транзисторе

- Выбрать номиналы выравнивающих резисторов

- Рассчитать параметры снабберных цепей

- Определить требования к схеме управления затворами

Правильный расчет всех элементов схемы позволяет обеспечить надежную и эффективную работу последовательно соединенных полевых транзисторов.

Применение последовательного соединения полевых транзисторов

Последовательное соединение полевых транзисторов применяется в следующих областях:

- Высоковольтные ключи и коммутаторы

- Импульсные источники питания большой мощности

- Инверторы для солнечных электростанций

- Преобразователи для электротранспорта

- Мощные усилители класса D

- Системы плазменной резки и сварки

Основная область применения — силовая электроника, где требуется коммутация высоких напряжений и больших токов.

Перспективы развития технологии последовательного соединения транзисторов

Перспективные направления совершенствования технологии последовательного соединения полевых транзисторов:

- Разработка специализированных драйверов для управления

- Применение новых типов полупроводниковых приборов (SiC, GaN)

- Интеграция схем управления и защиты в корпус транзистора

- Использование цифровых методов балансировки напряжений

- Создание модульных конструкций высоковольтных ключей

Развитие технологии позволит упростить применение последовательного соединения и расширить области его использования в силовой электронике.

Как правильно соединять транзисторы. На реальных примерах

zakruti.com » ru » Знания, наука, образование » ElectronicsClub

содержание видео

Рейтинг: 4.5; Голоса: 2

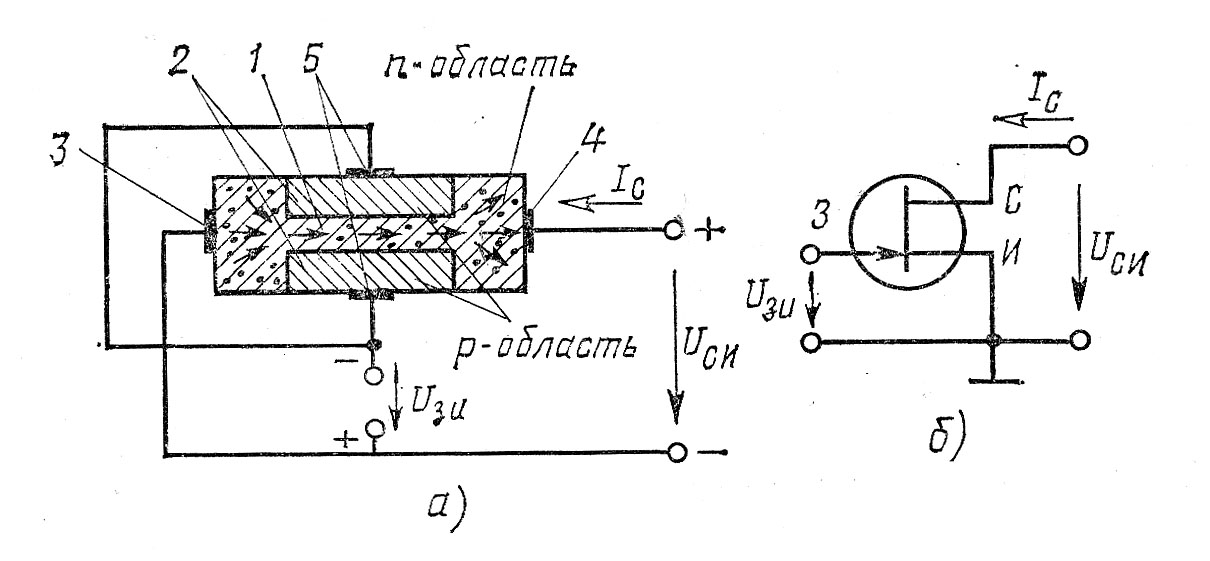

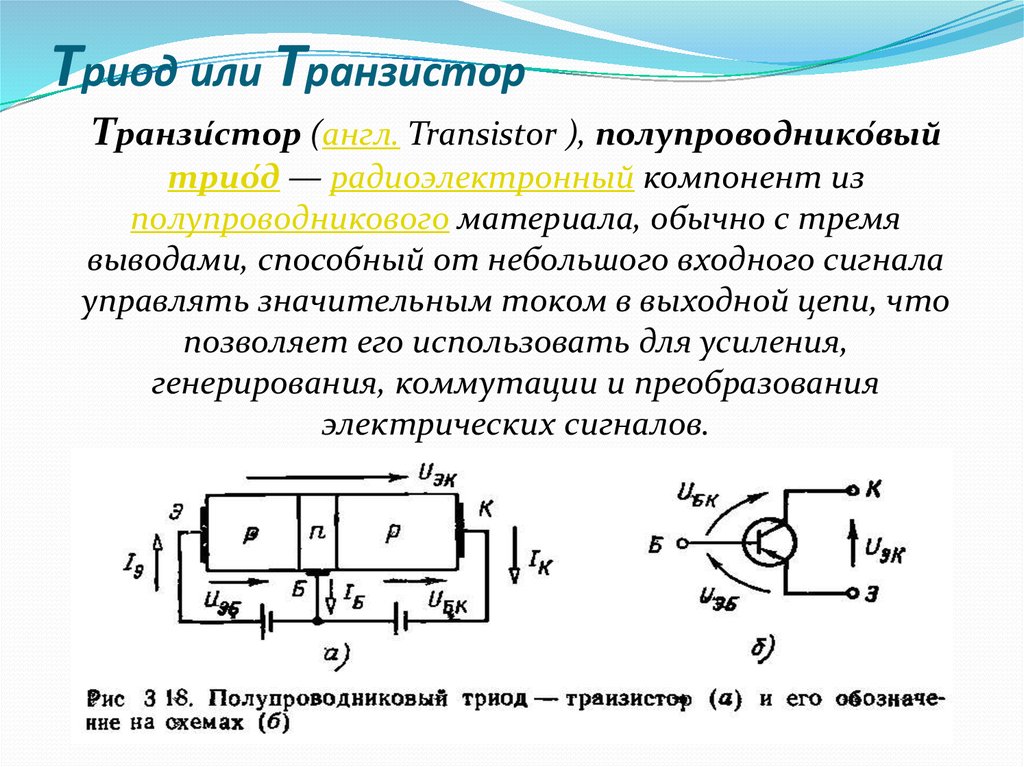

Полевой транзистор MOSFET управляется потенциалом или напряжением. Биполярный транзистор является токовым полупроводниковым прибором. Для его управления необходимо, чтобы протекал ток на переходе база эмиттер. Поэтому выдвигаются разные требования для полупроводниковых ключей разных типов при их соединении нескольких единиц.

Последовательное соединение транзисторов не допускается, так как вследствие наличия разброса характеристик приборов даже одного тика и из одной партии, один из нескольких транзисторов откроется быстрей. Тогда к оставшемуся полупроводниковому ключу будет приложена большая доля напряжения. В результате наступит его пробой, а затем пробьется и оставшийся ключ.

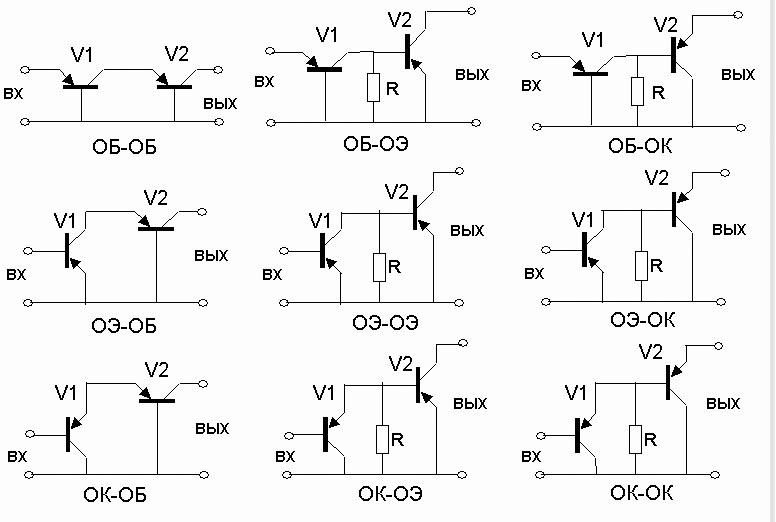

При параллельном соединении биполярных транзисторов в цепь эмиттера устанавливается токовыравнивающий резистор.

Дата: 2021-11-17

← STM32 или AVR. Как изучать программирование микроконтроллеров.

Как изучать программирование микроконтроллеров.

Что такое выход с Открытым Коллектором, открытым стоком →

Похожие видео

Эти 3 ошибки во время ходьбы уничтожают твой позвоночник и суставы навсегда. Никогда не ходи так!

• Антон Алексеев

2, 5 метровые женщины в кокошниках ПОХОРОНЕНЫ на допотопных кладбищах Турции и Египта

• Альтернативная история

Вот откуда на Земле взялись ГОРЫ ПЕСКА! Бархан САРЫКУМ

• Альтернативная история

Жестокая допотопная война ОРЛА со ЛЬВОМ не прекращается и в НАШЕ ВРЕМЯ

• Альтернативная история

Бодо Бородо. Снежный барс Русское географическое общество

• Русское географическое общество

Юэчжи и Кушанская империя

• Исторические фильмы

Другие видео канала

15:23

Урок 9. ПЕРЕМЕННЫЙ РЕЗИСТОР

12:17

Урок 8. РЕЗИСТОР СОПРОТИВЛЕНИЕ

16:16

Урок 7. ЗАКОН ОМА простыми словами с примерами

8:22

Урок 6. Что такое НАПРЯЖЕНИЕ

Что такое НАПРЯЖЕНИЕ

9:3

Урок 5. Какая Скорость электрического тока

11:16

КРУТОЙ АКУСТИЧЕСКИЙ ВЫКЛЮЧАТЕЛЬ света своими руками

11:25

7:6

Урок 3. Действительное Направление электрического тока

18:44

Урок 2. Электрический ток ЭДС — электродвижущая сила

18:43

Как подключить МОЩНЫЙ СВЕТОДИОД!

Не выдержать напряжения. Почему нельзя подключать электронные нагрузки последовательно?, статьи по электронике

Мы продолжаем знакомить читателей с материалами, посвященными базовым понятиям и подходам в использовании источников питания (ИП), современным решениям в данной области и уникальным функциям, помогающим решить самые сложные задачи, возникающие при тестировании. В этом номере инженер по системам электропитания и ведущий раздела по системам электропитания объединенного блога Keysight Technologies в России Алексей Телегин обсуждает особенности подключения электронных нагрузок.

Краткий ответ на вопрос подзаголовка этой статьи звучит следующим образом: потому что превышение допустимого напряжения, скорее всего, приведет к повреждению как минимум одной из таких нагрузок. Но данная тема требует развернутого объяснения.

Начнем с краткого пояснения того, что представляет собой электронная нагрузка и для чего она используется. Сразу оговорюсь: речь пойдет об электронных нагрузках постоянного тока. Электронная нагрузка постоянного тока — это электрический прибор с двумя клеммами для подключения, который потребляет мощность от источника постоянного тока. Нагрузки используются для тестирования источников постоянного тока. Любое устройство с источником выходной мощности постоянного тока (DC) — например, источник питания постоянного тока, преобразователь DC/DC, аккумулятор, топливный элемент или солнечная батарея — может быть нагружено посредством электронной нагрузки.

Рис. 1. Электронная нагрузка Keysight Technologies

Так, для тестирования источника питания постоянного тока с фиксированным выходным напряжением с номиналами 20 В, 5 A, 100 Вт нужно соединить выход источника питания с электронной нагрузкой с номинальными характеристиками (равными или превышающими номиналы источника питания), которая может потреблять постоянный ток от этого источника питания. Поскольку источник питания регулирует напряжение (20 В), нагрузка должна регулировать ток, потребляемый ею от этого источника (до 5 А). Если источник питания является источником постоянного тока, нагрузка должна быть способна потреблять питание с одновременным регулированием напряжения. Большинство электронных нагрузок можно настроить на потребление питания путем регулирования постоянного напряжения (CV) или постоянного тока (CC). Многие электронные нагрузки также можно настроить на регулирование постоянного сопротивления (CR) на входных клеммах, а некоторые блоки нагрузки способны регулировать постоянную мощность (CP).

Поскольку источник питания регулирует напряжение (20 В), нагрузка должна регулировать ток, потребляемый ею от этого источника (до 5 А). Если источник питания является источником постоянного тока, нагрузка должна быть способна потреблять питание с одновременным регулированием напряжения. Большинство электронных нагрузок можно настроить на потребление питания путем регулирования постоянного напряжения (CV) или постоянного тока (CC). Многие электронные нагрузки также можно настроить на регулирование постоянного сопротивления (CR) на входных клеммах, а некоторые блоки нагрузки способны регулировать постоянную мощность (CP).

Если тестируемый источник питания имеет выходное напряжение, превышающее величину, которую принимает одна электронная нагрузка, то возникает возникнуть мысль: а не подключить ли несколько входов нагрузок последовательно для решения проблемы повышенного напряжения? В конце концов, ведь можно же последовательно соединять выходы источника питания для увеличения напряжения, так почему бы не проделать то же самое с нагрузками?

Последовательное соединение электронных нагрузок может привести к тому, что на входы одной из нагрузок будет подано напряжение, превышающее ее возможности, а это может стать причиной повреждения нагрузки. Итак, есть намерение подключить нагрузки последовательно, потому что одной нагрузке не хватает номинального напряжения, чтобы справиться с напряжением источника постоянного тока. Но, поскольку сопротивление на входах одной из последовательно подключенных нагрузок во время тестирования снижается до минимального (практически до состояния короткого замыкания), напряжение от источника постоянного тока может появиться на входах других последовательно соединенных нагрузок цепи. Далее возможно несколько сценариев развития событий, способных привести к разрушительным последствиям. Чтобы разобраться в этих сценариях, сначала нужно понять, как действует электронная нагрузка.

Итак, есть намерение подключить нагрузки последовательно, потому что одной нагрузке не хватает номинального напряжения, чтобы справиться с напряжением источника постоянного тока. Но, поскольку сопротивление на входах одной из последовательно подключенных нагрузок во время тестирования снижается до минимального (практически до состояния короткого замыкания), напряжение от источника постоянного тока может появиться на входах других последовательно соединенных нагрузок цепи. Далее возможно несколько сценариев развития событий, способных привести к разрушительным последствиям. Чтобы разобраться в этих сценариях, сначала нужно понять, как действует электронная нагрузка.

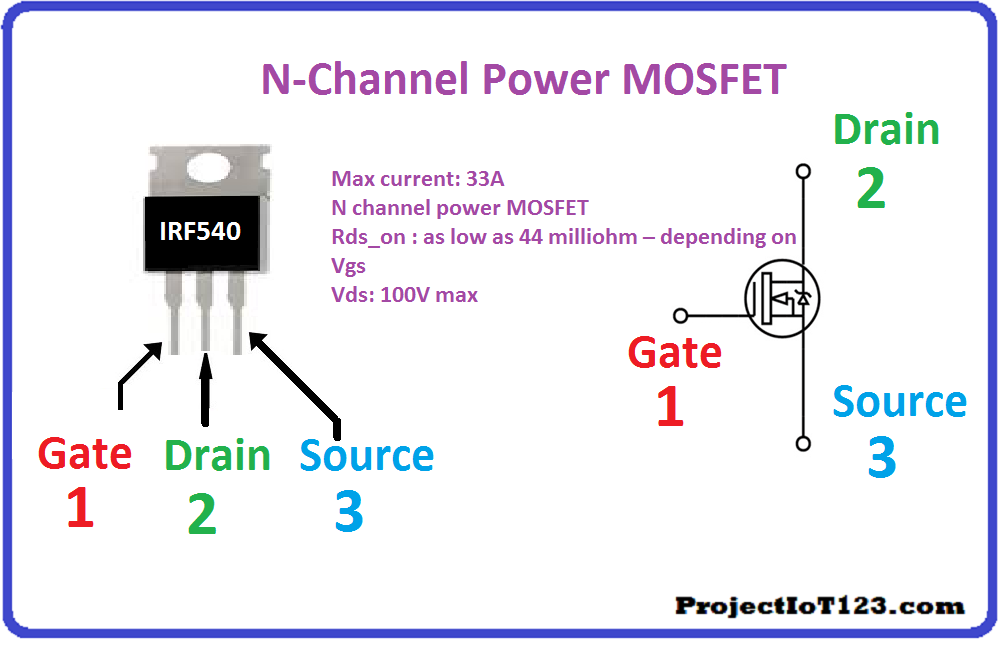

Нагрузки работают по принципу регулирования проводимости полевых транзисторов на входных клеммах. Данный процесс осуществляется с помощью контура обратной связи для корректировки измеряемого уровня (например, входного тока) таким образом, чтобы он был равен контрольному уровню — в нашем случае заданной силе тока.

Одна из проблем, связанных с последовательным соединением нескольких электронных нагрузок для соответствия более высоким напряжениям, возникает, если обе нагрузки настроены на работу в режиме СС. В этом случае задается одна и та же сила тока на обеих нагрузках. Через обе нагрузки проходит один и тот же ток (рис. 2.1, 2.2), однако из-за небольших погрешностей в настройках реально установленные значения никогда не будут полностью идентичными друг другу. Следовательно, одна из нагрузок будет пытаться потребить больший ток (нагрузка на рис. 2.1 и 2.2), чем другая (нагрузка 1 на рис. 2.1 и 2.2). Поскольку нагрузка 1 будет удерживать силу тока на более низком уровне (в данном примере 9,99 A), нагрузка 2 никогда не сможет достигнуть своего реально установленного значения (в данном примере 10,01 A). В результате внутренний контур обратной связи продолжает отдавать команды полевым транзисторам проводить все больше и больше тока — до тех пор пока они не станут работать на пределе своих возможностей, на грани короткого замыкания. Это приводит к тому, что почти все напряжение источника питания оказывается на входе нагрузки 1, что может вызвать повреждение схемы.

В этом случае задается одна и та же сила тока на обеих нагрузках. Через обе нагрузки проходит один и тот же ток (рис. 2.1, 2.2), однако из-за небольших погрешностей в настройках реально установленные значения никогда не будут полностью идентичными друг другу. Следовательно, одна из нагрузок будет пытаться потребить больший ток (нагрузка на рис. 2.1 и 2.2), чем другая (нагрузка 1 на рис. 2.1 и 2.2). Поскольку нагрузка 1 будет удерживать силу тока на более низком уровне (в данном примере 9,99 A), нагрузка 2 никогда не сможет достигнуть своего реально установленного значения (в данном примере 10,01 A). В результате внутренний контур обратной связи продолжает отдавать команды полевым транзисторам проводить все больше и больше тока — до тех пор пока они не станут работать на пределе своих возможностей, на грани короткого замыкания. Это приводит к тому, что почти все напряжение источника питания оказывается на входе нагрузки 1, что может вызвать повреждение схемы.

Рис. 2.1. Две включенные последовательно 60-В электронные нагрузки, работающие в режиме постоянного тока

2.1. Две включенные последовательно 60-В электронные нагрузки, работающие в режиме постоянного тока

Последовательное подключение нагрузок, настроенных на работу в режиме постоянного тока (CC), приводит к превышению допустимого напряжения на одной из них (в данном случае на нагрузке 1). Высокое установленное значение выходного напряжения переводит полевые транзисторы в «жесткий» режим работы.

Рис. 2.2. Две включенные последовательно электронные нагрузки (нагрузка 1 в режиме постоянного тока поддерживает ток на уровне 10 А; нагрузка 2 установлена в режим постоянного напряжения)

На первый взгляд может показаться, что если установить одну нагрузку в режим CC, а другую — в режим CV, будет получен вполне стабильный рабочий режим. Однако при этом придется как следует подумать о том, что потребуется для обеспечения такой стабильности. Если установить режимы нагрузок до подачи напряжения, нагрузка CC не будет обеспечена (отсутствует ток), поэтому она перейдет в состояние короткого замыкания; условия нагрузки CV также не будут удовлетворены (отсутствует напряжение), соответственно, она перейдет в режим обрыва цепи. При подаче испытательного напряжения все напряжение сначала появится на разомкнутой нагрузке CV, что может вызвать ее повреждение. Существуют и другие процедуры, выполнение которых может на какое-то время обеспечить стабильный рабочий режим (например, постепенное повышение испытательного напряжения, если прибор обладает такой функцией). Но любая неисправность в одной из нагрузок приведет к активации механизмов защиты, что повлечет за собой перевод полевых транзисторов в «жесткий» режим (короткое замыкание) либо размыкание полевых транзисторов. В любом их этих случаев на одной из нагрузок в последовательном соединении появится высокое напряжение, способное привести к повреждению цепи.

При подаче испытательного напряжения все напряжение сначала появится на разомкнутой нагрузке CV, что может вызвать ее повреждение. Существуют и другие процедуры, выполнение которых может на какое-то время обеспечить стабильный рабочий режим (например, постепенное повышение испытательного напряжения, если прибор обладает такой функцией). Но любая неисправность в одной из нагрузок приведет к активации механизмов защиты, что повлечет за собой перевод полевых транзисторов в «жесткий» режим (короткое замыкание) либо размыкание полевых транзисторов. В любом их этих случаев на одной из нагрузок в последовательном соединении появится высокое напряжение, способное привести к повреждению цепи.

Итак, теперь ясно, почему последовательное соединение нагрузок может моментально вызвать повреждение входных цепей как минимум одной из подключаемых нагрузок. Настоятельно рекомендую никогда этого не делать!

Ссылка на блог Keysight Technologies в России

Материал предоставлен Группой компаний «Диполь».

Официальный сайт Группы компаний «Диполь»: www.dipaul.ru

Понравилась статья? Поставьте лайк

Электроника Контроль, испытания, исследования Электрический контроль Измерительное оборудование Измерительное оборудование Keysight Technologies Keysight Technologies

Зависимость подвижности от размера проводящего канала органических полевых транзисторов на основе монокристаллических нанолент

Зависимость подвижности от размера проводящего канала органических полевых транзисторов на основе монокристаллических нанолент

Яцзе Чжан, ab Хуанли Донг* и Цинсинь Тан, и Юдонг Он и и Вэньпин Ху* и

Принадлежности автора

* Соответствующие авторы

и

Пекинская национальная лаборатория молекулярных наук, Ключевая лаборатория органических твердых тел, Институт химии Китайской академии наук, Пекин, Китай

Электронная почта:

huwp@iccas. ac.cn

ac.cn

Тел.: +86 010-82615030

б Высшая школа Китайской академии наук, Пекин, Китай

Аннотация

Понимание взаимосвязи между проводящим каналом и свойствами устройства в органических монокристаллических транзисторах важно для оценки материалов и создания высокопроизводительных устройств. Для достижения этой цели была исследована зависимость подвижности органических монокристаллических транзисторов от размера канала с использованием массивов наноленточных транзисторов из гексадекафторфталоцианина меди (F 16 CuPc) и рубрен. Монокристаллические наноленты F 16 CuPc и рубрена были получены методом физического паропереноса. Для массового производства массивов транзисторов был разработан метод фрикционной печати. High performance devices were obtained with mobility of F 16 CuPc up to 0.6 cm 2 V −1 s −1 and rubrene of 24.5 cm 2 V −1 s −1 , которые были среди OFET с самой высокой производительностью устройства. Распределения подвижности устройств на основе кристаллов разного размера были обобщены и тщательно проанализированы. Показано, что подвижность устройств экспоненциально уменьшалась с расширением и утолщением кристаллов, но линейно возрастала с увеличением проводящего канала на 3–15 мкм. Зависимости подвижности от размера канала в основном объяснялись изменением сопротивлений транзисторов, последовательно включенных в транзисторную цепь, влияющих на токоперенос между истоком и стоком.

Для массового производства массивов транзисторов был разработан метод фрикционной печати. High performance devices were obtained with mobility of F 16 CuPc up to 0.6 cm 2 V −1 s −1 and rubrene of 24.5 cm 2 V −1 s −1 , которые были среди OFET с самой высокой производительностью устройства. Распределения подвижности устройств на основе кристаллов разного размера были обобщены и тщательно проанализированы. Показано, что подвижность устройств экспоненциально уменьшалась с расширением и утолщением кристаллов, но линейно возрастала с увеличением проводящего канала на 3–15 мкм. Зависимости подвижности от размера канала в основном объяснялись изменением сопротивлений транзисторов, последовательно включенных в транзисторную цепь, влияющих на токоперенос между истоком и стоком.

Патент США на схему на полевых транзисторах. Патент (Патент № 4,394,590, выдан 19 июля 1983 г.)

ОПИСАНИЕ

1. ОБЛАСТЬ ТЕХНИКИ полевые транзисторы, такие как полевые МОП-транзисторы (далее именуемые МОП-транзисторами на полевых транзисторах), соединенные последовательно для работы в условиях высокого напряжения.

2. УРОВЕНЬ ТЕХНИКИ

Выдерживаемое напряжение между стоком и истоком полевого МОП-транзистора, имеющегося в настоящее время в продаже, составляет не более 400 В. Соответственно, чтобы MOSFET работал при напряжении 300 В или более для практического использования, необходимо соединить несколько MOSFET последовательно, чтобы увеличить выдерживаемое напряжение. С этой целью схемы, показанные на фиг. 1 и 2 до сих пор использовались.

В схеме, показанной на РИС. 1, импульсный трансформатор используется для обеспечения двух или более сигналов управления затвором, которые изолированы друг от друга. То есть на фиг. 1 сигнал Vin управления затвором подается на первичную обмотку W1 импульсного трансформатора PT. Отдельные выходные импульсы, полученные от вторичных обмоток W2 и W3, подаются соответственно на затворы n-канальных полевых МОП-транзисторов Q1 и Q2, соединенных последовательно. ZD1 и ZD2 являются защитными стабилитронами, каждый из которых ограничивает входной сигнал затвора, чтобы напряжение между затвором и истоком не превышало напряжения пробоя между затвором и истоком. Сток MOSFET Q1 подключен к источнику питания Vs через нагрузочный резистор RL, а исток MOSFET Q1 подключен к стоку MOSFET Q2, исток которого подключен к точке с общим потенциалом. Этот способ возбуждения, в котором используется импульсный трансформатор, часто применялся для последовательной работы биполярных транзисторов и тиристоров и т.п. Однако в методе возбуждения диапазон рабочих частот сигнала Vin возбуждения затвора ограничен характеристиками используемого импульсного трансформатора, и, в частности, ограниченный диапазон частот вызывает проблему, когда рабочая частота низкая, порядка нескольких кГц.

То есть на фиг. 1 сигнал Vin управления затвором подается на первичную обмотку W1 импульсного трансформатора PT. Отдельные выходные импульсы, полученные от вторичных обмоток W2 и W3, подаются соответственно на затворы n-канальных полевых МОП-транзисторов Q1 и Q2, соединенных последовательно. ZD1 и ZD2 являются защитными стабилитронами, каждый из которых ограничивает входной сигнал затвора, чтобы напряжение между затвором и истоком не превышало напряжения пробоя между затвором и истоком. Сток MOSFET Q1 подключен к источнику питания Vs через нагрузочный резистор RL, а исток MOSFET Q1 подключен к стоку MOSFET Q2, исток которого подключен к точке с общим потенциалом. Этот способ возбуждения, в котором используется импульсный трансформатор, часто применялся для последовательной работы биполярных транзисторов и тиристоров и т.п. Однако в методе возбуждения диапазон рабочих частот сигнала Vin возбуждения затвора ограничен характеристиками используемого импульсного трансформатора, и, в частности, ограниченный диапазон частот вызывает проблему, когда рабочая частота низкая, порядка нескольких кГц. до 100 кГц, так что период проводимости длительный.

до 100 кГц, так что период проводимости длительный.

Схема на фиг. 2 показан способ возбуждения, в котором импульсный управляющий сигнал подается на один из двух элементов для последовательной работы, а на другой элемент подается постоянное напряжение. На фиг. 2 одинаковые ссылочные позиции используются для обозначения одинаковых частей, показанных на фиг. 1. В обычном способе привода, показанном на фиг. 2, сигнал управления затвором Vin подается непосредственно на затвор MOSFET Q2, а постоянное напряжение Vdc подается на затвор другого MOSFET Q1 через параллельную цепь, состоящую из резистора R1 и конденсатора C1. Параллельная цепь, состоящая из резистора R2 и конденсатора C2, включена между затвором и стоком MOSFET Q1. Кроме того, резисторы R1 и R2 образуют делитель напряжения для определения фактического напряжения смещения, подаваемого на затвор MOSFET Q1. Конденсаторы C1 и C2 используются для коррекции доли переходного напряжения на MOSFET Q1 во время переключения. Соответствующие постоянные цепи этих резисторов и конденсаторов были выбраны равными C1/C2, примерно равными R2/R1, а значения емкости конденсаторов C1 и C2 были чрезвычайно малы, например, несколько десятков пФ. Согласно этому способу возбуждения диапазон рабочих частот не ограничен, в отличие от способа, показанного на фиг. 1. Однако, если принять во внимание напряжение источника питания (например, 400 В) MOSFET, необходимо обеспечить источник питания (например, 10 В) для привода затвора независимо или подать заданное напряжение от источника питания. источник MOSFET к затвору MOSFET через схему деления напряжения, имеющую большую потребляемую мощность. В этом отношении приводной метод имеет проблемы с точки зрения стоимости и удобства.

Согласно этому способу возбуждения диапазон рабочих частот не ограничен, в отличие от способа, показанного на фиг. 1. Однако, если принять во внимание напряжение источника питания (например, 400 В) MOSFET, необходимо обеспечить источник питания (например, 10 В) для привода затвора независимо или подать заданное напряжение от источника питания. источник MOSFET к затвору MOSFET через схему деления напряжения, имеющую большую потребляемую мощность. В этом отношении приводной метод имеет проблемы с точки зрения стоимости и удобства.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Соответственно, целью настоящего изобретения является создание схемы полевого транзистора, которая при управлении полевыми транзисторами, соединенными последовательно, устраняет дефекты описанных выше обычных способов управления без ограничение рабочей частоты и обеспечение отдельным источником питания постоянного тока.

В соответствии с данным изобретением для достижения вышеуказанной цели предлагается схема на полевых транзисторах, включающая в себя множество полевых транзисторов, каждый из которых имеет первый электрод (электрод стока) и второй электрод (электрод истока) и управляющий электрод, последовательно включенный между точкой напряжения источника питания и общей потенциальной точкой, при этом управляющий импульс подается на управляющий электрод (затворный электрод) полевого транзистора со стороны общей потенциальной точки, первая схема параллельного соединения, имеющая первый резистор и первый конденсатор, соединена между управляющим электродом каждого из оставшихся полевых транзисторов и точкой общего потенциала, а вторая цепь параллельного соединения, имеющая второй резистор и второй конденсатор, соединена между первую цепь параллельного соединения и первый электрод соответствующего полевого транзистора, благодаря чему оставшиеся g полевые транзисторы переходят в достаточно проводящее состояние в момент подачи управляющего импульса на полевой транзистор со стороны точки общего потенциала.

В предпочтительном варианте осуществления настоящего изобретения диод Зенера подключен между вторым электродом и управляющим электродом каждого из полевых транзисторов для его защиты, так что напряжение, прикладываемое между управляющим электродом и вторым электродом каждого соответствующих полевых транзисторов не превышает напряжения пробоя между управляющим электродом и вторым электродом.

Другой предпочтительный вариант осуществления изобретения имеет третий резистор для ограничения тока, который подключен между управляющим электродом каждого из оставшихся полевых транзисторов и точкой соединения между первой и второй цепями параллельного соединения.

Еще один предпочтительный вариант осуществления изобретения имеет четвертые резисторы, каждый из которых вставлен между первым электродом и вторым электродом каждого из полевых транзисторов, для исправления дисбаланса напряжений, разделяемых соответствующими полевыми транзисторами, из-за изменений характеристик ток утечки между первым и вторым электродами среди полевых транзисторов.

В еще одном варианте осуществления изобретения цепь последовательного соединения, имеющая пятый резистор и третий конденсатор, подключается между первым электродом и вторым электродом каждого из полевых транзисторов для исправления дисбаланса напряжений, разделяемых соответствующими полевых транзисторов из-за различий характеристик переключения среди полевых транзисторов.

В настоящем изобретении предпочтительно выбирать емкость первого конденсатора большей, чем емкость второго конденсатора. Емкость первого конденсатора примерно в 5-10 раз превышает статическую входную емкость соответствующего полевого транзистора. Кроме того, емкость второго конденсатора выбирается так, чтобы она находилась в диапазоне примерно от 2/3 до 1/несколько от емкости первого конденсатора.

В соответствии с одним аспектом настоящего изобретения предложена схема на полевых транзисторах, включающая в себя множество полевых транзисторов, имеющих первый и второй электроды и управляющий электрод, и нагрузку, которые последовательно соединены между источником напряжения питания точки и общей потенциальной точки, в которой на управляющий электрод полевого транзистора со стороны общей потенциальной точки подается управляющий импульс, между общей потенциальной точкой и управляющий электрод полевого транзистора примыкает к полевому транзистору со стороны общей потенциальной точки среди остальных полевых транзисторов, множество цепей, имеющих параллельно соединенные резисторы и конденсаторы, соединены последовательно между схемой параллельного соединения и первый электрод полевого транзистора со стороны питания s Исходное напряжение и соответствующие точки соединения этих последовательно соединенных цепей последовательно и соответственно подключаются к соответствующим управляющим электродам остальных полевых транзисторов, посредством чего оставшиеся полевые транзисторы переводятся в достаточно проводящее состояние в момент подачи управляющего импульса к полевому транзистору со стороны точки общего потенциала.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

РИС. 1 и 2 — принципиальные схемы, показывающие два варианта осуществления обычной схемы управления полевым транзистором с последовательным соединением;

РИС. 3 представляет собой принципиальную схему, показывающую вариант осуществления схемы схемы управления полевым транзистором в соответствии с настоящим изобретением;

РИС. 4 представляет собой диаграмму сигналов, иллюстрирующую примеры форм сигналов напряжений и токов в соответствующих частях схемы, показанной на фиг. 3;

РИС. 5 представляет собой диаграмму сигналов, иллюстрирующую формы сигналов тока и напряжения при включении полевого МОП-транзистора; и

ФИГ. 6 и 7 представляют собой принципиальные схемы, показывающие другие варианты осуществления настоящего изобретения.

НАИЛУЧШИЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Настоящее изобретение будет подробно описано со ссылками на прилагаемые чертежи.

Схема с использованием двух МОП-транзисторов, соединенных последовательно, показана на РИС. 3, в качестве варианта осуществления схемы на полевом транзисторе в соответствии с настоящим изобретением. На фиг. 3 одинаковые ссылочные обозначения используются для обозначения соответствующих частей, показанных на фиг. 2. В варианте, показанном на фиг. 3, в то время как подача сигнала Vin возбуждения затвора на затвор (узел E) MOSFET Q2 выполняется аналогично способу возбуждения, показанному на фиг. 2 схема смещения затвора полевого МОП-транзистора Q1 имеет следующую конструкцию. Между затвором (узлом D) полевого МОП-транзистора Q1 и общей потенциальной точкой последовательно соединены токоограничивающий резистор RG и параллельная цепь с резистором R3 и конденсатором С3. Между узлом G между резистором RG и параллельной цепью R3, C3 и стоком MOSFET Q1 подключена параллельная цепь, имеющая резистор R4 и конденсатор C4. Цепь с резисторами R3 и R4 и конденсаторами C3 и C4 образует цепь смещения затвора для подачи надлежащего положительного импульса затвора на затвор MOSFET Q1 в течение желаемого периода времени. Здесь следует отметить, что схема смещения затвора не требует подачи питания от дополнительно предусмотренного источника питания постоянного тока, в отличие от обычной схемы, и подключается только между источником питания Vs и точкой общего потенциала. Значения сопротивления резисторов R3 и R4 выбраны такими высокими, чтобы обеспечить достаточное разделение напряжения для тока утечки на полевой МОП-транзистор Q1 и стабилитрон ZD1. На фиг. 3, между стоком (узел А) и истоком (узел В) МОП-транзистора Q1 подключена параллельная цепь с резистором RE и последовательная цепь с резистором RS и конденсатором CS. Точно так же между стоком (узел B) и истоком (узел C) MOSFET Q2 подключена параллельная цепь с резистором RE и последовательная цепь с резистором RS и конденсатором CS. Резисторы RE используются для коррекции дисбаланса напряжений, разделяемых полевыми МОП-транзисторами Q1 и Q2, из-за разницы между характеристиками тока утечки между стоками и истоками соответствующих полевых МОП-транзисторов Q1 и Q2.

Здесь следует отметить, что схема смещения затвора не требует подачи питания от дополнительно предусмотренного источника питания постоянного тока, в отличие от обычной схемы, и подключается только между источником питания Vs и точкой общего потенциала. Значения сопротивления резисторов R3 и R4 выбраны такими высокими, чтобы обеспечить достаточное разделение напряжения для тока утечки на полевой МОП-транзистор Q1 и стабилитрон ZD1. На фиг. 3, между стоком (узел А) и истоком (узел В) МОП-транзистора Q1 подключена параллельная цепь с резистором RE и последовательная цепь с резистором RS и конденсатором CS. Точно так же между стоком (узел B) и истоком (узел C) MOSFET Q2 подключена параллельная цепь с резистором RE и последовательная цепь с резистором RS и конденсатором CS. Резисторы RE используются для коррекции дисбаланса напряжений, разделяемых полевыми МОП-транзисторами Q1 и Q2, из-за разницы между характеристиками тока утечки между стоками и истоками соответствующих полевых МОП-транзисторов Q1 и Q2. Последовательные цепи RS, CS предназначены для коррекции дисбаланса напряжений, разделяемого полевыми МОП-транзисторами Q1 и Q2, из-за разницы между характеристиками переключения полевых МОП-транзисторов Q1 и Q2.

Последовательные цепи RS, CS предназначены для коррекции дисбаланса напряжений, разделяемого полевыми МОП-транзисторами Q1 и Q2, из-за разницы между характеристиками переключения полевых МОП-транзисторов Q1 и Q2.

В схеме, показанной на РИС. 3, если соответствующие номиналы резисторов R3 и R4 и конденсаторов C3 и C4 определены тем же расчетным образом, что и соответствующие номиналы резисторов R1 и R2 и конденсаторов C1 и C2 на фиг. 2, напряжение VDB между затвором и истоком MOSFET Q1 снижается до нескольких вольт или меньше. Такое низкое напряжение может недостаточно включить MOSFET Q1. Ввиду этой проблемы сопротивления и емкости этих резисторов и конденсаторов, в частности конденсаторов С3 и С4, определяются следующим образом согласно изобретению.

Способ определения этих значений в соответствии с изобретением будет объяснен при объяснении работы схемы по настоящему изобретению. В начале работы схемы, показанной на фиг. 3 зарядное напряжение на конденсаторе С3 определяется коэффициентом деления напряжения резисторов R3 и R4; когда R3=R4, VGC =1/2 Vs. Рассмотрим ситуацию, когда сигнал Vin управления затвором в виде импульса положительного напряжения, как показано на фиг. 4 применяется между затвором и истоком E-C MOSFET Q2. Этот сигнал Vin представляет собой напряжение между узлами Е и С и, соответственно, может быть представлен как VEC. Это представление будет соответственно применяться к напряжениям между другими связанными узлами в дальнейшем. Предположим также, что сигнал управления затвором Vin больше, чем пороговое напряжение (около 3 В) MOSFET Q2, например, 10 В. Приложение сигнала управления затвором Vin переводит MOSFET Q2 в состояние с низким импедансом, так что потенциал стока мгновенно падает до потенциала истока или значения потенциала, близкого к общему потенциалу. С падением потенциала стока напряжение VBC между стоком и истоком B-C MOSFET Q2 резко падает, как показано на фиг. 4. В результате положительное напряжение, подобное напряжению VDB, показанному на фиг. 4 появляется между затвором и истоком DB MOSFET Q1, так что MOSFET Q1 переключается в состояние ON.

Рассмотрим ситуацию, когда сигнал Vin управления затвором в виде импульса положительного напряжения, как показано на фиг. 4 применяется между затвором и истоком E-C MOSFET Q2. Этот сигнал Vin представляет собой напряжение между узлами Е и С и, соответственно, может быть представлен как VEC. Это представление будет соответственно применяться к напряжениям между другими связанными узлами в дальнейшем. Предположим также, что сигнал управления затвором Vin больше, чем пороговое напряжение (около 3 В) MOSFET Q2, например, 10 В. Приложение сигнала управления затвором Vin переводит MOSFET Q2 в состояние с низким импедансом, так что потенциал стока мгновенно падает до потенциала истока или значения потенциала, близкого к общему потенциалу. С падением потенциала стока напряжение VBC между стоком и истоком B-C MOSFET Q2 резко падает, как показано на фиг. 4. В результате положительное напряжение, подобное напряжению VDB, показанному на фиг. 4 появляется между затвором и истоком DB MOSFET Q1, так что MOSFET Q1 переключается в состояние ON.

Дальнейшее рассмотрение будет более подробно в отношении работы схемы во время этого процесса. Напряжение VDB имеет в начальной части своего импульса значение, полученное путем вычитания напряжения на резисторе RG и напряжения в открытом состоянии на полевом транзисторе Q2 из напряжения на конденсаторе С3. Что касается тока, протекающего в то время, когда МОП-транзистор Q2 является проводящим, то ток течет по маршруту G.fwdarw.RG.fwdarw.ZD1.fwdarw.источник стока Q2 C, когда потенциал в узле G выше, чем сумма напряжений напряжения Зенера V z1 стабилитрона ZD1 и напряжения включения полевого МОП-транзистора Q2. Ток протекает по маршруту G.fwdarw.RG.fwdarw.затвор-исток Q1.fwdarw.сток-исток Q2.fwdarw.C, когда потенциал в узле G ниже суммы напряжений стабилитрона V. sub.z1 стабилитрона ZD1 и напряжение включения MOSFET Q2. Таким образом, когда МОП-транзисторы Q1 и Q2 оба включены, ток нагрузки I L протекает через нагрузочный резистор RL к МОП-транзисторам Q1 и Q2. Ток нагрузки I L определяется активными сопротивлениями полевых МОП-транзисторов Q1 и Q2 и нагрузочным резистором RL. Сопротивление во включенном состоянии MOSFET Q2 определяется сигналом управления затвором Vin и проводимостью в прямом направлении MOSFET Q2, а сопротивление во включенном состоянии MOSFET Q1 также определяется напряжением V DB и проводимостью в прямом направлении МОП-транзистор Q1. Среди сопротивлений, существующих в главной цепи RL.fwdarw.Q1.fwdarw.Q2, нагрузочный резистор RL имеет фиксированное значение, а сопротивление в открытом состоянии MOSFET Q2 управляется пиковым значением положительного импульсного напряжения Vin (V.sub .EC) применяется между затвором и истоком MOSFET Q2 снаружи. Соответственно, чтобы обеспечить ток нагрузки I L достаточной величины, необходимо подать надлежащее положительное напряжение между затвором и истоком D-B MOSFET Q1 с помощью цепи смещения затвора R3, R4, C3 и C4. .

Сопротивление во включенном состоянии MOSFET Q2 определяется сигналом управления затвором Vin и проводимостью в прямом направлении MOSFET Q2, а сопротивление во включенном состоянии MOSFET Q1 также определяется напряжением V DB и проводимостью в прямом направлении МОП-транзистор Q1. Среди сопротивлений, существующих в главной цепи RL.fwdarw.Q1.fwdarw.Q2, нагрузочный резистор RL имеет фиксированное значение, а сопротивление в открытом состоянии MOSFET Q2 управляется пиковым значением положительного импульсного напряжения Vin (V.sub .EC) применяется между затвором и истоком MOSFET Q2 снаружи. Соответственно, чтобы обеспечить ток нагрузки I L достаточной величины, необходимо подать надлежащее положительное напряжение между затвором и истоком D-B MOSFET Q1 с помощью цепи смещения затвора R3, R4, C3 и C4. .

Когда МОП-транзисторы Q1 и Q2 оба включены, потенциал в узле А равен Vs-I L RL. В это время, если C3=C4 и R3=R4, то потенциал в узле G падает на I L×RL/2 от начального значения. В результате существует вероятность того, что полевой МОП-транзистор Q1 не сможет поддерживать свое состояние ВКЛ. Кроме того, если МОП-транзисторы Q1 и Q2 включены, заряд, хранящийся в конденсаторе C3, разряжается по пути G.fwdarw.RG.fwdarw. входная емкость MOSFET Q1. Количество заряда, разряжаемого по этому пути, определяется входной емкостью MOSFET Q1, если разряд токами утечки, протекающими через затвор и исток D-B MOSFET Q1 и стабилитрон ZD1, пренебрежимо мал. Как правило, входная емкость MOSFET сильно изменяется в течение периода его включения. Как видно из осциллограмм тока стока I D и напряжения сток-исток V DS во время включения, входная емкость Cin МОП-транзистора выбрана таким образом, чтобы иметь максимальное значение в фазе II трех фаз I, II и III периода включения, а его значение Cin(II) определяется следующим уравнением:

В результате существует вероятность того, что полевой МОП-транзистор Q1 не сможет поддерживать свое состояние ВКЛ. Кроме того, если МОП-транзисторы Q1 и Q2 включены, заряд, хранящийся в конденсаторе C3, разряжается по пути G.fwdarw.RG.fwdarw. входная емкость MOSFET Q1. Количество заряда, разряжаемого по этому пути, определяется входной емкостью MOSFET Q1, если разряд токами утечки, протекающими через затвор и исток D-B MOSFET Q1 и стабилитрон ZD1, пренебрежимо мал. Как правило, входная емкость MOSFET сильно изменяется в течение периода его включения. Как видно из осциллограмм тока стока I D и напряжения сток-исток V DS во время включения, входная емкость Cin МОП-транзистора выбрана таким образом, чтобы иметь максимальное значение в фазе II трех фаз I, II и III периода включения, а его значение Cin(II) определяется следующим уравнением:

Cin(II)=Ciss-AvCss

, где

Av=.DELTA.Vds/.DELTA.Vgs, где .DELTA.Vds и .DELTA.Vgs — приращения напряжения сток-исток и затвор-исток соответственно.

Crss=Cgd

Ciss: статическая входная емкость, описанная в каталоге

Cgd: емкость между затвором и стоком, описанная в каталоге Ciss из-за эффекта Миллера для емкости Cgd между затвором и стоком. Соответственно, если емкость конденсатора С3 мала и С3.перспектива.С4, перераспределение заряда разрядом через конденсатор С4 и динамическая входная емкость МОП-транзистора Q1 в начальном состоянии включения не смещает в достаточной степени. положительное напряжение VDB между затвором и истоком D-B полевого МОП-транзистора Q1. Следовательно, MOSFET Q1 не был достаточно включен.

Как будет понятно из приведенного выше рассмотрения, чтобы приложить достаточное положительное напряжение смещения между затвором и истоком полевого МОП-транзистора Q1 в течение периода времени включения, в настоящем изобретении емкость конденсатора C3 выбрана равной быть в 5-10 раз больше, чем у конденсатора C4, тем самым уменьшая скорость падения напряжения на конденсаторе C3 из-за разряда через конденсатор C4 в течение переходного периода включения, а также для зарядки динамического входного конденсатора полевого МОП-транзистора. Q1 до надлежащего положительного напряжения. В частности, емкость конденсатора C3 определяется в 5-10 раз больше, чем статическая входная емкость полевого МОП-транзистора Q1 в соответствии с шириной импульса, а емкость конденсатора C4 выбирается примерно от 2/3 до 1. /несколько емкостей конденсатора С3, так что полевой МОП-транзистор Q1 достаточно включен.

Q1 до надлежащего положительного напряжения. В частности, емкость конденсатора C3 определяется в 5-10 раз больше, чем статическая входная емкость полевого МОП-транзистора Q1 в соответствии с шириной импульса, а емкость конденсатора C4 выбирается примерно от 2/3 до 1. /несколько емкостей конденсатора С3, так что полевой МОП-транзистор Q1 достаточно включен.

Рассмотрим теперь период выключения MOSFET Q1. Емкость конденсатора С3 больше, чем у конденсатора С4, а сопротивление резистора R4 велико, поэтому скорость нарастания напряжения конденсатора С3 медленная, так что потенциал в узле В быстрее приближается к значению равно 1/2 напряжения источника питания, чем потенциал в узле G. В результате ток заряда конденсатора С3 течет из узла В через стабилитрон ZD1 в проводящем направлении (где напряжение падает примерно на 0,6…0,7 В) и резистор RG. В результате затвор и исток полевого МОП-транзистора Q1 имеют обратное смещение примерно на 0,6–0,7 В, что повышает скорость выключения.

Кроме того, резистор RG предназначен для управления соответствующими пиковыми значениями разрядного тока на пути C3. fwdarw.RG.fwdarw.D.fwdarw.B.fwdarw.Q2.fwdarw.C в течение периода включения и зарядный ток на пути B.fwdarw.ZD1.fwdarw.RG.fwdarw.C3 в период выключения.

fwdarw.RG.fwdarw.D.fwdarw.B.fwdarw.Q2.fwdarw.C в течение периода включения и зарядный ток на пути B.fwdarw.ZD1.fwdarw.RG.fwdarw.C3 в период выключения.

Конкретные значения соответствующих компонентов схемы, показанной на РИС. 3 показаны ниже.

Напряжение источника питания Vs: 400 В

Нагрузочный резистор RL: 30.OMEGA.

МОП-транзисторы Q1 и Q2: HEX2

Резисторы R3=R4: 100 K.OMEGA.

Резистор RG: 200.OMEGA.

Статическая входная емкость (HEX2) Ciss: 450 пФ

Конденсатор C3=10×Ciss: 0,005 мкФ

Конденсатор C4=(1/2,5) C3: 0,002 мкФ

Z1 и VZ2: 19 В

Резистор Rs: 15.OMEGA.

Конденсатор C 5 : 0,0022 мкФ

Резистор R E : 20 K.OMEGA.

В схеме с вышеуказанными константами цепи максимальные значения напряжений VAB и VBC составляли 200 В, а максимальное значение напряжения VDB составляло 19 В.V, а максимальное значение тока I L составляло 6 А, когда импульс возбуждения затвора Vin составлял 10 В. последовательно, ясно, что изобретение применимо к схемотехнике на полевых транзисторах, имеющей желаемое количество (два или более) полевых МОП-транзисторов. Вариант осуществления схемной схемы МОП-транзистора в соответствии с изобретением, имеющей множество n МОП-транзисторов, соединенных последовательно, показан на фиг. 6. На фиг. 6 одинаковые ссылочные обозначения используются для обозначения соответствующих частей на фиг. 3. На фиг. 6, Q3 представляет собой МОП-транзистор, соответствующий МОП-транзистору Q1, а ZD3 представляет собой защитный стабилитрон, подобный стабилитрону ZD1. Цепь смещения затвора MOSFET Q3 состоит из конденсаторов C5 и C6 и резисторов R5 и R6. Конденсаторы С5 и С6 соответствуют соответственно конденсаторам С3 и С4; резисторы R5 и R6 соответствуют соответственно резисторам R3 и R4. Условия выбора емкостей конденсаторов С5 и С6 соответствуют условиям выбора емкостей конденсаторов С3 и С4, поэтому здесь подробное описание не приводится.

последовательно, ясно, что изобретение применимо к схемотехнике на полевых транзисторах, имеющей желаемое количество (два или более) полевых МОП-транзисторов. Вариант осуществления схемной схемы МОП-транзистора в соответствии с изобретением, имеющей множество n МОП-транзисторов, соединенных последовательно, показан на фиг. 6. На фиг. 6 одинаковые ссылочные обозначения используются для обозначения соответствующих частей на фиг. 3. На фиг. 6, Q3 представляет собой МОП-транзистор, соответствующий МОП-транзистору Q1, а ZD3 представляет собой защитный стабилитрон, подобный стабилитрону ZD1. Цепь смещения затвора MOSFET Q3 состоит из конденсаторов C5 и C6 и резисторов R5 и R6. Конденсаторы С5 и С6 соответствуют соответственно конденсаторам С3 и С4; резисторы R5 и R6 соответствуют соответственно резисторам R3 и R4. Условия выбора емкостей конденсаторов С5 и С6 соответствуют условиям выбора емкостей конденсаторов С3 и С4, поэтому здесь подробное описание не приводится.

РИС. 7 показан другой вариант схемы согласно изобретению, в котором последовательно соединены три или более полевых МОП-транзисторов. На фиг. 7 одинаковые части обозначены одинаковыми ссылочными позициями, используемыми на фиг. 6. В этом варианте последовательно соединены цепи параллельного соединения, имеющие соответственно пары резистора R11 и конденсатора С11, резистора R12 и конденсатора С12 и резистора R13 и конденсатора С13. Цепь последовательного соединения, включая эти цепи параллельного соединения, имеет один конец X, подключенный к общей потенциальной точке, а другой конец Y, подключенный к стоку MOSFET Q3 на стороне источника питания. Узлы Z1 и Z2 между соседними цепями параллельного соединения подключены к затворам соответствующих МОП-транзисторов Q1 и Q3 соответственно. Емкости тех конденсаторов С11, С12 и С13 подобраны так, чтобы емкость конденсатора С11 на стороне общего потенциала была наибольшей и последующие конденсаторы ступенчато уменьшались в последовательности порядка подключения конденсаторов; то есть С11 С12 С13. Соответствующие емкости конденсаторов C11, C12 и C13 примерно в 5-10 раз больше, чем входная емкость соответствующих МОП-транзисторов.

На фиг. 7 одинаковые части обозначены одинаковыми ссылочными позициями, используемыми на фиг. 6. В этом варианте последовательно соединены цепи параллельного соединения, имеющие соответственно пары резистора R11 и конденсатора С11, резистора R12 и конденсатора С12 и резистора R13 и конденсатора С13. Цепь последовательного соединения, включая эти цепи параллельного соединения, имеет один конец X, подключенный к общей потенциальной точке, а другой конец Y, подключенный к стоку MOSFET Q3 на стороне источника питания. Узлы Z1 и Z2 между соседними цепями параллельного соединения подключены к затворам соответствующих МОП-транзисторов Q1 и Q3 соответственно. Емкости тех конденсаторов С11, С12 и С13 подобраны так, чтобы емкость конденсатора С11 на стороне общего потенциала была наибольшей и последующие конденсаторы ступенчато уменьшались в последовательности порядка подключения конденсаторов; то есть С11 С12 С13. Соответствующие емкости конденсаторов C11, C12 и C13 примерно в 5-10 раз больше, чем входная емкость соответствующих МОП-транзисторов. Сопротивления резисторов R11, R12 и R13 могут быть выбраны равными друг другу. Хотя вариант осуществления, показанный на фиг. 7 использует три полевых МОП-транзистора, соединенных последовательно, количество полевых МОП-транзисторов может быть увеличено, если это необходимо, как само собой разумеющееся.

Сопротивления резисторов R11, R12 и R13 могут быть выбраны равными друг другу. Хотя вариант осуществления, показанный на фиг. 7 использует три полевых МОП-транзистора, соединенных последовательно, количество полевых МОП-транзисторов может быть увеличено, если это необходимо, как само собой разумеющееся.

Хотя в вышеупомянутых вариантах осуществления настоящее изобретение было объяснено в случае n-канальных полевых МОП-транзисторов, настоящее изобретение может быть применено к схеме последовательного соединения, содержащей р-канальные полевые МОП-транзисторы, полевые транзисторы с переходом (J FET), MONOS FET или другие полевые транзисторы с изолированным затвором.

ПРОМЫШЛЕННАЯ ПРИМЕНИМОСТЬ

Как описано выше, схема полевого транзистора согласно изобретению использует схему смещения затвора, которая не требует дополнительного источника питания постоянного тока для управления включением и выключением соответствующего затвора полевые транзисторы, соединенные последовательно.