Как прошить Xbox 360 через JTAG. Какое оборудование необходимо для прошивки. Какие версии прошивок поддерживают JTAG. Пошаговая инструкция по прошивке Xbox 360 через JTAG.

Что такое JTAG-прошивка Xbox 360

JTAG-прошивка — это метод модификации программного обеспечения Xbox 360, позволяющий запускать неподписанный код и пиратские игры. Название «JTAG» происходит от интерфейса отладки, через который выполняется прошивка.

Основные преимущества JTAG-прошивки Xbox 360:

- Возможность запуска пиратских игр

- Установка эмуляторов и homebrew-приложений

- Модификация системного ПО консоли

- Разблокировка скрытых возможностей Xbox 360

Однако JTAG-прошивка имеет ряд ограничений:

- Поддерживаются только консоли с Dashboard версии не выше 2.0.7371.0

- Дата производства консоли должна быть до мая 2009 года

- Требуется физическое вмешательство в консоль и пайка

- Теряется возможность играть онлайн через Xbox Live

Необходимое оборудование для JTAG-прошивки

Для прошивки Xbox 360 через JTAG потребуется следующее оборудование:

- Паяльник, канифоль, припой

- Тонкий провод (например, МГТФ 0.07 или 0.05 мм)

- Термоусадочная трубка

- 5 резисторов по 100 Ом (0.125 Вт)

- 3 диода 1N4148

- LPT-разъем на 25 контактов (для подключения к компьютеру)

Также понадобится компьютер с LPT-портом и установленным программным обеспечением для прошивки.

Подготовка Xbox 360 к прошивке

Перед началом прошивки необходимо выполнить следующие подготовительные действия:

- Проверить версию Dashboard в настройках консоли. Она должна быть не выше 2.0.7371.0.

- Уточнить дату производства консоли на задней панели. Она должна быть до мая 2009 года.

- Разобрать консоль, чтобы получить доступ к материнской плате.

- Очистить контактные площадки на плате для пайки.

Пошаговая инструкция по прошивке Xbox 360 через JTAG

Процесс JTAG-прошивки Xbox 360 включает следующие основные этапы:

- Припаивание проводов к контактным площадкам на плате консоли

- Подключение проводов к LPT-разъему через резисторы и диоды

- Установка программного обеспечения на компьютер

- Запуск процесса прошивки и записи нового ПО

- Проверка работоспособности прошивки

Рассмотрим каждый этап подробнее.

Припаивание проводов к плате Xbox 360

Необходимо припаять провода к следующим контактным площадкам на материнской плате Xbox 360:

- TDI

- TDO

- TMS

- TCK

- RST

- GND

Схему расположения контактов можно найти в документации по JTAG-прошивке. Провода желательно припаивать тонкие и гибкие, чтобы не повредить плату.

Подключение к LPT-разъему

Припаянные провода необходимо подключить к LPT-разъему через резисторы и диоды согласно следующей схеме:

- TDI — контакт 2 через резистор 100 Ом

- TDO — контакт 10 через диод 1N4148

- TMS — контакт 4 через резистор 100 Ом

- TCK — контакт 3 через резистор 100 Ом

- RST — контакт 5 через резистор 100 Ом

- GND — контакт 18-25

Диоды подключаются анодом к плате Xbox, катодом к LPT-разъему.

Установка программного обеспечения

На компьютер необходимо установить следующее ПО для прошивки:

- 360 Flash Tool v0.97

- Nandpro20e

- Xell (загрузчик для Xbox 360)

Также потребуются драйверы для работы с LPT-портом в режиме прямого доступа.

Процесс прошивки Xbox 360

Основные шаги процесса прошивки:

- Подключить Xbox 360 к компьютеру через LPT-кабель

- Запустить 360 Flash Tool

- Выбрать тип консоли и версию прошивки

- Запустить процесс прошивки

- Дождаться окончания записи нового ПО

- Перезагрузить консоль

Процесс прошивки занимает 10-15 минут. Не отключайте питание во время прошивки!

Проверка работоспособности

После прошивки необходимо убедиться, что:

- Консоль успешно загружается

- Работает меню Freestyle Dash

- Запускаются игры с жесткого диска

- Работают homebrew-приложения

При возникновении проблем может потребоваться повторная прошивка.

Часто задаваемые вопросы о JTAG-прошивке Xbox 360

Можно ли прошить Xbox 360 Slim через JTAG?

Нет, JTAG-прошивка поддерживается только на оригинальных моделях Xbox 360, выпущенных до мая 2009 года. Более поздние ревизии и модель Slim не поддерживают этот метод.

Теряется ли гарантия при JTAG-прошивке?

Да, JTAG-прошивка полностью аннулирует гарантию на консоль, так как требует физического вмешательства в устройство.

Можно ли играть онлайн после JTAG-прошивки?

Нет, Xbox Live блокирует консоли с модифицированным ПО. Онлайн-игра возможна только через альтернативные сервисы для взломанных консолей.

Какие риски есть при самостоятельной прошивке?

Основные риски — это повреждение материнской платы при пайке и вывод консоли из строя при неправильной прошивке. Рекомендуется обращаться к специалистам.

Заключение

JTAG-прошивка позволяет значительно расширить возможности Xbox 360, но требует определенных технических навыков и несет риски повреждения консоли. Перед прошивкой внимательно изучите все требования и ограничения. При отсутствии опыта лучше обратиться к специалистам по прошивке игровых консолей.

Извлечение прошивки с использованием JTAG

Ах, JTAG. Стандарт универсален, так как бесполезен.

JTAG — это универсальный «стандарт», в первую очередь потому, что он определяет все, но ничего не определяет. Помните, он начинался как способ тестирования всей печатной платы и их целостности в целом, он никогда не определялся как (и не должен быть) протокол эмуляции программирования / отладки / в цепи, хотя он создает большую физическую шину для реализовать такие функции на. Одна из наиболее удобных функций заключается в том, что она обладает высокой цепью, что позволяет последовательно соединять несколько устройств на одной плате и тестировать (или что-то еще) их все, используя только один интерфейс JTAG.

JTAG — это просто конечный автомат, который дает вам доступ к адресам памяти. Он не определяет какой-либо протокол или систему для каких-либо действий с чем-либо, он просто обеспечивает среду. То, как или что вы на самом деле делаете через интерфейс JTAG, будет очень специфичным для рассматриваемого чипа, и часто эти функции не публикуются и требуют использования аппаратного и программного обеспечения, предоставляемого поставщиком.

«Интерфейс программирования / отладки JTAG» не является чем-то стандартизированным. В некотором роде он будет использовать конечный автомат JTAG, но здесь нет никакого взаимодействия или универсальности. Этот интерфейс настолько уникален и специфичен для данного чипа, насколько это допускается стандартом JTAG. Чтобы использовать аналогию, JTAG может быть стандартизированной почтовой системой с адресами и форматированием и, возможно, конкретными бумагами и конвертами, которые должны использоваться, все очень строго определены. То, что он не очень хорошо определяет, это то, что вы на самом деле пишете на этих письмах. Он определяет пишущую машинку, шрифт, размер, интервал, алфавит и т. Д., Но то, что вы на самом деле пишете, остается в основном на ваше усмотрение.

Хорошо, я взял на себя смелость с этой аналогией, но я думаю, что это понятно.

Поэтому, когда в спецификации этого чипа написано «введен указанный сигнал», это хороший способ сказать вам, что они не собираются рассказывать, как перевести чип в режим программирования. Там написано, чтобы обратиться к руководству пользователя для их флеш-программиста, JET51. Это на китайском языке, но оно, конечно, не раскрывает их проприетарный протокол (который явно является интеллектуальной собственностью на миллиарды , по крайней мере, в голове у одного наивного руководителя), так что вы можете создать собственное устройство и программное обеспечение.

Там написано, чтобы обратиться к руководству пользователя для их флеш-программиста, JET51. Это на китайском языке, но оно, конечно, не раскрывает их проприетарный протокол (который явно является интеллектуальной собственностью на миллиарды , по крайней мере, в голове у одного наивного руководителя), так что вы можете создать собственное устройство и программное обеспечение.

К сожалению, ответы на многие ваши вопросы предназначены для Sino Wealth, а вы … ну … нет. Вы пытались написать им письмо? Кто знает, может быть, они позволят вам подписать NDA или что-то в этом роде.

Теперь все может быть хуже. Есть поставщики, которые даже не продают вам программиста или проприетарное программное обеспечение, необходимое для его использования, если вы не являетесь крупным бизнесом, и все ваши инженеры не подписывают NDA, не заключают какой-то оккультный договор и т. Д. Но, к счастью, Sino Wealth знает, как немного расслабиться, и любезно предоставил руководство пользователя, прошивку (!!) для своих программистов и необходимое программное обеспечение. Как это работает? Если Sino Wealth не скажет вам, я боюсь, что ваш единственный оставшийся вариант — это также перепроектировать все это. Принимая во внимание, что есть несколько сторонних программистов, которые поддерживают этот конкретный чип, и что они предоставляют программное обеспечение и даже встроенное программное обеспечение для своих программистов, вероятно, не так уж и сложно перепроектировать. Или вы можете просто купить программатор JET51. Используете ли вы его или перепроектируете, его работа зависит от вас.

Как это работает? Если Sino Wealth не скажет вам, я боюсь, что ваш единственный оставшийся вариант — это также перепроектировать все это. Принимая во внимание, что есть несколько сторонних программистов, которые поддерживают этот конкретный чип, и что они предоставляют программное обеспечение и даже встроенное программное обеспечение для своих программистов, вероятно, не так уж и сложно перепроектировать. Или вы можете просто купить программатор JET51. Используете ли вы его или перепроектируете, его работа зависит от вас.

Кроме того, блок-схема конечного автомата, на которой вы разместили скриншот, относится к проприетарному режиму программирования SSP Sino Wealth и совершенно не относится к «указанной форме волны», упомянутой в разделе программирования флэш-памяти ICP, и не имеет ничего общего с интерфейсом программирования JTAG. К сожалению, это не имеет никакого отношения к остальной части вашего вопроса.

Что касается ЖК-дисплея, это не имеет значения. SH79F1619 — это сегментный ЖК-контроллер.

Единственное, что отличается между ЖК-дисплеем и светодиодом, это то, что ЖК-дисплеи должны работать с переменным током, а светодиоды, очевидно, с постоянным током. Это совершенно универсально и обычно работает так же, как если бы вы использовали светодиод, только с переменным током. Хотите, чтобы сегмент был включен? Подайте переменное напряжение. Хотите это? Не применяйте переменное напряжение (или просто уменьшайте среднеквадратичное напряжение переменного тока). Все, что LCD-контроллер делает для вас — это переключение COM и различных сегментирующих выводов назад и вперед относительно друг друга, и обычно между несколькими напряжениями смещения, чтобы создать ступенчатую форму волны и дать вам некоторые приятные функции, такие как изменение контрастности / оттенков серого и т. Д. Но это совершенно общий характер, и вам не нужно ничего знать об этом ЖК-дисплее. Если вы хотите скоротать выходные, полные разочарований, вы можете даже побить их самостоятельно, используя микро и несколько транзисторов для переключения между напряжениями смещения. Если вы страдаете от суицидальных мыслей, я советую не пытаться это делать.

Все, что LCD-контроллер делает для вас — это переключение COM и различных сегментирующих выводов назад и вперед относительно друг друга, и обычно между несколькими напряжениями смещения, чтобы создать ступенчатую форму волны и дать вам некоторые приятные функции, такие как изменение контрастности / оттенков серого и т. Д. Но это совершенно общий характер, и вам не нужно ничего знать об этом ЖК-дисплее. Если вы хотите скоротать выходные, полные разочарований, вы можете даже побить их самостоятельно, используя микро и несколько транзисторов для переключения между напряжениями смещения. Если вы страдаете от суицидальных мыслей, я советую не пытаться это делать.

Мои последние заключительные мысли:

Жизнь коротка. Не тратьте на это самый ценный ресурс из всех, время. Нет причин, чтобы перепроектировать все это. Это не будет особенно ценный опыт обучения — вы узнаете много нового об очень специфичном чипе и его проприетарном интерфейсе программирования, который будет совершенно непримечательным и просто еще одним вариантом того же самого дерьма, которое делалось десятилетиями в совершенно разных реализациях. все виды микро И в любом случае в этом чипе не стоит ничего восстанавливать и декомпилировать. Нет ничего революционного в дрянной флэш-микросхеме со встроенным контроллером сегментов ЖК-дисплея и «10-битным» (вероятно, ближе к 6 битам и еще 4 бесполезным шумом) аналого-цифровым преобразователем. Из этого кода нечему учиться, и вы сравните или улучшите его, просто написав свой собственный с нуля для более открытого и доступного микро. Atmel производит чипы, такие как atmega169, которые имеют те же контакты контроллера сегментов lcd, общедоступный и хорошо документированный интерфейс программирования, инструменты с открытым исходным кодом и множество примеров кода.

все виды микро И в любом случае в этом чипе не стоит ничего восстанавливать и декомпилировать. Нет ничего революционного в дрянной флэш-микросхеме со встроенным контроллером сегментов ЖК-дисплея и «10-битным» (вероятно, ближе к 6 битам и еще 4 бесполезным шумом) аналого-цифровым преобразователем. Из этого кода нечему учиться, и вы сравните или улучшите его, просто написав свой собственный с нуля для более открытого и доступного микро. Atmel производит чипы, такие как atmega169, которые имеют те же контакты контроллера сегментов lcd, общедоступный и хорошо документированный интерфейс программирования, инструменты с открытым исходным кодом и множество примеров кода.

Я не берусь говорить, стоит ли заниматься проектом или нет, интересным или нет. У каждого свое определение веселья — и я говорю, есть у него. Заставьте эту кофеварку вести себя, или дайте ей петлю управления PID, или заставьте ее запустить Linux и добавить шину CAN, чтобы ваш автомобиль мог с ней разговаривать — сходите с ума. Но не тратьте свое время на обратный инжиниринг чего-то, что не стоит никому другого времени на обратный инжиниринг. Если вы не очень заботитесь о кофеварке и хотите что-то перепроектировать, выберите то, что поможет вам освоить навыки обратного проектирования, а не бессмысленные особенности какой-то проприетарной системы. Или, с другой стороны, выберите что-то, что действительно может иметь что-то интересное и достойное восстановления. Хотя я сомневаюсь, что что-нибудь стоящее будет сидеть там и ждать, пока кто-нибудь его бросит.

Но не тратьте свое время на обратный инжиниринг чего-то, что не стоит никому другого времени на обратный инжиниринг. Если вы не очень заботитесь о кофеварке и хотите что-то перепроектировать, выберите то, что поможет вам освоить навыки обратного проектирования, а не бессмысленные особенности какой-то проприетарной системы. Или, с другой стороны, выберите что-то, что действительно может иметь что-то интересное и достойное восстановления. Хотя я сомневаюсь, что что-нибудь стоящее будет сидеть там и ждать, пока кто-нибудь его бросит.

Поверьте мне — есть множество не менее интересных вещей, на которые можно потратить ваше время, гораздо больше, чем может вместить любая человеческая жизнь. Выберите хорошие или лучшие из вас могут справиться, и отказаться от меньших. Даже если это означает, что вы никогда не изучите 200 инструкций по сборке, которые делают вашу кофемашину галочкой.

Прошивка ESP32 через JTAG — Блог айтишника

При разработке устройств настает момент, когда перестаешь использовать dev kit и переходишь на свою плату.

Начнем с теории. На официальном сайте есть руководство по установке всего необходимого софта (компиляторы, библиотеки, отладчики и примеры кода). И рядом имеется руководство по отладке при помощи openocd. Этот софт через программатор подключается к чипу. Различными командами можно записать прошивку на чип, стереть его или считать. В общем, манипуляции с памятью, команды на перезагрузку и прочие низкоуровневые функции. Далее, openocd и предоставляет отладчику GDB доступ чипу. GDB уже понимает что переменная X лежит по адресу 0xff и так далее. Можно прыгать по прошивке, читать переменные… Можно сказать, высокоуровневая отладка. Как-то так оно и работает.

Теперь о железе. В первую очередь требуется подключить плату к программатору. На официальном же сайте есть схема подключения.

На официальном же сайте есть схема подключения.

| ESP32 Pin | JTAG Signal |

|---|---|

| CHIP_PU | TRST_N |

| MTDO / GPIO15 | TDO |

| MTDI / GPIO12 | TDI |

| MTCK / GPIO13 | TCK |

| MTMS / GPIO14 | TMS |

| GND | GND |

Но я дополню эту схему. Не знаю, для всех ли программаторов это актуально. В моем случае, в программаторе содержатся буферы, которые «запитывает» TARGET устройство. Таким образом, если мы подаем на пин V_TARGET/VREF (1 контакт 20-пинового разъема) напряжением 3.3 вольта, то и все сигнальные линии будут с уровнями 3.3 вольта. Так же и для 5 вольт. Таким образом программатор становится универсальным и подходит для работы с чипами, работающими на различных уровнях сигналов. Если V_TARGET не подключать, то openocd просто не обнаружит чип.

Теперь сам процесс прошивки. По умолчанию команда make flash скрывает вызовы компилятора и различных утилит для прошивки. В качестве примера возьмем проект работы с GPIO.

В качестве примера возьмем проект работы с GPIO.

Но, если добавить ключ -e, то она их покажет.

Теперь мы видим, что на самом деле прошивается не только build/gpio.bin, а ещё и build/bootloader/bootloader.bin c build/partitions_singleapp.bin. Причем в определенном порядке и с определенными смещениями.

Если посмотреть файл с описанием esp32 в скриптах openocd (openocd-esp32/share/openocd/scripts/target/esp32.cfg), то можно найти в нем команду program_esp32, которая в качестве аргумента принимает имя файла и смещение. Можно воспользоваться и ей, но все равно нужно прошивать все три bin файла.

На самом деле эта команда просто проверяет входные данные и вызывает встроенные в openocd функции. Поэтому перейдем сразу к их описанию в документации. В ней описаны команды для работы с flash: erase_sector, erase_sector, write_bank, read_bank, verify_bank, write_image. Сейчас интересует только последняя. С остальными разобраться не проблема, если вдруг понадобятся.

С остальными разобраться не проблема, если вдруг понадобятся.

Требуется указать имя файла с прошивкой, смещение и нужно ли предварительно стереть используемую область памяти и проводить проверку после записи. Загружать bin файлы скорее всего нужно в том же порядке, который получили из вывода make flash.

В моем случае, в домашней директории лежит скрипт ~/.openocd.sh, в котором находятся команды для запуска openocd со всеми параметрами. Это удобно.

[walhi@walhi] ~ $ cat ~/.openocd.sh

#!/bin/sh

#OCD=ocd-h

OCD=ocd

case `pwd` in

*stm32*)

exec openocd -f interface/ftdi/olimex-arm-usb-${OCD}.cfg\

-f interface/ftdi/olimex-arm-jtag-swd.cfg\

-f target/stm32f1x.cfg\

-c 'init'\

"$@"

*esp*)

exec ~/esp/openocd-esp32/bin/openocd -s ~/esp/openocd-esp32/share/openocd/scripts\

-f interface/ftdi/olimex-arm-usb-${OCD}.cfg\

-f board/esp-wroom-32.cfg\

"$@"

esac

[walhi@walhi] ~ $

Поясню один момент. Конструкция «$@» позволяет передать все параметры, которые передали этому скрипту, в openocd.

Конструкция «$@» позволяет передать все параметры, которые передали этому скрипту, в openocd.

Теперь можно попробовать прошить ESP32. Сформируем команду:

~/.openocd.shДля начала нужно проинициализировать чип и остановить выполнение текущей программы. Добавим команды для этого:

-c "init" -c "reset halt"Прошивка файла build/bootloader/bootloader.bin:

-c "flash write_image erase build/bootloader/bootloader.bin 0x1000"

Прошивка программы build/gpio.bin:

-c "flash write_image erase build/gpio.bin 0x10000"Прошивка файла build/partitions_singleapp.bin:

-c "flash write_image erase build/partitions_singleapp.bin 0x8000"На этом формирование команды на прошивку завершено. Но программа не начнет выполняться и openocd останется запущенным. Для решения этих проблем добавим ещё две команды

-c "reset run" -c "exit"В результате полная команда на прошивку выглядит следующим образом:

~/.openocd.sh -c "init" -c "reset halt" -c "flash write_image erase build/bootloader/bootloader.bin 0x1000" -c "flash write_image erase build/gpio.bin 0x10000" -c "flash write_image erase build/partitions_singleapp.bin 0x8000" -c "reset run" -c "exit"Учтите, что при копировании строки с сайта, могут возникнуть проблемы из-за символов юникода. Выглядит это так:

Набрать команду не так уж и сложно. А вообще, лучше бы оформить это в скриптик.

Результат успешного выполнения команды выглядит следующим образом:

А теперь давайте сравним скорости загрузки через UART Bootloader и через JTAG. Для справки приведу размеры прошивки:

[walhi@walhi] ~/esp/esp-idf/examples/peripherals/gpio $ make size

Toolchain path: /home/walhi/esp/xtensa-esp32-elf/bin/xtensa-esp32-elf-gcc

Toolchain version: crosstool-ng-1.22.0-80-g6c4433a

Compiler version: 5.2.0

App "gpio" version: v4.0-dev-73-gf1e9078cb

Python requirements from /home/walhi/esp/esp-idf/requirements.txt are satisfied.

Total sizes:

DRAM .data size: 7852 bytes

DRAM .bss size: 4128 bytes

Used static DRAM: 11980 bytes ( 168756 available, 6.6% used)

Used static IRAM: 32839 bytes ( 98233 available, 25.1% used)

Flash code: 78932 bytes

Flash rodata: 38508 bytes

Total image size:~ 158131 bytes (.bin may be padded larger)| Программатор | Время (сек) |

| UART Bootloader | 14,245 |

| Olimex ARM-USB-OCD | 16,093 |

| Olimex ARM-USB-OCD-H | 4,084 |

Надеюсь, статья поможет освоиться.

Делаем JTAG программатор для прошивки флеш-памяти спутниковых тюнеров и не только

Нашел в своем архиве фото, на котором был запечатлен процесс изготовления JTAG-программатора, который понадобился мне, чтобы оживить спутниковый тюнер. Теперь немного подробнее, что за «зверь» такой JTAG:

JTAG (сокращение от англ. Joint Test Action Group; произносится «джей-тáг») — название рабочей группы по разработке стандарта IEEE 1149. Позднее это сокращение стало прочно ассоциироваться с разработанным этой группой специализированным аппаратным интерфейсом на базе стандарта IEEE 1149.1. Официальное название стандарта Standard Test Access Port and Boundary-Scan Architecture. Интерфейс предназначен для подключения сложных цифровых микросхем или устройств уровня печатной платы к стандартной аппаратуре тестирования и отладки. Кому интересно и дальше, полная статья на википедии.

А теперь вернемся к делу, от знакомых попал ко мне спутниковый тюнер, самый обычный и простой Globo на процессоре Ali M3329B. С такими симптомами, вообще не включался, сначала я грешил на блок питания, но прозвонив все напруги мультиметром оказалось все же с питанием все нормально. Поизучав немного разных статьей по ремонту данных ресиверов, пришел к выводу, что судя по симптомам полностью слетела прошивка, и восстановить его можно прошив через JTAG-программатор. Так же была мысль, что он полностью сгорел и восстановлению не подлежит, но я все-же предпочитал верить, что прошивка через JTAG поможет.

Для изготовления выбрал вот эту схему:

Питание на схему подаётся от ресивера, к которому она подключается. В использовании внешнего источника питания для схемы нет необходимости по двум причинам. Во-первых, потребляемый ток очень мал и не создаёт дополнительной нагрузки на блок питания ресивера, во-вторых, питание от того же источника, что и процессор с флэш-памятью улучшает согласование логических уровней.

74HC244 это не инвертирующий буфер. Микросхема содержит два независимых четырехразрядных буфера. Каждый буфер имеет свой сигнал разрешения выхода (низкий активный уровень). На входах нет триггеров Шмитта. Микросхема выполнена по технологии “быстрый” КМОП, что обеспечивает высокое быстродействие. Мощный токовый выход делает возможным сохранение высокого быстродействия даже при емкостной нагрузке. Быстродействие 74HC244 сравнимо с быстродействием микросхем, основанных на диодах Шоттки, при этом 74HC244 сохраняет достоинства микросхем КМОП, т.е. высокая помехозащищенность и низкая потребляемая мощность. Входы микросхемы защищены от повреждения статическим электричеством при помощи диодов.

Увы 74HC244 в своих запасах я не обнаружил. Нашел только аналог 74F244, который немного отличался напряжением питания Vcc. У 74HC244 рекомендуемое от 2 до 6 В, а у 74F244 — от 4,5 до 5,5 В. Хотя максимальные пределы от -0.5 до +7 В, поэтому решил не заморачиваться, и приступить к изготовлению.

Взяв исходную схему на первом изображении, и перерисовав ее в программе DipTrace получилась вот такая схема:

Далее преобразовал ее в печатную плату:

Все было оттрасировано автоматически, не оттрасировало только одну линию, но это проблема была решена двумя SMD перемычками. На изображении выше — готовая для изготовления печатная плата.

На плате я так же подписал все выводы, но к сожалению с выходные сигналы неправильно подписал, как видно на первоисточнике 1- GND, 2- TCK, 3- TMS, 4- TDO, 5- TDI и 6- RST, у меня же получилось GND, TMS, TCK, TDI, TDO, и RST, ошибся именно когда делал подписи контактам, по схеме все правильно, согласно первоисточнику, т.е. 1- GND, 2- TCK, 3- TMS, 4- TDO, 5- TDI и 6- RST.

Печатная плата с правильными обозначением контактов:

Далее собственно процесс физического изготовления:

Собственно главное — гетинакс, напильник, небольшая ручная ножовка, наждачная бумага. Отвертка и резак для расслоения гетинакса на 2 части, поскольку у меня кусочек был фольгированный с двух сторон, а плата наша простая, односторонняя.

Проделав всю роботу, выточив гетинакс под размеры платы (примерно 55х50 мм), берем чистящее средство COMET (Комет) в порошке и губку для мытья посуды. Очищаем гетинакс от следов жира и грязи. Лучше не вытирать остатки воды, а дать просохнуть так.

Пока сохнет гетинакс идем за компьютер и печатаем нашу схему на лазерном принтере и фотобумаге в зеркальном отражении указав максимальное качество печати. Важно не забыть поставить зеркальное отражение, иначе в итоге на плате получим все на выворот!

И так, гетинакс готов, печатная плата напечатана, аккуратно подогнав края гетинакса к рисунку печатной платы на фотобумаге крепим ее липкой бумажной лентой к гетинаксу, берем утюг и ставим его на максимальную температуру.

Естественно фольгированной стороной гетинакса к рисунку печатной платы.

Когда утюг нагрелся, плотно прижимая, начинаем гладить — равномерно прогревая гетинакс со стороны бумаги. Плату такого размера греем не более 30-60 сек, иначе тонер расползется. Рекомендую поставить таймер на телефоне, чтобы время было рядом, перед глазами. Когда все сделано, даем время плате остыть.

Отдираем фотобумагу от платы, перед нами готовая плата, которую остается вытравить в хлорном железе FeCl₃, если есть не большие огрехи, перед травление, поправляем дорожки скальпелем и тонким маркером для дисков.

В процессе травления хлорным железом необходимо непрерывно перемешивать раствор, например покачиванием посуды. Если размер платы не очень большой, можно плату класть на поверхность раствора рисунком вниз — не нужно покачивать, но трудно отследить окончание процесса травления. Время травления хлорным железом составляет от 5 до 50 минут и зависит от температуры, концентрации раствора и его загрязнённости медью, толщины медной фольги. После травления плату нужно промыть проточной водой и высушить.

В итоге получаем вот такую печатную плату

Тонер так же очищаем порошком «Комет», он держится достаточно хорошо, и чтоб не повредить дорожки платы очищаем его не спеша.

После очистки от тонера видим аккуратную, красивую печатную плату

Далее приступаем к лужению, берем паяльник, канифоль, олово и флюс, которым намажем плату, для более комфортного лужения:

Теперь приступаем к пайке элементов:

На фото плата с запаянным 74F244 и двумя SMD перемычками.

Запаяем резисторы, конденсатор и разъем LPT-порта (папа), а так же провода GND, TCK, TMS, TDO, TDI и RST для подключения к устройству которое необходимо прошить. И два провода, для питания программатора

Собственно, на этом процесс изготовления окончен, JTAG-программатор готов для работы, можно прошивать спутниковый тюнер, главное наличие LPT-порта в компьютере, во многих современных компьютерах он к сожалению отсутствует.

О самом процессе прошивки спутникового тюнера, с помощью данного программатора напишу своей следующей статье.

прошивка микроконтроллеров

Прошивка по UART (4 линии VCC, Ground, Tx, Rx) и прошивка по USB однозначно требует зашитого загрузчика.

На заводе микросхемы шьют через JTag (или SWD)

Когда еще никакого загрузчика нет (контроллер девственно чистый) после изготовления платы шьют по JTag (Joint Test Action Group) или , что почти тоже самое по SWD ( Serial Wire Debug).

JTAG — Joint Test Action Group (специализированный аппаратный интерфейс на базе стандарта IEEE 1149.1).

линии JTAG:

TDI (test data input — «вход тестовых данных») — вход последовательных данных периферийного сканирования. Команды и данные вводятся в микросхему с этого вывода по переднему фронту сигнала TCK.

TDO (test data output — «выход тестовых данных») — выход последовательных данных. Команды и данные выводятся из микросхемы с этого вывода по заднему фронту сигнала TCK.

TCK (test clock — «тестовое тактирование») — тактирует работу встроенного автомата управления периферийным сканированием. Максимальная частота сканирования периферийных ячеек зависит от используемой аппаратной части и на данный момент ограничена 25…40 МГц[источник не указан 2305 дней].

TMS (test mode select — «выбор режима тестирования») — обеспечивает переход схемы в/из режима тестирования и переключение между разными режимами тестирования.

В некоторых случаях к перечисленным сигналам добавляется сигнал TRST для инициализации порта тестирования, что необязательно, так как инициализация возможна путём подачи определённой последовательности сигналов на вход TMS.

JTAG позволяет прошивать не одно , а несколько устройств расположенных на одной плате.

Если на плате установлено несколько устройств, поддерживающих JTAG, они могут быть объединены в общую цепочку.

Уникальной особенностью JTAG является возможность программирования не только самого микроконтроллера (или ПЛИС), но и подключённой к его выводам микросхемы флэш-памяти.

Причём существует два способа программирования флэш-памяти с использованием JTAG: через загрузчик с последующим обменом данными через память процессора, либо через прямое управление выводами микросхемы.

DFU — Device Firmware upgrade

Установка Freeboot 12611 (JTAG метод) | прошить xbox 360 в москве | прошивка xbox 360 и Slim Москва

Freeboot для xbox 360

дата выпуска xbox 360 до мая 2009 (возможно до 13 июня). Дата производства указана на задней панели консоли.

Установить фрибут на дашборд 15574, 16202, 16203 в Москве можно здесь для чего нужен Freeboot можно узнать здесь

Все действия по данному руководству вы совершаете на свой страх и риск , за последствия ваших трудов отвечаете только вы сами.

Чтобы определить версию дашборда идем в настройки системы (System Settings) -> Настройки консоли (Console Settings) -> Сведения о системе (System info) — Внизу набор цифр D:2.0.7xxx.0.

Внимание если версия D:2.0.8xxx.0 и выше — Freeboot невозможен и дальше читать только из любопытства. Понизить версию дашборда тоже нельзя.

нам понадобятся:

— Паяльник, канифоль,припой

— Провод МГТФ 0.07, 0.05 или любой другой каким вам удобней паять.

— Термоусадка по желанию

для LTP — метода:

— 5 резисторов 100 Ом, 0.125W

— 3 маломощных диода 1N4148

— Разьем-штекер:LPT 25 pin

для USB — метода

— usb psi flasher ( nand-extractor )

— 2 маломощных диода 1N4148

программное обеспечение:

— 360 Flash Tool.exe v0.97

— Nandpro20e

— Xell — загрузчик

— freeBOOT_ToolBox_Maker

Скачать перечисленное ПО

Приступаем.

— устанавливаем port95nt (находится в папке с nandpro)

— выключаем ПК

— паяем согласно схеме.

диод ставить правильно как на фото

— подключаем lpt-штекер в гнездо на материнской плате ПК

— подключаем питание к материнской плате xbox 360(дежурный режим), консоль не включать, просто воткнуть кабель от блока питания и блок питания подключить к 220В

— включаем ПК , заходим в настройку bios-а настраиваем parallel port

вариант USB-схемы считывания nand xbox 360 здесь

— загружаем windows

— запускаем командную строку

— переходим в паку куда распаковали nandpro. например > cd C:\nandpro

— рабочей станет папка C:\nandpro>

— считываем первый дамп nand.

C:\nandpro> nandpro lpt: -r16 nand1.bin

(-r чтение , 16 — объем nand-флешки, если у вас 256Мб или 512Мб вписываем -r64, *.bin — название выходного файла)

размер можно узнать по маркировке микросхемы флеш-памяти NAND:

HY27US08281A — 16мбайт

HY27UF082G2A или HY27UF082G2B — 256мбайт

HY27UF084G2B или h37U4G8F2C — 512мбайт

— Убедитесь, что FlashConfig имеет верное значение (таблица ниже).

Значение flashconfig | Тип материнской платы | Объем NAND

01198010 ……………… | Xenon,Zephyr,Falcon …. | 16 Мб

00023010 ……………… | Jasper, Cronos ……………|16 Мб

008A3020 ……………… | Jasper, Cronos ……………| 256 Мб

00AA3020 ……………… | Jasper, Cronos ………….. | 512 Мб

При неверном значении FlashConfig проверьте качество соединения проводов. Нажмите любую клавишу, дождитесь окончания считывание NAND-а.

Во время чтения могут возникать ошибки типа 250, 280, 300. Если они повторяются в одном и том же месте при нескольких считываниях, значит это битые сектора и нужно производить их ремаппинг во фрибут образе. Процесс переноса битых секторов читаем по этой ссылке, все что относится к BadBlockRemapperHelper4Nandpro

— ждем

— один образ на 16Мб считывается по lpt минут 30-40

— на 256 и 512 лучше использовать usb nand-extractor

,

либо придется ждать по 3 часа считываение по LPT одного 256мб образа,а нам нужно хотябы 3.

через USB — все гораздо быстрей

— по завершении запускаем считывание еще раз, но с другим названием итогового файла. Например,

nandpro lpt: -r16 nand2.bin ( между считываниями питание платы не отключать иначе md5 сумма будет различной даже при верном считывании nand)

— затем nandpro lpt: -r16 nand3.bin

— когда получены (через USB или LPT ) хотябы 3 образа (можно и больше), сравниваем их например в total commander

Если файлы идентичны идем дальше

Проверяем подходит ли наш нанд для freeboot

— Данные должны быть такими:

Exploitable CD versions(Версии CD подверженные взлому):

1888, 1902, 1903, 1920,1921: exploitable xenon

4558: exploitable Zephyr

5761, 5766, 5770: exploitable falcon

6712, 6723: exploitable jasper

если в поле CD у вас нет версии из списка, то увы. Отпаивайте провода и собирайте бокс назад. Если все подходит — идем далее.

CD-версию Xell можно узнать с помощью программы 360 Flash Tool.exe, открыв в ней снятый образ с NAND флэш-памяти.

Затем заливаем в nand-флешку Xell — линукс загрузчик, чтобы узнать cpu-key нашего xbox 360.

— Скопируйте Xell для вашей материнской платы в папку с NandPro. Xell должен быть соответствующей CD-версии.

— Запустите NandPro в командной строке, введите Nandpro lpt: -wY xell_hack.bin (где xell_hack.bin – имя Xell для вашей материнской платы, а Y – объём NAND флэш-памяти 16,256 или 512).

— USB вариант для spi flasher Nandpro usb: -wY xell_hack.bin

— дождитесь окончания записи Xell

— После завершения процесса записи отключите приставку от блока питания выключите ПК

— отсоедините lpt разъем от ПК.

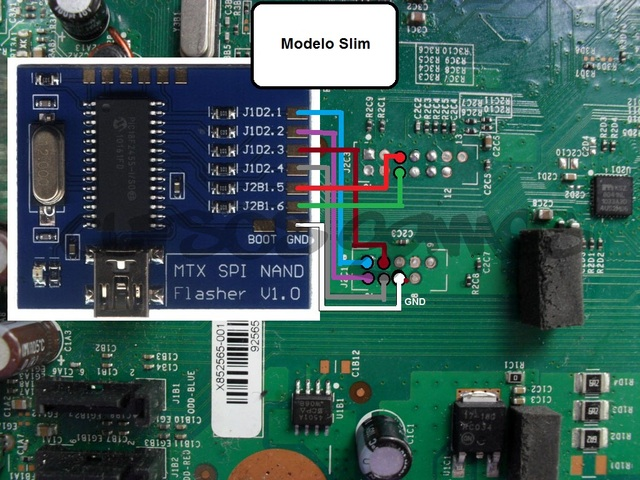

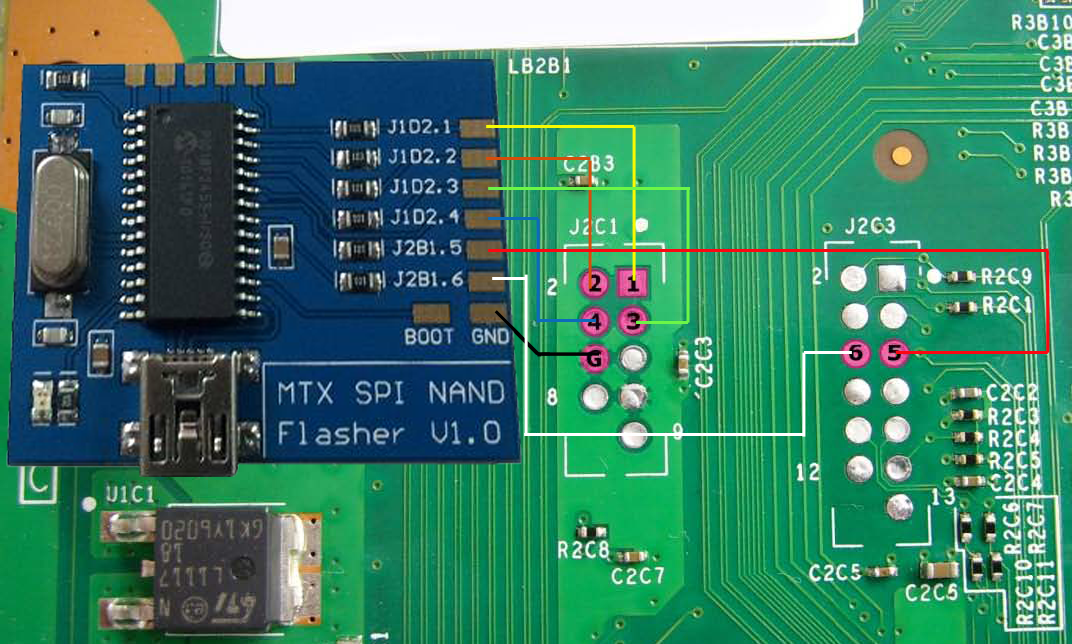

— снова паяем согласно фото, то что уже есть на плате не отпаиваем

Диоды ставим правильно , согласно схеме.

Для Zephyr/Opus/Falcon/Jasper/Kronos:

если Xenon ревизия , то так

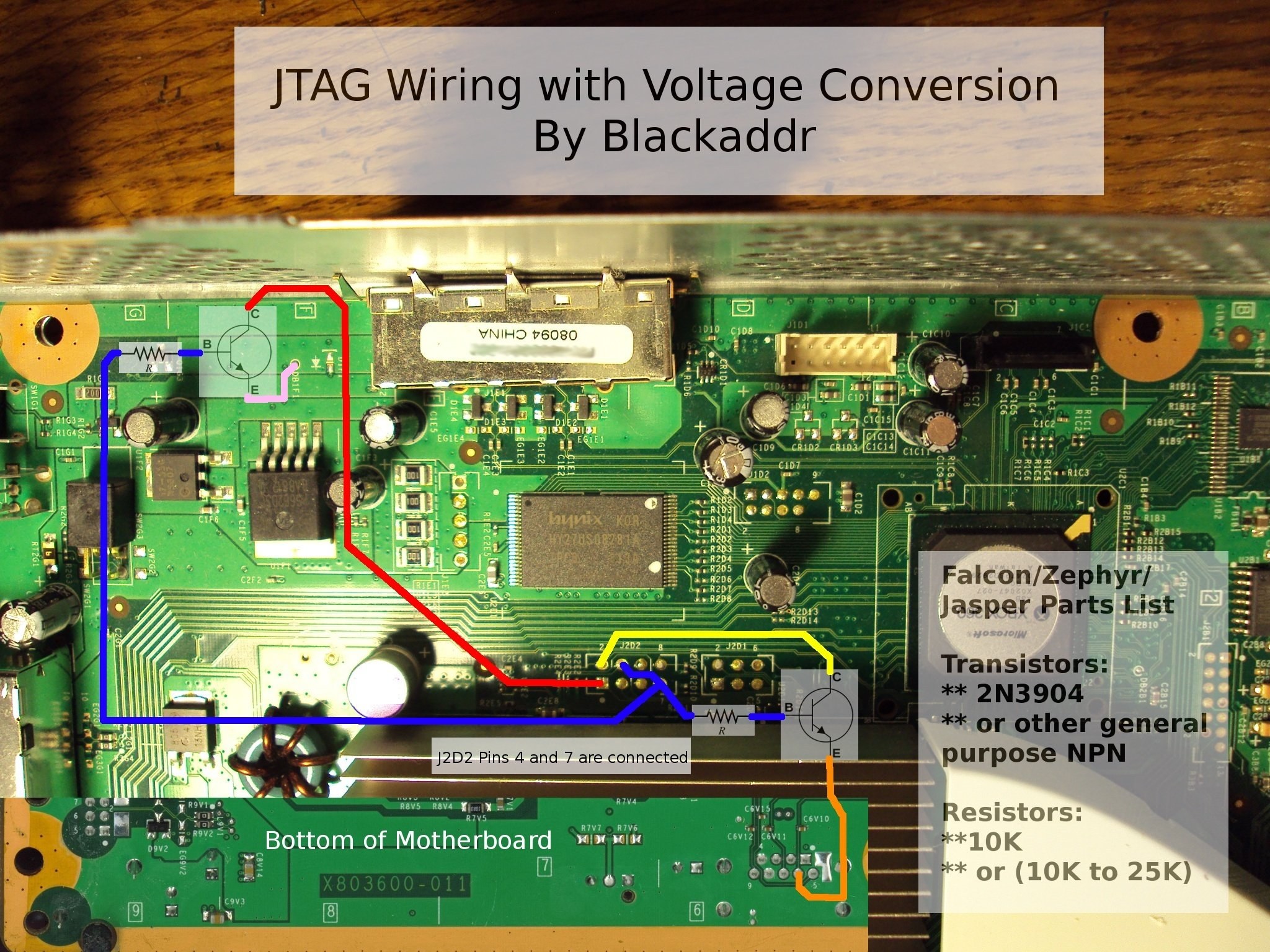

также привожу альтернативную JTAG-схему, если на диодах не работает или их просто не нашли

тут потребуются:

2 х транзистора 2N3904 (или другой NPN-типа )

2 x 10 КОм 0.125 ВТ резистора (можно и 0.25)

на схеме плохо видно, но пины 4 и 7 площадки J2D2 соеденены

Внимательно изучаем расположение эммитера , коллектора и базы транзистора для своей модели

— проверив пайку, подключаем xbox360 к телевизору и включаем

— Сфотографируйте появившиеся надписи на экране вашего телевизора

— Объединив строки 03 и 06, получим CPU ключ. Сохраним его в блокноте.

— Выключаем консоль и блок питания.

Создаем Freeboot-образ:

— запускаем freeBOOT_ToolBox_Maker

— вставляем CPU-ключ в соответствующее поле

— выбираем тип материнской платы(motherboard type)

— в destination directory указываем папку где будет сформирован freeboot-образ

— в filename destination — выбираем имя freeboot-файла

— если нет DVD-привода — отмечаем my console do not have a DVD drive

— жмем generate freeboot

— выбираем оригинальный nand-файл

— в итоге получаем 12611 freeboot-образ в папке, в соответствии с destination directory

— помещаем freeboot-образ в папку с nandpro.exe

Теперь заливаем freeboot образ в нанд-флеш на материнской плате xbox

— Подключаем питание к плате (дежурный режим)

— вводим Nandpro lpt: -wY freeboot.bin (где freeboot.bin – имя freeboot-образа , а Y – объём NAND флэш-памяти 16,или 64).

— USB вариант для spi flasher Nandpro usb: -wY freeboot.bin

— ждем окончания процедуры, время опять же зависит от используемого интерфейса LTP или USB

— если есть битые сектора в nand-микросхеме, то при записи будет ошибка 210(при считывании 250), и нужно производить ремаппинг секторов, иначе freeboot выдаст 3 красных огня при включении.

— после окончания процесса отпаиваем только lpt-схему ,а jtag-схему(что паяли для запуска xell) оставляем навсегда.

— Ну и наконец-то, проверяем работу уже готовой Freeboot xbox 360 консоли

Вышла новая версия ПО Octoplus JTAG PRO v.1.3.9!

Вышла новая версия ПО Octoplus JTAG PRO v.1.3.9!

Добавлена поддержка через eMMC (ISP) для Samsung SM-G316HU, Samsung SM-J320F, LG AS330, LG M400DY и поддержка через USB для LG H961N, LG AS330 и LG M160!

Добавлены «запись / обновление прошивки eMMC» для многочисленных чипов Samsung eMMC.

Прошивка программатора была обновлена.

Загружены новые “Live logs” в зону поддержки.

Некоторые исправления и улучшения.

Новые возможности ПО Octoplus JTAG PRO v.1.3.9:

- Добавлена поддержка через eMMC для следующих моделей:

- Samsung SM-G316HU — добавлены чтение / запись / стирание, простое восстановление, менеджер разделов, конструктор для файлов восстановления

- Samsung SM-J320F — добавлены чтение / запись / стирание, простое восстановление, менеджер разделов, конструктор для файлов восстановления

- LG AS330 — добавлены чтение / запись / стирание, простое восстановление, менеджер разделов, конструктор для файлов восстановления

- LG M400DY — добавлены чтение / запись / стирание, простое восстановление, менеджер разделов, конструктор для файлов восстановления

- Добавлена поддержка через USB для следующих моделей:

- LG H961N — добавлены чтение / запись / полное стирание, простое восстановление, менеджер разделов, конструктор для файлов восстановления

- LG AS330 — добавлены чтение / запись / полное стирание, простое восстановление, менеджер разделов, конструктор для файлов восстановления

- LG M160 — добавлены чтение / запись / полное стирание, простое восстановление, менеджер разделов, конструктор для файлов восстановления

- Загружен файл SRF для LG K430 в зону поддержки (папка «USER UPLOADED SRF») (спасибо Mr. agrsat)

- Добавлены «запись / обновление прошивки eMMC» для следующих чипов Samsung eMMC:

- KLM4G1FE3B-B001 (M4G1FB)

- KMS5U000KM-B308 (SSU00M)

- KMSJS000KM-B308 (SJS00M)

- KMVUS000LA-B304 (VUS00A)

- KLM8G2FE3B-B001 (M8G2FB)

- KMJJS000WA-B409 (JJS00A)

- KMKUS000VM-B410 (KUS00M)

- KMNJS000ZM-B205 (KJS00M)

- KMK7U000VM-B309 (K7U00M)

- KMN5X000ZM-B209 (N5XZMB)

- KLM8G1WEMB-B031 (8WMB3R)

- KMK7X000VM-B314 (K7XVMB)

- KMK5X000VM-B314 (K5XVMB)

Мы оттестировали и добавили фотографии тестпоинтов (TP), для форсирования eMMC в режим загрузки для перечисленных выше чипов eMMC.

Для записи / обновления прошивки eMMC, пожалуйста, выполните следующие шаги:

- Выберите опцию интерфейс «eMMC»

- Выберите «Марка: eMMC_чипы»

- Выберите заводской номер чипа eMMC в списке ПО «Модель:»

- Нажмите кнопку «Помощь» для просмотра распиновки eMMC и тестпоинтов. Ознакомьтесь с инструкцией

- Припаяйте все требующиеся провода для подсоединения eMMC (если требуется, припаяйте провод TP для форсирования eMMC в загрузочный режим, название продукта будет отображаться как 000000)

- Нажмите кнопку «Соединение» для соединения с eMMC (если требуется, подсоедините провод TP к GND)

- После успешного подключения отсоедините провод TP от GND и перейдите на закладку «eMMC сервис» в программном обеспечении

- Нажмите кнопку «запись / обновление прошивки», выберите нужный чип eMMC из списка и нажмите кнопку «запись / обновление прошивки eMMC»

Внимание: Пожалуйста, не выбирайте неправильный чип eMMC (с не совпадающим номером)! Если вы запишите неправильную прошивку, вы повредите ваш eMMC!

- Добавлен автоматический анализ зоны TA (Trim Area) в устройствах Sony (структура, IMEI, статус блокировки).

С данного момента ПО автоматически проверяет зону ТА и информирует вас, повреждена ли зона ТА или с ней все в порядке.

Вы должны помнить, для успешного восстановления большинства устройств Sony, их зона TA должна быть оригинальной и не поврежденной. - Прошивка программатора была обновлена до версии 1.19. В версии прошивки 1.19 мы улучшили процедуру распознания eMMC.

Для автоматического обновления прошивки нужно подключить программатор, а затем запустить программное обеспечение.

Также, вы можете обновить прошивку вручную, с помощью кнопки «Обновить прошивку программатора» на закладке «Добро пожаловать» в ПО Octoplus JTAG PRO. - В зону поддержки добавлены новые файлы “Live logs”

- Некоторые изменения в информации логов

- Все распиновки, а также руководства по восстановлению, доступны в основном ПО (кнопка «Помощь»)

Скачать ПО Octoplus JTAG PRO v.1.3.9

Open-PLC

Open-PLC|

Прошивка микроконтроллера |

|

Оглавление

Первый вопрос, который возникает при знакомстве с контроллерами STM32103C8T6, это как залить «прошивку» в микроконтроллер?

Существует три варианта:

используя UART

используя JTAG-SWD

написать собственный загрузчик

Оборудование

Программы

Заливка «прошивки» с использованием UART

Использование UART- самый простой вариант прошивки. Утилита «Flash Loader Demonstrator» бесплатна и её можно скачать как с официального сайта, так и отсюда (link).

В системной области памяти микроконтроллера зашит bootloader. Именно он и позволяет записать прошивку во flash-память через последовательный интерфейс.

Детально bootloader описан в документе AN2606 ( CD00167594.pdf ), а используемый им протокол — в документе AN3155 ( CD00264342.pdf ). Это для тех, кто хочет исчерпывающей информации, а мы рассмотрим процесс прошивки через bootloader вкратце.

Для начала вам нужно установить себе на компьютер утилиту «Flash Loader Demonstrator».

Далее, нужно соединить контроллер с компьютером через UART1. STM32F103C8T6 имеет 48 — выводный корпус, в котором UART1 выведен на ноги 30 — PA9 — (Tx) и 31 — PA10 — (Rx). Подключить +5V и GND к микроконтроллеру.

Обратите внимание, что в контроллере используется UART с уровнями 0/+3,3V, а не 0/+5V, как у Arduino.

«Ногу» Tx контроллера нужно соединить с «ногой» Rx адаптера USB — UART, а «ногу» Rx контроллера — с ногой Tx адаптера. Кроме этого, контроллер нужно запитать и обеспечить нужные уровни на ногах BOOT0 ( pin 44 ), BOOT1 ( PB2 — pin 20 ). Для запуска bootloadera ногу BOOT1 нужно подтянуть к «земле» или GND, а BOOT0 — к «питанию» 3.3V, для этого на контроллере есть перемычки BOOT0 и BOOT1. Или проще: поместить перемычку BOOT0 в положение «1». Нажать и отпустить «Reset», после этого котроллер входит в режим загрузки.

Далее пользуемся утилитой «Flash Loader Demonstrator». Откроется страничка, на которой нужно выбрать com-порт, скорость обмена.

Чётность и

количество бит данных уже настроены как надо, скорость можно менять —

контроллер в процессе инициализации обмена настраивается на выбранную

скорость автоматически, COM-порт нужно выбрать тот, который создался

при подключении USB-to-COM адаптера к компьютеру. После того, как всё

настроили — жмём «Next».

О том, что всё нормально и соединиться с контроллером удалось, нам сообщит зелёный сигнал светофора на следующей страничке. Если связь не установится — на эту страничку нас вообще не пустят, сообщив, что контроллер не отвечает.

При

установлении связи программа автоматически определит сколько у

контроллера flash-памяти и защищена ли эта память от чтения. Если

память защищена, то нажав кнопку «Remove protection» защиту

можно снять, но при этом содержимое памяти будет стёрто (предыдущая

записанная туда прошивка уничтожится). Жмём «Next».

В следующем

окне нам предлагают выбрать тип микроконтроллера ( хотя

непонятно зачем, — он и так автоматически определяется ), а

также показывают для нашего контроллера PID, карту flash-памяти, и

версию bootloader-а. Просто жмём «Next».

В следующем

окне нужно выбрать, что мы собственно хотим с нашим контроллером

делать. Тут возможны следующие варианты: «Erase»

( стереть ), «Download to device» ( загрузить

в контроллер прошивку ), «Upload from device»

( считать прошивку с контроллера ), «Enable / Disable

Flash protection» ( включить / выключить защиту

flash-памяти ), Edit option bytes ( изменить байты опций ).

Соответственно, если мы хотим залить «прошивку» — выбираем

«Download to device», потом жмём на квадрат с тремя точками

и выбираем в проводнике файл с прошивкой, которую надо залить, после

чего опять жмём «Next».

На следующей

странице внизу появится прогресс-бар, в котором будет показан ход

выполнения процедуры загрузки.

После того,

как вся прошивка будет загружена в контроллер, этот прогресс-бар

станет зелёным и в нём белыми буквами будет написано: «Download

operation finished successfully» ( операция загрузки

успешно завершена ).Далее, можно нажать кнопку «Close»

чтобы закрыть «Flash Loader Demonstrator» или «Back»,

чтобы вернуться на стартовую страничку.

Вернуть перемычки в состояние «0» и нажать «Reset», чтобы программа начала выполняться.

Заливка «прошивки» с использованием JTAG SWD

В этом случае вам нужно установить себе на компьютер утилиту «STM32 ST-LINK Utility» и подключить ST-LINK/V2, подать питание на плату микроконтроллера. Рекомендуется использовать питание 5V.

После запуска

STM32 ST-LINK откроется стартовая страничка программы.

Нажать кнопку

«Connect to the target». Микроконтроллер должен

определиться автоматически.

Нажимаем

кнопку «Open file», в открывшемся окне выбираем нужный

файл.

Далее в меню

выбираем «Target» -> «Program &

Verify»… ( CTRL+P )

В открывшемся

окне «Download» нажимаем «Start». Программа

должна загрузиться и в случае, если установлен флажок «Reset

after programming» стартовать автоматически.

В случае, если при попытке коннекта микроконтроллер не определился, то одна из вероятных причин — это ремаппинг «ног» JTAG. В этом случае последовательность действий следующая:

Нажать и удерживать «Reset» на плате микроконтроллера.

Нажать кнопку «Connect to the target», подождать 1 секунду и отпустить «Reset».

Оглавление

Аппаратная отладкадля инженеров-реверс-инженеров. Часть 2: JTAG, твердотельные накопители и извлечение микропрограмм.

В продолжение моего последнего сообщения о SWD и отладке оборудования я хотел глубоко погрузиться в JTAG с точки зрения обратного инжиниринга. Предыдущий пост получил много отличных отзывов, и кажется, что людям интересна эта тема, поэтому я хотел продолжить серию и расширить другой механизм аппаратной отладки. Для тех, кто не знаком, JTAG — это механизм отладки на аппаратном уровне, который используют многие встроенные процессоры. В этом посте я надеюсь объяснить, как подойти к JTAG с точки зрения обратного инженера, и по ходу предоставить несколько практических примеров.

Goals

В этом посте я надеюсь сделать следующее:

- Объяснить, как работает JTAG

- Продемонстрировать, как обнаружить и использовать порт / интерфейс JTAG на неизвестной цели

- Предоставить обзор некоторых из текущих Инструменты OSS, которые можно использовать для взаимодействия с интерфейсом JTAG

- Использование JTAG для извлечения микропрограмм и отладки целевого объекта

Кроме того, прежде чем я дам обзор, я хотел бы указать на несколько замечательных ресурсов для изучения JTAG

JTAG Обзор

JTAG — это аппаратный интерфейс, разработанный для помощи разработчикам и тестировщикам при низкоуровневой отладке.Изначально JTAG был разработан для тестирования интегральных схем и, в частности, для выборки выводов ввода-вывода на тестируемой цели. Этот тип интерфейса отладки позволяет инженерам тестировать соединения на печатных платах без необходимости проверять сам физический контакт. Интерфейс JTAG управляется с помощью конечного автомата, описанного ниже:

Одна из важных вещей, которые следует помнить о JTAG на этом уровне, заключается в том, что он включает в себя два регистра, регистр команд и регистр данных.Чтобы использовать эти регистры, правильные состояния в вышеуказанном конечном автомате должны быть введены с использованием следующих сигналов интерфейса:

| Строка | Использование |

|---|---|

| TMS | Этот вывод используется для навигации и управления JTAG. конечный автомат |

| TDI | Входной контакт, используемый для записи данных в цель |

| TDO | Выходной контакт, используемый для обратного чтения данных из цели |

| TCK | Используется для определения, когда данные выбирается для всех входов и выходов |

| TRST (необязательно) | Этот вывод можно использовать для сброса конечного автомата в начальное состояние. |

. записывается или считывается через TDI и TDO соответственно.TMS выбирается по нарастающему фронту TCK, что означает, что строка TMS должна быть подтверждена до того, как TCK будет переключен для навигации по конечному автомату. Затем данные сдвигаются в регистр команд (IR) или регистр данных (DR) в зависимости от состояния конечного автомата JTAG. Когда операция завершена (или после фазы обновления DR / IR) результирующие данные могут быть сдвинуты на из DR путем перехода в состояние Shift-DR . Имея эти примитивы, производители могут реализовать любые функции, которые они пожелают, через JTAG.

Стандарт JTAG рассматривает IR и DR как регистры сдвига, и благодаря этому несколько целей могут быть соединены гирляндой вместе.

Вкратце, JTAG определяет конечный автомат, для управления которым используется минимум 4 сигнала. С этим конечным автоматом конечные пользователи могут писать и читать из двух регистров сдвига, IR и DR.

Регистры JTAG

JTAG использует два основных регистра, регистр команд и регистр данных. Регистр команд используется для определения того, какую функцию собирается выполнять контроллер JTAG, например, чтение или запись в память.Регистр данных затем используется как дополнительный вход в регистр команд, в предыдущем примере они могут использоваться для предоставления адреса для чтения или записи. Эти регистры могут различаться по размеру в зависимости от их функции.

Для записи в регистр нужно выполнить следующие шаги, мы будем использовать IR в качестве примера:

- Введите

Test Logic Resetstate (TLR) (Это можно сделать, установив строкуTMSи циклCLK5 раз) - Введите

Выберите состояние IR Scan - Введите

Capture IR Состояние - Введите

Shift IR— Здесь мы загружаем данные в IR из TDI - Enter

Exit IRstate - Enter

Update IRstate — этот этап «фиксирует» значение в IR.

После этого, если регистры данных не требуются, операция будет выполнена, и результат (если есть) будет загружен в регистр данных для смещения. Однако многие инструкции требуют, чтобы регистр данных также был заполнен перед работой. В этом случае, как только регистр данных будет записан и обновлен, операция будет выполнена, и результат может быть сдвинут из регистра данных.

Некоторые инструкции не требуют загрузки DR, например, если бы мы загрузили инструкцию IDCODE в IR (1110b), это загрузило бы значение IDCODE процессора в регистр данных, чтобы мы могли затем синхронизировать и прочитать это на TDO .Чтобы прочитать результат из TDO , нужно перейти в состояние Shift-DR и синхронизировать 32 бита на TDI , это приведет к смещению данных в регистре данных на TDO линия. На изображении ниже наглядно показано, что произойдет, если загрузить в IR инструкцию IDCODE

. Важно помнить, что IR и DR можно рассматривать как регистры сдвига, что означает, что когда мы обновляем их новыми значениями, старые значения затем смещаются на TDO .

Стандарт JTAG определяет следующие регистры команд:

-

BYPASS- Эта инструкция соединяет

TDIиTDO - В состоянии

Shift DRданные передаются изTDIвTDOс задержкой в один циклTCK - 0 загружается в регистр данных во время состояния

Capture DR - Это можно использовать для определения количества устройств в цепочке сканирования

- Эта инструкция соединяет

-

IDCODE- При загрузке регистр идентификатора кода устройства выбирается в качестве последовательного пути между TDI и TDO

- В состоянии Capture-DR 32-битный код идентификатора устройства загружается в эту секцию сдвига

- В состоянии Shift-DR эти данные сдвигается наружу, младший бит первым

- Основные концепции JTAG

- Навигация по конечному автомату осуществляется с помощью 4 сигналов:

TCK,TMS,TDOиTDI -

TDIиспользуется для обеспечения ввода,TDOиспользуется для вывода - С помощью этого конечного автомата данные могут быть сдвинуты в ИК (

Shift IR) и DR (Shift DR) - Регистр команд (

IR) можно рассматривать как функцию, а регистр данных (DR) можно рассматривать как аргумент этой функции.DRиIR, предыдущее содержимое сдвигается наTDO - Как только данные сдвигаются в эти регистры, может выполняться операция (полностью зависит от реализации хоста, за исключением нескольких зарезервированных инструкций)

- Данные считывает из цели путем сдвига его на

TDOиз регистра данных в состоянииShift DR.

- Навигация по конечному автомату осуществляется с помощью 4 сигналов:

Итак, теперь, когда мы рассмотрели, как JTAG работает на низком уровне, мы должны поговорить о том, почему нам это может быть небезразлично, и как этот интерфейс может предоставить доступ к полезным функциям для реверс-инженеров. Одно из наиболее часто используемых приложений интерфейса JTAG — отладка на аппаратном уровне (отсюда и название этого поста). Это реализуется производителем микросхемы и может варьироваться от микросхемы к микросхеме, однако одной из наиболее распространенных реализаций отладки на аппаратном уровне для целей ARM является интерфейс отладки CoreSight от ARM.Это та же реализация, с которой мы общались через SWD в моем последнем посте, только в этом случае порт доступа отладки связывается через JTAG. Подробности реализации JTAG можно найти здесь. К счастью для нас, для связи с этими портами можно использовать отличные инструменты OSS — этот пост будет посвящен использованию OpenOCD.

OpenOCD заботится об использовании интерфейса JTAG или SWD для предоставления конечному пользователю различных примитивов, которые предоставляются интерфейсом отладки, предоставляемым через CoreSight DAP.Архитектура Coresight / DAP довольно сложна и слишком сложна для рассмотрения в этом (уже длинном) посте, поэтому я потенциально сохраню это для другого поста

JTAG for Reverse Engineers

Чрезвычайно важно иметь твердое понимание основ протокола подходя к чему-то подобному с точки зрения реверс-инженера. При обратном проектировании оборудования (или программного обеспечения) вы хотите, чтобы ваша основная правда была раскрыта, поскольку всегда есть бесконечное количество неизвестных.В следующих нескольких разделах будет рассмотрено, как мы можем воспользоваться нашим низкоуровневым знанием этих протоколов, чтобы помочь нам на нашем пути к получению доступа к отладке на аппаратном уровне через JTAG. Первое, что нам нужно сделать, это определить распиновку и разрешить ли открытые контакты доступ к интерфейсу JTAG.

Определение распиновки

Сигнальные линии JTAG часто сгруппированы вместе, иногда (если вам очень повезет!) Вы увидите один из следующих заголовков:

Но если вы найдете что-то подобное, возможно, это не так. точные группировки сигналов, поэтому мы обсудим, как определить распиновку, если предполагается, что она используется для JTAG.

При обратном проектировании чего-то вроде этого вы хотите начать с того, что вы знаете. Поскольку мы знаем, что большинство производителей по меньшей мере реализуют IDCODE и BYPASS , давайте поговорим о том, как мы можем воспользоваться этими двумя инструкциями.

Если вы определили то, что вы считаете потенциальным заголовком или распиновкой JTAG, но не знаете контактов, мы можем использовать поведение этих двух регистров для определения распиновки.

Поскольку регистр IDCODE обычно загружается как IR по умолчанию, можно проверить предполагаемую распиновку, выполнив следующие действия:

- Назначьте роли потенциальным выходным контактам (TMS, TCK и т. Д.)

- Войдите в логику тестирования

Сброс состояния - Введите

Выберите DR Scan,Capture DR,Shift DR - Значения часов 32 на

TDIи контролируйтеTDOна предмет действительного значенияIDCODE - Проверьте

IDCODEзначение, которое вы перенесли, если оно выглядит правильным, поздравляем! В противном случае переназначьте контакты и повторите!

В дополнение к использованию того факта, что регистр IDCODE часто загружается в IR по умолчанию, мы также можем использовать тот факт, что и IR, и DR ведут себя как регистры сдвига, поэтому, если мы предположим общий регистр длины (часто работает 32 бита), мы можем попытаться перебрать распиновку, выполнив следующие действия:

- Назначьте роли потенциальным выходным контактам (TMS, TCK и т. д.)

- Используя эти предполагаемые значения, введите

Test Logic Resetstate - Введите

Shift IRstate - Shift в уникальном 32-битном значении на

TDI - Продолжайте сдвигать 1 на

TDI, отслеживая свой уникальный шаблон на TDO (обязательно сделайте это как аренда 32 раза!). - Если узор обнаружен, поздравляем! В противном случае выберите новые назначения для контактов и повторите!

Оба этих метода используются ранее упомянутым сценарием JTAGEnum, а также JTAGULATOR.

Определение длины инструкции

После того, как вы определили распиновку цели, можно начинать настоящее веселье. Следующим шагом будет определение длины IR / DR. Для этого, начиная с IR, войдите в состояние Shift IR и заполните цепочку единицами на TDI , используя большое число, например 1024 или 4096, а затем синхронизируйте 0.Как только это будет сделано, просто продолжайте синхронизировать единицы на TDI , считая количество тактов, которое требуется до появления 0 на TDO . Это скажет вам длину IR. Как только у вас есть это, вы можете войти в состояние Shift DR и повторить процесс, чтобы определить состояние DR. Это то, что urjtag делает очень хорошо.

Практический пример: Samsung M.2 SSD

Целью этого поста будет SSD Samsung M.2, который я недавно восстановил со старого ноутбука.Посмотрев на печатную плату и определив, что потенциально может быть заголовками JTAG, я хотел обрисовать процесс от начала до конца.

Как упоминалось ранее, линии JTAG часто сгруппированы, поэтому при взгляде на новую платформу с точки зрения оборудования поиск групп контактов больше 5 всегда является хорошим началом. К счастью для нас, в этой цели есть 9 переходных отверстий, расположенных вдоль внешней стороны печатной платы. Начнем с исследования уровней напряжения на этих выводах, когда привод находится в нормальном рабочем состоянии

| Вывод | Уровень напряжения | Использование |

|---|---|---|

| 1 | 0.1 В | ??? |

| 2 | 1,8 В | ??? |

| 3 | 0,1 В | ??? |

| 4 | 0,1 В | ??? |

| 5 | 0,1 В | ??? |

| 6 | 0,1 В | ??? |

| 7 | ЗЕМЛЯ | ЗЕМЛЯ |

| 8 | 1,8 В | ??? |

| 9 | 1.8 В | ??? |

С первого прохода — эти значения напряжения нам ни о чем не говорят, так что мы можем определить на основе имеющейся информации? Во-первых, у нас есть GND, который легко определить, используя режим непрерывности на мультиметре и проверяя что-то вроде экрана разъема USB (пока цель, конечно, отключена!). Затем у нас есть одна линия на 1,8 В, обычно можно было бы ожидать, что это будет TMS, поскольку в большинстве документов рекомендуется поддерживать высокий уровень.

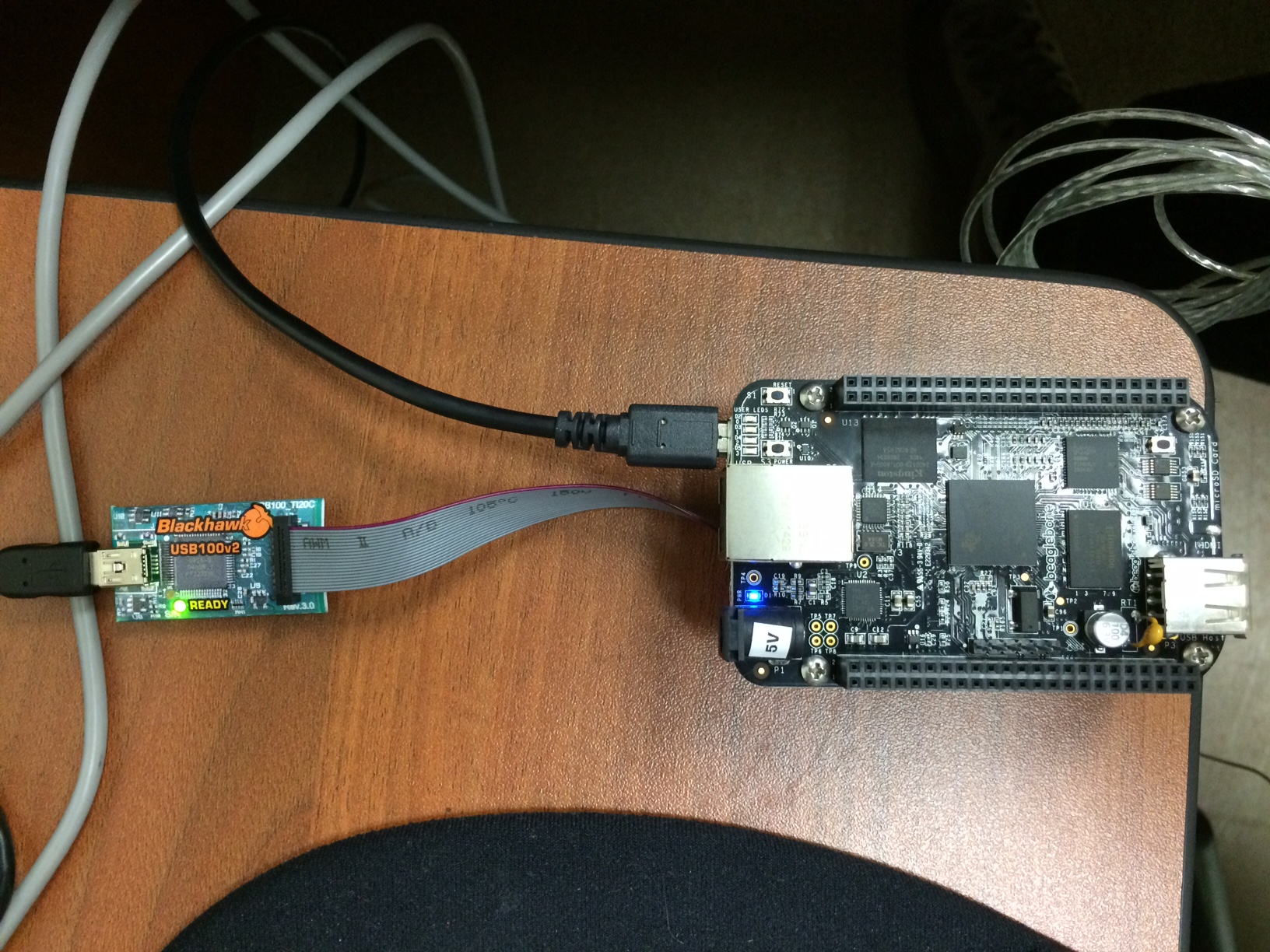

Для определения распиновки мы будем использовать Raspberry Pi и проект JTAGEnum. Этот сценарий использует вышеупомянутые методы, чтобы попытаться идентифицировать распиновку JTAG. Здесь также важно отметить, что логические уровни находятся на уровне 1,8 В, поэтому нам нужно будет использовать переключатель логического уровня, если мы собираемся взаимодействовать с этой целью. JTAGEnum.sh использует линии GPIO Raspberry Pi для активации целевого интерфейса, в сценарии оболочки они включают карту значений GPIO, которые можно увидеть ниже:

1

2

3

# определить контакты BCM (отображаются непосредственно в / sys / class / gpio / gpio $ {pin [N]})

# 5v 5v г 14 15 18 г 23 24 г 25 8 7 1 г 12 г 16 20 21

# 3v 2 3 4 г 17 27 22 3v 10 9 11 г 0 5 6 13 19 26 г

Используя нашу таблицу выше, мы подключим следующие GPIO к неизвестному заголовку:

| Вывод заголовка SSD | RPi GPIO |

|---|---|

| 1 | 2 |

| 2 | 3 |

| 3 | 9 |

| 4 | 10 |

| 5 | 11 |

| 6 | 25 |

In JTAGenum.sh мы изменим переменную pins следующим образом:

1

2

контактов = (9 11 25 2 3 10)

pinnames = (pin1 pin2 pin3 pin4 pin5 pin6)

Теперь с подключенными выводами и установленным переключателем логического уровня мы можем запустить JTAGenum.sh .

Выполнение скрипта, подключенного, как показано ниже, дает ТОННУ результатов, результат можно увидеть [здесь]. К счастью для нас, он правильно определяет две возможные конфигурации, которые можно увидеть ниже:

1

2

НАЙДЕНО! ntrst: pin4 (RPi GPIO 2) tck: pin6 (RPi GPIO 10) tms: pin1 (RPi GPIO 9) tdo: pin3 (RPi GPIO 25) tdi: pin2 (RPi GPIO 11) Длина IR: 4

НАШЕЛ! ntrst: pin5 (RPi GPIO 3) tck: pin6 (RPi GPIO 10) tms: pin1 (RPi GPIO 9) tdo: pin3 (RPi GPIO 25) tdi: pin2 (RPi GPIO 11) Длина IR: 4

Затем сценарий выполнил сканирование идентификатора.Вы могли заметить, что для этого было получено много результатов, как их отфильтровать? Есть несколько вещей, которые вы можете сделать для фильтрации результатов, например, у нас, вероятно, только 1-2 устройства в цепочке сканирования (ЦП и флэш-память), поэтому мы можем сразу игнорировать те, которые имеют более 2-3 записей. Затем вы можете исключить те, которые имеют длинные (более 4-5) последовательности единиц или нулей. К счастью, в этом списке есть идентификатор, который я видел раньше: 0x4ba00477 — этот идентификатор предназначен для ядра ARM Cortex, и я видел его раньше, когда пытался получить доступ к Beaglebone Black.

1

2

3

4

5

6

7

8

ntrst: pin4 tck: pin6 tms: pin1 tdo: pin3 tdi: pin2 устройств: 1

0x4ba00477

ntrst: pin4 tck: pin6 tms: pin1 tdo: pin3 tdi: pin5 устройства: 1

0x4ba00477

ntrst: pin5 tck: pin6 tms: pin1 tdo: pin3 tdi: pin2 устройства: 1

0x4ba00477

ntrst: pin5 tck: pin6 tms: pin1 tdo: pin3 tdi: pin4 устройства: 1

0x4ba00477

Вы заметите, что при сканировании IDCODE значение TDI меняется, потому что этот метод вообще не полагается на TDI , поэтому это предположение.

К счастью, некоторые из этих результатов хорошо совпадают с результатами сканирования по образцу, так что теперь мы можем предположить, что знаем распиновку интерфейса JTAG!

| Контакт | Уровень напряжения | Использование |

|---|---|---|

| 1 | 0,1 | ??? |

| 2 | 1,8 | ??? |

| 3 | 0,1 | TMS |

| 4 | 0,1 | CLK |

| 5 | 0.1 | TDI |

| 6 | 0,1 | TDO |

| 7 | GND | GND |

| 8 | 1,8 | ??? |

| 9 | 1,8 | ??? |

Практический пример: определение длины инструкции с помощью UrJtag

Хотя OpenOCD отлично подходит для взаимодействия с контроллерами DAP и подключения к ядрам отладки, проект UrJTAG отлично подходит для взаимодействия с JTAG на низком уровне.Мы можем использовать это для определения различной длины DR с помощью их полезной команды discover . Этот метод использует те же принципы, упомянутые ранее, чтобы выбрать IR , затем сдвинуть большое количество единиц в DR , за которым следует 0, а затем синхронизировать больше единиц, пока в TDO не будет считан 0!

UrJTAG может использовать rc-файл, расположенный по адресу ~ / .jtag / rc , мой код выглядит следующим образом:

1

2

3

4

pi @ raspberrypi: ~ $ cat.jtag / rc

кабель gpio tck = 10 tms = 9 tdi = 11 tdo = 25

обнаруживать

обнаружить

Ниже мы можем увидеть результат запуска UrJTAG с этими командами:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21 год

22

23

24

25

26 год

27

28 год

29

30

31 год

32

33

34

35 год

pi @ raspberrypi: ~ $ sudo -E jtag

UrJTAG 2019.12 #

Авторские права (C) 2002, 2003 ETC s.r.o.

Copyright (C) 2007, 2008, 2009 Коля Ващк и соответствующие авторы

UrJTAG - бесплатное программное обеспечение, на которое распространяется Стандартная общественная лицензия GNU, и вы

добро пожаловать, чтобы изменить его и / или распространять его копии при определенных условиях.На UrJTAG нет гарантии.

предупреждение: UrJTAG может повредить ваше оборудование!

Введите «quit», чтобы выйти, «help», чтобы получить помощь.

Инициализация цепочки GPIO JTAG

ИК-длина: 4

Длина цепочки: 1

Id устройства: 01001011101000000000010001110111 (0x4BA00477)

Неизвестный производитель! (01000111011) (/ usr / local / share / urjtag / ПРОИЗВОДИТЕЛИ)

Определение длины ИК-излучения ... 4

Определение длины DR для IR 1111 ... 1 <- Это обход!

Определение длины DR для IR 0000 ... 1

Определение длины DR для IR 0001 ... 1

Определение длины DR для IR 0010... 1

Определение длины DR для IR 0011 ... 1

Определение длины DR для IR 0100 ... 1

Определение длины DR для IR 0101 ... 1

Определение длины DR для IR 0110 ... 1

Определение длины DR для IR 0111 ... 1

Определение длины DR для IR 1000 ... 35

Определение длины DR для IR 1001 ... 1

Определение длины DR для IR 1010 ... 35

Определение длины DR для IR 1011 ... 35

Определение длины DR для IR 1100 ... 1

Определение длины DR для IR 1101 ... 1

Определение длины DR для IR 1110 ... 32 <- Это IDCODE!

Я хотел выделить UrJTAG в этом посте, потому что он чрезвычайно полезен при просмотре цели с полностью неизвестной цепочкой сканирования или архитектурой DAP.К счастью для нас, IDCODE этой цели говорит нам, что это ARM, и мы, вероятно, сможем использовать CoreSight DAP, для этого мы будем использовать OpenOCD. Если вы смотрите на цепочку сканирования, о которой вы ничего не знаете, , , я обычно начинаю с UrJtag, чтобы получить карту всех регистров. Привязки python для UrJTAG также работают достаточно хорошо и могут использоваться для взаимодействия с JTAG на низком уровне.

Отладка JTAG через OpenOCD.

Поскольку мы знаем распиновку интерфейса JTAG на нашей цели, теперь мы можем перейти к использованию OpenOCD для связи с ним.Я выбираю OpenOCD для этой задачи, потому что он имеет отличную поддержку отладки для микроконтроллеров ARM, особенно серии Cortex, в которой используется CoreSight. Первое, что нам нужно сделать, это выбрать аппаратный адаптер, мы будем использовать коммутационный модуль FT2232H.

JTAG через FT2232H

Поняв распиновку, мы можем теперь попытаться поговорить с DAP с помощью OpenOCD. Для этого мы будем использовать адаптер FT2232H, для этого поста я использую стандартную коммутационную плату FT2232H. Эти платы могут использоваться для взаимодействия с несколькими интерфейсами аппаратного уровня и имеют отличную программную поддержку.Вы можете вспомнить, что я использовал их для таких вещей, как SWD, а также для сброса SPI flash. Используя эту плату вместе с преобразователем логического уровня от 3,3 В до 1,8 В, мы можем подключить его к цели следующим образом:

| FT2232H Pin | Target |

|---|---|

| CN2-7 | TCK |

| CN2-10 | TDI |

| CN2-9 | TDO |

| CN2-12 | TMS |

Затем мы напишем схему нашего файла конфигурации, начиная с переменных, которые мы знаем о цели.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21 год

22

23

24

25

26 год

27

источник [find target / swj-dp.tcl]

# Используется имя на SoC

если {[информация существует CHIPNAME]} {

установить _CHIPNAME $ CHIPNAME

} еще {

установить _CHIPNAME s4ln045x01

}

# Это идентификатор TAP, который мы обнаружили на предыдущем шаге

если {[информация существует CPUTAPID]} {

установить _CPUTAPID $ CPUTAPID

} еще {

установить _CPUTAPID 0x4ba00477

}

# Устанавливаем скорость нашего адаптера

адаптер_хз 200

# Мы действительно используем JTAG

транспорт выбрать jtag

# У нас нет пина SRST, только TRST вроде бы

reset_config trst_only

# Здесь мы создаем JTAG TAP / DAP, определяя расположение и характеристики нашего DAP

swj_newdap $ _CHIPNAME cpu -irlen 4 -ircapture 0x1 -irmask 0xf -expected-id $ _CPUTAPID

dap создать $ _CHIPNAME.dap -chain-position $ _CHIPNAME.cpu

установить _TARGETNAME $ _CHIPNAME.cpu

Когда мы запускаем openocd с этим файлом конфигурации, мы получаем следующие результаты:

1

2

3

4

5

6

7

8

9

10

11

12

13

invalidbaud @ wubuntu: ~ / blog / samsung-jtag $ sudo openocd -f minimodule.cfg -f config.cfg

Откройте встроенный отладчик 0.10.0 + dev-01040-ge7e681ac (2020-01-27-18: 55)

Под лицензией GNU GPL v2

Для отчетов об ошибках прочтите

http: // openocd.org / doc / doxygen / bugs.html

Информация: автоматический выбор первого доступного транспорта сеанса "jtag". Чтобы переопределить использование транспорта, выберите <транспорт>.

Предупреждение: транспорт "jtag" уже выбран

Информация: тактовая частота 200 кГц

Информация: JTAG tap: s4ln045x01.cpu tap / обнаружено устройство: 0x4ba00477 (mfg: 0x23b (ARM Ltd.), часть: 0xba00, ver: 0x4)

Информация: прослушивание порта 6666 для соединений tcl

Информация: прослушивание порта 4444 для соединений Telnet

Информация: JTAG tap: s4ln045x01.cpu tap / найдено устройство: 0x4ba00477 (mfg: 0x23b (ARM Ltd.), часть: 0xba00, ver: 0x4)

Предупреждение: сервисам gdb необходимо определить одну или несколько целей

Теперь давайте взглянем на DAP и посмотрим, есть ли там еще какая-либо соответствующая информация:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21 год

22

23

24

25

26 год

27

28 год

29

30

31 год

32

33

34

35 год

36

37

38

39

40

41 год

42

43 год

44 год

45

46

47

48

49

50

51

52

53

54

55

56

57 год

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

> dap info 0

Транзакция DAP остановлена (WAIT) - замедляется

Транзакция DAP остановлена (WAIT) - замедляется

Регистр идентификатора AP 0x24770002

Тип MEM-AP APB

БАЗА MEM-AP 0x80000000

Таблица ROM в устаревшем формате

Базовый адрес компонента 0x80000000

Периферийный ID 0x0000080000

Конструктор - 0x080, <недействительный>

Часть 0x0, нераспознанная

Класс компонента - 0x1, таблица ROM

Системная память MEMTYPE отсутствует: выделенная шина отладки

ROMTABLE [0x0] = 0x1003

Базовый адрес компонента 0x80001000

Периферийный ID 0x04008bbc14

Конструктор 0x4bb, ООО «АРМ».Часть 0xc14, отладка Cortex-R4 (модуль отладки)

Класс компонента - 0x9, компонент CoreSight

Тип - 0x15, логика отладки, процессор

ROMTABLE [0x4] = 0x2003

Базовый адрес компонента 0x80002000

Периферийный ID 0x04008bbc14

Конструктор 0x4bb, ООО «АРМ».

Часть 0xc14, отладка Cortex-R4 (модуль отладки)

Класс компонента - 0x9, компонент CoreSight

Тип - 0x15, логика отладки, процессор

ROMTABLE [0x8] = 0x3003

Базовый адрес компонента 0x80003000

Периферийный ID 0x04008bbc14

Конструктор 0x4bb, ООО «АРМ».Часть 0xc14, отладка Cortex-R4 (модуль отладки)

Класс компонента - 0x9, компонент CoreSight

Тип - 0x15, логика отладки, процессор

ROMTABLE [0xc] = 0x4003

Базовый адрес компонента 0x80004000

Недействительный CID 0x00000000

ROMTABLE [0x10] = 0x5003

Базовый адрес компонента 0x80005000

Недействительный CID 0x00000000

ROMTABLE [0x14] = 0x6003

Базовый адрес компонента 0x80006000

Недействительный CID 0x00000000

ROMTABLE [0x18] = 0x7003

Базовый адрес компонента 0x80007000

Недействительный CID 0x00000000

ROMTABLE [0x1c] = 0x8003

Базовый адрес компонента 0x80008000

Недействительный CID 0x00000000

ROMTABLE [0x20] = 0x9003

Базовый адрес компонента 0x80009000

Недействительный CID 0x00000000

ROMTABLE [0x24] = 0xa003

Базовый адрес компонента 0x8000a000

Недействительный CID 0x00000000

ROMTABLE [0x28] = 0xb003

Базовый адрес компонента 0x8000b000

Недействительный CID 0x00000000

ROMTABLE [0x2c] = 0xc003

Базовый адрес компонента 0x8000c000

Недействительный CID 0x00000000

ROMTABLE [0x30] = 0xd003

Базовый адрес компонента 0x8000d000

Недействительный CID 0x00000000

ROMTABLE [0x34] = 0xe003

Базовый адрес компонента 0x8000e000

Недействительный CID 0x00000000

ROMTABLE [0x38] = 0xf003

Базовый адрес компонента 0x8000f000

Недействительный CID 0x00000000

ROMTABLE [0x3c] = 0x0

Конец таблицы ПЗУ

Первое, что бросается в глаза, это то, что это Cortex R4, с этой дополнительной информацией мы можем создать цель в файле конфигурации, которая должна предоставить доступ к MEM-AP для отладки.Это можно сделать, добавив следующую строку:

1

цель создать $ _TARGETNAME.1 cortex_r4 -endian $ _ENDIAN -dap $ _CHIPNAME.dap

С помощью этой дополнительной строки мы можем попытаться остановить цель с помощью команды halt и прочитать память с помощью mdw из командной строки OpenOCD:

1

2

3

4

5

6

7

8

9

> остановка

MPIDR не в многопроцессорном формате

цель остановлена в состоянии Thumb из-за запроса отладки, текущий режим: Supervisor

cpsr: 0x80000133 ПК: 0x0001abfc

D-Cache: отключен, I-Cache: отключен

> mdw 0x800000000 10

Транзакция DAP остановлена (WAIT) - замедляется

0x800000000: eafffffe ea000005 ea000006 ea000006 ea00000b e320f000 ea00000e eafffffe

0x800000020: ea0000e3 eafffffe

Здесь мы тестируем пошаговое выполнение работающей прошивки:

1

2

3

4

5

6

7

8

9

10

> остановка

MPIDR не в многопроцессорном формате

цель остановлена в состоянии ARM из-за отладочного запроса, текущий режим: Supervisor

cpsr: 0x80000113 ПК: 0x0000e10c

D-Cache: отключен, I-Cache: отключен

> шаг

цель остановлена в состоянии ARM из-за точки останова, текущий режим: Supervisor

cpsr: 0x80000113 ПК: 0x0000e110

D-Cache: отключен, I-Cache: отключен

Успех! Кажется, он работает, и мы можем выполнить пошаговую прошивку.Затем давайте воспользуемся этой возможностью для получения дампов ОЗУ, на этой странице представлен обзор модели памяти, поэтому мы можем использовать ее в качестве справки. Память можно выгрузить в файл с помощью OpenOCD с помощью команды dump_image .

1

2

3

4

5

6

7

8

9

> остановка

MPIDR не в многопроцессорном формате

цель остановлена в состоянии ARM из-за отладочного запроса, текущий режим: Abort

cpsr: 0x200001d7 ПК: 0x00000048

D-Cache: отключен, I-Cache: отключен

Регистры ошибок данных DFSR: 00000008, DFAR: 9f7e3000

Регистры ошибок команд IFSR: 00000000, IFAR: 00000000

> dump_image SDRAM.bin 0x20000000 0xA0000000

> dump_image RAM.bin 0 0xFFFFFFF

Наконец, давайте возьмем эти дампы ОЗУ и загрузим их в GHIDRA, чтобы посмотреть, имеют ли они смысл:

Отлично, у нас есть внешние ссылки, и код инициализации выглядит довольно разумно. Также похоже, что есть какое-то меню отладки, которое представлено поверх UART, вероятно, это контакты 8/9 на нашей распиновке! Можно с уверенностью сказать, что это действительный дамп оперативной памяти, и на этом я закончу этот пост.

Заключение