Что такое регистр сдвига. Какие бывают виды регистров сдвига. Как работает регистр сдвига вправо и влево. Где применяются регистры сдвига в цифровой электронике. Каковы основные характеристики и функции регистров сдвига.

Что такое регистр сдвига и для чего он нужен

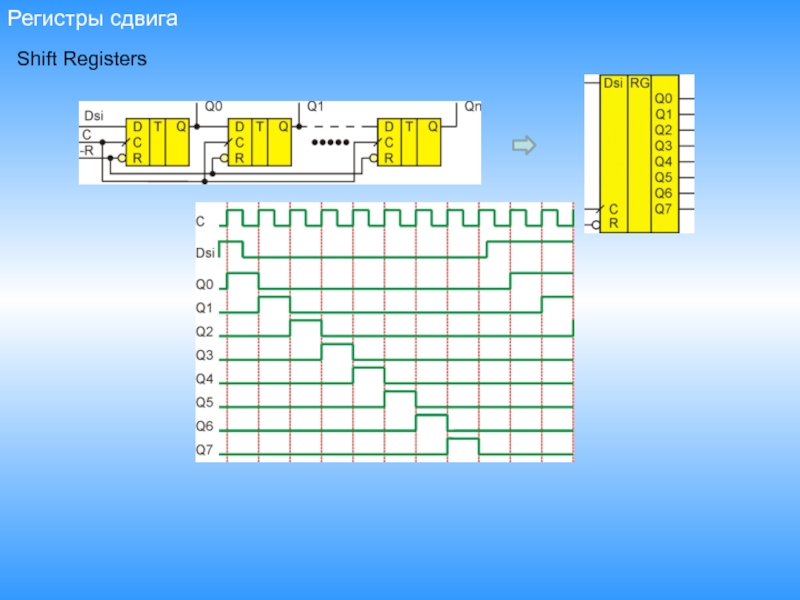

Регистр сдвига — это последовательное цифровое устройство, предназначенное для хранения и поразрядного сдвига двоичной информации. Он состоит из цепочки последовательно соединенных триггеров, в которых информация может сдвигаться в одном направлении (вправо или влево) под действием тактовых импульсов.

Основные функции регистра сдвига:

- Хранение многоразрядных двоичных чисел

- Преобразование последовательного кода в параллельный и наоборот

- Выполнение арифметических и логических операций

- Задержка цифровых сигналов на заданное число тактов

Виды регистров сдвига

По направлению сдвига информации регистры сдвига делятся на:

- Регистры сдвига вправо — информация сдвигается от старших разрядов к младшим

- Регистры сдвига влево — информация сдвигается от младших разрядов к старшим

- Реверсивные регистры — могут сдвигать информацию как вправо, так и влево

По способу ввода/вывода информации выделяют:

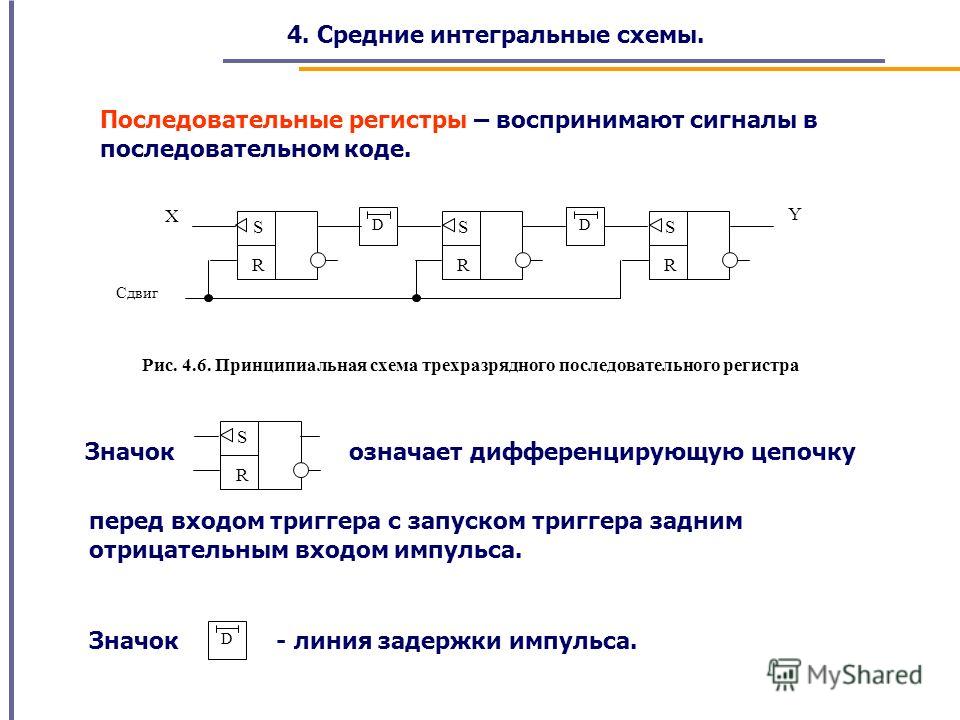

- Последовательные регистры — информация вводится и выводится последовательно, бит за битом

- Параллельные регистры — информация вводится и выводится параллельно, всеми разрядами одновременно

- Последовательно-параллельные регистры — комбинируют оба способа ввода/вывода

Принцип работы регистра сдвига вправо

Регистр сдвига вправо состоит из цепочки D-триггеров, в которой выход каждого триггера соединен со входом D следующего. Информация вводится в крайний левый триггер, а выводится с выхода крайнего правого.

При подаче тактового импульса происходит следующее:

- Содержимое каждого триггера передается в следующий справа триггер

- Информация из крайнего правого триггера выводится наружу

- В крайний левый триггер вводится новый бит информации

Таким образом, за один такт происходит сдвиг всей информации на один разряд вправо.

Принцип работы регистра сдвига влево

Регистр сдвига влево устроен аналогично, но информация в нем движется в противоположном направлении — от младших разрядов к старшим. При подаче тактового импульса:

- Содержимое каждого триггера передается в следующий слева триггер

- Информация из крайнего левого триггера выводится наружу

- В крайний правый триггер вводится новый бит информации

За один такт вся информация сдвигается на один разряд влево.

Применение регистров сдвига в цифровой электронике

Регистры сдвига широко используются в различных цифровых устройствах и системах:

- В арифметико-логических устройствах для выполнения операций умножения и деления

- В устройствах ввода-вывода для преобразования последовательного кода в параллельный и обратно

- В генераторах псевдослучайных чисел

- В схемах задержки цифровых сигналов

- В кодерах и декодерах для выполнения операций шифрования

Основные характеристики регистров сдвига

Ключевые параметры регистров сдвига:

- Разрядность — количество триггеров, определяющее максимальную длину хранимого двоичного числа

- Быстродействие — максимальная частота тактовых импульсов

- Направление сдвига — вправо, влево или реверсивное

- Способ ввода/вывода — последовательный, параллельный или комбинированный

- Наличие дополнительных функций — сброс, установка, инверсия и т.д.

Схемотехническая реализация регистров сдвига

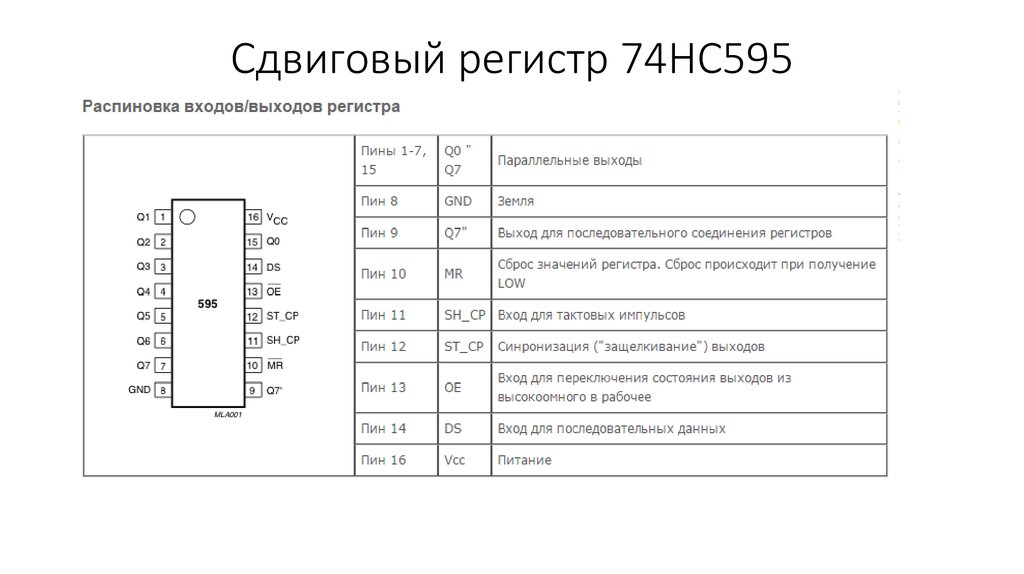

Простейший регистр сдвига может быть построен на основе D-триггеров. Однако в современной цифровой технике чаще используются готовые интегральные микросхемы регистров сдвига, например:

- 74164 — 8-разрядный регистр сдвига с последовательным вводом и параллельным выводом

- 74165 — 8-разрядный регистр сдвига с параллельным вводом и последовательным выводом

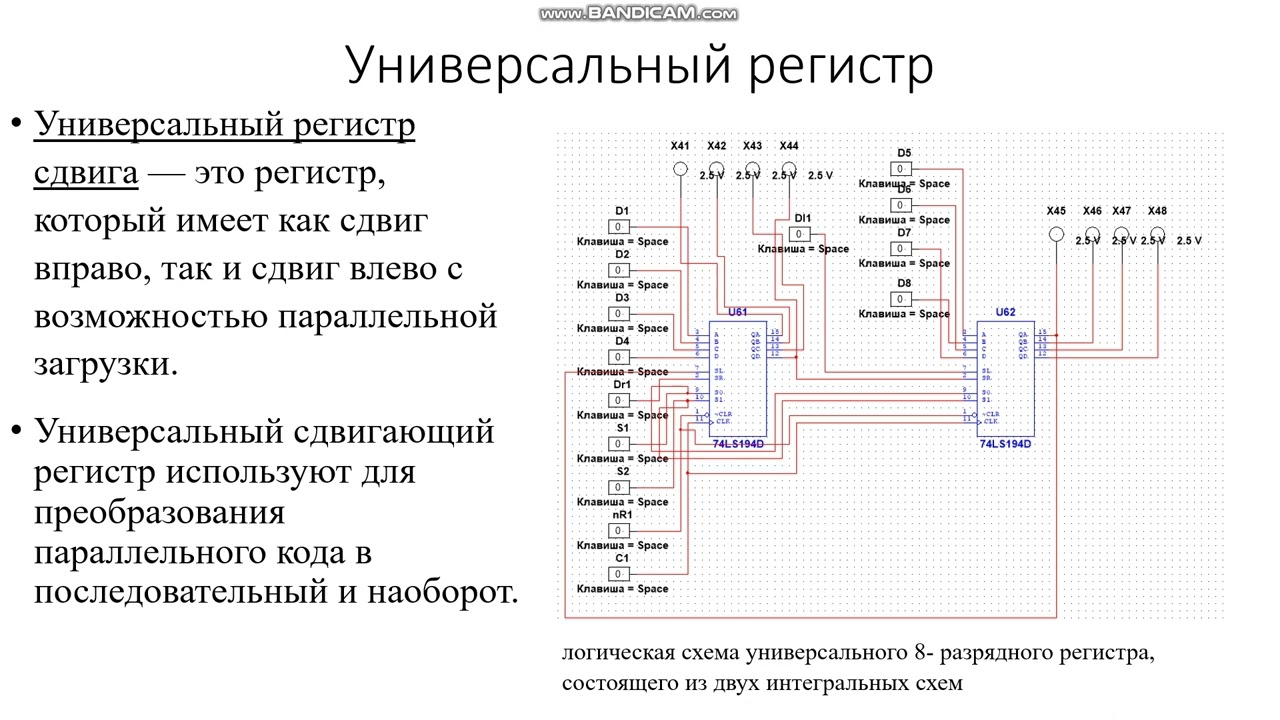

- 74194 — 4-разрядный универсальный реверсивный регистр сдвига

- 74299 — 8-разрядный универсальный регистр сдвига с трехстабильным выходом

Данные микросхемы позволяют легко создавать регистры сдвига с требуемыми параметрами и функциональностью.

Преимущества использования регистров сдвига

Применение регистров сдвига в цифровых схемах дает ряд важных преимуществ:

- Упрощение аппаратной реализации операций умножения и деления

- Возможность преобразования формата данных (последовательный/параллельный)

- Организация временной задержки сигналов с точностью до такта

- Создание генераторов псевдослучайных последовательностей

- Реализация различных алгоритмов шифрования данных

Ограничения регистров сдвига

При использовании регистров сдвига следует учитывать некоторые их ограничения:

- Ограниченная разрядность, определяемая количеством триггеров

- Потеря крайних битов при сдвиге за пределы регистра

- Необходимость внешней синхронизации тактовыми импульсами

- Относительно низкое быстродействие по сравнению с комбинационными схемами

- Усложнение схемы при добавлении дополнительных функций

Перспективы развития регистров сдвига

Основные направления совершенствования регистров сдвига:

- Увеличение разрядности для работы с длинными двоичными последовательностями

- Повышение рабочей частоты для увеличения быстродействия

- Добавление новых функциональных возможностей

- Снижение энергопотребления

- Уменьшение размеров кристалла для повышения степени интеграции

Дальнейшее развитие регистров сдвига позволит расширить области их применения в современных цифровых системах.

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

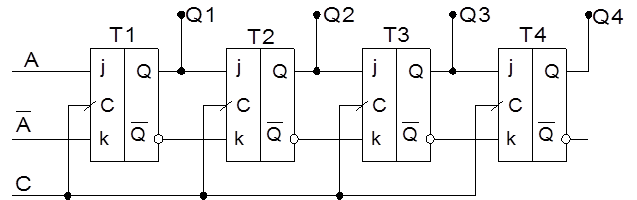

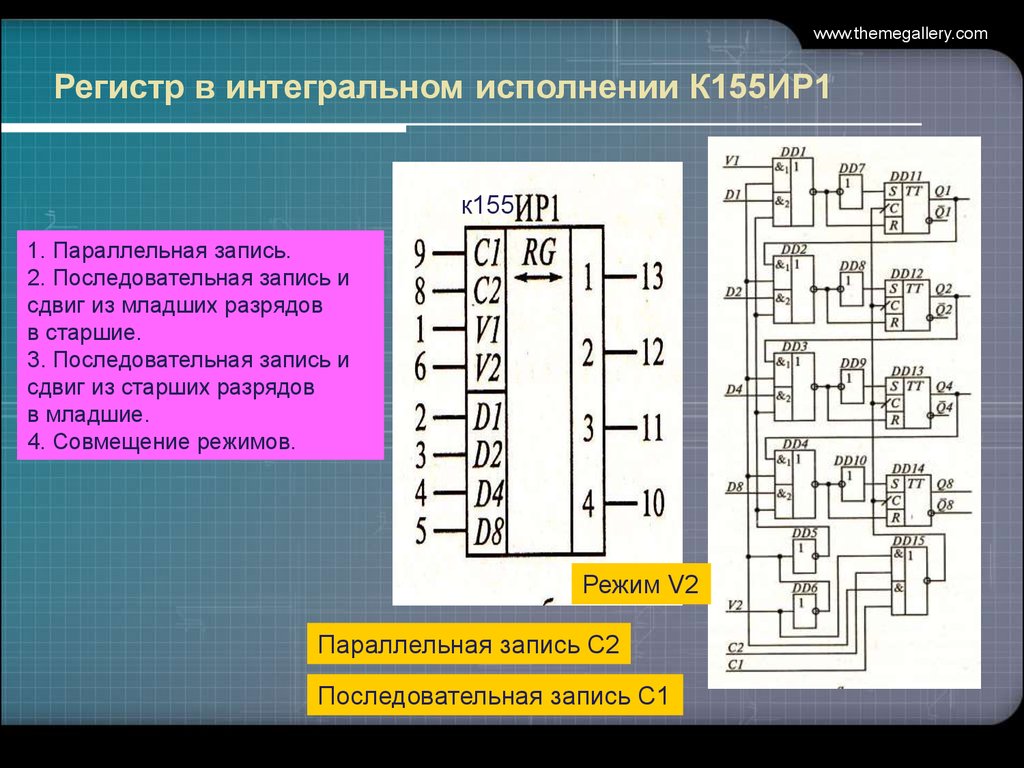

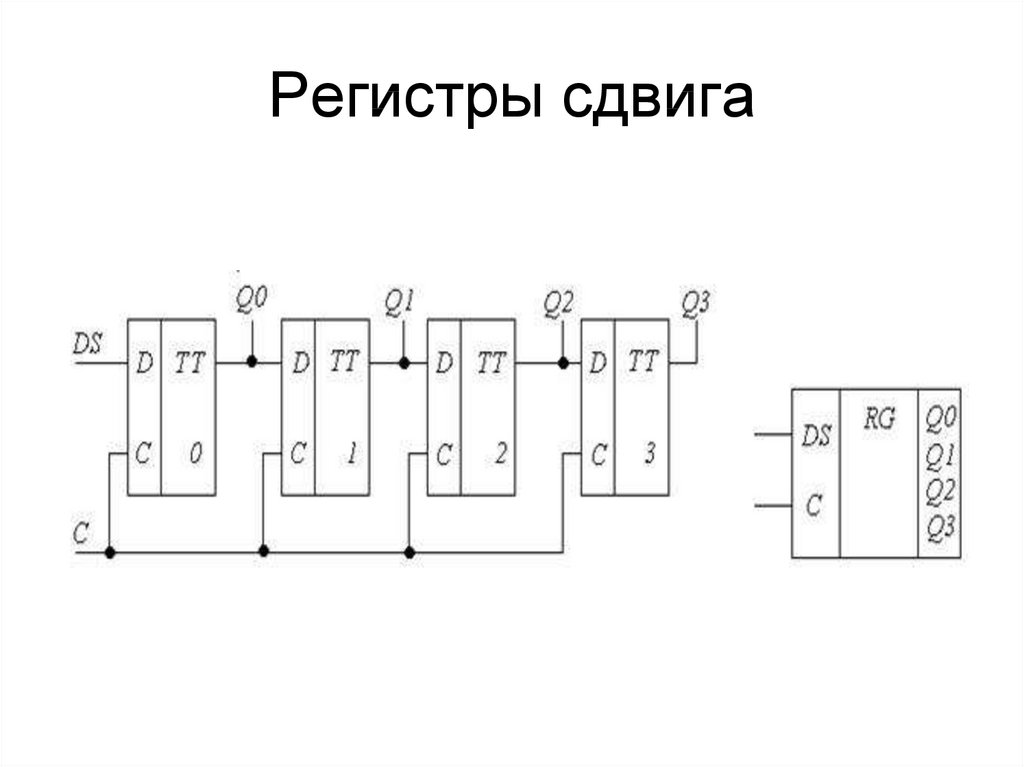

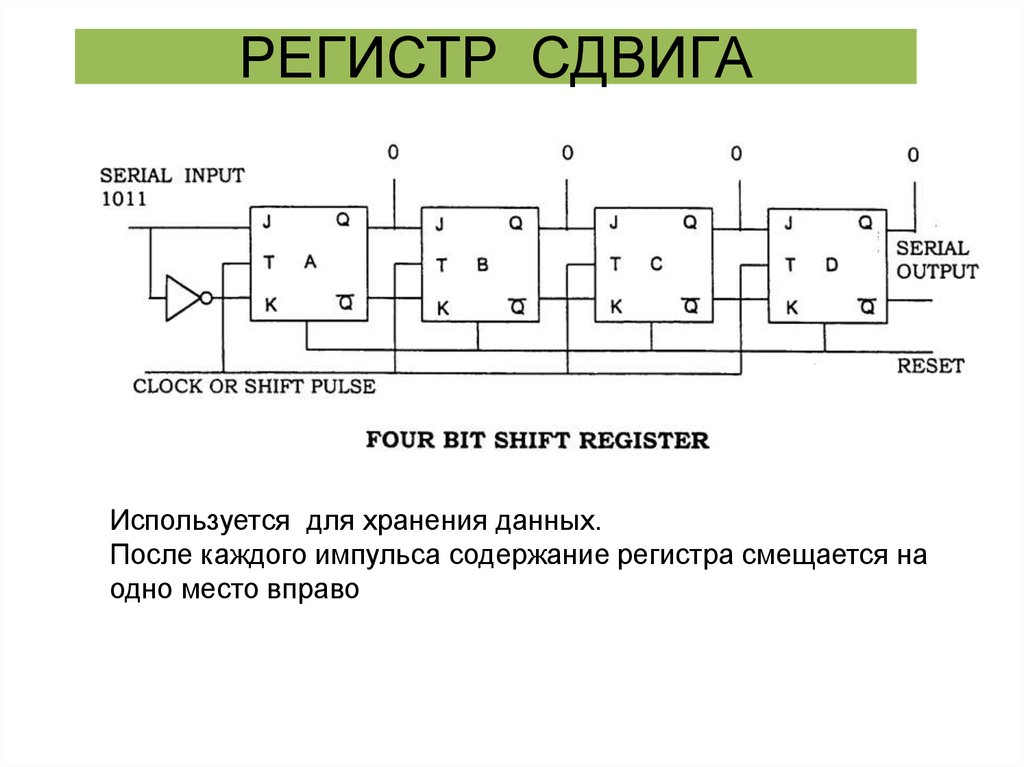

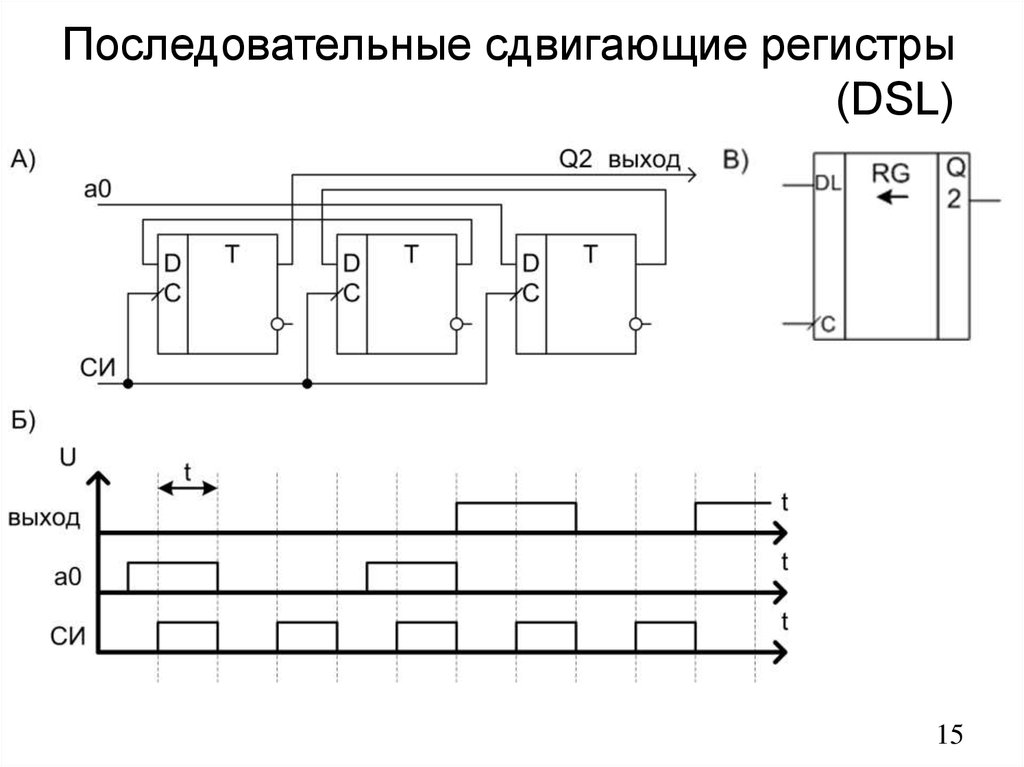

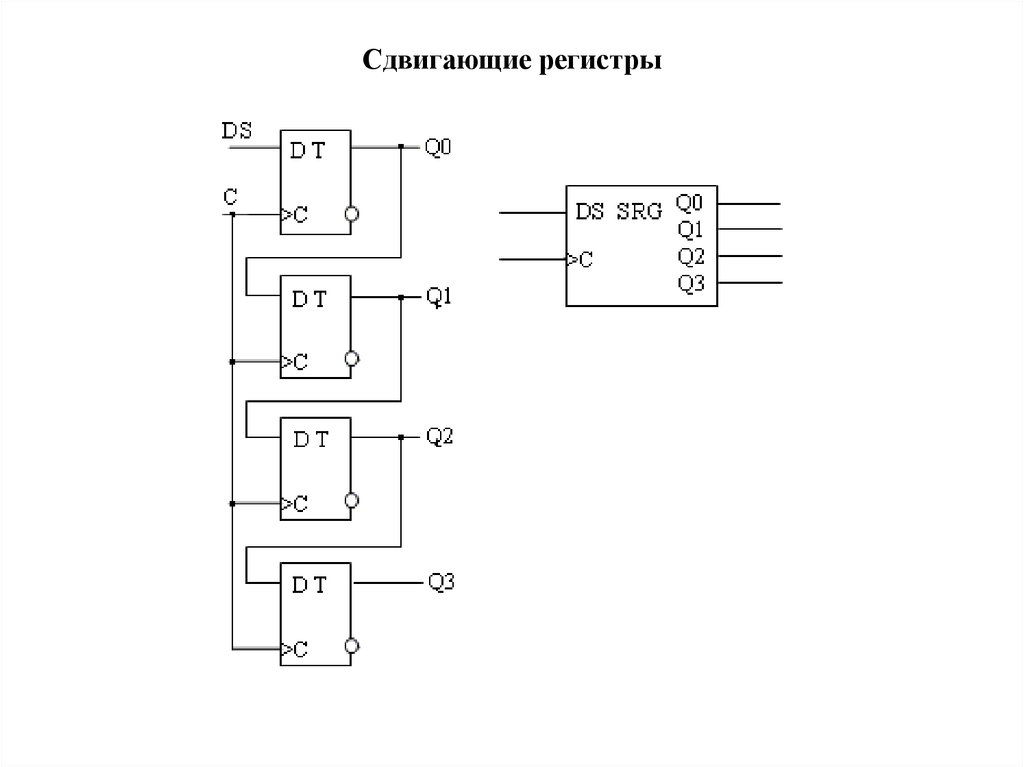

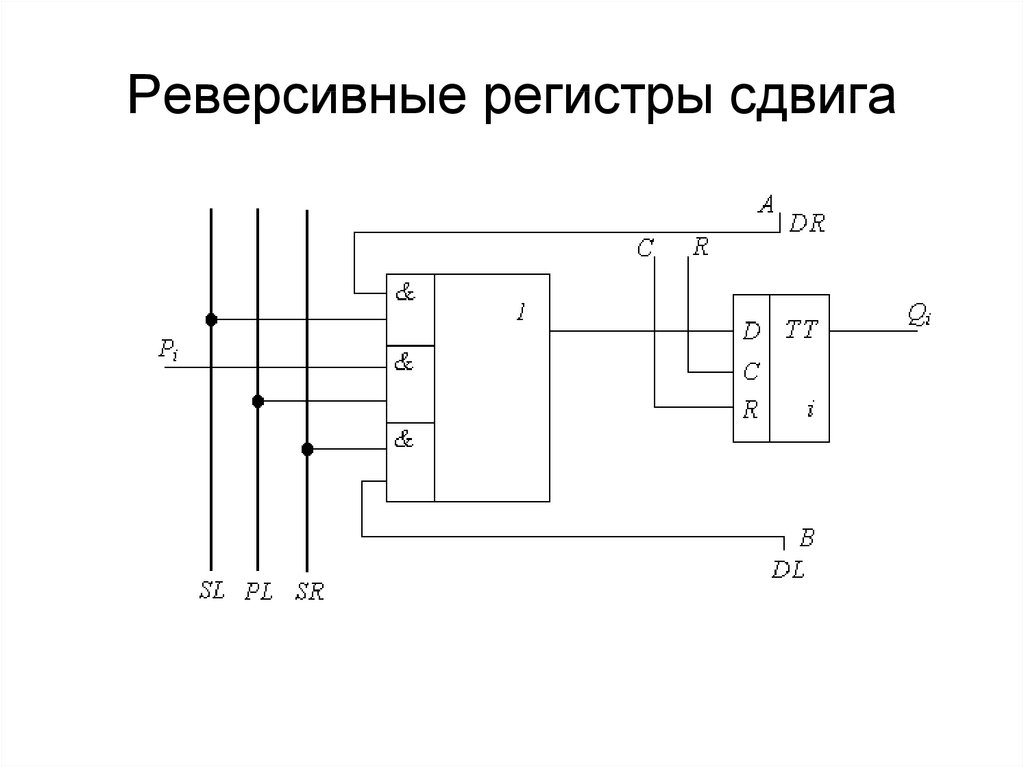

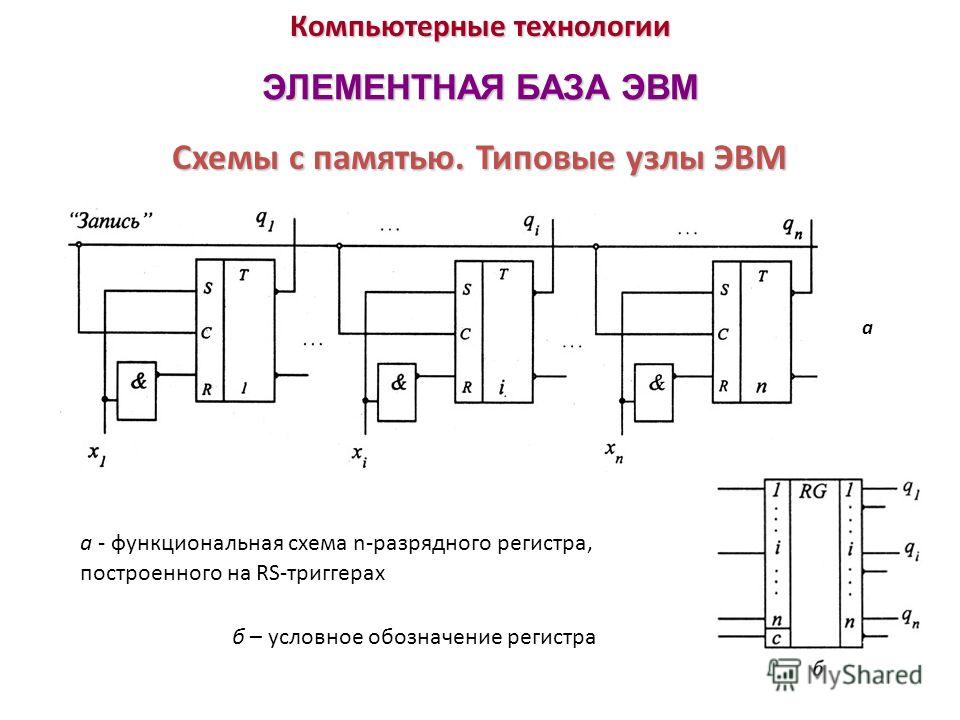

Рисунок 54 Функциональная схема а) и УГО б) параллельного регистра. Перед записью информации все триггеры регистра устанавливают в состояние «0» путём подачи импульса «1» на их R-входы. Записываемая информация подаётся на входы DI1…DI4. Для записи информации подаётся импульс «Зп», открывающий входные элементы «И». Код входного числа записывается в регистр. По окончании импульса «Зп» элементы D1…D4 закрываются, а информация, записанная в регистр, сохраняется несмотря на то, что входная информация может изменяться. Для считывания информации подают сигнал «1» на вход «Чт». По этому сигналу на выходные шины регистра на время действия сигнала передаётся код числа, записанный в регистр. По окончанию операции чтения выходные ключи закрываются, а информация, записанная в регистр, сохраняется. То есть возможно многократное считывание информации. Условное графическое обозначение параллельного регистра приведено на рисунке 54,б. 5.2.2 Регистры сдвига Регистры сдвига представляют собой цепочку последовательно включённых D-триггеров или RS- и JK-триггеров, включённых в режим D-триггера. Схема 4-разрядного регистра сдвига приведена на рисунке 55. Схема работает следующим образом. Благодаря тому, что выход предыдущего разряда соединён со входом «D» последующего, каждый тактовый импульс устанавливает последующий триггер в состояние, в котором до этого находился предыдущий. Так осуществляется сдвиг информации вправо. Рисунок 54 4-разрядный регистр сдвига Вход «D» первого триггера служит для приёма в регистр входной информации DI в виде последовательного кода. С каждым тактовым импульсом на этот вход должен подаваться код нового разряда входной информации. Запись параллельного кода информации может быть произведена через нетактируемые установочные входы триггеров (на рисунке 55 не показаны). С выхода «Q4» последнего триггера снимается последовательный выходной код. Код на этом выходе регистра появляется с задержкой относительно входного последовательного кода на число периодов тактовых импульсов, равное числу разрядов регистра. Параллельный выходной код можно снять с выходов Q1…Q4 всех триггеров регистра сдвига, снабдив их выходными ключами, подобными выходным ключам параллельного регистра (См. рисунок 54,а). 5.2.3 Реверсивные регистры сдвига Реверсивные регистры сдвига обеспечивают возможность сдвига информации как вправо, так и влево. Они имеют специальный вход управления направлением сдвига. Поскольку транзисторы и логические элементы способны передавать сигналы только в одном направлении с входа на выход (слева направо), то, для сдвига информации влево, необходимо информацию с выхода последующих триггеров по специально созданным цепям подавать на входы предыдущих триггеров и записывать их следующим тактовым сигналом. Это эквивалентно сдвигу информации влево. Фрагмент функциональной схемы реверсивного регистра сдвига приведён на рисунке 56. Рисунок 56 Реверсивный регистр сдвига Если сигнал на входе направления сдвига N=1, то потенциал на входе «Di» триггера определяется выходом Q триггера, стоящего слева от него. Если N=0, то выходом триггера, стоящего справа. Таким образом, при N=1 тактовые импульсы производят сдвиг информации вправо, а при N=0 –— сдвиг информации влево. 5.2.4. Интегральные микросхемы регистров (примеры) Интегральные микросхемы регистров, как и другие микросхемы, имеют дополнительные управляющие входы, расширяющие их функциональные возможности и делающие их универсальными. В качестве примера рассмотрим микросхему К155ИР13. К155ИР13 — это 8-разрядный реверсивный регистр сдвига с возможностью параллельной записи информации. УГО этого регистра приведено на рисунке 57. Изучив назначение входных и выходных сигналов, легко усвоить функциональные возможности микросхемы и особенности её применения. Рисунок 57 Реверсивный регистр сдвига и записи информации К155ИР13 Буферный регистр КР580ИР82, входящий в состав МП-комплекта КР580, построен на D-триггерах и предназначен для записи и сохранения 8-разрядных данных в течение заданного промежутка времени. Этот регистр называют также регистром-защёлкой. Например, в МП-системах на МР КР580 он используется сохранения в течение машинного цикла байта состояния, а на МП1810 — адреса, поступающего по мультиплексированной шине адреса-данных. Его функциональная схема и условное графическое обозначение приведены на рисунке 58,а,б. Рисунок 58 Буферный регистр КР580ИР82: а) — функциональная схема, б) — УГО Регистр состоит из 8-и D-триггеров, тактируемых фронтом, и 8-и элементов с тремя выходными состояниями. Схема управления построена на двух элементах ИЛИ-НЕ. Если на вход поступит разрешающий сигнал низкого уровня, а на вход STB — сигнал высокого уровня, то информация с входов передаётся на выходы. переводит выводы DO0–DO7 в 3-е (высокоомное) состояние. Таким образом, микросхема может работать в трёх режимах: — =0, STB=1 — режим шинного формирователя; — =0, STB=0 — режим защёлки: — =1 — 3-е состояние (режим отключения от нагрузки). Многорежимный буферный регистр (МБР) К589ИР12 является универсальным 8-и разрядным регистром, состоящим из D-триггеров и выходных буферных схем с 3-мя устойчивыми состояниями. МБР имеет также встроенную селективную логику: «Схема управления режимами» и отдельный D-триггер для формирования запроса на прерывание центрального процессора. МБР предназначен для использования в качестве портов ввода информации в МП от внешних устройств, или портов вывода информации из МП во внешние устройства. Функциональная схема МБР и его УГО приведены на рисунке 59,а,б. Рисунок 59 МБР К589ИР12: а) Функциональная схема, б) УГО. Схема управления режимами (D1, D2, D4) в зависимости от сочетания управляющих сигналов C, ВР, обеспечивает: — Запись входной информации от внешнего устройства по сигналам , или выходной информации по сигналам ; |

Сдвиг вправо и Сдвиг влево Регистры со схемой

Содержание

Введение

Группа триггеров, которая используется для хранения или защиты двоичных чисел или двоичных данных, называется регистром. Другими словами, регистр — это такая группа (набор) элементов памяти, в которой обычные элементы памяти или триггеры работают вместе как единое целое. Функция регистра состоит только в том, чтобы хранить двоичное слово. Другими словами, регистр — это устройство, которое выполняет задачу хранения информации, а для его изготовления используются триггеры. Поскольку каждый триггер, существующий в регистре, может хранить только один двоичный бит (0 или 1) информации за раз, поэтому для хранения «n» битов в регистре требуется «n» триггеров (т. е. количество битов, которые желательно хранить в регистре, на нем используется такое же количество триггеров в соответствии с количеством битов). Например, если требуется сохранить в регистре 8-битное слово или двоичное число, в этом регистре необходимо использовать всего 8 триггеров. Поскольку триггер может хранить только один бит за раз, общее количество битов в регистре или диапазоне битов называется емкостью памяти этого регистра.

Поскольку каждый триггер, существующий в регистре, может хранить только один двоичный бит (0 или 1) информации за раз, поэтому для хранения «n» битов в регистре требуется «n» триггеров (т. е. количество битов, которые желательно хранить в регистре, на нем используется такое же количество триггеров в соответствии с количеством битов). Например, если требуется сохранить в регистре 8-битное слово или двоичное число, в этом регистре необходимо использовать всего 8 триггеров. Поскольку триггер может хранить только один бит за раз, общее количество битов в регистре или диапазоне битов называется емкостью памяти этого регистра.

Сдвиговый регистр представляет собой группу триггеров, в которой все триггеры соединены между собой таким образом, что двоичное число может сдвигаться как внутри, так и снаружи этих триггеров. Другими словами, сдвиговым регистром называется группа соединенных между собой триггеров, по которым двоичное число или двоичная информация могут сдвигаться как внутрь, так и наружу этих триггеров. Сдвиговый регистр также является запоминающим устройством, в котором хранятся двоичные данные или цифровая информация. Это устройство сконструировано таким образом, что хранящиеся в нем биты могут сдвигаться или передаваться с одного триггера на другой (т. е. регистры сдвига используются для хранения и сдвига данных (0 и 1) в цифровой системе). Таким образом, сдвиговый регистр — это своего рода цифровая схема, которая выполняет две основные функции: хранение данных и сдвиг данных. Помните, что сдвиговые регистры — это форма последовательных логических схем, которые широко используются.

Сдвиговый регистр также является запоминающим устройством, в котором хранятся двоичные данные или цифровая информация. Это устройство сконструировано таким образом, что хранящиеся в нем биты могут сдвигаться или передаваться с одного триггера на другой (т. е. регистры сдвига используются для хранения и сдвига данных (0 и 1) в цифровой системе). Таким образом, сдвиговый регистр — это своего рода цифровая схема, которая выполняет две основные функции: хранение данных и сдвиг данных. Помните, что сдвиговые регистры — это форма последовательных логических схем, которые широко используются.

Емкость регистра или его емкость для хранения данных относится к числу битов цифровых данных (0 и 1), которые он может хранить или сохранять внутри себя. Поскольку каждый каскад триггера, присутствующий в сдвиговом регистре, отражает емкость хранения бита (то есть каждый триггер из всех триггеров, существующих в регистре, может хранить только один бит), следовательно, количество каскадов (флип-флоп -flops) в регистре представляет его общую емкость хранения. Однако способность регистра перемещать данные с одного триггера на другой триггер или с одной ступени на другую, существующую в нем, или способность регистра позволять вводить данные в него или позволять извлекать данные из него , зависит от использования тактовых импульсов.

Однако способность регистра перемещать данные с одного триггера на другой триггер или с одной ступени на другую, существующую в нем, или способность регистра позволять вводить данные в него или позволять извлекать данные из него , зависит от использования тактовых импульсов.

Короче говоря, сдвиговый регистр состоит из двоичных запоминающих элементов (т. вместе таким образом, что выход одного триггера является входом для другого триггера, этот процесс называется каскадированием триггеров). Однако следует помнить, что все регистры хранения, присутствующие в цифровой системе, могут работать вместе с помощью входного тактового импульса или импульса сдвига. Следовательно, когда применяется сдвиговый импульс, данные, присутствующие в сдвиговом регистре, могут смещаться только на однобитовую позицию за раз последовательно вправо или влево. В результате этой функции сдвига или перемещения только одного бита данных за раз регистры сдвига широко используются для выполнения таких функций, как счет, деление частоты или арифметические операции и т. д.

д.

Механизм сдвига в сдвиговом регистре также можно понять с помощью экрана дисплея калькулятора, на котором, когда мы нажимаем цифры на клавиатуре, число, присутствующее на дисплее калькулятора, продолжает сдвигаться влево, а первые цифры на дисплее также не исчезают. (поскольку регистр сдвига в калькуляторе также работает как память, так и элемент сдвига). Например, чтобы ввести число 268 в калькулятор, сначала кратковременно нажимают клавишу с цифрой 2, а затем отпускают. Таким образом, цифра 2 появится в правой части дисплея калькулятора. После этого нажимается и затем отпускается клавиша номер 6. Как только нажата 6, цифра 2 (которая была в основном ближе к правому краю экрана) смещается на одну позицию влево, и ее место занимает цифра 6. Таким образом, на экране калькулятора отображается цифра 26. Наконец, мы должны нажать и отпустить клавишу с цифрой 8 на клавиатуре калькулятора. В результате цифры 2 и 6 сдвигаются дальше на одну позицию влево и, таким образом, цифра 6 заменяется на 8. Таким образом, на экране калькулятора начинает отображаться число 268. В этом примере проявились обе особенности сдвиговых регистров, т. е. временная память и сдвиг, благодаря которым сдвиговый регистр приобрел статус чрезвычайно бесценного устройства в многочисленных цифровых системах.

Таким образом, на экране калькулятора начинает отображаться число 268. В этом примере проявились обе особенности сдвиговых регистров, т. е. временная память и сдвиг, благодаря которым сдвиговый регистр приобрел статус чрезвычайно бесценного устройства в многочисленных цифровых системах.

На рис. 7.1 показано использование сдвигового регистра в цифровой системе (калькуляторе или компьютере), где сдвиговый регистр устанавливается до декодера и после кодера. Здесь регистр, установленный после кодера, временно хранит информацию для блока обработки, а регистр, закрепленный между блоком обработки и декодером, временно сохраняет информацию, передаваемую между ними. Следует помнить, что сдвиговый регистр можно применять и в ряде других мест в цифровой системе.

Рисунок 7.1 – цифровая система с использованием регистров сдвига

Регистры сдвига вправо и сдвига влево

импульс», данные, хранящиеся в регистре, сдвигаются последовательно справа налево. Таким образом, последовательные сдвиговые регистры бывают следующих двух типов в зависимости от их работы.

Таким образом, последовательные сдвиговые регистры бывают следующих двух типов в зависимости от их работы.

(1). Сдвиг правого регистра

(2). Сдвиг в левом регистре

Регистры сдвига вправо

Регистры сдвига, в которых ввод вводится с левой стороны, а числа, уже присутствующие в нем, вытекают или выделяются с правой стороны, называются регистрами сдвига вправо. Другими словами, регистры, которые переносят или сдвигают входные данные вправо, называются регистрами сдвига вправо. На рисунке 7.2 показан регистр сдвига вправо, который содержит четыре триггера (это означает, что этот регистр может хранить только 4-битное двоичное число). Согласно этому рисунку, каждый выход Q продолжает устанавливать вход D каждого следующего триггера. Когда приходит нарастающий тактовый фронт, сохраненные биты сдвигаются вправо в соответствии с принципом «одна битовая позиция на тактовый импульс». Например, Д в значении равно 1 (т. е. D в = 1) и Q = 0000, то при наступлении первого положительного фронта тактового сигнала (т. е. тактового импульса) левый триггер стремится установиться. В такой ситуации все входные данные, кроме ввода с левой стороны, равны 0. Таким образом, в результате установки триггера D 3 слово, хранящееся в регистре, выглядит следующим образом:

е. тактового импульса) левый триггер стремится установиться. В такой ситуации все входные данные, кроме ввода с левой стороны, равны 0. Таким образом, в результате установки триггера D 3 слово, хранящееся в регистре, выглядит следующим образом:

Q = 1 0 0 0

С появлением этого слова значения D 2 и D 3 получаются 1 (т.е. D 2 = D 3 = 1 с), потому что выход Q 3 стремится установить выход D 3 (см. рисунок). Точно так же следующие результаты с появлением второго нарастающего фронта тактового сигнала.

Q = 1 1 0 0

Аналогично, следующие изменения происходят в результате 3 -го -го тактового импульса и 4-го -го -го тактового импульса. Рис. 7.2 Этот регистр сдвига также содержит четыре элемента двоичной памяти (т.е. четыре триггера), и в нем предварительно хранится число 1011. Двоичное число 0110 существует в последовательном порту за пределами этого сдвигового регистра, и его желательно сохранить в этом регистре. Поскольку к регистру применяются тактовые импульсы или сдвиговые импульсы, то в соответствии с принципом однобитовой позиции на импульс класса сохраненные цифры в сдвиговом регистре исчезают после выхода одна за другой с правого конца. И в то же время внешние цифры, присутствующие слева, продолжают смещаться в регистр один за другим.

Поскольку к регистру применяются тактовые импульсы или сдвиговые импульсы, то в соответствии с принципом однобитовой позиции на импульс класса сохраненные цифры в сдвиговом регистре исчезают после выхода одна за другой с правого конца. И в то же время внешние цифры, присутствующие слева, продолжают смещаться в регистр один за другим.

Рисунок 7.3 – Работа сдвигового регистра

На рисунке (А) изображено начальное состояние сдвигового регистра. Согласно рисунку (Б), после появления первого тактового импульса, уже хранящиеся в регистре числа, как на одноразрядную позицию сдвигаются вправо со своего места. Таким образом, самый правый бит (1) в сдвиговом регистре сдвигает или переносит из регистра, а правый первый бит (0) внешнего числа перемещается в крайнюю левую позицию сдвигового регистра (помните, что в результате каждого импульс сдвига, все входы, присутствующие в сдвиговом регистре, сдвигаются на одну позицию вправо. Таким образом, пустое пространство, которое создается слева от регистра, вставляется в него внешний бит).

Аналогично, после прихода второго импульса сдвига (как показано на рисунке C), самый правый бит сдвигового регистра сдвигается из регистра. В то время как самый правый следующий бит, находящийся вне регистра, входит в самое левое пустое место регистра. Таким образом, подобная ситуация повторяется с приходом третьего и четвертого сдвиговых импульсов (как видно из рисунков D и E). Следовательно, после четырех импульсов сдвига предварительно сохраненное в регистре число исчезает после полного сдвига из регистра, в то время как внешнее число в левом конце регистра полностью смещается извне и сохраняется в регистре после четырех импульсов сдвига. Он остается в нем до тех пор, пока на вход регистра не поступит какое-либо другое внешнее число после поступления нового сдвигового импульса.

На рис. 7.4 показан правый регистр последовательного сдвига нагрузки типа 74194 – IC. Поскольку этот регистр 74194 — IC является универсальным регистром сдвига, поэтому, когда он используется в качестве регистра сдвига вправо, его регулятор режима (S 0 , S 1 ) должен быть в положении сдвига вправо в соответствии с рисунком (т. е. S 0 должен быть на 1, тогда как S 1 на 0). Здесь сдвиг вправо фактически означает сдвиг от Q A к Q D . вот этот регистр сдвигает данные вправо и извлекает данные из Q D исчезает или теряется.

е. S 0 должен быть на 1, тогда как S 1 на 0). Здесь сдвиг вправо фактически означает сдвиг от Q A к Q D . вот этот регистр сдвигает данные вправо и извлекает данные из Q D исчезает или теряется.

Рисунок 7.4 – 74149 – ИС, подключенная как 4-битный последовательный сдвиг загрузки – правый регистр

Регистры сдвига влево регистр опустить/удалить с левой стороны, называются регистрами сдвига влево. Другими словами, регистры, которые сдвигают входные данные влево, называются регистрами сдвига влево.

На рис. 7.5 показан регистр сдвига влево, который состоит из четырех триггеров D-типа. По рисунку Д в устанавливает самый правый триггер, Q 0 устанавливает второй триггер, Q 1 устанавливает третий триггер и Q 2 устанавливает четвертый или последний триггер. Помните, что каждый раз, когда этот регистр получает следующий положительный тактовый импульс, его сохраненные биты сдвигаются влево в соответствии с принципом одной позиции / тактового импульса. Например, если состояние D в = 1 и Q = 0000 выходит из регистра, в такой ситуации самый правый триггер (Q 0 ) устанавливается с приходом первого тактового импульса (или нарастающим тактовым фронтом). ), в результате значения всех входных данных равны 0, кроме 1, существующей на правом конце. Другими словами, хранимое слово в регистре выглядит следующим образом;

Например, если состояние D в = 1 и Q = 0000 выходит из регистра, в такой ситуации самый правый триггер (Q 0 ) устанавливается с приходом первого тактового импульса (или нарастающим тактовым фронтом). ), в результате значения всех входных данных равны 0, кроме 1, существующей на правом конце. Другими словами, хранимое слово в регистре выглядит следующим образом;

Q = 0 0 0 0

Так как выход первого триггера (Q 0 ), расположенный справа, является входом второго триггера (т.е. D 1 = D 0 ), таким образом D Значение 1 равно 1 или равно значению D 0 . Таким образом, в результате столкновения очередного тактового импульса триггер Q 1 устанавливается и сохраняемое в регистре число оказывается следующим;

Q = 0 0 1 1

Аналогично, в результате третьего и четвертого положительных тактовых импульсов в регистре происходят следующие изменения;

Q = 0 1 1 1

Q = 1 1 1 1

Аналогично, после четырех импульсов сдвига уже существующее число в регистре полностью выбивается из регистра и теряется или исчезает. А внешний номер в правом конце регистра полностью сдвигается и сохраняется в регистре после четырех импульсов сдвига. Он остается в регистре до тех пор, пока значение D в равно 1 (т.е. D в = 1) или пока не происходит изменение в D в .

А внешний номер в правом конце регистра полностью сдвигается и сохраняется в регистре после четырех импульсов сдвига. Он остается в регистре до тех пор, пока значение D в равно 1 (т.е. D в = 1) или пока не происходит изменение в D в .

Рисунок 7.5 – сдвиг – левый регистр

Предположим, что значение D в теперь изменено на 0 (т. е. D в = 0). Таким образом, в такой ситуации непрерывные тактовые импульсы вызывают следующие изменения в регистре;

Q = 1 1 1 0

Q = 1 1 0 0

Q = 1 0 0 0

Q = 0 0 0 0

Следует помнить, что пока двоичное значение D в равно 0 (т. е. D в = 0) в сохраненных номерах регистров не происходит никаких изменений даже при наличии устойчивых тактовых импульсов.

Функция сдвига левого регистра была усовершенствована с помощью ее простого проявления, см. рис. 7.6. этот регистр состоит из четырех двоичных запоминающих элементов и в нем предварительно хранится двоичное число 0000. Это можно увидеть на рисунке «А» через его примитивное состояние. Принимая во внимание, что двоичное число 1111 желательно хранить в регистре. При поступлении первого тактового импульса все биты предварительно запомненных чисел в регистре сдвигаются влево в соответствии с однобитовой позицией. Таким образом, один бит выходит из левого конца регистра и теряется. И самый правый бит из внешних битов, присутствующих в правой части регистра, сдвигается внутрь регистра, как показано на рисунке B.

Это можно увидеть на рисунке «А» через его примитивное состояние. Принимая во внимание, что двоичное число 1111 желательно хранить в регистре. При поступлении первого тактового импульса все биты предварительно запомненных чисел в регистре сдвигаются влево в соответствии с однобитовой позицией. Таким образом, один бит выходит из левого конца регистра и теряется. И самый правый бит из внешних битов, присутствующих в правой части регистра, сдвигается внутрь регистра, как показано на рисунке B.

Рисунок 7.6 – операция сдвига регистра влево

Точно так же, при получении очередного тактового импульса, биты в левой части регистра покидают или выходят один за другим и освобождается место в правой части регистра, все внешние числовые биты вводятся и сохраняются в регистре поочередно. Следует помнить, что направление перемещения или сдвига внешних битов, поступивших в регистр, должно быть справа налево в соответствии с однобитовой позицией. Это показано стрелкой над рисунком. Поэтому этот тип регистра называется регистром сдвига влево.

Поэтому этот тип регистра называется регистром сдвига влево.

показан последовательный сдвиг нагрузки – левый регистр, доступный в 74194 – IC shape. Помните, что когда эта микросхема должна работать как регистр сдвига влево, ее регулятор режима должен находиться в положении сдвига влево в соответствии с рисунком (т. е. S 0 должен быть на 0, а S 1 на 1). . В таком типе регистра данные вторгаются с каждым тактовым импульсом через D или Q D и имеют тенденцию сдвигаться в сторону A или Q A .

Предыдущая тема: 555 Таймер как нестабильный и моностабильный мультивибратор со схемой

Следующая тема: Различные типы регистров сдвига в цифровой электронике

Для проектов, связанных с электроникой и программированием, посетите мой канал YouTube.

Мой канал на YouTube Ссылка

Digital Logic Design Engineering Электроника

CS302 — Цифровая логика и дизайн

Урок № 34

СМЕНА РЕГИСТРЫ

нужно хранить бинарные данные

обсуждалось ранее. В

цифровые схемы многоразрядные

данные

В

цифровые схемы многоразрядные

данные

должны быть временно сохраняется до тех пор, пока обработанный. Триггер способен хранить один двоичный бит

информации. Несколько битов данных хранится с использованием нескольких шлепанцы, у которых есть свои часы

ввод связаны вместе. Таким образом, по активация тактового сигнала несколько битов данных хранится.

Технически, регистр выполняет два основных функции. Он хранит данные и он движется или

смены данные. Сдвиг данных включает в себя сдвиг битов от одного триггера к другое в реестре

или перемещение данных в и из реестр. Смена работа с бинарными данными

нес вне, применяя часы сигналы. Несколько разных виды сменных работ может быть идентифицирован

. Другая смена операции описаны используя 4-битный сдвиг регистр.

1. Серийный номер Вход/Сдвиг вправо/Последовательный выход Операция

Данные смещен в правую руку направление по одному биту за раз с каждым переходом

часы

сигнал. Рисунок 34.1.

данные входят в смену

регистрировать последовательно с

левая сторона

и

Рисунок 34.1.

данные входят в смену

регистрировать последовательно с

левая сторона

и

после четыре часовых перехода 4-битный регистр имеет 4 бита данные. Данные сдвинуты серийно

один понемногу от правая сторона зарегистрируйтесь, если часы сигнализируют постоянно применяются

. Таким образом, после 8 тактовых сигналов 4-битные данные полностью выбыл из смены регистр.

Рисунок 34.1

Серийный Вход/Серийный правый/Серийный выход Операция

2. Серийный Вход/Сдвиг влево/Серийный выход Операция

Данные перешел в левую руку направление по одному биту за раз с каждым переходом часы

сигнал. Рисунок 34.2. данные входят в смену регистрировать последовательно с Правая сторона и

после четыре часовых перехода 4-битный регистр имеет 4 бита данные. Данные сдвинуты серийно

один

понемногу от

левая сторона

зарегистрируйтесь, если часы сигнализируют

постоянно

применяемый.

Таким образом после 8 часов сигнализирует 4-битные данные полностью выбыл из смены регистр.

Рисунок 34,2

Серийный номер Вход/Серийный левый/Серийный выход Операция

Последовательный сдвиговый регистр имеет обсуждалось ранее, реализовано с использованием JK шлепки.

Серийный номер регистры сдвига могут быть реализуется с использованием любого типа триггеров. Серийный сдвиг регистр

реализован с помощью D-триггеров с последовательные данные, применяемые в D вход первого триггера и

серийный номер данные, полученные на Q выход последнего триггера Показано. Рисунок 34.3. В каждые часы

переход 1 бит последовательных данных сдвинулся и в то же время мгновенный 1-бит последовательных данных смещается

из. Для 4-битного сдвигового регистра 8 тактовых переходов требуется сдвиг в 4-битном данные и

346

CS302 — Цифровая логика и дизайн

полностью

сместить 4-битный

данные. По мере сдвига данных

выводиться по 1 биту за раз, логика

0 значение

По мере сдвига данных

выводиться по 1 биту за раз, логика

0 значение

обычно перешел на пополнение свободные биты в смене регистр.

Рисунок 34.3a Последовательный вход/смена Правый/серийный выход Регистр

Рисунок 34.3b Временная диаграмма Последовательный ввод/Сдвиг вправо/Последовательный Выходной регистр

сдвиг влево и сдвиг регистры правого сдвига идентичны по своей работе. Они

подключены иначе для сдвига влево и операции сдвига вправо. Двунаправленные сдвиговые регистры доступны

которые позволяют данным быть смещены влево или вправо. Рисунок 34.4. 4-битный регистр

настроен на сдвиг влево или вправо на установка сигнала ВПРАВО/ВЛЕВО на высокий логический уровень или низкий

соответственно. Когда реестр будет настроен на сдвиг вправо, вентили И, отмеченные цифрой 1 включены

. Ввод первого триггер подключен к серийный ввод, входы следующий

три

триггеры подключены к

выходы Q

предыдущие триггеры. Таким образом, на

часы

Таким образом, на

часы

переход данные сдвигаются на 1 бит вправо. последовательные данные смещаются реестра

через выход Q3. Когда реестр настроен на сдвиг влево от ворот И отмечены 2

включены, подключение выходов Q триггер справа со стороны руки к входу D триггер

на левая сторона. Таким образом, на каждых часах данные перехода сдвинуты 1 бит влево.

Серийный номер Дата выхода доступна через выход Q0. Серийные данные ввод через последовательный Данные в

строка который подключен к четвертые ворота И отмечены 2 на крайняя правая рука сторона.

347

CS302 — Цифровая логика и дизайн

ПРАВО / Слева

Сериал

1

2

1

2

1

2

1

2

Данные

в

Q0

0002 Q3SET

SET

SET

SET

D

D

D

D

Q

Q

Q

Q

Q0

Q1

Q2

триггер 1

триггер 2

триггер 3

триггер 4

В

В 9Рисунок

34. 4a Двунаправленный, 4-битный

Сдвиговый регистр

4a Двунаправленный, 4-битный

Сдвиговый регистр

ВПРАВО / СЛЕВА

Рисунок 34.4b Временная диаграмма Двунаправленный, 4-битный сдвиг регистр

временная диаграмма показывает работа Двунаправленная сдвиговый регистр, который изначально сдвигает

данные влево. В интервал t5, зарегистрированный настроен на сдвиг вправо и в t8 в сторону

влево и снова в сторону прямо на интервале t14. А логика 1 применяется в Последовательный ввод данных из

интервалов от t1 до t10. В интервал t11 и логический 0 применяется в Серийные данные вход.

3. Серийный номер Вход/параллельный выход Операция

Данные перешел в левую руку направление по одному биту за раз с каждым переходом на часы

сигнал. Данные поступают в регистр сдвига последовательно от правая сторона и через четыре часы

переходов

4-битный регистр имеет

4 бита данных. Данные

выведены параллельно на

Данные

выведены параллельно на

348

CS302 — Цифровая логика и дизайн

приложение одиночный тактовый сигнал. сдвиговый регистр имеет 4 параллельные выходы. схема

схема последовательный вход/параллельный выход показан регистр. Фигура 34.5.

Рисунок 34,5

Серийный номер Вход/параллельный выход Операция

74HC164 — это 8-битный последовательный порт MSI. В/параллельное смещение Регистр. Смена регистр

имеет 8 параллельные выходы, асинхронный Вход CLR с активным низким уровнем, который очищает смену регистр.

сдвиговый регистр срабатывает позитивные часы переход. Серийные данные подается через

входы A и B. Входные контакты A и B внутренне связаны через внутреннюю NAND ворота.

два контакта действуют как данные ввод и сдвиговый регистр включить входы. Серийные данные подается либо на вход

A, либо на вход B. Другой вход, когда

установка на высокий логический уровень включает

операция смены.

Рисунок

Другой вход, когда

установка на высокий логический уровень включает

операция смены.

Рисунок

34.6

A

B

74HC164

CLR

CLK

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

3 Рисунок 34.6a 74HC164, 8-битный последовательный В/параллельное смещение Регистрация

349

CS302 — Цифровая логика и дизайн

CLR

Рисунок 34.6b Временная диаграмма 74HC164, 8-битный последовательный В/параллельное смещение Регистрация

В временная диаграмма, регистр очищается асинхронно путем активации активный-

низкий Вход CLR в интервале t0. Серийные данные подается на вход А зарегистрироваться до интервал

т0. Тем не менее, реестр разрешено выполнять смену срабатывание в интервале t1, когда вход B установить

на логику высокий. В интервале t2 есть от низкого к высокому переход в сериале ввод данных, который защелка

по

первый триггер в

положительный часовой переход в

интервал t3. В

каждые положительные часы

переход

В

каждые положительные часы

переход

от интервал t4 к t10 данные сдвигаются вправо на 1 бит.

4. Параллельный Вход/Последовательный выход Операция

регистр имеет параллель входы, биты данных загружается в реестр в параллельно

активируя сигнал нагрузки. Данные последовательно выведены Применение тактовых сигналов. Таким образом, в

4-битный сдвиговый регистр, после 4 часы сигнализируют 4-битный данные полностью сдвинуты из регистра сдвига

. Рисунок 34.7

350

CS302 — Цифровая логика и дизайн

Рисунок 34,7

Параллельный Вход/Последовательный выход Операция

внутренняя схема 4-битного Параллельный вход/последовательный выход показан регистр. Фигура 34.8.

4-битные данные изначально загружается параллельно в регистр сдвига, установив

СМЕНА /

Вход ЗАГРУЗКИ в низкий логический уровень. Ворота И, отмеченные цифрой 2,

включено, позволяя данным

быть

Ворота И, отмеченные цифрой 2,

включено, позволяя данным

быть

применяется в входы соответствующих D-триггеры. На позитивных часах передать данные

запирается соответствующие триггеры. К сдвигать данные, т. СДВИГ / НАГРУЗКА установить на высокий логический уровень

который включает вентили И, отмеченные 1 подключение выходов Q каждый триггер подключен

к D ввод следующего резкий поворот.

D0

D1

D2

D3

SHIFT / Загрузка

1

2

1

2

1

2

Q3

Установите

Установите

SET

SET

D

D

D

D

Q

Q

Q

Q

Q0

Q1

Q2

Serial

Data

flip -флоп 1

триггер 2

триггер 3

триггер 4

Выход

В

В

В

Q

CLR

CLR

CLR

CLR

CLK

34,8

4 бита Параллельный вход/последовательный выход регистр

74HC165 — 8-битный параллельный Регистр In/Serial Out, который также может работать как 8-битный

Последовательный

Входной/последовательный выходной регистр. Параллельно данные загружаются

асинхронно с помощью

Параллельно данные загружаются

асинхронно с помощью

Асинхронный Установить/очистить входы. После загрузка параллельного 8-бти данные, последовательный сдвиг операция

осуществляется вне, включив часы сигнал. CLK и Сигнал CLK INH внутренне подключенный

через ИЛИ ворота к тактовым входам восемь триггеров. тактовый сигнал включен по

установка сигнал CLK INH на логику низкий. Рисунок 34.9.

351

CS302 — Цифровая логика и дизайн

D0 D1 D2 D3 D4 D5 D6 D7

SH / LD

Q7

SER

74HC165

CLK INH

Q7

CLK

Рисунок 34,9

74HC165, 8-битный параллельный вход/последовательный выход Сдвиговый регистр

5. Параллельный Вход/параллельный выход Операция

регистр имеет параллельные входы и параллельные выходы. Данные вводится параллельно

с применением

одиночный тактовый импульс. Данные

защелкивается на шлепанцах

часовой переход и

Данные

защелкивается на шлепанцах

часовой переход и

доступен в параллельная форма на триггерные выходы. Фигура 34.10. Внутренняя схема 4-битный

Параллельный Входной/параллельный выходной регистр показано. Рисунок 34.11. Параллельный вход/параллельный выход зарегистрироваться

магазина Параллельные данные и обычно не допускает никаких сменные операции.

Рисунок 34.10 Параллельный вход/Параллельный Выход Операция

Рисунок 34.11 На основе D-триггера 4-битный параллельный вход/параллельный Выходной регистр

352

CS302 — Цифровая логика и дизайн

D0 D1 D2 D3

Дж

К

74HC195

SH / LD

CLR

CLK

Q0 Q1 Q2 Q3

Рисунок 34.12 74HC195, 4 бита Параллельный вход/параллельный выход Сдвиговый регистр

74HC195 — 4-битный параллельный

Входной/параллельный выходной регистр. Это

также имеет серийный вход

ввод,

Это

также имеет серийный вход

ввод,

поэтому реестр также может быть используется как последовательный/параллельный Выход или как последовательный вход/ Серийный выход

регистр. Выход Q3 используется как вывод Serial Out. 74HC195. Входы J и K используются до

вход данные последовательно. Эти входы подключены к первому резкий поворот. SH / LD есть используется для загрузки

Параллельные данные и разрешить сменные работы на часовой переход. Вход CLR используется до

очистить регистр асинхронно. Рисунок 34.12.

D0 D1 D2 D3

CLR

S0

S1

74HC194

SR СЕР

СЛ SER

CLK

Q0 Q1 Q2 Q3

Рисунок 34.13 Двунаправленный 4-битный Универсальный сдвиг Регистрация

74HC194 — 4-битный двунаправленный Сдвиговый регистр, который сдвигает данные слева и правая

ручная

направления и имеет оба

Параллельный и последовательный ввод

и возможность вывода. Рисунок 34.13.

Рисунок 34.13.

регистр имеет 4-битные параллельные входы от D0 до D3 и Параллельные выходы с Q0 по Q3. Активный низкий уровень

Асинхронный Ввод CLR очищает регистр. Реестр сдвигает данные в положительную сторону часы

переход. Входы S0 и S1 управляют работа с реестром. Когда S0 и S1 оба имеют логику

высокий, регистр загружается параллельные данные, применяемые в входы D0 до D3 по часам переход.

353

CS302 — Цифровая логика и дизайн

Когда S0 высокий, сдвиг выполняется правильная операция out, серийные данные вводятся через вход SR SER

. Когда S1 высокий, сдвиньте проводится левая операция out, серийные данные вводятся через SL

SER вход. Когда оба S0 и S1 находятся низкий логический уровень регистра заторможенный.

6. Повернуть Правая операция

серийный вывод

регистр подключен к

последовательный ввод

регистр. По

По

заявка данные тактовых импульсов сдвинуты правильно. Данные сдвинуты из сериала булавка справа

рука сторона рециркулируется назад в сдвиговый регистр ввод с левой стороны сторона. Таким образом данные

вращается прямо в реестре. Рисунок 34.14

Рисунок 34.14 Повернуть вправо Операция

7. Поворот Левая операция

серийный вывод регистр подключен к последовательный ввод регистр. По

заявка данные тактовых импульсов сдвинуты левый. Данные сдвинуты из сериала шпилька слева

рука сторона рециркулируется назад в сдвиговый регистр ввод справа сторона. Таким образом данные

вращаются осталось в реестре. Рисунок 34.15

Рисунок 34.15 Повернуть влево Операция

Смена Счетчики регистров

Сдвиг счетчики регистров в основном регистры сдвига подключен для выполнения поворота слева и

повернуть

правильные операции. Когда данные

вращается через регистр

противодействовать определенной последовательности

из

Когда данные

вращается через регистр

противодействовать определенной последовательности

из

штатов повторил. Два часто используемых регистрировать счетчики в цифре логика Джонсон

Счетчик и Кольцо Прилавок.

1. Джонсон Счетчик

В Джонсоне счетчик, выход Q последнего триггер смены регистр подключен

на номер ввод данных первого резкий поворот. Схема 4-битный, на основе D-триггера Счетчик Джонсона

показан на рисунок 34.16. Последовательность государств, которые реализовано n-битным Джонсон

счетчик 2н. Таким образом, 4-битный Последовательности счетчиков Джонсона через 8 состояний и 5-битный Джонсон

счетчик последовательности через 10 состояний. Таблица 34.1

354

CS302 — Цифровая логика и дизайн

Рисунок 34.16 4-битный Джонсон Counter

Clock

Q0

Q1

Q2

Q3

Pulse

0

0

0

0

0

1

1

0

0

0

2

1

1

0

0

3

1

1

1

0

4

1

1

1

1

5

0

1

1

1

Таблица

34. 1 Последовательность состояний

4-битный счетчик Джонсона

1 Последовательность состояний

4-битный счетчик Джонсона

2. Кольцо Счетчик

Счетчик звонков похож на счетчик Джонсона, кроме что выход Q последний

триггер сдвиговый регистр подключен к вводу данных первого триггера сдвиг

регистр. Все триггеры счетчик очищается до логики низкий, за исключением первый триггер

, который настроен на высокий логический уровень. Фигура 34.17.

PRE

CLR

Рисунок 34.17 4-битное кольцо Счетчик

После инициализация счетчик, логика высокая устанавливается на выходе из первый триггер

сдвинут прямо в каждые часы переход. Таблица 34.2. С Цепь счетчика звонков нет расшифровка

ворот являются обязательными. Каждое состояние кольцевой счетчик имеет уникальный выход.

Clock

Q0

Q1

Q2

Q3

Pulse

0

1

0

0

0

1

0

1

0

0

Таблица

34.

к. выполняется за один такт

к. выполняется за один такт

Появление импульса на тактовом входе регистра сдвига вызывает перемещение записанной в нём информации на один разряд вправо или влево. Как и другие регистры, регистры сдвига используются для записи, хранения и выдачи информации, но основным их назначением является преобразование последовательного кода в параллельный или параллельного в последовательный.

Появление импульса на тактовом входе регистра сдвига вызывает перемещение записанной в нём информации на один разряд вправо или влево. Как и другие регистры, регистры сдвига используются для записи, хранения и выдачи информации, но основным их назначением является преобразование последовательного кода в параллельный или параллельного в последовательный.

После перехода сигнала на входе STB с высокого уровня на низкий, информация, записанная в регистр, сохраняется до появления следующего разрешающего сигнала на входе STB. Сигнал высокого уровня

После перехода сигнала на входе STB с высокого уровня на низкий, информация, записанная в регистр, сохраняется до появления следующего разрешающего сигнала на входе STB. Сигнал высокого уровня