Что такое стробирующий вход. Как работает стробирование в электронных схемах. Для чего используется стробирование в цифровых устройствах. Какие преимущества дает применение стробирующих входов.

Что такое стробирующий вход и его назначение

Стробирующий вход (строб-вход) — это специальный управляющий вход в электронных схемах, предназначенный для разрешения или запрещения прохождения сигнала в определенные моменты времени. Основная функция стробирующего входа заключается в синхронизации работы устройства и фиксации момента времени для выполнения определенного действия.

Стробирующие входы широко применяются в различных цифровых устройствах, таких как:

- Компараторы

- Мультиплексоры

- Демультиплексоры

- Аналого-цифровые преобразователи

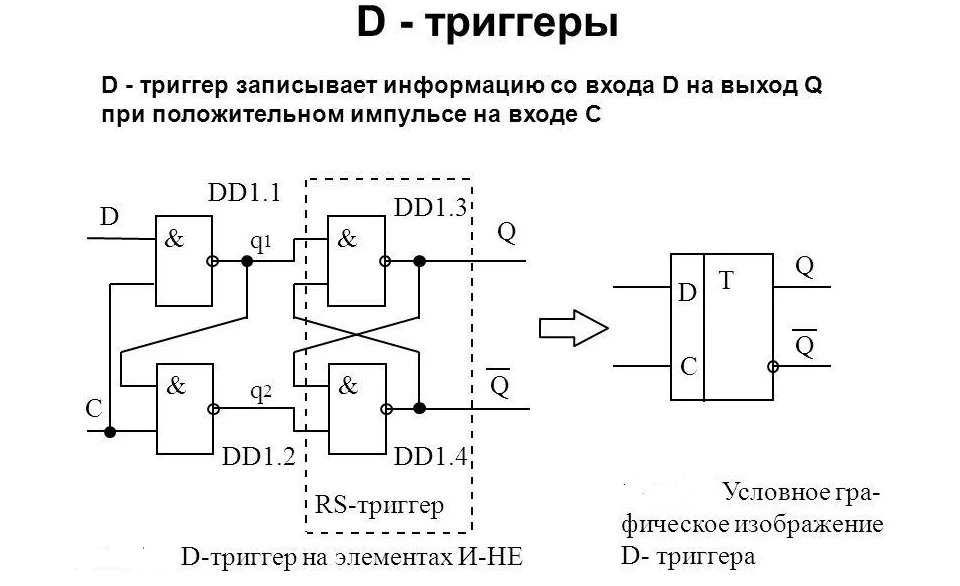

- Триггеры и регистры

- Счетчики

Использование стробирующих входов позволяет точно управлять моментом срабатывания устройства и синхронизировать его работу с другими элементами схемы.

Принцип работы стробирования в электронных схемах

- На стробирующий вход подается управляющий сигнал (строб-импульс)

- При наличии активного уровня на стробирующем входе разрешается прохождение основного сигнала через схему

- При отсутствии строб-импульса основной сигнал блокируется

Таким образом, строб-вход выполняет роль «электронного ключа», который открывается только в определенные моменты времени, задаваемые строб-импульсами.

Виды стробирования

Существует два основных вида стробирования:

- Стробирование по уровню — устройство активно, пока на стробирующем входе присутствует активный уровень сигнала

- Стробирование по фронту — устройство срабатывает по переднему или заднему фронту строб-импульса

Выбор типа стробирования зависит от конкретной схемы и решаемой задачи.

Применение стробирующих входов в компараторах

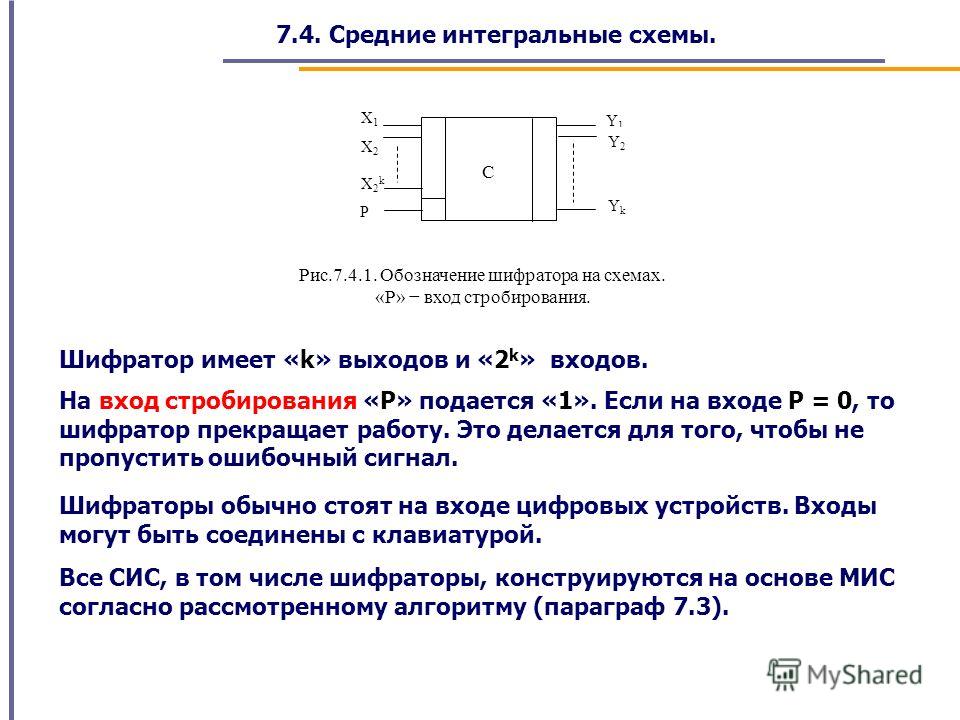

Одной из важных областей применения стробирующих входов являются компараторы. Компаратор — это устройство для сравнения двух аналоговых сигналов.Стробируемые компараторы имеют дополнительный строб-вход, который позволяет:

- Фиксировать момент времени для сравнения входных сигналов

- Выдавать результат сравнения на выход только во время действия строб-импульса

- Запоминать результат сравнения до прихода следующего строб-импульса (в компараторах с памятью)

Это дает возможность точно синхронизировать работу компаратора с другими узлами схемы и избежать ложных срабатываний от помех.

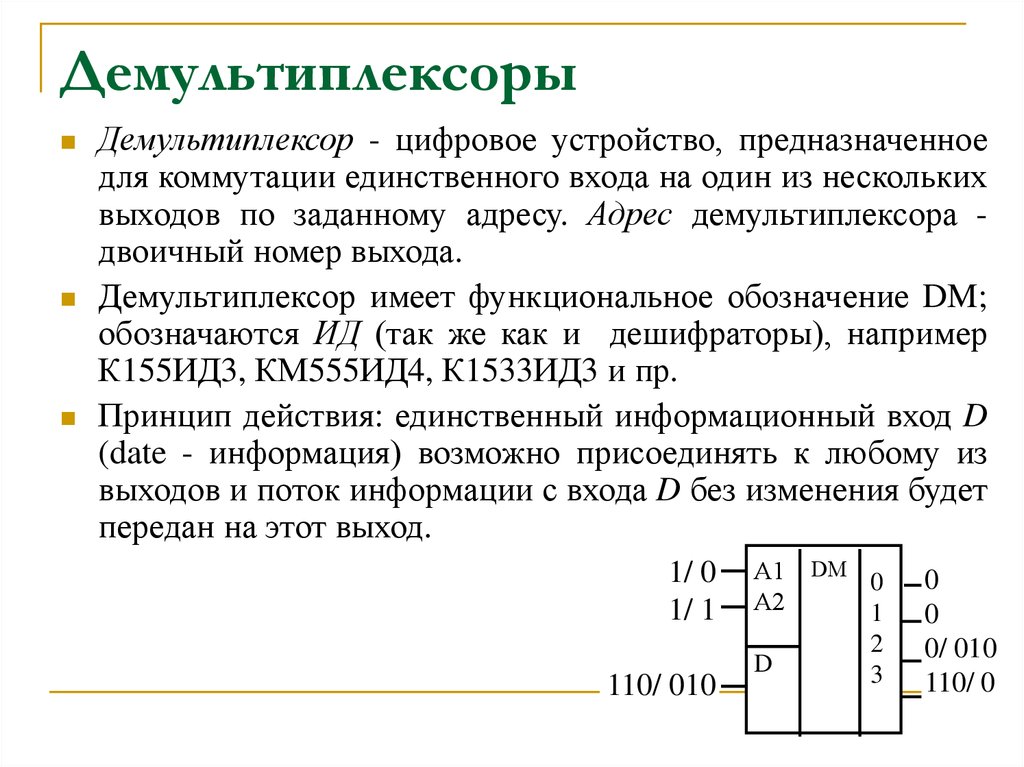

Использование стробирующих входов в мультиплексорах и демультиплексорах

Мультиплексоры и демультиплексоры широко применяются для коммутации цифровых сигналов. Стробирующие входы в этих устройствах выполняют следующие функции:

- Разрешение/запрещение работы устройства

- Синхронизация переключения каналов

- Расширение функциональных возможностей

Например, в мультиплексоре строб-вход позволяет управлять одновременно всеми информационными входами, блокируя или разрешая их работу независимо от состояния адресных входов. Это расширяет возможности по управлению устройством.

Роль стробирующих входов в аналого-цифровых преобразователях

В аналого-цифровых преобразователях (АЦП) стробирующий вход играет важную роль в процессе преобразования аналогового сигнала в цифровой код. Основные функции строб-входа в АЦП:

- Запуск процесса преобразования в заданный момент времени

- Фиксация входного аналогового сигнала на время преобразования

- Синхронизация работы АЦП с внешними устройствами

В зависимости от типа АЦП, стробирование может использоваться для преобразования максимального значения сигнала за время строб-импульса или его интегрального значения.

Преимущества использования стробирующих входов

Применение стробирующих входов в электронных схемах дает ряд существенных преимуществ:- Повышение помехоустойчивости за счет выборки сигнала только в заданные моменты времени

- Улучшение синхронизации работы различных узлов схемы

- Расширение функциональных возможностей устройств

- Возможность временного отбора сигналов

- Снижение энергопотребления за счет активации схемы только при необходимости

Эти преимущества делают стробирование важным инструментом при проектировании современных цифровых и аналого-цифровых устройств.

Особенности реализации стробирующих входов в интегральных схемах

При реализации стробирующих входов в интегральных микросхемах учитываются следующие аспекты:

- Быстродействие стробирующего входа должно соответствовать быстродействию основной схемы

- Необходимо обеспечить согласование уровней сигналов строб-входа с остальными входами микросхемы

- Важно минимизировать задержки распространения сигнала через стробирующий вход

- В некоторых случаях используются дополнительные схемы формирования строб-импульсов

Правильная реализация стробирующих входов позволяет максимально эффективно использовать их возможности в интегральных микросхемах различного назначения.

Применение стробирования в системах сбора и обработки данных

Стробирование широко используется в современных системах сбора и обработки данных. Основные области применения включают:

- Синхронизацию работы АЦП с источниками сигналов

- Управление мультиплексорами при последовательном опросе нескольких каналов

- Запуск процесса измерения в заданные моменты времени

- Синхронизацию работы различных измерительных модулей

Применение стробирования позволяет повысить точность измерений и обеспечить корректную временную привязку данных в многоканальных измерительных системах.

Вход — стробирование — Большая Энциклопедия Нефти и Газа, статья, страница 1

Cтраница 1

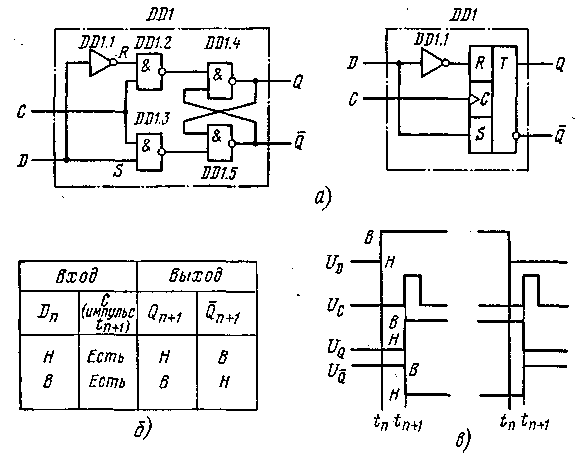

| Передаточная характеристика ( а и условное изображение стробируемых компараторов со стробированием по уровню ( б и по фронту ( в. [1] |

Входы стробирования предназначены для фиксации момента времени, когда производится сравнение входных сигналов и выдача результата сравнения на выход. Для этого на вход стробирования подается импульсный сигнал разрешения сравнения. Результаты сравнения могут появляться на выходе компаратора только во время строба или могут фиксироваться в элементах памяти компаратора до прихода очередного импульса строба. Таким образом, стробируемые компараторы могут быть без памяти и с памятью. [2]

ИС имеет два входа стробирования: вход синхронизации С и вход управления полярностью. Бескорпусная ИС с гибкими выводами. [3]

ИС имеют два [4]

[4]

ВО; 21 — вход стробирования ОЕ; 22 — вход выбора режима приема / передачи SBA; 23 — вход тактовый CAB; 24 — напряжение питания. [5]

Компаратор К521СА2 выполнен без входов стробирования. Его выходная мощность достаточна для управления десятью ТТЛ вентилями. [6]

Вторые эмиттеры ключевых каскадов служат входами стробирования. Использование импульсных транзисторов с барьерами Шотки значительно повысило быстродействие компаратора без изменения потребляемой мощности, поскольку исключено время выховд транзисторов из насыщения. Гарантируется стабильность выходного напряжения в широком диапазоне температур. [7]

Вторые эмиттеры ключевых каскадов служат входами стробирования. Использование импульсных транзисторов с барьерами Шотки значительно повысило быстродействие компаратора без изменения потребляемой мощности, поскольку исключено время выхода транзисторов из насыщения.

| Амплитудный дискриминатор.| Характеристика усилителя в режиме компаратора. 1н — уровень выходного сигнала компаратора, соответствующий логической 1 ( компаратор выдает сигнал. О — сигнала на выходе нет.| Блок-схема дифференциального амплитудного дискриминатора. СЗ — схема задержки, Ф — формирователь длительности импульса, А — схема антисовпадений, выполняющая функции временного отбора.| Временнйя диаграмма работы дифференциального амплитудного дискриминатора. [9] |

Для временного отбора в АЦП предусмотрен вход стробирования. В зависимости от стоящей задачи в код прообразуется максимальное значение сигнала аа время стрсб-импульса или его интеграл. [10]

Микросхема К521СА1 представляет собой двойной дифференциальный компаратор с двумя входами стробирования, позволяющий строить двухпороговые схемы с симметричным откликом на положительное и отрицательное превышение абсолютного уровня сигнала над пороговым уровнем. [12]

[12]

Микросхемы представляют собой сдвоенный цифровой селектор-мультиплексор 4 — 1 с общими входами выбора данных и раздельными входами стробирования. [13]

Микросхемы представляют собой сдвоенный селектор-мультиплексор 4×1 с инверсией входной информации, общими входами выбора данных и раздельными входами стробирования. [14]

Назначение выводов: 1 — вход умножения V2; 2-вход умножения W6; 3 — вход умножения V32, 4 — вход умножения W; 5 — выход Z; 6 — выход У; 7 — выход разрешение счета; в — общий; 9 — вход счетный Г; 10 — вход стробирования С; 11 — вход разрешение счета; 12 — вход последовательного включения; 13 — вход установки О R; 14 — вход умножения V4 -, 15 — вход умножения V8; 16 — напряжение питание. [15]

Страницы: 1 2

1.Основные понятия

Цель

работы:

Знакомство с принципом работы

мультиплексора и демультиплексора. Получение навыков работы по определению

временных диаграмм и составлению таблиц

соответствия.

Получение навыков работы по определению

временных диаграмм и составлению таблиц

соответствия.

Мультиплексоры

и демультиплексоры — цифровые

многопозиционные переключатели,

по-другому, коммутаторы. Мультиплексоры

предназначены для коммутации в желаемом

порядке информации, поступающей с

нескольких входных шин на одну выходную

и преобразования параллельного кода,

поступающего на информационные входы,

в последовательный код на выходе.

Мультиплексоры обладают двумя группами

входов и одним, реже двумя взаимодополняющими

выходами. Входы подразделяются на

информационные, на которые непосредственно

поступает код слова и служебные

(управляющие), к ним относятся: адресные

и разрешающие (стробирующие) входы. В

зависимости от комбинации сигналов на

адресных входах, происходит передача

бита информации с одного из информационных

входов на выход. Если мультиплексор

имеет n адресных входов, то максимальное

число информационных входов будет равно

2

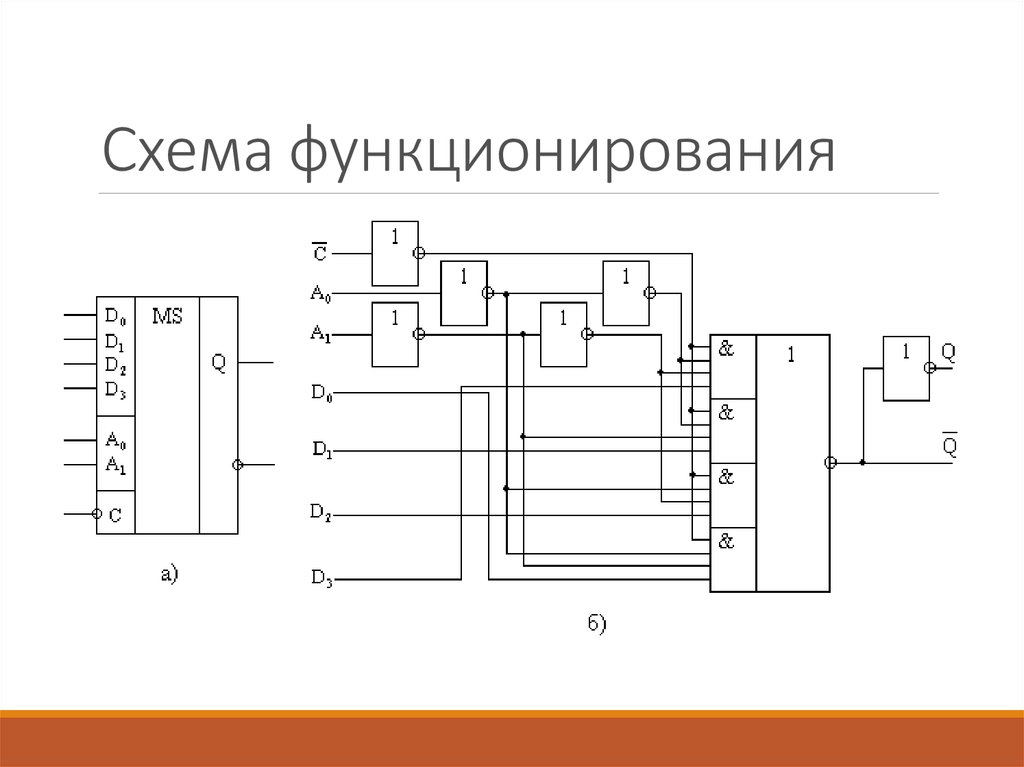

Разрешающий (стробирующий) вход управляет одновременно всеми информационными входами независимо от состояния адресных входов. Запрещающий сигнал на этом входе блокирует действие всего устройства. Наличие разрешающего входа расширяет функциональные возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов. Разрешающий вход употребляется также для наращивания разрядности мультиплексоров.

Демультиплексоры в функциональном отношении противоположны мультиплексорам. В демультиплексорах сигналы с одного информационного входа распределяются в желаемой последовательности по нескольким выходам, то есть происходит преобразование последовательного кода слова в параллельный. Выбор нужной выходной шины, как и в мультиплексоре, обеспечивается кодом на адресных входах. При m адресных входах мультиплексор может иметь, в зависимости от конструкции, до 2m выходов.

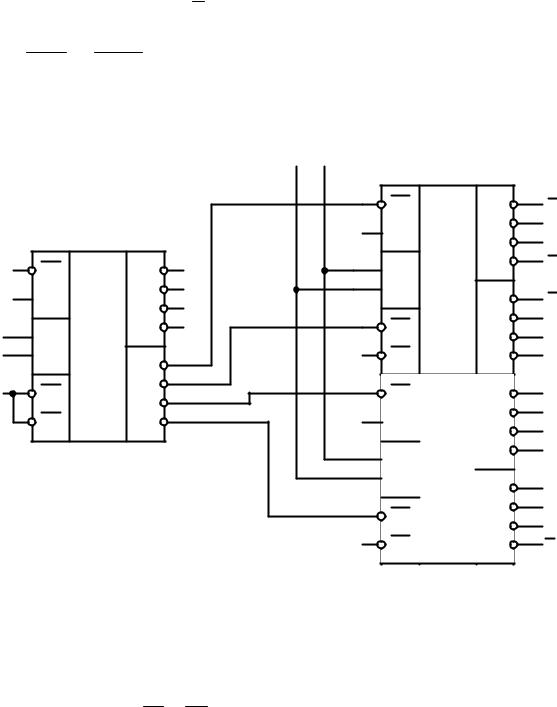

На

Рис. 1 показана логическая структура

мультиплексора “четыре линии к одной”

(4:1). Она содержит четыре информационных

входа D0-D3, два адресных входа Х1 и Х2 и

разрешающий вход С. Вход Х1 принадлежит

младшему разряду, Х2 — старшему. Когда

разрешающий вход находится под высоким

потенциалом Uвх (логическая единица),

один из входов логических элементов

“И” будет под низким и, следовательно,

на их выходах также будут нулевые уровни

независимо от состояния остальных

входов. Выходной сигнал в этом случае

также будет Y=0.

Она содержит четыре информационных

входа D0-D3, два адресных входа Х1 и Х2 и

разрешающий вход С. Вход Х1 принадлежит

младшему разряду, Х2 — старшему. Когда

разрешающий вход находится под высоким

потенциалом Uвх (логическая единица),

один из входов логических элементов

“И” будет под низким и, следовательно,

на их выходах также будут нулевые уровни

независимо от состояния остальных

входов. Выходной сигнал в этом случае

также будет Y=0.

Рис.1 Логическая структура мультиплексора вида (4:1)

Схема управления выполнена так, что при разрешающем сигнале на входе С любые комбинации сигналов на адресных входах Х1 и Х2 создают условия, при которых на входах (а, значит, и на выходах) трёх логических элементов “И” существуют потенциалы низкого уровня, неактивные для элемента “ИЛИ”.

Состояние

четвёртого элемента “И” и сигнала на

выходе мультиплексора определяется

сигналом на информационном входе.

Двоичные числа (00; 01; 10 и 11), эквивалентны

индексу задействованного информационного

входа (D0; D1; D2; D3).

Так, например, двоичное число 10 на адресных входах обеспечит селекцию шины D2. У мультиплексоров, выпускаемых в виде отдельных микросхем, число информационных входов не превышает шестнадцати. Увеличение числа входов обеспечивается путём наращивания. Наращивание можно выполнять двумя способами: объединением нескольких мультиплексоров в пирамидальную (древовидную) систему, либо последовательным соединением разрешающих входов и внешних логических элементов. На практике применяют оба метода.

Пирамидальные мультиплексоры (Рис. 2) строятся по ступенчатому принципу, причём обычно применяются две, реже — три и более ступени. Пирамидальный характер схемы состоит в том, что каждая ступень, начиная с первой, имеет больше входов, чем последующая.

D MS Y

Х

D MS Y

Х

D MS Y

Х

Y1

D0

D1

D3

D2

D4

D6

D5

Y2

D7

X2

X1

X3

Y

Рис. 2

Пирамидальный мультиплексор вида (8:1)

2

Пирамидальный мультиплексор вида (8:1)

Младшие разряды кода адреса подаются на адресные входы первой ступени, а ступеням более высокого ранга соответствуют старшие разряды адресного кода. Общее число информационных входов при однотипных мультиплексорах младшего ранга равно произведению числа входов отдельных мультиплексоров и числа самих мультиплексоров: Nвх.общ = Nвх*n.

Для очень больших Nвх.общ понадобится третий ряд мультиплексоров. Порядок их подключения не требует пояснений. Общее число входов определяется по той же формуле.

Недостатками пирамидального наращивания считается повышенный расход микросхем, а также невысокое быстродействие из-за суммирования задержек при последовательном прохождении сигналов по ступеням пирамиды. Логическая структура матричного демультиплексора представлена на рис. 3.

Рис.3 Логическая структура демультиплексора вида (1 : 4).

Здесь

Х2 и Х1 — адресные входы, D

— информационный вход, С — разрешающий. Схема управления выполнена также как,

и у мультиплексора, только задача состоит

в переключении одного входящего сигнала

на один из четырех выходов.

Схема управления выполнена также как,

и у мультиплексора, только задача состоит

в переключении одного входящего сигнала

на один из четырех выходов.

У демультиплексоров, как и у мультиплексоров, увеличение числа входов обеспечивается путем наращивания.

Интегральная схема— Пояснение к 4-битной защелке «строб-вывод» / декодеру от 4 до 16 строк

Задавать вопрос

спросил

Изменено 1 год, 11 месяцев назад

Просмотрено 181 раз

\$\начало группы\$

Мне интересно, смогу ли я добиться определенного поведения от этого чипа. Я прочитал техническое описание, и у меня возникли некоторые проблемы с пониманием использования булавки Strobe.

CD4515BM96 Datasheet PDF

Я пытаюсь сконструировать компьютер из интегральных микросхем без использования микропроцессоров или микроконтроллеров. Я хотел бы использовать этот чип для декодирования и адресации до 16 МБ памяти, разделенной на микросхемы SRAM по 512 КБ. Шина адреса данных имеет разрядность 24 бита. Старший бит будет использоваться для переключения между старшими 8 МБ и младшими 8 МБ памяти, более высокие 8 МБ, скорее всего, будут адресовать съемную энергонезависимую память. Следующие 4 старших бита шины адреса данных пойдут на микросхему LY625128SL, о которой я хотел бы спросить. Его выходы будут поступать на контакты включения/записи выхода соответствующего статического ОЗУ. (Я мог бы заменить их другой ИС, чтобы получить такое поведение, или у меня могло бы быть только два CD4515BM9.6)

Я не хочу беспокоиться о подаче импульсов часов на штырек стробоскопа на этой микросхеме, потому что я считаю, что в этом может не быть необходимости. Если я просто привяжу шпильку стробоскопа высоко, не обойдет ли она защелку? Мне не нужна защелка в этом чипе, потому что я могу просто использовать вывод регистра адреса данных, хранящего четыре необходимых ему бита.

Есть ли лучшая микросхема для моего варианта использования? Верно ли мое предложенное решение (высокая завязка стробоскопа)?

Спасибо за ваше время. Я всего лишь программист, от всей этой электротехнической чепухи голова идет кругом.

- интегральная схема

- параллельная

- компьютерная архитектура

- защелка

- декодер

\$\конечная группа\$

\$\начало группы\$

Если вы привяжете штифт стробоскопа высоко, он будет передавать входное значение через защелку.

Эта ИС очень подходит для вашего приложения, и ваше решение правильное.

\$\конечная группа\$

1

\$\начало группы\$

Строб просто позволяет вводить данные. Это видно на рис.13 — Логическая схема. Пока строб равен 0, данные 1-4 недействительны.

Пока строб равен 0, данные 1-4 недействительны.

\$\конечная группа\$

2

Зарегистрируйтесь или войдите в систему

Зарегистрируйтесь с помощью Google

Зарегистрироваться через Facebook

Зарегистрируйтесь, используя электронную почту и пароль

Опубликовать как гость

Электронная почта

Требуется, но никогда не отображается

Опубликовать как гость

Электронная почта

Требуется, но не отображается

Нажимая «Опубликовать свой ответ», вы соглашаетесь с нашими условиями обслуживания, политикой конфиденциальности и политикой использования файлов cookie

Выход стробоскопа

Что вы ищете?

Фильтр:

Отправить поиск

Если параметр OutputFunction класса Board имеет значение UNKNOWN, выходной мультиплексор IOUT1 находится под управлением параметра StrobeMode класса Channel.

Диаграмма состояния выходного мультиплексора (OutputFunction = UNKNOWN)

Выходной мультиплексор перенастраивается при активации канала (событие SCA) и деактивации (событие ECA) в соответствии со значением StrobeMode:

| ● | Когда StrobeMode = AUTO или MAN, выходной мультиплексор настраивается следующим образом: |

| □ | При активации канала принудительно устанавливается в положение STROBE, позволяя сигналу STROBE управлять оптопарой выходного порта. |

| □ | При деактивации канала принудительно устанавливается в положение LOW, отключая оптопару и предотвращая появление любых стробирующих импульсов, пока канал деактивирован. |

| ● | Когда StrobeMode = OFF, выходной мультиплексор настраивается при активации канала в положение LOW, отключая оптопару и предотвращая возникновение стробирующих импульсов во время активности канала.

|