Что такое RS-триггер и как он работает. Какие бывают схемы RS-триггеров. Как выглядит таблица истинности RS-триггера. Чем отличаются синхронные и асинхронные RS-триггеры. В чем преимущества и недостатки RS-триггеров.

Что такое RS-триггер и его основные характеристики

RS-триггер — это простейший тип триггера, способный хранить 1 бит информации. RS расшифровывается как Reset-Set (Сброс-Установка). Основные характеристики RS-триггера:

- Имеет два входа: S (Set) для установки и R (Reset) для сброса

- Два выхода: прямой Q и инверсный Q’

- Может находиться в одном из двух устойчивых состояний: Q=1, Q’=0 или Q=0, Q’=1

- Переключается между состояниями под действием сигналов на входах S и R

- Простейшая схема строится на двух логических элементах И-НЕ или ИЛИ-НЕ

Принцип работы RS-триггера

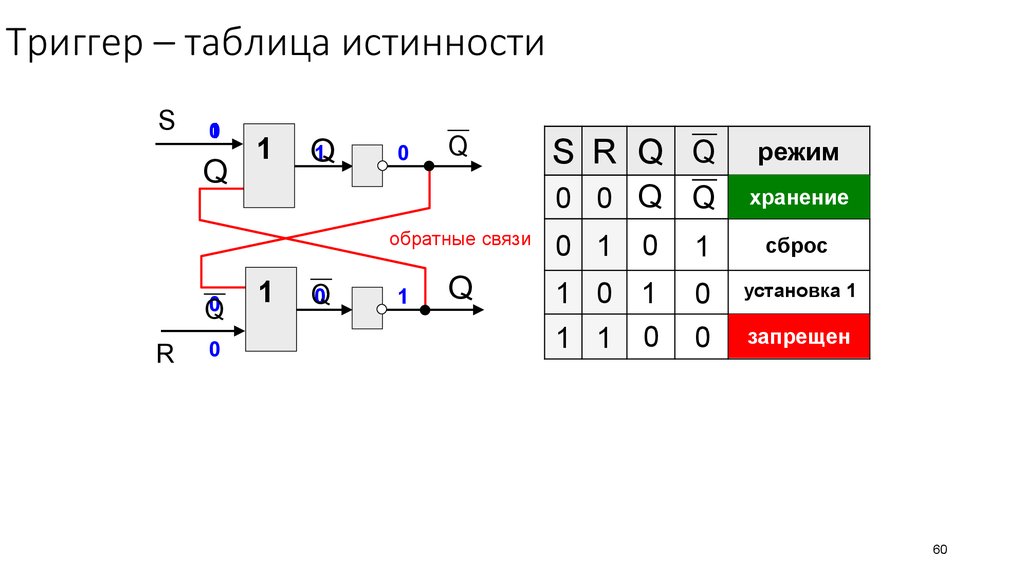

Принцип работы RS-триггера основан на логике обратной связи между двумя логическими элементами. Рассмотрим основные режимы работы:

- Режим хранения информации (S=0, R=0): состояние выходов не меняется

- Режим установки в 1 (S=1, R=0): устанавливает Q=1, Q’=0

- Режим сброса в 0 (S=0, R=1): устанавливает Q=0, Q’=1

- Запрещенное состояние (S=1, R=1): состояние неопределенно

Схемы реализации RS-триггеров

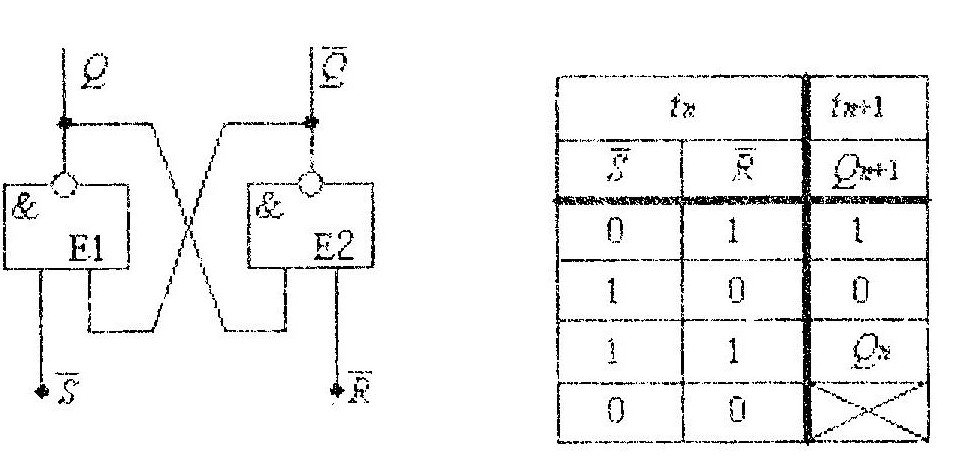

Существует несколько вариантов схем RS-триггеров:

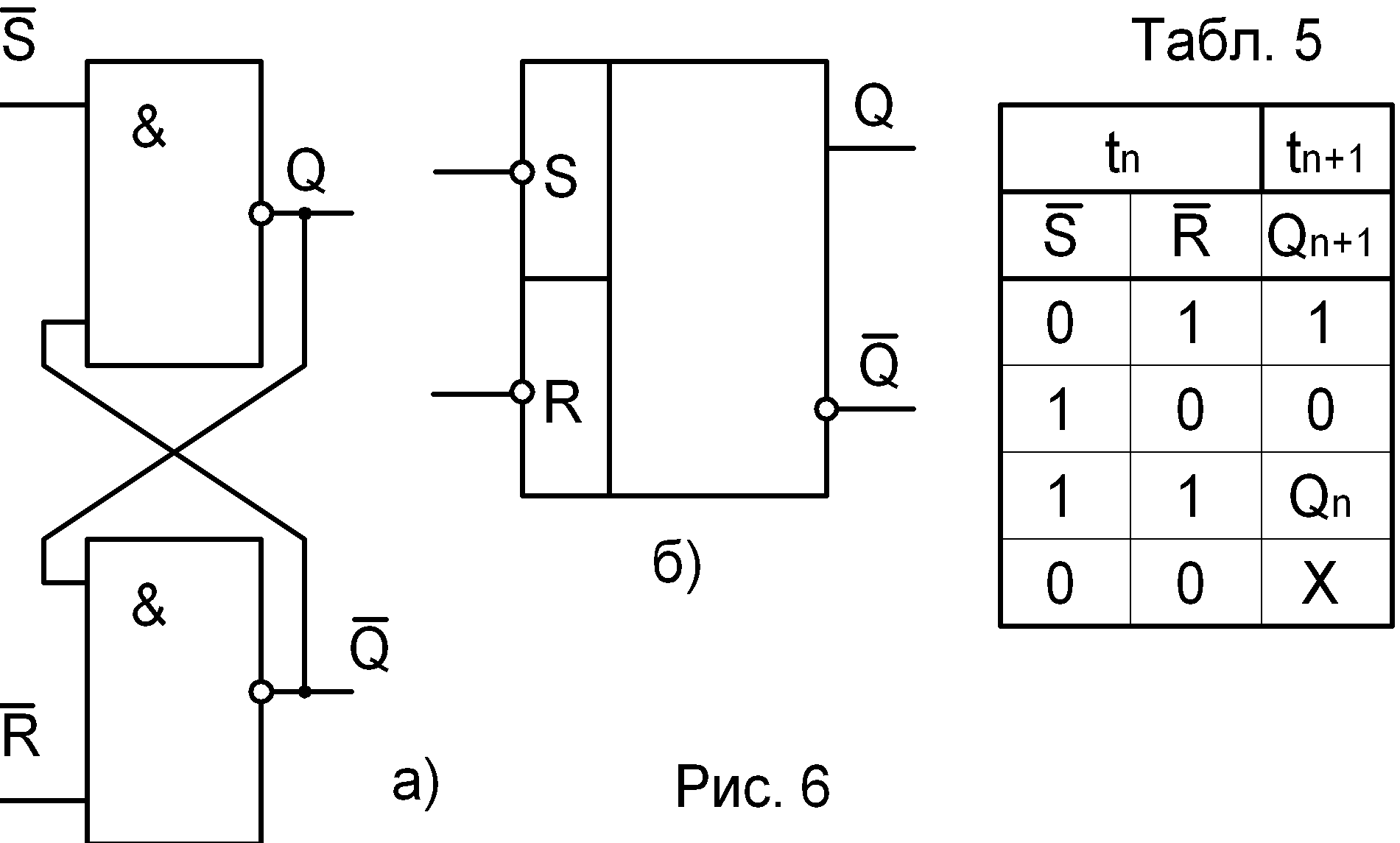

1. RS-триггер на элементах И-НЕ

Это классическая реализация RS-триггера. Схема состоит из двух элементов 2И-НЕ, соединенных перекрестными обратными связями.

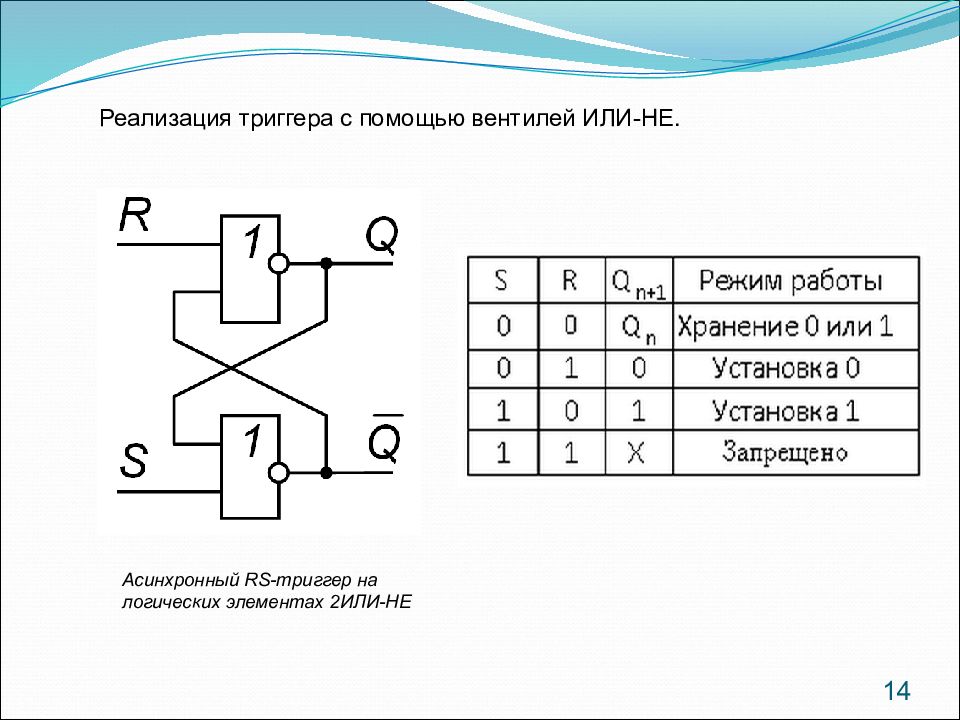

2. RS-триггер на элементах ИЛИ-НЕ

Аналогичная схема, но на элементах 2ИЛИ-НЕ. Работает по тому же принципу, что и схема на И-НЕ.

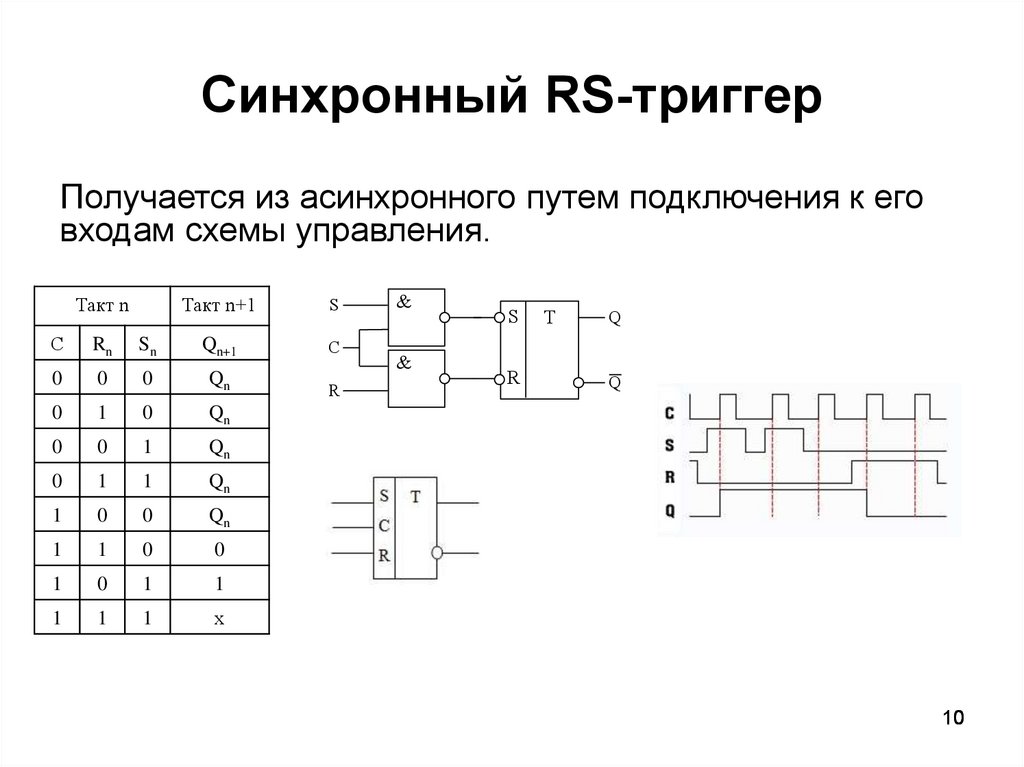

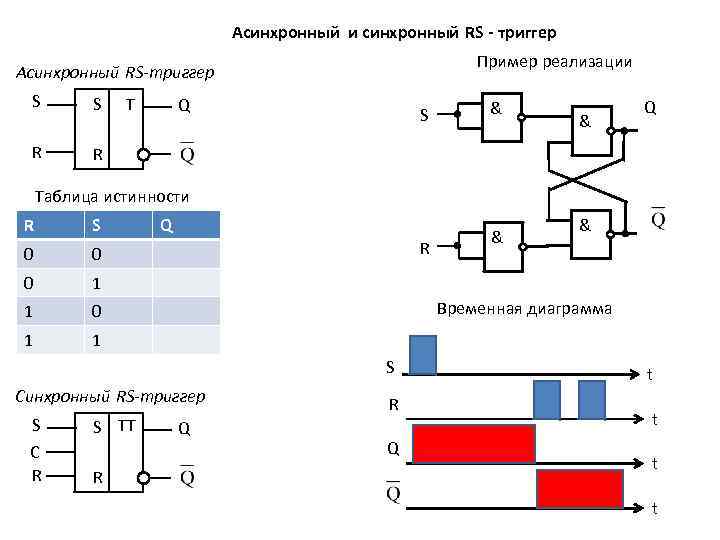

3. Синхронный RS-триггер

Отличается наличием дополнительного входа синхронизации C. Переключение происходит только при активном сигнале синхронизации.

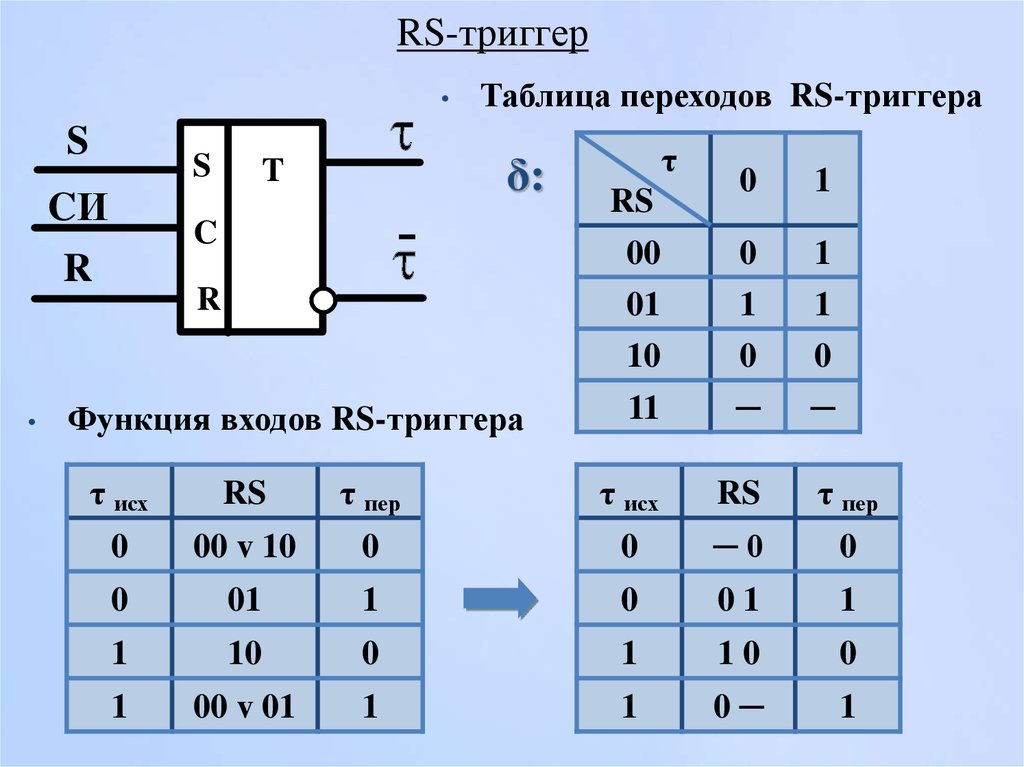

Таблица истинности RS-триггера

Таблица истинности описывает поведение RS-триггера при различных комбинациях входных сигналов:

| S | R | Q(t+1) | Режим |

|---|---|---|---|

| 0 | 0 | Q(t) | Хранение |

| 0 | 1 | 0 | Сброс |

| 1 | 0 | 1 | Установка |

| 1 | 1 | X | Запрещено |

Синхронные и асинхронные RS-триггеры: в чем разница

Основное отличие синхронных RS-триггеров от асинхронных:

- Асинхронные RS-триггеры переключаются сразу при изменении входных сигналов S и R

- Синхронные RS-триггеры имеют дополнительный вход синхронизации C

- Переключение синхронных триггеров происходит только по фронту или спаду тактового сигнала

- Синхронные триггеры менее подвержены ложным срабатываниям от помех

Преимущества и недостатки RS-триггеров

RS-триггеры имеют ряд преимуществ и недостатков:

Преимущества:

- Простая схемотехническая реализация

- Высокое быстродействие

- Низкое энергопотребление

- Возможность асинхронной работы

Недостатки:

- Наличие запрещенного состояния (S=R=1)

- Возможность «гонок» сигналов при одновременном переключении S и R

- Ограниченные функциональные возможности по сравнению с другими типами триггеров

Области применения RS-триггеров

RS-триггеры находят применение в различных цифровых устройствах:

- Формирование импульсов заданной длительности

- Устранение дребезга контактов

- Построение более сложных триггерных схем (JK-, D-, T-триггеры)

- Синхронизация сигналов в цифровых системах

- Запоминание битов информации в регистрах и ОЗУ

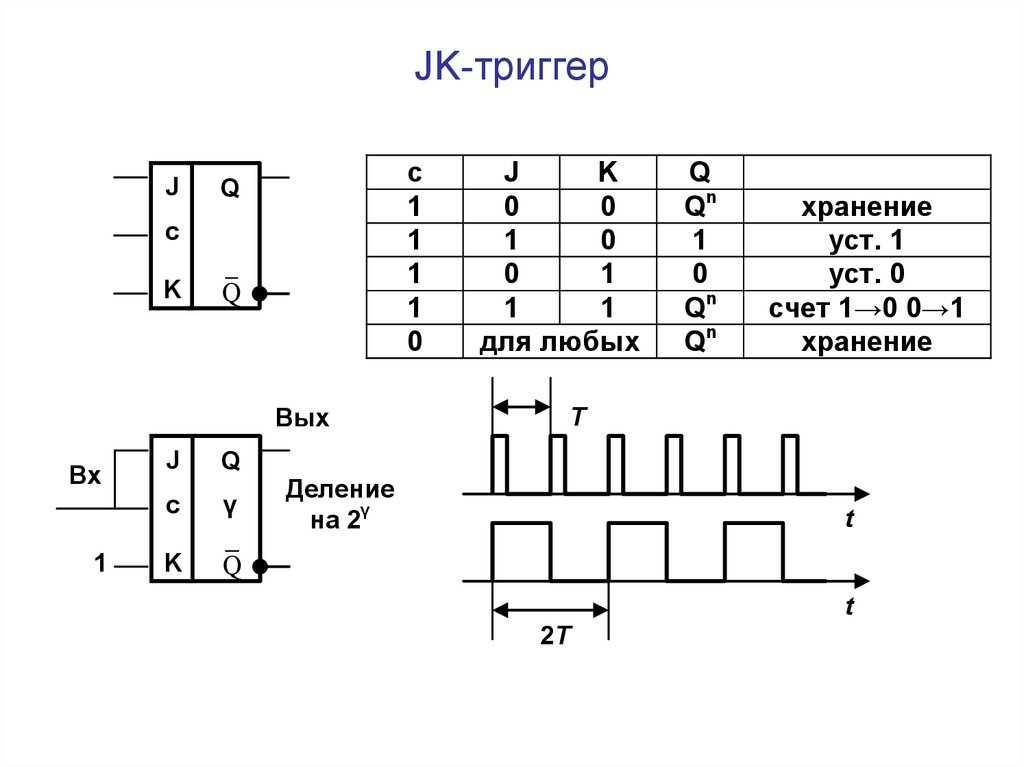

Сравнение RS-триггера с другими типами триггеров

RS-триггер является базовым элементом для построения более сложных триггеров. Рассмотрим его отличия от других распространенных типов:

- JK-триггер: устраняет проблему запрещенного состояния RS-триггера

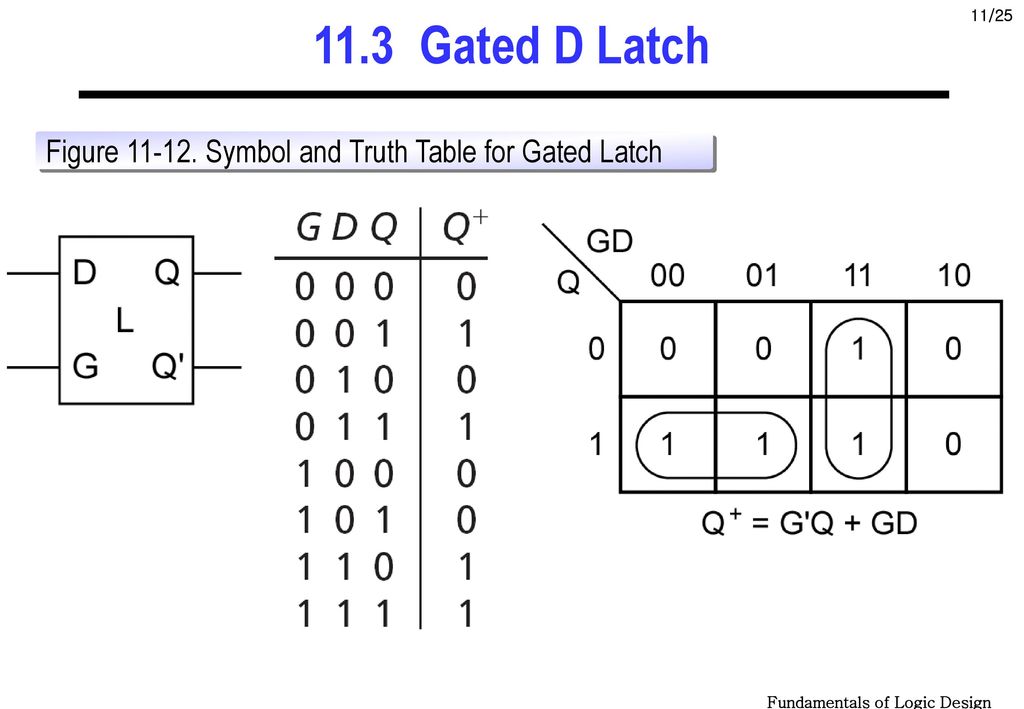

- D-триггер: имеет один информационный вход, что упрощает управление

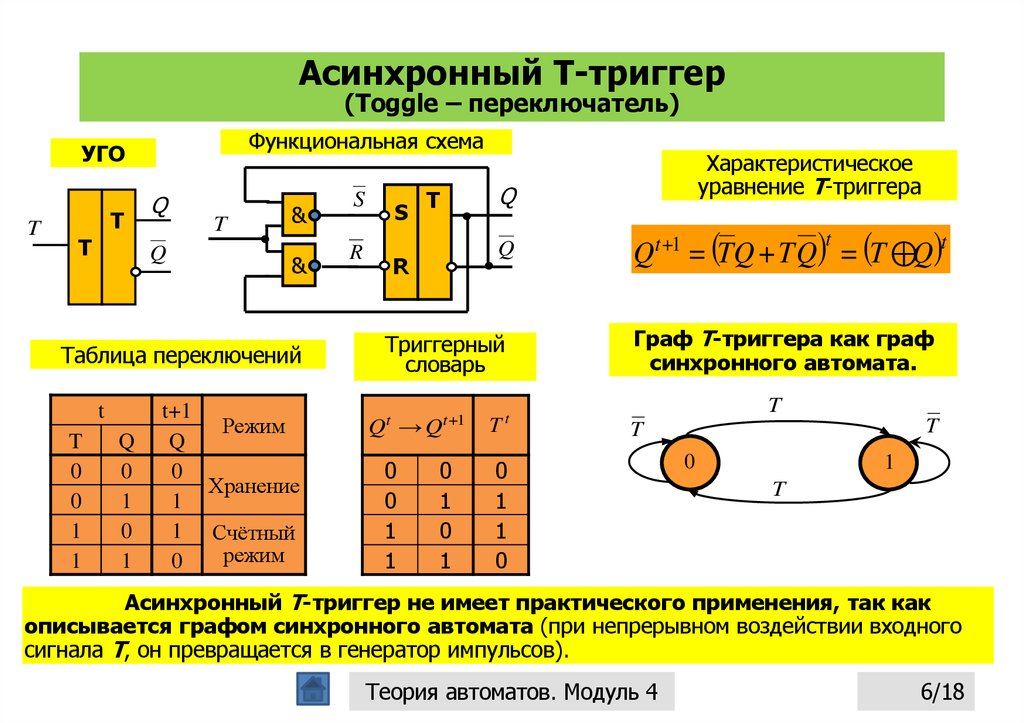

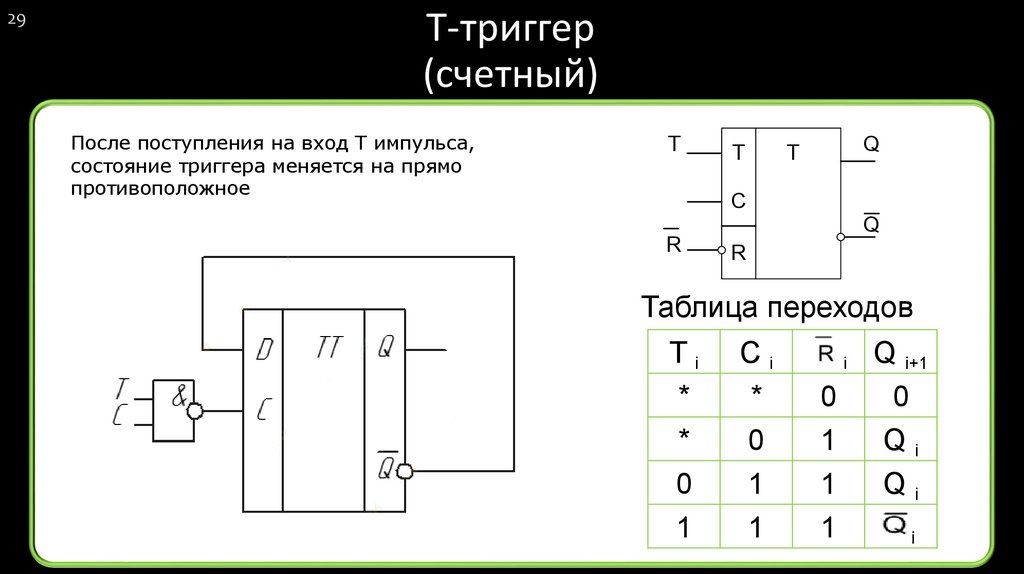

- T-триггер: переключается в противоположное состояние по каждому тактовому импульсу

Каждый тип триггера имеет свои преимущества и области применения. RS-триггер остается востребованным благодаря своей простоте и универсальности.

Как правильно использовать RS-триггер в схемах

При использовании RS-триггеров в схемах следует учитывать несколько важных моментов:

- Избегать одновременной подачи активных уровней на входы S и R

- Учитывать возможность ложных срабатываний от помех в асинхронных схемах

- Использовать подтягивающие резисторы на входах для определения состояния по умолчанию

- В синхронных схемах обеспечивать стабильность сигналов S и R во время активного уровня синхросигнала

Моделирование и анализ работы RS-триггера

Для глубокого понимания работы RS-триггера полезно провести его моделирование и анализ. Это можно сделать следующими способами:

- Использование программ схемотехнического моделирования (например, Multisim, LTspice)

- Построение временных диаграмм работы триггера при различных входных воздействиях

- Анализ переходных процессов и задержек распространения сигналов

- Исследование влияния паразитных параметров на работу реальных схем RS-триггеров

Такой анализ позволяет выявить особенности работы RS-триггера и оптимизировать его использование в конкретных приложениях.

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Определение триггера.

RS-триггер

RS-триггер - Подробности

- Автор: EngineerDeveloper®

Классическое определение термина «триггер» звучит следующим образом:

Триггер— класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов.

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этого устройства в английском языке чаще употребляется термин flip-flop, что в переводе означает «хлопанье».

Поясню. Триггер – это устройство, относящееся к классу электронных цифровых устройств обладающие способностью находиться либо в «0», либо в «1» и чередовать их под воздействием тактов и сигналов разрешения тактов, а также сигнала сброса.

Исторически триггеры разрабатывались на лампах, транзисторах. Но я бы не хотел углубляться в принцип работы триггера до уровня транзисторов и направлений протекания токов. Поэтому абстрагируемся от физики его работы и акцентируем внимание на особенности и принципе его работы с точки зрения цифровых процессов.

Поэтому абстрагируемся от физики его работы и акцентируем внимание на особенности и принципе его работы с точки зрения цифровых процессов.

На рис. 1 приведен самый элементарный триггер, реализованный на двух инверторах.

Рис.1. Простейший RS-триггер на инверторах.

RS – триггер изображенный на рис.1 способен хранить 1 бит информации. Но он не позволяет записать этот бит информации, стереть бит информации. Чего нельзя сказать про RS – триггер реализованный на двух элементах 2И-НЕ (см.рис.2)

Рис.2. Простейший RS-триггер (асинхронный) на элементах 2И-НЕ.

Из рисунка видно, что появились два входа: «S» — set (установка) и «R» — reset (сброс). С помощью входа «S» мы можем установить триггер в одно из двух устойчивых состояний, а вход «R» служит для сброса триггера.

Чтобы разобраться с принципом работы RS-триггера обратимся к таблице истинности приведенной в табл.1

|

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

0 |

0 |

0 |

Режим хранения информации R=S=0 |

|

0 |

0 |

1 |

1 |

|

|

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

|

0 |

1 |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

Режим записи нуля R=1 |

|

1 |

0 |

1 |

0 |

|

|

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

|

1 |

1 |

1 |

* |

Таблица 1. Таблица истинности RS-триггера (асинхронного).

Таблица истинности RS-триггера (асинхронного).

Из таблицы видно, если подать единицы на вход S выходное состояние становится равным логической единице. А при подаче единицы на вход R выходное состояние становится равным логическому нулю. Если одновременно установить на оба входы две логической единицы, тогда триггер может оказаться в любом не устойчивом состоянии. Подобная комбинация (R=1, S=1) является запрещенная. В более сложных триггерных схемах при запрещенной комбинации на входе, триггер переходит в третье состояние. Одновременное снятие обоих единиц практически невозможно, поэтому состояние после снятия запрещенной комбинации будет определяться оставшейся единицей. Таким образом, RS-триггер может находиться в трех состояниях, два из которых устойчивых и одно не устойчивое.

На рис.3 приведена схема синхронного RS-триггера. По сравнению с асинхронным триггером добавились два логических элемента «И-НЕ». Тем самым добавлен вход синхронизации «С». При этом принцип работы остался прежний за исключением того, что все процессы синхронны (см. табл. 2).

табл. 2).

Рис.3. Простейший RS-триггер (синхронный) на элементах 2И-НЕ.

В таблице 2 приведена таблица истинности для синхронного RS-триггера.

|

С |

R |

S |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

x |

0 |

0 |

Режим хранения информации |

|

0 |

x |

x |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

0 |

Режим хранения информации |

|

1 |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

1 |

Режим установки единицы S=1 |

|

1 |

0 |

1 |

1 |

1 |

|

|

1 |

1 |

0 |

0 |

0 |

Режим записи нуля R=1 |

|

1 |

1 |

0 |

1 |

0 |

|

|

1 |

1 |

1 |

0 |

* |

R=S=1 запрещенная комбинация |

|

1 |

1 |

1 |

1 |

* |

Таблица 2. Таблица истинности RS-триггера (синхронного).

Таблица истинности RS-триггера (синхронного).

Что такое RS Flip Flop? Ворота NAND и NOR RS Flip Flop & Truth Table

A Flip Flop — бистабильное устройство. Существует три класса триггеров, они известны как триггеры с защелками , триггеры с импульсным запуском, триггеры , триггеры с запуском по фронту, триггеры . В этом наборе слово означает, что выход схемы равен 1, а слово сброс означает, что выход равен 0.

Существует два типа триггеров, один из которых RS Flip Flop и JK Flip Flop . В этой статье подробно объясняется RS Flip Flop.

Содержимое :

- NAND Gate RS Flip-Flop

- Установленное состояние

- Состояние сброса

- Шлепанцы NOR Gate RS

RS Flip Flop считается одной из самых простых последовательных логических схем. Flip Flop — это бистабильное устройство с однобитовой памятью.

Он имеет два входа, один называется «SET» , который устанавливает устройство (выход = 1) и помечен как S, а другой известен как «СБРОС» , который сбросит устройство (выход = 0), помеченное как R. RS означает SET/RESET.

Триггер сбрасывается в исходное состояние с помощью входа RESET, а выход Q, который будет либо на логическом уровне «1», либо на логическом «0». Это зависит от состояния установки/сброса триггера. Слово Flip Flop означает, что его можно «FLIPPED» перевести в одно логическое состояние или «FLOPPED» обратно в другое.

Базовая схема RS Flip Flop вентиля И-НЕ используется для хранения данных и, таким образом, обеспечивает обратную связь от обоих своих выходов обратно к своим входам. RS Flip Flop фактически имеет три входа: SET, RESET и его текущий выход Q, относящийся к его текущему состоянию.

Символ RS Flip-Flop показан ниже:

RS Flip Flop Gate NAND

Пара соединенных между собой двухэлементных вентилей NAND — это самый простой способ выполнить базовую однобитовую установку/сброс. РС флип-флоп. Он формирует бистабильную установку/сброс или активную защелку LOW RS NAND. Обратная связь подается с каждого выхода на один из других входов логического элемента И-НЕ.

РС флип-флоп. Он формирует бистабильную установку/сброс или активную защелку LOW RS NAND. Обратная связь подается с каждого выхода на один из других входов логического элемента И-НЕ.

Устройство состоит из двух входов; один известен как SET, (S), а другой называется RESET, (R).

Два выхода Q и Q bar, как показано на рисунке ниже:

Установленное состояние

Рассматривая приведенную выше схему. Если на входе R находится логический уровень «0» (R = 0), а на входе S — логическая «1» (S = 1), элемент И-НЕ Y имеет, по крайней мере, один из своих входов на уровне логического «0». ». Следовательно, на его выходе Q должен быть уровень логической «1» (принцип вентиля И-НЕ). Выход (Q) подается обратно на вход «А». Оба входа элемента И-НЕ X находятся на уровне логической «1», а значит, его выход Q должен быть на уровне логического «0».

Вход сброса R меняет свое состояние и переходит в ВЫСОКИЙ уровень на логическую «1», при этом константа S равна логической «1». Вход Y ворот И-НЕ теперь (R = 1) и (B = 0). Выход на Q остается на ВЫСОКОМ уровне или на логическом уровне «1», так как один из его входов все еще находится на логическом уровне «0».

Вход Y ворот И-НЕ теперь (R = 1) и (B = 0). Выход на Q остается на ВЫСОКОМ уровне или на логическом уровне «1», так как один из его входов все еще находится на логическом уровне «0».

В результате состояние не изменилось. Следовательно, схема триггера называется «защелкнутой» или «установленной» с Q = 1 и Ǭ = 0.

Состояние сброса

его инверсный выход Q находится на уровне логической «1». И определяется как (R = 1) и (S = 0). Так как вентиль X имеет один из своих входов в состоянии логического «0», его выход Q должен быть равен логическому уровню «1». (Согласно принципу ворот И-НЕ). Выход Q подается на вход B, так что оба входа вентиля И-НЕ Y находятся в состоянии логической «1», следовательно, Q = 0,9.0011

Если установленный вход S теперь меняет состояние на логическую «1», а вход R остается в состоянии логической «1», выход Q остается НИЗКИМ на уровне логического «0». И никаких изменений в состоянии.

Следовательно, состояние «СБРОС» схемы триггера зафиксировано.

Таблица истинности Set/Reset приведена ниже:

| Состояние | S | R | Q | 9 Описание | |

|---|---|---|---|---|---|

| НАБОР | 1 | 0 | 1 | 0 | Комплект Q >>1 |

| 1 | 1 | 1 | 0 | Без изменений | |

| СБРОС | 0 | 1 | 0 | 1 | Сброс Q >>0 |

| 1 | 1 | 0 | 1 | Без изменений | |

| НЕДЕЙСТВИТЕЛЬНЫЙ | 0 | 0 | 0 | 1 | Память с Q = 0 |

| 0 | 0 | 1 | 0 | Память с Q = 1 |

Из таблицы истинности видно, что когда оба входа S = 1 и R = 1, выходы Q и Ǭ могут быть либо на логическом уровне «1», либо на «0» в зависимости от состояния входов. .

.

Когда состояние входа R = 0 и S = 0 является недопустимым условием, и его следует избегать, потому что это приведет к тому, что оба выхода Q и Ǭ будут на логическом уровне «1» одновременно, и необходимое условие состоит в том, чтобы Q был инверсия Ǭ.

Триггер переходит в нестабильное состояние, так как оба выхода становятся НИЗКИМИ. Это нестабильное состояние возникает, когда НИЗКИЙ вход переключается на ВЫСОКИЙ. Триггер переключается в то или иное состояние, и любой выход триггера переключается быстрее, чем другой. Это нестабильное состояние известно как метастабильное состояние.

Бистабильный RS-триггер активируется или устанавливается в логическую «1», подаваемую на его вход S, и деактивируется или сбрасывается логической «1», подаваемой на R. Считается, что RS-триггер находится в недопустимом состоянии, если оба входы установки и сброса активируются одновременно.

RS-триггер с вентилем ИЛИ-ИЛИ

Принципиальная схема триггера с вентилем ИЛИ-ИЛИ показана на рисунке ниже: такая же конфигурация. Схема будет работать аналогично схеме вентиля И-НЕ.

Схема будет работать аналогично схеме вентиля И-НЕ.

Таблица истинности вентиля NOR RS Flip Flop показана ниже:0089

Входы активны ВЫСОКИМ, и существует недопустимое состояние, когда оба его входа находятся на логическом уровне «1».

Освойте основы триггеров типов RS, JK, T и D

— Реклама —

Триггер в цифровой электронике — это схема с двумя устойчивыми состояниями, которую можно использовать для хранения двоичных данных. Сохраненные данные могут быть изменены путем применения различных входных данных. Триггеры и защелки являются основными строительными блоками систем цифровой электроники, используемых в компьютерах, средствах связи и многих других типах систем. Оба используются в качестве элементов хранения данных.

Оба используются в качестве элементов хранения данных.

Это основной элемент памяти в последовательной логике. Но сначала давайте проясним разницу между защелкой и триггерами.

Флип-флоп и защелка

Основное различие между защелкой и триггером заключается в механизме стробирования или синхронизации.

— Реклама —

Простыми словами. Флип-флоп срабатывает по фронту, а защелка срабатывает по уровню.

Если вы не понимаете, что такое защелка и триггер, вам следует ознакомиться с этой подробной статьей, в которой мы обсуждали разницу между защелкой и триггером.

Например, давайте поговорим о SR-защелке и SR-триггерах. В этой схеме, когда вы устанавливаете S как активный, выход Q будет высоким, а Q’ будет низким. Это независимо ни от чего другого. (Это схема с активным низким уровнем; поэтому здесь «активный» означает низкий уровень, но для схемы с активным высоким уровнем «активный» будет означать высокий уровень)

Защелка SR Триггер, с другой стороны, является синхронной схемой и также известен как защелка SR со стробированием или синхронизацией .

На этой принципиальной схеме выход изменяется (то есть сохраненные данные изменяются) только при подаче активного тактового сигнала. В противном случае, даже если S или R активны, данные не изменятся.

Давайте подробно разберем триггер с таблицей истинности и схемами.

Типы

Существует 4 основных типа триггеров:

- Триггер SR

- JK Триггер

- D Триггер

- T Триггер

SR Flip Flop

Это самый распространенный триггер среди всех. Эта простая триггерная схема имеет вход установки (S) и вход сброса (R). В этой системе, когда вы устанавливаете «S» как активный, выход «Q» будет высоким, а «Q ‘ » будет низким. Как только выходы установлены, проводка схемы сохраняется до тех пор, пока «S» или «R» не перейдут в высокий уровень или питание не будет отключено.

Как показано выше, это самый простой и легкий для понимания. Два выхода, как показано выше, являются обратными друг другу. Таблица истинности SR Flip-Flop выделена ниже.

Два выхода, как показано выше, являются обратными друг другу. Таблица истинности SR Flip-Flop выделена ниже.

| С | Р | Q | Вопрос |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | ∞ | ∞ |

Триггер JK

Из-за неопределенного состояния триггеров SR в электронике требуется другой триггер. Триггер JK является усовершенствованием триггера SR, где S = R = 1 не является проблемой.

JK Flip Flop CircuitВходное условие J=K=1 дает выход, инвертирующий состояние выхода. Тем не менее, результаты одинаковы при практическом тестировании схемы.

Проще говоря, если входные данные J и K различны (т. е. высокий и низкий уровень), то выход Q принимает значение J на следующем фронте тактового сигнала. Если J и K оба низкие, то никаких изменений не происходит. Если J и K оба имеют высокий уровень на фронте тактового сигнала, то выход будет переключаться из одного состояния в другое. JK Flip-Flops могут работать как Set или Reset Flip-flops.

Если J и K оба низкие, то никаких изменений не происходит. Если J и K оба имеют высокий уровень на фронте тактового сигнала, то выход будет переключаться из одного состояния в другое. JK Flip-Flops могут работать как Set или Reset Flip-flops.

Таблица истинности:

| J | К | В | Вопрос |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

D-триггер

D-триггер — лучшая альтернатива, очень популярная в цифровой электронике. Они обычно используются для счетчиков и регистров сдвига, а также для синхронизации ввода.

Они обычно используются для счетчиков и регистров сдвига, а также для синхронизации ввода.

В D-триггерах выход может быть изменен только по фронту тактового сигнала, и если вход изменяется в другое время, выход не изменится.

Таблица истинности:

| Часы | Д | Q | Вопрос |

| ↓ » 0 | 0 | 0 | 1 |

| ↑ » 1 | 0 | 0 | 1 |

| ↓ » 0 | 1 | 0 | 1 |

| ↑ » 1 | 1 | 1 | 0 |

Изменение состояния выхода зависит от переднего фронта тактового сигнала. Выход (Q) такой же, как и вход, и может изменяться только по переднему фронту тактового сигнала.

T-триггер

T-триггер похож на JK-триггер. В основном это версии JK-триггеров с одним входом. Эта модифицированная форма JK получается путем соединения входов J и K вместе. Он имеет только один вход вместе с тактовым входом.

Эта модифицированная форма JK получается путем соединения входов J и K вместе. Он имеет только один вход вместе с тактовым входом.

Эти триггеры называются Т-триггерами из-за их способности дополнять свое состояние, т.е. переключаться, поэтому они называются Триггеры-переключатели .

Таблица истинности:

| T | Q | Q (т+1) |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

Приложения

Это различные типы триггеров, используемых в цифровых электронных схемах, и области применения триггеров указаны ниже.

- Счетчики

- Делители частоты

- Сдвиговые регистры

- Регистры хранения

Вы также можете проверить эту презентацию ppt, чтобы узнать больше.

4).

4). 8. Схема реализации синхронного RS-триггера.

8. Схема реализации синхронного RS-триггера.