Что такое устройство управления с жесткой логикой. Как оно устроено и работает. Для чего применяется жесткая логика в управлении. Преимущества и недостатки по сравнению с программируемой логикой.

Что представляет собой устройство управления с жесткой логикой

Устройство управления (УУ) с жесткой логикой — это аппаратная реализация алгоритма управления, при которой логика работы задается схемными решениями. В таком УУ последовательность формирования управляющих сигналов определяется соединениями между логическими элементами.

Основные характеристики УУ с жесткой логикой:

- Алгоритм работы «зашит» в схему на этапе проектирования

- Высокое быстродействие за счет аппаратной реализации

- Ограниченные возможности модификации алгоритма

- Надежность в эксплуатации

- Относительная простота реализации для несложных алгоритмов

УУ с жесткой логикой широко применяются в системах управления технологическими процессами, станками, роботами и другим оборудованием, где требуется высокая скорость реакции и надежность работы.

Структура и принцип работы УУ с жесткой логикой

Типовая структура УУ с жесткой логикой включает следующие основные блоки:

- Регистр команд — хранит код текущей выполняемой команды

- Дешифратор команд — формирует сигналы для каждой команды

- Счетчик тактов — отсчитывает такты выполнения команды

- Дешифратор тактов — формирует сигналы для каждого такта

- Комбинационная логика — вырабатывает управляющие сигналы

- Формирователи управляющих сигналов

Принцип работы УУ с жесткой логикой:

- Код команды из регистра команд поступает на дешифратор

- Дешифратор активирует линию, соответствующую данной команде

- Счетчик тактов отсчитывает такты выполнения команды

- Дешифратор тактов активирует линию текущего такта

- Комбинационная логика вырабатывает управляющие сигналы для данной команды и такта

- Формирователи выдают управляющие сигналы на исполнительные устройства

Таким образом, последовательность управляющих сигналов жестко задана схемой и определяется текущей командой и тактом ее выполнения.

Преимущества и недостатки УУ с жесткой логикой

Основные преимущества УУ с жесткой логикой:

- Высокое быстродействие за счет аппаратной реализации алгоритма

- Надежность в эксплуатации

- Устойчивость к внешним помехам

- Относительная простота реализации для несложных алгоритмов

- Возможность работы в жестких условиях эксплуатации

Недостатки УУ с жесткой логикой:

- Сложность модификации алгоритма работы

- Увеличение сложности схемы при усложнении алгоритма

- Отсутствие гибкости в изменении функций устройства

- Сложность отладки и диагностики неисправностей

- Избыточность аппаратных средств при реализации сложных алгоритмов

Как правильно выбрать между УУ с жесткой и программируемой логикой? Это зависит от конкретной задачи и требований к системе управления.

Области применения УУ с жесткой логикой

УУ с жесткой логикой широко применяются в различных системах управления, где требуется высокая скорость реакции, надежность и работа в жестких условиях эксплуатации:

- Системы управления технологическими процессами

- Системы числового программного управления станками

- Управление промышленными роботами и манипуляторами

- Системы противоаварийной защиты

- Управление транспортными средствами

- Бортовые системы управления

- Системы управления вооружением

Где наиболее эффективно использовать УУ с жесткой логикой? В системах с четко определенным и редко меняющимся алгоритмом работы, требующих высокого быстродействия и надежности.

Сравнение УУ с жесткой и программируемой логикой

Основные отличия УУ с жесткой и программируемой логикой:

| Параметр | УУ с жесткой логикой | УУ с программируемой логикой |

|---|---|---|

| Реализация алгоритма | Аппаратная | Программная |

| Быстродействие | Высокое | Ниже |

| Гибкость | Низкая | Высокая |

| Надежность | Высокая | Ниже |

| Сложность модификации | Высокая | Низкая |

При выборе типа УУ необходимо учитывать требования к системе управления, сложность алгоритма, условия эксплуатации и другие факторы.

Проектирование УУ с жесткой логикой

Основные этапы проектирования УУ с жесткой логикой:

- Разработка алгоритма управления

- Составление графа микроопераций

- Кодирование состояний автомата

- Составление таблицы переходов и выходов

- Минимизация логических функций

- Построение логических схем

- Выбор элементной базы

- Разработка принципиальной схемы

При проектировании УУ с жесткой логикой важно тщательно проработать алгоритм управления и оптимизировать логические схемы для минимизации аппаратных затрат.

Перспективы развития УУ с жесткой логикой

Несмотря на широкое распространение программируемых логических контроллеров, УУ с жесткой логикой продолжают применяться во многих областях. Основные направления их развития:

- Применение современной элементной базы (ПЛИС, ASIC)

- Интеграция с программируемыми компонентами

- Использование в системах с повышенными требованиями к надежности

- Развитие средств автоматизированного проектирования

- Применение в системах реального времени

Какое будущее у УУ с жесткой логикой? Они будут применяться там, где требуется максимальное быстродействие, надежность и устойчивость к внешним воздействиям.

2.3. Устройство управления с жесткой логикой

Глава 2. Структура и функционирование процессора |

21 |

применением вместо постоянного ЗУ ПМК программируемого либо перепрограммируемого ЗУ (РПЗУ или ППЗУ соответственно). Возможна также замена БИС ПЗУ на ПЗУ с другой микропрограммой.

К числу микропроцессорных комплектов, в которых устройства управления реализованы в виде отдельного узла с использованием ПЗУ или РПЗУ в качестве памяти микрокоманд, относятся секционные (секционируемые) МП БИС серий К583, К584 К587,

К589, К1800, КР1802, К1804, К1883.

Управляющее устройство с «жесткой» логикой управления операционным блоком, то есть реализованное аппаратно, представляет собой так же как и УУ с программируемой логикой, конечный автомат. Для каждой операции, задаваемой, например, кодом операции команды на входе, строится набор комбинационных схем, которые в нужных тактах возбуждают соответствующие управляющие сигналы.

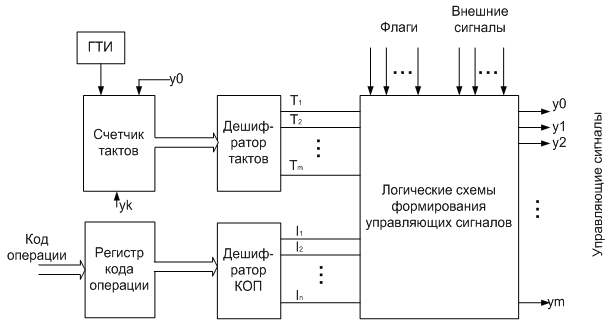

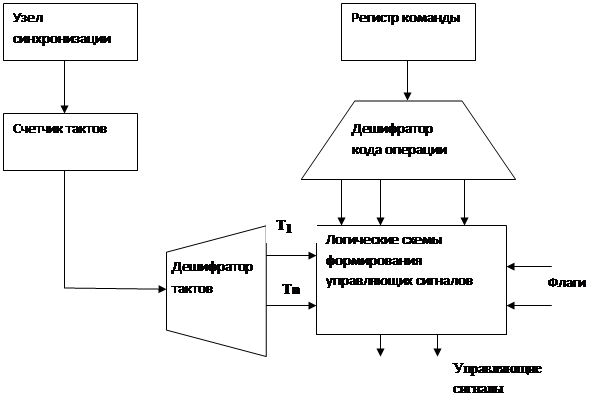

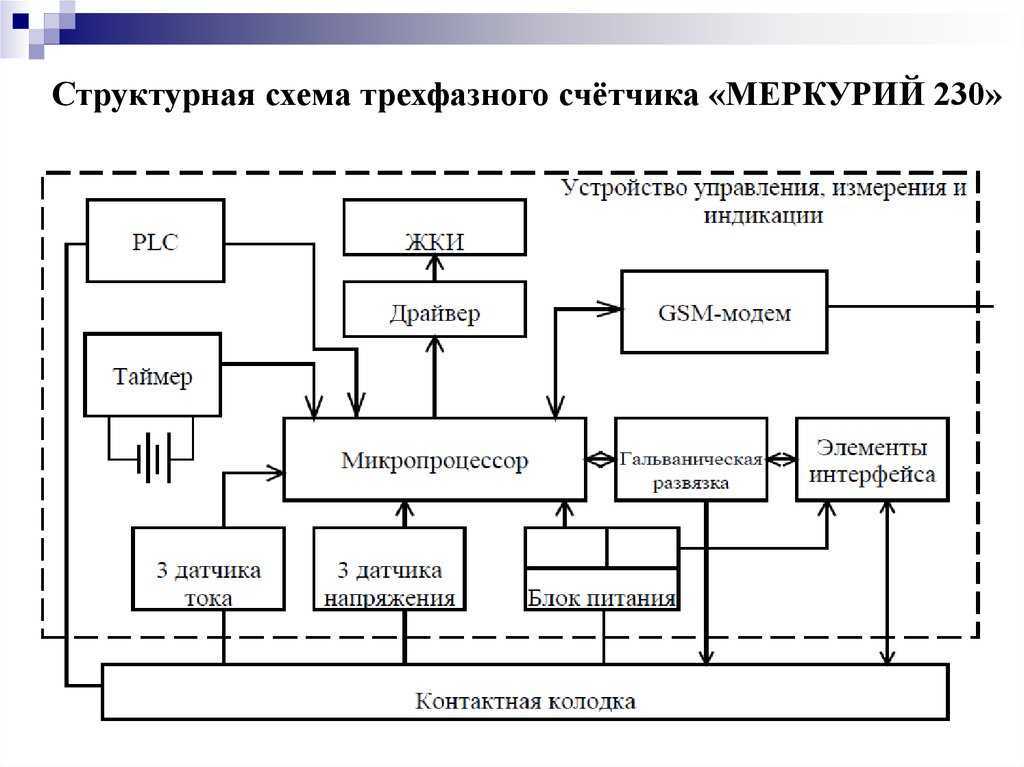

Логические схемы УУ вырабатывают распределенные во времени управляющие, функциональные сигналы. В отличие от УУ с хранимой в памяти последовательностью операций у этих автоматов можно изменить логику работы только путем переделок схем автомата. Типичная структурная схема УУ с жесткой логикой показана на рис.2.3. В состав схемы входят регистр кода операции РгКОП, являющийся частью регистра команд, счетчик тактов СчТ, дешифратор тактов ДшТ и дешифратор КОП — ДшКОП, а также логические схемы ЛС образования управляющих функциональных сигналов.

На СчТ поступают сигналы от блока синхросигналов, и счетчик с каждым сигналом меняет свое состояние. Состояния счетчика представляют номера тактов, изменяющиеся от 1 до n. ДшТ формирует на i-м выходе единичный сигнал при i-м состоянии счетчика, то есть во время i-го такта.

ДшТ формирует на i-м выходе единичный сигнал при i-м состоянии счетчика, то есть во время i-го такта.

ДшКОП вырабатывает единичный сигнал на j-м выходе, если должна исполняться j-я команда. Если на ЛС поступают две лог. «1» с ДшКОП и ДШТ, образуется управляющий сигнал.

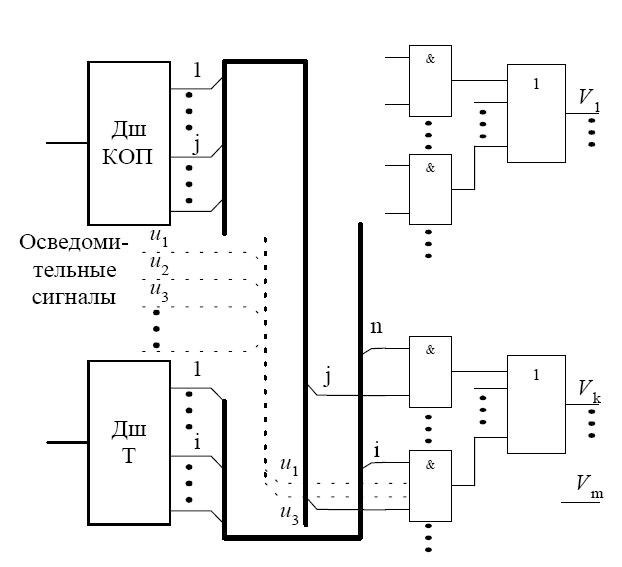

ЛС образования управляющих сигналов для каждой команды возбуждают формирователи управляющих функциональных сигналов для выполнения требуемых в данном такте микроопераций. Принцип построения ЛС образования управляющих сигналов поясняется на рис. 2.4, где показан фрагмент ЛС, обеспечивающей выработку управляющего сигнала Vк в i-м и n-м тактах выполнения j-ой команды. В общем случае значения управляющих сигналов зависят еще и от осведомительных сигналов u, отражающих ход вычислительного процесса — признаки, слово состояния (разд.2.4) и др. Для реализации этих зависимостей элементы, представленные на рис. 2.4, берутся многовходовыми и на них заводятся показанные пунктиром требуемые сигналы логических условий. Если, например, необходимо, чтобы при выполнении j-ой команды управляющий сигнал Vк появлялся в i-м такте только при значениях осведомительных сигналов u1=0 и u3=1, а в n-м такте всегда, то на логическую схему, вырабатывающую Vк,

необходимо подать сигналы u1, и u3 .

Недостатком рассмотренных схем является одинаковое число тактов для всех команд. Это требует выравнивания числа тактов исполнения команд по наиболее «длинной» команде, что ведет к непроизводительным затратам времени. Для устранения этого недостатка ЛС строят с использованием нескольких счетчиков тактов.

Глава 2. Структура и функционирование процессора |

22 |

Однокристальные наборы МП серий К536, К580, К581, К586, К588, К1801 и К1810 имеют УУ с жесткой логикой управления операционным блоком.

|

В операционный блок |

|

|

Блок |

||

|

V 1 |

|

V m |

|

|

синхро- |

|

|

|

|

|

|

сигналов |

|

Формирователи управляющих |

|

|

|||

|

функциональных сигналов |

|

|

|||

ЛС1 |

ЛСm |

Логические схемы образования |

||||

|

управляющих сигналов |

|||||

|

|

|

||||

|

Сложить |

Вычесть |

j |

Такт 1 |

Такт 2 |

i Такт n |

|

|

Дш КОП |

|

Дш тактов |

||

Регистр команд |

|

|

|

|

|

|

Команда |

|

Рг КОП |

|

Сч тактов |

||

|

|

|

||||

Рис. 2.3. Структура УУ с «жесткой» логикой

2.3. Структура УУ с «жесткой» логикой

Дш

КОП

Осведоми- u1 тельные u2 сигналы u3

Дш

T

1 |

& |

|

|

1 |

V 1 |

||

|

|||

|

|

||

j |

|

|

|

|

& |

|

|

|

n |

|

1 |

|

& |

|

j |

1 |

V k |

|

|

|

|

|

i |

u1 |

i |

|

|

& |

V m |

|

|

u3 |

|

|

|

|

|

Рис. 2.4. Схема образования управляющих сигналов в зависимости от осведомительных сигналов

2.4. Схема образования управляющих сигналов в зависимости от осведомительных сигналов

Глава 2. Структура и функционирование процессора |

23 |

Для нормального функционирования МПС недостаточно управляющих сигналов Vi, генерируемых управляющим устройством МП или поступающих из ОЗУ и УВВ, таких как Сброс, Синхронизация, Готовность или Ожидание, Запрос прямого доступа к памяти (ПДП) и Разрешение ПДП, Управление прерыванием, Управление шиной -Чтение, Запись и др. МПС в каждом машинном цикле должна получать более полную информацию о состоянии МП. В условиях «узкого» интерфейса, когда внешних выводов для индикации внутреннего состояния (слова состояния СС) МП недостаточно, эта задача решается с использованием мультиплексирования шины данных и представления внутреннего состояния МП на внешнем по отношению к МП регистре РгСС. Слово состояния процессора полностью описывает состояние процессора в каждый момент и указывает, какие классы операций разрешаются и какие запрещаются, а также состояние всех прерываний. Это слово содержит адрес команды, выполняемой в текущий момент, а в ряде случаев ещё и адрес слова, в котором хранится очередная подлежащая выполнению команда.

Это слово содержит адрес команды, выполняемой в текущий момент, а в ряде случаев ещё и адрес слова, в котором хранится очередная подлежащая выполнению команда.

Процессор в первом такте каждого машинного цикла генерирует на шине данных слово состояния, которое содержит информацию о процессах, происходящих в МП. На рис. 2.5 приведена схема присоединения РгСС к шине данных МП. Сигнал синхронизации Синхро вырабатывается в МП в начале каждого машинного цикла и используется в качестве сигнала, идентифицирующего информацию, представленную в шине данных, как слово состояния. Слово состояния загружается во внешний регистр РгСС под воздействием сигнала Синхро. Сигналы, которые показаны на выходе в данном случае 8-разрядного РгСС используются в качестве управления периферийными устройствами МПС и ОЗУ. Если при реализации любой команды первый машинный цикл есть цикл выборки команды, то машинные циклы во время выполнения собственно команды могут следовать в достаточно произвольном порядке, что определяется кодом команды. Всего МП К580, например, имеет 10 типов машинного цикла и соответственно 10 кодов слова состояния, идентифицирующих эти циклы (рис. 2.5). Каждый разряд слова состояния заводится на соответствующие управляющие входы адаптеров или схем сопряжения с УВВ, определяя тем самым их режим функционирования в соответствии с данным текущим состоянием МП.

Всего МП К580, например, имеет 10 типов машинного цикла и соответственно 10 кодов слова состояния, идентифицирующих эти циклы (рис. 2.5). Каждый разряд слова состояния заводится на соответствующие управляющие входы адаптеров или схем сопряжения с УВВ, определяя тем самым их режим функционирования в соответствии с данным текущим состоянием МП.

Таким образом, в условиях узкого интерфейса управление МПС осуществляется генерацией управляющих воздействий на двух уровнях:

1. На уровне управляющих сигналов Vi микрокоманд по шине управления ШУ собственно МП в каждом такте работы УУ ТТ.

2. На уровне команд путем генерации слова состояния в каждом машинном цикле ТЦ. Выходы РгСС и управляющие линии корпуса МП БИС образуют шину управления ШУ МПС. Для МП К580, например, 12 линий шины системного управления обеспечивают

возможность работы МПС со сложным многофункциональным периферийным оборудованием. При этом использование временного мультиплексирования ШД для вывода на внешний регистр состояния сигналов управления МПС снижает общую производительность системы.

На рис. 2.6 приведен формат слова состояния процессора микроЭВМ Электроника60. Признак (флаг, флажок) Р определяет приоритет процессора с точки зрения допустимости прерывания от внешнего устройства . Если Р=0, то сигнал прерывания принимается к обработке, то есть происходит прерывание текущей программы. При Р=1 прерывание процесса запрещено — замаскировано.

Глава 2. Структура и функционирование процессора |

24 |

D7 — D0 |

|

ШД |

|

|

|

|

|

|

|

|

|

ППР |

|

МП |

|

D7 — D0 |

D |

|

|

ЗП Выв |

|

0 |

На адаптеры |

Стек |

|||

|

Рг слова |

|||||

Синхро |

|

|

либо схемы |

Пост |

||

состо- |

|

|

||||

(Прием) |

|

|

сопряж. |

Выв |

||

яния |

|

|

||||

|

|

D |

|

с УУ |

М1 |

|

j1 |

|

Рг СС |

7 |

|||

|

|

|

|

Вв |

||

|

|

|

|

|

|

Пам |

ТТ1 |

ТТ2 |

|

|

|

|

|

|

|

j1( ТИ1) |

|

|

|

МП |

|

|

j2( ТИ2) |

|

|

|

|

|

|

разрядовНомера |

|

|

состоянииоИнформация |

|

|

|

Синхро |

|

|

||

|

|

|

|

|

|

|

|

|

ШД |

|

|

|

|

|

|

РС |

|

|

|

|

№слова состояния процессора

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

управляющихСистема |

данномвсигналовТц |

|

|

|

|

|

|

|

|

|

||||

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

||

|

|

|

||||||||||

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

||||||||||

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

||||||||||

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

||||||||||

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

||||||||||

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

||||||||||

1 |

1 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

|

|

|

|

|

|

|

|||||||||

Выборка команды |

Чтение из памяти |

Запись в память |

Чтение из стека |

Запись в стек |

Чтение из УВВ |

Запись в УВВ |

Разрешение прерывания |

Разрешение останова |

Разреш. |

|

|

|

|

Тип маш. цикла Т Цi |

|

|

|

|

|||||||

Рис. 2.5. Слово состояния процессора типа К580

|

|

P |

|

|

T |

|

N |

Z |

V |

C |

|

|

|

|

|

|

|

|

|

|

|

15 разряд |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

Рис. |

|

|

|||||||

Признак Т — признак « ловушки», будучи установлен, то есть при Т=1, задает прерывание программы сразу после выполнения текущей команды и переход на специальную программу, называемую «ловушкой» .Этот признак используется главным образом на этапе отладки программы и ее трассировки.

Признаки N, Z, V, С представляют собой коды, или признаки условий, формируемые в результате исполнения команд и запоминаемые в разрядах 3-0 соответственно. Эти признаки устанавливаются в следующих случаях: N=1, если результат выполнения команды отрицательный; Z=1, если результат равен нулю; V=1, если произошло арифметическое переполнение; С= 1, если произошел перенос из самого старшего разряда результата или если при сдвиге числа вправо (влево) была выдвинута единица самого младшего (старшего) разряда.

Если ситуация установки кода условия не имеет места, то соответствующий код принимает значение 0. Подчеркнем, что на коды условий воздействуют только некоторые, главным образом арифметические и логические, команды. При выполнении всех прочих команд коды условий не изменяются, какими бы они ни были. Неиспользуемые поля регистра РгСС — разряды 5, 6 и 8-15 не используются и оставлены для будущих расширений структуры МПС.

Подчеркнем, что на коды условий воздействуют только некоторые, главным образом арифметические и логические, команды. При выполнении всех прочих команд коды условий не изменяются, какими бы они ни были. Неиспользуемые поля регистра РгСС — разряды 5, 6 и 8-15 не используются и оставлены для будущих расширений структуры МПС.

Устройства управления с жесткой логикой — Энциклопедия современных знаний

Обычно тип микропрограммного автомата (МПА), формирующего сигналы управления, определяет название всего УУ. Так, УУ с жесткой логикой управления имеет в своем составе МПА с жесткой (аппаратной) логикой. При создании такого МПА выходные сигналы управления реализуются за счет однажды соединенных между собой логических схем.

Непосредственно по графу микроалгоритма может быть построено УУ на линиях задержки сигналов. При этом операторным вершинам графа заменяются линиями задержки, величина которых соответствует длительности инициируемой в данной вершине микрооперации. Условные вершины, проверяющие логические условия (флаги) заменяются элементами И, а объединения ребер графа — элементами ИЛИ. Применению подобного подхода препятствует низкая технологичность линий задержки при использовании интегральных технологий.

Применению подобного подхода препятствует низкая технологичность линий задержки при использовании интегральных технологий.

Типичная структура микропрограммного автомата с жесткой логикой управления показана на рис. 1.

Исходной информацией для УУ служат: содержимое регистра команды, флаги, тактовые импульсы и сигналы, поступающие с шины управления.

Рис. 1. Микропрограммный автомат с жесткой логикой

Код операции, хранящийся в РК, используется для определения того, какие СУ и в какой последовательности должны формироваться, при этом, с целью упрощения логики управления, желательно иметь в УУ отдельный логический сигнал для каждого кода операции (I0, I1,…, Ik) . Это может быть реализовано с помощью дешифратора. Дешифратор кода операции преобразует j-й код операции, поступающей из регистра команды (РК), в единичный сигнал на j-м выходе.

Машинный цикл выполнения любой команды состоит из нескольких тактов. Сигналы управления, по которым выполняется каждая микрооперация, должны вырабатываться в строго определенные моменты времени, поэтому все СУ «привязаны» к импульсам синхронизации (СИ), формируемым узлом синхроимпульсов. Период СИ должен быть достаточным для того, чтобы сигналы успели распространиться по трактам данных и другим цепям. Каждый СУ ассоциируется с одним из тактовых периодов в рамках машинного цикла. Узел синхроимпульсов после завершения очередного такта работы добавляет к содержимому счетчика тактов единицу. К выходам счетчика подключен дешифратор тактов, с которого и снимаются сигналы тактовых периодов: T1…, Tn. В i-м состоянии счетчика тактов, то есть во время i-го такта, дешифратор тактов вырабатывает единичный сигнал на своем i-м выходе. При такой организации в УУ должна быть предусмотрена обратная связь, с помощью которой по окончании цикла выполнения команды счетчик тактов опять устанавливается в состояние T1.

Период СИ должен быть достаточным для того, чтобы сигналы успели распространиться по трактам данных и другим цепям. Каждый СУ ассоциируется с одним из тактовых периодов в рамках машинного цикла. Узел синхроимпульсов после завершения очередного такта работы добавляет к содержимому счетчика тактов единицу. К выходам счетчика подключен дешифратор тактов, с которого и снимаются сигналы тактовых периодов: T1…, Tn. В i-м состоянии счетчика тактов, то есть во время i-го такта, дешифратор тактов вырабатывает единичный сигнал на своем i-м выходе. При такой организации в УУ должна быть предусмотрена обратная связь, с помощью которой по окончании цикла выполнения команды счетчик тактов опять устанавливается в состояние T1.

Дополнительным фактором, влияющим на последовательность формирования СУ, являются состояние осведомительных сигналов (флагов), отражающих ход вычислений, и сигналы с шины управления. Эта информация также поступает на вход УУ, причем каждая линия здесь рассматривается независимо от остальных. Принцип построения логических схем формирования управляющих сигналов поясняется на рис. 2. Здесь показан фрагмент схемы, обеспечивающей выработку управляющего сигнала Сk в i-м и s-м тактах выполнения команды с кодом операции j, причем сигнал Сk появляется в i-м такте только при значениях осведомительных сигналов x1 = 1 x2 = 1, a s-м такте всегда.

Принцип построения логических схем формирования управляющих сигналов поясняется на рис. 2. Здесь показан фрагмент схемы, обеспечивающей выработку управляющего сигнала Сk в i-м и s-м тактах выполнения команды с кодом операции j, причем сигнал Сk появляется в i-м такте только при значениях осведомительных сигналов x1 = 1 x2 = 1, a s-м такте всегда.

Рис. 2. Фрагмент схемы формирования сигналов управления.

Процесс синтеза схемы МПА с жесткой логикой называется структурным синтезом и разделяется на следующие этапы:

- выбор типа логических и запоминающих элементов;

- кодирование состояний автомата;

- синтез комбинационной схемы, формирующей выходные сигналы.

Чтобы определить способ реализации МПА с жесткой логикой, необходимо описать внутреннюю логику УУ, формирующую выходные сигналы управления, как булеву функцию входных сигналов.

Как известно, задача синтеза автомата сводится к синтезу комбинационной схемы путем построения системы логических функций с последующей их минимизацией.

Comprehensive iPhone XS China Aftermarket Screens Comparison Test

Похожие статьи.

-

Устройства микропрограммного управления

-

Управление файлами и внешними устройствами

-

Программное управление внешними устройствами

-

Проектирование блока управления цифровым замком.

программных ПЛК против аппаратных ПЛК — какое будущее?

Программируемые логические контроллеры (ПЛК) традиционно основывались на аппаратных средствах. Рожденные автомобильной промышленностью в конце 1960-х годов, они были такой же частью производственных линий, как и любое другое физическое оборудование.

В последнее время, условно говоря, появились программные ПЛК, что вызвало вопрос; что лучше подходит для обеспечения будущего производства, аппаратный ПЛК или программный ПЛК?

Что такое программируемый логический контроллер?

ПЛК — это компьютер, специально разработанный для управления различными производственными процессами, такими как сборочные линии, производственные роботы, автоматизированное оборудование и многое другое.

Как правило, они изготавливаются по назначению и рассчитаны на работу в промышленных условиях окружающей среды, включая расширенные диапазоны температур, большое количество электрических помех, а также обладают устойчивостью к ударам и вибрации.

Первый ПЛК был создан для автомобильной промышленности в 1968 и способствовала дальнейшей автоматизации производства. Они в значительной степени заменили релейные логические системы, которые с трудом поддавались автоматизации за пределами выделенных сред с замкнутым контуром. Они также боролись с надежностью, так как если бы даже один провод был не на месте, весь производственный процесс мог бы остановиться. С другой стороны, ПЛК

были более модульными, надежными и компактными. Они обеспечивали масштабируемость, расширялись за счет дополнительных модулей ввода-вывода (IO) и лучше переносили более экстремальные промышленные условия.

Как программируются ПЛК?

ПЛК обычно программируются с использованием релейной логики..jpg) Лестничная логика изначально была разработана как средство документирования конструкции релейных стоек; электрические реле, подключенные в определенных конфигурациях.

Лестничная логика изначально была разработана как средство документирования конструкции релейных стоек; электрические реле, подключенные в определенных конфигурациях.

Он лег в основу языка программирования, который точно отражал реальную работу электрических реле в физическом оборудовании, таком как ПЛК. Поскольку этот язык вычислений очень похож на физическую работу этих устройств, он имеет ряд преимуществ и недостатков.

Это позволяет инженерам по техническому обслуживанию легче устранять неполадки, требуя меньше технических знаний. Например, инженерам не нужно разбираться в тонкостях специализированных языков программирования.

Однако это ограничивает возможности процессора. Лестничная логика ограничена физическими ограничениями описываемой системы, сводя к минимуму степень адаптивности, на которую способна система.

В чем разница между программным ПЛК и аппаратным ПЛК?

Программный ПЛК определяется как программное обеспечение, которое способно выполнять функции компонента ЦП в ПЛК, но может существовать на аппаратном уровне вместе с другими частями программного обеспечения. Аппаратный ПЛК — это конкретная часть оборудования, которая действует исключительно как ПЛК, а его функции ЦП выполняются на выделенном устройстве.

Аппаратный ПЛК — это конкретная часть оборудования, которая действует исключительно как ПЛК, а его функции ЦП выполняются на выделенном устройстве.

Главное, на что нужно обратить внимание, это где находится ЦП, потому что ПЛК — это такие разные вещи, что определение их типа по их входам (датчики) или выходам (приводы) очень быстро превратится в беспорядок. Итак, если ЦП существует как часть ПЛК, это жесткий ПЛК. Если он существует на отдельном компьютере, это программный ПЛК.

Зачем использовать жесткие ПЛК?

Каждый производственный процесс сложен. Даже в самых простых процессах потребуются сотни или тысячи движущихся частей, и все они должны работать согласованно для создания продуктов в масштабе.

Наличие выделенного ПЛК здесь имеет очевидные преимущества. У вас есть одна система для программирования, обслуживания и понимания. Устранение неполадок ограничено ограниченным пространством, а обновления зависят только от самой системы, а не от какого-либо другого программного обеспечения, загруженного вместе с ПЛК.

Им также помогают специальные знания. Технические специалисты, поддерживающие аппаратные ПЛК, имеют специальный опыт, и эти системы имеют за собой давние традиции, что делает их более разумными в обслуживании.

Зачем переходить на программные ПЛК?

Учитывая предыдущие абзацы, вы можете подумать, что переход на программные ПЛК — это плохо. Но, как и в случае любого технического прогресса, в этой истории есть две стороны. Программные ПЛК могут делать то, что не могут аппаратные ПЛК, и некоторые из преимуществ аппаратных ПЛК также могут создавать проблемы, которые могут решить программные ПЛК.

Переходя в мир Индустрии 4.0, мы понимаем, что гибкость является ключевым компонентом прогресса. Функциональная совместимость машин требует таких концепций, как программируемые ПЛК, в которых потенциальные настройки для любой производственной операции бесконечно изменчивы.

На фабрике будущего функциональные возможности ЦП могут существовать в облаке, что позволит одновременно работать в нескольких производственных центрах. Это возлагает ответственность за ПЛК на мир ИТ, искусственного интеллекта и облачных вычислений.

Это возлагает ответственность за ПЛК на мир ИТ, искусственного интеллекта и облачных вычислений.

Важно помнить, что в программных ПЛК ЦП существуют отдельно от остальной части ПЛК. С этим разделением приходят некоторые действительно интересные преимущества.

Сетевые системы

Аппаратные ПЛК не всегда могут быть жестко подключены, но они всегда будут ограничены в том, насколько хорошо они могут работать в сети. Поскольку это специализированное оборудование, любой, кто устанавливает их, ограничен возможностями конкретного ПЛК. Улучшения могут быть сделаны, но только в рамках того, что предоставил их поставщик.

Теоретически программный ПЛК может иметь любое количество датчиков и приводов, объединенных в сеть. Программное обеспечение, управляющее ПЛК, может быть переработано в цифровом, а не физическом виде, чтобы позволить управлять новыми устройствами в установленной системе.

Модульность

Продолжая эту идею, поскольку программные ПЛК могут быть переработаны на программном уровне, они могут бесконечно адаптироваться к изменениям в оборудовании. Жесткий ПЛК будет ограничен доступным ему аппаратным обеспечением, чего не может сделать программный ПЛК.

Жесткий ПЛК будет ограничен доступным ему аппаратным обеспечением, чего не может сделать программный ПЛК.

Диверсификация поддержки

Со специфичностью возникают определенные проблемы. Системы, созданные по индивидуальному заказу, могут быть идеально спроектированы для включения определенных процессов, но в то же время их внедрение и обслуживание могут быть более дорогостоящими.

Если в вашем жестком ПЛК возникла проблема, то ограниченное число людей, которым вы можете позвонить для ее устранения. Что еще хуже, если по какой-либо причине поддержка вашего аппаратного ПЛК будет прекращена, вы, возможно, не сможете просто адаптировать и обновить его, возможно, вы подумываете об установке совершенно нового ПЛК.

Задел на будущее

Жесткий ПЛК также может препятствовать адаптации операции. Если ваш красиво спроектированный, отлично реализованный аппаратный ПЛК работает в строгих рамках, вы не сможете извлечь выгоду из тенденций в отрасли, адаптируя свое производство к потребностям меняющейся клиентской базы.

Благодаря программному ПЛК, включающему функции ЦП на отдельном ПК, можно расширять и адаптировать по мере развития технологии как «мозги» операции, так и устройства ввода и вывода.

В мире Индустрии 4.0 объекты, полные устройств Интернета вещей (IoT), могут быть связаны между собой, эти объекты могут быть объединены в сеть, эта сеть может существовать в облаке, и все это управляется ПЛК, который существует в цифровом виде на всех объектах, сети, нации и континенты. Небо действительно предел.

Что лучше: программный ПЛК или аппаратный ПЛК?

В конце концов, производство всегда будет нуждаться в чем-то вроде ПЛК, позволяющем эффективно производить большое количество вещей. Жесткие ПЛК и программные ПЛК имеют свои преимущества и недостатки, и какой из них выберет ваша компания, зависит от ваших бизнес-целей, методологий и прогнозов на будущее.

Жесткие ПЛК имеют смысл во многих ситуациях, но для реализации достижений Индустрии 4.0 могут потребоваться программные ПЛК. Потенциальный рост, предлагаемый программным ПЛК, необходимо учитывать при принятии решений.

Потенциальный рост, предлагаемый программным ПЛК, необходимо учитывать при принятии решений.

Rad-Hard Logic ICs — STMicroelectronics

- RHFOSC04

Rad-Hard, драйвер кварцевого генератора и делитель

- RHFAHC00

Rad-Hard, четырехъядерный высокоскоростной вентиль NAND

- 0002 Rad-Hard 16-битный трансивер, двунаправленный сдвиг уровня от 1,8 В до 3,3 В

- 54VCXh262244

Rad-Hard 16-битный трансивер без инвертирования

- 54VCXh262374

Rad-Hard 3-государственное

- 54VCXH262373

RAD-HARD 16-битная защелка D-Type 3-State

- 54VCXHR162245

RAD-Hard 16-битный трансис-транс неверный с резистором

- 54VCX 26245245245245245245245245245245245245245245245245245245454545454545454545454545454545454545454545245454545452454545454524-hard 54-битный. -состояние Не инвертирующий

- HCC4072B

RAD-Hard Dual 4-входной или ворот

- HCC4071B

RAD-Hard QUAD 2-й или ворота

- HCC4073B

RAD-HARD TPROU двойной 4-ступенчатый статический сдвиговый регистр

- HCC4014B

Rad-hard 8-ступенчатый статический синхронный сдвиговый регистр

- HCC4081B

Rad-hard quad 2-input AND gate

- HCC4012B-divider Rad-hard 9000 счетчик/делитель0003

- HCC4093B

Rad-hard quad 2-input NAND Schmitt trigger

- HCC4075B

Rad-hard triple 3-input OR gate

- HCC4013B

Rad-hard dual D Flip-Flop

- HCC4077B

Rad-hard Четверной эксклюзивный логический элемент NOR

- HCC4051B

Rad-hard одиночный 8-канальный аналоговый мультиплексор/демультиплексор

- HCC4050B

Rad-жесткий шестигранный неинвертирующий буфер/преобразователь

- Rad-hard m/channel m/demux 900 другой аналоговый m/demux

- HCC4050B

демультиплексор

- HCC4556B

Rad-hard двойной выход декодера/демультиплексора «1 из 4», низкий уровень

- HCC4555B

Rad-hard двойной выход декодера/демультиплексора «1 из 4», высокий уровень NOR gate

- HCC4068B

Rad-hard 8-input NAND/AND gate

- HCC4067B

Rad-hard single 16-channel analog mux/demux

- HCC4070B

Rad-hard quad exclusive OR gate

- HCC4069UB

Радиационный шестигранный инвертор

- HCC4060B

RAD-Hard 14-стадный счетчик/див.

Счетверенный двухсторонний переключатель Rad-hard

- HCC4063B

Rad-hard 4-битный компаратор величин

- HCC4034B

Rad-hard 8-ступенчатый статический двунаправленный шинный регистр

- HCC4030B

Rad-hard четырехъядерный вентиль исключающего ИЛИ

- HCC4040B

Rad-hard 12-этапный двоичный/пульсирующий счетчик

- HCC4001B

- HCC4046B

Микромощная фазовая синхронизация Rad-hard

- HCC4520B

Rad-hard двойной двоичный реверсивный счетчик

- HCC4049UB

Rad-hard шестнадцатеричный инвертирующий буфер/преобразователь 6 8093 9003

083 HCC4047B

Rad-hard monostable/astable multivibrator

- HCC4538B

Rad-hard dual precision monostable multivibrator

- HCC4041UB

Rad-hard quad true/complement buffer

- HCC4514B

Rad-hard 4-bit Latch / 4- выход декодера до 16 строк, высокий

- HCC4512B

Rad-hard 8-канальный выбор данных.

с 3-позиционным выходом

с 3-позиционным выходом - HCC4516B

Rad-hard предустановленный 4-битный двоичный прямой/обратный счетчик

- HCC4043B

Rad-hard quad 3-state NOR R/S latch

- HCC4022B

Rad-hard divide-by-8 counter/divider

- HCC4019B

Rad-hard quad AND/OR select gate

- HCC4094B

Rad-hard 8-ступенчатый шинный регистр сдвига и сохранения

- HCC4018B

Rad-hard предустановленный счетчик деления на N

- HCC4021B

Rad-hard 8-ступенчатый статический сдвиговый регистр

-9000B - HCC 40086 жесткий 14-ступенчатый двоичный/пульсирующий счетчик

- HCC4098B

Rad-hard dual monostable multivibrator

- HCC4027B

Rad-hard dual J-K master-slave Flip-Flop

- HCC40109B

Rad-hard quad low-to-high voltage level shifter

- HCC4029B

Rad -Hard Presettable Up/Down counter

- HCC4028B

Rad-hard BCD-to-decimal decoder

- HCC40174B

Rad-Hard Hex D Flip-Flop

- downtable 9 HCC40103B-900 двоичный предустановленный счетчик HCC40103B-

03

- HCC4024B

RAD-Hard 7-ступенчатая бинарная/волновая счетчик

- HCC40106B

RAD-HARD SCHMITT TRIGGE -Input AND Gate

- 54ACT10

Rad-Hard Triple 3-Input NAND Gate

- 54ACT74

Rad-Hard Двойной триггер D-типа с Preset & Clear

- 54AC04-Hardxx20003

- 54ACT174

RAD-Hard Hex D-Type Flip Flop с прозрачным

- 54ACT373

RAD-Hard Octal D-Type Latch 3-State

- 54AC08

RAD-HARD Квад 2-в-вульдон и заварной ряд

- 54AC08

RAD-HARD Квад 2-в-вульдон и заварной ряд

- 54AC08

RAD-HARD Квад 2-в-вульдон и заварной ряд

- 54AC08

RAD-HARD Кварта 54ACT191

Rad-Hard 4 Bit Synchronous Binary Up/Down Counter

- 54AC521

Rad-Hard 8-bit Comparator with Enable

- 54AC11

Rad-Hard Triple 3-Input AND Gate

- 54AC138

Rad-Hard 3 на 8-линейный инвертор декодера

- 54ACT157

RAD-Hard Quad 2-канальный мультиплексор

- 54AC174

RAD-Hard Hex D-Type Flip-Flop с прозрачным буфером Octal Octal Octal Bus 3-State

- 33333333333 54-й.

-Hard Octal Flip Flop с прозрачным

-Hard Octal Flip Flop с прозрачным - 54ACT240

RAD-Hard Octal Buffer 3-State Inverter

- 54AC157

RAD-Hard Quad 2-Chann Защелка D-типа, 3 состояния,

- 54AC16374

Rad-Hard 16-bit D-Type Flip Flop 3-state

- 54AC14

Rad-Hard Hex Schmitt Inverter

- 54AC244

Rad-Hard Octal Bus Buffer 3-state

- 54ACT244

Rad — Hard Octal Bus Buffer 3-state

- 54AC245

Rad-Hard Octal Bus Transceiver 3-state

- 54AC16244

Rad-hard 16-bit буфер 3-state

- 900AC16 . Очистить

- 54AC374

Rad-Hard Octal D-Type Flip-Flop 3-state

- 54AC10

Rad-Hard Triple 3-Input NAND Gate

- 54ACT151

Rad-Hard 8-Channel Multiplexer

- 54ACT11

Rad -Хард Тройной 3-Вйра и Врата

- 54AC16245

RAD-HARD 16-битный приемопередатчик 3-государственный

- 54ACT16244

RAD-Hard 16-битный буфер 3-state

- 54AC151

Rad-Hard 8-Cannel Multiplecmer

- 54AC151

Rad-Hard 8-Cannel Multiplecmer

- 54AC151

- 54AC14A

Rad-hard hex Schmitt inverter low power

- 54ACT32

Rad-Hard Quad 2-Input OR Gate

- 54ACT14

Rad-Hard Hex Schmitt Inverter

- 54ACT86

Rad-Hard Quad exclusive OR

- 54AC191

Rad-Hard 4-битный синхронный двоичный счетчик вверх/вниз

- 54AC541

Rad-Hard Octal Bus Buffer 3-state

- 54ACT574

Rad-Hard Octal-Flop-state 3 Flip Octal D-Type0003

- 54ACT374

Rad-Hard Octal D-Type Flip-Flop с 3 состояниями

- 54AC74

Rad-Hard Dual D-Flip-Flop типа Preset & Clear

- 54ACT245 Rad-Hard3 Transceiver Octal-Hard3 Bus состояние

- 54AC373

Rad-Hard Octal D-Type Latch 3-state

- 54AC574

Rad-Hard Octal D-Type Flip-Flop 3-state

- 54AC32-Hard0 Gate 3 Quad-OR

- 54ACT16245

Rad-Hard 16-разрядный буфер с 3 состояниями

- 54AC273

Rad-Hard Octal D-Type Flip Flop с Clear

- 54ACT16373

Rad-Hard 16-разрядная защелка D-типа с 3 состояниями 5 4AC2 2

-

Rad-Hard Quad 2-nput Nor Gate

- 54ACT16374

RAD-Hard 16-битный шлепанщик D-Type 3-State

- 54AC00

RAD-Hard Quad 2-nand Gate Gate

- 54AC25525

RAD-nand Gate Gate

- 54AC25525

RAD RAD-nand Gate

- 54AC25525

RAD RAD-nand Gate

- 54AC25525

RAD RAD-nand Gate

- 54AC25525

RAD RAD-nand Gate Драйвер жестких часов с перекосом от 1 до 8

- 54AC540

Rad-Hard Octal Buffer/Line Driver 3-State

- 54AC164245

Rad-Hard 16-bit transceiver, 3.

3 to 5 V bidirectional level shifter transceiver

3 to 5 V bidirectional level shifter transceiver - 54ACT04

Rad-Hard Hex Inverter

- 54ACT161

Rad-Hard Synchronous Binary Counter с Async. Прозрачный

- 54ACT02

Rad-Hard Quad с 2 входами NOR Gate

- 54AC86

Rad-Hard Quad с эксклюзивным ИЛИ

- 54ACT139

Rad-Hard Dual 2 to 4 Line Decoder/Demultiplexer

- 54ACT00

Rad-Hard Quad 2-Input NAND Gate

- 54AC139

Rad-Hard Dual 2 to 4 Line Decoder/Demultiplexer

- 54AC240

Rad-Hard Октальный автобусный буфер 3-государственный инвертор

- M54HC10

RAD-Hard Triple 3-й входной GATE

- M54HC4514

RAD-Hard 4-16 Line Decoder 4-Bit 40003

- M54HC85

RAD-HARD MAGDAT

- M54HC11

Rad-Hard Triple 3-Input AND Gate

- M54HC00

Rad-Hard Quad 2-Input NAND Gate

- M54HC109

Rad-Hard Dual J-K Flip-Flop With Preset & Clear

- M54HC125

Rad-Hard Quad Bus Buffer 3-State

- M54HC148

Rad-Hard 8-to-3 Line Priority Encoder

- M54HC123

Rad-Hard Dual Retrigg.

Моностабильный мультивибратор с прозрачным

Моностабильный мультивибратор с прозрачным - M54HC191

Rad-Hard 4-bit Synchronous Binary Up/Down Counter

- M54HC14

Rad-Hard Hex Schmitt Inverter

- M54HC374

Rad-Hard Octal D-Type Flip-Flop 3-State

- M54HC151

Rad- Жесткий 8-канальный мультиплексор

- M54HC373

RAD-Hard Octal D-тип защелки -Состояние

- M54HCT244

Rad-Hard Octal Bus Buffer 3-State

- M54HC257

Rad-Hard Quad 2-Channel Multiplexer 3-State

- M54HCT245

Rad-Hard Octal Bus Transceiver 3-State

- M54HC157

Rad -Hard Quad 2-канальный мультиплексор

- M54HC160

Rad-Hard Синхронный счетчик декад с асинхронным. Прозрачный

- M54HC273

Rad-Hard Octal D-Type Flip-Flop с прозрачным

- M54HC132

RAD-HARD QUAD 2-INPUT SCHMITT NAND GATE

- M54HC237

RAD-HARD 3-8 LINE DECODE Жесткий 8-битный регистр-защелка/сдвиг

- M54HC04

Rad-Hard Hex Inverter

- M54HC161

Rad-Hard Синхронный двоичный счетчик с асинхронным.

прерыв. во время останова

прерыв. во время останова 2.6. Формат слова состояния МП микроЭВМ типа Электроника-60

2.6. Формат слова состояния МП микроЭВМ типа Электроника-60