Что такое Verilog и для чего он используется. Какие преимущества дает Verilog при разработке цифровых схем. Как освоить Verilog и начать применять его на практике.

Что представляет собой язык Verilog

Verilog — это язык описания аппаратуры (HDL), который позволяет описывать и моделировать цифровые системы, электронные схемы, микропроцессоры и другие аппаратные компоненты. Он был разработан в 1984 году компанией Gateway Design Automation и быстро стал одним из основных инструментов для проектирования интегральных схем.

Ключевые особенности Verilog:

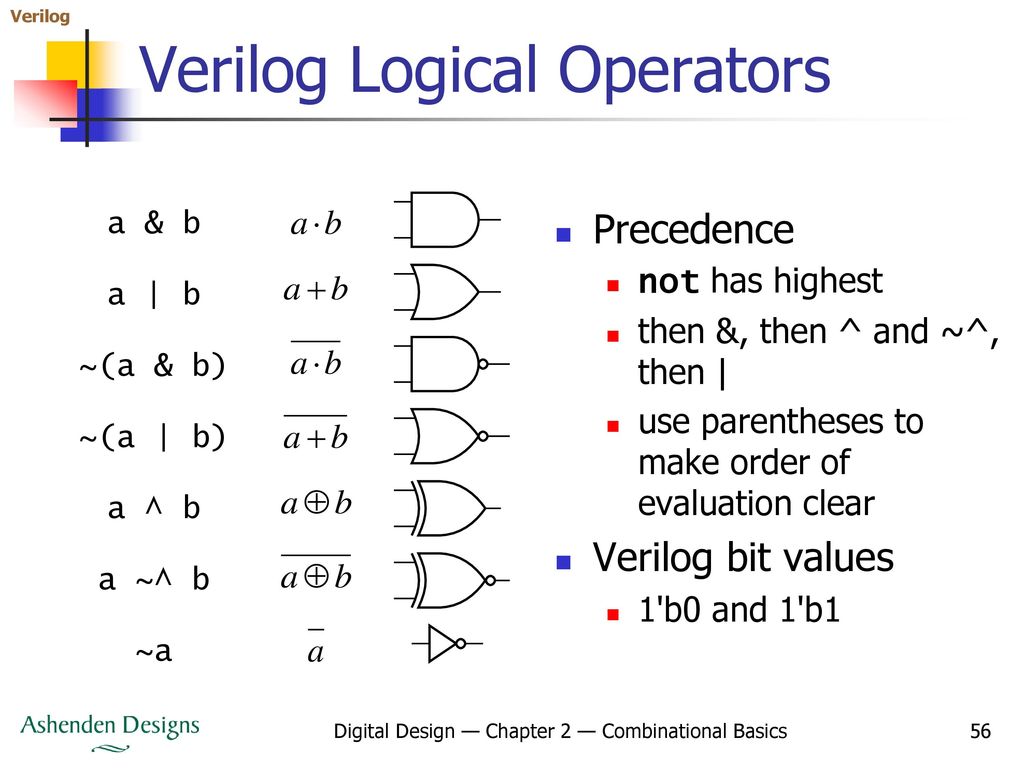

- Позволяет описывать аппаратуру на разных уровнях абстракции — от транзисторного до поведенческого

- Имеет синтаксис, похожий на язык C, что упрощает его освоение программистам

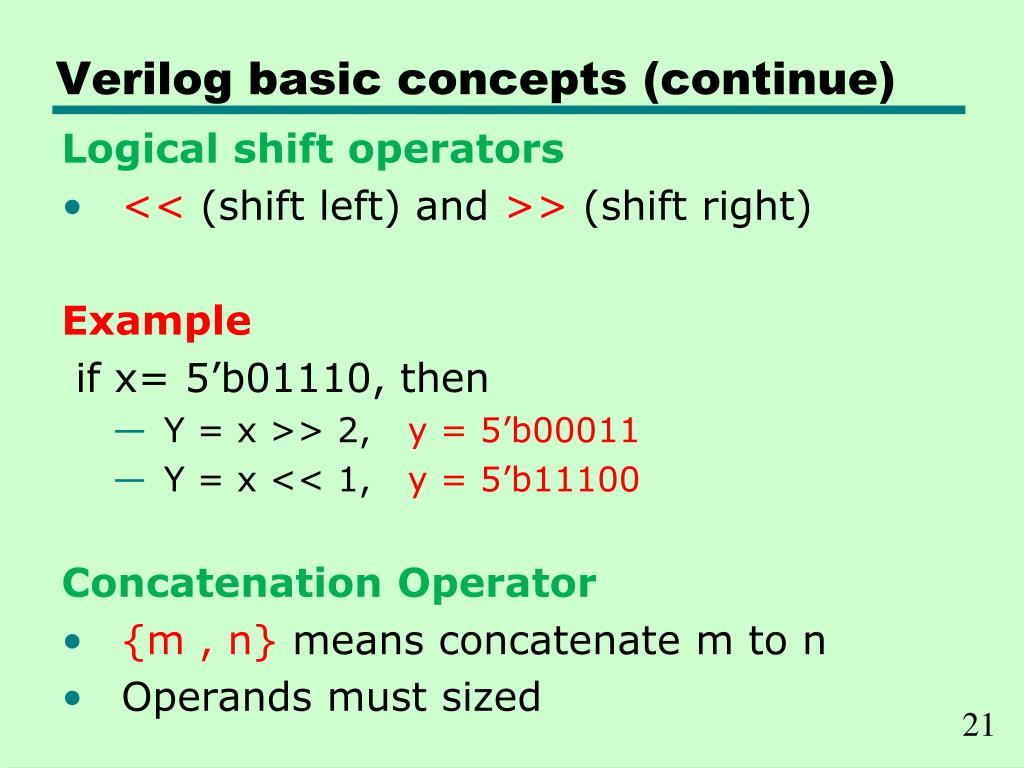

- Поддерживает параллельное и последовательное выполнение операторов

- Предоставляет средства для временного моделирования и верификации проектов

- Широко применяется в промышленности для разработки ASIC и FPGA

Области применения Verilog

Где используется язык Verilog в современной электронике и разработке цифровых систем?

- Проектирование интегральных схем специального назначения (ASIC)

- Разработка систем на программируемых логических интегральных схемах (FPGA)

- Моделирование и верификация цифровых схем

- Синтез логических схем из высокоуровневого описания

- Создание прототипов сложных вычислительных систем

- Разработка встраиваемых систем и систем на кристалле (SoC)

Таким образом, Verilog находит широкое применение на всех этапах проектирования современной цифровой электроники — от концепции до реализации в кремнии.

Преимущества использования Verilog

Почему Verilog стал одним из основных языков для разработки цифровых схем? Рассмотрим его ключевые преимущества:

- Стандартизация — Verilog является открытым стандартом IEEE, что обеспечивает его совместимость и переносимость

- Простота изучения — синтаксис похож на C, что упрощает освоение языка программистам

- Гибкость — позволяет описывать системы на разных уровнях абстракции

- Эффективность — обеспечивает компактное и производительное описание аппаратуры

- Поддержка инструментов — широкая экосистема средств разработки и верификации

- Масштабируемость — подходит как для небольших, так и для крупных проектов

Эти преимущества делают Verilog мощным инструментом в руках разработчиков цифровых систем, позволяя создавать сложные проекты быстро и эффективно.

Основные концепции языка Verilog

Для понимания Verilog важно разобраться в его ключевых концепциях и элементах. Рассмотрим основные из них:

Модули

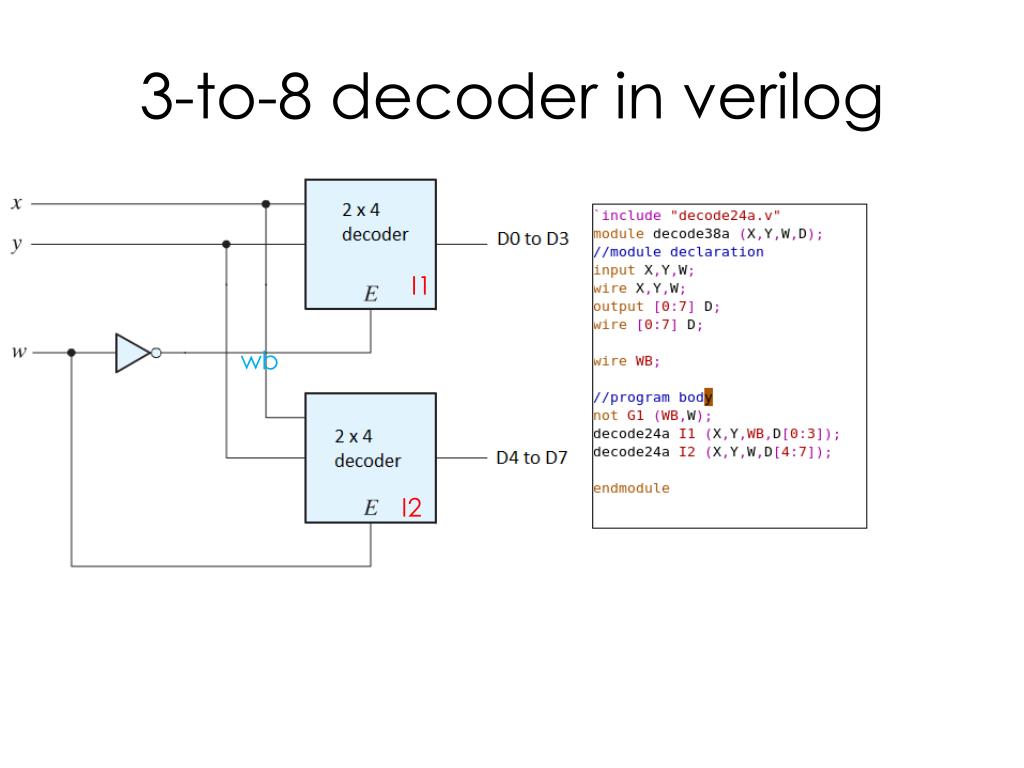

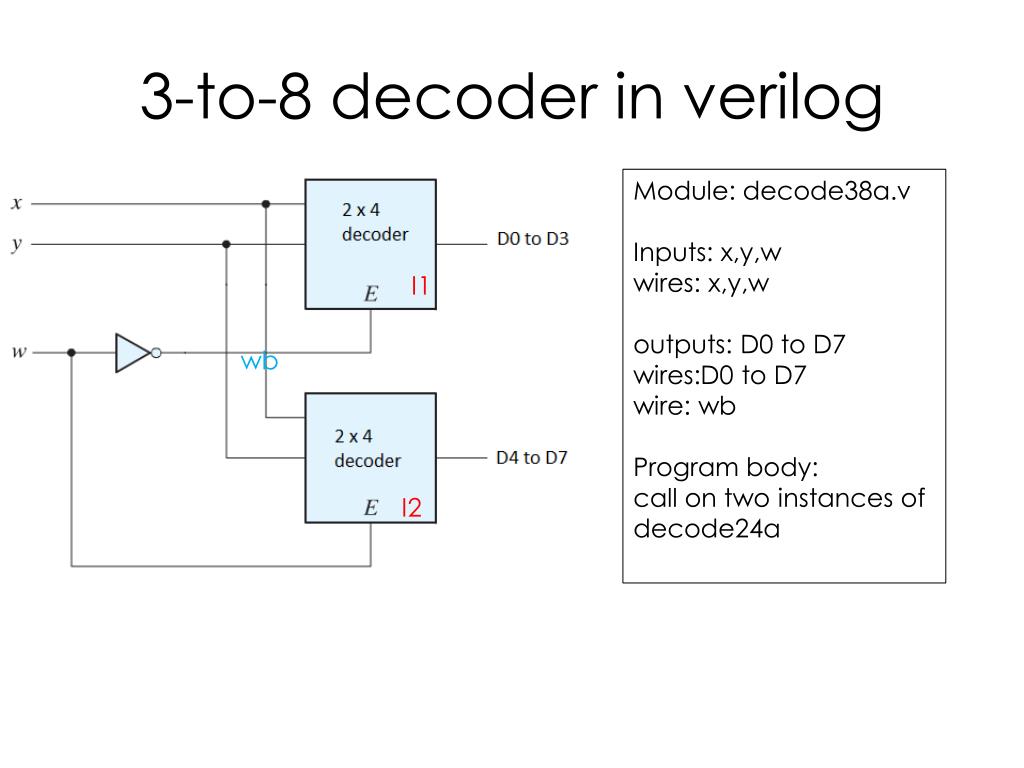

Модуль — это базовый строительный блок в Verilog. Он представляет собой функциональную единицу схемы с определенными входами и выходами. Модули могут содержать описание поведения схемы или ее структуры из более мелких компонентов.

Порты

Порты определяют интерфейс модуля — его входы, выходы и двунаправленные линии. Они позволяют соединять модули между собой и с внешним миром.

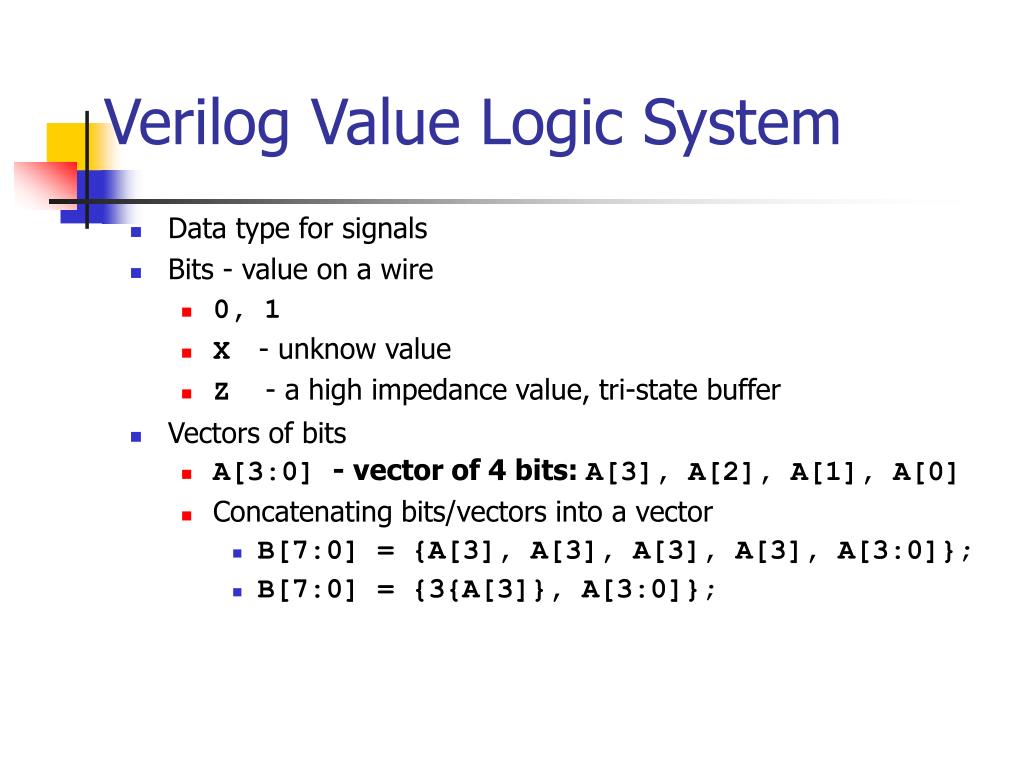

Сигналы и переменные

В Verilog используются различные типы сигналов и переменных для представления данных:

- wire — для моделирования физических соединений

- reg — для хранения значений в процедурных блоках

- integer, real — для целочисленных и вещественных вычислений

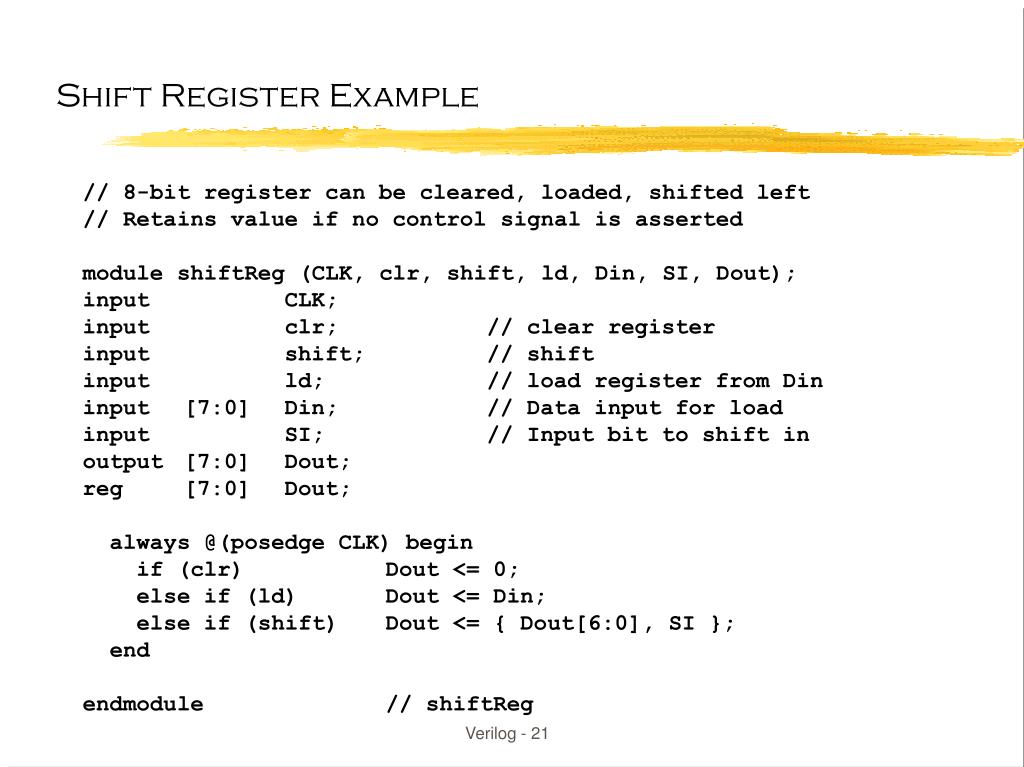

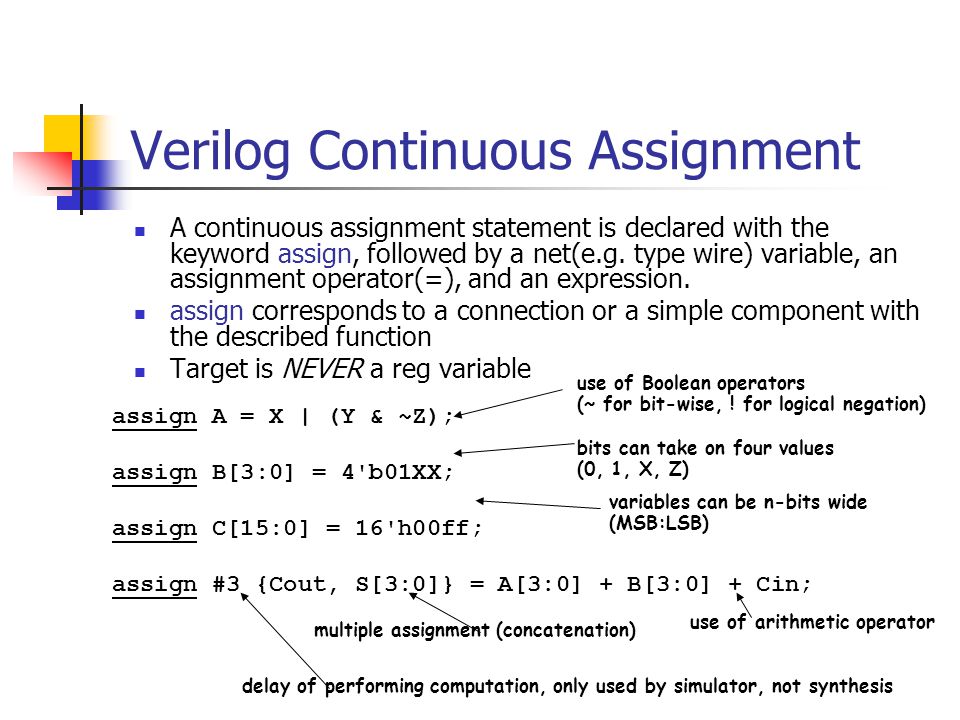

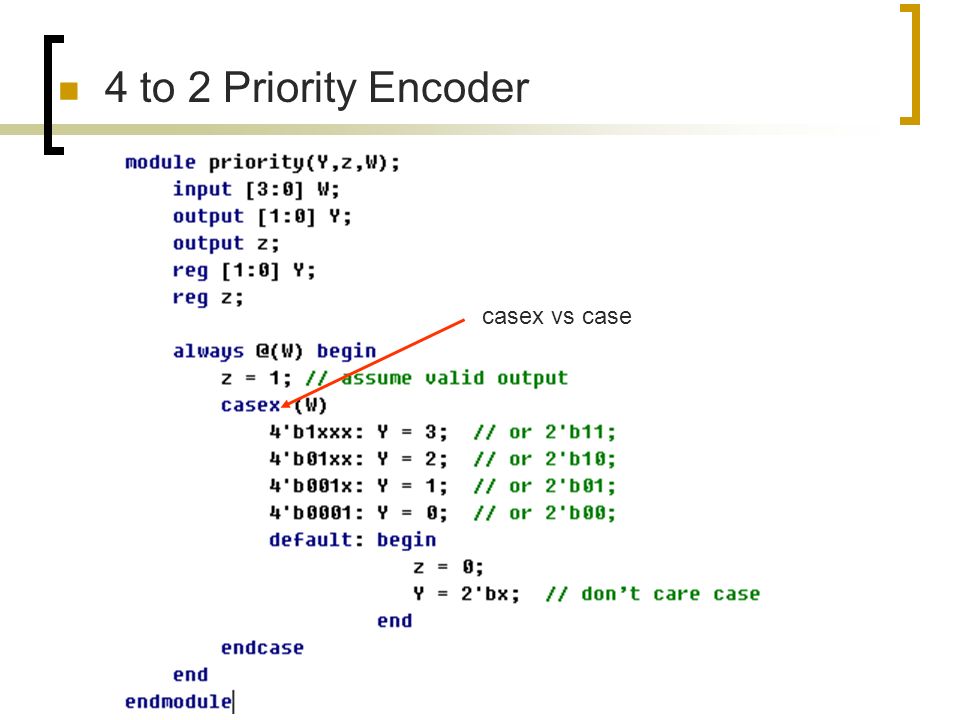

Процедурные блоки

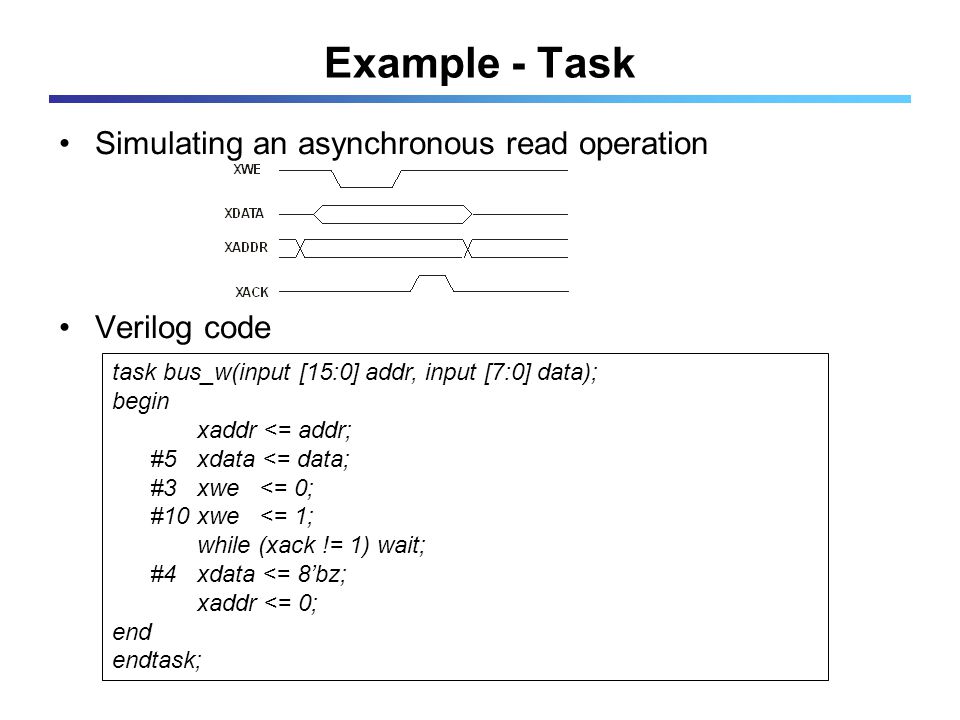

Процедурные блоки (initial и always) используются для описания последовательного поведения схемы. В них можно использовать привычные программистам управляющие конструкции — if-else, case, for и т.д.

Уровни абстракции в Verilog

Одно из ключевых преимуществ Verilog — возможность описывать системы на разных уровнях абстракции. Какие уровни поддерживает язык?

- Поведенческий уровень — описание алгоритма работы системы без детализации реализации

- Уровень регистровых передач (RTL) — описание потоков данных между регистрами и логическими блоками

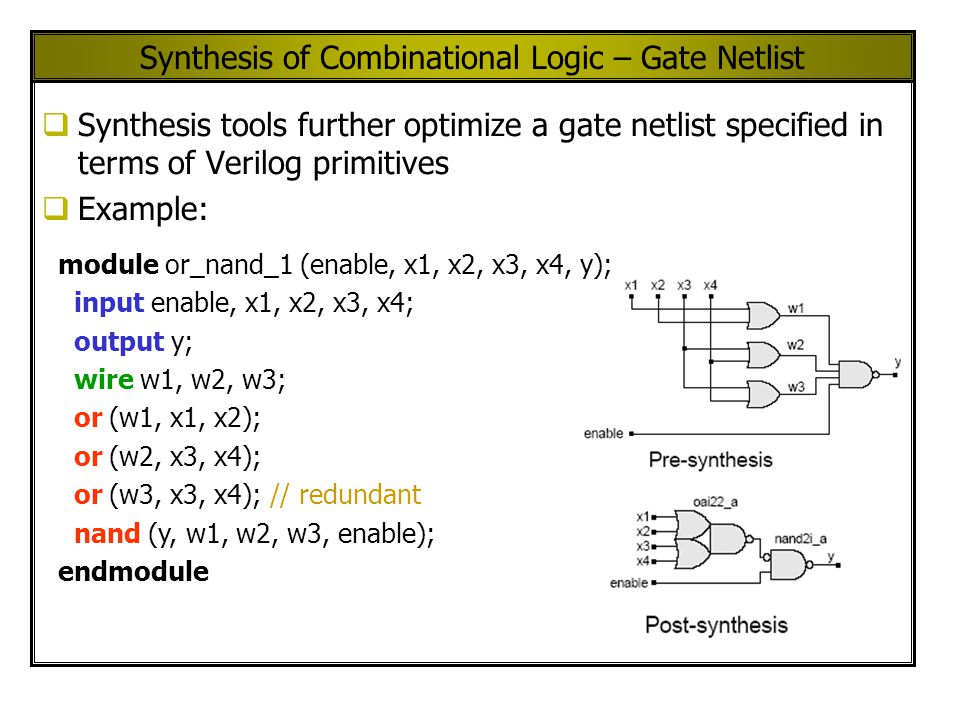

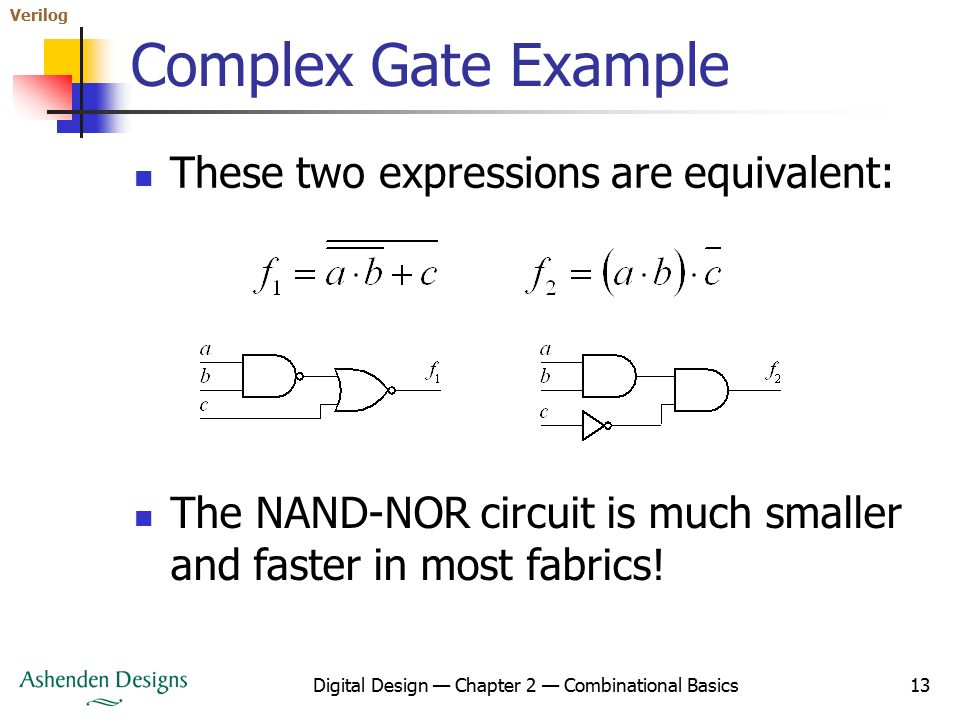

- Вентильный уровень — описание схемы в виде соединений логических вентилей

- Транзисторный уровень — низкоуровневое описание на уровне отдельных транзисторов

Такая многоуровневая модель позволяет разработчикам выбирать оптимальный уровень абстракции для каждой части проекта, сочетая высокоуровневое и низкоуровневое описание.

Инструменты разработки на Verilog

Для эффективной работы с Verilog необходимы специализированные инструменты. Какие средства разработки доступны инженерам?

Симуляторы

Симуляторы позволяют моделировать работу описанных на Verilog схем и проводить их функциональную верификацию. Популярные симуляторы:

- ModelSim от Mentor Graphics

- VCS от Synopsys

- Incisive от Cadence

- Icarus Verilog (открытый исходный код)

Синтезаторы

Синтезаторы преобразуют RTL-описание на Verilog в список соединений на уровне вентилей. Ведущие инструменты синтеза:

- Design Compiler от Synopsys

- Genus Synthesis Solution от Cadence

- Precision от Mentor Graphics

Средства отладки и анализа

Для анализа результатов моделирования и отладки проектов применяются специальные инструменты:

- Waveform viewers для анализа временных диаграмм

- Debuggers для пошагового выполнения симуляции

- Code coverage tools для оценки полноты тестирования

Сравнение Verilog и VHDL

Verilog и VHDL — два основных языка описания аппаратуры. В чем их ключевые различия?

| Критерий | Verilog | VHDL |

|---|---|---|

| Синтаксис | Похож на C | Похож на Ada |

| Типизация | Слабая | Сильная |

| Уровень абстракции | От транзисторного до системного | От вентильного до системного |

| Простота освоения | Проще для программистов | Сложнее, но строже |

| Производительность симуляции | Выше | Ниже |

Выбор между Verilog и VHDL часто зависит от специфики проекта, предпочтений команды и используемых инструментов. Многие современные среды разработки поддерживают оба языка.

Перспективы развития Verilog

Несмотря на свой возраст, Verilog продолжает развиваться. Какие тенденции наблюдаются в эволюции языка?

- Развитие стандарта SystemVerilog, расширяющего возможности Verilog для верификации

- Интеграция с высокоуровневыми языками программирования (C++, Python) для системного проектирования

- Поддержка новых технологий, таких как квантовые вычисления и нейроморфные системы

- Улучшение средств анализа энергопотребления и оптимизации мощности

- Развитие инструментов автоматизации проектирования на основе Verilog

Эти тенденции показывают, что Verilog остается актуальным инструментом для разработки современных цифровых систем и продолжит играть важную роль в будущем электроники.

Learn Verilog — лучшие учебники Verilog

Вы также можете быть заинтересованы в:

Frequently Asked Questions(FAQs)

What is Verilog?

Verilog is a hardware description language that allows you to describe the digital system, electronic circuits, memory, or a microprocessor. Verilog can be used for time analysis, test analysis, and logic synthesis. You can design and verify digital circuits at a register-transfer level of abstraction. These description languages differ from the software programming language as they are used to model the hardware. Verilog works well if you have the hardware specifications handy. It has a simple C like structure and requires digital logic knowledge.

What are VHDL and Verilog?

VHDL and Verilog are both languages for hardware description. These languages allow you to write programs for electronic chips or digital systems that do not share the computer’s basic architecture. VHDL is a little older and based on Ada and Pascal and inherits both characteristics. If VHDL scripts are not strongly typed, then it is difficult to get them compiled. Since VHDL is a strongly typed language, it does not allow variables from different classes.

If VHDL scripts are not strongly typed, then it is difficult to get them compiled. Since VHDL is a strongly typed language, it does not allow variables from different classes.

But on the other hand, Verilog is based on the C programming language and uses weakly typed language. Verilog is case sensitive.

Difference Between VHDL, Verilog, and SystemVerilog

VHDL and Verilog are general-purpose digital system language while the SystemVerilog specifies the Verilog’s enhanced version. Each of them has their unique usage and characteristics. VHDL has Ada and pascal syntax and concept while programming, Verilog has C programming language model and concept.

VHDL is strongly typed while Verilog has simple syntax, so extra coding will be required for VHDL to convert one data type to others. VHDL has better error debugging methods and better portability between different tools.

SystemVerilog is different, which allows the developers to verify more complex designs. It is considered to be the combination of both VHDL and Verilog that uses C and C++ language.

It is considered to be the combination of both VHDL and Verilog that uses C and C++ language.

Should I learn Verilog or VHDL?

There is some difference when it comes to coding and the understanding of the code. On the one hand, VHDL is more verbose, thus making use of more lines of code than Verilog that has C-like syntax and is much easier to code. VHDL has better code flow, while Verilog is more compact and more suitable for hardware modeling. It’s up to you what type of language suits for your coding style.

Which software is used for Verilog?

Some of the simulators that are used for the Verilog are-

- Synopsys

- Mentor

- Cadence

- Aldec

- ASIC

- FPGA tools

- IBM driver Vivado suite

- questaSim

Who Uses Verilog?

This language plays an important role in the Electronics engineer’s career. You will get job opportunities like a design engineer, verification engineer, RTL designer, etc.

5 лучших Zynq Fpga онлайн-курсов, тренингов, уроков и тьюториалов по [2022 Обновлено]

«This post includes affiliate links for which I may make a small commission at no extra cost to you should you make a purchase.»

Наша команда экспертов проанализировала большой объем данных и прослушала часы видеозаписей, чтобы составить список 5 лучших Zynq Fpga онлайн-курсов, тренингов, уроков и тьюториалов по.

| Название курса | Студенты (кол-во) | Отзывы (кол-во) |

|---|---|---|

| 1. Embedded System Design with Xilinx Zynq FPGA and VIVADO Наш лучший выбор | 915+ | 148+ |

| 2. Zynq Training – Learn Zynq 7000 SOC device on Microzed FPGA | 4471+ | 144+ |

| 3. Hands-On ZYNQ: Mastering AXI4 Bus Protocol | 376+ | 45+ |

| 4. Getting Started with Xilinx Zynq SoC Devices with Vivado | 20+ | 4+ |

5. Getting Started with Custom AXI peripherals for Zynq Devices Getting Started with Custom AXI peripherals for Zynq Devices |

11+ | 1+ |

1. Embedded System Design with Xilinx Zynq FPGA and VIVADO от Digitronix Nepal Udemy Course

Наш лучший выбор“Zynq Training with VIVADO Tool: Embedded System Design with Zynq 7000 (Zedboard/Zybo/MicroZed), VIVADO IPI & SDK.”

На момент написания этой статьи более 915+ человек прошли этот курс и оставили 148+ отзывов.

Нажмите здесь и ПОЛУЧИТЕ скидку 95%, скидка будет автоматически применена при нажатии

2. Zynq Training – Learn Zynq 7000 SOC device on Microzed FPGA от Augmented Startups Udemy Course

Learn the Basics of Xilinx Zynq® All Programmable System on a Chip (SoC) Design in Xilinx SDK.

На момент написания этой статьи более 4471+ человек прошли этот курс и оставили 144+ отзывов.

Нажмите здесь и ПОЛУЧИТЕ скидку 95%, скидка будет автоматически применена при нажатии

3. Hands-On ZYNQ: Mastering AXI4 Bus Protocol от Erwin Ouyang Udemy Course

Create Verilog and C codes for implementing the AXI4 bus protocol on ZYNQ FPGA

На момент написания этой статьи более 376+ человек прошли этот курс и оставили 45+ отзывов.

Нажмите здесь и ПОЛУЧИТЕ скидку 95%, скидка будет автоматически применена при нажатии

4. Getting Started with Xilinx Zynq SoC Devices with Vivado от Kumar K. Udemy Course

“All about Vivado IPI, Xilinx Drivers and SDK”

На момент написания этой статьи более 20+ человек прошли этот курс и оставили 4+ отзывов.

Нажмите здесь и ПОЛУЧИТЕ скидку 95%, скидка будет автоматически применена при нажатии

5. Getting Started with Custom AXI peripherals for Zynq Devices от Kumar K. Udemy Course

Using Verilog and Vivado Design Suite

На момент написания этой статьи более 11+ человек прошли этот курс и оставили 1+ отзывов.

Нажмите здесь и ПОЛУЧИТЕ скидку 95%, скидка будет автоматически применена при нажатии

Learn Verilog — лучшие учебные пособия по Verilog

Вас также может заинтересовать:

Часто задаваемые вопросы (FAQ)

Что такое Verilog?

Verilog — это язык описания оборудования, который позволяет вам описывать цифровую систему, электронные схемы, память или микропроцессор. Verilog можно использовать для временного анализа, тестового анализа и логического синтеза. Вы можете проектировать и проверять цифровые схемы на уровне абстракции регистр-передача. Эти языки описания отличаются от языка программирования программного обеспечения, поскольку они используются для моделирования оборудования. Verilog работает хорошо, если у вас под рукой есть технические характеристики оборудования. Он имеет простую C-подобную структуру и требует знания цифровой логики.

Verilog можно использовать для временного анализа, тестового анализа и логического синтеза. Вы можете проектировать и проверять цифровые схемы на уровне абстракции регистр-передача. Эти языки описания отличаются от языка программирования программного обеспечения, поскольку они используются для моделирования оборудования. Verilog работает хорошо, если у вас под рукой есть технические характеристики оборудования. Он имеет простую C-подобную структуру и требует знания цифровой логики.

Что такое VHDL и Verilog?

VHDL и Verilog являются языками описания оборудования. Эти языки позволяют писать программы для электронных микросхем или цифровых систем, которые не используют базовую архитектуру компьютера. VHDL немного старше, основан на Ada и Pascal и наследует обе характеристики. Если сценарии VHDL не являются строго типизированными, их трудно скомпилировать. Поскольку VHDL является строго типизированным языком, он не позволяет использовать переменные из разных классов.

Но, с другой стороны, Verilog основан на языке программирования C и использует язык со слабой типизацией. Verilog чувствителен к регистру.

Разница между VHDL, Verilog и SystemVerilog

VHDL и Verilog являются языком цифровой системы общего назначения, тогда как SystemVerilog определяет расширенную версию Verilog. Каждый из них имеет свое уникальное использование и характеристики. VHDL имеет синтаксис и концепцию Ada и Pascal при программировании, Verilog имеет модель и концепцию языка программирования C.

VHDL строго типизирован, в то время как Verilog имеет простой синтаксис, поэтому VHDL потребуется дополнительное кодирование для преобразования одного типа данных в другой. VHDL имеет лучшие методы отладки ошибок и лучшую переносимость между различными инструментами.

SystemVerilog отличается, что позволяет разработчикам проверять более сложные конструкции. Считается, что это комбинация VHDL и Verilog, использующая языки C и C++.

Должен ли я изучать Verilog или VHDL?

Есть некоторая разница в кодировании и понимании кода. С одной стороны, VHDL более многословен, поэтому использует больше строк кода, чем Verilog, который имеет синтаксис, подобный C, и его гораздо проще кодировать. VHDL обеспечивает лучший поток кода, а Verilog более компактен и больше подходит для аппаратного моделирования. Вам решать, какой тип языка подходит для вашего стиля кодирования.

С одной стороны, VHDL более многословен, поэтому использует больше строк кода, чем Verilog, который имеет синтаксис, подобный C, и его гораздо проще кодировать. VHDL обеспечивает лучший поток кода, а Verilog более компактен и больше подходит для аппаратного моделирования. Вам решать, какой тип языка подходит для вашего стиля кодирования.

Какое программное обеспечение используется для Verilog?

Some of the simulators that are used for the Verilog are-

- Synopsys

- Mentor

- Cadence

- Aldec

- ASIC

- FPGA tools

- IBM driver Vivado suite

- questaSim

-

Who Использует Верилог?

Этот язык играет важную роль в карьере инженера-электронщика. Вы получите возможность трудоустройства, например, инженера-конструктора, инженера по проверке, дизайнера RTL и т. д.

Учебное пособие Verilog

| |||||||||||||||