Каковы основные различия между последовательным и параллельным соединением реакторов. Какая схема обеспечивает более высокую степень превращения. В каких случаях предпочтительнее использовать последовательное или параллельное соединение. Как выбрать оптимальную схему для конкретного химико-технологического процесса.

Особенности последовательного соединения реакторов

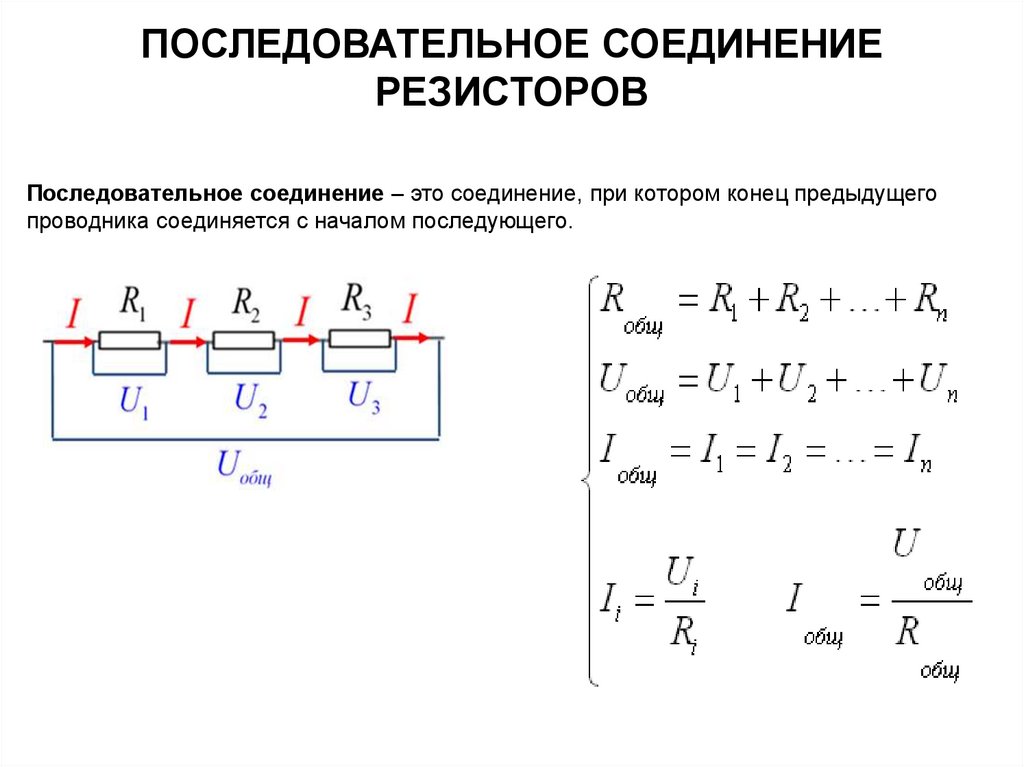

При последовательном соединении реакторов продукты реакции из первого реактора поступают во второй, затем в третий и т.д. Такая схема имеет ряд преимуществ:

- Обеспечивает более высокую степень превращения исходных веществ

- Позволяет создать оптимальные условия на каждой стадии процесса

- Дает возможность организовать промежуточное охлаждение или нагрев реакционной массы

Однако последовательное соединение требует большего числа аппаратов и усложняет технологическую схему.

Характеристики параллельного соединения реакторов

При параллельном соединении исходное сырье распределяется между несколькими одинаковыми реакторами. Основные особенности такой схемы:

- Повышает общую производительность установки

- Упрощает регулирование процесса

- Обеспечивает гибкость производства

- Позволяет проводить ремонт отдельных аппаратов без остановки всей установки

Главный недостаток — более низкая степень превращения по сравнению с последовательной схемой.

Сравнение эффективности последовательной и параллельной схем

Эффективность различных схем соединения реакторов зависит от многих факторов:

- Кинетики химической реакции

- Тепловых эффектов

- Гидродинамических условий

- Требуемой степени превращения

Для реакций первого порядка последовательное соединение всегда эффективнее параллельного. Для реакций более высоких порядков преимущество последовательной схемы проявляется при высоких степенях превращения.

Выбор оптимальной схемы соединения реакторов

При выборе схемы соединения реакторов необходимо учитывать следующие факторы:

- Кинетику и механизм химической реакции

- Требуемую степень превращения

- Тепловой эффект реакции

- Необходимость промежуточного охлаждения или нагрева

- Гибкость производства

- Капитальные и эксплуатационные затраты

Оптимальная схема определяется путем технико-экономического сравнения различных вариантов с учетом всех перечисленных факторов.

Применение последовательных схем в промышленности

Последовательное соединение реакторов широко применяется в следующих процессах:

- Каталитический крекинг нефтяных фракций

- Синтез аммиака

- Окисление этилена в этиленоксид

- Производство серной кислоты

- Синтез метанола

Использование каскада последовательных реакторов позволяет повысить степень превращения и селективность процесса за счет создания оптимальных условий на каждой стадии.

Использование параллельных схем в химической технологии

Параллельное соединение реакторов эффективно применяется в следующих случаях:

- Процессы с высоким тепловым эффектом

- Производство полимеров

- Биохимические процессы

- Гетерогенно-каталитические реакции

- Процессы, требующие частой замены катализатора

Параллельная схема обеспечивает гибкость производства и позволяет регулировать производительность установки в широких пределах.

Комбинированные последовательно-параллельные схемы

Во многих случаях оптимальной является комбинированная последовательно-параллельная схема соединения реакторов. Она позволяет сочетать преимущества обоих типов соединения:

- Высокую степень превращения

- Гибкость производства

- Возможность оптимизации условий на разных стадиях

- Эффективное использование тепла реакции

Комбинированные схемы применяются в производстве этилена, пропилена, бутадиена и других крупнотоннажных продуктов нефтехимии.

Математическое моделирование систем реакторов

Для выбора оптимальной схемы соединения реакторов широко применяются методы математического моделирования:

- Составление материальных и тепловых балансов

- Решение систем дифференциальных уравнений

- Оптимизационные алгоритмы

- Имитационное моделирование

Моделирование позволяет сравнить эффективность различных схем без проведения дорогостоящих экспериментов.

Заключение

Выбор схемы соединения реакторов является важной задачей при проектировании химико-технологических процессов. Последовательное соединение обеспечивает более высокую степень превращения, но требует большего количества аппаратов. Параллельное соединение повышает гибкость производства. Оптимальная схема определяется для каждого конкретного процесса путем технико-экономического анализа с учетом кинетики реакции, теплового эффекта и других факторов.

последовательная схема — это… Что такое последовательная схема?

- последовательная схема

- sequential circuit

Большой англо-русский и русско-английский словарь. 2001.

- последовательная сумма

- последовательная схема запуска

Смотреть что такое «последовательная схема» в других словарях:

последовательная схема — — [http://www.iks media.ru/glossary/index.html?glossid=2400324] Тематики электросвязь, основные понятия EN sequential circuit … Справочник технического переводчика

последовательная схема соединения полупроводниковых преобразователей — Схема соединения, в которой два или более полупроводниковых преобразователя соединены таким образом, что их постоянные напряжения складываются. [ГОСТ 23414 84] Тематики преобразователь электроэнергии … Справочник технического переводчика

последовательная схема горячего водоснабжения — (с использованием аккумулирующей способности здания для выравнивания суточного графика тепловой нагрузки) [А.С.Гольдберг. Англо русский энергетический словарь. 2006 г.] Тематики энергетика в целом EN series circuit of the hot water system … Справочник технического переводчика

параллельно-последовательная схема — lygiagrečiai nuosekli grandinė statusas T sritis radioelektronika atitikmenys: angl. parallel series circuit vok. Parallelreihenschaltung, f rus. параллельно последовательная схема, f; параллельно последовательная цепь, f pranc. circuit parallèle … Radioelektronikos terminų žodynas

КОНТАКТНАЯ СХЕМА — специальная управляющая система, одна нз математических моделей реальных устройств, построенных из контактов реле. К. с. модельный класс управляющих систем, и для него рассматриваются все те же задачи, что и для прочих классов управляющих систем; … Математическая энциклопедия

параллельно-последовательная цепь — lygiagrečiai nuosekli grandinė statusas T sritis radioelektronika atitikmenys: angl. parallel series circuit vok. Parallelreihenschaltung, f rus. параллельно последовательная схема, f; параллельно последовательная цепь, f pranc. circuit parallèle … Radioelektronikos terminų žodynas

параллельно-последовательная цепь — Схема с параллельным и последовательным соединением (элементов). [Я.Н.Лугинский, М.С.Фези Жилинская, Ю.С.Кабиров. Англо русский словарь по электротехнике и электроэнергетике, Москва, 1999 г.] Тематики электротехника, основные понятия EN parallel… … Справочник технического переводчика

эквивалентная схема варикапа и туннельного диода

— Сп параллельная емкость; gпер отрицательная проводимость; rп сопротивление потерь; Lg последовательная индуктивность; Cпер емкость перехода. Черт.7 [ГОСТ 25529 82] Тематики полупроводниковые приборы … Справочник технического переводчикаКриптографическая хеш-функция — Криптографической хеш функцией называется всякая хеш функция, являющаяся криптостойкой, то есть, удовлетворяющая ряду требований специфичных для криптографических приложений. Содержание 1 Требования 2 Принципы построения … Википедия

Ствол шахтный — (a. mine shaft; н. Schacht; ф. puits de mine; и. pozo) капитальная вертикальная или наклонная горн. выработка, имеющая выход на земную поверхность и предназначенная для вскрытия м ний и обслуживания подземных работ. Pазличают главные и… … Геологическая энциклопедия

Parallelreihenschaltung — lygiagrečiai nuosekli grandinė statusas T sritis radioelektronika atitikmenys: angl. parallel series circuit vok. Parallelreihenschaltung, f rus. параллельно последовательная схема, f; параллельно последовательная цепь, f pranc. circuit parallèle … Radioelektronikos terminų žodynas

Последовательная разводка водопровода | elesant.ru

Вступление

Последовательная разводка водопровода, по-другому, называемая тройниковая, остается самым дешевым вариантом индивидуального водопровода. Невысокая цена последовательной разводки определяется меньшим, по сравнению с коллекторной и смешанной разводками, количеством необходимого материала, и меньшим объемом необходимых сантехнических работ.

Последовательная разводка водопровода

Определение последовательной разводки водопровода, понятно из ее названия. Все сантехнические приборы в квартире, требующие постоянной (стационарной) подводки воды, подключаются к водопроводному вводу в квартиру, от общей магистральной трубы через специальные сантехнические тройники. На рисунке это хорошо видно.

Основной недостаток последовательной разводки водопровода это всем знакомое, падение напора воды, предположим в смесители душа при включении воды на кухне. То есть напор воды во всех сантехнических приборах зависит друг от друга. Кстате,этот недостаток почти отсутствует при коллекторной разводке водопровода в квартире.

Для борьбы с этим недостатком, при монтаже тройникового водопровода, диаметр труб от тройника до прибора, делается на шаг меньше диаметра магистральной трубы. Например, магистраль D=20 мм, а подводка к приборам D=16 мм. Этим повышается напор воды в отводных трубах.

Здесь хочу остановиться еще на одной особенности последовательного водопровода. Строго говоря, последовательная разводка водопровода делится на последовательную тройниковую разводку водопровода (рис выше) и последовательную разводку с использованием проходных водорозеток (рис.)

Монтаж водопровода с использованием проходных водорозеток, еще больше увеличивает зависимость напора воды одного работающего прибора от другого.

Для примера правильного, профессионального монтажа последовательного водопровода приведу монтажную схему последовательной (тройниковой) разводки водопровода.

Схема последовательной (тройниковой) разводки водопровода

Монтажная последовательная схема водопровода оцинкованными трубами

Монтажная схема водопровода делается на основе плана квартиры с последовательной схемой водопровода и аксонометрической схемы последовательной разводки.

На монтажной схеме вы можете видеть, что все отводы труб к приборам, делают из труб D=16 мм, тогда как магистральная труба имеет диаметр D=20мм.

Для практики, посмотрите Спецификацию по материалам

И, конечно же, не обойтись без условных обозначениях на сантехнических схемах.

На этом тема Последовательная разводка водопровода закончена.

©Elesant.ru

Другие статьи раздела: Водопровод

Похожие статьи

Последовательная схема разводки водопровода: плюсы и минусы

Ещё одна схема разводки водопровода — последовательная (о двух других схемах разводки — тройниковой и коллекторной — рассказано в первой части статьи).

Итак, последовательная схема разводки водопровода выглядит так:

Здесь делаем отвод от стояков к потребителю; возле потребителя ставятся такие тройники (водоразборные розетки):

К одному отводу тройника присоединяется сам потребитель, а к двум другим — труба с водой.

По схеме ниже можно получить более наглядное представление:

Последовательная схема разводки водопровода имеет такие же элементы, как тройниковая и коллекторная, только перед потребителями установлены водоразборные розетки в виде тройников.

Такая схема разводки водопровода используется редко, но всё же используется. Она актуальна в том случае, если есть возможность спрятать весь трубопровод где-то в стене либо за перегородкой, за гипсокартоном и т. п. Единственное предостережение: если труба металлопластиковая, то прятать в стене или за гипсокартоном тройники не следует.

Далее вашему вниманию сравнительная таблица, из которой можно видеть, какие достоинства и недостатки имеет каждая схема разводки водопровода (для увеличения кликнуть по таблице):

За основу (100%) принято тройниковое соединение, как наиболее часто используемое.

Обратите внимание, что при тройниковом подключении имеет место неравномерное давление: чем дальше прибор от места подключения (стояка), тем меньше в нём давление – за счёт потребления ранее расположенных приборов. А при коллекторном подключении давление во всех приборах равномерное. При этом количество применяемых соединений меньше (71% — по сравнению с тройниковым), трудозатраты тоже меньше (88%), зато больше понадобится трубы, и материал обойдётся дороже.

Точно так же по таблице можно увидеть преимущества/недостатки последовательной системы по приводимым параметрам.

Итак, мы разобрались, что такое схема разводки водопровода и какие схемы можно применять в квартире или в частном доме. И теперь самое время завершить проектирование водопровода и канализации, начатое «давным-давно».

схема разводки водопровода

Не удается найти страницу | Autodesk Knowledge Network

(* {{l10n_strings.REQUIRED_FIELD}})

{{l10n_strings.CREATE_NEW_COLLECTION}}*

{{l10n_strings.ADD_COLLECTION_DESCRIPTION}}

{{l10n_strings.COLLECTION_DESCRIPTION}} {{addToCollection.description.length}}/500 {{l10n_strings.TAGS}} {{$item}} {{l10n_strings.PRODUCTS}} {{l10n_strings.DRAG_TEXT}}{{l10n_strings.DRAG_TEXT_HELP}}

{{l10n_strings.LANGUAGE}} {{$select.selected.display}}{{article.content_lang.display}}

{{l10n_strings.AUTHOR}}{{l10n_strings.AUTHOR_TOOLTIP_TEXT}}

{{$select.selected.display}} {{l10n_strings.CREATE_AND_ADD_TO_COLLECTION_MODAL_BUTTON}} {{l10n_strings.CREATE_A_COLLECTION_ERROR}}Последовательные и параллельные схемы реакторов

Схемы с последовательно-параллельным соединением реакторов.. [c.151]

ПОСЛЕДОВАТЕЛЬНЫЕ И ПАРАЛЛЕЛЬНЫЕ СХЕМЫ РЕАКТОРОВ [c.192]

В 4.1. ПОСЛЕДОВАТЕЛЬНЫЕ И ПАРАЛЛЕЛЬНЫЕ СХЕМЫ РЕАКТОРОВ 4.1.1. Расчетные формулы [c.114]

Получите математическую модель процесса в реакторе идеального вытеснения при протекании сложной реакции а) с параллельной схемой превращения б) с последовательной схемой превращения Покажите график изменения концентраций компонентов по длине реактора и объясните его вид (почему концентрации увеличиваются, уменьшаются, не меняются и Т.Д.). [c.184]

Рассмотрим еще один пример. Пусть в схеме имеется последовательно-параллельная совокупность реакторов и требуется найти оптимальное сочетание числа параллельных ветвей с числом реакторов в каждой ветви при сохранении остальной структуры схемы неизменной. Легко видеть, что применение двухуровневой процедуры синтеза приведет к необходимости решения на втором уровне задачи (VI 1,8), где — число ветвей ищ — число реакторов в каждой ветви. Здесь также можно использовать метод Гаусса — Зейделя. [c.249]

Технологическая схема установки приведена на рис. VI.3. Сырье из секции подготовки (на схеме не показана) подается насосом 1 в холодильник 2 (здесь хладагент — испаряющийся изобутан), а затем равными порциями вводится параллельно в пять зон реактора 6. В первую зону реактора 6 вводится циркулирующая и свежая серная кислота насосом 4 и проходит последовательно все зоны реактора. [c.61]

Несмотря на сравнительно небольшие размеры, эта схема интересна тем, что в ней присутствуют все элементы сложных схем 1) аппараты различных типов (реакторы, экстракторы, смесители) 2) аппараты, расположенные последовательно (параллельно) 3) рецикл 4) аппараты (экстракторы), расчет которых-требует итерационных процедур. [c.57]

Использование этого подхода к задаче оптимизации последовательности реакторов идеального смешения [И, с. 50] показало его эффективность. На этом примере ясно видна также польза введения дополнительных поисковых переменных для распараллеливания вычислений в случае использования многопроцессорных ЭВМ или многомашинных комплексов. Благодаря последовательной структуре схемы (см. рис. 22) здесь может эффективно использоваться только одна ЭВМ. Введение же дополнительных поисковых переменных позволяет параллельно обрабатывать отдельные участки на нескольких ЭВМ. [c.136]

В начальный период работы установки, когда активность катализатора еще высокая, можно рекомендовать параллельную схему работы реакторов. С понижением активности катализатора для сохранения глубины превращения рекомендуется пользоваться последовательной схемой. [c.44]

Кроме перечисленных выше вопросов, были рассмотрены и решены также вопросы, связанные с выбором состава газовой смеси на входе в реактор, с расположением реакторов (параллельное или последовательное) в схеме процесса, а также ряд других вопросов. [c.96]

На нескольких заводах в США и в Англии двойной суперфосфат получают непрерывным методом по схеме, изображенной на рис. 73. Реакция между измельченным фосфоритом и фосфорной кислотой, содержащей 38% Р2О5, осуществляется в трех непрерывно действующих реакторах 3, через которые пульпа проходит последовательно. Из последнего реактора пульпа поступает в два параллельно работающих смесителя 4, в каждом из которых имеются два горизонтальных вала с лопастными мешалками. Здесь пульпа смешивается с мелкой фракцией продукта, получаемого после сушки и рассева, причем образуются влажные гранулы, направляющиеся в барабанную сушилку 5. Сухие гранулы рассеиваются в грохоте 10 на три фракции. Средняя фракция является продуктом крупная — [c.149]

VI-4. Завод располагает реактором, в котором степень превращения вещества А достигает 90%. Был приобретен второй реактор, аналогичный первому. При каком соединении реакторов (последовательном или параллельном) и сохранении первоначальной степени превращения производительность технологической схемы будет больше [c.158]

Примером параллельной схемы может служить группа параллельно работающих теплообменников группа насосов, подающих жидкость в один коллектор группа параллельно рабо тающих реакторов. Параллельные схемы характерны для крупного химического производства и широко распространены в химической промышленности. Это связано, во-первых, с их повышенной надежностью, так как выход из строя одного из аппаратов не нарушает работы всей системы. Во-вторых, параллельные схемы обладают большой гибкостью, позволяющей в одной технологической схеме применять оборудование разной производительности, т. е. в разных последовательных звеньях производства использовать разное число параллельно работающих аппаратов. Такие схемы, называемые коллекторными, позволяют обеспечить непрерывность общего технологического потока в ряде производств, в состав которых входят отдельные агрегаты, работающие по периодической или полу-периодической схеме. [c.12]

Заменив в формулах (Х1.52), (Х1.53), (Х1.54) и (Х1.55) время реакции 1 удельной энергией 1//о, можно вычислить константы и 2 и по их средним значениям сравнить опытные и вычисленные, значения ос. Как оказалось, последовательная схема удовлетворительно описывает найденную на опыте зависимость а=/(1//о) только для цельностеклянного реактора. Для описания кинетики образования — разложения перекиси водорода в стеклянно-металлических реакторах схема (Х1.49) не годится. В связи с этим в дальнейшем была испытана схема двух последовательно-параллельных реакций. В соответствии со сказанным ранее ее можно представить в виде [c.320]

Конструкция реактора и схема его работы описаны выще. Свежее сырье подается во все 5 секций реакционной зоны равными параллельными потоками, а рециркулирующий изобутан и кислота вводятся в первую секцию и затем последовательно проходят все секции реактора. [c.189]

VI-3. При каких значениях порядка реакции, коэффициента расширения и степени превращения схему с двумя последовательно соединенными реакторами идеального вытеснения целесообразнее эксплуатировать, чем схему с параллельным соединением тех же реакторов [c.158]

Схемой предусматривается как последовательное, так и параллельное подключение аппаратов сероочистки и конверсии. Это позволит исключить необходимость остановок установки на период замены катализаторов и хемосорбентов в реакторах. Предпочтительней последовательное подключение аппаратов, поскольку при этом уменьшается опасность неравномерного распределения потока газа по сечению аппаратов и отрицательное влияние пристеночного эффекта (проскок газа вдоль стенки). [c.61]

При осуществлении непрерывных процессов, а также для обеспечения необходимых температурных условий на различных стадиях реакции отдельные аппараты компонуются в каскад реакторов. В таком каскаде жидкость проходит последовательно через все аппараты, а газ может подаваться последовательно или параллельно в каждый реактор. В случае, если количество газа, рассчитанного по стехиометрическому уравнению реакции, недостаточно для обеспечения оптимальных гидродинамических условий в каждом аппарате, а разбавление инертным газом нежелательно, каскад может работать по замкнутой циркуляционной схеме (рис. 45). Согласно этой схеме, основная масса газа транспортируется через все аппараты каскада циркуляционным компрессором 1. Свежий газ в количестве, достаточном для реакции, вводится в циркуляционной контур компрессором 2. На выходе из 6 83 [c.83]

Технологическая схема процесса получения винилтолуола на основе толуола и ацетилена представлена на рис. 4.4. Потоки толуола и Н2804 с добавкой НеЗО из дозатора / подают последовательно в каскад реакторов 2 с мешалками, в которые параллельно поступает ацетилен. После отделения катализатррного слоя в разделителе 5 алкилат нейтрализуют в аппарате 4 и разделяют в комбинированной колонне /О, откуда дитолилэтан подают через перегреватель 5 в секцию крекинга 6. Катализат крекинга через систему утилизации теплоты и сепарации (7—9) поступает в колонну 10 и в колонны И и /2 для выделения толуола, дитолилэтана, винилтолуола и побочно образующегося при крекинге ДТЭ этйлтолуола. Слой катализатора из разделителя 3 направляют в секцию регенерации 13. [c.109]

Так, для организации производства этиленгликоля мощностью 5000 т/год по раствору, содержащего около 80% масс, гликолей и обеспечения стабильной работы катализатора в течение длительн010 времени (более 8000 час), необходим реакторный узел с рассредоточенной подачей оксида этилена с числом точек ввода оксида равным, как минимум, 3. Для реализации данного решения на производстве нами была предложена технологическая схема, включающая каскад последовательно соединенных реакторов не равного объема с гюдачей оксида этилена в смесители, установленные перед каждым реактором каскада. При этом реакторы каскада могут содержать один или несколько модулей (например, модулей разработанных нами в [6]), соединенных в последовательно параллельную цепь. [c.5]

С увеличением производительности технологических линий при соответственном увеличении объемов реакторов перемешивание и теплосъем существенно усложняются. Поэтому не случайно такие фирмы, как Хехст , Монтэдисон и другие, используют каскады из 2—3 реакторов. Этим обеспечиваются, с одной стороны, сравнительно небольшие габариты каждого из реакторов, с другой стороны, возможность расширения выпускаемого ассортимента продукции за счет использования различных схем обвязки реакторов и их последовательной или параллельной работы. Параллельную схему работы реакторов (на различных режимах) часто используют для регулирования ММР конечного продукта. Последовательная схема, кроме лучших условий доработки катализаторов, позволяет получать сополимеры различного состава и структуры. Надежность работы технологической линии, обеспечивается не только качеством и техническим уровнем используемых технологии и оборудования, но и системой автоматического контроля и управления. Наиболее успешно эта задача решается с помощью автоматизированных систем управления технологическим процессом (АСУ ТП). [c.137]

Процесс осутцествляется в три ступени реакторы I и II ступени включены последовательно, а два реактора Ш ступени включены параллельно, один из которых может служить резервным. В первых двух ступенях протекают в основном реакции дегидрирования нафтеновых углеводородов и изомеризации парафиновых углеводородов. На последней ступени в более жестких условиях интенсифицируются реакции дегидроциклизации парафинов и гидрокрекинга, сопровождаемые отложением кокса на катализаторе. Для увеличения длительности рабочего цикла предусмотрена возможность отключения одного параллельно работающего реактора Ш ступени с целью проведения в нем регенерации катализатора без прекращения эксплуатации всей установки. При снижении же активности катализатора в реакторах I и II ступени прекращается подача сырья и регенерацию катализатора проводят во всех реакторах одновременно. Таким образом, указанная схема риформинга является промежуточной между технологиями с регенерацией катализатора во всех реакторах установки и регенерацией катализатора в резервном реакторе (процесс ультраформинга). [c.62]

При анализе реакционноспособного диоксида азота его целесообразно бывает перевести в азот, что упрощает количественный анализ и не требует специальной коррозионноустойчивой аппаратуры и детектора. В работе [51] описана методика разделения примесей оксидов азота, углерода и постоянных газов с использованием реакционной хроматографии и схемы с последовательно параллельными колонками. Анализируемая проба сначала проходит через колонку с углем СКТ (200Х Х0,4 см), на которой при 145°С происходит разделение на три зоны [первая — постоянные газы и оксид азота (П), вторая — диоксид азота (IV) и диоксид углерода и третья — оксид азота (I)]. Затем первая зона при комнатной температуре разделяется на второй колонке на компоненты, включая все постоянные газы и оксид азота (П), а вторая и третья зоны поступают в реактор, заполненный медью, в котором при 900 °С происходит восстановление оксидов азота до азота. Затем в колонке с углем СКТ, последовательно соединенной с реактором, происходит разделение диоксида углерода и азота, образовавшегося из диоксида азота (IV), т. е. второй общий пик разделяется на отдельные компоненты. [c.236]

При использовании данных непрерывного процесса для идентификации модели наряду с задачей определения неизвестных констант может решаться и задача сжатия , упрощения модели. При этом наиболее интересен прием экви-валентнрования, т. е. замены реальной модели ее упрощенным с точностью до известных экспериментальных данных эквивалентом. Эту задачу можно решать различными способами, однако наиболее удачным является замена рассматриваемого реактора реакторами идеального смешения, соединенными последовательнопараллельно [1, 3, 4]. При этом существенно облегчается анализ как стационарных, так и нестационарных режимов, поскольку обеспечивается возможность вычисления по рекуррентным формулам. Именно поэтому в данной работе рассмотрены модели преимущественно такого типа. Можно полагать, что модель идеального смешения — это тот основной модуль, с помощью которого (задавая граф последовательно-параллельного соединения) можно представить любую реакторную систему. Отметим, что благодаря однородности такой эквивалентной схемы можно решать вопросы оптимизации ее структуры, тогда как в других случаях эта задача практически неразрешима . [c.81]

Технологическая схема реакторного-отделения в зна чительной степени определяется применяемой конструкцией реактора. Для каждого из реакторов имеются особенности в подаче сырья, рециркулирующего изобутана, хладагентов и кислоты. Сырье и рециркулирующий изобутан могут подаваться в реакторы параллельно или последовательно. Хладагенты отнимают тепло от реакционной смеси снаружи реактора или непосредственно в реакционной зоне. [c.114]

Пример VI-4. Установка, показанная на рпс. YI-7, состоит из трех реакторов и, (еальиого вытеснения, соедииепиых в виде схемы с двумя параллельными потоками. Поток D проходит через последовательно соединенные реакторы объемами 5 и 3. и , потрк Е — через один реактор объемом 4 Какую долю от общей нагрузки установки должен составлять поток D — [c.144]

Технологическая схема процесса сернокислотного алкилирования в каскадном реакторе приведена на рис. 4.6. Свежая и циркулирующая кислота, а также потоки, содержащие изобутан, проходят последовательно через все секции реактора (обычно 6—8 секций). Свежий изобутаи после очистки в системе 1 вводят в деизобутанизатор 2 и затем по линиям II и И направляют в каскадный реактор 3. Олефиновое сырье после очистки в системе 4 по линиям V—VII подают параллельными потоками в каждую секцию реактора 3. Давление в реакторе снижается от 0,15—0,20 МПа в первой секции реактора до 0,04—0,08 МПа в последней. После разделения в отстойных зовах реактора углеводородную часть продуктов алкилирования VIII нейтрализуют и затем, промыв, вводят по линии IX в деизобутани- [c.120]

Описанная принципиальная схема в сущности положена в основу всех современных процессов гидрокрекинга над стационарными катализаторами, Различие заключается лищь в применении реакторов со значительно большими диаметрами, работающих при более низких давлениях и включаемых, как правило, не последовательно, а параллельно (для снижения перепадов давления в реакторных блоках). Кроме того, во всех [c.266]

Последовательная логика | Синхронная и асинхронная логическая схема

Последовательная логика

Содержание: последовательная логикаПоследовательное логическое определение:Что такое последовательная логическая схема?Тип логики, в котором предыдущее состояние последовательности входов, а также текущий вход могут влиять на текущее состояние выхода.

Освободи Себя последовательная логическая схема представляет собой комбинированную форму комбинационной схемы с базовым элементом памяти. При наличии элемента памяти схема может сохранять предыдущие состояния ввода и вывода. В то же время последовательная логическая схема обычно известна как двухпозиционное или бистабильное устройство, потому что она имеет только два стабильных состояния, «0» и «1», по одному состоянию за раз. Элемент памяти в схеме может хранить один бит за раз.

Этот тип схемы имеет конечное количество входов и конечное количество выходов. Благодаря элементу памяти эта схема обеспечивает решение многих наших проблем. Последовательная логическая схема в основном используется как регистр, счетчик, аналого-цифровой преобразователь (АЦП), и так далее

Последовательная логическая диаграмма | Последовательная логическая архитектура :Рис. Последовательная логическая схемаТипы последовательных логических схем:Как правило, мы можем разделить последовательную логическую схему на два основных типа:

- A. Асинхронная последовательная логическая схема.

- Б. Синхронная последовательная логическая схема.

Выход этой логической схемы зависит от входного импульса и тактового импульса схемы. Схема синхронизирована с часами, т.е. выход может измениться только через конечный интервал времени. Здесь элемент памяти и часы — необходимость. Без тактового импульса выход не будет изменен. Для изменения одного состояния выхода на другой эта схема ожидает следующего изменения тактового импульса.

Этот тип схемы может использоваться для синхронизации всех элементов, присутствующих в схеме, практически для реагирования на изменение входного сигнала. Для того, чтобы обработанный вывод происходил главным образом, необходимо ограниченное время, известное как задержка распространения. Задержка распространения может варьироваться от элемента к элементу. Итак, для правильно работающей схемы нам нужен определенный интервал времени, чтобы все элементы могли получить время для правильной реакции. Примером синхронных логических схем являются триггеры, синхронный счетчик и т. Д.

Асинхронные последовательные логические схемы:Выход этой логической схемы зависит только от входного импульса и последовательности предыдущих входных данных.Эта схема не имеет часов и не требует никакой синхронизации, поэтому схема не зависит от часов, что делает ее быстрее, чем синхронная последовательная логическая схема, поскольку выходной сигнал может изменяться относительно изменения входа с минимальным требуемым временем, может изменяться независимо от времени. Единственное препятствие для скорости этой схемы — задержка распространения элементов схемы. Он потребляет меньше энергии, низкие электромагнитные помехи.

Асинхронные последовательные логические схемы обычно выполняют операции в следующих случаях:

Эти схемы в основном используются, когда скорость работы является приоритетом, например, в микропроцессорах, цифровой обработке сигналов, для доступа в Интернет и т. Д. Из-за асинхронного поведения выход иногда может быть неопределенным, что ограничивает применение асинхронной последовательной логики. схема. Сформировать такой тип схемы тоже сложно.

Разница между синхронными и асинхронными последовательными логическими схемами:| Синхронная последовательная логическая схема | Асинхронная последовательная логическая схема |

| Выход этой логической схемы зависит от входного импульса, а также тактового импульса схемы. | Выход этой логической схемы зависит только от входного импульса и последовательности предыдущих входных данных. |

| Часы присутствуют в этой схеме. | В цепи нет часов. |

| Схема проста в проектировании. | Конструкция этой схемы сложна. |

| Относительно медленнее, чем у асинхронной последовательной логической схемы. | Относительно быстрее, чем у синхронной последовательной логической схемы. |

| Состояние вывода всегда предсказуемо | Состояние вывода иногда непредсказуемо |

| Эта схема потребляет довольно большую мощность. | Он потребляет относительно меньше энергии. |

Последовательная логическая диаграмма состояний — это характерная диаграмма схемы, в которой мы можем определить переход между состояниями относительно входа. На диаграммах этого типа это состояние в основном представлено в виде круга, а переход от одного состояния к другому обозначен стрелкой, вместе с этой стрелкой представлен входной импульс, который вызывает переход между состояниями. Когда есть импульсный выход, стрелка может быть представлена выходом, связанным с входным импульсом. Здесь стрелка начинается с одного круга и переходит к другому кругу, а иногда может вернуться к тому же кругу в зависимости от условия.

Схема последовательной логики | Принципы последовательного логического проектированияМы уже знаем, что последовательная логическая схема объединяет комбинационную схему с элементом памяти. А для элемента памяти нам нужен элемент статической памяти для хранения данных в схемах. Поэтому для создания ячейки статической памяти в схеме мы используем инверторы.

Этапы проектирования последовательной логической схемы:- Создайте диаграмму состояний для требуемой последовательной цепи с желаемыми выходными состояниями.

- Преобразуйте диаграмму состояний в таблицу состояний.

- Выберите триггер в соответствии с вашими требованиями и который удовлетворяет всем необходимым условиям, используйте таблицу характеристик или таблицу возбуждений для выбора триггера.

- Минимизируйте входные функции в триггер с помощью K-карты или требуемых логических алгоритмов.

- Используйте упрощенную функцию для разработки последовательной схемы, и если комбинационная схема необходима для требуемого выхода, добавьте ее соответствующим образом.

- Наконец, проверьте наличие требуемого выхода через схему.

Следуя вышеуказанному шагу, мы можем разработать любую требуемую последовательную схему.

Последовательные логические схемы MOS:Как известно, последовательная логическая схема — это комбинация комбинационной схемы с элементом памяти. А для элемента памяти нам нужен элемент статической памяти, чтобы он мог хранить данные в схемах. Поэтому для создания ячейки статической памяти в схемах мы используем инверторы.

Рис. На этом рисунке два инвертора связаны друг с другом обратной связью.Ячейка статической памяти может быть создана двумя или любым четным числом инверторов, соединенных последовательно с обратной связью. Он имеет два стабильных состояния, но одно стабильное состояние за раз, а стабильное состояние выхода относится к входу. Когда шум (в виде напряжения или другой формы) суммируется с выходом, что может сделать схему нестабильной, а выход может быть нестабильным в определенном состоянии, но когда шум проходит через любой из инверторов, он устраняется. поскольку этот контур регенерируется, он всегда пытается вернуться в определенное стабильное состояние, что помогает нам создать активную и регенерирующую ячейку памяти.

Рис. На этом рисунке КМОП-схема двух инверторов, соединенных с обратной связью.Приведенная выше диаграмма — это CMOS Схема — ячейка памяти (два инвертора подключены в обратную связь). Если эта схема будет стабильной на «0» или «1» с учетом входного напряжения (напряжения), подаваемого через вход, эта ячейка памяти в CMOS является ячейкой статической памяти. И, объединив схему КМОП этой ячейки памяти с комбинационной схемой КМОП, мы можем разработать схему КМОП последовательной схемы.

Комбинационная логика против последовательной логики:| Комбинационная логика | Последовательная логика |

| Это тип цифровой логики, состоящей из множества логических схем, и ее выход зависит только от токовых входов. | Это также тип цифровой логики, состоящей из комбинационного элемента, а также элемента памяти, его выход не только зависит от текущего входа, но также может управляться последовательностью предыдущих входов. |

| Его схема относительно дорогостоящая. | Его схема относительно дешевая. |

| Часы отсутствуют в его схеме. | Часы — необходимый элемент в синхронной последовательной схеме. |

| В его схеме нет элемента памяти. | В схеме этой логики должен быть элемент памяти. |

| Схема обратной связи отсутствует. | Для манипулирования прошлыми входами необходима схема обратной связи. |

| Проектировать схему через логические вентили легко. | Здесь мы можем столкнуться со сложностями при проектировании схемы из-за требований к элементам памяти и обратной связи. |

| Обработка результатов происходит сравнительно быстрее. | После рассмотрения каждого аспекта обработка вывода может быть относительно медленнее. |

| Мы можем определить отношения ввода-вывода через таблицу истинности. | Отношения ввода-вывода можно определить с помощью таблицы характеристик, таблицы возбуждений и диаграмм состояний. |

| Требование этой логики в основном состоит в выполнении логических операций. | Требование этой логики для хранения данных, создания счетчика, регистров и т. Д. |

С конечным числом входов и выходов последовательная логическая схема используется для построения конечного автомата. Он может действовать как регистр, счетчик и т. Д. С помощью комбинационной схемы можно создать многие базовые устройства, такие как RAM (оперативное запоминающее устройство), поскольку последовательная логическая схема предоставляет нам возможность хранить данные, которые открывают двери для микропроцессор и арифметическая логическая схема.

Устройства последовательной логики:Выход последовательного логического устройства может управляться текущим входом и предыдущим входом или тактовыми импульсами. Последовательные устройства хранят последние данные в элементе памяти. Благодаря этой возможности хранения данных эти устройства открывают новые способы решения проблемы.

Последовательные устройства — это счетчики, регистры и т. Д.

Последовательные логические микросхемыПреимущества и недостатки последовательной логики:Преимущества последовательной логики:Существенным преимуществом последовательной логики является то, что ее схема содержит элемент памяти, позволяющий хранить данные и создавать регистр, счетчик и микропроцессоры. С помощью тактового импульса он может синхронизировать все элементы схемы независимо от различных задержек распространения и обеспечивать надлежащий выходной сигнал. Выходом можно управлять через текущий вход, прошедшую последовательность входов, а также через тактовый импульс.

Недостатки последовательной логики:Наличие часов и обратной связи в схеме, обработка вывода может быть медленнее. Осложнения схемы могут увеличиваться, что может вызвать трудности при построении схемы. Результат иногда может быть неопределенным.

Последовательная логическая история :Последовательная логика используется для разработки конечного автомата, который является основным строительным блоком всех цифровых схем. Для дополнительной информации нажмите сюда.

В. Как ОЗУ компьютера использует последовательную логику?Q.

ПЗУ / ОЗУ — это комбинационная или последовательная схема?Отвечать: — ROM (постоянная память) состоит из кодировщика, декодера, мультиплексора, схемы сумматора, схемы вычитания и т. д. Кодер — это комбинационная схема, которая в основном преобразует одну форму данных в другой формат, например, десятичные данные в двоичные данные. Декодер здесь тоже комбинационная схема. То же самое и с мультиплексором, сумматором и вычитателем. Все это здесь комбинационная схема.

В ПЗУ мы не можем изменять содержимое памяти. Следовательно, вывод ПЗУ зависит только от ввода. Таким образом, нет требований к прошлому значению ввода или вывода. Итак, ПЗУ имеет в своей схеме только комбинационную схему.

В то время как для RAM (оперативная память), PROM (программируемая постоянная память), EPROM (стираемая программируемая постоянная память), EEPROM (электрически стираемая программируемая постоянная память) имеет память, которая может изменяться. В случае PROM его можно запрограммировать один раз после изготовления. RAM, EPROM, EEPROM, где можно изменить состояние. В этом типе памяти нам всегда нужна последовательная схема для правильной работы, так как здесь есть необходимость в прошлых входных и выходных значениях. Текущий вывод может быть изменен предыдущей последовательностью данных. Следовательно, этот тип памяти требует последовательной схемы.

В. Является ли сумматор с переносом пульсации примером последовательной схемы. Почему?Ответ: — Сумматор с переносом пульсаций — это цифровая схема, которая выполняет арифметические операции сложения двух различных двоичных чисел. Он может быть спроектирован с каскадным подключением соединителя полного сумматора к выходу переноса, где выход переноса полного сумматора соединяется со входом следующего полного сумматора. Как мы видим здесь, один полный сумматор подключен к следующему сумматору в качестве обратной связи, здесь выход одного полного сумматора может управлять выходом другого полного сумматора. Итак, здесь мы видим, что прошлый вывод может управлять текущим выводом схемы. Поэтому сумматор с переносом пульсаций можно рассматривать как последовательную схему.

В. Почему неблокирующие назначения используются в последовательных схемах в Verilog ?Ответ: — В неблокирующих назначениях, когда происходит первый шаг, оценка выражения правой части неблокирующего оператора происходит после того, как эта ревизия левой части неблокирующего оператора принимает место, а в конце временного шага выполняется оценка левого оператора.

Поскольку неблокирующие назначения не блокируют оценку каких-либо последовательных операторов, выполнение этих назначений происходит одновременно или параллельно. Итак, для создания последовательной логической схемы в Verilog мы всегда должны учитывать синхронизированные блочные и неблокирующие назначения. С помощью неблокирующих назначений мы можем исключить состояние гонки вокруг последовательной схемы.

В. Определите асинхронные последовательные логические схемы ?Ответ: объяснено в разделе асинхронных последовательных логических схем.

Q.

Сколько триггеров требуется для построения последовательной схемы с 20 состояниями.Отвечать: — Вьетнамки является основным элементом памяти в последовательной цифровой схеме, которая имеет два стабильных состояния, и эти два состояния могут быть представлены как «0» и «1», но одновременно может хранить один бит.

Согласно двоичному кодированию n число триггеров может представлять максимум количество состояний.

Здесь нам понадобится 20 состояний последовательной схемы.

So

После решения приведенного выше уравнения получаем

Что касается, там всего 16 состояний, а нам нужно 20 состояний. Здесь у нас есть еще 4 состояния для работы, поэтому мы должны выбрать число больше 4. Итак, мы будем использовать n = 5, где имеет 32 состояния, что достаточно для 20 состояний.

В то время как при однократном кодировании количество триггеров, необходимых для n состояний, равно n. Итак, нам нужно 20 шлепанцев для 20 состояний.

В. Как можно сделать последовательный чип только из комбинационных чипов?Ответ: — Когда комбинационная логическая схема соединена с цепью обратной связи, результирующая схема является последовательной логической схемой.

Если мы перейдем к схеме основных элементов памяти, таких как триггер, защелки, мы увидим, что триггер может быть создан с помощью логических элементов И, И НЕ, ИЛИ и т. Д., Когда они связаны с обратной связью. друг другу.

Рис. Это схема триггера SR.На схеме показаны два логических элемента И-НЕ, соединенные трактом обратной связи, который формирует схему триггера SR. Таким образом, комбинационная схема может быть преобразована в последовательную схему.

В. Принцип работы нестабильных последовательных логических схемОтвет: — Нестабильная последовательная логическая схема не имеет стабильного состояния на выходе, т.е. она нестабильна ни в каком состоянии. Выход непрерывно переходит из одного состояния в другое. Этот тип схемы может использоваться в качестве генератора, такого как генератор для генерации тактового импульса в цепи. Примером нестабильной схемы является кольцевой генератор.

Дополнительные статьи нажмите сюда

О Sneha Panda

Я получил образование по специальности «Прикладная электроника и приборостроение». Я любознательный человек. У меня есть интерес и опыт в таких областях, как преобразователь, промышленные приборы, электроника и т. Д. Мне нравится узнавать о научных исследованиях и изобретениях, и я верю, что мои знания в этой области будут способствовать моим будущим усилиям.

LinkedIn ID — https://www.linkedin.com/in/sneha-panda-aa2403209/

4 Меню Редактирования | Справочное руководство Capture 2020

4.1 Отмена

Эта команда отменяет последнюю модификацию.

4.2 Восстановить

Эта команда повторяет ранее отмененную модификацию.

4.3 Клонирование.

Эта команда позволяет создать одну или несколько копий выбранного объекта или группы объектов. Используйте зеленый куб навигатора, чтобы ориентироваться в направлениях X, Y и Z в текущем представлении. Значения смещения применяются постепенно, что означает, что если вы укажете две копии со смещением 2 м, то первая копия будет создана на расстоянии 2 м от оригинала, а вторая-на расстоянии 4 м от оригинала и т. д. Обратите внимание, что угол поворота учитывает размещение указателя вращения.

Например, вы можете создать круг из десяти ящиков, выбрав ящик, переместив указатель вращения из круга, выбрав команду клонирования, введя угол 36 градусов (полный круг 360 градусов, разделенный на десять объектов) и 9 копий (поскольку один ящик уже существует, результат будет 10 ящиков).

4.4 Заменить

Чтобы заменить приборы в вашем проекте, Сначала выберите приборы, которые вы хотите заменить, затем активируйте режим замены с помощью этой команды, найдите тип прибора, который вы хотите использовать вместо него, на Вкладке библиотека и, наконец, перетащите его на один из выбранных приборов.

Таким образом, все выбранные приборы заменяются на новый выбранный тип прибора. Вы также можете поместить новый тип прибора на любой другой прибор или заменяемый объект, который не выбран, но таким образом вы можете заменить только один прибор или объект за один раз.

4.5 Удалить

Эта команда удаляет выбранные в данный момент объекты.

4.6 Группа

Эта команда создает группу из выбранных в данный момент объектов.

4.7 Разрыв Группы

Эта команда разбивает все выбранные в данный момент группы без удаления их содержимого.

4.8 Трансформация

Эта команда позволяет вам перемещать приборы на точное расстояние или поворачивать на нужное количество градусов. Используйте зеленый куб навигатора, чтобы ориентироваться в направлениях X, Y и Z в текущем виде. Обратите внимание, что угол поворота учитывает размещение привязки вращения и всегда выполняет групповое вращение.

4.9 Выравнивание

Эта команда позволяет выбрать группу объектов и быстро выровнять их по длинной определенной оси. Какая бы функция выравнивания ни использовалась, она всегда имеет отношение к Виду проекта, в котором вы ее используете. Доступные параметры отображаются справа.

4.10 Распределение

Эта команда позволяет очень быстро выбрать группу объектов или приборов и равномерно распределить их по вертикальной или горизонтальной оси. Это чрезвычайно полезен для быстрого построения линий объектов.

4.11 Удаление Корректировки Графика

Эта команда удаляет все корректировки графика, сделанные для выбранных объектов. Эта команда доступна только при включенной корректировке графика.

4.12 Мэппинг матириала

Эта команда используется для включения режима отображения материалов, в котором текстурированные материалы могут быть расположены / нанесены на объекты.

Текстура материала очерчена и перечеркнута пунктирными линиями. Перемещайте и вращайте текстуру материала с помощью указатель поворота, как если бы перемещали и вращали любой другой объект.

Чтобы выйти из режима отображения материала, используйте кнопку Выход в правом нижнем углу навигатора выбора.

4.12.1 Размер мэппинга

Эта команда автоматически настраивает отображение материала таким образом, чтобы оно точно заполняло объем выбранных объектов.

При одновременном отображении материалов нескольких объектах, эта команда также выравнивает отображение всех материалов.

4.12.2 Сброс мэппинга

Эта команда сбрасывает мэппинг материала в состояние по умолчанию.

4.12.3 Выбор региона >

Эта команда выбирает ранее определенную область мэппинга. См.Редактирование регионов.. о том, как определить регион мэппинга.

4.12.4 Очистить регион

Эта команда очищает любую выбранную область отображения.

4.12.5 Редактирование Регионов..

Эта команда открывает окно Мэппинга регионов. В этом окне можно определить подобласти отображения. Это полезно, когда текстура материала разделена на сегменты, которые должны быть нанесены на отдельные объекты.

Установите Ширину разрешения/Высоту разрешения в соответствии с разрешением текстуры (или носителя). Используйте свойства X / Y Offset и Width/Height для определения субрегиона.

4.13 Модель >

4.13.1 Скрыть Отвлекающие границы

Этой команды скрывает отвлекающий многоугольников, т. е. границы многоугольников, которые лежат на плоских поверхностях, оставляя только края многоугольников на углах. Это уменьшает визуальный беспорядок импортируемых объектов. Это также может оказать небольшое положительное влияние на производительность рендеринга каркаса.

4.13.2 Преобразование линий в трубы

Эта команда преобразует все линии в трубы. Это полезно для преобразования линейных чертежей ферменных конструкций в твердотельную геометрию, это можно ы увидеть на Проектных видах в режиме Реального времени.

Созданные трубы представляют собой просто полые цилиндры, которые не предполагают какой-либо специализированной функциональности, которая поставляется с реальными фермами, такими как стыковка между фермами или ориентирование расположения приборов.

4.14 Назначить последовательность>

4.14.1 Последовательности Блок

Эта команда позволяет установить последовательность для выбранных объектов. Вы можете указать Префикс, а также Постфикс к нумерации. Свойство Старт определяет первое число диапазона. Свойство Совмещение позволяет создавать такие ряды, как 1, 1, 2, 2, 3, 3 а свойство Пробел позволяет создавать ряды, такие как 1, 3, 5, 7. обратите внимание, что если вы выбираете объекты вручную один за другим, это определяет порядок нумерации. Однако если вы выберете их, проведя мышью по объектам, порядок расположения объектов не будет определен.

4.14.2 Последовательная Схема

Последовательная схема по существу работает так же, как и последовательное объединение, за исключением того, что вы присваиваете номера схем свойству канала светильников. Вы можете указать Префикс, а также Постфикс к нумерации.

4.14.3 Последовательный Патч

Эта команда позволяет последовательно патчить приборы. Порядок, в котором вы выбираете приборы, будет соответствовать порядку их применения к патчу. Вы можете выбрать поток Юниверса и начать адрес, введя адрес как Юниверс.Адрес. Например, ввод 2.1 приведет к тому, что приборы начнут работать с первого канала в потокеDMX 2. У вас также есть возможность оставить пробел между приборами, если вы хотите.

4.14.4 Последовательность Каналов

Последовательность каналов по существу работает так же, как и последовательное объединение, за исключением того, что вы присваиваете номера приборов свойству канала приборов. Поскольку это число, а не текст, вам не разрешается указывать префикс или постфикс.

4.15 Фокус

Эта команда переводит прибор в режим фокусировки. В режиме фокусировки клик по объектам фокусирует все выбранные приборы на заданной точке, а не выделяет объекты под мышкой. Однако щелчок по приборам для их выбора все еще возможен, так что другие приборы могут быть сфокусированы без предварительного выхода из режима фокусировки.

Если в проекте присутствуют плоскости фокусировки, то в правом верхнем углу навигатора выбора в режиме фокусировки отображается дополнительный набор кнопок. Эти кнопки переключают стиль рендеринга плоскостей фокусировки.

- Невидимый

- Сетка, полезная в качестве инструмента наведения и выравнивания при фокусировке пучка света

- Сплошной, полезные для устранения визуально отвлекающих материалов

- Тепловая карта, полезная для оценки уровня освещенности

Дополнительные сведения о плоскостях фокусировки см. В разделе Плоскость фокусировки

Чтобы выйти из режима фокусировки, используйте кнопку выхода в правом нижнем углу навигатора выбора.

4.16 Удалить Фильтры/Гобо

Эта команда удаляет все фильтры или гобо из выбранных приборов.

4.17 Отмена патча.

Эта команда отменяет патч выбранных приборов.

4.18 Выберите Все >

4.18.1 По слоям

Эта команда выбирает все остальные объекты в том же слое(слоях), что и уже выбранные объекты.

4.18.2 По примыкающим фермам

Эта команда выбирает все остальные фермы, подключенные к уже выбранным фермам.

4.18.3 По близости на ферм

Эта команда выбирает все приборы, достаточно близкие к выбранной ферме(фермам).

4.18.4 По типу прибора

Эта команда выбирает все приборы того же типа, что и уже выбранные приборы.

4.18.5 По названию чертежного блока

Эта команда выбирает все остальные импортированные объекты с тем же именем блока чертежа, что и уже выбранные импортированные объекты.

4.18.6 По управлению движения

Эта команда выбирает все объекты, движение которых контролируется уже выбранным объектом(объектами).

4.19 Выбирать Только >

4.19.1 Аннотация

Эта команда отменяет выбор всех объектов, кроме аннотаций выбранных объектов.

4.20 Отменить выбор

Эта команда отменяет выбор всех объектов.

Введение в последовательные схемы — GeeksforGeeks

A Последовательная схема — это комбинационная логическая схема, которая состоит из входной переменной (X), логических вентилей (вычислительная схема) и выходной переменной (Z).

Вниманию читателя! Не прекращайте учиться сейчас. Практикуйте экзамен GATE задолго до самого экзамена с помощью предметных и общих викторин, доступных в курсе GATE Test Series .

Изучите все концепции GATE CS с бесплатными живыми классами на нашем канале YouTube.

Комбинационная схема выдает выходной сигнал только на основе входной переменной, а последовательная схема выдает выходной сигнал на основе текущего входного сигнала и предыдущих входных переменных . Это означает, что последовательные схемы включают элементы памяти, способные хранить двоичную информацию. Эта двоичная информация определяет состояние последовательной цепи в то время. Защелка, способная хранить один бит информации.

Как показано на рисунке, существует два типа входов для комбинационной логики:

- Внешние входы, которые не контролируются схемой.

- Внутренние входы, которые являются функцией предыдущих состояний выхода.

Вторичные входы — это переменные состояния, создаваемые элементами хранения, тогда как вторичные выходы — возбуждения для элементов хранения.

Типы последовательных схем — Существует два типа последовательных схем:

- Асинхронная последовательная схема — Эти схемы не используют тактовый сигнал , но используют импульсы входов.Эти схемы на быстрее на , чем синхронные последовательные схемы, потому что есть тактовый импульс и они меняют свое состояние немедленно при изменении входного сигнала. Мы используем асинхронные последовательные схемы, когда важна скорость работы и независимых внутренних тактовых импульсов.

Но эти схемы более сложны в разработке , и их выходная мощность неопределенная .

- Синхронная последовательная схема — Эти схемы используют тактовый сигнал и входы уровня (или импульсные) (с ограничениями на ширину импульса и распространение цепи).Выходной импульс такой же длительности, как и тактовый импульс для синхронизированных последовательных схем. Поскольку они ждут прибытия следующего тактового импульса для выполнения следующей операции, эти схемы на бит медленнее по сравнению с асинхронными. Выход уровня изменяет состояние в начале входного импульса и остается в нем до следующего входного или тактового импульса.

Мы используем синхронную последовательную схему в синхронных счетчиках, триггерах и при разработке машин управления состоянием MOORE-MEALY.

Мы используем последовательные схемы для разработки счетчиков, регистров, RAM, MOORE / MEALY Machine и других машин с сохранением состояния.

GATE CS Corner Questions

Выполнение следующих вопросов поможет вам проверить свои знания. Все вопросы задавались в GATE в предыдущие годы или в пробных тестах GATE. Настоятельно рекомендуется попрактиковаться в них.

- GATE CS 2010, вопрос 65

- GATE CS 1999, вопрос 33

- GATE CS 2014 (набор 3), вопрос 65

Ссылки —

Последовательные схемы

Последовательная логика — Википедия

пользователя Mithlesh Upadhyay.Если вам нравится GeeksforGeeks и вы хотите внести свой вклад, вы также можете написать статью, используя write.geeksforgeeks.org, или отправить свою статью по адресу [email protected]. Посмотрите, как ваша статья появляется на главной странице GeeksforGeeks, и помогите другим гикам.

Пожалуйста, напишите комментарии, если вы обнаружите что-то неправильное, или если вы хотите поделиться дополнительной информацией по теме, обсуждаемой выше.

Синхронная последовательная цепь — обзор

6.7 Триггер JK

Описанные ранее схемы защелки не подходят для работы в синхронных последовательных схемах из-за их прозрачности.Для синхронных схем предусмотрен тактовый сигнал, который управляет временем, в которое выходы элементов памяти могут изменять состояние. В синхронной схеме в качестве основного элемента памяти используются триггеры, типичным примером которых является JKFF. В отличие от защелок, они реагируют только на переход на тактовом входе или на изменение асинхронного ввода, такого как Clear.

Символьное представление JKFF показано на рисунке 6.14 (a), а таблица состояний, описывающая его логическую работу, — на рисунке 6.14 (б). Логическая работа этого триггера отличается в одном отношении от таковой защелки SR тем, что допускается одновременное равенство f и K 1. Когда J = K = 1, триггер flop переключает , т.е. в строке 7 триггер меняет состояние с 0 на 1, а в строке 8 происходит обратное действие. В строках 4 и 5 выполняются обычные операции сброса и настройки, как описано для защелки SR в разделе 6.3.

Рисунок 6.14. JK-триггер (a) символическое представление (b) таблица состояний (c) представление JK-триггера с помощью SR-защелки и двух вентилей И (d) график K-карты состояния Q t + δt (e) диаграмма (f) управляющая таблица

Изучение таблицы состояний показывает, что триггер включен в строках 5 и 7, а в строках 4 и 8 он выключен.Условие включения для Q :

S = JK¯Q¯ + JKQ¯ = JQ¯

Условие выключения для Q :

R = J¯KQ + JKQ = KQ

Эти два уравнения указывают, что триггер JK можно рассматривать как защелку SR, перед которой стоят два логических элемента И, которые реализуют функции включения и выключения соответственно, как показано на рисунке 6.14 (c).

Характеристическое уравнение триггера JK получается путем нанесения текущих состояний состояния на K-карту, показанную на рисунке 6.14 (г). После упрощения характеристическое уравнение может быть записано как

Qt + δt = (JQ¯ + K¯Q)

Диаграмма состояний, описывающая конечное поведение триггера, показана на рисунке 6.14 (e). Предполагая, что триггер синхронизирован и в настоящее время находится в состоянии Q = 0 с J = 1 и Ck , изменяющимся с 0 на 1, он переходит в состояние Q = 1. Аналогично, в состоянии Q = 1 с K = 1 и Ck при изменении от 0 до 1 происходит переход к Q = 0.

Управляющая таблица для триггера JK, полученная из состояния стабильного, показана на рисунке 6.14 (f). Сравнивая управляющий стол защелки SR и триггера JK на рисунках 6.7 и 6.14 (f), можно заметить, что триггер JK имеет больше условий ввода «X» или «безразлично». На практике увеличенное количество терминов «безразлично» приводит к упрощению комбинационной логики при проектировании последовательной логической схемы.

Триггер JK может быть реализован путем соединения выходов двух логических элементов И на рисунке 6.14 (c) к входам S и R управляемой защелки, показанной на рисунке 6.10 (a). Выходы Q и Q¯ этой защелки и ее тактовых соединений подаются на входы двух логических элементов И вместе с входами J и K , как показано на рисунке 6.15 (a). Обратите внимание, что логические элементы И формируются из двух пар логических элементов И-НЕ в каскаде, а именно: g 5 и g 7 , а также g 6 и g 8 . Очевидно, что вентили g 7 и g 1 , а также вентили g 8 и g 2 дают двойную инверсию и являются избыточными, тем самым уменьшая JKFF до массива только из четырех вентилей, как показано на рисунке 6. .15 (б).

Рисунок 6.15. (а) реализация JK-триггера в NAND и (б) его сокращенная форма

Как и в случае с управляемыми защелками, описанными ранее в этой главе, триггер отключается, когда Ck = 0, и активен, когда Ск = 1. К сожалению, соединение, показанное на рисунке 6.15 (b), демонстрирует нестабильность, когда J = K = 1 и Ck = 1 из-за обратной связи дополнительных выходных сигналов на входе. Диаграмма состояний показывает, что в этих условиях выход Q является колебательным и будет оставаться таковым до тех пор, пока Ck не выполнит переход 1 → 0, когда часы отключены.

Основы работы с последовательными цепями

В этом руководстве мы узнаем о последовательных схемах, что такое последовательная логика, чем последовательные схемы отличаются от комбинационных схем, различные типы последовательных схем, некоторые важные основы работы с последовательными схемами и многое другое.

Комбинированная логика и последовательная логика являются строительными блоками проектирования цифровых систем. Комбинационные схемы включают в себя мультиплексоры, демультиплексоры, кодеры, декодеры и т. Д., Тогда как последовательные схемы — это защелки, триггеры, счетчики, регистры и т. Д.

Чтобы узнать больше об основах последовательной логики и всех ее элементов, таких как часы, запуск, синхронные, асинхронные схемы и т. Д., Продолжайте читать следующее руководство.

Введение

Последовательные логические схемы — это схемы, выход которых зависит не только от текущего значения входа, но и от предыдущих значений входного сигнала (истории значений), что в отличие от комбинационных схем, где выход зависит только от текущих значений входного сигнала. ввод в любой момент времени.Последовательную схему можно рассматривать как комбинационную схему со схемой обратной связи. Последовательная схема использует элемент памяти, такой как триггеры, в качестве схемы обратной связи для сохранения прошлых значений. Блок-схема последовательной логики показана ниже.

Последовательные логические схемы используются для создания конечных автоматов, которые являются основным строительным блоком во всех цифровых схемах, а также в схемах памяти. По сути, все схемы в практических цифровых устройствах представляют собой смесь комбинационных и последовательных логических схем.

Пример:

Как правило, мы сталкиваемся с множеством счетчиков в нашей повседневной жизни, чтобы подсчитать количество объектов. Например, чтобы подсчитать количество зрителей, которые входят или выходят из зала или подсчитывают количество транспортных средств на стоянке. Это когда любой человек входит в аудиторию. счетчик увеличивает свое значение в зависимости от его текущего значения. Точно так же он уменьшает свою стоимость в зависимости от своей предыдущей и текущей стоимости. Таким образом, Counter сохраняет текущее состояние счетчика для выполнения следующей операции.

Аналогичен последовательным цепям, которые изменяют свое состояние в соответствии с предыдущими и текущими сигналами.

К началу

Комбинационные схемы и последовательные схемы

| Комбинированные схемы | Последовательные схемы |

|---|---|

| Выход зависит только от текущей стоимости входов. | Выход зависит как от текущего, так и от предыдущего значения состояния входов |

| У этих схем не будет памяти, так как их выходы изменяются с изменением входного значения. | Последовательные схемы имеют своего рода память, поскольку их выход изменяется в соответствии с предыдущими и текущими значениями. |

| Нет обратной связи. | В последовательной схеме выходы подключены к ней как канал обратной связи. |

| Используется в основных логических операциях. | Используется при проектировании запоминающих устройств. |

| Реализовано в: Схема полусумматора, схема полного сумматора, мультиплексоры, демультиплексоры, декодеры и кодеры. | Реализовано в: ОЗУ, регистрах, счетчиках и других машинах, сохраняющих состояние. |

К началу

Тактовый сигнал в последовательных цепях

Тактовый сигнал играет решающую роль в последовательных цепях. Часы — это сигнал, который периодически колеблется между логическим уровнем 0 и логическим уровнем 1. Прямоугольная волна с постоянной частотой является наиболее распространенной формой тактового сигнала. Тактовый сигнал имеет «края». Это моменты, когда часы меняются с 0 на 1 (положительный фронт) или с 1 на 0 (отрицательный фронт).

Сигналы

Clock управляют выходами последовательной схемы, то есть определяют, когда и как элементы памяти изменяют свои выходы. Если последовательная схема не имеет на входе тактового сигнала, выходной сигнал схемы будет изменяться случайным образом. Так что они не могут сохранять свое состояние до прихода следующего входного сигнала. Но последовательные схемы с тактовым входом сохранят свое состояние до наступления следующего фронта тактового сигнала.

К началу

Классификация последовательных цепей

По входному тактовому сигналу последовательные схемы подразделяются на два типа.

- Синхронная последовательная цепь

- Асинхронная последовательная цепь

Синхронные последовательные схемы

Определение:

В синхронной последовательной схеме выход зависит от текущего и предыдущего состояний входов в синхронизированных экземплярах. В схемах используется элемент памяти для хранения предыдущего состояния. Элементы памяти в этих схемах будут иметь часы. Все эти тактовые сигналы управляются одним и тем же тактовым сигналом.

- Используя тактовый сигнал, изменения состояния будут происходить во всех элементах памяти.

- Эти схемы немного медленнее по сравнению с асинхронными, потому что они ждут прибытия следующего тактового импульса для выполнения следующей операции.

- Эти схемы могут быть синхронизированными или импульсными.

- Синхронные последовательные схемы, которые используют тактовые импульсы на своих входах, называются синхронизированными последовательными схемами. Они очень стабильны.

- Последовательные цепи, которые изменяют свое состояние с помощью импульса, и они называются импульсными или несинхронизированными последовательными цепями.

Где мы используем синхронные последовательные схемы ??

• Используется при разработке машин управления состоянием MOORE-MEALY.

• Используются в синхронных счетчиках, триггерах и т. Д.

К началу

Ограничения синхронных последовательных цепей

- Все триггеры в синхронных последовательных схемах должны быть подключены к тактовому сигналу. Тактовые сигналы — это очень высокочастотные сигналы, а распределение тактовых импульсов потребляет и рассеивает большое количество тепла.

- Критический путь или самый медленный путь определяет максимально возможную тактовую частоту. Следовательно, они медленнее, чем асинхронные схемы.

Асинхронные последовательные схемы

Определение

Последовательные схемы, которые не работают с тактовыми сигналами, называются «асинхронными последовательными схемами».

- Эти схемы изменят свое состояние сразу же при изменении входного сигнала.

- Поведение схемы определяется сигналами в любой момент времени и порядком изменения входных сигналов.

- Они не работают в импульсном режиме.

- Они обладают лучшими характеристиками, но их сложно спроектировать из-за проблем с синхронизацией.

- В основном мы используем асинхронные схемы, когда нам требуются операции с низким энергопотреблением.

- Они быстрее, чем синхронные последовательные схемы, поскольку им не нужно ждать какого-либо тактового сигнала.

Где мы используем асинхронные последовательные схемы ??

Они используются, когда важна скорость работы.Поскольку они не зависят от внутреннего тактового импульса, они работают быстро. поэтому они используются в схемах быстрого реагирования.

- Используется для связи между двумя устройствами, имеющими свои собственные независимые часы.

- Используется, когда требуется улучшенная внешняя обработка ввода.

Ограничения асинхронных последовательных цепей

- Асинхронные последовательные схемы труднее спроектировать.

- Хотя они имеют более высокую производительность, их производительность сомнительна.

Наверх

Обратная связь в последовательных цепях

Комбинационные схемы не требуют никакой обратной связи, поскольку выходы полностью зависят от текущего значения входа. Но в случае последовательных схем выходы зависят от прошлых значений входных данных вместе с текущими значениями. Чтобы задействовать элемент памяти как триггер, в схему необходимо ввести обратную связь. Например, рассмотрим простую схему обратной связи, как показано ниже.

Если 0 является входом для инвертора в экземпляре, этот 0 будет распространяться, и на выходе будет 1.Эта 1 возвращается как ввод. Эта 1 будет распространяться, и на выходе будет 0. Процесс повторяется, и результатом является непрерывное колебание выходного сигнала между 0 и 1. В этом сценарии нет стабильного состояния.

Теперь рассмотрим следующий пример подключения двух инверторов, как показано.

Здесь два инвертора подключены друг к другу, причем выход второго инвертора подается обратно на вход первого инвертора. Если 0 является входом для первого инвертора в экземпляре, он распространяется через первый инвертор, а выход равен 1.Эта 1 вводится во второй инвертор и распространяется через него. Выход второго инвертора равен 0, который возвращается на первый инвертор. Но на входе первого инвертора уже 0 и, следовательно, никаких изменений не происходит. Считается, что схема находится в стабильной цепи. Другое стабильное состояние может быть получено, когда на входе первого инвертора 1.

К началу

Защелки и Вьетнамки

Защелка

Защелка — это основной строительный элемент в последовательных цепях.Защелки не имеют тактового сигнала, то есть представляют собой асинхронные последовательные схемы.

• Защелки состоят из статических ворот.

• Защелка — это бистабильный мультивибратор, т.е. он имеет два стабильных состояния и может переключаться между этими состояниями.

• Защелки будут иметь обратную связь от выхода. Таким образом, они изменяют свой выход в любой момент, используя предыдущее и текущее состояния входных сигналов.

• Когда включено, на выход защелки постоянно влияет его вход i.е. выход изменяется немедленно, когда изменяется вход. При отключении состояние защелки остается постоянным, то есть запоминает свое предыдущее значение. В качестве управляющего сигнала используется тактовый или разрешающий сигнал.

• Защелки постоянно проверяют все входы и, соответственно, меняют свой выход при включении.

Пример: защелка S-R — это пример простой защелки.

Пример: защелка S-R — это пример простой защелки.

Триггер

Триггер также является строительным блоком синхронных последовательных схем.Имеет два стабильных состояния. Он может хранить один бит информации. Шлепанцы будут иметь тактовый сигнал. Их состояние меняется в зависимости от тактового импульса. Эти устройства будут иметь два состояния и путь обратной связи.

- Flip-Flop чувствителен к краям. Они изменят свое состояние при переходе тактового сигнала с низкого на высокий или с высокого на низкий.

- После перехода синхросигнала с 0 на 1 или с 1 на 0, т.е. когда часы находятся на постоянном значении 0 или 1, состояние остается неизменным даже при изменении входа.

Пример : JK Flip-Flop.

ПРИМЕЧАНИЕ : Единственное различие между защелками и триггерами состоит в том, что защелка чувствительна к уровню управляющего сигнала (тактовый или разрешающий), в то время как триггер чувствителен к фронту управляющего сигнала (обычно тактового сигнала).

Запуск

Определение

Изменение выхода триггера может быть выполнено путем небольшого изменения входного сигнала. Это небольшое изменение может быть выполнено с помощью тактового импульса.Этот тактовый импульс известен как импульс запуска.

Триггер называется «запускаемым», когда на вход подается импульс запуска, который вызывает изменения на выходе. Триггеры — это базовые компоненты регистров и счетчиков, которые хранят данные в виде многобитовых чисел. Несколько триггеров соединены в последовательную цепь, и все эти триггеры требуют запускающего импульса. Количество импульсов запуска, подаваемых на вход, определяет количество в счетчике.

Существует два типа запуска: запуск по уровню и запуск по фронту

Запуск уровня

Процесс запуска, в котором изменение состояния выхода соответствует активному уровню входов, называется «запуском по уровню».

Срабатывание уровня бывает двух типов, это

1. Запуск высокого уровня.

2. Запуск по низкому уровню.

Запуск высокого уровня

При высокоуровневом запуске выходной сигнал триггера изменяется только тогда, когда его разрешающий вход находится в высоком состоянии, т.е. логическом высоком уровне или логической 1. Символьное представление триггера высокого уровня показано ниже.

Запуск по низкому уровню

При запуске по низкому уровню выход триггера изменяется только тогда, когда его вход разрешения находится в низком состоянии i.е. низкий логический уровень или логический 0. Ниже показано символическое представление срабатывания низкого уровня. Запуск по низкому уровню обычно определяется по пузырьку на входе часов.

Запуск по краю

В режиме запуска по фронту выход изменяется только тогда, когда входы присутствуют на любом из переходов тактового импульса, то есть либо от низкого уровня к высокому (от 0 до 1), либо от высокого к низкому (от 1 до 0).

Запуск по фронту бывает двух типов, это

1.Запуск по положительному фронту.

2. Срабатывание по отрицательному фронту.

Срабатывание по положительному фронту

При запуске по положительному фронту выход изменяется только тогда, когда вход находится на положительном фронте входного тактового импульса, то есть при переходе от низкого уровня к высокому (от 0 до 1).

Метод запуска по положительному фронту используется, когда триггер должен реагировать при переходе от низкого уровня к высокому. Символьное представление срабатывания по положительному фронту показано ниже.

Срабатывание по отрицательному фронту

При запуске по отрицательному фронту выход изменяется только тогда, когда вход находится на отрицательном фронте входа i тактового импульса.е. переход от высокого к низкому (от 1 до 0).

Метод запуска по отрицательному фронту используется, когда триггер должен реагировать при переходе от высокого уровня к низкому. Символьное представление срабатывания отрицательного фронта показано ниже.

Триггер по фронту лучше, чем по уровню

Лучше использовать запуск по фронту, а не по уровню. Это связано с тем, что запуск по уровню может вызвать нестабильность в схеме для конкретного случая триггера, запускаемого по уровню, когда тактовый импульс подается на вход одновременно с изменением выхода триггера.Обратная связь от выхода к входу вызывает эту нестабильность. Чтобы избежать этой нестабильности, используются триггеры с синхронизацией по фронту.

К началу

Асинхронных последовательных цепей: определение и преимущества

Асинхронные последовательные схемы

Давайте рассмотрим асинхронных последовательных схем , которые состоят из триггеров . Триггер — это базовый элемент памяти, который может хранить один бит информации. Асинхронные последовательные схемы изменяют свои состояния и выходные значения всякий раз, когда происходит изменение входных значений.

В асинхронных последовательных схемах входы являются уровнями и отсутствуют тактовые импульсы. Входные события управляют схемой. Другими словами, схема называется асинхронной, если она не управляется периодическим тактовым сигналом для синхронизации своих внутренних состояний.

Например, рассмотрим счетчик пульсаций, который является асинхронным. В счетчике пульсаций:

- Первый триггер управляется внешними часами.

- Для остальных триггеров часы для каждого триггера управляются выходом из предыдущих триггеров.

Триггеры

Чтобы быть более конкретным, триггер — это запоминающее устройство, управляемое часами. Это означает, что триггер сохраняет входное значение и отправляет сохраненное значение как выход только при наличии тактового сигнала.

Если мы соединим много триггеров вместе, они могут сохранить данные. Эти данные могут быть числовым символом в памяти компьютера или любой другой информацией.

На следующем рисунке представлен D-триггер, популярный тип триггера, и его таблица истинности:

На следующем рисунке представлена временная диаграмма для предыдущего триггера:

В этом примере триггер оценивает свой вход D и изменяет свои выходы Q и Q ‘только на переднем фронте сигнала тактовой частоты (CLK).