Как работает схема делителя частоты на 10. Какие компоненты используются в схеме делителя частоты. Для чего применяются делители частоты в электронике. Какие бывают виды делителей частоты.

Принцип работы делителя частоты на 10

Делитель частоты на 10 представляет собой электронную схему, которая уменьшает частоту входного сигнала в 10 раз. Его основная задача — преобразовать высокочастотный сигнал в сигнал более низкой частоты.

Принцип работы такого делителя основан на использовании счетчика импульсов. Схема считает входящие импульсы и выдает выходной сигнал после каждого 10-го импульса. Таким образом, частота выходного сигнала оказывается в 10 раз ниже частоты входного.

Основные компоненты схемы делителя на 10:

- Счетчик импульсов (например, микросхема К155ИЕ4)

- Логические элементы для формирования выходного сигнала

- Цепи синхронизации и сброса счетчика

Виды схем делителей частоты

Существует несколько основных типов схем делителей частоты:

- Цифровые делители на логических элементах и триггерах

- Делители на счетчиках импульсов

- Аналоговые делители на операционных усилителях

- Делители на системах ФАПЧ (фазовой автоподстройки частоты)

Какой тип делителя выбрать? Это зависит от требуемого коэффициента деления, рабочей частоты, точности и других параметров.

Применение делителей частоты в электронике

Делители частоты находят широкое применение в различных областях электроники и радиотехники:

- Системы связи — для согласования частот в приемопередающей аппаратуре

- Измерительная техника — в частотомерах, анализаторах спектра

- Цифровая электроника — для синхронизации работы узлов устройств

- Радиолокация — в системах обработки сигналов

- Бытовая электроника — в синтезаторах частот

Где конкретно используются делители частоты на 10? Такие схемы часто применяются для преобразования высокочастотных сигналов в более низкочастотные, удобные для дальнейшей обработки.

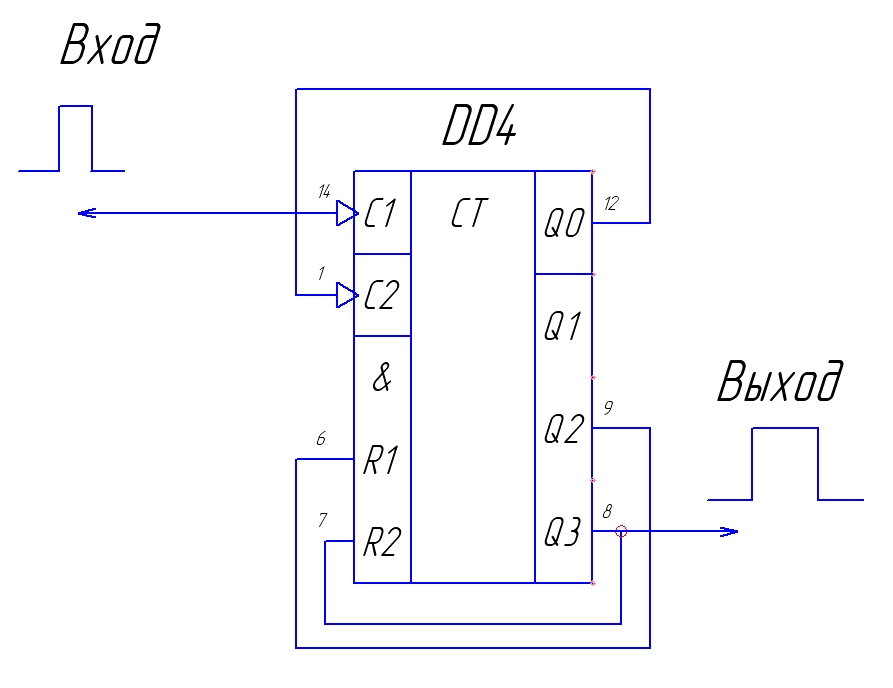

Схема делителя частоты на счетчике К155ИЕ4

Рассмотрим пример построения делителя частоты на 10 с использованием микросхемы К155ИЕ4:

- К155ИЕ4 — четырехразрядный двоично-десятичный счетчик

- Входной сигнал подается на вход С микросхемы

- С выхода Q3 снимается выходной сигнал с частотой в 10 раз ниже входной

- Для сброса счетчика используется вход R

Такая схема обеспечивает надежное деление частоты в широком диапазоне входных частот. Какие преимущества дает использование специализированной микросхемы-счетчика? Это простота схемы, высокая помехоустойчивость и стабильность работы.

Особенности проектирования делителей частоты

При разработке схем делителей частоты необходимо учитывать ряд факторов:

- Максимальную рабочую частоту элементов схемы

- Погрешность деления и стабильность частоты выходного сигнала

- Нагрузочную способность выхода

- Потребляемую мощность

- Помехоустойчивость

Как обеспечить высокую точность деления? Для этого используют прецизионные компоненты, термокомпенсацию, экранирование от помех.

Расчет параметров делителя частоты

При проектировании делителя частоты на 10 необходимо произвести ряд расчетов:

- Определить требуемый диапазон входных и выходных частот

- Выбрать тип счетчика и рассчитать цепи его синхронизации

- Рассчитать цепи формирования выходного сигнала

- Определить требуемое быстродействие элементов схемы

Как правильно выбрать элементную базу? Следует ориентироваться на максимальную рабочую частоту, учитывая запас по быстродействию.

Настройка и проверка работы делителя частоты

После изготовления схемы делителя частоты необходимо выполнить ее настройку и проверку:

- Подать на вход сигнал известной частоты

- Измерить частоту выходного сигнала

- Проверить форму выходного сигнала осциллографом

- Определить диапазон рабочих частот

- Измерить потребляемый ток

На что нужно обратить особое внимание при проверке? Важно убедиться в стабильности частоты выходного сигнала во всем рабочем диапазоне входных частот.

Перспективы развития схем делителей частоты

Развитие технологий позволяет создавать все более совершенные схемы делителей частоты:

- Интеграция делителей в системы на кристалле

- Применение программируемых логических матриц

- Использование цифровых синтезаторов частоты

- Разработка делителей на основе оптоэлектронных компонентов

Какие преимущества дают новые технологии? Они позволяют создавать более компактные, экономичные и функциональные устройства с улучшенными характеристиками.

|

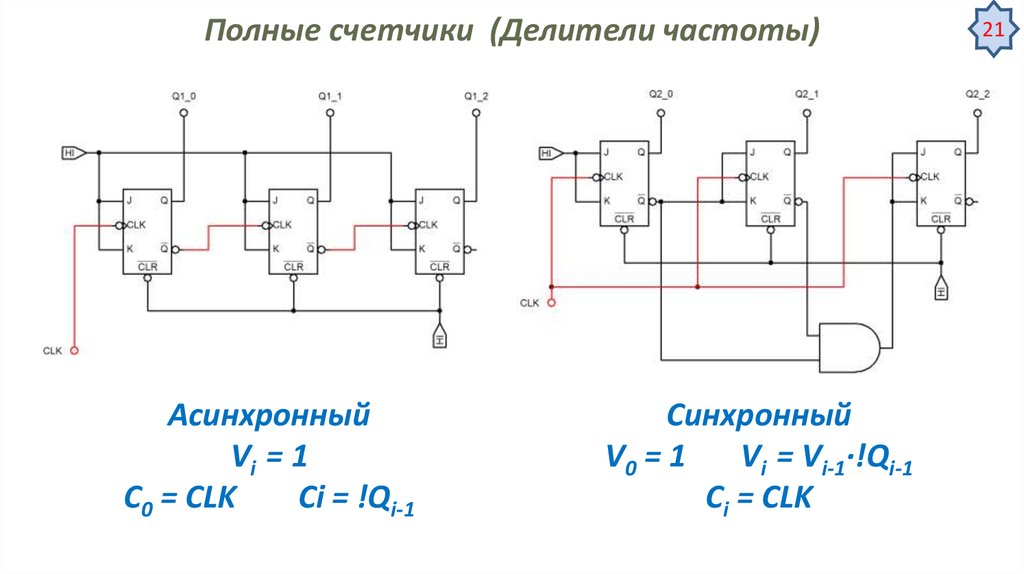

Наиболее часто для этого используют

счетчики, хотя можно разделить частоту с

помощью ждущего мультивибратора, ограничив

число проходящих на выход импульсов. Рис. 1.60 Делитель частоты с использованием ждущего мультивибратора Как только импульс входной частоты поступает на выход 5, ждущий мультивибратор D1.1, D1.3 запирает элемент D1.2 на время, определяемое резистором R1. Когда ждущий мультивибратор возвращается в исходное состояние, на выход поступает следующий импульс и цикл возобновляется. Схему можно усовершенствовать, заменив потенциометр полевым транзистором, что позволит управлять коэффициентом деления с помощью напряжения. Рис. 1.61. Счетный триггер на логических элементах Рис. 1.62. Делитель частоты на 2 Рис. 1.63. Делитель на 3 Делитель на 2 можно собрать из простейших ЛЭ, рис. 1.61. Схемы делителей без использования RC-цепей имеют лучшую помехоустойчивость и болееширокий диапазон входной частоты сигнала. Основным элементом всех счетчиков является триггер с так называемым счетным входом, рис. 1.62. Таблица поясняет логику работы триггера 561ТМ2

в зависимости от управляющих сигналов (х —

безразлично состояние на данном входе;

состояние, когда на входах S и R микросхемы

одновременно действует лог.

Рис. Рис. 1 65. Схема делителя на 60 Рис. 1. 66. а)

Универсальный реверсивный счетчик, Комбинационное включение триггеров позволяет получать счетчик с нужным коэффициентом деления входной частоты. На рис. 1.63…1.65 приведены примеры включения элементов микросхем для получения деления на 2, 3, 6, 10 и 60. Промышленность выпускает универсальные счетчики, которые в зависимости от управляющих сигналов могут переключаться по переднему или заднему фронту входного сигнала, а также менять направление счета (сложение или вычитание). В качестве примера приведена диаграмма работы двоичного четырехразрядного реверсивного счетчика на микросхеме 561ИЕ11, рис. 1.66. Таблица истинности поясняет назначение

управляющих сигналов и логику управления

микросхемой (1 — лог. «1»; 0 — лог.

«0»; х — состояние безразлично, т. е. 0

или 1). Счетчик предусматривает возможность

загрузить по входам D1, D2, D4, D8 параллельный

код.

Pис 1.67. Делитель на 1000 Для получения нужного коэффициента деления

можно использовать микросхемы двоичных

счетчиков, соединяя соответствующие выходы

с помощью ЛЭ, рис. 1.67, или же применить

счетчик с программируемым коэффициентом

деления 564ИЕ15, см. рис. 1.26.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

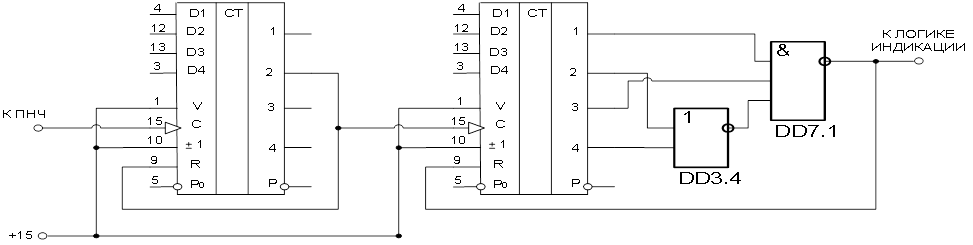

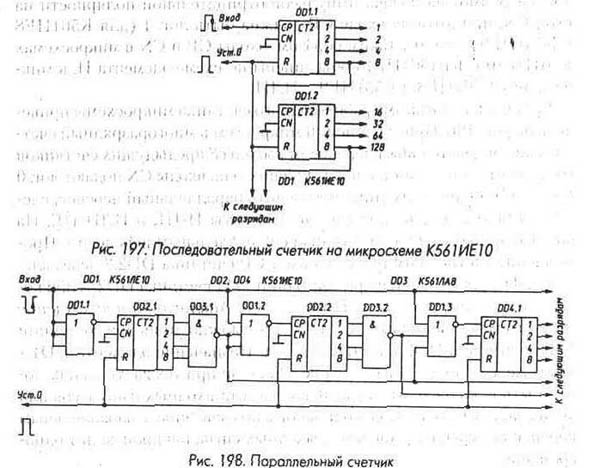

7.3. Блок деления частоты

Задача данного блока

– обеспечить деление входной частоты

до частоты 1 Гц, которая в дальнейшем

будет предназначена для формирования

фазы счета и индикации. Для получения

1 Гц на выходе, соединим последовательно

счетчики, делящие на 10. Так как на вход

блока деления частоты подается 10 МГц

(частота генерации кварцевого резонатора),

то для получения на выходе 1 Гц, нам

понадобится 7 счетчиков-делителей. В

блоке деления частоты используется

счетчик К155ИЕ4 (рис.14). Характеристики и

функциональная схема счетчика указаны

в Приложении Е.

Так как на вход

блока деления частоты подается 10 МГц

(частота генерации кварцевого резонатора),

то для получения на выходе 1 Гц, нам

понадобится 7 счетчиков-делителей. В

блоке деления частоты используется

счетчик К155ИЕ4 (рис.14). Характеристики и

функциональная схема счетчика указаны

в Приложении Е.

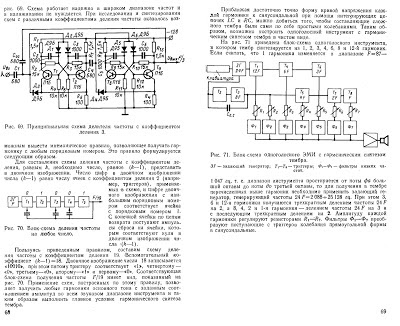

Рис.14. Схема счетчика-делителя К155ИЕ4

К155ИЕ4 – четырехразрядный счетчик-делитель на 2, на 6 и на 12. Он содержит по четыре счетных триггера. Один из триггеров имеет отдельный вход С1 и прямой выход, три оставшихся триггера соединены между собой так, что образуют делитель на 6.

При соединении выхода первого триггера с входом С2 цепочки из трех триггеров образуется делитель на 12. Делитель на 12 работает в коде 1-2-4-6. Чтобы получить делитель на 2, нужно соединить выводы 14 и 12.

Построим счетчик с

модулем деления на 10. Наличие входов

установки, объединенных по схеме &,

позволяет строить делители частоты с

различными коэффициентами деления в

пределах 2-6 без использования дополнительных

логических элементов.

На рис.15 приведены схема декады на микросхеме К155ИЕ4 и ее временная диаграмма.

Рис.15. Делитель частоты на 10 на микросхеме К155ИЕ4

и диаграмма его работы.

До прихода десятого импульса декада работает как делитель частоты на 12. Десятый импульс переводит триггеры микросхемы в состояние 10, при котором на выходах 4 и 6 микросхемы формируются уровни лог. 1. Эти уровни, поступая на входы R микросхемы, переводят ее в 0, в результате чего коэффициент пересчета К становится равным 10.

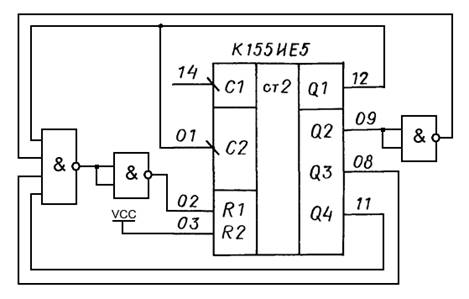

Схема управления

обеспечивает режимы сброса, счета и

индикации. Она состоит из схемы счета,

схемы сброса, схемы управления циклом

измерения, RC-фильтра и

триггера Шмитта. Для схемы управления

циклом измерения можно использовать

микросхему К555ИЕ5. Микросхема К555ИЕ5

(рис.16) является четырехразрядным

асинхронным двоичным счетчиком. Состоит

из счетного триггера (вход С1 и выход

Q0), работающего по модулю деления

2, и трех последовательно соединенных

триггеров (вход С2), работающих по

модулю деления 8, с асинхронной

потенциальной установкой нулевого

состояния значением сигнала R= R1

∙ R2 =1. Характеристики и диаграмма

работы счетчика представлены в Приложении

Ж.

Характеристики и диаграмма

работы счетчика представлены в Приложении

Ж.

Рис.16. Схема управления циклом измерения

на счетчике К555ИЕ5

Основу этой интегральной микросхемы составляют четыре счетных триггера, каждый из которых изменяет свое состояние на противоположное по срезу импульса (переходу с лог.1 в лог.0) на счетном входе Т. Все триггеры имеют вход R асинхронной установки в нуль, т.е. предусмотрена возможность сброса счетчика в нуль по сигналам R1 и R2, объединенным по функции И. Таким образом, счетчик устанавливается в нуль при R1=R2=1.

Для расширения функциональных возможностей первый триггер изолирован от других и представляет собой счетчик на 2 (mod2) (вход — C1, выход — Q0) — одноразрядный счетчик. Три остальных триггера соединены по схеме последовательного переноса и образуют счетчик на 8 (mod8) (вход — С2, выходы — Q1, Q2, Q3) — трехразрядный счетчик.

При

необходимости получить счетчик, считающий

до 16 (mod16),

необходимо внешним соединением соединить

выход Q0 со

входом С2,

тогда эта микросхема преобразуется в

4-разрядный асинхронный счетчик с

коэффициентом счета 16 (рис. 17). Тактовые

импульсы в этом случае подаются на вход

C1.

17). Тактовые

импульсы в этом случае подаются на вход

C1.

а б

Рис.17. Включение счетчика К555ИЕ5 по mod16 (а),

временная диаграмма его работы (б)

В режиме счета хотя бы на один из входов R1 или R2 должен быть подан нуль.

Счетчик

работает следующим образом: входные

импульсы подаются на вход синхронизации

C1

первого триггера. Так как триггеры

меняют свое состояние в момент перепада

с лог.1 на

лог.0,

то в момент окончания первого входного

импульса на выходе Q0

появится лог.1.

В момент окончания второго импульса

первый триггер вернется в исходное

нулевое состояние. При этом перепад

сигнала с лог.1,

на лог.0 на

выходе Q0

перебросит второй триггер в состояние

лог.1.

Третий импульс перебросит первый триггер

в единичное состояние. Четвертый импульс

вызывает переброс первого и второго

триггеров в нулевое состояние, а третьего

– в единичное. Состояния триггеров

счетчика при дальнейшем увеличении

числа входных импульсов видно из таблицы

истинности.

Состояния триггеров

счетчика при дальнейшем увеличении

числа входных импульсов видно из таблицы

истинности.

Таблица состояния выходов счетчика (таблица 2) приведена для схемы, приведенной на рис. 17, когда счетный вход счетчика по mod8 соединен с выходом счетчика по mod2 и, таким образом, получается счетчик по mod16 (с коэффициентом пересчета 16).

Таблица 2. «Таблица состояния выходов счетчика,

Схема делителя частоты

Фарва Навази

602 просмотраВведение

В цифровой логической схеме схема делителя частоты является одной из основных схем. Как следует из названия, он делит частоту. Вход часов делится на указанное значение компонентом делителя частоты, который генерирует выход. Таким образом, в этом уроке мы собираемся сделать «схему делителя частоты»

Задача схемы состоит в том, чтобы разделить или отбросить частоту высокочастотного сигнала, чтобы получить более низкочастотный сигнал для частотного сигнала. Наряду с микросхемой таймера 555 в схеме используется CD4017 для разделения частоты. Это ИС, которая допускает десять декодированных выходов и позволяет считать от нуля до десяти. CD4017 представляет собой десятичный делитель или счетчик КМОП с 10 выходными контактами.

Наряду с микросхемой таймера 555 в схеме используется CD4017 для разделения частоты. Это ИС, которая допускает десять декодированных выходов и позволяет считать от нуля до десяти. CD4017 представляет собой десятичный делитель или счетчик КМОП с 10 выходными контактами.

Hardware Required

| Sr. No | Components | Qty |

|---|---|---|

| 1 | Timer IC (NE555) | 1 |

| 2 | Decade Counter Divider IC (CD4017) | 1 |

| 3 | Voltage Regulator IC (7805) | 1 |

| 4 | Potentiometer 50KΩ | 1 |

| 5 | Switch 3 way | 1 |

| 6 | LED | 2 |

| 7 | Capacitor (0. 1uF), 1uF), | 1 |

| 8 | Resistor (330Ω, 10KΩ, 33KΩ) | 2, 1 , 1 |

| 9 | 9V Батарея | 1 |

| 10 | Электролитический конденсатор (10UF). микросхема таймера 555 для генерации входного частотного сигнала. Мы поместили резистор 10 кОм между VCC и контактом 7 микросхемы таймера 555. Затем мы подключили резистор R3 и потенциометр на 50 кОм между контактами 7 и 6. Контакт 2 закорочен на контакт 6, а конденсатор на 4,7 мкФ подключен к контакту 2 или 6. Контакты 1, 4 и 8 напрямую подключены к земля. Мы связываем выходной контакт этого таймера 555 с контактом часов счетчика IC 4017 через резистор 330 Ом и светодиод D. Таким образом, этот светодиод показывает наличие входного сигнала. Частота делится на 4017 Счетчик IC. Код ПояснениеПрименение и использование

Похожие сообщения:flipflop — Делитель частоты Flip Flop на 17спросил Изменено 1 год, 3 месяца назад Просмотрено 326 раз \$\начало группы\$ У меня есть задача сделать делитель частоты на 12, 17, 30. 1 9n — 1\$» с использованием вентиля исключающее ИЛИ должно быть достаточно. Таким образом, вы можете сделать деление на три, используя схему деления на четыре и один вентиль исключающего или. Затем каскадируйте это с помощью деления на- 6, и у вас есть схема деления на 18. Используя тот же эксклюзивный трюк или трюк с воротами, это можно превратить в деление на 17. Схема деления на три: —

Формы сигналов: —

Как вы можете видеть, сигнал Vout (красный) представляет собой входной тактовый сигнал (синий), разделенный на 3. Итак, если вы хотите разделить на шесть, используйте деление на восемь и два вентиля exor: —

Как вы можете видеть, приведенная выше схема использует деление на восемь и, используя два вентиля исключающего ИЛИ, превращает его в деление на шесть. |

Пример

такой схемы показан на рис. 1.60.

Пример

такой схемы показан на рис. 1.60.

«1»,

является запрещенным).

«1»,

является запрещенным).

1.64. а) Делитель на

10 на RS-триггерах; б) делитель на 10 на JK-триггерах

1.64. а) Делитель на

10 на RS-триггерах; б) делитель на 10 на JK-триггерах

входу

входу

Переключатель используется для выбора частоты. Резистор на 220 Ом подключает светодиод к выводу 2 микросхемы IC 4017, отображая разнесенную частоту. Это означает, что в зависимости от положения переключателя светодиод D1 мигает с частотой f, а светодиод D2 мигает с частотой f/2 или f/4. ИС 7805 используется для управления напряжением.

Переключатель используется для выбора частоты. Резистор на 220 Ом подключает светодиод к выводу 2 микросхемы IC 4017, отображая разнесенную частоту. Это означает, что в зависимости от положения переключателя светодиод D1 мигает с частотой f, а светодиод D2 мигает с частотой f/2 или f/4. ИС 7805 используется для управления напряжением.  Я разобрался как сделать делитель на 12 используя ступенчатые делители на 6 и ступенчатые делители на 10. Но 17 нечетное число и у меня не получается как и другие два.

Как и на изображении, используя промежуточные триггеры с делителем на 2 и на 6, я могу получить деление на 12.

\$\конечная группа\$

Я разобрался как сделать делитель на 12 используя ступенчатые делители на 6 и ступенчатые делители на 10. Но 17 нечетное число и у меня не получается как и другие два.

Как и на изображении, используя промежуточные триггеры с делителем на 2 и на 6, я могу получить деление на 12.

\$\конечная группа\$