Что такое логические элементы. Как работают базовые логические схемы И, ИЛИ, НЕ. Какие бывают типы триггеров. Как устроены счетчики и регистры сдвига. Чем отличаются ТТЛ и КМОП технологии.

Что такое логические элементы и для чего они нужны

Логические элементы — это базовые «кирпичики», из которых строятся все цифровые устройства. Они выполняют элементарные логические операции над входными сигналами и формируют выходной сигнал в соответствии с заданной логической функцией.

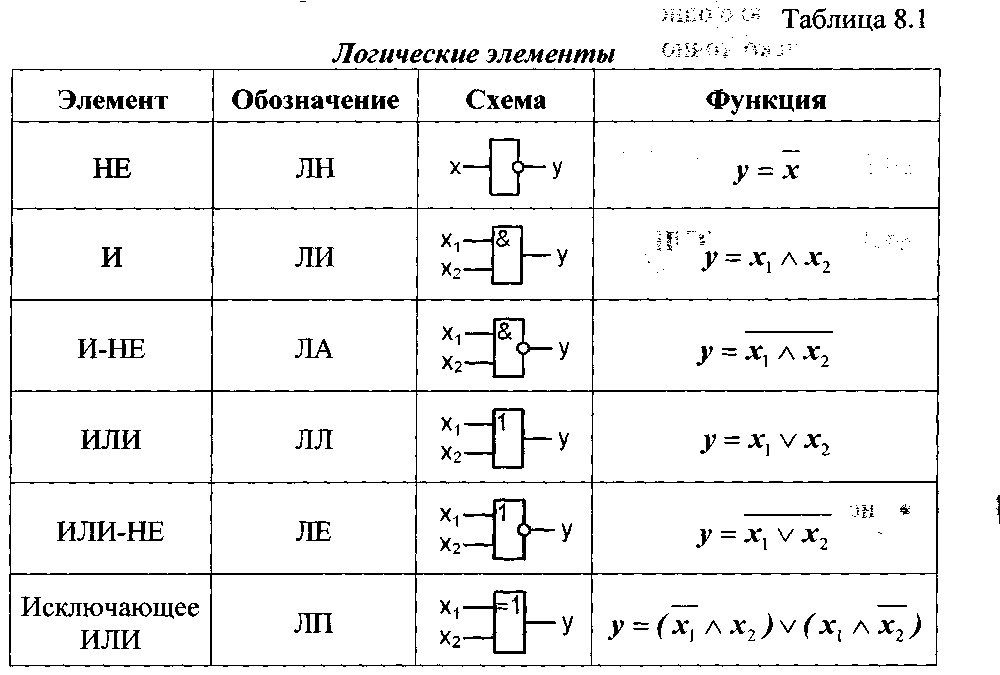

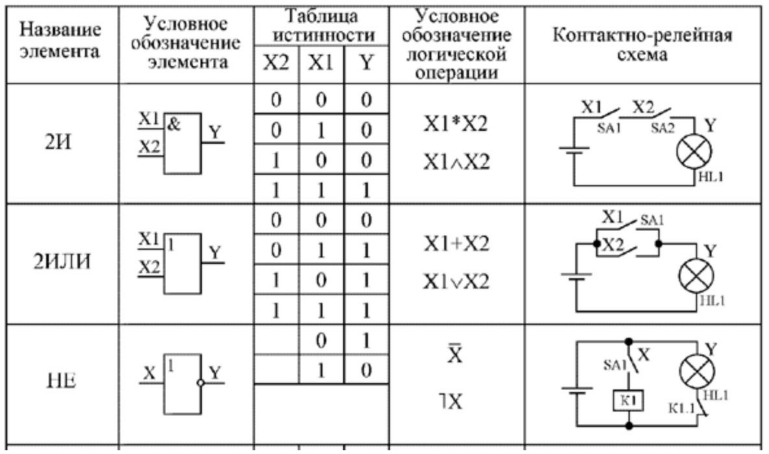

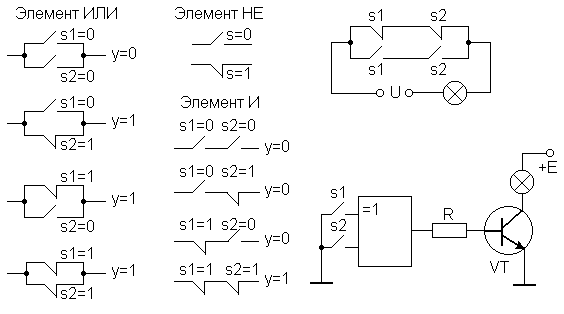

Основные типы логических элементов:

- И (AND) — выход равен 1, только если все входы равны 1

- ИЛИ (OR) — выход равен 1, если хотя бы один вход равен 1

- НЕ (NOT) — инвертирует входной сигнал

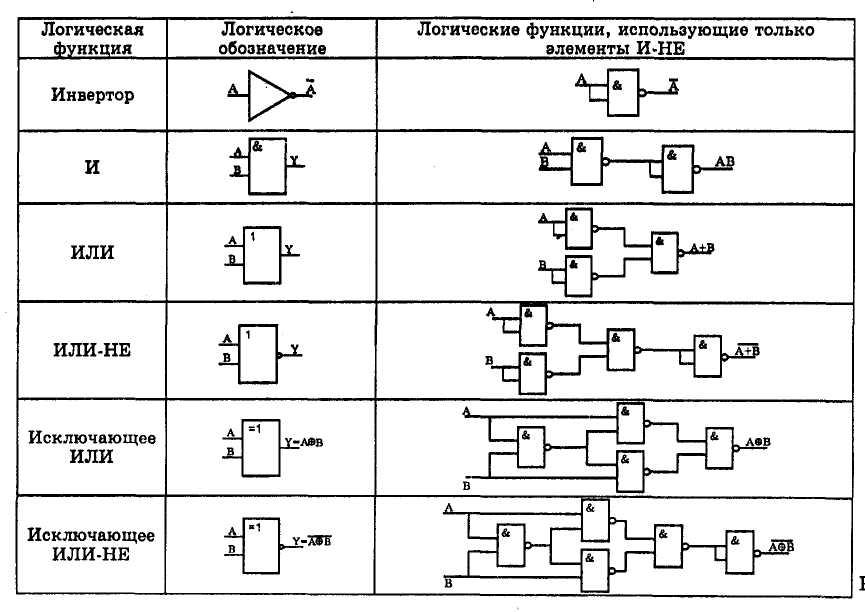

- И-НЕ (NAND) — инвертированный выход элемента И

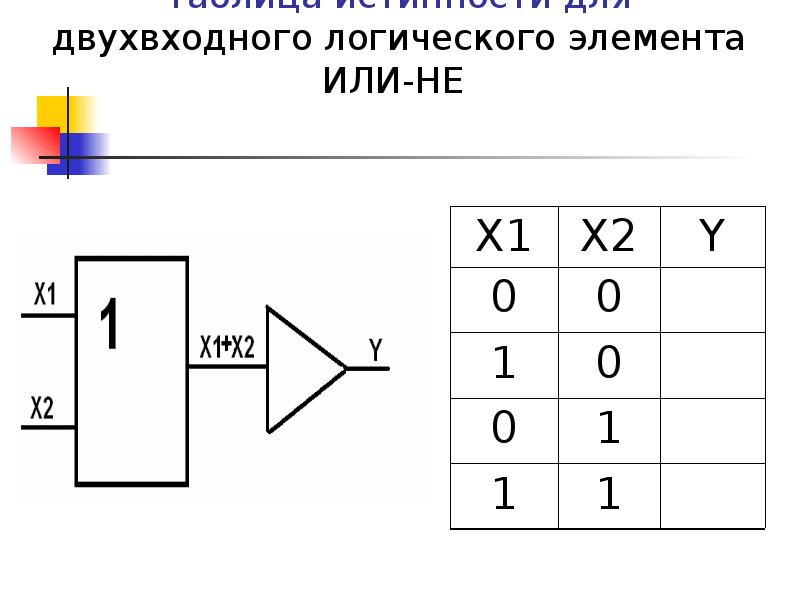

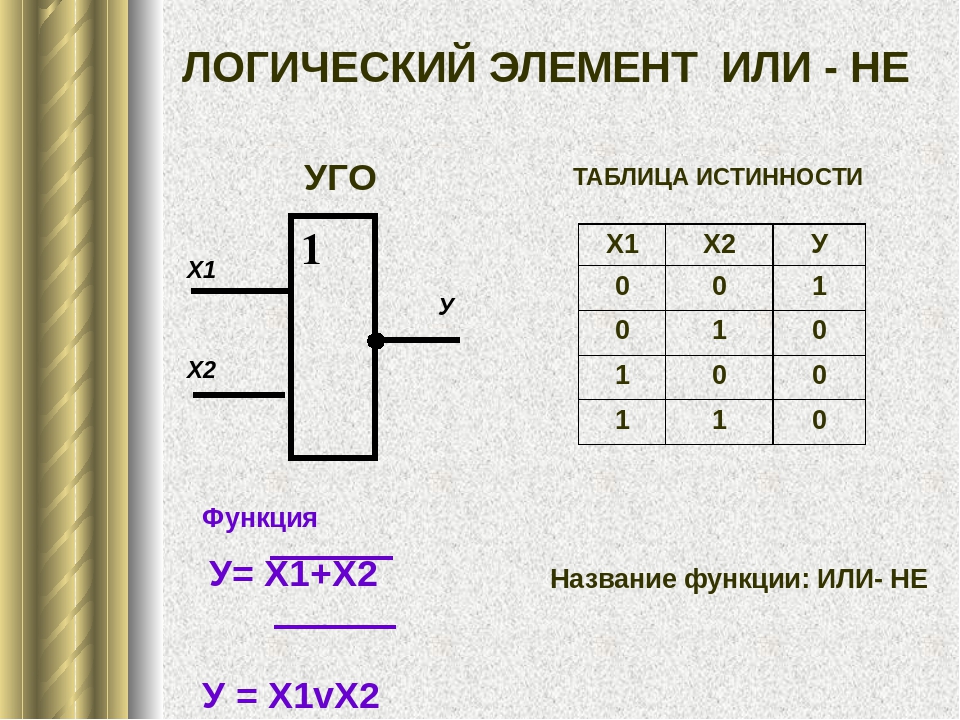

- ИЛИ-НЕ (NOR) — инвертированный выход элемента ИЛИ

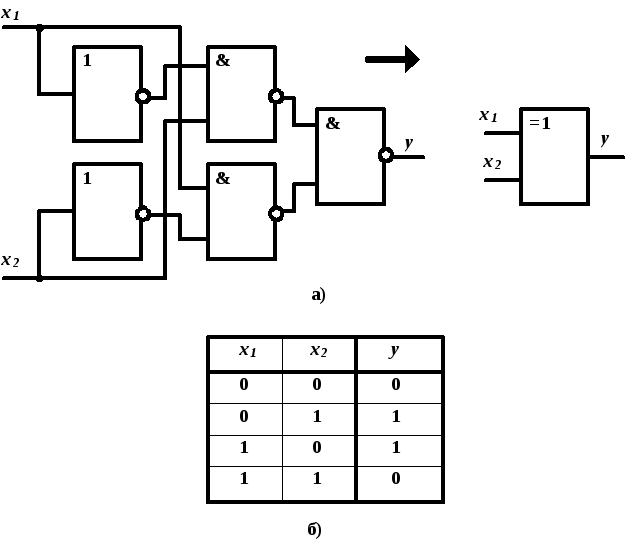

- Исключающее ИЛИ (XOR) — выход равен 1, если входы различны

Логические элементы позволяют создавать сложные цифровые схемы для обработки и хранения информации в двоичном коде. Они являются основой для построения процессоров, памяти и других цифровых устройств.

Как работают базовые логические схемы И, ИЛИ, НЕ

Рассмотрим принцип работы трех базовых логических элементов:

Элемент И (AND)

Элемент И выполняет операцию логического умножения. Его выход равен 1 только в том случае, если все входы равны 1.

Таблица истинности элемента И с двумя входами:

| Вход A | Вход B | Выход Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Элемент ИЛИ (OR)

Элемент ИЛИ реализует операцию логического сложения. Его выход равен 1, если хотя бы один из входов равен 1.

Таблица истинности элемента ИЛИ с двумя входами:

| Вход A | Вход B | Выход Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Элемент НЕ (NOT)

Элемент НЕ выполняет операцию логического отрицания, инвертируя входной сигнал.

Таблица истинности элемента НЕ:

| Вход A | Выход Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

Комбинируя эти базовые элементы, можно создавать более сложные логические схемы для решения различных задач цифровой обработки информации.

Триггеры — элементы памяти в цифровых схемах

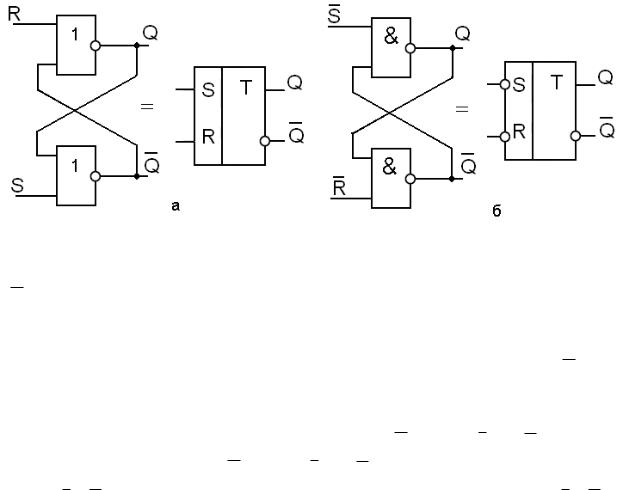

Триггеры — это базовые элементы памяти в цифровых схемах. Они способны хранить 1 бит информации и имеют два устойчивых состояния. Основные типы триггеров:

RS-триггер

Простейший тип триггера с двумя входами — Set (установка) и Reset (сброс). Имеет неопределенное состояние при одновременной подаче сигналов на оба входа.

D-триггер

Имеет один информационный вход D и тактовый вход C. При поступлении тактового импульса запоминает состояние входа D.

JK-триггер

Универсальный триггер с двумя информационными входами J и K и тактовым входом. Не имеет неопределенных состояний.

T-триггер

Счетный триггер. При поступлении импульса на вход T меняет свое состояние на противоположное.

Триггеры позволяют создавать более сложные элементы памяти — регистры, счетчики, а также служат основой для построения цифровых автоматов.

Счетчики и регистры сдвига в цифровой электронике

Счетчики и регистры сдвига — это более сложные цифровые устройства, состоящие из нескольких триггеров.

Счетчики

Счетчики предназначены для подсчета числа импульсов. Они бывают:

- Суммирующие — увеличивают свое состояние на 1 при поступлении импульса

- Вычитающие — уменьшают состояние на 1

- Реверсивные — могут работать в обоих режимах

По способу организации различают:

- Асинхронные счетчики — сигнал переноса передается последовательно между разрядами

- Синхронные — все разряды переключаются одновременно

Регистры сдвига

Регистры сдвига позволяют осуществлять последовательный ввод и вывод информации, а также выполнять операции сдвига.

Основные типы регистров сдвига:

- Последовательные — информация вводится и выводится последовательно, разряд за разрядом

- Параллельные — допускают одновременный ввод/вывод всех разрядов

- Универсальные — сочетают возможности последовательного и параллельного ввода/вывода

Регистры сдвига широко применяются для преобразования параллельного кода в последовательный и обратно, а также для выполнения арифметических операций.

Технологии изготовления логических элементов: ТТЛ и КМОП

Существует две основные технологии изготовления интегральных микросхем с логическими элементами:

ТТЛ (транзисторно-транзисторная логика)

Особенности ТТЛ:

- Высокое быстродействие

- Относительно высокое энергопотребление

- Напряжение питания 5В

- Меньшая помехоустойчивость по сравнению с КМОП

КМОП (комплементарная металл-оксид-полупроводник)

Преимущества КМОП:

- Очень низкое энергопотребление в статическом режиме

- Широкий диапазон напряжений питания (3-15В)

- Высокая помехоустойчивость

- Возможность создания схем с высокой степенью интеграции

В настоящее время технология КМОП является доминирующей при производстве цифровых интегральных схем благодаря своим преимуществам.

Применение логических элементов в современной электронике

Логические элементы являются основой для построения всех современных цифровых устройств. Вот некоторые области их применения:

- Процессоры и микроконтроллеры

- Оперативная и постоянная память

- Программируемые логические интегральные схемы (ПЛИС)

- Цифровые системы управления

- Устройства цифровой обработки сигналов

- Кодеры и декодеры информации

Несмотря на простоту отдельных логических элементов, их комбинации позволяют создавать невероятно сложные системы, лежащие в основе всей современной цифровой техники.

Логические схемы

Логические элементы, включая вентили, счетчики и запоминающие устройства, изготавливаются в виде интегральных модулей, или интегральных схем (ИС). Эти ИС разбивают на классы, называемые семействами, по числу полупроводниковых приборов, содержащихся в одной ИС. В настоящее время существуют следующие семейства.

|

1. |

ИС низкой степени интеграции |

до 10 приборов. |

|

2. |

ИС средней степени интеграции |

10-100 приборов. |

|

3. |

ИС большой степени интеграции, или большие ИС (БИС) |

100-1000 приборов. |

|

4. |

ИС сверхбольшой степени интеграции, или сверхбольшие ИС (СБИС) |

1000-10000 приборов. |

|

5. |

Ультрабольшие ИС (УБИС) |

10000-100000 приборов. |

Степень интеграции определяет сложность интегральной схемы. Каждое следующее по сложности семейство характеризуется десятикратным увеличением числа элементов по сравнению с предыдущим. К ИС низкой и средней степени интеграции относятся дискретные логические элементы, такие, как вентили, счетчики и регистры. БИС иСБИС используются в качестве запоминающих устройств, микропроцессоров и законченных систем, таких, как микрокомпьютеры.

Логические состояния

Логический элемент имеет два различных состояния: состояние логического 0, представляемое низким уровнем напряжения, обычно 0 В; и состояние логической 1. представляемое высоким уровнем напряжения (положительной полярности в случае положительной логики и отрицательной полярности в случае отрицательной логики). Уровень напряжения, который представляет логическую 1. зависит от используемого типа ИС. Для ИС, изготавливаемых по биполярной технологии, например для ПС ТТ, I (ИС на основе транзисторно-транзисторной логики), логической 1 соответствует напряжение 5 В, в то время как для ИС КМОП (ИС на комплементарных, или дополняющих, МОП-транзисторах) логическая 1 может быть представлена напряжением в диапазоне от 3 до 15 В и выше. ИС ТТЛ имеют преимущество в быстродействии, а ИС КМОП позволяют реализовать более высокую степень интеграции компонентов

представляемое высоким уровнем напряжения (положительной полярности в случае положительной логики и отрицательной полярности в случае отрицательной логики). Уровень напряжения, который представляет логическую 1. зависит от используемого типа ИС. Для ИС, изготавливаемых по биполярной технологии, например для ПС ТТ, I (ИС на основе транзисторно-транзисторной логики), логической 1 соответствует напряжение 5 В, в то время как для ИС КМОП (ИС на комплементарных, или дополняющих, МОП-транзисторах) логическая 1 может быть представлена напряжением в диапазоне от 3 до 15 В и выше. ИС ТТЛ имеют преимущество в быстродействии, а ИС КМОП позволяют реализовать более высокую степень интеграции компонентов

(т. е. позволяют разместить большее число логических элементов в одном интегральном модуле) и не требуют использования стабилизированных источников питания.

Транзисторно-транзисторные логические элементы (ТТЛ)

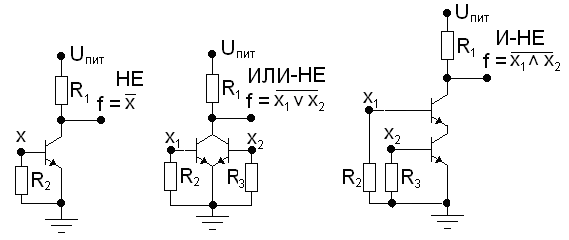

ТТЛ-элементы применяются в интегральных схемах и обеспечивают высокую скорость переключения. На рис. 34.1 показана упрощенная схема логического элемента И-НЕ с многоэмиттерным транзистором T1 на входе. Когда на обоих входах присутствует логический 0, транзистор T

1 насыщен и напряжение на его коллекторе близко к 0 В. Следовательно, транзистор T2 находится в состоянии отсечки, и на выходе мыимеем логическую 1. Когда на оба входа подается логическая 1, транзистор T1 закрывается и переключает транзистор T2 в состояние насыщения. В этом случае на выходе элемента мы имеем логический 0.

На рис. 34.1 показана упрощенная схема логического элемента И-НЕ с многоэмиттерным транзистором T1 на входе. Когда на обоих входах присутствует логический 0, транзистор T

1 насыщен и напряжение на его коллекторе близко к 0 В. Следовательно, транзистор T2 находится в состоянии отсечки, и на выходе мыимеем логическую 1. Когда на оба входа подается логическая 1, транзистор T1 закрывается и переключает транзистор T2 в состояние насыщения. В этом случае на выходе элемента мы имеем логический 0.

Рис. 34.1. Логический элемент И-НЕ (ТТЛ-типа).

Логические элементы на полевых транзисторах

Логические схемы в настоящее время изготавливаются только в виде интегральных схем. Огромное количество логических элементов можно разместить на мельчайшем кристалле (чипе) кремния размером 1х2 мм. В силу своей простоты полевые транзисторы применяются чаще, чем биполярные транзисторы. Наиболее широко распространены логические элементы на основе так называемых КМОП-ячеек (здесь они не рассматриваются). На рис. 34.2 приведена схема логического элемента ИЛИ-НЕ на МОП-транзисторах, который работает на основе отрицательной логики. В этой схеме T

Наиболее широко распространены логические элементы на основе так называемых КМОП-ячеек (здесь они не рассматриваются). На рис. 34.2 приведена схема логического элемента ИЛИ-НЕ на МОП-транзисторах, который работает на основе отрицательной логики. В этой схеме T

Рис. 34.2. Логический элемент Рис. 34.3. Логический элемент на И-НЕ

ИЛИ-НЕ на МОП-транзисторах. МОП-транзисторах.

На рис. 34. 3 показана схема логического элемента И-НЕ на основе полевых МОП-транзисторов с каналом п-типа. Поскольку используется источник питания положительной полярности, данный логический элемент работает на основе положительной логики. Транзистор T3 постоянно смещен в активную рабочую область напряжением VDD, подаваемым на затвор, и выполняет функцию активной нагрузки логического элемента. Когда на одном или на обоих входах присутствует логический 0, один или оба транзистора находятся в состоянии отсечки, выдавая логическую 1 на выходе. Ток через транзисторы будет протекать только в том случае, когда на оба входа будет подана логическая 1, и только в этом случае мы получим на выходе логический 0.

3 показана схема логического элемента И-НЕ на основе полевых МОП-транзисторов с каналом п-типа. Поскольку используется источник питания положительной полярности, данный логический элемент работает на основе положительной логики. Транзистор T3 постоянно смещен в активную рабочую область напряжением VDD, подаваемым на затвор, и выполняет функцию активной нагрузки логического элемента. Когда на одном или на обоих входах присутствует логический 0, один или оба транзистора находятся в состоянии отсечки, выдавая логическую 1 на выходе. Ток через транзисторы будет протекать только в том случае, когда на оба входа будет подана логическая 1, и только в этом случае мы получим на выходе логический 0.

Булевы выражения

Функции, реализуемые отдельным логическим элементом или комбинацией логических элементов, могут быть выражены логическими формулами, называемыми булевыми выражениями. В булевой алгебре используются следующие обозначения логических функций (см. табл. 34.1):

табл. 34.1):

• Функция И обозначается символом точки (·). Двухвходовый (входы А и В) логический элемент И вырабатывает на выходе сигнал, представляемый булевым выражением А · В.

• Функция ИЛИ обозначается символом (+). Двухвходовый логический элемент ИЛИ вырабатывает на выходе сигнал, представляемый булевым выражением А + В.

Таблица 34.1. Булевы выражения

|

Функция |

Обозначение в булевой алгебре |

|

И |

А·В |

|

или |

А+В

|

|

НЕ |

|

|

И-НЕ |

|

|

ИЛИ-НЕ |

|

|

Исключающее ИЛИ |

|

|

Исключающее ИЛИ-НЕ |

• Логическая функция НЕ обозначается символом черты над обозначением входного сигнала. Логическая схема НЕ с одним входом А вырабатывает на выходе сигнал, представляемый булевым выражением (читается «НЕ А»).

Логическая схема НЕ с одним входом А вырабатывает на выходе сигнал, представляемый булевым выражением (читается «НЕ А»).

Через эти простые функции можно выразить более сложные:

• Функция Н-НЕ записывается как .

• Функция ИЛИ-НЕ записывается как .

• Функция Исключающее ИЛИ записывается как . Ее можно также записать, используя специальное обозначение, .

• Функция Исключающее ИЛИ-НЕ записывается как . Ее можно также записать, используя специальное обозначение, .

Комбинаторная логика

Рассмотрим логическую схему на рис. 34.4. Логическую функцию, выполняемую этой схемой, можно описать с помощью следующих булевых выражений.

Выходной сигнал логического элемента ИЛИ (i): A + В

Выходной сигнал логического элемента И-ИЕ (ii):

Выходной сигнал логического элемента ИЛИ (iii): (А + В) +

Пример 1

Обратимся к рис. 34.5.

34.5.

а) Найдите булево выражение для логической функции изображенной комбинации логических элементов.

б) Составьте таблицу истинности, показывающую логические состояния во всех точках схемы, и докажите, что эту схему можно свести к одному логическому элементу.

Решение

а) Булево выражение для точки С = .

Булево выражение для точки D= .

Булево выражение для точки F = ·.

б) Таблица истинности

|

Входы |

Точки |

Выход |

||

|

А

|

В

|

С

|

D

|

F

|

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

Как видно из таблицы истинности, приведенная комбинация логических элементов эквивалентна логическому элементу ИЛИ-НЕ.

Пример 2

Обратимся к рис. 34.6.

а) Найдите булево выражение для логической функции изображенной комбинации логических элементов.

б) Составьте таблицу истинности, показывающую логические состояния во всех точках схемы, и докажите, что эту схему можно свести к одному логическому элементу.

Решение

а) Булево выражение для точки С = .

Булево выражение для точки D = .

Булево выражение для точки F = +.

6) Таблица истинности

|

Входы |

Точки |

Выход |

||

|

А

|

В

|

С

|

D

|

F

|

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

0 |

Как видно из таблицы истинности, приведенная комбинация логических элементов эквивалентна логическому элементу И-НЕ.

Счетчики

Функцию счета в двоичном счетчике выполняет бистабильный мультивибратор, или делитель на 2, чаще называемый триггером. Цепочка из нескольких таких триггеров образует счетчик. На рис. 34.7 показан двоичный счетчик, состоящий из трех триггеров. Каждый триггер делит частоту поступающих импульсов на 2. Таким образом, два последовательных триггера обеспечивают деление на 4 (2 · 2), а три триггера – на 8 (2 · 2 · 2). Другими словами, на каждые восемь входных импульсов на выходе А появятся четыре импульса, на выходе В — два импульса и на выходе С — один импульс (рис. 34.7).

Как уже говорилось в гл. 32, бистабильный мультивибратор изменяет свое состояние только во время действия одного из фронтов входного импульса. Уровень входного импульса изменяется от 0 к 1 и обратно к 0, и так для каждого приходящего импульса. Обычно предполагается, что состояние триггера изменяется при приходе отрицательного фронта импульса (т. е. при переходе от 1 к 0).

Сигнал на выходе QА триггера А соответствует 20, или столбцу «единиц» в табл. 34.2, сигнал на выходе QB— 21, или столбцу «двоек», и наконец, сигнал на выходе QC — 22, или столбцу «четверок». После поступления 6 импульсов на вход счетчика он оказывается в следующем состоянии: А (число единиц) = 0, В (число двоек) = 1. С (число четверок) = 1; это состояние соответствует десятичному числу 6 (0 + 2 + 4).

Рис. 34.7. Двоичный счетчик на трех триггерах.

Таблица 34.2

|

Импульс |

QА единицы (20) |

QB двойки (21) |

QC четверки (22) |

|

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

|

2 |

0 |

1 |

0 |

|

3 |

1 |

1 |

0 |

|

4 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

|

7 |

1 |

1 |

1 |

|

8 |

0 |

0 |

0 |

В двоичном исчислении это число записывается как 110 при порядке следования двоичных разрядов СВА. Обратите внимание, что в счетчике двоичному разряду единиц соответствует выход первого триггера, начиная от входа счетчика, а в двоичном числе разряд единиц всегда является самым правым разрядом.

Обратите внимание, что в счетчике двоичному разряду единиц соответствует выход первого триггера, начиная от входа счетчика, а в двоичном числе разряд единиц всегда является самым правым разрядом.

Когда приходит седьмой импульс, на всех выходах счетчика устанавливается 1. Восьмой импульс сбрасывает все триггеры в 0. Еще раз отметим, что выходной сигнал каждого триггера представляет столбец в таблице двоичного кода. Сам двоичный код записывается в порядке СВА.

Обратная связь

Обратная связь вводится в двоичных счетчиках для изменения коэффициента деления частоты входного сигнала. Для примера рассмотрим действие обратной связи в счетчике на рис. 34.8(а), состоящем из трех триггеров. Процесс счета происходит обычным образом до прихода третьего импульса, когда счетчик находится в состоянии 011 (см. табл. 34.3).

Рис. 34.8. (а) Счетчик-делитель на 6 с обратной связью, охватывающей триггеры В и С.

(б) Замена петли обратной связи эквивалентным модулем деления на 3.

Таблица 34.3

|

Импульс |

QА |

QB |

QC |

|

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

|

2 |

0 |

1 |

0 |

|

3 |

1 |

1 |

0 |

|

Обратная связь |

(0) |

(0) |

(1) |

|

4 |

0 |

1 |

1 |

|

5 |

1 |

1 |

1 |

|

6 |

0 |

0 |

0 |

Четвертый импульс переключает сигнал на выходах А и В к 0 и на выходе С к 1. В отсутствие обратной связи счетчик переключился бы в состояние 100. Однако при включении обратной связи изменение сигнала на выходе С передается на вход триггера В, возвращая его выходной сигнал обратно к 1. Счетчик окажется в состоянии 110. Пятый импульс переключит все выходы к 1, и шестой импульс сбросит все триггеры в 0, т. е. получился счетчик-делитель на 6.

В отсутствие обратной связи счетчик переключился бы в состояние 100. Однако при включении обратной связи изменение сигнала на выходе С передается на вход триггера В, возвращая его выходной сигнал обратно к 1. Счетчик окажется в состоянии 110. Пятый импульс переключит все выходы к 1, и шестой импульс сбросит все триггеры в 0, т. е. получился счетчик-делитель на 6.

Вообще, можно показать, что петля обратной связи уменьшает коэффициент деления триггеров внутри петли на 1. В предыдущем примере внутри петли обратной связи находились триггеры В и С. Без обратной связи они осуществляли деление на 4. С обратной связью триггеры В и С образуют блок деления на 3 (= 4 – 1), как показано на рис. 34.8(б). С учетом триггера А вне петли обратной связи полный коэффициент деления счетчика равен 6 (= 2 · 3).

Десятичный счетчик

На рис. 34.9(а) изображена схема десятичного счетчика с двумя петлями обратной связи. Обратной связью охвачены : 1) блок 1, включающий триггеры С и D и обеспечивающий деление на 3 (= 4 – 1), и 2) блок 2, включающий блок 1 и триггер В. Из рис. 34.9(б) видно, что без обратной связи блок 2 делил бы на 6 (= 2 · 3). С обратной связью его коэффициент деления равен 5 (= 6 – 1). С учетом триггера А, не охваченного обратной связью, полный коэффициент деления счетчика равен 10 (= 2 · 5).

Из рис. 34.9(б) видно, что без обратной связи блок 2 делил бы на 6 (= 2 · 3). С обратной связью его коэффициент деления равен 5 (= 6 – 1). С учетом триггера А, не охваченного обратной связью, полный коэффициент деления счетчика равен 10 (= 2 · 5).

Регистр сдвига

Для передачи данных из одной части системы, например компьютера, в другую можно использовать два метода. Первый, более быстрый, заключается в одновременной передаче всех разрядов. При этом для передачи восьми разрядов требуется восемь отдельных линий. Для передачи информации на расстояния в несколько метров этот метод вполне пригоден, но при передаче на большие расстояния, например между городами, он становится слишком дорогим. В этом случае применяется второй, более медленный метод: данные передаются последовательно разряд за разрядом по одному проводу. Для одновременного сдвига всех двоичных разрядов влево или вправо применяется регистр сдвига. Он состоит из нескольких триггеров, способных передвигать двоичные разряды в последовательном порядке.

Рис. 34.9. Десятичный счетчик (а) и его представление в виде эквивалентных модулей (б).

Кольцевой счетчик

Кольцевой счетчик — это обычный счетчик, составленный из нескольких триггеров, в котором выходной сигнал подается обратно на вход, отсюда и происходит его название. Импульсы циркулируют по счетчику от входа к выходу и обратно на вход. В конце каждого цикла выходной сигнал кольцевого счетчика можно снять для переключения другого счетчика. Например, выходной сигнал десятичного, или декадного, счетчика можно использовать для переключения еще одного декадного счетчика, обеспечивая тем самым коэффициент пересчета, равный 100.

Фиксатор (триггер-защелка)

В гл. 32 рассматривались бистабильные мультивибраторы, или триггеры, построенные на дискретных компонентах. Триггеры — очень важные и нужные базовые элементы логических устройств. Они применяются в качестве делителей на 2, фиксаторов (одноразрядные ячейки памяти) и для других целей.

Базовый триггер, называемый RS-триггером, или триггером-защелкой, показан на рис. 34.10. Два выходных сигнала, снимаемые с выходов Q и (НЕ Q), находятся в противофазе друг к другу. Если Q = 1, то = 0, и наоборот. Таблица истинности для RS-триггера приведена на рис. 34.10(в). При подаче логической 1 на вход R (Reset — сброс) на выходе Q устанавливается уровень логического 0 (и уровень логической 1 на выходе ), при подаче логической 1 на вход S (Set — установка) на выходе Q устанавливается уровень логической 1 (и уровень логического 0 на выходе ).

|

S |

R |

|

|

0 |

0 |

Без изменений |

|

0 |

1 |

|

|

1 |

0 |

|

|

1 |

1 |

Неопределенное состояние |

(в)

Более сложным устройством по сравнению с простым RS-триггером является тактируемый JK-триггер, в котором имеется тактовый вход и отсутствует неопределенное состояние (рис. 34.11). Тактовый вход важен для синхронных систем, в которых переключение триггеров происходит лишь тогда, когда на тактовый вход подается логическая 1. При установке логической 1 на обоих входах J и К триггера его выход переключается из уровня логического 0 в логическую 1 при поступлении каждого тактового импульса.

|

Тактовый вход |

J

|

К

|

|

|

0 |

X |

X |

Без изменений |

|

1 |

0 |

0 |

Без изменений |

|

1 |

0 |

1 |

|

|

1 |

1 |

0 |

|

|

1 |

1 |

1 |

Переключение |

(а) (б)

Рис. 34.11. Условное обозначение (а) и таблица истинности (б) JK-триггера.

Логические элементы в виде ИС

Логические элементы изготавливаются в виде интегральных схем и выпускаются в виде модулей, содержащих большое число идентичных элементов на одном модуле (чипе). Известны два основных типа ИС: ИС ТТЛ и ИС КМОП. Примеры ИС ТТЛ приведены на рис. 34.12.

Рис. 34.12.

В этом видео рассказывается о элементах транзисторно-транзисторной логики:

Добавить комментарий

Урок 8.3 — Логические элементы

8.3. Логические элементы

Все, абсолютно все электронные компоненты, обрабатывающие цифровые сигналы, состоят из небольшого набора одинаковых «кирпичиков». В микросхемах малой степени интеграции могут быть единицы и десятки таких элементов, а в современных процессорах их может быть очень и очень много. Они называются логические элементы. Логическим элементом называется электрическая схема, предназначенная для выполнения какой-либо логической операции с входными данными. Логический элемент — элемент, осуществляющий определенные логические зависимость между входными и выходными сигналами. Входные данные представляются здесь в виде напряжений различных уровней, и результат логической операции на выходе — также получается в виде напряжения определенного уровня. Логические элементы обычно используются для построения логических схем вычислительных машин, дискретных схем автоматического контроля и управления.

Тем не менее, принцип работы цифровой логики остается неизменным – на входе логического элемента (входов может быть несколько) должен быть цифровой сигнал (сигналы, если входов несколько), который однозначно определяет сигнал на выходе логического элемента.

Конечно, логические элементы строятся, в свою очередь, из уже рассмотренных в предыдущих уроках резисторов, транзисторов и других электронных компонентов, но с точки зрения разработки цифровых схем именно логический элемент является их «элементарной» частицей.

При анализе работы логических элементов используется так называемая булева алгебра . Начала этого раздела математики было изложено в работах Джорджа Буля – английского математика и логика 19-го века, одного из основателей математической логики. Основами булевой алгебры являются высказывания, логические операции, а также функции и законы. Для понимания принципов работы логических элементов нет необходимости изучать все тонкости булевой алгебры, мы освоим ее основы в процессе обучения с помощью таблиц истинности.

Еще несколько замечаний. Логические элементы (как, впрочем, и другие элементы электронных схем) принято обозначать так, чтобы входы были слева, а выходы справа. Число входов может быть, вообще говоря, любым, отличным от нуля. Реальные цифровые микросхемы могут иметь до 8 входов, но мы ограничимся двумя – этого достаточно для понимания. Условные обозначения соответствуют отечественному ГОСТу, в других стандартах они могут быть иными.

Какие же бывают логические элементы?

Логические элементы имеют один или несколько входов и один или два (обычно инверсных друг другу) выхода. Значения «нулей» и «единиц» выходных сигналов логических элементов определяются логической функцией, которую выполняет элемент, и значениями «нулей» и «единиц» входных сигналов, играющих роль независимых переменных. Существуют элементарные логические функции, из которых можно составить любую сложную логическую функцию.

Элемент «И» (AND), он же конъюнктор, выполняет операцию логического умножения:

Условное обозначение — Таблица истинности

Здесь изображен логический элемент «2И» (цифра перед буквой «И» означает число входов). Знак & (амперсант) в левом верхнем углу прямоугольника указывает, что это логический элемент «И». Первые две буквы обозначения DD1.2 указывают на то, что это цифровая микросхема (Digital), цифра слева от точки указывает номер микросхемы на принципиальной схеме, а цифра справа от точки – номер логического элемента в составе данной микросхемы. Одна микросхема может содержать несколько логических элементов.

Состояние входов в таблице обозначаются «0» и «1» («ложь» и «истина»). Из таблицы видно, что выход «Y» будет иметь состояние «1» только в том случае, когда на обоих входах «Х1» и «Х2» будут «1». Это легко запомнить: умножение на «0» всегда дает «0».

Элемент «ИЛИ» (OR), он же дизъюнктор, выполняет операцию логического сложения:

Условное обозначение — Таблица истинности

Состояние «1» на выходе будет всегда, пока есть хотя бы одна «1» на входах.

Элемент «НЕ» (NOT), он же инвертор, выполняет операцию логического отрицания:

Условное обозначение — Таблица истинности

Состояние на входе обратно состоянию на входе.

Вот из этих трех элементов строятся все цифровые устройства!

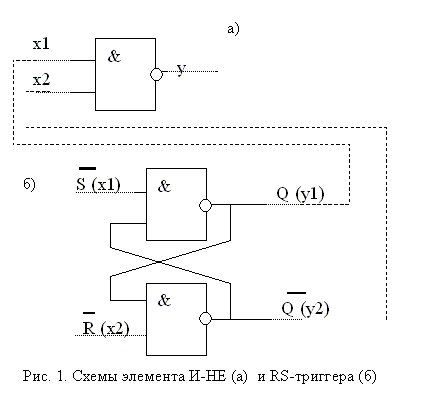

Рассмотрим еще три логических элемента, которые можно получить, комбинируя уже рассмотренные. В силу исторически сложившихся схемотехнических решений эти скомбинированные схемы тоже считаются логическими элементами.

Элемент «И-НЕ» (NAND), конъюнктор с отрицанием:

Условное обозначение — Таблица истинности

Элемент И-НЕ работает точно так же как «И», только выходной сигнал противоположен. Там где у элемента «И» на выходе должен быть «0», у элемента «И-НЕ» будет единица. И наоборот.

Элемент «ИЛИ-НЕ» (NOR), дизъюнктор с отрицанием:

Условное обозначение — Таблица истинности

Элемент работает так же как и «ИЛИ», но с инверсией выхода.

Элемент «Исключающее ИЛИ» (XOR), сумматор по модулю 2:

Условное обозначение — Таблица истинности

В этом элемента «1» на выходе будет только тогда, когда на входах разные состояния.

На таких элементах строят сумматоры двоичных многоразрядных чисел. Для этого используется еще один дополнительный выход, на котором при появлении на входах двух «1» появляется сигнал переноса разряда.

Мы рассмотрели логические элементы, которые применяются в цифровой технике для построения логических схем любого уровня сложности, но рассмотренные нами элементы не могут делать одну крайне важную работу – они не умеют хранить информацию. Для хранения используется более сложный класс устройств, называемый элементами с памятью или конечными автоматами. В этот класс входят триггеры, регистры, счетчики, шифраторы (дешифраторы), мультиплексоры (демультиплексоры) и сумматоры. Некоторый из этих устройств мы рассмотрим в следующем уроке.

Логические элементы

Логические элементыЛогические элементы

Логическим элементом называется электрическая схема, выполняющая какую-либо логическую операцию (операции) над входными данными, заданными в виде уровней напряжения, и возвращающая результат операции в виде выходного уровня напряжения. Так как операнды логических операций задаются в двоичной системе счисления, то логический элемент воспринимает входные данные в виде высокого и низкого уровней напряжения на своих входах. Соответственно, высокий уровень напряжения (напряжение логической 1) символизирует истинное значение операнда, а низкий (напряжение логического 0) — ложное. Значения высокого и низкого уровней напряжения определяются электрическими параметрами схемы логического элемента и одинаковы как для входных, так и для выходных сигналов. Обычно, логические элементы собираются как отдельная интегральная микросхема. К числу логических операций, выполняемых логическими элементами относятся конъюнкция (логическое умножение, И), дизъюнкция (логическое сложение, ИЛИ), отрицание (НЕ) и сложение по модулю 2 (исключающее ИЛИ). Рассмотрим основные типы логических элементов.

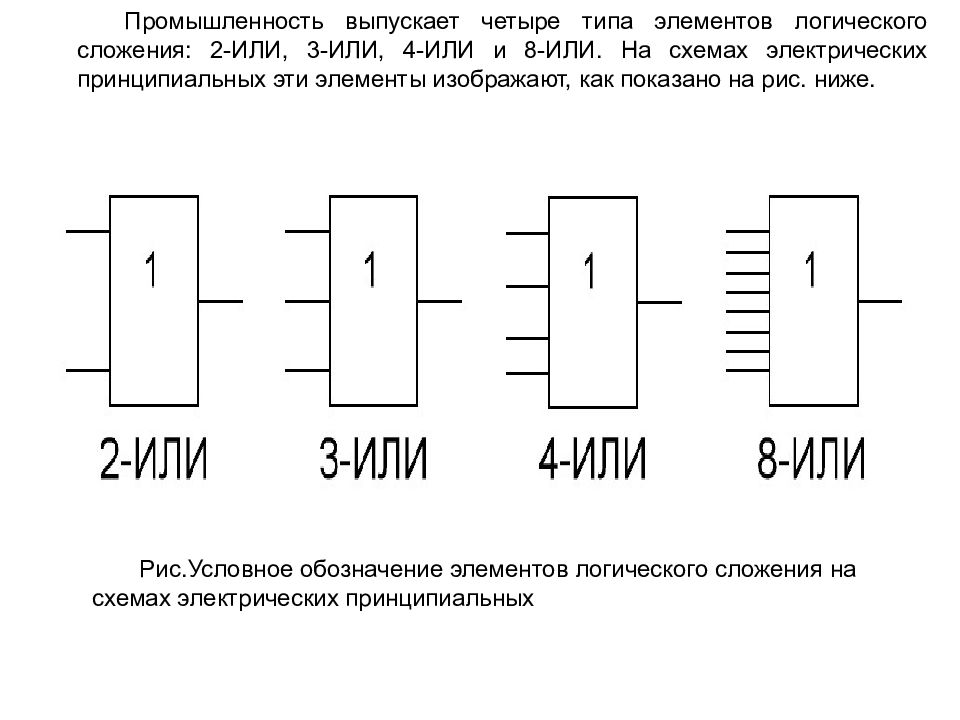

Элемент И

Логический элемент И выполняет операцию логического умножения (конъюнкция) над своими входными данными и имеет от 2 до 8 входов и один выход (как правило, выпускаются элементы с двумя, тремя, четырьмя и восемью входами). На рис. 1. изображены условные графические обозначения (УГО) логических элементов И с двумя, тремя и четырьмя входами соответственно. Элементы И обозначаются как NИ, где N — количество входов логического элемента (например, 2И, 3И, 8И и т.д.).

| Рис. 1 |

Элемент ИЛИ

Логический элемент ИЛИ выполняет операцию логического сложения (дизъюнкция) над своими входными данными и, также как и логический элемент И, имеет от 2 до 8 входов и один выход. На рис. 2. изображены УГО логических элементов ИЛИ с двумя, тремя и четырьмя входами соответственно. Элементы ИЛИ обозначаются также, как и элементы И (2ИЛИ, 4ИЛИ и т.д.).

| Рис. 2 |

Элемент НЕ (инвертор)

Логический элемент НЕ выполняет операцию логического отрицания над своими входными данными и имеет один вход и один выход. Иногда его называют инвертор, так как он инвертирует входной сигнал. На рис. 3 изображено УГО элемента НЕ.

| Рис. 3 |

Элемент И-НЕ

Логический элемент И-НЕ выполняет операцию логического умножения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент И-НЕ — это элемент И с инвертором на выходе. УГО элемента 3И-НЕ приведено на рис. 4.

| Рис. 4 |

Элемент ИЛИ-НЕ

Логический элемент ИЛИ-НЕ выполняет операцию логического сложения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент ИЛИ-НЕ — это элемент ИЛИ с инвертором на выходе. УГО элемента 3ИЛИ-НЕ приведено на рис. 5.

| Рис. 5 |

Элемент сложения по модулю 2

Этот логический элемент выполняет логическую операцию сложения по модулю 2 и, как правило, имеет 2 входа и один выход. Такой элемент, в основном, используется в схемах аппаратного контроля. УГО элемента приведено на рис. 6.

| Рис. 6 |

Комбинационные логические элементы

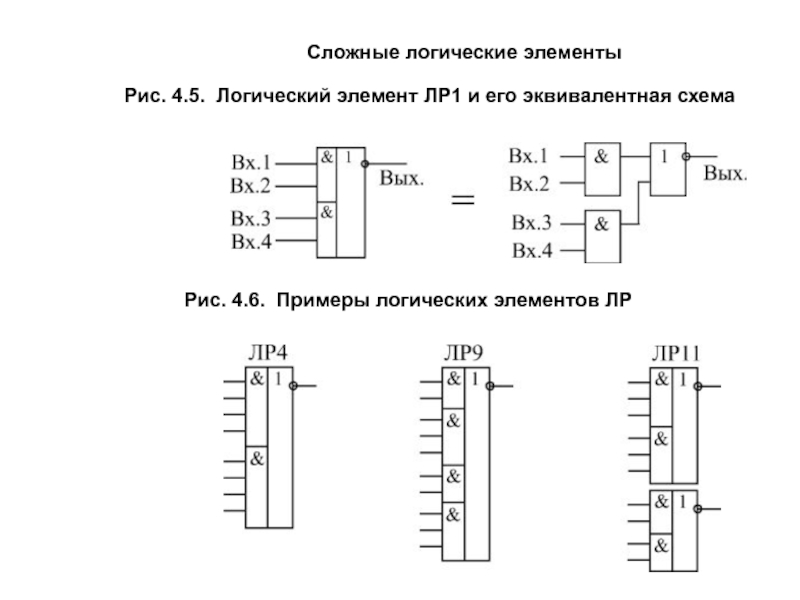

Существуют и более сложные логические элементы, выполняющие несколько логических операций над своими входными данными. Например, элемент 2И-ИЛИ, УГО и схема которого приведено на рис. 7, сначала выполняет операцию логического умножения над парами операндов x1, x2 и x3, x4, а затем выполняет операцию логического сложения над полученными результатами, т.е. y = x1x2 + x3x4. Можно придумать и более сложные комбинационные логические элементы, например 3-2И-ИЛИ-НЕ (рис. 8).

| Рис. 7 |

| Рис. 8 |

Универсальные логические элементы

Универсальные логические элементы могут использоваться для выполнения разнообразных операций над своими входными данными. Конкретная операция зависит от того, какие сигналы поданы на управляющие входы. Чтобы синтезировать такой универсальный логический элемент, обычно пользуются СКНФ или СДНФ, как и в синтезе комбинационных логических схем.

Электрические принципиальные схемы логических элементов

При рассмотрении электрических принципиальных схем логических элементов пользуются термином тип логики. Тип логики определяет элементную базу, на которой собран логический элемент, а также отражает некоторые особенности отдельных элементов этой элементной базы и характеристики самого логического элемента. Наиболее распространены следующие типы логик: ТТЛ, ДТЛ, МОП, КМОП, также существуют типы логик ЭСЛ, РЕТЛ и некоторые другие. Тип логики ТТЛ (транзисторно-транзисторная логика) определяет элементную базу, на которой собран логический элемент, как состоящую преимущественно из транзисторов, причём транзисторы используются и на входе, и на выходе логического элемента (отсюда и название — транзисторно-транзисторная). Тип логики ДТЛ (диодно-транзисторная логика) определяет элементную базу как состоящую преимущественно из транзисторов и диодов (диоды на входе, транзисторы — на выходе). Типы логик МОП (металл-оксид-полупроводник) и КМОП определяет элементную базу как состоящую из транзисторов МДП (металл-диэлектрик-полупроводник), причём микросхемы этого типа имеют очень низкую потребляемую мощность, засчёт особенностей МДП транзисторов оперировать малыми токами и имеющими очень малый ток утечки.

Рассмотрим электрические принципиальные схемы логического элемента И-НЕ с n входами — ДТЛ (рис. 9) и логического элемента И-НЕ с n входами — ТТЛ (рис. 10).

| Рис. 9 |

| Рис. 10 |

На рисунках +U обозначает положительный потенциал источника питания, а -U — отрицательный.

Рассмотрим сначала работу схемы на рис. 9. Если к одному из входных диодов приложено напряжение логического 0, то этот диод открыт и на базу транзистора подаётся напряжение логического 0. Транзистор закрывается и на выходе y устанавливается напряжение логической 1. Только когда ко всем входным диодам будет приложено напряжение логической 1 транзистор откроется и на выходе установится напряжение логического 0. Оставшиеся каскады на транзисторах выполняют функцию усиления сигнала и инвертирования. При подаче на вход второго транзистора напряжения логического 0, он закроется, подключив базы транзисторов оконечного каскада через резисторы к плюсу и к минусу источника питания. Один из транзисторов оконечного каскада откроется, а другой — закроется и на выходе установится напряжение логической 1. При подаче на второй транзистор напряжения логической 1, он откроется. Теперь открытый и закрытый транзисторы оконечного каскада поменяются местами и на выходе установится напряжение логического 0.

Теперь рассмотрим работу схемы на рис. 10. Вызывает некоторый интерес необычный транзистор на входе и схема его включения. Такие многоэмиттерные транзисторы всегда используются на входах логических элементов ТТЛ. Сам транзистор выполняет логическую операцию И. При подаче на один из входов напряжения логического нуля, транзистор открывается и, таким образом, на коллекторе устанавливается напряжение логического 0. Напряжение логической 1 будет на коллекторе только тогда, когда на всех входах будет напряжение логической 1. Подобный транзистор можно рассматривать как много n-p переходов, а соответственно, как много диодов. Таким образом такое включение транзистора в цепь эквивалентно диодной сборке на входе логического элемента И на рис. 9.

Применение логических элементов

Логические элементы могут использоваться как самостоятельные части схемы, так и входить в состав более сложной цифровой комбинационной схемы или схемы с памятью. Как самостоятельные части схемы, логические элементы могут применяться в качестве управляющей логики какого-либо устройства, а также в качестве генератора прямоугольных импульсов с подключённой ёмкостью или кварцевым резонатором. В качестве комбинационных схем логические элементы используются в составе микросхем БИС и СБИС, а также в дешифраторах и шифраторах, выполненных в виде отдельных микросхем. Также, логические элементы могут входить в состав схем с памятью (триггеры, регистры, счётчики и т.д.), выполненных в виде отдельной микросхемы или в составе других микросхем.

Логические элементы и логические схемы компьютера. 10-й класс

Цель урока:

- дать учащимся представление о том, как в компьютере при помощи логических элементов выполняются арифметические и логические операции.

Опорные понятия:

- логическая операция;

- сложное логическое выражение (формула).

Новые понятия:

- логический элемент,

- логическая схема.

Задачи учителя:

- на аналогиях из повседневной жизни показать, что логика хорошо реализуется при помощи электронных схем;

- познакомить учащихся с логическими элементами;

- познакомить учащихся с некоторыми логическими устройствами компьютера;

- дать представление учащимся о последовательности создания логического устройства.

Методика проведения урока

ПОВТОРЕНИЕ.

Аналоги логических операций в повседневной жизни

Примеры для повторения операции логического сложения

- Ученик должен быть толковым и усидчивым (т.е. ученик достигает хороших результатов, если он либо толковый, либо усидчивый, либо и то и другое вместе).

- Для сдачи экзамена необходимы знание или везение.

- Высказывание А: «p – четное число»; высказывание В: «p делится на 3». Каков результат операции логического сложения: А + В?

РЕШЕНИЕ. Множество всех случаев, когда А истинно: p = 2, 4, 6, 8, 10,… Множество всех случаев, когда В истинно: p = 3, 6, 9,… Множество всех случаев, когда истинно А+ В: p = 2, 3, 4, 6, 8, 9, 10,…, т.е. объединение двух множеств.

Примеры для повторения операции логического умножения

- Учитель должен быть умным и терпеливым (только одновременное наличие двух качеств, ума и терпения, делает выражение истинным).

- Только умение и настойчивость приводят к достижению цели (достижение цели возможно только при одновременной истинности двух предпосылок – наличия и умения, и настойчивости).

- Высказывание А: «p делится на 5»; высказывание В: «p меньше 20». Чему равен результат логического умножения: А & В?

РЕШЕНИЕ. Множество всех случаев, когда А истинно: p = 5, 10, 15, 20, 25, … Множество всех случаев, когда В истинно: p = 1, 2, 3,…, 19. Множество всех случаев, когда истинно А & В: p = 5, 10, 15, т.е. пересечение двух множеств.

Примеры для повторения операции импликации

- Если выучить материал, то сдашь зачет (высказывание ложно только тогда, когда материал выучен, а зачет не сдан, ведь сдать зачет можно и случайно, например если попался единственный знакомый вопрос или удалось воспользоваться шпаргалкой).

- Высказывание А: «х делится на 9»; высказывание В: «х делится на 3». Операция означает следующее: «если число делится на 9, то оно делится и на 3».

При анализе этого примера можно перебрать следующие варианты:

o А – ложно, В – ложно. Можно найти такие числа, для которых истиной является высказывание: «если А – ложно, то и В – ложно». Например, х = 4, 17, 22…

o А – ложно, В – истинно. Можно найти такие числа, для которых истиной является высказывание: «если А – ложно, то и В – истинно». Например, х = 6, 12, 21…

o А – истинно, В – истинно. Можно найти такие числа, для которых истиной является высказывание: «если А – истинно, то и В – истинно». Например, х = 9, 18, 27…

o А – истинно, В – ложно. Невозможно найти такие числа, которые делились бы на 9, но не делились на 3, т.е. истинная предпосылка не может приводить к ложному результату импликации.

Примеры для повторения операции эквивалентности

Когда в зимний день светит солнце и «кусает» мороз, это значит, что атмосферное давление высокое.

Высказывание А: «сумма цифр, составляющих число х, делится на 3», высказывание В: «х делится на 3». Операция означает следующее: «число делится на 3 тогда и только тогда, когда сумма его цифр делится на 3».

2.РЕАЛИЗАЦИЯ ЛОГИКИ ПРИ ПОМОЩИ ЭЛЕКТРОННЫХ СХЕМ

Можно начать урок с исторической справки.

Историческая справка

С 1867 года американский логик Чарльз Сандерс Пирс ( в его честь названа одна из логических операций – «стрелка Пирса») работает над модификацией и расширением булевой алгебры. Пирс первым осознал, что бинарная логика имеет сходство с работой электрических переключательных схем. Электрический переключатель либо пропускает ток (что соответствует значению Истина), либо не пропускает (что соответствует значению Ложь). Позже Пирс даже придумал простую электрическую логическую схему, но так и не собрал ее.

Учитель предлагает учащимся самим воспроизвести возможный ход рассуждений Ч.Пирса.

ВАРИАНТ ДИАЛОГА

Вопрос: Есть электрическое устройство, которым мы пользуемся каждый день. Оно реализует логическую операцию отрицания. Подумайте, что это за устройство?

Ответ: Выключатель. Если свет не горел, он его включает, если горел – выключает.

Вопрос: Вспомните Новый год и старую елочную гирлянду. Почему она была недолговечна?

Ответ: В старых гирляндах лампочки включались последовательно. Гирлянда горела только тогда, когда все лампочки были исправны. Стоило перегореть хотя бы одной, вся гирлянда не работала.

Вопрос: На какую логическую операцию это похоже?

Ответ: На логическое умножение.

Вопрос: А в современных гирляндах как подключаются лампочки?

Ответ: Параллельно. Гирлянда горит, если хотя бы одна лампочка исправна.

Вопрос: На какую логическую операцию это похоже?

Ответ: На логическое сложение.

Учитель подводит итоги диалога: подобно Пирсу, вы сейчас убедились, как хорошо реализуются логические операции в простейших схемах. В настоящее время существуют электронные схемы, реализующие все логические операции.

3. В КАКОМ ВИДЕ ЗАПИСЫВАЮТСЯ В ПАМЯТИ КОМПЬЮТЕРА И В РЕГИСТРАХ ПРОЦЕССОРА ДАННЫЕ И КОМАНДА

Существуют различные физические способы кодирования двоичной информации, но чаще всего единица кодируется более высоким уровнем напряжения, чем нуль (или наоборот).

4.ЧТО ТАКОЕ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КОМПЬЮТЕРА.

Как при строительстве дома применяют различного рода типовые блоки – кирпичи, рамы, двери и т.п., так и при разработке компьютера используют типовые электронные схемы. Каждая схема состоит из определенного набора типовых электронных элементов.

Электронным элементом называется соединение различных деталей, в первую очередь – диодов и транзисторов, а также резисторов и конденсаторов, в виде электрической схемы, выполняющей некоторую простейшую функцию.

Электронный элемент, реализующий логическую функцию, называется логическим элементом.

ИЛИ

Логический элемент компьютера – это часть электронной логической схемы, которая реализует элементарную логическую функцию.

Тысячи микроскопических электронных переключателей в кристалле интегральной схемы сгруппированы в системы, выполняющие логические операции, т.е. операции с предсказуемыми результатами, и арифметические операции над двоичными числами. Соединенные в различные комбинации, логические элементы дают возможность компьютеру решать задачи, используя язык двоичных кодов.

Логическими элементами компьютеров являются электронные схемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и др. (называемые также вентилями), а также триггер, регистр, сумматор.

Триггер – это логическая схема, способная сохранять одно из двух состояний до подачи нового сигнала на вход. Это, по сути, разряд памяти, способный хранить 1 бит информации.

Регистр – это устройство, состоящее из последовательности триггеров. Регистр предназначен для хранения многоразрядного двоичного числового кода, которым можно представлять и адрес, и команду, и данные.

Сумматор – это устройство, предназначенное для суммирования двоичных кодов.

С помощью этих схем можно реализовать любую логическую функцию, описывающую работу устройств компьютера. Обычно у вентилей бывает от двух до восьми входов и один или два выхода.

Чтобы представить два логических состояния «1» и «0» в вентилях, соответствующие им входные и выходные сигналы имеют один из двух установленных уровней напряжения. Например, +5 вольт и 0 вольт.

Высокий уровень обычно соответствует значению «истина» («1»), а низкий – значение «ложь («0»).

Каждый логический элемент имеет свое условное обозначение, которое выражает его логическую функцию, но не указывает на то, какая именно электронная схема в нем реализована. Это упрощает запись и понимание сложных логических схем.

Работу логических элементов описывают с помощью таблиц истинности.

Таблица истинности – это табличное представление логической схемы (операции), в котором перечислены все возможные сочетания значений истинности входных сигналов (операндов) вместе со значениями истинности выходного сигнала (результата операции) для каждого из этих сочетаний.

5. ФИЗКУЛЬТПАУЗА.

6. ЧТО ТАКОЕ СХЕМЫ И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ.

Схема И реализует конъюнкцию двух или более логических значений.

Условное обозначение на структурных схемах схемы И с двумя входами представлено на рис.1, а таблица истинности в таблице 1.

Таблица 1

х |

у |

х * у |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль.

Связь между выходом z этой схемы и входами х и у описывается отношением z = х * у (читается как «х и у»).

Операция конъюнкции на функциональных схемах обозначается знаком & (читается как «амперсэнд»), являющимся сокращенной записью английского слова and.

Схема ИЛИ реализует дизъюнкцию двух или более логических значений.

Когда хотя бы на одном входе схемы ИЛИ будет единица, на ее выходе также будет единица.

Условное обозначение схемы ИЛИ знак «1». Связь между выходом z этой схемы и входами х и у описывается соотношением z = х + у (читается как «х или у»). Рис.2 и таблица 2.

Таблица 2

х |

у |

х + у |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

Схема НЕ (инвертор) реализует операцию отрицания.

Связь между входом х этой схемы и выходом z можно записать соотношением z = , где читается как «не х» или «инверсия х».

Если на входе схемы 0, то на выходе 1. Когда на входе 1, на выходе 0. Условное обозначение инвертора — на рис.3, а таблица истинности – в таблице 3

.

Таблица 3

x |

|

0 |

1 |

1 |

0 |

Схема И-НЕ состоит из элемента И и инвертора и осуществляет отрицание результата схемы И.

Связь между выходом z и входами х и у схемы записывают следующим образом:

z = , где читается как «инверсия х и у».

рис. 4

Таблица 4

х |

у |

|

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

Условное обозначение схемы И-НЕ представлено на рис. 4, а таблица истинности схемы И-НЕ – в таблице 4.

Схема ИЛИ-НЕ состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ.

Связь между выходом z и входами х и у схемы записывают следующим образом:

z = , где читается как «инверсия х или у».

Таблица 5

х |

у |

|

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

Условное обозначение схемы ИЛИ-НЕ представлено на рис. 5, а таблица истинности схемы ИЛИ-НЕ – в таблице 5.

Что такое триггер.

Триггер – это электронная схема, широко применяемая в регистрах компьютера для надежного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое – двоичному нулю.

Термин «триггер» происходит от английского слова trigger – защелка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip – flop, что в переводе означает «хлопанье». Это звукоподражательное название электронной схемы указывает на ее способность почти мгновенно переходить из одного электрического состояния в другое и наоборот.

Самый распространенный тип триггера – так называемый RS – триггер ( S и R соответственно от английских слов set – установка и reset – сброс). Условное обозначение триггера – на рис.6. Он имеет два симметричных входа S и R и два симметричных выхода Q и , причем выходной сигнал Q является логическим отрицанием сигнала . На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов. Наличие импульса на входе будем считать единицей, а его отсутствие – нулем.

На рис. 7 показана реализация триггера с помощью вентилей ИЛИ-НЕ, в таблице 6 – соответствующая таблица истинности.

Таблица 6

S |

R |

Q |

|

0 |

0 |

Запрещено |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

Хранение бита |

|

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ-НЕ (см. табл. 5).

- Если на входы триггера подать S = «1», R = «0», то (независимо от состояния) на выходе Q верхнего вентиля появится «0». После этого на входах нижнего вентиля окажется R = «0», Q = «0» и выход станет равным «1».

- Точно так же при подаче «0» на вход S и «1» на вход R на выходе появится «0», а на Q – «1».

- Если на входы S и R подана логическая «1», то состояние Q и не меняется.

- Подача на оба входа R и S логического «0» может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта соответственно 8*210=8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

Что такое сумматор.

Сумматор – это электронная логическая схема, выполняющая суммирование двоичных чисел.

Сумматор служит прежде всего центральным узлом арифметико–логического устройства компьютера, однако он находит применение также и в других устройствах машины.

Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров, с рассмотрения которых мы и начнем. Условное обозначение одноразрядного сумматора приведено на рис. 8.

При сложении чисел А и В в одном i –м разряде приходится иметь дело с тремя цифрами:

1. цифра аi первого слагаемого;

2. цифра bi второго слагаемого;

3. перенос рi-1 из младшего разряда.

В результате сложения получаются две цифры:

1) цифра сi для суммы;

2) перенос рi из данного разряда в старший.

Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами, работа которого может быть описана следующей таблицей истинности – табл.7.

Схема полусумматрора.

Таблица 7

Входы |

Выходы |

|||

Первое слагаемое |

Второе слагаемое |

Перенос |

Сумма |

Перенос |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Если требуется складывать двоичные слова длиной два и более бит, то можно использовать последовательное соединение таких сумматоров, причем для двух соседних сумматоров выход переноса одного сумматора является входом для другого.

Домашнее задание

1. Читать: стр.140 — 145.

2. Письменно: задание 3.10 стр. 145.

Логические элементы

Любые цифровые микросхемы строятся на основе простейших логических элементов «НЕ», «ИЛИ», «И». В настоящее время используется несколько технологий построения логических элементов:

- транзисторно-транзисторная логика (ТТЛ, TTL)

- логика на основе комплементарных МОП транзисторов (КМОП, CMOS)

- логика на основе сочетания комплементарных МОП и биполярных транзисторов (BiCMOS)

Простейшим логическим элементом является инвертор, который работает в соответствии со следующей таблицей:

| Рис 1 Таблица истинности логического инвертора | |

| Рис 2 Изображение логического инвертора на принципиальных схемах. |

Чаще всего существуют не отдельные схемы логического «И», а более сложные схемы, выполняющие одновременно логическую функцию «И» и логическую функцию «НЕ» Таблица истинности и изображение схемы, выполняющей логическую функцию «И-НЕ» изображены на рис 3 и 4 соответственно:

| Рис 3 Таблица истинности схемы, выполняющей логическую функцию «И-НЕ». | |

| Рис 4 Изображение схемы, выполняющей логическую функцию «И-НЕ». |

Точно также как не существует отдельных схем логического «И», выполненных по технологии ТТЛ, не существует отдельных схем логического «ИЛИ». Таблица истинности и изображение схемы, выполняющей логическую функцию «ИЛИ-НЕ» изображены на рис 5 и 6 соответственно:

| Рис 5 Таблица истинности схемы, выполняющей логическую функцию «ИЛИ-НЕ». | |

| Рис 6 Изображение схемы, выполняющей логическую функцию «ИЛИ-НЕ». |

Построение произвольной таблицы истинности.

Любая логическая схема без памяти полностью описывается таблицей истинности. При построении сложных логических схем с произвольной таблицей истинности используется сочетание простейших схем «И» «ИЛИ» «НЕ».

При построении схемы, реализующей произвольную таблицу истинности, каждый выход анализируется (и строится схема) отдельно. Для реализации таблицы истинности при помощи логических элементов «И» достаточно рассмотреть только те строки таблицы истинности, которые содержат логические «1» в выходном сигнале. Строки, содержащие в выходном сигнале логический 0 в построении схемы не участвуют. Каждая строка, содержащая в выходном сигнале логическую «1», реализуется схемой логического «И» с количеством входов, совпадающим с количеством входных сигналов в таблице истинности. Входные сигналы, описанные в таблице истинности логической «1» подаются на вход этой схемы непосредственно, а входные сигналы, описанные в таблице истинности логическим «0» подаются на вход через иверторы. Объединение сигналов с выходов схем, реализующих отдельные строки таблицы истинности, производится при помощи схемы логического ИЛИ. Количество входов в этой схеме определяется количеством строк в таблице истинности, в которых в выходном сигнале присутствует логическая «1».

Рассмотрим конкретный пример. Пусть необходимо реализовать таблицу истинности, приведенную на рисунке 7:

Рисунок 7 Произвольная таблица истинности.

Для построения схемы, реализующей сигнал Out1, достаточно рассмотреть строки, выделенные красным цветом. Эти строки реализуются микросхемой D2 на рисунке 8. Каждая строка реализуется своей схемой «И», затем выходы этих схем объединяются Для построения схемы, реализующей сигнал Out2, достаточно рассмотреть строки, выделенные зеленым цветом. Эти строки реализуются микросхемой D3.

Рисунок 8. Принципиальная схема, реализующая таблицу истинности, приведенную на рисунке 7.

[Содержание] [Вперёд]

Построение тестов для константных неисправностей произвольных логических элементов комбинационных схем на основе графического представления функций элементов Текст научной статьи по специальности «Математика»

А.Ю. Матросова, А.Г. Плешков, А.С. Алемасов

ПОСТРОЕНИЕ ТЕСТОВ ДЛЯ КОНСТАНТНЫХ НЕИСПРАВНОСТЕЙ ПРОИЗВОЛЬНЫХ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ КОМБИНАЦИОННЫХ СХЕМ НА ОСНОВЕ ГРАФИЧЕСКОГО ПРЕДСТАВЛЕНИЯ ФУНКЦИЙ ЭЛЕМЕНТОВ

Работа выполнена при финансовой поддержке гранта министерства образования РФ: грант 2003, ЕО 2-2.0-30.

Предложен алгоритм синтеза тестовых наборов для константных неисправностей произвольных логических элементов комбинационных схем. Алгоритм основан на использовании свойств ортогональных дизъюнктивных нормальных форм (ОДНФ) функций, реализуемых схемой. Графическое представление схемы композицией альтернативных графов ее элементов, названных впоследствии SSBDD-графами (Structurally Synthesized Binary Decision Diagram), наряду с информацией о структуре схемы задают ОДНФ функций этой схемы. Это позволяет, с одной стороны, использовать композицию графов при построении тестов для различных неисправностей в структуре схемы, а с другой — сокращать перебор при поиске тестов за счет графического представления ОДНФ булевых функций. Введен FSSBDD-граф (Full Structurally Synthesized Binary Decision Diagram), задающий в компактной форме ОДНФ схемы в целом. Алгоритм синтеза тестовых наборов сводится к поиску подходящих путей в FSSBDD-графе. Созданы программные реализации алгоритма. Одна из них ориентирована на построение FSSBDD-графа и последующий его анализ. Другая — на обход подмножеств путей этого графа без его явного построения за счет использования SSBDD-графов элементов схемы и информации о связях между ними. Приводятся результаты испытания программ.

Графическое представление логических схем широко используется при решении различных задач их анализа, связанных с проблемами диагностики дискретных систем. Это представление предполагает, что вершинам графа сопоставляются элементы схемы, а дугам — связи между элементами. Оно, как правило, является более компактным по сравнению с формулами, описывающими системы булевых функций, реализуемые комбинационной схемой или комбинационной частью последовательностной схемы.

Следует, однако, иметь в виду, что аналитическое представление булевых функций зачастую ориентировано на такие формулы, которые в явном виде несут информацию о свойствах функции: ее единичных наборах (ДРФ), нулевых наборах (КHФ), однородности но переменным (произвольные формулы над множеством {—, л, v } булевых функций, в которых инверсии опущены со скобок на переменные и т.д. Графическое представление логических схем такой информации в явном виде не содержит.

ROBDD-графы (Reduced Ordered Binary Decision Diagram), предложены R.E. Bryant в 1986 г. [1]. Они, в отличии от традиционных графических представлений логических схем своими путями (простыми цепями), соединяющими корень графа с 1(0)-концевой вершиной, представляют единичные (нулевые) наборы булевой функции, однако не содержат информации о структуре схемы, реализующей эту функцию.

В задачах анализа логических схем (моделирование, но-строение проверяющих и диагностических тестов для неисправностей логических элементов схем, вычисление оценок унравляемости и наблюдаемости и др.) необходима как информация о структуре схемы, так и о единичных и нулевых наборах реализуемых ею функций. Эта информация содержится в альтернативных графах, предложенных P.P. Убаром

[2].вденным точкам ветвления сопоставляются корни других SSBDD-графов и т.д. В результате одновыходная комбинационная схема задается системой SSBDD-графов. Сложность системы SSBDD-графов (число ее вершин) линейно зависит от числа элементов схемы [3].

В [4] предлагается вместо системы SSBDD-графов использовать один FSSBDD-граф (Full SSBDD), который строится аналогично SSBDD-графам но структуре схемы при движении от ее выхода к входам. Каждая переменная точки ветвления заменяется специальным BDD-графом элемента схемы, выход которого сопоставляется этой ветви или BDD-графам инверсного элемента. FSSBDD-граф в общем случае получается значительно сложнее системы SSBDD-графов, и используется главным образом для объяснения метода синтеза тестов, поскольку ближе к традиционным BDD-графам. Оба рассматриваемые графические представления содержит в себе «упакованные» ортогональные дизъюнктивные нормальные формы (ОДОФ) функций всевозможных подсхем схемы, для которой они построены. Они различаются способами «упаковки» этих ОДДФ.

В данной работе обсуждается алгоритм построения тестов для одиночных константных неисправностей комбинационной схемы [4], ориентированный на достраивание конъюнкций [5] и использование ортогональных дизъюнктивных нормальных форм (ОДДФ) [6]. Алгоритм адоптируется на схемы из произвольных логических элементов. Приводятся результаты испытания программ для схем из произвольных логических элементов.

1. FSSBDD-ГРАФЫ И ОРТОГОНАЛЬНЫЕ ДИЗЪЮНКТИВНЫЕ НОРМАЛЬНЫЕ ФОРМЫ (ОДНФ)

1.1. Построение FSSBDD-графов

Будем иметь в виду, что построение КОБББ-графов [1] основано на использовании известного разложения булевой функции по одной переменной (разложение К. Шеннона):

F (x1 >…> Xn ) = XTF (x1 >…> Xi-1 > a i > X+1V..> Xn ) V

—ai

Xi F

(x1,…,

i+1 ? F (x1>

(1)

обычно называются коэффициентами разложения, a,=1. 210

Это разложение применяется многократно сначала к самой функции, а потом к ее коэффициентам разложения с целью построения КОВББ-графа. При представлении этого разложения фрагментом ЮВББ-графа вершине фрагмента сопоставляется переменная х. Исходящая из нее дуга, помеченная 1 (1-дуга), соответствует фиксированию переменной хI функции Е константой 1 (результат фиксирования сопоставляется вершине, в которую эта дуга заходит), а дуга, помеченная 0 (0-дуга), — константой 0 (результат фиксирования сопоставляется вершине, в которую эта дуга заходит). Если на очередном шаге разложения при фиксировании перемен-

x

n

ной функция обращается в константу 1(0), то вершина, в которую заходит дуга, соответствующая функции, объявляется 1(0)-концевой вершиной. В ЯОБББ-графе все 1-кон-цевые вершины объединяются в одну 1-концевую вершину графа, также как и все 0-концевые вершины [1]. Вершина графа, отмеченная первой по порядку переменной разложения, называется корнем графа. В [1] введены операции, позволяющие сократить число вершин в графе. Построение ЮБББ-графа связано с выбранным заранее для графа в целом порядком разложения по переменным. При выбранном порядке разложения построенный граф оказывается единственным для функции, что позволяет использовать ЯОБББ-графы для верификации дискретных схем. Договоримся в дальнейшем любой граф, полученный с использованием разложения Шеннона и совмещением 1(0)-концевых вершин, называть просто БББ-графом, если другие особенности его построения нас не интересуют.

При построении 88БББ-графов [3] применяется многократное разложение по переменной элементарных функций алгебры логики произвольного числа переменных: И, ИЛИ, НЕ И, НЕ ИЛИ, НЕ с целью построения БББ-графа для каждой из элементарных функций. Причем, наряду с обычным представлением разложения Шеннона фрагментом БББ-графа, предложено использовать модификацию этого представления, в которой вершине сопоставляется переменная Хі. В этом случае 1-дуга соответствует фиксированию

переменной хі функции Е константой 0, а 0-дуга — константой 1 (это следует из формулы (1)).

К булевым функциям И, ИЛИ применяется обычное представление разложения Шеннона, а к булевым функциям НЕ И, НЕ ИЛИ, НЕ — разложение с использованием в качестве меток вершин инверсных переменных, что соответствует опусканию инверсии с функции на входные переменные и замене функции на двойственную: л заменяется на V, V заменяется на л. В результате каждый элемент комбинационной схемы представлен в системе 88БББ-графов либо элементом И, либо элементом ИЛИ, а инвертор — инверсией переменной, сопоставляемой его входу.

И = х1 х2…хп И = х1 V х1 х2 V … V х1…хи-1 хп

Рис. 2. Элементарный БББ-граф для НЕ ИЛИ. И = х1 Х2…Хп И = х1 Vх1 х2 V… Vх1…хп-1 хп

Рис. 3. Элементарный БББ-граф для ИЛИ.

И = х1 VХ1 х2 V…VХ1…Хп-1 хп И = Х1 Х2…Хп

Рис. 4. Элементарный БББ-граф для НЕ И.

И = Х1 VХ1Х2 V…VХ1…Хп-1 Хп И = Х1 Х2…Хп

і

1

0

о

Рис. 5. Элементарный ВББ-граф для НЕ. к = х1 к = х1

На рис.1-5 приведены примеры ВББ-графов для элементарных булевых функций. В дальнейшем будем называть эти графы элементарными ВББ-графами.

Дизъюнктивная нормальная форма называется ортогональной (ОДНФ), если ее конъюнкции попарно ортогональны.

Две конъюнкции ортогональны, если в одной из них некоторая переменная х, присутствует без инверсии, а в другой — с инверсией.

Каждая ОДНФ элементарной функции представляется 1-путями (простыми цепями), соединяющими корневую вершину (корень) соответствующего элементарного ВББ-графа с 1-концевой вершиной, ОДНФ инверсии

элементарной функции представляется 0-путями, соединяющими эту же корневую вершину с 0-концевой вершиной. Всякому пути, проходимому в направлении ориентации дуг из корня некоторого элементарного БББ-графа в его 1(0)-концевую вершину сопоставляется конъюнкция переменных, отмечающих вершины этого пути. Если дуга помечена константой 1, то входящая в конъюнкцию переменная имеет знак инверсии, совпадающий с меткой вершины, из которой дуга исходит, иначе эта переменная имеет противоположный знак инверсии.

На рис. 1-5 приведены ОДНФ элементарных булевых функций.

88БВБ-граф строится путем совмещения элементарных БББ-графов элементов схемы вплоть до точек ветвления схемы; точкам ветвления сопоставляются новые 88БББ-графы и т.д., пока не построим 88БББ-графы, зависящие только от входных переменных. Заметим, что элемент, выход которого является точкой ветвления, в дальнейшем может использоваться как в прямой, так и инверсной форме.

Вместо системы 88БВБ-графов для одновыходной комбинационной схемы будем строить аналогичным образом единственный граф, а именно, Р88БВБ-граф. Опишем процедуру его построения.

Будем считать, что элементы комбинационной схемы пронумерованы в соответствие с разбиением схемы на ярусы от выхода к входам схемы. Сопоставим выходам элементов внутренние переменные. Вершины Р88БББ-графа будем нумеровать в порядке их появления.

Начнем с построения элементарного БББ-графа для элемента, корень которого сопоставляется выходу схемы, а затем последовательно заменим внутренние переменные схемы элементарными БББ-графами. Пусть часть Р88БВБ-графа уже построена и представляет собой граф, в котором выделен корень и 1(0)-кон-цевые вершины. В любую вершину графа (кроме корневой) в общем случае может заходить несколько дуг. Из любой неконцевой вершины исходит ровно две дуги: одна помечена символом 1, другая — символом 0. Каждой ветви точки ветвления, как и в системе 88БББ-графов, сопоставим внутренние переменные, отличающиеся друг от друга индексом, указывающим на номер ветви, а возможно, и знаком инверсии. Внутренние переменные с индексами и знаками инверсии отмечают вершины строящегося Р88БББ-графа.

Если в уже построенном подграфе нет вершин, помеченных внутренними переменными, процедура построения закончена, и Р88БВБ-граф получен.

Иначе выбираем очередную вершину, помеченную внутренней переменной. Из нее исходит 1-дуга, заходящая в вершину построенного графа (обозначим вершину е1), и 0-дуга, заходящая в другую вершину построенного графа (обозначим вершину е0). В рассматриваемую вершину, помеченную внутренней переменной, в общем случае может заходить несколько дуг. Строим элементарный БББ-граф для элемента схемы, выход которого сопоставлен этой внутренней переменной.

Корень этого элементарного БББ-графа замещает вершину, отмеченную рассматриваемой внутренней переменной, возможно, с индексом и знаком инверсии. Все входящие в замещаемую вершину дуги теперь входят в корневую вершину замещающего элементарного БББ-

графа. Совмещаем 1-концевую вершину элементарного БББ-графа с е1, а его 0-концевую вершину — с е0. При этом метка 1(0)-концевой вершины элементарного БББ-графа исключается, метка вершины е1(е0) сохраняется.

Такая подстановка выполняется до тех пор, пока все вершины, помеченные внутренними переменными, не будут исчерпаны. В результате получим Р88БББ-граф схемы.

Рис. 6. Комбинационная схема

Рис. 7. Процесс получения FSSBDD-графа

На рис. 6 приведена комбинационная схема, а на рис. 7 представлены этапы получения для этой схемы FSSBDD-графа. При каждом замещении вершины, отмеченной внутренней переменной, возможно, с индексом и знаком инверсии, этой переменной сопоставляется номер вершины в строящемся FSSBDD-графе, являющейся корнем подставляемого элементарного BDD-графа, и номера вершин строящегося Р88БDD-графа, совмещаемые с 1(0)-концевыми вершинами этого BDD-графа. Последние номера снабжены индексами, указывающими на тип концевых вершин. Если 1(0)-концевая вершина подставляемого BDD-графа совпадает с 1(0)-концевой вершиной FSSBDD-графа (это одна и та же вершина для строящихся FSSBDD-графов и окончательного FSSBDD-графа), то номер вершины Р88БDD-графа не указывается. Соответствующий список номеров приведен на рис. 7.

1.2. Получение ОДНФ для комбинационной схемы и ее подсхем

Конъюнкцию будем называть пустой, если в ней переменная и ее инверсия присутствуют одновременно.

Конъюнкцию будем называть неэлементарной, если она пустая или содержит несколько переменных с одним и тем же знаком инверсии, иначе конъюнкция считается элементарной.

В ROБDD-графе любой простой цепи, соединяющей корень графа с его 1(0)-концевой вершиной, сопоставляется элементарная конъюнкция. Аналогичная конъюнкция в Р88БDD-графе может быть неэлементарной.

Обозначим через Д(/) дизъюнкцию попарно ортогональных, не обязательно элементарных, конъюнкций одновыходной комбинационной схемы, полученную в результате подстановки вместо внутренних переменных (например, при движении от выхода схемы к ее входам) ОДНФ элементов И, ИЛИ, НЕ И, НЕ ИЛИ, НЕ (они приведены на рис. 1-5) от входных переменных элементов и последующего раскрытия скобок. Выбрасывание пустых конъюнкций, повторяющихся букв в непустых конъюнкциях, поглощения и склеивания конъюнкций не допускаются. Такая подстановка гарантирует попарную ортогональность конъюнкций, не обязательно элементарных.

Аналогичным образом может быть получена Д (/) для инверсной схемы, в ней элемент, выход которого является выходом схемы, заменен инверсным элементом. В [4] доказано, что множество 1(0)-путей Р88БDD-графа представляет Д (/) Д (/) .

Каждому 1(0)-пути Р88БDD-графа сопоставляется конъюнкция входных переменных. Если в конъюнкции встречаются взаимно инверсные переменные, то такой путь будем называть противоречивым, то есть противоречивый путь представляет пустую конъюнкцию. Любую непустую конъюнкцию можно привести к элементарной, исключив повторение одинаковых букв. Это значит, что

из Д (/) Д (/) можно получить (ОДНФ) функции (ОДНФ инверсии функции), исключив пустые конъюнкции и повторяющиеся буквы в непустых конъюнкциях с целью превращения последних в элементарные конъюнкции. Обозначим ОДНФ через Д (/) Д (/) .

FSSBDD-граф содержит также ОДНФ и ее инверсию для любой подсхемы, выход которой сопоставляется выходу некоторого элемента схемы, а входы -входным переменным рассматриваемой схемы [4].

Выясним, как найти ОДНФ (ее инверсию) для подсхемы.

Подсхеме (будем называть ее v-подсхемой) в общем случае может быть сопоставлено в Р88БDD-графе несколько подграфов, корни которых сопоставлены символу одной и той же внутренней переменной V, возможно, с различными индексами и знаками инверсии. Обозначим символом Н функцию, реализуемую v-подсхемой, а через Н — инверсию этой функции. Каждый из подграфов задается номером вершины Р88БDD-графа, сопоставленной переменной V и являющейся корнем выделяемого подграфа, и номерами вершин Р88БDD-графа, сопоставленными 1,0-концевым вершинам этого подграфа. Непротиворечивые пути (простые цепи), соединяющие корень выделяемого подграфа с его 1(0)-концевой вершиной,

представляют функцию Н(Н) в виде ОДНФ. Номера вершин, сопоставляемых корню подграфа и его 1,0-кон-цевым вершинам были найдены при подстановке элементарного БDD-графа вместо вершины, отмеченной переменной V с соответствующим индексом и знаком инверсии. При дальнейших подстановках с целью замены других внутренних переменных элементарного БDD-графа эти вершины стали корнем и 1,0-концевыми вершинами

подграфа, представляющего рассматриваемую подсхему. Назовем выделенный подграф у-подграфом.

На рис. 7, например, подсхеме, выходом которой является выход элемента 6 комбинационной схемы, представленной на рис. 6, сопоставляется два подграфа. Корнем одного из подграфов является вершина 3 Р88БББ-графа, 1-концевая вершина подграфа совпадает с 1-концевой вершиной Р88БББ-графа, а 0-кон-цевая вершина подграфа есть вершина 2 Р88БББ-графа. Пути, ведущие из 3 в 1-концевую вершину Р88БББ-графа, представляют функцию Н, реализуе-

мую у-подсхемой, в виде дизъюнкции соответствующих путям конъюнкций: а V асё, а пути из вершины 3

в вершину 2 — инверсию этой функции: ас V асй . Корнем другого подграфа является вершина 2 Р88БББ-графа, его 1-концевая вершина есть вершина 4 Р88БББ-графа, а его 0-концевая вершина совпадает с

0-концевой вершиной Р88БББ-графа. Будем иметь ввиду, что у-подграфы, сопоставляемые внутренней переменной, возможно, с разными индексами, но одним и тем же знаком инверсии, изоморфны.

2. ПОСТРОЕНИЕ ТЕСТОВ ДЛЯ ОДИНОЧНЫХ КОНСТАНТНЫХ НЕИСПРАВНОСТЕЙ ПОЛЮСОВ ЭЛЕМЕНТОВ КОМБИНАЦИОННОЙ СХЕМЫ

В работе [6] предложен метод построения тестов для одиночных константных неисправностей полюсов элементов комбинационной схемы, основанный на использовании ОДНФ, описывающих поведение фрагментов схемы.

Пусть не исправен выход элемента схемы, сопоставляемый переменной V (выход элемента может быть точкой ветвления). Задана неисправность константа 0. Необходимо найти набор значений входных переменных схемы (тестовый набор), обнаруживающий эту неисправность. (2).

Здесь ОДНФ К представляет конъюнкции, не содержащие переменной V, ОДНФ К у представляет конъюнкции, содержащие переменную V, ОДНФ К представляет конъюнкции, содержащие переменную V. Эти ОДНФ попарно ортогональны между собой.

Обозначим через К* ОДНФ, полученную из Ку вычеркиванием переменной V. Аналогичным образом получим ОДНФ К *. Пусть Д0(Н) есть ОДНФ функции, реализуемые подсхемой, выход которой сопоставлен переменной V, (подсхеме сопоставляется v-подграф в FSSBDD-графе [4] ), а Д0(Н) — ОДНФ инверсии

этой функции. Напомним, что рассматриваемые ОДНФ зависят от входных переменных схемы. В [6] доказано, что набор значений входных переменных является тестовым для константной неисправности 0, если и только если он обращает в единицу выражение К * & Д 0(Н) и в нуль выражение К * .

Любую часть пути в графе будем называть отрезком пути. Отрезки не противоречивы, если сопоставляемые им непустые конъюнкции образуют при перемножении непустую конъюнкцию.

Приведенные ниже теоремы относятся к фрагментам упомянутых в них ОДНФ, связанных с одним и тем же v-подграфом [4].

Теорема 1. Конъюнкция из К* представляется двумя непротиворечивыми отрезками пути FSSBDD-графа. Первый из них начинается в корне графа и заканчивается в корневой вершине рассматриваемого у-под-графа, сопоставляемой переменной у( V), а второй на-

начинается в 1(0)-концевой вершине этого у-подграфа и заканчивается в 1-концевой вершине FSSBDD-графа.