Как работают логические элементы на полевых транзисторах. Какие виды полевых транзисторов используются для создания логических схем. Как реализуются базовые логические операции с помощью МОП-транзисторов. Особенности и преимущества КМОП-логики.

Принцип работы полевых транзисторов в логических схемах

Полевые транзисторы играют ключевую роль в построении современных логических схем. Их основное преимущество заключается в том, что они управляются не током, а напряжением, что позволяет создавать схемы с очень низким энергопотреблением. Рассмотрим основные принципы работы полевых транзисторов в логических элементах:

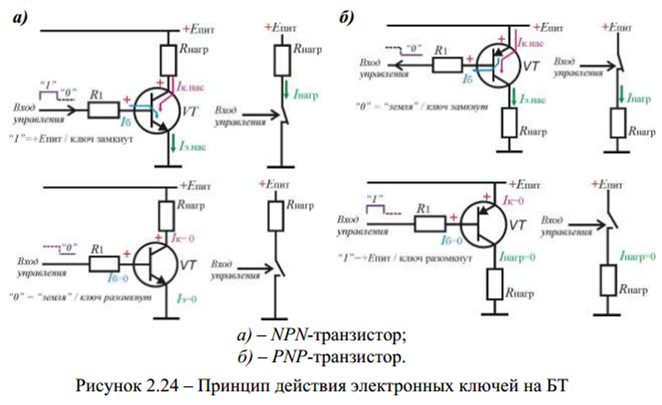

- Полевой транзистор работает как управляемый напряжением ключ — при подаче напряжения на затвор канал открывается и пропускает ток.

- В логических схемах используются МОП-транзисторы (металл-оксид-полупроводник) с изолированным затвором.

- Существуют n-канальные и p-канальные МОП-транзисторы, которые открываются при разной полярности напряжения на затворе.

- Комбинируя транзисторы разных типов, можно реализовать любые логические функции.

Такой принцип работы позволяет создавать логические элементы с очень низким статическим энергопотреблением, так как ток через транзисторы протекает только в момент переключения.

Реализация базовых логических элементов на МОП-транзисторах

Рассмотрим, как реализуются основные логические операции с помощью МОП-транзисторов:

Инвертор (НЕ)

Простейший логический элемент на МОП-транзисторах — инвертор. Он состоит из двух комплементарных транзисторов:

- p-канального транзистора, подключенного к напряжению питания

- n-канального транзистора, подключенного к земле

При подаче логического нуля на вход открывается p-канальный транзистор, а n-канальный закрывается. На выходе формируется высокий уровень. При подаче логической единицы — наоборот.

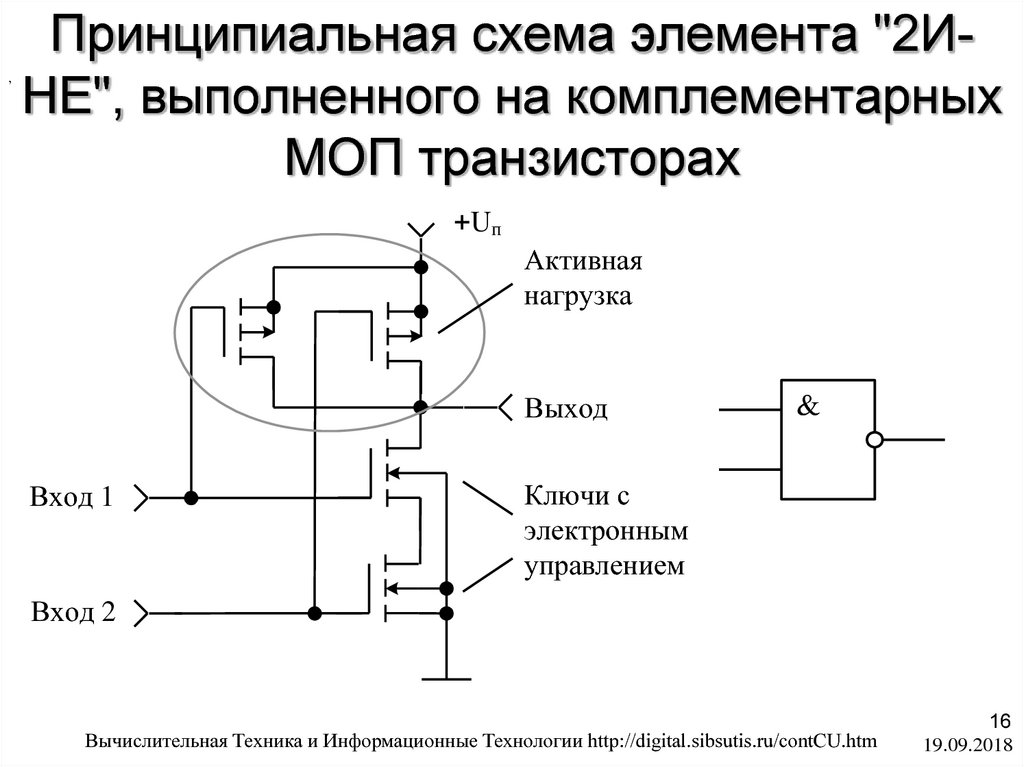

Элемент И-НЕ

Элемент И-НЕ реализуется с помощью двух последовательно соединенных n-канальных транзисторов и двух параллельно соединенных p-канальных:

- Если хотя бы на одном входе низкий уровень — открывается соответствующий p-канальный транзистор, формируя на выходе высокий уровень

- Только если на обоих входах высокий уровень — открываются оба n-канальных транзистора, формируя на выходе низкий уровень

Элемент ИЛИ-НЕ

Элемент ИЛИ-НЕ строится аналогично, но с параллельным соединением n-канальных транзисторов и последовательным p-канальных:

- Если хотя бы на одном входе высокий уровень — открывается соответствующий n-канальный транзистор, формируя на выходе низкий уровень

- Только если на обоих входах низкий уровень — открываются оба p-канальных транзистора, формируя на выходе высокий уровень

Особенности и преимущества КМОП-логики

КМОП-логика (комплементарная МОП) является наиболее распространенной технологией построения логических схем. Ее ключевые преимущества:

- Очень низкое статическое энергопотребление — ток потребляется только при переключении

- Высокая помехоустойчивость за счет большого диапазона питающего напряжения

- Высокая степень интеграции — можно создавать сложные схемы с миллионами транзисторов

- Простота изготовления — требуется меньше технологических операций по сравнению с биполярными транзисторами

Благодаря этим преимуществам КМОП-логика стала основой для создания современных процессоров, микроконтроллеров и других сложных цифровых схем.

Применение логических элементов на полевых транзисторах

Логические элементы на полевых транзисторах нашли широкое применение в различных областях электроники:

- Процессоры и микроконтроллеры — основа всех вычислительных устройств

- Оперативная и флеш-память — ячейки памяти строятся на КМОП-транзисторах

- Программируемые логические интегральные схемы (ПЛИС) — позволяют создавать сложные цифровые устройства

- Цифровые датчики и АЦП — обработка сигналов с датчиков

- Цифровые схемы управления в различной технике

Практически вся современная цифровая электроника в той или иной степени использует логические элементы на полевых транзисторах. Это делает их изучение крайне важным для понимания принципов работы электронных устройств.

Проектирование логических схем на МОП-транзисторах

При проектировании логических схем на МОП-транзисторах необходимо учитывать ряд важных аспектов:

- Правильный выбор соотношения ширины и длины канала транзисторов для обеспечения нужных характеристик

- Учет паразитных емкостей, влияющих на быстродействие схемы

- Обеспечение симметричности фронтов переключения для уменьшения задержек

- Оптимизация топологии для минимизации площади кристалла

- Учет статических токов утечки, особенно в субмикронных технологиях

Современные средства автоматизированного проектирования позволяют учесть все эти факторы и создавать оптимальные схемы с миллионами транзисторов. Однако понимание базовых принципов построения логических элементов остается крайне важным для разработчиков цифровых схем.

Цифровая логика — Компьютерные системы, часть 3

Оглавление

- Общий взгляд

- Представление данных

- Цифровая логика

- Архитектура фон Неймана

Транзисторы

Транзистор является ключевым устройством, которое позволяет построить логический элемент. Существует несколько видов транзисторов, мы рассмотрим МОП-транзисторы (от слов металл-диэлектрик-полупроводник), как наиболее популярные. Что бы понять их детальное устройство требуются предварительные знания физики, поэтому тут мы рассмотрим лишь функциональную модель, которой будет вполне достаточно для наших целей. Существует два типа МОП-транзисторов: P-тип и N-тип. Что бы понять их использование, рассмотрим сначала простую электрическую цепь.

Тут мы видим источник тока, лампу и также переключатель. Если переключатель закрыт, то мы имеем замкнутую цепь, по которой идет ток, если открыт – то цепь незамкнута и, соответственно, тока не возникает. Что бы проще изображать цепь, можно не показывать каждый раз источник питания целиком, а изобразить сверху место высокого напряжения (условно – 1.2 вольта), а снизу – место низкого (0 вольт).

Что бы проще изображать цепь, можно не показывать каждый раз источник питания целиком, а изобразить сверху место высокого напряжения (условно – 1.2 вольта), а снизу – место низкого (0 вольт).

Так вот, полезное для нас свойство транзистора заключается в том, что его можно использовать в качестве переключателя. Рассмотрим схему транзистора N-типа.

У него есть три терминала. Верхний называется сток, нижний исток, средний – затвор.

Смысл в том, что мы можем использовать его как переключатель. Если на затвор подать высокое напряжение, транзистор будет действовать как переключатель в закрытом состоянии, то есть пропускать ток. Если же на затвор подать низкое напряжение, транзистор действует как переключатель в открытом состоянии (или как разрыв в цепи) и не пропускает ток.

Рассмотрим тебе транзистор P-типа.

Он ведет себя противоположным образом, если на его затвор подать высокое напряжение, он действует как переключатель в открытом положении, если же низкое – как переключатель в закрытом.

Логические элементы

Как я уже писал, на основе транзисторов можно построить логические элементы (мы также будем их называть логическими гейтами или просто гейтами). Логический гейт – это устройство, которое принимает на вход одно или несколько значений битов и на основе их генерируют значение, которое подает на выход. С физическое точки зрения эти значения являются показателями напряжения. Высокое напряжение мы условно обозначаем единицей, низкое – нулем.

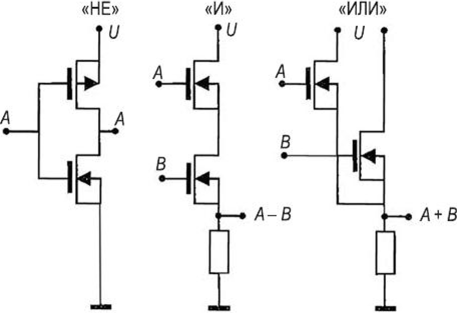

NOT-гейт

Самым простым гейтом является NOT-гейт. Он принимает на вход один бит и выдает на выход противоположный.

|

A |

Z |

|

0 |

1 |

|

1 |

0 |

Его электрическая схема выглядит так.

Если на вход подается высокое напряжение, то на выход низкое и наоборот.

OR-гейт

OR-гейт (от английского OR – или) принимает на вход два значения, если какое-либо из них равно единице, то и на выход подается единица, если оба нуля, то на выходе мы имеем ноль.

|

A |

B |

Z |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

Электрическая схема.

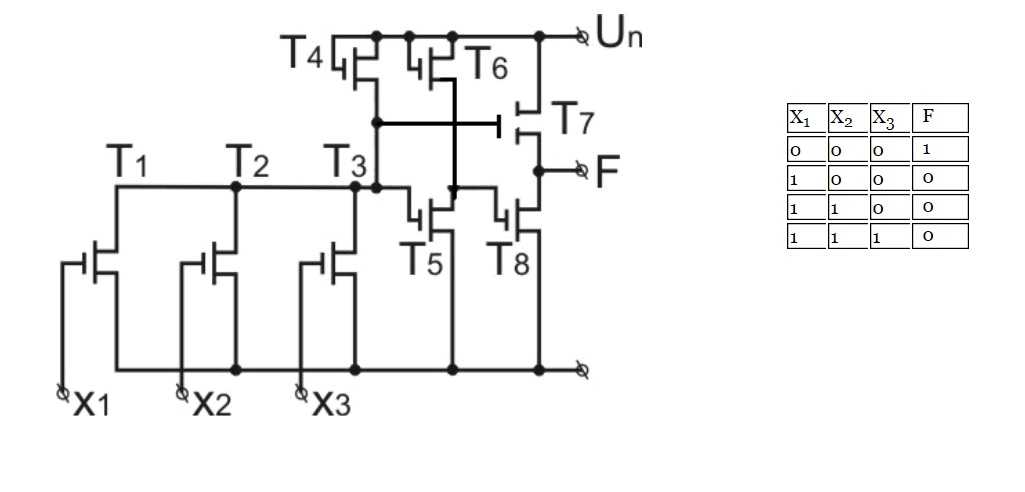

NOR-гейт

NOR-гейт работает как OR наоборот. То есть, если на обоих входах нули, то на выходе будет единица, во всех остальных случаях на выходе будет ноль.

|

A |

B |

Z |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

Электрическая схема.

AND-гейт

AND-гейт (от английского and – или) выдает единицу только если на обоих его входах единицы. В остальных случаях он выдает ноль.

|

A |

B |

Z |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

Электрическая схема.

NAND-гейт

NAND-гейт является обратным к AND. Он выдает ноль, если на обоих его входах единицы. В других случаях он выдает единицу.

|

A |

B |

Z |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Электрическая схема.

Комбинационные логические схемы

Комбинируя логические гейты между собой можно создавать логические схемы. Можно выделить два вида логических схем: комбинационные и последовательные. Начнем с первых.

Декодер

Декодер – это такая схема, которая имеет несколько выходов, но только один ее выход всегда выдает единицу (какой именно – зависит от входных значений), а остальные всегда выдают ноль. Рассмотрим декодер 2×4.

2 означает количество входов, а 4 – количество выходов. 2 бита могут образовывать четыре комбинации, соответственно каждому возможному входу соответствует уникальная выходная комбинация. Таким же образом можно создавать и более большие регистры, например 3×8, 4×16 и т.д.

Мультиплексер

Мультиплексер имеет несколько входов и один выход.

Его смысл в том, что из нескольких входных сигналов (I0, I1, I2, I3) один и только один он пропускает на выход. Какой именно – мы можем выбрать с помощью входов A и B. Можно создавать мультиплексеры и с большим количеством входных сигналов.

Сумматор

Когда мы побитого складываем два бинарных числа мы должны сложить два текущих бита, перенести единицу если результат больше 1 и еще добавить результат предыдущего переноса, если он есть.

|

Первый бит |

Второй бит |

Входящий перенос |

Сумма |

Перенос |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

Теперь построим такую схему с помощью логических элементов.

Последовательные логические схемы

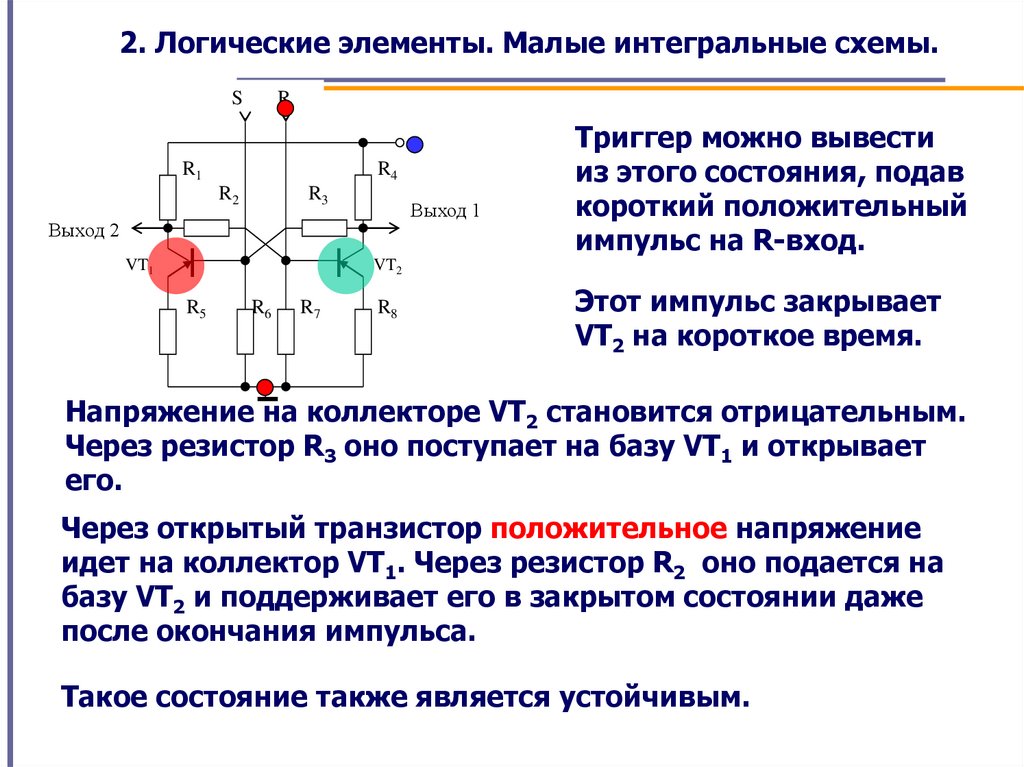

В комбинационных логических схемах выходные значение зависят только от входных. Но что бы реализовать, например, запоминающий элемент такие схемы не годятся, ведь понятие памяти по отношению к схеме означает ее способность иметь несколько возможных состояний, переходить из одного состояния в другое под действием входных сигналов и сохраняться в этом состоянии. Схемы такого рода еще называют триггерами. Рассмотрим один из них.

R-S триггер

Возьмем два NAND-гейта и соединим таким образом.

Представим, что на A и на B поданы единицы, какие значения будут на C и на D? На самом деле мы будем иметь неопределенность, поскольку значение C зависит от значения D, а мы не знаем не того не другого.

Теперь подадим единицу на A и ноль на B.

Как работает NAND-гейт? Он выдает ноль, только если на обоих его входах единицы. То есть в данном случае у нас уже есть ноль на входе B, значит нижний NAND будет выдавать единицу. Тогда верхний гейт будет выдавать ноль.

Тогда верхний гейт будет выдавать ноль.

Подадим теперь единицу на B. Как видно, это никак не повлияет на значения C и D

Теперь подадим ноль на A и единицу на B.

В данном случае верхний гейт будет выдавать единицу, поскольку на его вернем входе ноль, следовательно нижний гейт будет выдавать ноль.

Теперь подадим единицу на A. Верхний и нижний гейт продолжат выдавать предыдущие значения!

Как видно, при единицах на A и B, гейты сохраняют свои предыдщие выходные значения.

Такая схема называется R-S триггером. Ее свойство, позволяющее хранить предыдущее состояние и используется для создания запоминающего элемента. У гейтов может быть два варианта выходных значений, один из будет использовать для хранение единицы, другой – для хранения нуля.

В зависимости от того, какое значение мы хотим записать мы либо подаем ноль на A и единицу на B – либо наоборот. Если после этого подать единицу на тот вход, на котором до этого был подан ноль, входные значения сохранятся.

Теперь можно сделать полноценный запоминающий элемент

Если на S единица, то на B мы также будем иметь единицу, а на A – либо единицу (если на i – ноль), либо ноль (если на i – единица). Таким образом мы записываем нужное нам значение, которое гейт выдает на C. Если на S ноль – то в независимости от значения i схема будет сохранять предыдущее значение, которое было записано, когда на S была единица. Таким образом, с помощью входа S мы открывает схему для записи, с помощью входа i записываем какое-либо значение. Такое устройство может хранить 1 байт.

Регистр

Мы можем объединить несколько запоминающих устройств, емкостью 1 байт в одно.

Получившиеся устройство называют регистром. Тут мы привели регистр емкостью в один байт. В современных же процессорах размер регистра может достигать восьми байт.

Логические элементы на полевых транзисторах

Похожие презентации:

3D печать и 3D принтер

Видеокарта. Виды видеокарт

Анализ компании Apple

Трансформаторы тока и напряжения

Транзисторы

Устройство стиральной машины LG. Электрика

Электрика

Конструкции распределительных устройств. (Лекция 15)

Электробезопасность. Правила технической эксплуатации электроустановок

Магнитные пускатели и контакторы

Работа на радиостанциях КВ и УКВ диапазонов. Антенны военных радиостанций. (Тема 5.1)

1. Логические элементы на полевых транзисторах

Полевой транзистор – транзистор, в котором сила проходящего через него токарегулируется внешним электрическим полем, т. е. напряжением.

Это принципиальное различие между ним и биполярным транзистором, где сила

основного тока регулируется управляющим током.

Принцип действия полевого транзистора

Поскольку у полевого транзистора нет управляющего тока, то у него очень высокое

входное сопротивление, достигающее сотен ГигаОм и даже ТерраОм (против сотен

КилоОм у биполярного транзистора).

Полевые транзисторы иногда называют униполярными, поскольку носителями

электрического заряда в нем выступают только электроны или только дырки.

В работе же биполярного транзистора, как следует из названия, участвует одновременно

два типа носителей заряда – и электроны и дырки.

Классификация полевых транзисторов

Полевые транзисторы (FET: Field-Effect-Transistors) разделяются на два типа:

– с управляющим PN-переходом (JFET: Junction-FET) и

– с изолированным затвором (MOSFET: Metal-Oxid-Semiconductor-FET).

Каждый из типов может быть как с N–каналом, так и с P-каналом.

В роли носителей электрического заряда выступают:

– у транзисторов с N-каналом – электроны.

– у транзисторов с P-каналом – дырки.

Обозначение JFET транзисторов на принципиальных схемах

Полевой транзистор с изолированным затвором MOSFET

Полевой транзистор с изолированным затвором – это полевой транзистор, затвор которого

электрически изолирован от проводящего канала полупроводника слоем диэлектрика.

Благодаря этому, у транзистора очень высокое входное сопротивление (у некоторых

моделей оно достигает 1017 Ом).

МОП-транзистор (Металл-Оксид-Полупроводник), или

МДП-транзистор (Металл-Диэлектрик-Полупроводник).

MOSFET (Metal-Oxide-Semiconductor-Field-Effect-Transistor)

МДП-транзисторы делятся на два типа

– со встроенным каналом и

– с индуцированным каналом.

В каждом из типов есть транзисторы с N–каналом и P-каналом.

УГО МОП (MOSFET) транзистора

со встроенным каналом

УГО МОП (MOSFET) транзистора

с индуцированным каналом

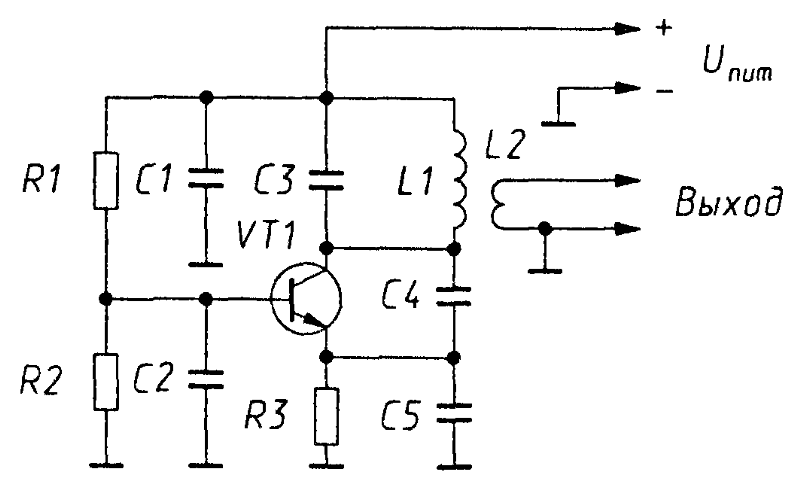

Работа n-МДП-транзистора с индуцированным каналом

Выходные (стоковые) характеристики

Сток-затворная характеристика

Характеристики n-МОП и p-МОП транзисторов

Характеристики транзисторов p-типа имеют аналогичный вид, но отличаются

напряжением на затворе и полярностью приложенных напряжений (зеркальное

отображение в третьем квадранте).

p-МОП транзистор

Передаточная характеристика

Крутизна передаточной характеристики:

S=DIC/DUЗИ (при UCИ – const)

Коэффициент усиления: KU = SRC

n-МОП транзистор

Передаточная характеристика

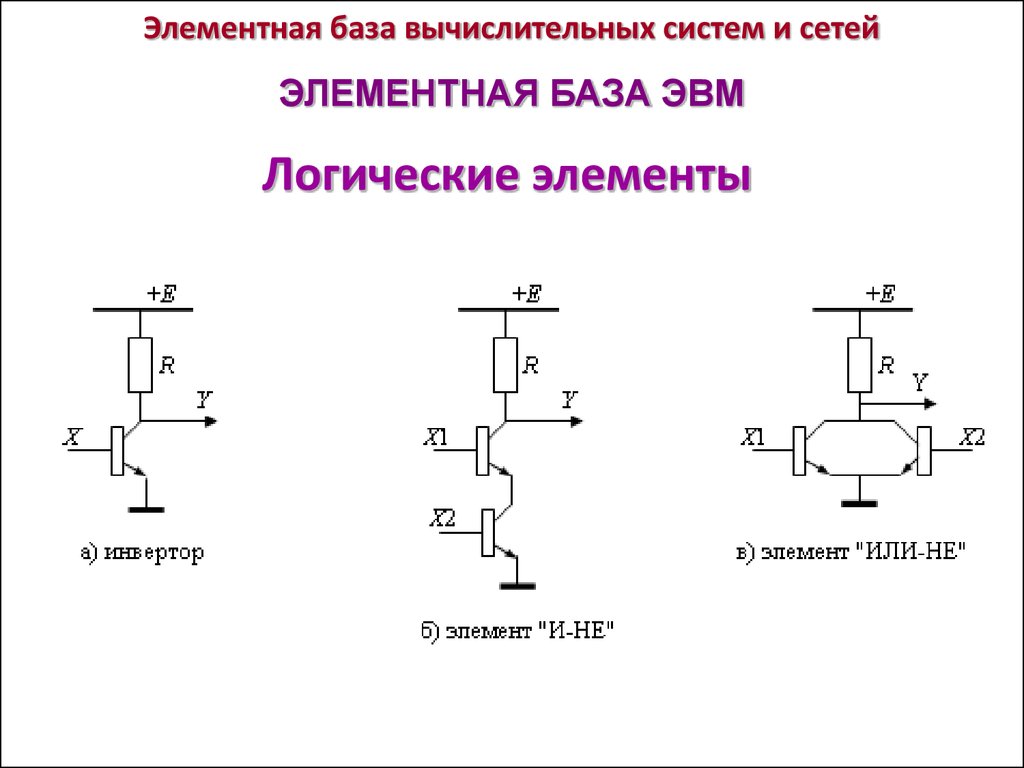

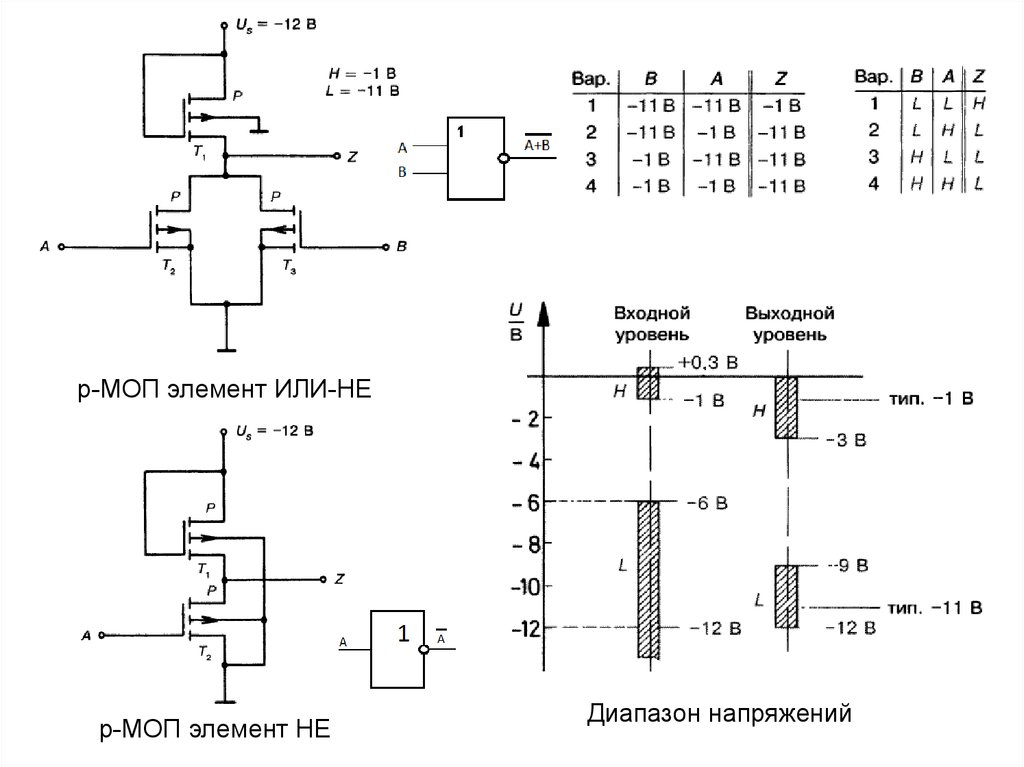

Логические элементы на p-МОП транзисторах

RK,Т1 ≥ 100 кОм

RK,Т2,Т3 ≤ 1 кОм

р-МОП элемент И-НЕ

Реализация логического элемента

И-НЕ в интегральной схеме

р-МОП элемент ИЛИ-НЕ

р-МОП элемент НЕ

Диапазон напряжений

Важнейшие параметры семейства p-МОП

1.

2.

3.

4.

5.

Напряжение питания – -12В (от -9 В до -20 В)

Энергопотребление на вентиль – 6 мВт при H и 0 мВт при L

Быстродействие – 400 нс.

Частота переключения (макс.) – 2 МГц

Зазор помехоустойчивости (типовой) – 5 В

• p-МОП логические элементы работают медленно, но устойчиво.

Нуждаются в достаточно большом напряжении питания.

• Применяются в схемах с низким быстродействием и высокой

помехоустойчивостью.

• Интегральные

элементов.

схемы

обладают

высокой

плотностью

упаковки

Логические элементы на n-МОП транзисторах

n-МОП логические элементы

Напряжение питания – +5В

Энергопотребление – 2 мВт (L)

0 мВт (Н)

Быстродействие – 50 нс

Максимальная частота – 20 МГц

Зазор помехоустойчивости – 2 В.

Диапазон напряжений

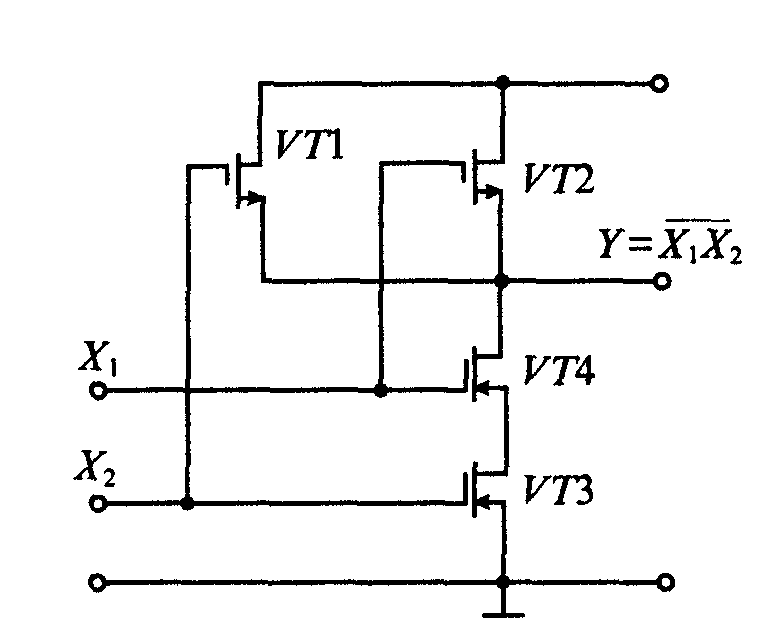

Логические элементы на КМОП транзисторах

Схема КМОП НЕ-элемента

Принцип действия КМОП НЕ-элемента

Все КМОП-элементы устроены так, что в токовой ветви один транзистор всегда закрыт, а

другой всегда открыт.

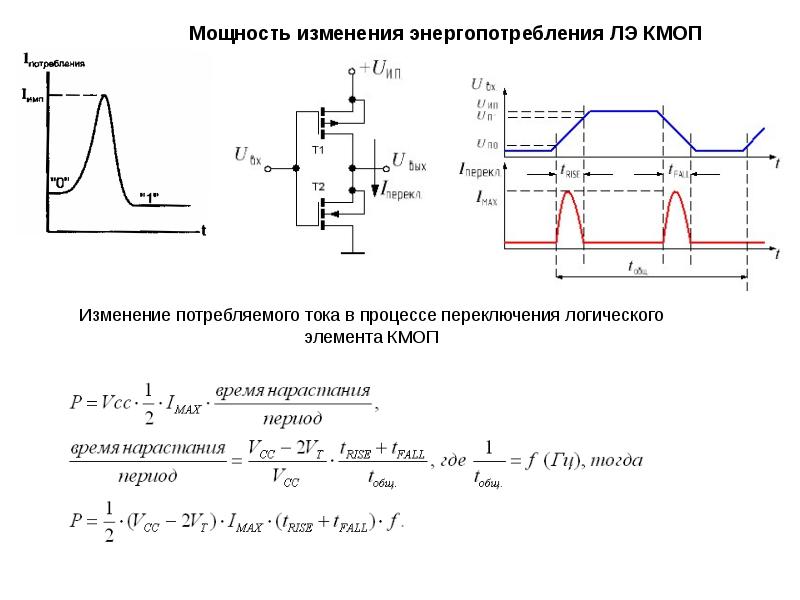

Энергопотребление КМОП-элементов крайне низко. Оно зависит в основном от

количества переключений в секунду или частоты переключения.

Только во время переключения от источника питания потребляется небольшой ток, так как

оба транзистора одновременно, но недолго открыты. Один из транзисторов переходит из

открытого состояния в запертое и еще не полностью заперт, а другой — из запертого в

открытое и еще не полностью открыт. Также должны перезарядиться транзисторные

емкости.

Мощность изменения энергопотребления ЛЭ КМОП

Изменение потребляемого тока в процессе переключения логического

элемента КМОП

Базовые логические элементы КМОП

Схема КМОП ИЛИ-НЕ-элемента

Логический элемент 4ИЛИ-НЕ,

входящий в состав микросхемы

КР1561ЛЕ6

Схема КМОП И-НЕ-элемента

Логический элемент 4И-НЕ,

входящий в состав микросхемы

КР1561ЛА1

Передаточный логический элемент КМОП

(электронный ключ, переключатель)

Ключ на n-канальном МОП-транзисторе

с индуцированным каналом

Зависимость сопротивления

канала n-МОП и p-МОП ключа от Uвх

Рабочая таблица передаточного

логического элемента

№

Принципиальная схема

передаточного

логического элемента

З2

З1

L ≈ 0 В, H ≈ +5 В

1

L

H

RAZ — высокоомный

2

H

L

RAZ — низкоомный

Передаточный элемент работает как переключатель.

Принципиальная схема

Для того чтобы перевести коммутатор в состояние

включено, нужно приложить к затвору нормально

открытого МОП-транзистора VT1 положительное

управляющее напряжение Uупр, равное, по меньшей

мере 2Uoтc, а к затвору транзистора VT2 – такое же

напряжение, но противоположное по знаку.

При малых величинах входного напряжения Uвх оба

МОП-транзистора будут открыты.

При отрицательных значениях входного напряжения

транзисторы VT1 и VT2 меняются ролями.

Передаточный логический

элемент с управляющим

элементом НЕ

Для того чтобы перевести коммутатор в состояние

выключено, необходимо изменить полярность

управляющего напряжения.

Важнейшие электрические параметры семейства КМОП

до 15 Вольт)

(30÷40% от UИ.П.)

Передаточные характеристики КМОП

UИ.П. = +5В

+10В

Особенности микросхем КМОП структуры

Специфические особенности микросхем КМОП структуры:

чувствительность к

статическим зарядам, диодно-резистивная охранная цепочка и малая токовая отдача

требуют соблюдения правил предосторожности в применении и обращении.

Емкость на выходе и входе. Если на выходе инвертора присутствует конденсатор, в

моменты переключений через открытые транзисторы протекают токи заряда и разряда.

При больших значениях ёмкости, открытый транзистор работает в режиме близком к

короткому замыканию. В обычных условиях емкостная нагрузка не должна превышать

500 пФ. Если ёмкость больше, то надо использовать разрядный резистор R для

ограничения тока, чтобы был не более 1÷2 мА.

Включение ограничивающих резисторов

Диодно-резистивная охранная цепочка

Защита входов от перегрузок.

Входное напряжение микросхем КМОП с охранной диодно-резистивной цепочкой на

входе для предотвращения отпирания входных диодов в прямом направлении не должно

выходить за пределы –0,7В ≤ Uвх ≤ UИ.П.+0,7В. Иначе также надо использовать

токоограничивающий резистор для ограничения тока уровнем 1÷2мА.

Неиспользуемые входы КМОП. Их надлежит включать определённым

образом, так, чтобы не нарушились условия работы микросхемы в целом.

Так же как и в ТТЛ свободные входы объединяют с +UИ.П. или общим проводом

в зависимости от функции элемента либо объединяют их с другими,

задействованными входами.

а)

б)

В случае варианта б) за счёт постоянного смещения отпирание n-канальных

транзисторов происходит раньше и общее пороговое напряжение становится

меньше, чем в случае а). Поэтому вариант а) более эффективен применительно

к помехам, возникающим в общей шине, а вариант б) в отношении защиты от

помех, возникающих в шине питания.

Входы КМОП микросхем (в отличие от ТТЛ) оставлять свободными

недопустимо.

Если какой-нибудь вход окажется неподсоединённым, на нём могут возникнуть

непредсказуемые напряжения за счёт наводок и связей через паразитные

ёмкости. Следствием этого может быть не только неверное действие

микросхемы, но и её повреждение.

Правила обращения с микросхемами КМОП

Микросхемы КМОП структуры нуждаются в сравнении с микросхемами других

семейств, например, ТТЛ, ЭСЛ в более бережном отношении.

Это касается

Это касаетсякак условий монтажа микросхем на платах, так и правил их хранения и

эксплуатации в аппаратуре.

При обращении с микросхемами КМОП следует соблюдать следующие меры

предосторожности:

В процессе хранения и транспортировки отдельных микросхем выводы их должны

быть соединены между собой;

Нельзя производить смену микросхем при включённом напряжении питания;

Допустимый электростатический потенциал на входах – не более 100В;

Плату со смонтированными микросхемами следует брать за торцы, не касаясь

разъёмов;

При монтаже тело монтажника должно быть заземлено с помощью проводящего

браслета, соединённого с контуром заземления через резистор 500 кОм или

вначале коснуться общего провода питания;

Необходимо избегать одежды из синтетических материалов;

Микросхему следует устанавливать на плату после выполнения всех остальных

соединений;

Пайку выводов следует вести в последовательности: «общий». «питание»,

остальные контакты.

English Русский Правила

Транзисторные затворы

Транзисторные затворы

|

Индекс Концепции электроники Цифровая электроника Справочник | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

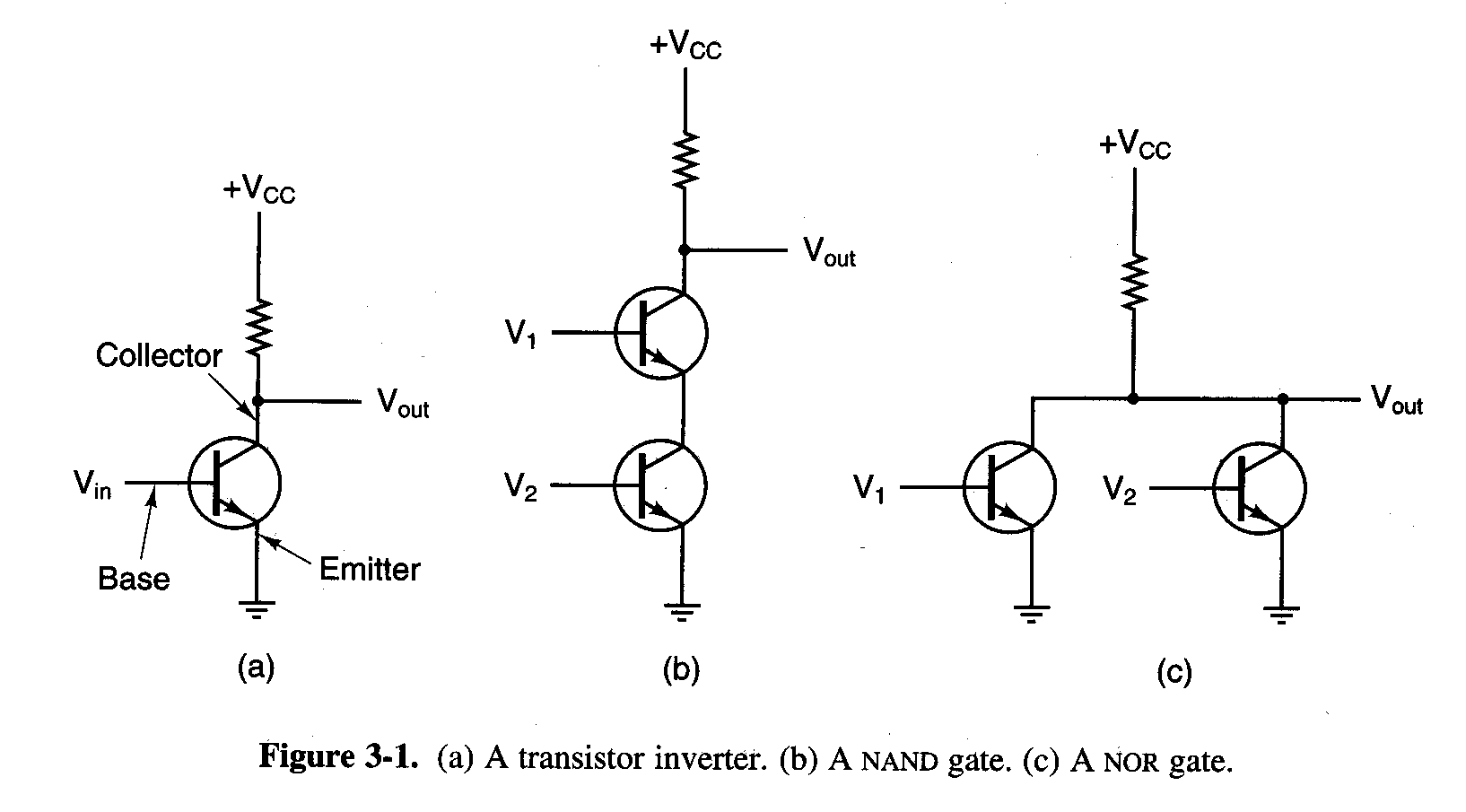

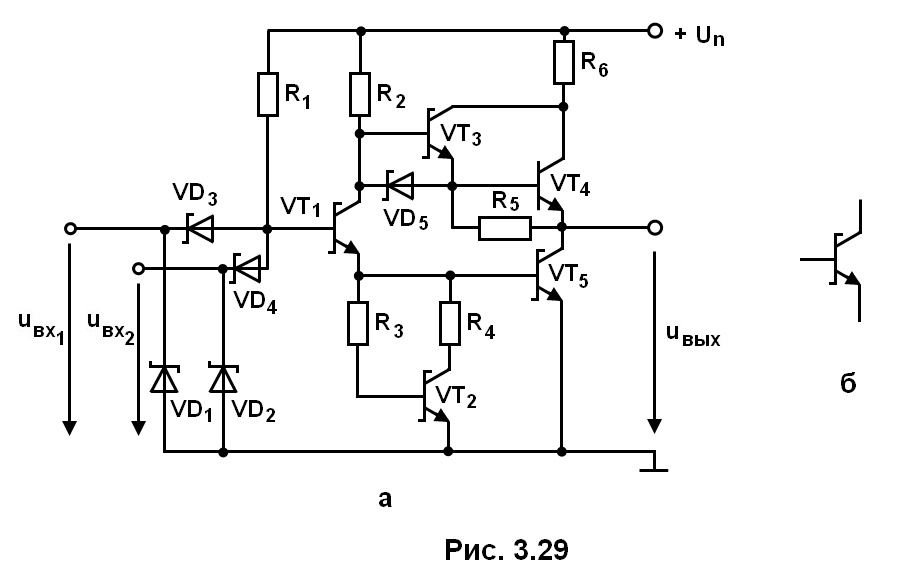

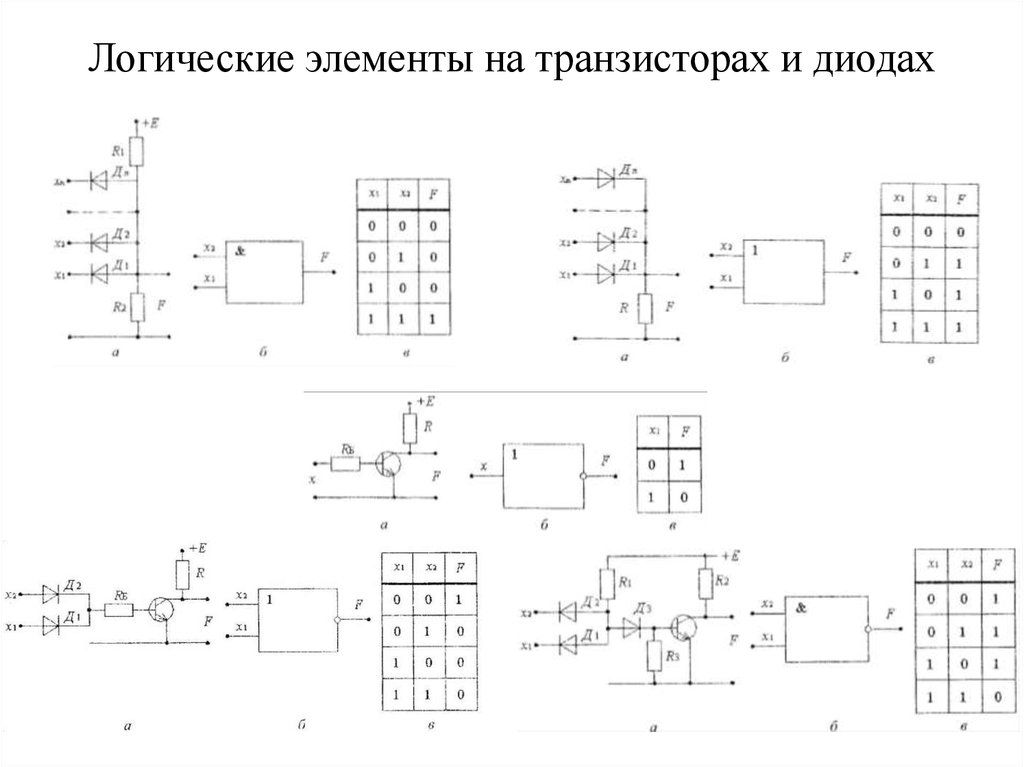

Когда диод база-эмиттер включен достаточно, чтобы перейти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики ИЛИ транзисторы включены параллельно, и на выходе устанавливается высокий уровень, если какой-либо из транзисторов находится в проводящем состоянии.

Когда диод база-эмиттер включен достаточно, чтобы перейти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики ИЛИ транзисторы включены параллельно, и на выходе устанавливается высокий уровень, если какой-либо из транзисторов находится в проводящем состоянии.  Когда диод база-эмиттер включен достаточно, чтобы перейти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики И-НЕ транзисторы включены последовательно, но выход находится над ними. Выход высокий, если оба входа A и B не имеют высокого уровня, и в этом случае выход снимается близко к потенциалу земли.

Когда диод база-эмиттер включен достаточно, чтобы перейти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики И-НЕ транзисторы включены последовательно, но выход находится над ними. Выход высокий, если оба входа A и B не имеют высокого уровня, и в этом случае выход снимается близко к потенциалу земли.  Когда диод база-эмиттер включен достаточно, чтобы перейти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики ИЛИ-НЕ транзисторы подключены параллельно выходу над ними, поэтому, если один или оба входа имеют высокий уровень, на выходе устанавливается низкий уровень.

Когда диод база-эмиттер включен достаточно, чтобы перейти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. Для логики ИЛИ-НЕ транзисторы подключены параллельно выходу над ними, поэтому, если один или оба входа имеют высокий уровень, на выходе устанавливается низкий уровень.  Когда диод база-эмиттер включен достаточно, чтобы перейти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. В этом альтернативном способе достижения логики НЕ-ИЛИ используется только один транзистор с двумя входами, подключенными к его базе через резисторы. Если один или оба входа имеют высокий уровень, на выходе устанавливается низкий уровень.

Когда диод база-эмиттер включен достаточно, чтобы перейти в состояние насыщения, напряжение коллектора по отношению к эмиттеру может быть близко к нулю, и его можно использовать для построения логических элементов семейства ТТЛ. В этом альтернативном способе достижения логики НЕ-ИЛИ используется только один транзистор с двумя входами, подключенными к его базе через резисторы. Если один или оба входа имеют высокий уровень, на выходе устанавливается низкий уровень.  Этот метод называется резисторно-транзисторной логикой (RTL).

Этот метод называется резисторно-транзисторной логикой (RTL).