Что такое логические элементы в цифровых схемах. Как работают базовые логические вентили И, ИЛИ, НЕ. Где применяются логические элементы в электронике. Какие бывают типы логических микросхем.

Основные логические элементы и их принцип действия

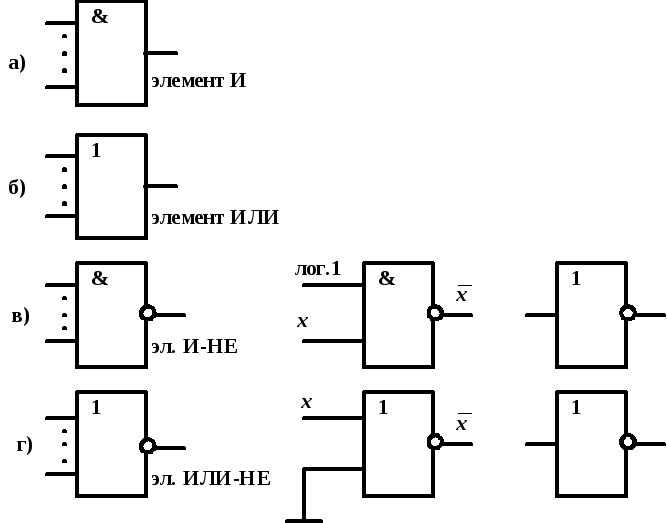

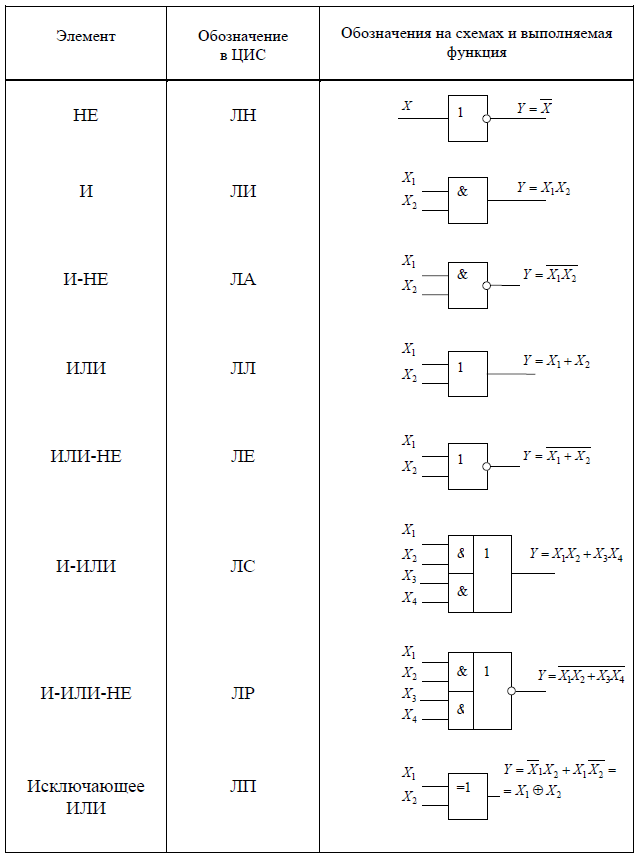

Логические элементы являются фундаментальными компонентами цифровых электронных схем. Они выполняют базовые логические операции над входными сигналами и формируют соответствующий выходной сигнал. Рассмотрим принцип действия основных логических элементов:

Элемент И (AND)

Логический элемент И имеет два или более входа и один выход. Выходной сигнал равен логической 1 только в том случае, если на все входы подана логическая 1. В остальных случаях на выходе будет логический 0.

Элемент ИЛИ (OR)

Элемент ИЛИ также имеет несколько входов и один выход. Выходной сигнал равен логической 1, если хотя бы на один из входов подана логическая 1. Выход будет равен 0 только если на все входы подан логический 0.

Элемент НЕ (NOT)

Элемент НЕ или инвертор имеет один вход и один выход. Он инвертирует входной сигнал — если на входе 0, то на выходе 1 и наоборот.

Комбинированные логические элементы

На основе базовых логических элементов строятся более сложные комбинированные элементы:

- И-НЕ (NAND) — выполняет операцию И с последующей инверсией

- ИЛИ-НЕ (NOR) — выполняет операцию ИЛИ с инверсией результата

- Исключающее ИЛИ (XOR) — выход равен 1, если входы не равны

Комбинированные элементы позволяют реализовывать более сложные логические функции и упрощают построение цифровых схем.

Применение логических элементов в электронике

Логические элементы находят широкое применение в различных областях цифровой электроники:

- Процессоры и микроконтроллеры — основа вычислительных устройств

- Оперативная и постоянная память

- Шифраторы и дешифраторы

- Мультиплексоры и демультиплексоры

- Счетчики и регистры

- Цифро-аналоговые и аналого-цифровые преобразователи

Практически любое современное электронное устройство содержит в своем составе логические элементы в том или ином виде.

Типы логических микросхем

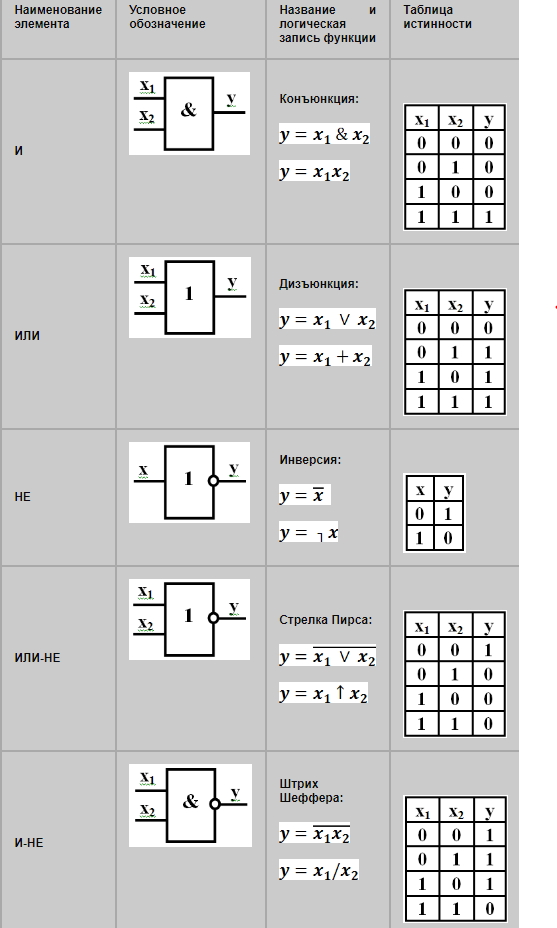

Логические элементы реализуются в виде интегральных микросхем. Существует несколько основных типов логики:

ТТЛ — транзисторно-транзисторная логика

ТТЛ-микросхемы строятся на биполярных транзисторах. Отличаются высоким быстродействием, но имеют относительно большое энергопотребление. Типичные представители — серии К155, К555.

КМОП — комплементарная металл-оксид-полупроводниковая логика

КМОП-микросхемы используют полевые МОП-транзисторы. Главное преимущество — крайне низкое энергопотребление в статическом режиме. Недостаток — меньшее быстродействие по сравнению с ТТЛ. Типичные серии — К561, К1564.

ЭСЛ — эмиттерно-связанная логика

ЭСЛ-микросхемы обеспечивают сверхвысокое быстродействие за счет работы транзисторов в линейном режиме. Недостаток — большое энергопотребление. Применяются в высокоскоростных системах. Пример — серия К500.

Особенности применения логических микросхем

При разработке цифровых устройств на логических микросхемах следует учитывать ряд важных моментов:

- Напряжение питания должно строго соответствовать типу логики

- Необходимо соблюдать правила согласования уровней при стыковке разных типов логики

- Неиспользуемые входы нужно подключать к определенному логическому уровню

- Следует учитывать нагрузочную способность выходов микросхем

- Важно обеспечивать качественную развязку по питанию

Соблюдение этих правил позволит создавать надежно работающие цифровые устройства на логических элементах.

Применение логических элементов в аналоговых схемах

Интересной особенностью логических элементов является возможность их использования для обработки аналоговых сигналов. Рассмотрим некоторые примеры:

Усилители на логических элементах

Логические элементы можно использовать в качестве простых усилителей аналоговых сигналов. Для этого элемент выводится в линейный режим с помощью отрицательной обратной связи. Коэффициент усиления при этом составляет 10-20 дБ.

Генераторы импульсов

На основе логических элементов легко реализуются различные генераторы прямоугольных импульсов. Частота генерации определяется внешней RC-цепью и может достигать нескольких мегагерц.

Компараторы напряжения

Логические элементы с положительной обратной связью работают как компараторы, преобразуя аналоговый сигнал в цифровой. Такие схемы часто используются в качестве пороговых устройств.

Применение логических элементов в аналоговых схемах позволяет создавать простые и дешевые устройства обработки сигналов.

Современные тенденции развития логических элементов

- Уменьшение размеров транзисторных структур до нанометровых масштабов

- Снижение напряжения питания и энергопотребления

- Увеличение степени интеграции элементов на кристалле

- Применение новых материалов (графен, углеродные нанотрубки и др.)

- Разработка квантовых логических элементов

Эти технологии позволяют создавать все более быстродействующие и энергоэффективные цифровые устройства.

Заключение

Логические элементы являются фундаментальными «кирпичиками» современной цифровой электроники. Понимание принципов их работы и особенностей применения необходимо для успешного проектирования электронных устройств. Несмотря на кажущуюся простоту, логические элементы обладают огромным потенциалом и продолжают активно развиваться, открывая новые возможности в области вычислительной техники и обработки информации.

Цифровые микросхемы. Логический элемент НЕ (INV)

Всем доброго времени суток! Как дом строят из кирпичей, так и цифровые устройства состоят из простых элементов – цифровых микросхем. Наиболее простые из них – логические элементы (или вентили, gates). В одной микросхеме может содержаться только строго определённое количество логических элементов, их может быть или 1, или 2, или 3, или 4, или 8 в одной микросхеме. Соответственно каждый логический элемент может иметь от 1 до 12 входов и 1 выход. При этом связь между входами и выходом соответствует таблице истинности. Логические элементы относятся к так называемым комбинационным микросхемам, и у них отсутствует какая-либо внутренняя память.

Достоинством логических вентилей является высокое быстродействие и небольшая потребляемая мощность, но на их основе довольно трудно реализовать сложную функциональность, поэтому чаще всего они используются в качестве дополнения к более сложным цифровым микросхемам или микроконтроллерам.

Логический элемент НЕ (Hex Inverters)

Начнём с наиболее простого из логических элементов – логического элемента НЕ (INV) или как его ещё называют инвертора. Как понятно из названия инвертор применяется для инвертирования, то есть изменения уровня сигнала (например, на вход поступает логическая «1», а на выходе получаем логический «0»). Как самый простой из логических элементов инвертор содержит всего один вход и один выход. Инверторы могут быть с тремя типами выходов: 2С, ОК или с Z – состоянием. Как указывалось в этой статье логический элемент НЕ имеет следующую таблицу истинности:

Таблица истинности логического элемента НЕ

На принципиальных схемах логические элементы НЕ (инверторы) имеют следующее обозначение

Обозначения логических элементов НЕ (Hex Inverters): ANSI (слева) и DIN (справа).

Микросхемы инверторов содержат обычно шесть логических элементов НЕ (INV) и обозначаются префиксом ЛН (например, К155ЛН1, К561ЛН2). Как говорилось ранее, для ТТЛ микросхем с выходом ОК необходим выходной нагрузочный резистор (pull-up). Величина которого рассчитывается очень просто: R > U/IOL, где U – напряжение источника питания, к которому подключается резистор.

Применение инверторов

Обычно, элементы НЕ применяются для преобразования уровней сигнала (из высокого в низкий или из низкого в высокий уровень). Второе предназначение – увеличения нагрузочной способности (буферизации) с инвертирование выходов более сложных микросхем. Например, когда сигнал с выхода микросхемы необходимо подать на несколько других, а выходной ток недостаточен.

Но существует и несколько нестандартных применений инверторов: построение генераторов и в случае, когда необходимо создать задержку сигнала.

Схема генератора на логических элементах НЕ

Схемы генераторов представляют собой обыкновенные RC-генераторы, но характеристики можно рассчитать только приблизительно, так как она зависит от напряжения питания и типа применённой микросхемы. Частота генератора будет равна

[math]f \approx \frac{1}{2RC}[/math]Генераторы данного типа можно применять там, где не важна стабильность частоты, а важен лишь факт генерации импульсов. Более стабильные по частоте генераторы получаются, если вместо конденсатора применить кварцевый резонатор.

Схема кварцевого генератора на логических элементах НЕ

Довольно часто в цифровых схемах необходимо получит некоторую задержку сигнала, в этом случае инверторы могут пригодиться, на большую задержку рассчитывать не приходится (примерно до 100 нс). Для получения задержки сигнала инверторы соединяют последовательно.

Схема для создания задержки сигнала на инверторах

Величину задержки можно рассчитать приблизительно по сумме задержек входного и выходного сигналов (tPLH и tPHL) для данной микросхемы. Например, для четырёх инверторов величину задержки можно оценить по формуле

[math]t_{З} = 2t_{PLH} + 2t_{PHL}[/math]но необходимо учитывать, что значения реальных задержек сильно отличаются от тех что даны в справочнике (в справочнике даны максимальные величины, а реальные могут обличаться более, чем в 2 раза).

Более значительные величины задержки сигнала можно получить, используя интегрирующие RC-цепи, но и здесь нельзя точно говорить о величине задержки, потому что разные типы цифровых микросхем срабатывают при разном уровне сигнала и разных напряжениях питания.

Схема для создания задержки сигнала c интегрирующей цепью

Ниже приведена таблица некоторых семейств микросхем, которые имеют в своём составе инверторы

| Серия | Номер микросхемы | |||||||

| ЛН1 | ЛН2 | ЛН3 | ЛН5 | ЛН6 | ЛН7 | ЛН8 | ЛН10 | |

| К155 | 6НЕ | 6НЕ(ОК) | 6НЕ(ОК) | 6НЕ(ОК) | 6НЕ(Z) | 6НЕ(Z) | — | — |

| К555 | 6НЕ | 6НЕ(ОК) | — | — | — | 6НЕ(Z) | — | — |

| КР1533 | 6НЕ | 6НЕ(ОК) | — | — | — | 6НЕ(Z) | 6НЕ | 6НЕ(ОК) |

| К561 | 6НЕ(Z) | 6НЕ | 6НЕ(Z) | — | — | — | — | — |

| КР1554 | 6НЕ | — | — | — | — | — | — | — |

| КР1564 | 6НЕ | — | — | — | — | 6НЕ(Z) | — | — |

Теория это хорошо, но без практического применения это просто слова.Здесь можно всё сделать своими руками.

www.electronicsblog.ru

Микросхема 74266

74266

Описание

Описание

Микросхема 74266 содержит четыре отдельных логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ с двумя входами каждый. Выходы имеют открытый коллектор.

Работа схемы

Работа схемы

Все четыре логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ микросхемы 74266 можно использовать независимо друг от друга.

Когда сигнал высокого уровня присутствует только на одном из входов микросхемы 74266, на выходе логического элемента формируется напряжение низкого уровня. Если же на оба входа подается напряжение высокого или низкого уровня, то на выходе формируется напряжение высокого уровня.

Логический элемент микросхемы 74266 можно использовать в качестве цифрового компаратора, в котором на выходе устанавливается напряжение высокого уровня при поступлении на входы сигналов одного и того же логического уровня. Если же на входы приходят сигналы разных логических уровней, то на выходе создается напряжение низкого уровня. Логический элемент может также работать как управляемый инвертор, поскольку напряжение высокого уровня на входе позволяет всегда передавать сигнал, подаваемый на второй вход, без изменения. И наоборот, напряжение низкого уровня на одном входе позволяет передавать на выход инвертированное значение напряжения со второго входа.

Выходы с открытым коллектором микросхемы 74266 дают возможность использовать микросхему в качестве 4-разрядного компаратора.

Применение

Применение

Реализация логической операции ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, формирование и проверка на чётность-нечётность; сумматор/вычитатель, логические компараторы. Производится следующая номенклатура микросхем: 74LS266.

| Тип микросхемы | 74LS266 |

|---|---|

| Максимальное выходное напряжение, В | 5,5 |

| Время задержки прохождения сигнала, нс | 18 |

| Ток потребления, мА | 8 |

| Входы | Выход | |

|---|---|---|

| A | B | Y |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

www.microshemca.ru

Применение цифровых микросхем | HomeElectronics

Всем доброго времени суток! В предыдущих постах я рассказывал о логических элементах – «кирпичиках» слагающих фундамент цифровой техники и об их назначениях. В этом посте я расскажу более подробно о применении цифровых микросхем содержащих логические элементы.

Простейшие схемы

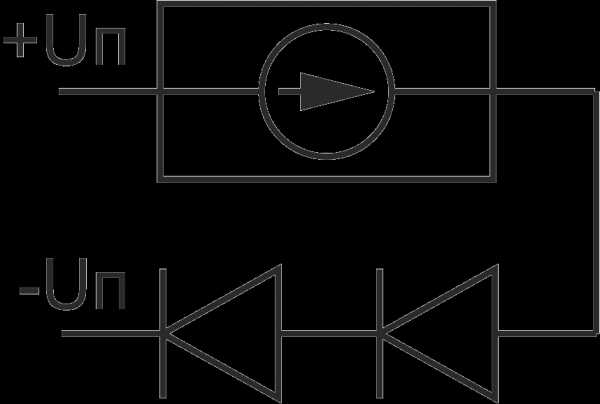

Первая схема представляет собой простейший пробник для прозвонки электрических цепей. С помощью данного пробника можно определить надёжность электрического контакта, найти обрыв в цепи, проверить исправность резисторов и полупроводниковых диодов и транзисторов.

Схема пробника для прозвонки электрической цепи.

Опишем его работу. При разомкнутых щупах ХТ на входах логического элемента DD1 относительно общего провода устанавливается высокий логический уровень напряжения. Соответственно на выходе элемента DD1 будет низкий логический уровень, при этом светодиод VD1 не будет гореть. Если щупы замкнуть между собой, то на входе DD1 будет низкий логический уровень, а на выходе – высокий. Светящийся диод сообщит о том, что выходы замкнуты между собой. Таким образом, при подключении щупов к исправной цепи будет загораться светодиод, а если светодиод не горит – значит, в цепи имеется обрыв.

Следующая схема, представленная ниже, представляет собой логический пробник. Предназначенный он для определения логического уровня напряжения в электрических цепях цифровых устройств.

Схема логического пробника.

В исходном состоянии на входах логического элемента DD1 и выходе DD2 устанавливается высокий логический уровень, соответственно светодиод VD1 горит. При включении светодиодов в цепь с высоким логическим уровнем светодиод VD1 продолжает гореть, а когда на входе DD1 появится низкий логический уровень, то светодиод VD1 соответственно погаснет.

Дальнейшее повествование о применении цифровых микросхем не возможно без знания внутреннего устройства цифровых ТТЛ и КМОП микросхем и их передаточных характеристиках.

Внутреннее устройство цифровых микросхем ТТЛ

Все семейства цифровых микросхем, основываются на базовых логических элементах

Схема базового элемента ТТЛ 2И-НЕ и его переходная характеристика.

На входе элемента стоит многоэмиттерный транзистор VT1, затем усилительный каскад на транзисторе VT2 и двухтактный выходной каскада на транзисторах VT3, VT4.

Опишем работу логического элемента 2И-НЕ. В исходном состоянии входное напряжение не превышает 0,5 В, а эмиттерный переход транзистора VT1 открыт, данного напряжения не достаточно для перевода коллекторного перехода в открытое состояние, то же относится и к эмиттерным переходам транзисторов VT2, VT4. Поэтому данные транзисторы закрыты, а транзистор VT3 – открыт, напряжением, поступающим с R2. Диод VD3 оказывается открытым и на выходе элемента напряжение составляет примерно 3…4 В (точка А). Когда начинается увеличиваться напряжение на эмиттерах VT1, то транзистор VT2 начинает открываться, а транзистор VT3 плавно закрываться (участок А – Б). Дальнейшее увеличение напряжения на входном транзисторе приводит к тому, что транзистор VT2 ещё больше открывается, напряжение на R3 тоже возрастает и открывается транзистор VT4. В результате, эмиттерный переход транзистора VT4 шунтирует резистор R3, и транзистор VT2 резко открывается, а напряжение на выходе элемента уменьшается. В этот момент (участок Б – В) все транзисторы открыты и находятся в активном режиме. Если продолжать увеличивать входное напряжение, то транзисторы VT2 и VT4 перейдут в режим насыщения (участок В – Г), а транзистор VT3 закроется и значение выходного напряжения станет равным напряжению насыщения транзистора VT4, а ток будет ограничен резистором R4.

Участок Б – В переходной характеристики можно использовать для обработки аналоговых сигналов, в данном режиме переходная характеристика обладает высокой линейностью и максимальной потребляемой мощностью.

Внутреннее устройство цифровых микросхем КМОП

Так же как и в ТТЛ семействе, КМОП микросхемах базовым элементом является 2И-НЕ, внутреннее устройство которого показано ниже

Схема базового элемента КМОП 2И-НЕ и его переходная характеристика.

В данном логическом элементе работают комплементарные полевые транзисторы. Транзисторы с каналом р-типа (VT1, VT2) подключены к положительному проводнику источника питания, с каналом n-типа (VT3, VT4) соединены последовательно.

При входном напряжении 2 В и менее транзисторы VT1 и VT2 открыты, так как напряжение на участках затвор – исток (при напряжении питания 9 В) составляет не менее 7 В. Напряжение на таких же участках транзисторов VT3 и VT4 оказывается недостаточным для их открывания, поэтому на выходе элемента будет напряжение, почти равное напряжению питания, то есть около 9 В (точка А). По мере увеличения входного напряжения транзисторы начинают открываться, а VT1 и VT2 закрываться. На участке А – Б этот процесс происходит сравнительно плавно, а на участке Б – В он ускоряется и наиболее линеен. В точке В транзисторы VT1 и VT2 почти полностью закрыты, а VT3 и VT4 открыты. Выходное напряжение в этом случае невелико и при дальнейшем увеличении входного напряжения до уровня источника питания оно стремиться к нулю (точка Г).

Логический элемент в линейном режиме

Использование логических элементов цифровых микросхем для работы с аналоговыми сигналами возможно лишь в случае, если их режим выведен в линейный или близкий к нему. Так в линейном режиме ТТЛ элемент эквивалентен усилителю к коэффициентом усиления 10 … 15 (примерно 20 дБ), а элемент КМОП – усилителю с коэффициентом усиления 10 … 20 (20 … 26 дБ).

Вывод логического элемента в линейный режим: слева-направо током, напряжением, обратной связью.

Для вывода логического элемента на линейный участок применяют различные способы. Один из них основан на включении на входе элемента ТТЛ резистора R. Этот резистор вызовет ток, который будет протекать через эмиттерный переход входного транзистора элемента ТТЛ. Изменяя сопротивление внешнего резистора, можно изменять напряжение на выходе элемента, то есть изменять положение его рабочей точки на передаточной характеристике. Для элементов ТТЛ сопротивление такого внешнего резистора составляет от 1 кОм до 3 кОм. Однако такой способ не применим для КМОП микросхем, так как они работают без выходных токов (есть токи утечки, но они малы и нестабильны).

Второй способ вывода логического элемента на рабочий режим может быть подача на вход соответствующего напряжения, например с помощью резистивного делителя. Так, для элементов ТТЛ середина линейного участка передаточной характеристики соответствует входное напряжение 1,5…1,8 В, а для КМОП 3…6 В (при напряжении питания 9 В). Для разных логических элементов это напряжение не одинаково, поэтому его подбирают опытным путём. Номиналы входных резисторов выбирают таким образом, что бы входные токи элементов не влияли на напряжение, снимаемое с резистивного делителя.

Третий способ, является наиболее эффективным, для этого создают отрицательную обратную связь (ООС) по постоянному току между входом и выходом элемента, благодаря чему рабочая точка автоматически поддерживается на требуемом участке передаточной характеристики и не требуется тщательного подбора внешних резисторов. Этот способ реализуется для логических элементов с инверсией входного сигнала: НЕ, И-НЕ, ИЛИ-НЕ.

Сопротивление резистора в цепи ООС выбирают исходя из обеспечения элементу необходимого входного тока. Для элементов КМОП оно составляет от нескольких килоом до десятков мегаом, а для ТТЛ – от десятков Ом до 1 кОм. Но применение ООС снижает коэффициент усиления элемента.

Усилители на логических элементах

Для использования логических элементов в качестве усилителей сигналов необходимо вывести рабочую точку на линейный участок передаточной характеристики. Основные характеристики таких усилителей приведены в таблице ниже.

| Серия | Схема вывода в линейный режим | КУС, дБ | Fmax, МГц | Рпотр мВт | Uвых, В | Rвх, кОм | Rвых, кОм | R1, кОм | R2, кОм |

| К155 | OOC | 18 | 40 | 20 | 1,2 | 0,6 | 0,05 | 0,68 | 0,68 |

| Ток | 21 | 0,8 | 1,9 | — | |||||

| К176 | ООС | 25 | 5,5 | 5 … 20 | 1,5 | 0,4 | 0,05 | 7,5 | 5,1 |

| Ток | 17 | 3 … 4 | 5,0 | 3,5 | 6 | 6,2 | 4 | ||

| 561 | OOC | 25 | 1000 | 7 | 1000 | 1000 |

Схема простейшего усилителя на элементе ТТЛ приведена ниже. Регулировка усилителя сводится к установке подстроечным резистором R1рабочей точки элемента на середине линейного участка передаточной характеристики.

Простейший усилитель на ТТЛ элементе

Недостатком простых усилителей является невысокое входное сопротивление, что ограничивает область их применения. К тому же коэффициент усиления небольшой. Устраняется данный недостаток использованием совместно с транзисторами. Коэффициент усиления повышается включением последовательно нескольких каскадов. Кроме того, цифровая микросхема содержит несколько идентичных элементов, это позволяет создавать многоканальные усилители. Примером может служить схема показанная ниже. Основные характеристики усилителя: коэффициент усиления – 50; выходное сопротивление 50 Ом, входное сопротивление 5 кОм, верхняя граничная частота 40 МГц.

Схема усилителя с транзистором на входе

Элементы КМОП также можно использовать для усилителей, схема одного из ни приведена ниже. Общий недостаток усилителей на элементах КМОП – высокое выходное сопротивление. Устранить его можно установкой на выходе логического элемента эмиттерного повторителя на транзисторе и включения его в цепь ООС.

Схемы усилителей на элементах КМОП.

Пороговые устройства на логических элементах

Пороговые устройства, называемые компараторами, предназначены для преобразования аналогового сигнала в цифровую информацию. Простейшим пороговым устройством является триггер Шмитта, который описан в этом посте. Кроме формирования импульсов и восстановлении цифровых сигналов, пороговые устройства применяют в аналогово – цифровых преобразователях, генераторах импульсов различной формы.

Схема порогового устройстван на логических элементах.

По большёму счёту логический элемент является сам пороговым устройствам, однако его передаточная характеристика не совсем линейна. Для повышения линейности передаточной характеристики логического элемента, его необходимо охватить положительной обратной связью (ПОС) по постоянному току через резистор R2. В таком случае он превращается в своеобразный триггер Шмитта с возможностью регулирования пороговых напряжений. Ширина петли гистерезиса (разность между пороговыми напряжениями) зависит от соотношения номиналов резисторов R1 и R2. От этих же резисторов зависит и чувствительность. При увеличении R2 и уменьшении R1 чувствительность повышается, а ширина петли гистерезиса уменьшается. Для микросхем ТТЛ сопротивление R1 = 0,1 … 2 кОм, а R2 = 2 … 10 кОм. Пороговые устройства на КМОП элементах отличаются высокой экономичностью, а недостатком является низкая чувствительность. Для КМОП микросхем R1 – несколько десятков килоом, а R2 – несколько сотен килоом.

Генераторы на логических элементах

Цифровые микросхемы нашли широкое применение в схемах различных генераторов с частотами от долей герца до десятков мегагерц и самой различной формой импульса. Вообще генераторы представляют собой усилительный каскад или несколько, который охвачен частотно-зависимой обратной связью. В качестве таких цепей используют RC-, LC-, RLC-цепи, а также пьезокерамические и кварцевые резонаторы.

Ниже показана схема генератора с RC частотно-зависимой цепью. Работа данного генератора связана с процессами зарядки-разрядки конденсатора С1 через резистор R1.

Схема RC-генератора

В данной схеме генератора через резистор R1 осуществляется ООС, которая выводит логический элемент в линейный режим, а через конденсатор С1 осуществляется частотно-зависимая ПОС. В таком генераторе используются как ТТЛ-элементы, так и КМОП. Сопротивление резистора R1 выбирается также как и для усилительного каскада с ООС, а емкость конденсатора – в зависимости от требуемой частоты колебаний. Частоту генерации можно определить по приближенной формуле

[math]F \approx \frac{0,7}{RC}[/math]При работе такой генератор вырабатывает прямоугольные импульсы со скважностью примерно равной 2. Максимальная частота генерации ограниченна величиной задержки переключения логических элементов, так для КМОП микросхем максимальная частота составляет 2 … 4 МГц, а для ТТЛ – несколько десятков МГц.

С помощью цифровых микросхем можно также получить генератор синусоидального сигнала, для этого в качестве частотно-задающей цепи необходимо использовать LC-контур. Схема такого генератора приведена ниже.

Схема LC-генератора

В качестве частотно-зависимой связи применяются как последовательный так и параллельный колебательный контур, но в любом случае частота колебаний будет соответствовать формуле Томпсона

[math]F=\frac{1}{2 \pi \sqrt{LC}}[/math]

Сопротивление резистора R1 выбирается также как и для усилительного каскада.

Недостатком вышеописанных генераторов является невысокая стабильность генерируемой частоты. Для её повышения применяются пьезокерамические и кварцевые резонаторы, включая их в цепи обратной связи вместо конденсатора или колебательного контура.

www.electronicsblog.ru

Цифровые микросхемы. Типы логики, корпуса

РадиоКот >Обучалка >Цифровая техника >Основы цифровой техники >Цифровые микросхемы. Типы логики, корпуса

Ну сначала скажем так: микросхемы делятся на два больших вида: аналоговые и цифровые. Аналоговые микросхемы работают с аналоговым сигналом, а цифровые, соответственно – с цифровым. Мы будем говорить именно о цифровых микросхемах.

Точнее даже, мы будем говорить не о микросхемах, а об элементах цифровой техники, которые могут быть «спрятаны» внутри микросхемы.

Что это за элементы?

Некоторые названия вы слышали, некоторые, может быть – нет. Но поверьте, эти названия можно произносить вслух в любом культурном обществе – это абсолютно приличные слова. Итак, примерный список того, что мы будем изучать:

- Триггеры

- Счетчики

- Шифраторы

- Дешифраторы

- Мультиплексоры

- Компараторы

- ОЗУ

- ПЗУ

Все цифровые микросхемы работают с цифровыми сигналами. Что это такое?

Цифровые сигналы – это сигналы, имеющие два стабильных уровня – уровень логического нуля и уровень логической единицы. У микросхем, выполненных по различным технологиям, логические уровни могут отличаться друг от друга.

В настоящее время наиболее широко распространены две технологии: ТТЛ и КМОП.

ТТЛ – Транзисторно-Транзисторная Логика;

КМОП – Комплиментарный Металл-Оксид-Полупроводник.

У ТТЛ уровень нуля равен 0,4 В, уровень единицы – 2,4 В.

У логики КМОП, уровень нуля очень близок к нулю вольт, уровень единицы – примерно равен напряжению питания.

По-всякому, единица – когда напряжение высокое, ноль – когда низкое.

НО! Нулевое напряжение на выходе микросхемы не означает, что вывод «болтается в воздухе». На самом деле, он просто подключен к общему проводу. Поэтому нельзя соединять непосредственно несколько логических выводов: если на них будут различные уровни – произойдет КЗ.

Кроме различий в уровнях сигнала, типы логики различаются также по энергопотреблению, по скорости (предельной частоте), нагрузочной способности, и т.д.

Тип логики можно узнать по названию микросхемы. Точнее – по первым буквам названия, которые указывают, к какой серии принадлежит микросхема. Внутри любой серии могут быть микросхемы, произведенные только по какой-то одной технологии. Чтобы вам было легче ориентироваться — вот небольшая сводная таблица:

| ТТЛ | ТТЛШ | КМОП | Бастродейств. КМОП | ЭСЛ | |

| Расшифровка названия | Транзисторно-Транзисторная Логика | ТТЛ с диодом Шоттки | Комплиментарный Металл-Оксид Полупроводник | Эмиттерно-Согласованная Логика | |

| Основные серии отеч. микросхем | К155 К131 |

К555 К531 КР1533 |

К561 К176 |

КР1554 КР1564 |

К500 КР1500 |

| Серии буржуйских микросхем | 74 | 74LS 74ALS |

CD40 H 4000 |

74AC 74 HC |

MC10 F100 |

| Задержка распространения, нС | 10…30 | 4…20 | 15…50 | 3,5..5 | 0,5…2 |

| Макс. частота, МГц | 15 | 50..70 | 1…5 | 50…150 | 300…500 |

| Напряжение питания, В | 5 ±0,5 | 5 ±0,5 | 3…15 | 2…6 | -5,2 ±0,5 |

| Потребляемый ток (без нагрузки), мА | 20 | 4…40 | 0,002…0,1 | 0,002…0,1 | 0,4 |

| Уровень лог.0, В | 0,4 | 0,5 | < 0,1 | < 0,1 | -1,65 |

| Уровень лог. 1, В | 2,4 | 2,7 | ~ U пит | ~ U пит | -0,96 |

| Макс. выходной ток, мА | 16 | 20 | 0,5 | 75 | 40 |

Наиболее распространены на сегодняшний день следующие серии (и их импортные аналоги):

- ТТЛШ – К555, К1533

- КМОП – КР561, КР1554, КР1564

- ЭСЛ – К1500

Цифровые схемы рекомендуется строить, используя микросхемы только одного типа логики. Это связано именно с различиями в логических уровнях цифровых сигналов.

Тип логики выбирают, в основном, исходя из следующих соображений:

— скорость (рабочая частота)

— энергопотребление

— стоимость

Но бывают такие ситуации, что одним типом никак не обойтись. Например, один блок должен иметь низкое энергопотребление, а другой – высокую скорость. Низким потреблением обладают микросхемы технологии КМОП. Высокая скорость – у ЭСЛ.

В этом случае понадобятся ставить преобразователи уровней.

Правда, некоторые типы нормально стыкуются и без преобразователей. Например, сигнал с выхода КМОП-микросхемы можно подать на вход микросхемы ТТЛ (при учете, что их напряжения питания одинаковы). Однако, в обратную сторону, т.е., от ТТЛ к КМОП пускать сигнал не рекомендуется.

Микросхемы выпускаются в различных корпусах. Наиболее распространены следующие виды корпусов:

DIP

(Dual Inline Package )

Обычный «тараканчик». Ножки просовываем в дырки на плате – и запаиваем.

Ножек в корпусе может быть 8, 14, 16, 20, 24, 28, 32, 40, 48 или 56.

Расстояние между выводами (шаг) – 2,5 мм (отечественный стандарт) или 2,54 мм (у буржуев).

Ширина выводов около 0,5 мм

Нумерация выводов – на рисунке (вид сверху). Чтобы определить нахождение первой ножки, нужно найти на корпусе «ключик».

SOIC

(Small Outline Integral Circuit)

Планарная микросхема – то есть ножки припаиваются с той же стороны платы, где находится корпус. При этом, микросхема лежит брюхом на плате.

Количество ножек и их нумерация – такие же как у DIP .

Шаг выводов – 1,25 мм (отечественный) или 1,27 мм (буржуазный).

Ширина выводов – 0,33…0,51

PLCC

(Plastic J-leaded Chip Carrier)

Квадратный (реже — прямоугольный) корпус. Ножки расположены по всем четырем сторонам, и имеют J -образную форму (концы ножек загнуты под брюшко).

Микросхемы либо запаиваются непосредственно на плату (планарно), либо вставляются в панельку. Последнее – предпочтительней.

Количество ножек – 20, 28, 32, 44, 52, 68, 84.

Шаг ножек – 1,27 мм

Ширина выводов – 0,66…0,82

Нумерация выводов – первая ножка возле ключа, увеличение номера против часовой стрелки:

TQFP

(Thin Quad Flat Package)

Нечто среднее между SOIC и PLCC .

Квадратный корпус толщиной около 1мм, выводы расположены по всем сторонам.

Количество ножек – от 32 до 144.

Шаг – 0,8 мм

Ширина вывода – 0,3…0,45 мм

Нумерация – от скошенного угла (верхний левый) против часовой стрелки.

Вот так, в общих чертах, обстоят дела с корпусами. Надеюсь теперь вам станет немножко легче ориентироваться в бесчисленном множестве современных микросхем, и вас не будет вгонять в ступор фраза продавца типа: «эта микросхема есть только в корпусе пэ эл си си»…

<<—Вспомним пройденное—-Поехали дальше—>>

Как вам эта статья? | Заработало ли это устройство у вас? |

www.radiokot.ru

Логический элемент Исключающее ИЛИ | HomeElectronics

Всем доброго времени суток! Сегодня мы рассмотрим последние два элемента, которые выполняют простейшие логические функции. Такими элементами являются Исключающее ИЛИ (Exclusive-OR, XOR) и Исключающее ИЛИ-НЕ (None Exclusive-OR, NXOR). Предыдущие статьи смотрите здесь, здесь, здесь и здесь.

Логический элемент Исключающее ИЛИ, как и ранее рассмотренные логические элементы имеет несколько равноправных входов и один выход, но не один из входных выводов не может заблокировать другие входы, установив выходной сигнал к уровню единицы или нуля. Исходя из сказанного, можно установить логику работы элемента Исключающее ИЛИ: высокий логический уровень на выходе появляется только тогда, когда только на одном из входов есть высокий уровень, а если на всех входах одновременно присутствуют сигналы логического нуля или логической единицы, то на выходе буде низкий уровень напряжения. Так же как и все остальные логические элементы элемент Исключающее ИЛИ может иметь инверсию на выходе, такой элемент называют Исключающее ИЛИ-НЕ. Логика работы такого элемента следующая: высокий уровень на выходе логического элемента Исключающее ИЛИ-НЕ появиться только в том случае, когда на всех входах одновременно присутствует сигналы лог. 0 или лог. 1. Таким образом таблица истинности логических элементов Исключающее ИЛИ и Исключающее ИЛИ-НЕ будет иметь следующий вид:

| Входные выводы | Тип логического элемента | ||

| 1 | 2 | Исключающее ИЛИ | Исключающее ИЛИ-НЕ |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Элементы Исключающее ИЛИ из-за своего специфического функционала не имеют широкого применения, поэтому отдельных суффиксов в их обозначении не присутствует, они в основном входят в серию ЛП (например, К555ЛП5, КР1533ЛП12, К561ЛП2), в составе которой микросхемы с различным функционалом. Логические элементы Исключающее ИЛИ имеют своё графическое обозначение, которое приведено ниже.

Условное графическое обозначение элементов Исключающее ИЛИ: DIN (слева) и ANSI (справа).

Применение элемента Исключающее ИЛИ

С точки зрения математики, элемент Исключающее ИЛИ выполняет операцию суммирования по модулю 2. Поэтому эти элементы иногда называют сумматорами по модулю два. Основное предназначение элементов Исключающее ИЛИ состоит в сравнении двух входных сигналов (когда на входы приходят два высоких или два низких логических уровня на выходе формируется лог. 0), очень часто данный элемент применяют для формирования задержки сигнала или формирования коротких импульсов.

Управляемый инвертор

Важное применение элементов Исключающее ИЛИ – управляемый инвертор. Опишем его работу. Один из входов используется как управляющий, а на другой поступает сигнал. Если на управляющем входе высокий логический уровень, то сигнал инвертируется, а если низкий, то не инвертируется. Чаще всего управляющий сигнал задаётся постоянным уровнем, определяя режим работы элемента, а информационный сигнал является импульсным. То есть элемент Исключающее ИЛИ может изменять полярность входного сигнала или фронта, а может и не изменять в зависимости от управляющего сигнала.

Элемент Исключающее ИЛИ в качестве управляемого инвертора.

Смешивание сигналов

В случае, когда имеется два сигнала и исключается их одновременный приход на элемент Исключающее ИЛИ, то он может быть использован для смешивания сигналов. Такое применение данного элемента может быть использовано в тех случаюх, когда остаются неиспользованными некоторые элементы Исключающее ИЛИ.

Применение элемента Исключающее ИЛИ для смешивания двух неодновременных сигналов.

Формирование коротких импульсов

Второе важное применение данного элемента – выделение фронта и среза входного импульса, которое традиционно делали с помощью дифференцирующего RC-звена, с последующим усилением и формированием сигнала. Микросхема с элементами Исключающее ИЛИ упрощает данную задачу.

Выделения фронта и среза импульса.

Ниже представлена схема для выделения среза и фронта входящего импульса. Входной сигнал задерживается цепочкой элементов, а затем исходный сигнал и его задержаная копия поступают на входы элемента Исключающее ИЛИ. В результате такого преобразования можно говорить об удвоении частоты входного сигнала, так как выходные импульсы следуют вдвое чаще, чем входные.

Схема реализующая выделение фронта и среза импульса.

Теория это хорошо, но без практического применения это просто слова.Здесь можно всё сделать своими руками.

www.electronicsblog.ru

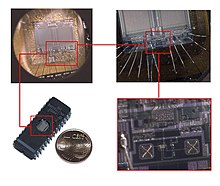

Микросхема Википедия

Запрос «БИС» перенаправляется сюда; см. также другие значения.

Интегра́льная (микро)схе́ма (ИС, ИМС, IC (англ.)), микросхе́ма, м/сх, чип (англ. chip «тонкая пластинка»: первоначально термин относился к пластинке кристалла микросхемы) — микроэлектронное устройство — электронная схема произвольной сложности (кристалл), изготовленная на полупроводниковой подложке (пластине или плёнке) и помещённая в неразборный корпус или без такового, в случае вхождения в состав микросборки[1].

Бо́льшая часть микросхем изготавливается в корпусах для поверхностного монтажа.

Часто под интегральной схемой (ИС) понимают собственно кристалл или плёнку с электронной схемой, а под микросхемой (МС) — ИС, заключённую в корпус. В то же время выражение чип-компоненты означает «компоненты для поверхностного монтажа» (в отличие от компонентов для пайки в отверстия на плате).

Содержание

- 1 История

- 2 Уровни проектирования

- 3 Классификация

- 3.1 Степень интеграции

- 3.2 Технология изготовления

- 3.3 Вид обрабатываемого сигнала

- 4 Технологии изготовления

- 4.1 Типы логики

- 4.2 Технологический процесс

- 4.3 Контроль качества

- 5 Назначение

- 5.1 Аналоговые схемы

- 5.1.1 Производство

- 5.2 Цифровые схемы

- 5.3 Аналого-цифровые схемы

- 5.1 Аналоговые схемы

- 6 Серии микросхем

- 6.1 Корпуса

- 6.2 Специфические названия

- 7

ru-wiki.ru

Первая микросхема 🙂 / Habr

Очень рад в подробностях рассказать о своей первой интегральной схеме и поделиться перипетиями этого проекта, которым занимался на протяжении прошлого года. Надеюсь, мой успех вдохновит других и поможет начать революцию в производстве домашних микросхем. Когда я приступил к этому проекту, то понятия не имел, во что ввязался, но в итоге узнал больше, чем когда-либо думал, о физике, химии, оптике, электронике и многих других областях.

Кроме того, мои усилия сопровождались лишь самыми положительными отзывами и поддержкой со всего мира. Искренне благодарен всем, кто мне помогал, давал советы и вдохновлял на этот проект. Особенно моим удивительным родителям, которые не только всегда поддерживают и поощряют меня как только могут, но и предоставили рабочее место и смирились с затратами на электроэнергию… Спасибо!

Без дальнейших церемоний представляю первую интегральную схему (ИС), изготовленную литографическим способом в домашних (гаражных) условиях — PMOS-чип двойного дифференциального усилителя Z1.

Я говорю «изготовленную литографическим способом», потому что Джери Эллсуорт изготовила первые транзисторы и логические вентили (с соединениями, тщательно проложенными вручную проводящей эпоксидной смолой) и показала миру, что это возможно. Вдохновленный её работой, я представляю интегральные схемы, созданные масштабируемым, стандартным фотолитографическим процессом. Излишне говорить, что это логический шаг вперёд по сравнению с моим предыдущей работой, где я воспроизвёл полевой транзистор Джери.

Я разработал усилитель Z1, когда искал простой чип для тестирования и настройки своего процесса. Макет сделан в Magic VLSI для процесса PMOS с четырьмя масками (активная/легированная область, подзатворный оксид, контактное окно и верхний металлический слой). У PMOS есть преимущество перед NMOS, если учесть ионные примеси из-за изготовления в гараже. Маски разработаны с соотношением сторон 16:9 для упрощения проекции.

Макет Magic VLSI

Генерация маски

Активная область

Затвор

Контакт

Металл

Размер затвора приблизительно 175 мкм, хотя на чипе для проверки выполнены элементы размером до 2 мкм. Каждая секция усилителя (центральная и правая) содержит три транзистора (два для двухтактной схемы с общим катодным сопротивлением и один в качестве источника тока/нагрузочного резистора), что означает в общей сложности шесть транзисторов на ИС. В левой части резисторы, конденсаторы, диоды и другие тестовые элементы, чтобы изучить характеристики техпроцесса. Каждый узел дифференциальных пар выходит отдельным штифтом на выводной рамке, поэтому его можно изучать, а при необходимости добавить внешнее смещение.

Процесс изготовления состоит из 66 отдельных шагов и занимает примерно 12 часов. Выход достигает 80% для больших элементов, но сильно зависит от количества выпитого кофе в конкретный день. Я также записал видео на YouTube о теории производства микросхем и отдельно об изготовлении МОП-транзисторов.

Кремниевые пластины 50 мм (2″) разбиваются на кристаллы 5,08×3,175 мм (площадь около 16 мм²) волоконным лазером Epilog. Такой размер кристалла выбран, чтобы он помещался в 24-контактный DIP-корпус Kyocera.

Пластина N-типа 50 мм

Пластина N-типа 50 мм

Сначала с пластины снимается нативная окись быстрым погружением в разбавленный фтороводород с последующей интенсивной обработкой травильной смесью «пиранья» (смесь серной кислоты и перекиси водорода), смесью RCA 1 (вода, аммиак, перекись водорода), смесью RCA 2 (вода, соляная кислота, перекись водорода) и повторным погружением во фтороводород.

Защитный окисел термически выращивается в водяном паре окружающего воздуха (влажное оксидирование) до толщины 5000−8000 Å.

Влажное термическое оксидирование

Влажное термическое оксидирование

Трубчатая печь

Оксидированная пластина

Оксидированная пластина готова к формированию рисунка на активной/легированной (Р-типа) области. Фоторезист AZ4210 наносится на вращающуюся примерно на 3000 оборотах в минуту подолжку, формируя плёнку толщиной около 3,5 мкм, которая аккуратно подсушивается при 90°С на электроплитке.

Процесс литографии детально

Маску активной зоны обрабатывает мой фотолитографический степпер Mark IV в ультрафиолете с шагом 365 нм — и структура отрабатывается в растворе гидроксида калия.

Структура резиста

Структура резиста

30-минутная подсушка

Травление активной зоны

После этого структура резиста плотно затвердела и применяется несколько других трюков, чтобы обеспечить хорошее сцепление и химическую стойкость во время следующего вытравливания во фтороводороде, который переносит эту структуру на слой подзатворного оксида и открывает окна к голому кремнию для легирования. Эти регионы позже станут истоком и стоком транзистора.

Частицы замыкают затвор

Легированные кристаллы с вытравленными затворами

После этого производится легирование, то есть введение примесей из твёрдого или жидкого источника. В качестве твёрдого источника применяется диск нитрида бора, размещённый поблизости (менее 2 мм) от пластины в трубчатой печи. Как вариант, можно приготовить жидкостный источник из фосфорной или борной кислоты в воде или растворителе — и провести легирование по стандартному процессу преднанесения/погружения во фтороводород/диффундирования/удаления глазури.

Вышеупомянутые шаги формирования рисунка затем повторяются дважды для подзатворного оксида и контактного слоя. Подзатворный оксид должен быть гораздо тоньше (менее ~750 Å), чем защитный оксид, поэтому зоны между стоком/истоком вытравливаются — и там выращивается более тонкий оксид. Затем, поскольку вся пластина оксидировалась на шаге легирования, нужно вытравить контактные окна, чтобы установить контакт металлического слоя с легированными зонами истока/стока.

Теперь все транзисторы сформированы и готовы к межсоединениям с выходом на выводную рамку. Защитный слой алюминия (400−500 нм) распыляется или термически напыляется на пластину. Альтернативой был бы метод взрывной литографии (lift-off process), когда сначала формируется фоторезист, а затем осаждается металл.

Напылённый металл

Напылённый металл

Затем на слое металла формируется рисунок методом фотолитографии и происходит травление в горячей фосфорной кислоте, чтобы завершить изготовление интегральной схемы. Заключительные шаги перед тестированием — это визуальный осмотр и высокотемпературный отжиг алюминия для формирования омических переходов.

Микросхема теперь готова для упаковки и тестирования.

У меня нет установки микросварки (принимаю пожертвования!), поэтому сейчас процесс тестирования ограничен прощупыванием пластины острым пинцетом или использованием платы flip-chip (трудно выровнять) c подключением к характериографу. Дифференциальный усилитель также эмпирически тестируется в цепи для проверки работоспособности.

Кривая IV

Кривая IV

Кривая FET Ids/Vds от с предыдущего устройства NMOS

Конечно, эти кривые далеки от идеальных (в том числе из-за излишнего сопротивления контактов и других подобных факторов), но я ожидаю улучшения характеристик, если раздобуду установку микросварки. Этим могут частично объясняться и некоторые отличия от кристалла к кристаллу. Скоро я добавлю на эту страницу новые кривые IV, характеристики транзистора и дифференциального усилителя.

habr.com